(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293759

(P2005-293759A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

F 1

テーマコード(参考)

**G 11 C 11/409**

G 11 C 11/34

3 5 3 E

5 F 0 8 3

**G 11 C 11/401**

G 11 C 11/34

3 7 1 K

5 M 0 2 4

**H 01 L 21/8242**

H 01 L 27/10

6 8 1 G

**H 01 L 27/108**

H 01 L 27/10

6 2 1 C

審査請求 未請求 請求項の数 15 O L (全 25 頁)

(21) 出願番号

特願2004-109598 (P2004-109598)

(22) 出願日

平成16年4月2日 (2004.4.2.)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100075096

弁理士 作田 康夫

(74) 代理人 100100310

弁理士 井上 学

(72) 発明者 秋山 悟

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 竹村 理一郎

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】微細化が進むと、センスアンプのオフセットが増加し、読み出し時に誤動作が生じてしまい、チップの歩留まりを低下させてしまう。

【解決手段】複数のプルダウン回路と一つのプルアップ回路から構成されるセンスアンプ回路を有する。また、複数のプルダウン回路の中、その一つにおいて、プルダウン回路を構成するトランジスタは、他方のプルダウン回路を構成するトランジスタよりも、チャネル長やチャネル幅といった定数が大きいことを特徴とする。さらに、複数のプルダウン回路のうち、トランジスタの定数が大きいプルダウン回路を先に活性化し、その後もう一つのプルダウン回路とプルアップ回路を活性化して読み出しを行う。

【選択図】図1

図1

**【特許請求の範囲】****【請求項 1】**

複数のワード線と、複数のデータ線と、その交点に配置される複数のメモリセルを具備するメモリアレーと、

前記複数のデータ線と接続された複数のセンスアンプ回路とを有し、

前記複数のセンスアンプ回路は、一方のゲートと他方のドレインが互いに接続された第1導電型の第1MISFET対と、一方のゲートと他方のドレインが互いに接続された第1導電型の第2MISFET対と、一方のゲートと他方のドレインが互いに接続された第2導電型の第3MISFET対とを各々具備し、

前記第1MISFET対は前記第2MISFET対より駆動力の大きい素子である半導体装置。 10

**【請求項 2】**

請求項1において、

前記第1導電型はN型であり、

前記第1MISFET対のソースは第1ソース線と接続され、

前記第2MISFET対のソースは第2ソース線と接続され、

前記第3MISFET対のソースは第3ソース線と接続され、

前記第1ソース線は前記第2ソース線より先に駆動される半導体装置。

**【請求項 3】**

請求項2において、

前記第2ソース線と前記第3ソース線は同じ信号に応じて、それぞれ第1電圧から第2電圧、前記第1電圧から第3電圧に変化する半導体装置。 20

**【請求項 4】**

請求項2において、

前記第1MISFET対と前記第3MISFET対との間に前記第2MISFET対に配置され、前記第2MISFET対と前記第3MISFET対との間に、前記第2ソース線を第1電圧から第2電圧に駆動する第1回路と、前記第3ソース線を前記第1電圧から第3電圧に駆動する第2回路を配置する半導体装置。

**【請求項 5】**

請求項4において、

前記第2MISFET対と前記第3MISFET対との間に、前記第1ソース線を前記第1電圧から前記第2電圧に駆動する第3回路をさらに配置し、前記第1回路内のMISFETの駆動力は前記第3回路のMISFETの駆動力より小さい半導体装置。 30

**【請求項 6】**

請求項2において、

前記第1MISFET対はゲートの形状がリング状のトランジスタで構成され、前記第2MISFET対はゲートの形状が矩形のトランジスタで構成される半導体装置。

**【請求項 7】**

請求項2において、

前記複数のセンスアンプ回路はメモリアレイの対抗する2辺に沿って配置され、その一方に配置された複数の前記第1MISFET対のソースは前記第1ソース線に共通接続されている半導体装置。 40

**【請求項 8】**

請求項2において、

前記複数のワード線のうち、非選択状態のワード線には前記第2電圧よりも低い電圧が供給される半導体装置。

**【請求項 9】**

複数のワード線と、複数のデータ線と、その交点に配置される複数のメモリセルを具備するメモリアレーと、

前記複数のデータ線と接続された複数のセンスアンプ回路とを有し、

前記複数のセンスアンプ回路は、第1プルアップ回路と第1プルダウン回路とをそれぞれ 50

具備し、

前記メモリセル内の情報を前記データ線において増幅する際に、前記第1プルダウン回路は、第1プルアップ回路より先に駆動する半導体装置。

**【請求項 10】**

請求項8において、

前記複数のセンスアンプ回路は、更に第2プルダウン回路とをそれぞれ具備し、

前記第2プルダウン回路は、第1プルダウン回路よりも小さい駆動力を持つトランジスタで構成される半導体装置。

**【請求項 11】**

請求項9において、

前記第1プルダウン回路は、ゲートがリング状でN型チャネルの第1と第2MISFETを具備し、前記第1と第2MISFETの入出力は互いにクロスカップルされ、

前記第2プルダウン回路は、ゲートがリング状になっていないN型チャネルの第3と第4MISFETを具備し、前記第3と第4MISFETの入出力は互いにクロスカップルされ、

前記第1プルダウン回路は、ゲートがリング状になっていないP型チャネルの第5と第6MISFETを具備し、前記第5と第6MISFETの入出力は互いにクロスカップルされる半導体装置。

**【請求項 12】**

請求項11において、

前記第2プルダウン回路は、前記第1プルダウン回路と前記第1プルアップ回路との間に配置される半導体装置。

**【請求項 13】**

請求項12の半導体装置は、前記メモリアレイに対し、前記第1プルダウン回路を駆動する第1回路と、前記第2プルダウン回路を駆動する第2回路と、前記第1プルアップ回路を駆動する第3回路とを複数具備し、前記複数の第2プルダウン回路と複数の前記第1プルアップ回路との間に分散して配置される半導体装置。

**【請求項 14】**

請求項11において、

前記複数のメモリセルは、MISFETとキャパシタをそれぞれ具備し、前記複数のメモリセル内のMISFETの拡散層は前記第1乃至第4MISFETの拡散層と同じウエルに形成されている半導体装置。

**【請求項 15】**

請求項14において、

前記複数のワード線を駆動する第4回路を具備し、

前記第1と第2プルダウン回路は第1電圧から第2電圧に変化することで駆動され、

前記第4回路は前記第2電圧よりも低い電圧を前記複数のワード線のうち、選択されていないワード線に対し、印加する半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体記憶装置に関する。特に低電力、高速、高集積な半導体記憶装置および、論理回路と半導体記憶装置を集積した半導体装置の差動増幅動作の部分に関する。

**【背景技術】**

**【0002】**

半導体記憶装置の一つである、ダイナミックランダムアクセスメモリ(Dynamic Random Access Memory、以下DRAMと記す)は、大型コンピュータ、パソコンコンピュータのメインメモリや、携帯電話、デジタルカメラといったデジタル家電のワークメモリなど、我々が日常利用する様々な電子機器に数多く搭載されている。これに加え、近年の機器の低消費電力化、高性能化のニーズに伴い、搭載されるDRAMも低電力化、高速化、大容量化といった高性能化が強く求められている。

10

20

30

40

50

高性能なDRAMを実現するために、最も有効な手段として挙げられるのが、DRAMのメモリセルに用いられるセルトランジスタや、セルキャパシタを微細化することである。微細化することで、メモリセルを小さくできる。そのためデータ線長が短くなり、データ線の寄生容量を低減できるので、低電圧動作が可能となり、低電力化が実現できる。また、データ線の寄生容量を低減できるので、高速なセンスアンプ動作が可能となる。さらには、メモリの大容量化により機器の高性能化が実現できるなど、微細化によって受ける恩恵は非常に大きい。したがって、現行製品のみならず、今後開発される製品も、一般的には微細化によって、高性能化が推進されると考えられている。

#### 【0003】

しかしながら、現行の製品のように、0.1mmノード、あるいはそれ以降の0.065mm、0.045mmノードにおいては、前述したような高性能化の効果だけではなく、微細化が進むにつれて、様々な副作用があらわれる。その副作用とは、微細化によって増加する素子特性のバラツキにより、メモリセルの信号を読み出す際に生じる誤動作のことである。ここで、素子特性のバラツキとは、例えばセルトランジスタの閾値電圧や、セルトランジスタから流れるリーク電流の大きさの分散値(平均値からのずれ)である。このように、素子特性のバラツキが大きいと、DRAMのデータ保持特性が劣化してしまい、チップの歩留まりが低下するといった問題を引き起こす。特に、センスアンプ回路の閾値電圧のバラツキが、今後著しく増加すると懸念される。その理由は、近年のDRAMでは、メモリセルのデータ線ピッチが非常に狭いため、データ線に接続されるセンスアンプ回路を小さくレイアウトして配置する必要があるためである。このため、センスアンプを構成するトランジスタの加工誤差が大きくなり、そのペアトランジスタの閾値電圧のバラツキを増大させてしまう。一般的にこの問題は、センスアンプのオフセットと言われ、DRAMの性能に対して、非常に大きな影響を及ぼす事項の一つである。また、センスアンプのオフセット問題は、非特許文献1に詳細に記載されており、オフセットを低減することは、DRAMの歩留まり向上に大きく寄与することが良く知られている。したがって、微細化による高性能化を実現するためには、プロセス改善による加工誤差低減のみならず、センスアンプオフセットを抑えるような回路対策を講じることが、今後非常に重要な技術となる。

#### 【0004】

このような課題の解決を試みた近年の例として、非特許文献2では、センスアンプのオフセットを相殺する技術が開示されている。この方法は、カレントミラー作動アンプを用い、データ線のプリチャージ電圧を補正することで、実質的にセンスアンプのオフセットを小さくすることができる。しかしながらこの方法は、センスアンプに追加する素子数が非常に多く、センスアンプの面積が大きくなり、チップサイズの増加を招く。さらに、駆動する制御信号も増えるため、タイミングマージンが増加し、速度の低下も懸念される。また、非特許文献3では電荷転送型のセンスアンプが開示されている。この方法は、データ線に接続されるスイッチトランジスタを介して、センスアンプなどの周辺回路に蓄積された電荷をメモリセル側のデータ線に転送し、センスアンプに大きな電位差を発生させる手法である。そのため、センスアンプのオフセットが増加した場合でも、オフセット以上の電位差をセンスアンプに印加できるので、本質的にバラツキに強く低電圧動作に優れている。しかしながら、この手法も追加のプリチャージ回路や再書き込み用のスイッチトランジスタなど、追加素子数が多く、チップサイズの増加を招くといった課題が残る。

#### 【0005】

【特許文献1】特開平7-226081号公報

#### 【0006】

【特許文献2】特開平2-146177号公報

【非特許文献1】Kiyoo Itoh, "VLSI Memory Chip Design", pp.195-247, Springer, 2001

【非特許文献2】Sang Hoon Hong et al., ISSCC2002 Dig. Tech. Papers, pp.154-155

【非特許文献3】Jae-Yoon Simm et al., 2003 Symposium on VLSI Circuits Dig. Tech. Papers, pp.289-292

#### 【発明の開示】

10

20

30

40

50

【発明が解決しようとする課題】

【0007】

上記のような状況のもと、本発明が解決しようとする課題は、追加素子数の少ない、高速動作が可能であり、かつセンスアンプのオフセットを低減できるセンスアンプ回路を実現することである。

本発明者等は、上記課題を解決するため、本願に先立ちセンスアンプのオフセットが読み出し動作に与える影響と、最小限のトランジスタの追加で実現可能な、オフセット低減できるセンスアンプの構成について検討した。

【0008】

図18は、代表的なDRAMの回路構成を示した図である。図18において、メモリセルMCは、ドレインがデータ線DLBに接続されたアクセストランジスタTN0と、電極の片側が、アクセストランジスタTN0のソースに接続されたセルキャパシタCS0から構成される。なおここでは、メモリセルMCにLの電位が保持されているとして以後説明する。複数のメモリセルが接続されたデータ線対DLT、DLBはスイッチトランジスタSHRを介して、センスアンプ回路SA0に接続されている。センスアンプ回路SA0は、カラムスイッチYSW、プリチャージ回路PCH、プルダウン回路NDRV、プルアップ回路PDRVから構成される。図19は、図18の従来のセンスアンプ回路SA0を使って、メモリセルMCの信号を読み出したときのタイミング波形であり、誤動作が起こったことを示している。まず、プリチャージ回路PCHを駆動して、データ線をプリチャージする。その後、プリチャージ回路PCHをネゲートし、選択サブアレイSARY側のスイッチトランジスタSHRLはハイにドライブした状態を維持しておき、もう一つのスイッチトランジスタSHRRはロウにネゲートする。サブワード線WL0がアサートされると、メモリセルMCからデータ線DLBに、Lに対応した微小な信号が出力され、データ線対に信号差dVsigが表れる。

10

20

30

40

50

【0009】

その後、プルダウン回路NDRVのコモンソース線CSNとプルアップ回路PDRVのコモンソース線CSPをそれぞれ接地電圧VSS、データ線電圧VDLに駆動することで、通常の場合、破線で示したように微小な電位差dVsigが、ハイレベルのVDLとロウレベルのVSSまで増幅され、カラムスイッチYSW及びローカルデータ線L10T、L10Bを経由して、後段の回路まで転送される。しかし先ほど述べたように、微細化が進むとセンスアンプのオフセットが増加する。例えば、図18において、プルダウン回路NDRVのNMOSトランジスタTN1の閾値電圧VTN1と、NMOSトランジスタTN2の閾値電圧VTN2との差、VTN1-VTN2が、微小な信号差dVsigよりも大きくなり、同時に、プルアップ回路PDRVのPMOSトランジスタTP1の閾値電圧VTP1と、PMOSトランジスタTP2の閾値電圧VTP2との差、VTP1-VTP2が、微小な信号差dVsigよりも大きくなる場合がある。この場合、データ線DLTがデータ線DLBよりも強くL側にドライブされるため、図19の実線で示したように読み出しの誤動作が生じてしまう。

【0010】

このような誤動作を防ぐためには、プルダウン回路NDRVやプルアップ回路PDRVを構成するトランジスタの定数を大きくしてオフセットを低減する、あるいは、微小な信号差dVsigを、少なくともオフセット以上の電圧差に増幅する、プリアンプ機能を追加すればよい。前者の具体的な手段としては、単純にプルダウン回路NDRVとプルアップ回路PDRVを構成するトランジスタ、TN1、TN2、TP1、TP2のチャネル長やチャネル幅を大きくして、オフセットを低減する方法が挙げられる。しかしこの方法だと、チャネル長が長くなることで、センスアンプ回路SA0の駆動電流が低下してしまう場合があり、メモリのアクセス速度がしまう可能性がある。一方、プリアンプ機能を追加する方法としては、例えばプルダウン回路NDRVをもう一つ追加すればよい。追加したプルダウン回路を先に駆動して、データ線を最初からあるプルダウン回路及び、プルアップ回路のオフセット以上の電圧差までプリアンプすれば、読み出し誤動作を防げる可能性がある。

【0011】

また追加トランジスタも二つと少なく、面積増加も最小限に抑えられる。このような回路構成の公知例として、特許文献1、特許文献2には、複数のプルダウン回路を用いたセン

50

スアンプ回路が開示されている。この開示の手法は追加回路が少なく、面積オーバヘッドも小さい。しかしこれらの方法は、センスアンプ回路の高速化について検討されているが、オフセットを低減し、読み出し誤動作を防ぐ手段については考慮されていない。すなわち、開示の手法では、プリアンプ機能を有していないため、原理的にオフセットの問題点を解決できていない。

以上のような状況のもと、本発明の目的の一つは、将来顕著になるセンスアンプオフセットを低減し、読み出し誤動作を防ぐことである。また、本発明の更なる目的の一つは、オフセットを低減しつつ、センスアンプ回路SA0のレイアウト面積を図ることである。

#### 【課題を解決するための手段】

##### 【0012】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

複数のメモリセルと複数のセンスアンプ回路からなる、半導体記憶装置において、前記センスアンプ回路は、少なくとも二つ以上のプルダウン回路を有する。また、前記プルダウン回路の一つを先に駆動して、後段のプルダウン回路およびプルアップ回路のオフセット以上にデータ線を増幅した後、前記後段のプルダウン回路と、前記後段のプルアップ回路を駆動する。このとき、前述した先に駆動するプルダウン回路においては、トランジスタのオフセットが小さくなるように、あらかじめトランジスタのチャネル長やチャネル幅を大きくしておくとよい。さらに、前記センスアンプは、複数のプルアップ回路から構成されてもよい。

#### 【発明の効果】

##### 【0013】

本発明では、複数のメモリセルと複数のセンスアンプ回路を含む半導体集積回路において、前記センスアンプのオフセットを低減できる。その結果、低電圧動作、高速読み出し動作が可能となる。またオフセットを低減できるので、データ線長を長くでき、メモリセル占有率を高くすることができます。すなわち、高集積な半導体記憶装置を実現できる。

#### 【発明を実施するための最良の形態】

##### 【0014】

以下、図面を用いて本発明の実施例を説明する。実施例の各ブロックを構成するトランジスタは、特に制限されないが公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような1個の半導体基板上に形成される。即ち、ウエルと素子分離領域と酸化膜が形成される工程の後、ゲート電極とソース・ドレイン領域を形成する第1と第2半導体領域とを形成する工程とを含む工程により形成される。MOSFET(Metal Oxide Semiconductor Field Effect Transistor)の回路記号はゲートに丸印をつけないものはN型MOSFET(NMOS)を表し、ゲートに丸印をつけたP型MOSFET(PMOS)と区別される。以下MOSFETを簡略化してMOSあるいはMOSトランジスタと呼ぶことにする。但し本発明は金属ゲートと半導体層の間に設けられた酸化膜を含む電界効果トランジスタだけに限定されるわけではなく絶縁膜を間に含むMISFET(Metal Insulator Semiconductor Field Effect Transistor)等の一般的なFETを用いた回路に適用される。

##### 【0015】

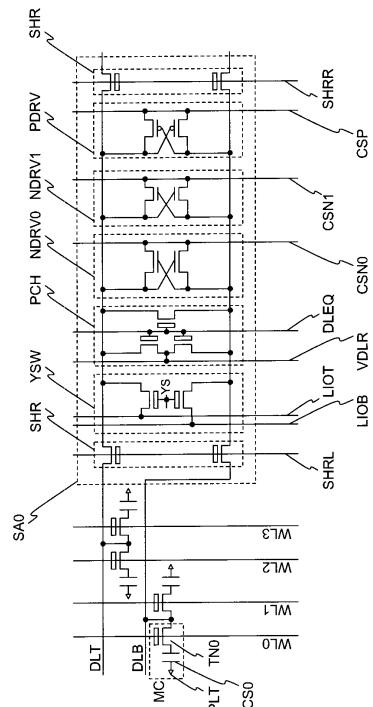

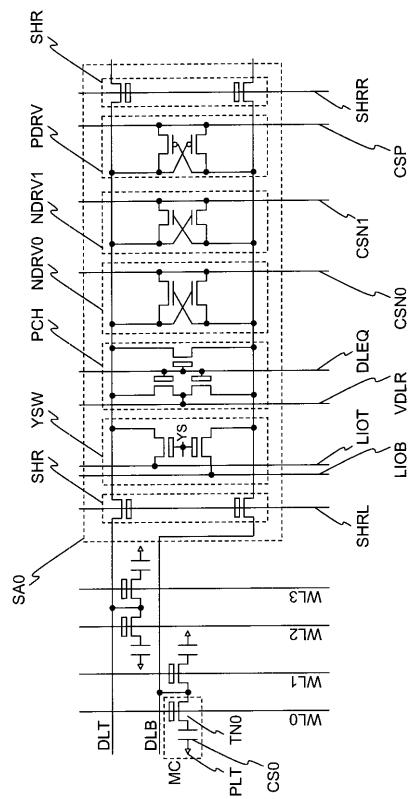

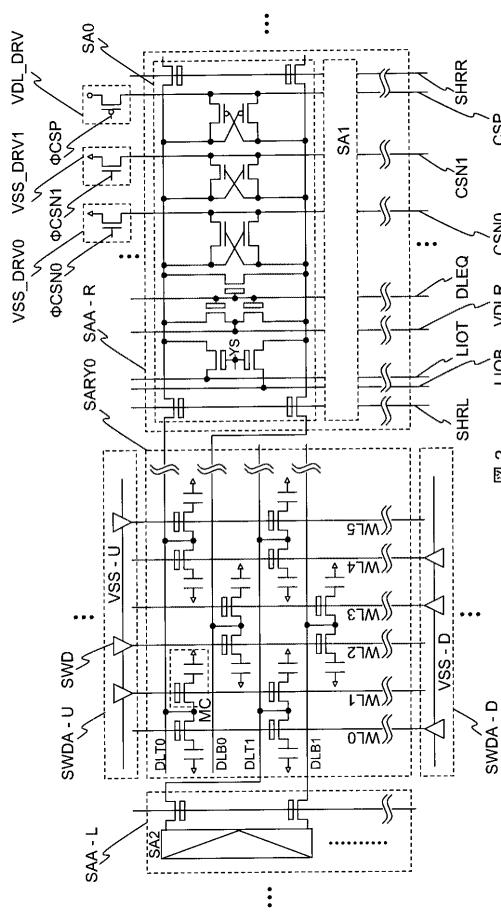

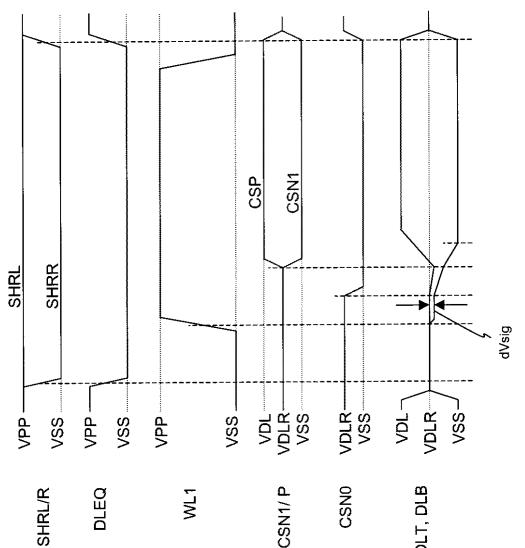

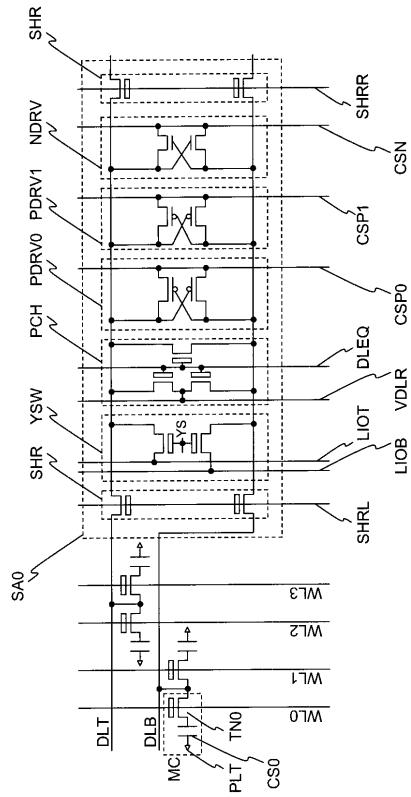

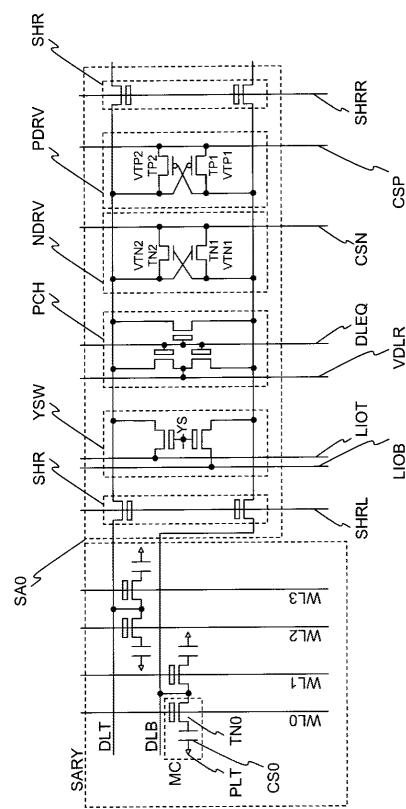

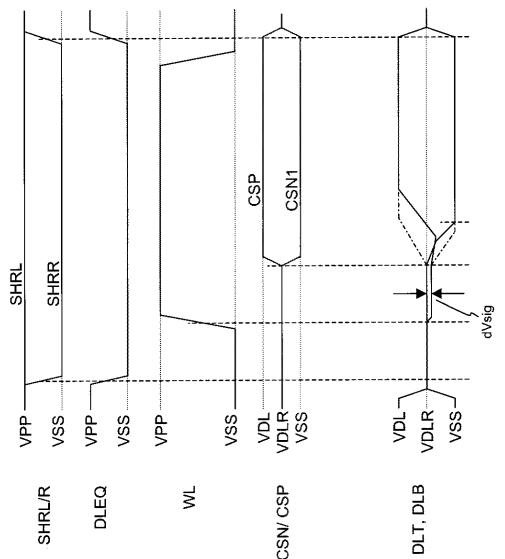

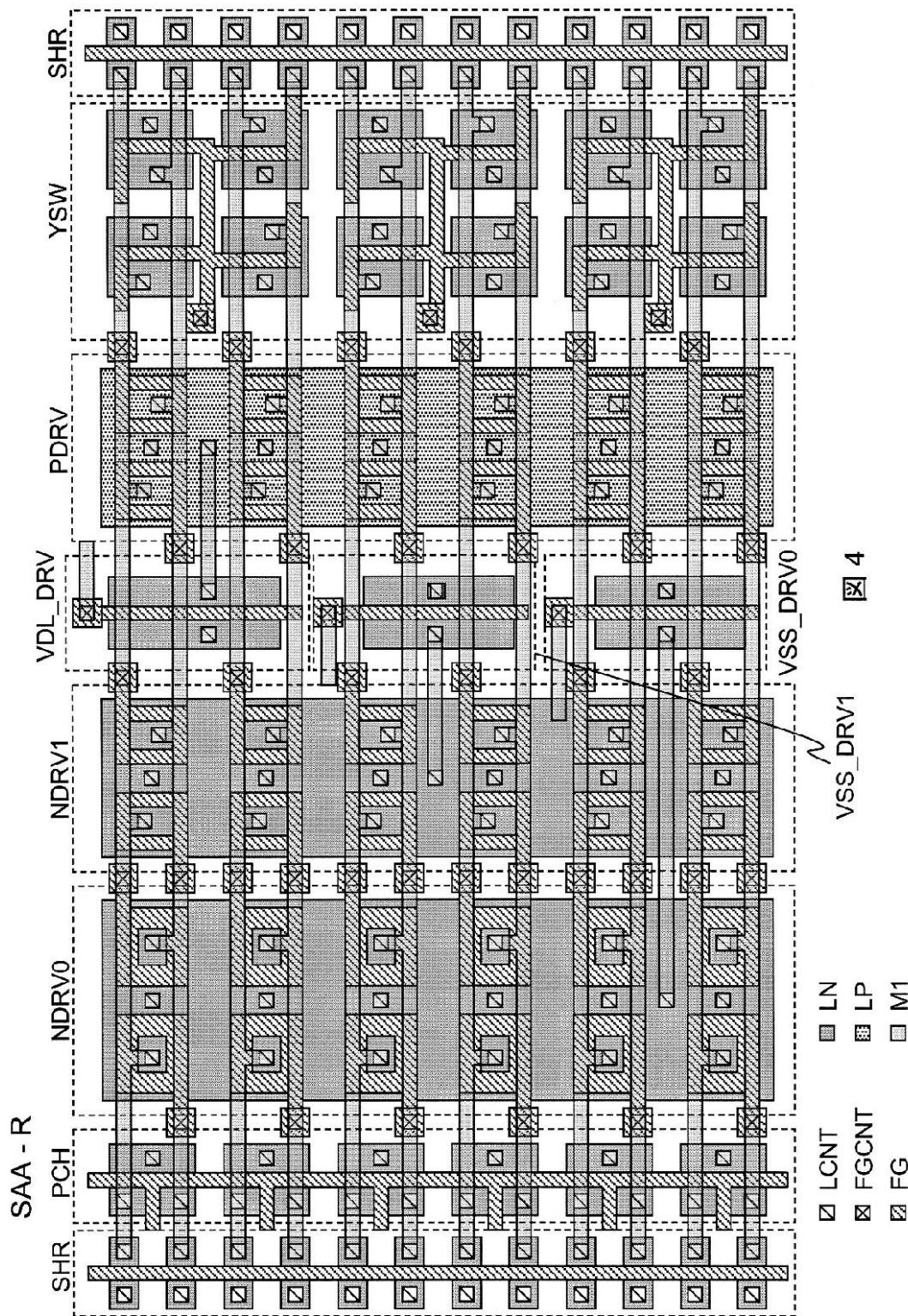

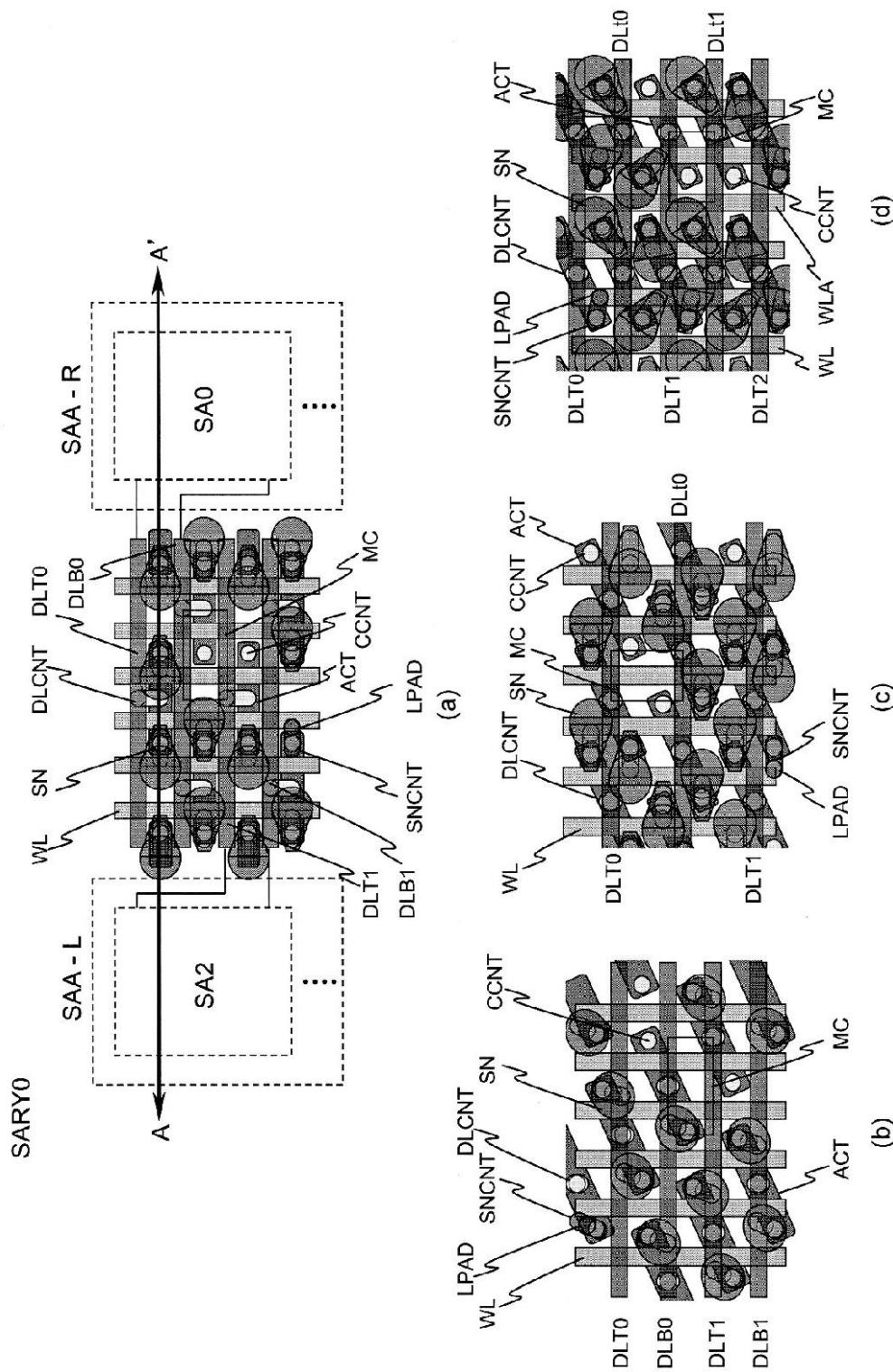

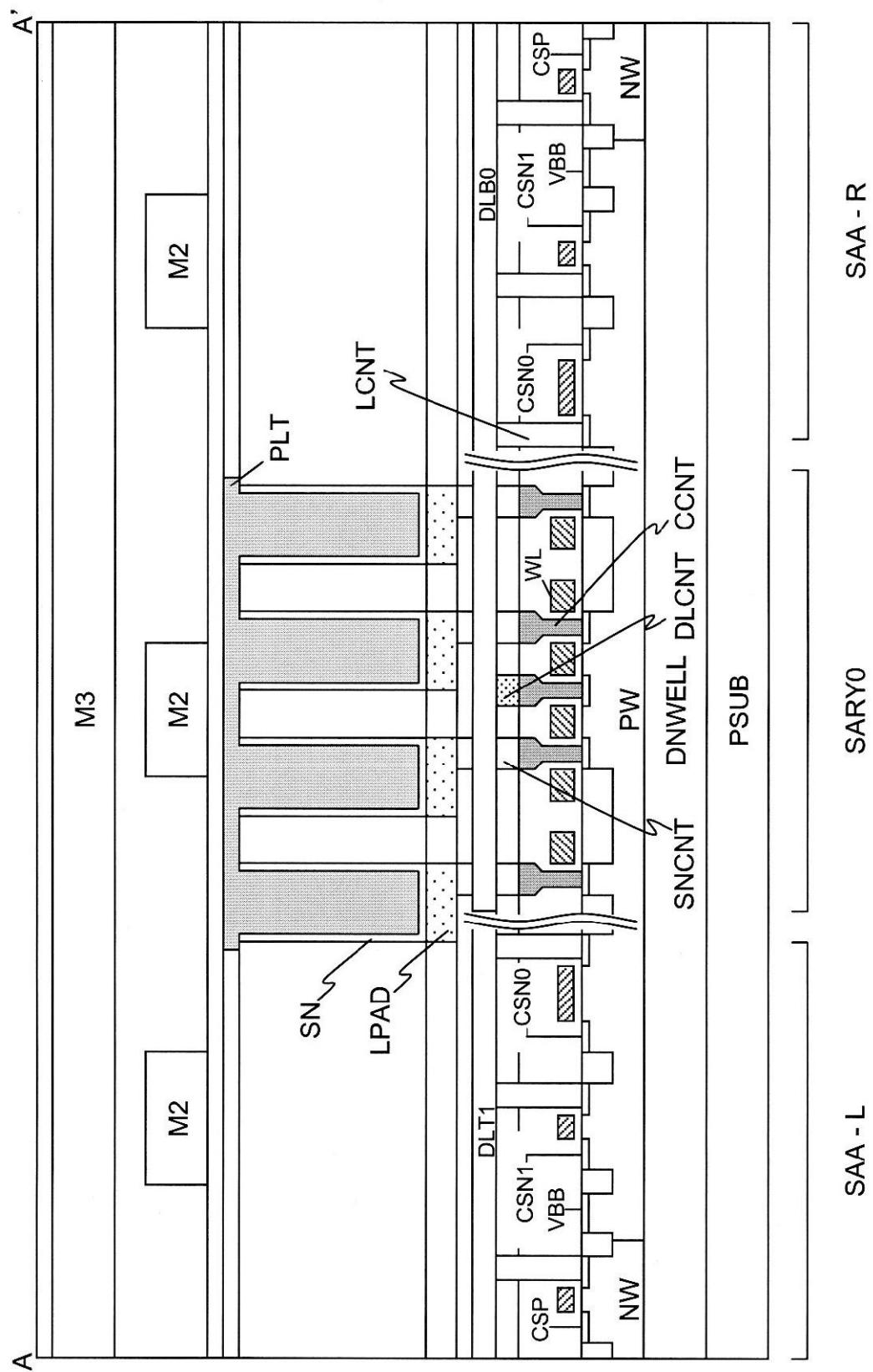

図1は、本発明の第一の実施例であるセンスアンプ回路SA0と、それに接続される複数のメモリセルMCを示す図である。図2は、本願の第一の実施例であるセンスアンプ回路SA0によって構成されるセンスアンプ回路アレイSAA-R、SAA-Lと、複数のメモリセルMCからなるサブアレイSARY0と、複数のサブワードドライバSWDからなるサブワードアレイSWDA-U、SWDA-Dから構成されるバンクBANKを示す図である。図3は、図1に示したセンスアンプ回路SA0のタイミング波形を示す図である。図4、図5は、図1に示したセンスアンプ回路SA0のレイアウト図である。図6は、図1に示した複数のメモリセルMCの平面レイアウトである。図7は、図6に示した複数のメモリセルMCとセンスアンプ回路SA0の断面図の一部を示した図である。図8は、図2に示したバンクBANKを複数用いて構成した、DRAMのブロック図を示している。

10

20

30

40

50

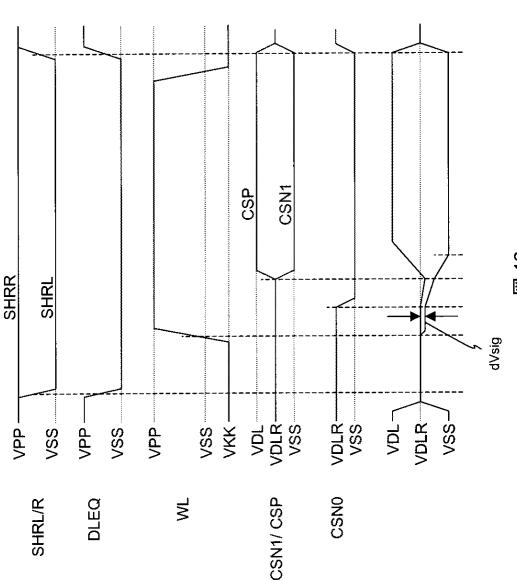

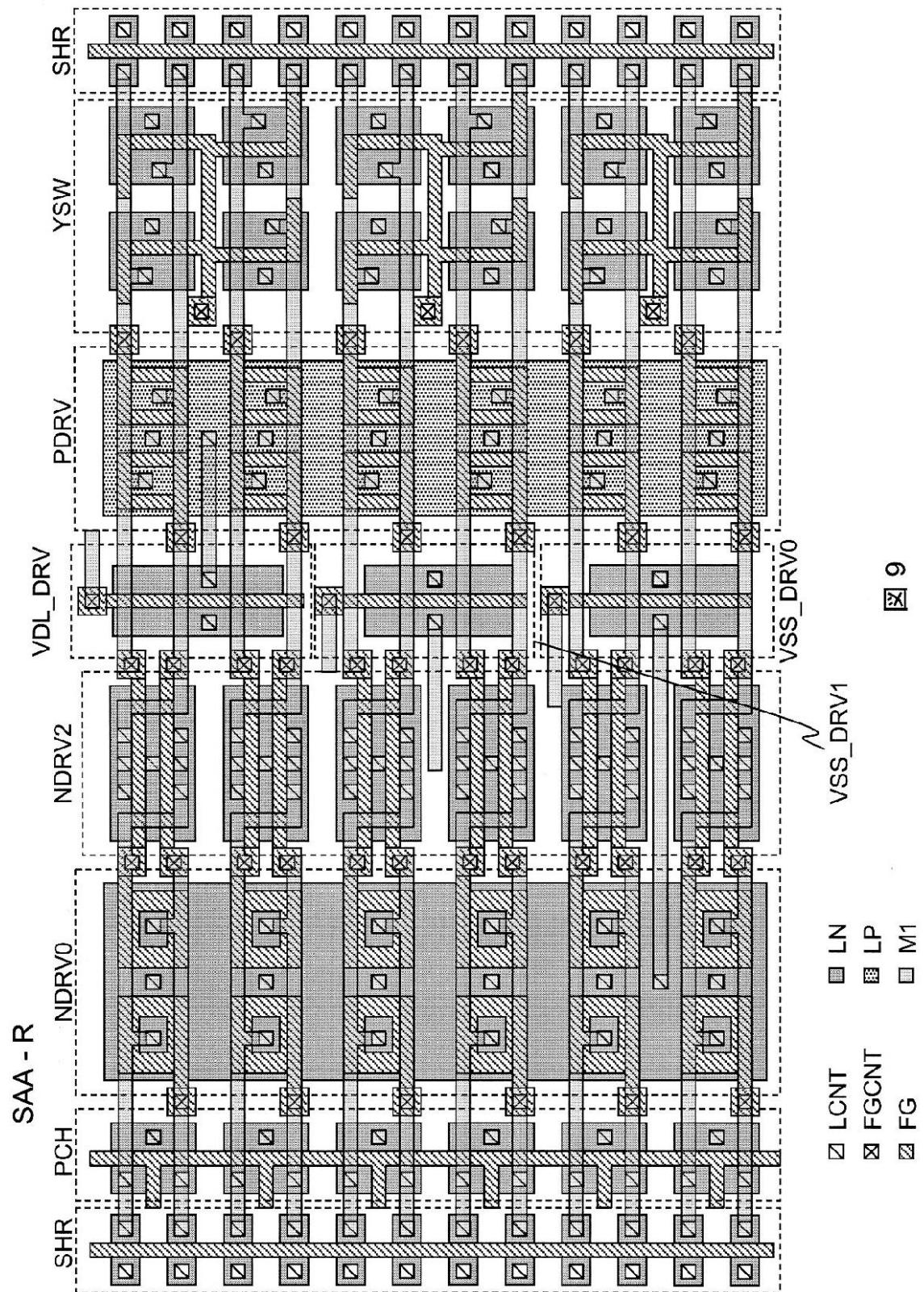

## 【0016】

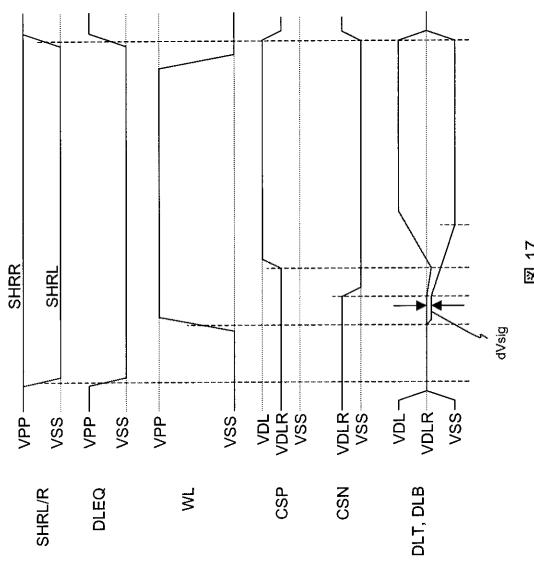

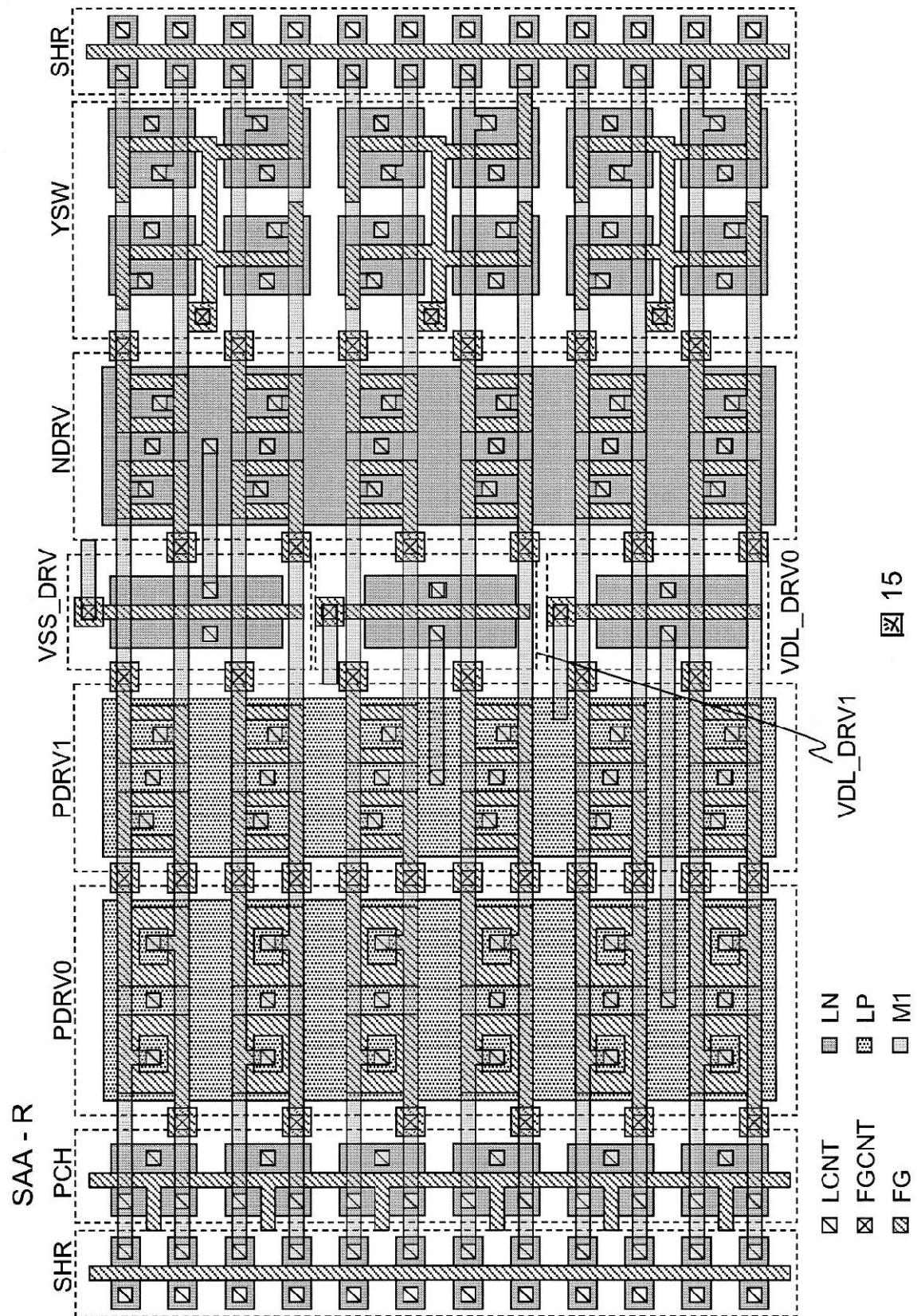

図9は、図1に示したセンスアンプ回路SA0のレイアウトの変形例を示した図である。図10は、図9に示したセンスアンプ回路SA0のタイミング波形を示す図である。図11は、ワード線に負電圧を印加するための、サブワードドライバ回路の具体例である。図12は、本実施のセンスアンプ回路に、ネガティブサブワードドライバを適用した第2の実施例の動作波形を示している。図13は、本発明の第三の実施例であり、複数のプルアップ回路を用いて構成したセンスアンプ回路の一例である。図14は、図13のセンスアンプ回路の動作波形を示した図である。図15は、図14のセンスアンプ回路を複数用いて構成されたセンスアンプアレイの平面レイアウトである。図16は、本発明の第四の実施例であり、プルダウン回路とプルアップ回路を一つずつ用いて構成したセンスアンプ回路の一例である。図17は、図16のセンスアンプ回路の動作波形を示す図である。図18は、従来のセンスアンプ回路を示す図である。図19は、図18の従来のセンスアンプ回路の動作波形と、その誤動作について説明した図である。

10

## 【実施例1】

## 【0017】

以下ではまず図1-図10について説明する。

図1の実施例では、複数のプルダウン回路NDRV0、NDRV1、一つのプルアップ回路PDRV、スイッチトランジスタSHR、カラムスイッチYSW、プリチャージ回路PCHから構成されるセンスアンプ回路SA0と、複数のメモリセルMCから構成されるサブアレイSARY0が記載されている。またそれぞれの記号は、プルダウン回路NDRV0、NDRV1を駆動するコモンソース線CSN0、CSN1、プルアップ回路PDRVを駆動するコモンソース線CSP、スイッチトランジスタ駆動線SHRR、SHRL、カラムスイッチ駆動線YS、ローカルデータ線L10T、L10B、プリチャージ駆動線DLEQ、プリチャージ電圧VDLR、サブワード線WL0-WL3、データ線DLT、DLB、アクセストランジスタTN0、セルキャパシタCS0、プレート電極PLTを示している。

20

複数のメモリセルMCは、N型チャネルMOSトランジスタTN0とキャパシタCS0をそれぞれ具備するDRAMメモリセルである。プルアップ回路PDRVは、一方のゲートと他方のドレインが互いに接続されたP型チャネルのMOSトランジスタ対で構成され、プルダウン回路NDRV0、NDRV1はそれぞれ、一方のゲートと他方のドレインが互いに接続されたN型チャネルのMOSトランジスタ対で構成される。

30

## 【0018】

図1に示すように、本実施例における複数のプルダウン回路のうち、プルダウン回路NDRV0を構成するトランジスタは、プルダウン回路NDRV1を構成するトランジスタと比較すると、例えば、チャネル長が長い、チャネル幅が広いというように、そのトランジスタの駆動力（定数）が大きい。トランジスタの定数を大きくする理由は、プルダウン回路NDRV0の駆動電流を大きくし、さらにオフセットをも低減できるためである。このとき、もう一つのプルダウン回路NDRV1を構成するNMOSトランジスタのチャネル長は短い、あるいはチャネル幅は広い方が望ましい。その理由は、プルダウン回路NDRV0を構成するトランジスタのチャネル長が長いので、プルダウン回路NDRV0の駆動電流が低下する場合がある。したがって、プルダウン回路NDRV1を構成するトランジスタのチャネル長を短くする、あるいはチャネル幅を広くして、駆動電流を大きく取れるようにしておけば、データ線をより高速に增幅できるからである。このように、オフセットを充分に低減したプルダウン回路NDRV0だけを追加し、コモンソース線CSN0を駆動して、後段のプルダウン回路NDRV1、プルアップ回路PDRVのオフセットよりも大きな電圧差までデータ線対をプリアンプさえすれば、読み出しの誤動作を防ぐことができる。なお動作の詳細は、後述する。

40

## 【0019】

図2は、本発案の実施例であるセンスアンプ回路SA0を複数用いたセンスアンプアレイSA-A-R、SAA-LとサブアレイSARY0、サブワードドライバSWDA-U、SWDA-Dを用いて構成したバンクBANKの具体例である。図2の例では、コモンソース制御線CSN0、CSN1、CSPは、複数のセンスアンプ回路SA0-SA5に対して、一つずつ配置されている。コモンソース制御線CSN0、CSN1、CSPにより制御されるコモンソース線を駆動する回路VSS\_DRV0、VS

50

S\_DRV1、VDL\_DRVは、サブアレイSARY0毎に一組ずつ設けられ、センスアンプアレイSAA-R、SAA-Lは、所謂分散ドライブ方式を用いている。サブワードドライバSWDA-U、SWDA-Dは、サブアレイ毎SARY0に設けられ、サブアレイSARY0内のサブワード線WL0,WL1,WL2,WL3,WL4,WL5をアドレスの選択により駆動している。VSS-U、VSS-Dは接地電圧である。

### 【0020】

図1のセンスアンプ回路SA0は、図18の構成と比較すると、追加トランジスタが一対のNMOSトランジスタのみであるため、面積増加が非常に小さい。したがって、図2に示すような、狭いデータ線ピッチにレイアウトでき、チップサイズ増加を抑えることができる。また、センスアンプ回路SA0は、プルダウン回路NDRV0の追加以外は、従来のセンスアンプ回路の構成と同じである。そのため、本実施のセンスアンプ回路SA0を用いれば、レイアウトや配線構成なども最小限の変更で抑えられる。また、図2ではサブワード線に対しデータ線対が交差する折り返しデータ線型のアレイ構成を示したが、もちろん本発案はこれに限定されない。例えば、いわゆる開放データ線型のアレイ構成でもいうまでもなく、本発案の主旨を逸脱しない範囲で様々な変更が可能であることは言うまでもない。

### 【0021】

図3は、図1に実施のセンスアンプ回路SA0の動作を説明する動作波形である。まず、プリチャージ駆動線DREQをアサートして、データ線対をプリチャージ電位VDLRにプリチャージする。プリチャージ駆動線DREQの駆動方法は様々あるが、例えばロウアドレ丝信号やサブアレイ選択信号を利用すればよい。同様に、スイッチトランジスタSHRRを、ロウアドレ丝等を利用してネゲートする。このようにすることで、選択サブアレイSARY0のデータ線対とセンスアンプアレイSAA-Rが電気的に接続される。次にサブワード線WL1がアサートされると、複数の選択メモリセルから保持されている信号が、データ線に出力される。例えば、図2のメモリセルMCのLに対応した微小な信号が、データ線DLT0に出力される。その後、コモンソース線CSNOが接地電圧VSSに駆動されると、データ線DLT0はデータ線DLB0に比べて強くVSS側にドライブされる。

### 【0022】

プルダウン回路NDRV0のトランジスタのチャネル長やチャネル幅を大きくし、オフセットを充分に低減したため、データ線DLT0をより選択的にLレベルのVSSに駆動することができる。プルダウン回路NDRV0を用いて、データ線DLT0を、プルダウン回路NDRV1、プルアップ回路PDRVのオフセット以上の電圧差に増幅した後、コモンソース線CSN1、CSPをそれぞれ駆動してデータ線対DLT0、DLB0をロウレベルのVSSとハイレベルのVDLまでそれぞれ増幅する。対となっているコモンソース線CSN1、CSPは同じ制御信号に基づいて駆動され、その結果ほぼ同じタイミングでそれぞれVDLRからVSS、VDL電位に変化させる。メモリセルMCに再書き込み動作をした後、サブワード線WL0をネゲートする。その後、コモンソース線CSN0、CSN1、CSPをプリチャージ電圧VDLRにプリチャージして、プリチャージ駆動線DREQをアサートし、データ線対を所望のプリチャージ電位VDLRにプリチャージする。以上が、本発明の実施例のセンスアンプ回路SA0の動作である。

### 【0023】

このように、オフセットを充分に低減したプルダウン回路NDRV0を追加することで、読み出し誤動作を防ぐことができる。また、DRAMの信号量設計における、いわゆるセンスアンプオフセットマージンを抑える事ができる。したがって、データ線電圧VDLを低くして、信号量が小さくなつた場合であつても、前述したセンスアンプオフセットマージンがほとんど不要となるため、安定した読み出し動作が可能となる。すなわち、低電圧動作が可能となり、低消費電力化が実現できる。また、データ線長を長くしても安定した読み出し動作が可能となる。この理由を以下に簡単に説明する。一般的には、データ線長を長くするとデータ線寄生容量が大きくなるため、データ線に出力される信号量が小さくなってしまう。その結果、センスアンプ回路に印加される電圧差が小さくなり、センスアンプ動作が不安定になる。しかし、本実施のセンスアンプ回路SA0を用いれば、センスアンプ回路SA0に印加される電圧差が小さい場合でも、プルダウン回路NDRV0のオフセットが充分に小さいため、データ線をプリアンプすることができる。つまり、プルダウン回路NDRV0を用

10

20

30

40

50

いて、プルダウン回路NDRV1、プルアップ回路PDRVのオフセット以上にデータ線をプリアンプできるので、データ線長を長くしても安定した読み出し動作が可能となる。言い換えると、メモリ占有率の高い、高集積な半導体記憶装置が実現できる。

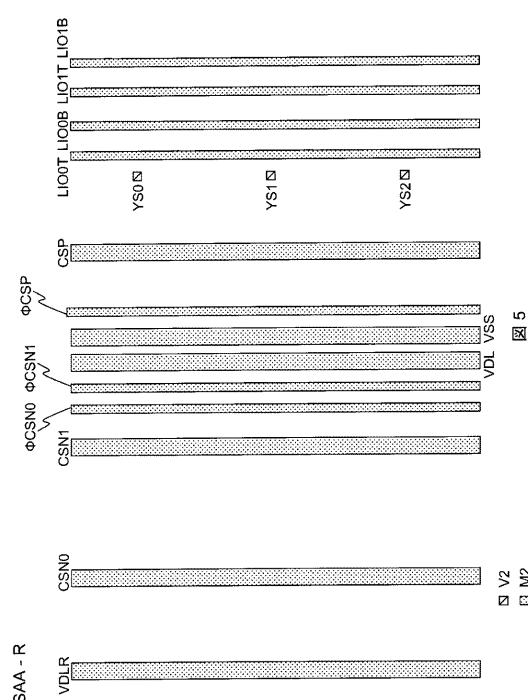

#### 【0024】

図4、図5は、図1の実施例であるセンスアンプ回路SA0を複数用いて構成した、センスアンプアレイSAA-Rの平面レイアウトである。破線部で囲まれた部分を示す記号の一部は、それぞれ図1のセンスアンプ回路SA0を構成する各回路に対応している。それ以外の、YS0-YS2はカラムスイッチ駆動線、L100T、L100B、L101T、L101Bはローカルデータ線を示している。なお、図5は、コンタクトV2と第2層の配線層M2の配線レイアウトの一例が示されている。また、図4、図5における記号の意味は、ゲート電極と第1層の配線層M1(データ線)を接続するゲートコンタクトFGCNT、拡散層LN、LP、ゲート電極FG、拡散層LN、LPと配線層M1を接続する拡散層コンタクトLCNT、第2層の配線層M2と第3層の配線層M3を接続するコンタクトV2である。尚、第1層の配線層M1と第2層の配線層M2を接続するコンタクトV1は図示されていない。また図4において、コモンソースドライバVSS\_DRV0、VSS\_DRV1、VDL\_DRVは、コモンソース線CSN0、CSN1、CSPを駆動するために用いられ、例えば、複数のセンスアンプ回路SA0-SA5にそれぞれひとつずつ配置される、いわゆる分散ドライブ方式のレイアウトの一例を示している。

#### 【0025】

すなわち、一つのサブアレイSARY0に対し、複数のプルダウン回路NDRV0及び、対として動作する複数のプルダウン回路NDRV1と複数のプルアップ回路PDRVとの間に、複数のコモンソース線を駆動する回路VDL\_DRV、VSS\_DRV0、VSS\_DRV1が分散配置されている。これらの駆動回路をVDL\_DRV、VSS\_DRV0、VSS\_DRV1を制御する制御線CSN0、CSN1、CSPは、プリチャージ電圧VDLRを供給する電源線と、ローカルデータ線L10T、L100T、L101T、L10B、L100B、L101Bと、コモンソース線CSN0、CSN1、CSP、CSPと、データ線電圧VDL、接地電圧VSSを供給する電源線と、同方向に延在し、同じ配線層で形成される。これらの配線はワード線と同方向に形成される。カラムスイッチ駆動線YS0-YS2は、コンタクトV2を介してカラムスイッチYSWと接続され、第2層の配線層M2より上層の第3層の配線層M3に形成され、データ線と同じ方向に延在する。

#### 【0026】

以上のように、サブアレイSARY0に対応するセンスアンプアレイSAA-Rで毎に駆動回路を分散配置することで、高速にコモンソース線を駆動することができ、またプルダウン回路NDRV1とプルアップ回路PDRVの間に配置することで、効率よくレイアウトを行うことが可能となる。なお、図面が煩雑になるため、配線層の一部は省略した。

図4、図5に示したように、図1に実施したセンスアンプ回路SA0の追加回路は、プルダウン回路NDRV0だけである。したがって図4からわかるように、センスアンプ回路SA0の面積増加も少ない。また、レイアウトの対称性にも優れているため、データ線ノイズも小さいという利点もある。さらに、従来のプルダウン回路NDRV1と同様のレイアウトが可能であり、追加回路に伴う追加配線は、コモンソース線CSN0のみであり実現が容易である。プルダウン回路NDRV0、NDRV1とプルアップ回路PDRV内のトランジスタのゲートはリング状のトランジスタで形成されている。このようにゲート電極をリング状にすることで、よりセンスアンプ回路のオフセットを低減できる。

#### 【0027】

なお図4においては、プルダウン回路NDRV0など、ゲート電極FGの形状をリング状で示したが、もちろん本発案がこれに限定されるものではない。コの字型や矩形のゲート電極FGなどさまざまな変形が可能である。また、コモンソースドライバVSS\_DRV0のチャネル幅を、図4に示したチャネル幅よりも狭くする、あるいはコモンソース制御線CSN0をゆっくり駆動するといった方法を適用して、図3に示されたコモンソース線CSN0の駆動速度をより遅くして、センスアンプ回路SA0を動作させてもよい。このようにすることで、プルダウン回路NDRV0のオフセットが大きくなった場合においても、データ線DLT0を正確にプリアンプできるという利点がある。また、図では示していないが、コモンソース線CSPを、

データ線のハイレベルVDL以上に昇圧する、所謂オーバードライブ方式と組み合わせて利用してもよい。その場合も、低電圧動作、高速動作といった効果が得られる。以上のように、本発案の主旨を逸脱しない範囲で様々な変形が可能であることは言うまでもない。

#### 【0028】

図6は、図1に示したメモリセルMCの平面レイアウトと、それに接続されるセンスアンプアレイSAA-L、SAA-Rを示した図である。アクセストランジスタTN0は、サブワード線WL、拡散層ACTから構成され、セルキャパシタCS0は、蓄積ノードSNとプレート電極PLTからなる。その他の記号は、拡散層ACTをその上部の配線やコンタクトに接続するためのセルコンタクトCCNT、データ線DLT、DLBとセルコンタクトCCNTを接続するデータ線コンタクトDL\_CNT、ランディングパッドLPADとセルコンタクトCCNTを接続する蓄積ノードコンタクトSNCNTである。ここで、ランディングパッドLPADは蓄積ノードSNと蓄積ノードコンタクトSNCNTを接続するコンタクトであり、セルキャパシタCS0の位置を最適化することができるので、セルキャパシタCS0の表面積を大きくすることができる。もちろん、セルキャパシタCS0の容量が充分に確保できるのであれば、ランディングパッドLPADを利用しなくてもよい。その場合、プロセス工程を削減できるのでコストを低減できる。

#### 【0029】

また、図6のようにメモリセルMCのレイアウトは様々な変形が可能である。図6(a)は、所謂折り返し型データ線構造であり、拡散層ACTが単純な矩形であるため、微細化が容易であるという利点がある。また図6(b)は、擬似折り返し型データ線構造である。(a)との違いは、拡散層ACTがサブワード線WLに対して斜めにレイアウトされていることである。このため、実効的にチャネル幅が大きく取れるため、アクセストランジスタTN0のオン電流を大きくとれるという利点がある。したがって、本実施のセンスアンプ回路SA0と組み合わせるとで、より高速動作が可能な半導体記憶装置を実現できる。図6(c)、(d)は、開放型データ線構造である。折り返し型データ線構造に比べると、セル面積を低減できるという利点がある。図6(c)はデータ線ピッチが広いため、データ線寄生容量も低減できる。そのため、本実施のセンスアンプ回路SA0と組み合わせることで、より高集積で、低電圧動作が可能な半導体記憶装置を実現できる。図6(d)は、(c)に比べさらにセル面積が小さくでき、本実施のセンスアンプ回路SA0と組み合わせることでより高集積な半導体記憶装置が実現できる。

#### 【0030】

もちろん本発案のセンスアンプに適用できるレイアウトは、これに限定されない。例えば、(d)の開放型データ線構造において、サブワード線WLに対して斜めにレイアウトされている拡散層ACTを、(a)のように直交するようにレイアウトしてもよい。その場合、形状が矩形であるため微細化が容易であるという利点がある。さらに、サブワード線SWLAの、左右の隣接セルの拡散層ACTを共有し、サブワード線WLAに常にロウレベルのVSSを印加する事で、素子分離するなどの応用も可能である。この場合、データ線と平行な方向に、絶縁体からなる素子分離領域を形成する必要がないため、プロセス工程を削減でき、コストを低減できる。

#### 【0031】

図7は、図6に示した複数のメモリセルMCとセンスアンプ回路SA0の断面図の一部を示した図である。図中の記号は、第2層の配線層M2、第3層の配線層M3、Pウェル基板PW、Nウェル基板NW、ディープNウェル基板DNWELLおよびP型基板PSUBである。なお、これらの形成方法は、一般的な半導体記憶装置、特に所謂汎用DRAMと同様なのでここでは説明の詳細は省略する。また、セルキャパシタCS0の構造は、これに限定されるものではない。例えばクラウン型のキャパシタをはじめとして、様々な変更が可能であることはいうまでもない。

このように、本実施のセンスアンプ回路SA0は、NMOSトランジスタを二つと、コモンソース線CSN0の配線追加だけでよいため、実現が容易である。プルダウン回路NDRV0のNMOSトランジスタの拡散層は、メモリセル内のトランジスタとプルダウン回路NDRV1のNMOSトランジスタの拡散層と同じP型ウェルPW内に構成することが可能である。また、サブアレイSARY0の上部に追加配線を配置する必要もないので、配線ノイズも発生しない。したが

10

20

30

40

50

って、メモリ動作に悪影響を及ぼすことがない。

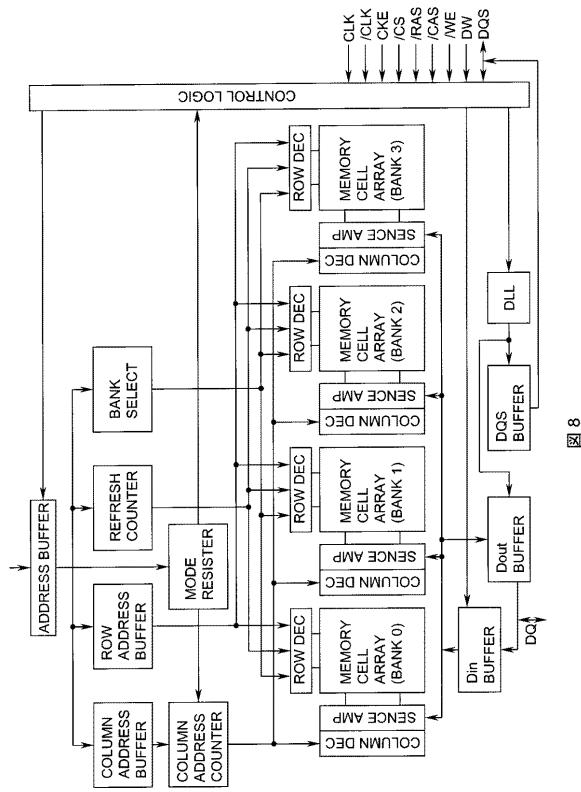

### 【0032】

図8は、図2に示したバンクBANKを複数用いて構成した、DRAMのブロック図の一例を示している。図に示した記号は、アドレスバッファADDRESS BUFFER、カラムアドレスバッファCOLUMN ADDRESS BUFFER、カラムアドレスカウンタCOLUMN ADDRESS COUNTER、ロウアドレスバッファROW ADDRESS BUFFER、リフレッシュカウンタREFRESH COUNTER、バンクセレクトBANK SELECT、モードレジスタMODE REGISTER、ロウデコーダROW DEC、カラムデコーダCOLUMN DEC、メインセンスアンプSENSE AMP、メモリセルアレイMEMORY CELL ARRAY、データ入力バッファDin BUFFER、データ出力バッファDout BUFFER、データバッファDQS BUFFER、ディレイロックドローブDLL、コントロールロジックCONTROL LOGIC、クロックCLK、I/C LK、クロックサイネーブル信号CKE、チップセレクト信号/CS、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE、データライト信号DW、データストローブ信号DQS、データDQである。なお、これらの回路や信号の制御方法は、公知のSDRAMなどと同様であるため、ここでは説明を省略する。本実施例のセンスアンプ回路SA0を用いて、図8のようにバンクBANKを構成することで、シンクロナスダイナミックメモリSDRAM等の半導体記憶装置が実現できる。もちろん言うまでもないが、本実施のセンスアンプ回路SA0を用いることで、前述したように低電圧動作が可能となる等の効果があることは言うまでもない。また、ブロックの構成は、図8に特に限定されない。メモリセルアレイMEMORY CELL ARRAYの数を増やしても良いし、本発案の主旨を逸脱しない範囲で様々な変更が可能である。

### 【0033】

図9は、図1に示したセンスアンプ回路SA0を複数用いて構成した、センスアンプアレイSAA-Rの平面レイアウトの変形例である。図4と異なる点は、プルダウン回路NDRV2のゲート電極形状がリング型ではなく、矩形であることである。図4、図5のように、リング型のゲート電極を利用した場合、プルダウン回路NDRV1の駆動電流が小さくなる場合がある。その場合は、図9のようにゲート電極を矩形にすることで、駆動電流を大きくすることができ、より安定した読み出し動作が可能となる。なお、コンタクトV1、第2層の配線層M2およびコンタクトV2のレイアウトは、図5とほぼ同様であるため、ここでは図面による説明を省略した。

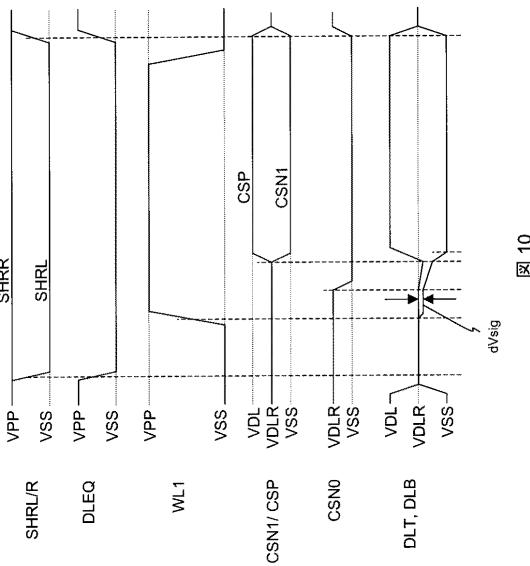

### 【0034】

図10は、図9に示したセンスアンプのレイアウトを適用した場合の、動作波形を示している。基本的な動作は、図3と同様なので説明の詳細は省略する。図3と異なる点は、プルダウン回路NDRV2とプルアップ回路PDRVを駆動した際に、プルダウン回路NDRV2の駆動電流が、図4のリング型のプルダウン回路NDRV1に比べて大きいので、プリアンプしたデータ線対をより高速に增幅できることである。このため、高速動作が可能な半導体記憶装置が実現できる。また、図9では、プルダウン回路NDRV2を矩形のゲート電極FGを用いて構成した場合を示したが、もちろんプルアップ回路PDRVに適用してもよい。この場合も、プルアップ回路PDRVの駆動電流が大きく取れるので、前述と同様に高速動作が可能となる。以上が実施例1の説明である。

### 【実施例2】

### 【0035】

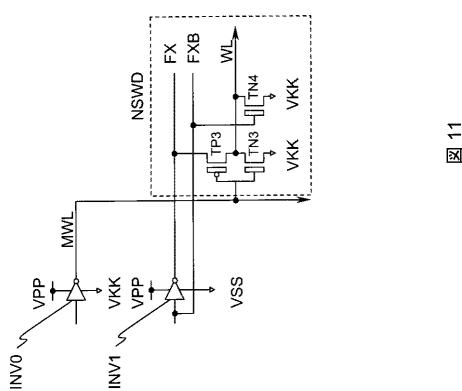

実施例1では、非選択時にメモリセルMCのサブワード線WLに接地電圧VSSを印加した場合について説明したが、負電圧を印加してもよい。

図11、図12は本実施のセンスアンプ回路SA0にネガティブワードドライバNSWDを適用した場合を示している。

図11は、図2におけるサブワードアレイSWDA-U、SWDA-Dを構成するサブワードドライバSWDの変形例である。図中の記号は、ワード線電圧VPP、ネガティブワード線電圧VKK、メインワード線MWL、サブワード線制御信号FX、FXB、インバータINV0、INV1である。各信号の制御方法は一般的なサブワードドライバと同様であるので、ここでは説明を省略する。

### 【0036】

10

20

30

40

50

図12は、本実施のセンスアンプ回路SA0に図11のネガティブサブワードドライバNSWDを適用した場合の動作波形である。図3の動作波形と異なる点は、非選択時のワード線電圧がプルダウン回路を駆動するときの電位よりも低い負電圧である、という点である。このように、ワード線の非選択時に、負電圧を印加することで、実効的にアクセストランジスタの閾値電圧を上げることができる。言い換えると、アクセストランジスタTN0の閾値電圧を低く設定しても、DRAMの所謂リテンション特性の劣化を招く恐れがない。すなわち、チャネル領域の不純物濃度を低減できるので、拡散層ACTとPウェル基板PWとの接合電界を低減できる。その結果、拡散層ACTを流れるリーク電流を低減できるので、より消費電力の少ない半導体記憶装置が実現できる。また、不純物濃度を低減できることから、アクセストランジスタTN0のゲート絶縁膜厚を薄膜化することができるので、より微細化が容易となり、高集積な半導体記憶装置が実現できる。

10

## 【0037】

また、本実施のセンスアンプ回路SA0を組み合わせることで、より効果が得られることは言うまでもない。すなわち、本実施のセンスアンプ回路SA0は、低電圧化した際、読み出し信号量が低下しても、充分に安定した読み出し動作を実現できることは前述した通りである。さらに、図9に示したような、矩形のゲート電極の形状を適用したレイアウトと組み合わせて利用すれば、高速動作が可能であることは言うまでもない。また、ネガティブサブワードドライバNSWDを用いれば、アクセストランジスタTN0を微細化できる、すなわちメモリセルMCをより微細化できるので、データ線寄生容量を低減できる。その結果、より低電圧動作が可能で、かつ高集積な半導体記憶装置が実現できることは言うまでもない。

20

## 【実施例3】

## 【0038】

実施例1、実施例2では複数のプルダウン回路を適用した場合について示した。この場合、プルダウン回路のオフセットの大きさで、安定した読み出し動作が可能であるか、誤動作が生じるかが決まる。したがって、プルアップ回路のオフセットを必要以上に低減しなくてよいため、所謂埋め込みチャネル型のPMOSトランジスタを利用して、PMOSトランジスタ形成に必要なマスク枚数を削減することができる。

30

また本発案は、前述した実施例に限定されることはなく、もちろん複数のプルアップ回路を用いてセンスアンプ回路SA0を構成してもよい。この場合、プルアップ回路を構成するPMOSトランジスタを、所謂埋め込みチャネル型トランジスタではなく、所謂デュアルゲート型トランジスタで形成するとよい。このようにすると、PMOSトランジスタ形成に必要なマスク枚数は増えるが、トランジスタ構造が簡素化されるので、PMOSトランジスタの閾値電圧のバラツキを抑えることができる。

## 【0039】

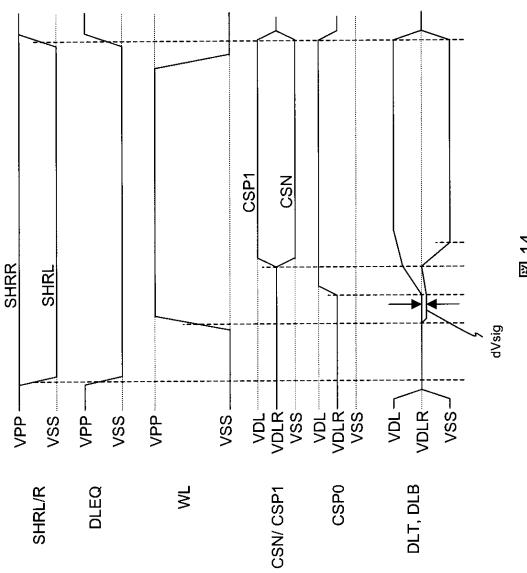

図13から図15は、複数のプルアップ回路を用いたセンスアンプ回路SA0の回路図と、動作波形および平面レイアウトを示している。

40

図13に示すように、本実施例のセンスアンプ回路SA0は、複数のプルアップ回路PDRV0、PDRV1から構成される。その他の記号は前述した実施例と同じであり、説明を省略する。また、前述の実施例と同様に、図13に示すプルアップ回路PDRV0を構成するPMOSトランジスタは、プルアップ回路PDRV1を構成するPMOSトランジスタに比べて、チャネル長やチャネル幅といったトランジスタの駆動力(定数)が大きい。その理由は、プルアップ回路PDRV0のオフセットを十分に低減し、後段において駆動するプルアップ回路PDRV1、プルダウン回路NDRVのオフセットよりも大きな電圧差まで、データ線対を充分にプリアンプするためである。このようにすることで、読み出しの誤動作を防ぐことができる。

## 【0040】

図14は図13に実施のセンスアンプ回路SA0の動作を説明する動作波形である。基本的な動作は、図3と同様であるので詳細な説明は省略する。図3と異なる点は、微小な信号差dV

50

$\text{sig}$ がデータ線対に出力された後、コモンソースドライバ $\text{VDL\_DRV}$ をアサートして、コモンソース線 $\text{CSP0}$ をデータ線電圧 $\text{VDL}$ まで駆動し、プルアップ回路 $\text{PDRV0}$ を活性化して、データ線対をプリアンプする点である。このようにすることで、データ線 $\text{DLB0}$ がデータ線 $\text{DLT0}$ に比べて強く $\text{VDL}$ 側にドライブされる。次に、プルアップ回路 $\text{PDRV1}$ およびプルダウン回路 $\text{NDRV}$ を駆動して、データ線対をハイレベルの $\text{VDL}$ とロウレベルの $\text{VSS}$ まで増幅する。以上が、実施例3のセンスアンプ回路 $\text{SA0}$ の動作である。

#### 【0041】

図15は、実施例3のセンスアンプ回路 $\text{SA0}$ を複数用いて構成した、センスアンプアレイ $\text{SA-A-R}$ の平面レイアウトの一例である。図4と異なる点は、複数のプルアップ回路 $\text{PDRV0}$ 、 $\text{PDRV1}$ と、それらを駆動する、コモンソースドライバ $\text{VDL\_DRV0}$ 、 $\text{VDL\_DRV1}$ を有する点である。

なお、これら以外の図中の記号は、前述の実施例と同様であるので、説明は省略する。また、コンタクト $\text{V1}$ 、第2層の配線層 $\text{M2}$ およびコンタクト $\text{V2}$ のレイアウトは、図4と同様なので、ここでは図面を省略した。図15に示すように、複数のプルアップ回路を用いた場合も、レイアウトの対称性に優れており、データ線ノイズの小さい追加トランジスタも二つであり、追加配線も少なく、実現が容易であることがわかる。

#### 【0042】

以上実施例3について、図13から図15を用いて説明したが、本発案はもちろんこれに限定されない。例えば、図9に示したような矩形のゲート電極形状のプルアップ回路を適用しても良いし、実施例2のようにネガティブサブワードドライバ $\text{NSWD}$ を用いてもよい。また、図15の例では、図4と同様に、所謂分散ドライブ方式のレイアウトの例を示したが、もちろんこれに限定されない。コモンソース線 $\text{CSP0}$ を、データ線のハイレベル $\text{VDL}$ 以上に昇圧する、所謂オーバードライブ方式と組み合わせて利用してもよい。この場合、前述した通りの効果が得られることは言うまでもない。以上のように、本発案の主旨を逸脱しない範囲で、様々な変更が可能である。

#### 【実施例4】

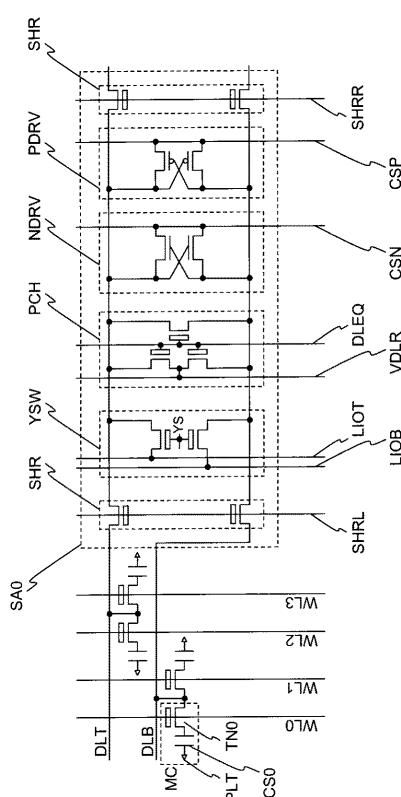

#### 【0043】

実施例1から実施例3においては、複数のプルダウン回路、もしくは複数のプルアップ回路を用いてセンスアンプ回路を構成したが、高速動作が要求されない場合には、それぞれ一つずつのプルダウン回路とプルアップ回路を用いてセンスアンプ回路を構成してもよい場合がある。その場合、例えばプルダウン回路、及びプルアップ回路を構成するトランジスタのチャネル長を長くする、あるいはチャネル幅を広くして、オフセットを低減する。さらに、例えばプルダウン回路を、プルアップ回路に先行して駆動することで、プルアップ回路のオフセット以上にデータ線対をプリアンプすればよい。

#### 【0044】

図16は、本実施例のセンスアンプ回路 $\text{SA0}$ を示す図である。前述の実施例と異なる点は、プルダウン回路とプルアップ回路がそれぞれ一つずつしかないことである。また図中の記号は、前述の実施例と同じであるため、ここでは説明を省略する。このように、本実施例では、従来のセンスアンプ回路に対して追加回路がないため、前述の実施例に比べセンスアンプ回路 $\text{SA0}$ の面積を低減できる。また、追加駆動信号もないため、制御信号用の配線追加も不要でありプロセスコストも低減できる。すなわち、安定した読み出し動作と、センスアンプの面積低減を両立した半導体記憶装置が実現できる。

#### 【0045】

図17は、図16に示した実施例の動作波形を示す図である。基本的な動作は、図3と同様であるので詳細な説明は省略する。図3と異なる点は、微小な信号差 $d\text{Vs}\text{ig}$ がデータ線対に出力された後、コモンソースドライバ $\text{VSS\_DRV}$ をアサートして、コモンソース線 $\text{CSN}$ を $\text{VSS}$ に駆動し、まずプルダウン回路 $\text{NDRV}$ を活性化する。データ線 $\text{DLT0}$ がプルアップ回路 $\text{PDRV}$ のオフセット以上まで充分に増幅された後、コモンソースドライバ $\text{VDL\_DRV}$ をアサートして、コモンソース線 $\text{CSP}$ をハイレベルの $\text{VDL}$ に駆動し、プルアップ回路 $\text{PDRV}$ を活性化する。先行して活性化したプルダウン回路 $\text{NDRV}$ によって、充分にデータ線 $\text{DLT0}$ が増幅されているので、プルアップ回路 $\text{PDRV}$ は、データ線 $\text{DLB0}$ をハイレベルの $\text{VDL}$ まで誤動作なく増幅できる

10

20

30

40

50

。以上が実施例4のセンスアンプ回路SA0の動作である。

#### 【0046】

なお、本実施例ではプルダウン回路NDRVを先行して活性化したが、もちろんプルアップ回路PDRVを先行して駆動しても同様の効果が得られることは言うまでもない。また、前述の実施例と組み合わせることで、低電圧動作が可能になる、高集積化が可能になるといった効果が得られることも言うまでもない。このように、本実施例においても、本発案の主旨を逸脱しない範囲で様々な変更が可能であることは言うまでもない。

また、実施例1から実施例4において説明したメモリセルMCは、1トランジスタ型のDRAMセルで説明したが、もちろん2トランジスタ型の所謂ツインセルでもよい。また、二つのメモリセルを利用して、その論理和をとる所謂ORセルでもよい。もちろんDRAMセルではなく、6トランジスタ型のスタティックランダムアクセスメモリでもよく、様々なメモリセルと本発案のセンスアンプ回路を組み合わせて利用することができる。

#### 【0047】

また、オフセットを低減する手段として、トランジスタのチャネル長を長くする、チャネル幅を広くするといった具体例を説明したが、本発案はもちろんこれに限定されない。センスアンプを構成するトランジスタ基板の不純物濃度を低くして、不純物揺らぎによる閾値電圧のバラツキを抑える手段を利用してもよい。また、センスアンプ回路を構成するNMOSトランジスタやPMOSトランジスタの閾値電圧を低くして、センスアンプを構成しても良い。この場合、センスアンプ回路に印加される電圧が、実効的に大きくなるので、より高速動作が可能となる。さらに、閾値電圧を低くすると、不純物濃度が低くなるため、閾値電圧のバラツキが抑えられる。そのため、オフセットを低減できるので、プルダウン回路やプルアップ回路のトランジスタのチャネル長やチャネル幅といった、トランジスタの駆動力(定数)を必要以上に大きくしなくてもよい。すなわち、センスアンプ回路の面積を低減することができる。あるいは、前述のセンスアンプ回路を構成するトランジスタの基板電圧を、読み出し動作時に動的に変化させてもよい。この場合も、センスアンプ回路に印加される電圧差が実効的に大きくなるので、より高速動作が可能となる。

#### 【0048】

なお、動的にトランジスタの基板電圧を変えるために、追加回路が必要となるが、一般的な回路変更で容易に実現できるので、ここでは図面を省略した。またこの場合、メモリセル部分とセンスアンプ部分で、異なる基板電圧を印加する必要があるが、簡単な回路変更で実現できるので、ここでは説明を省略した。以上のように、本発案のセンスアンプ回路は、低電圧動作や高速動作、高集積化といった目的に応じて、様々な変更が可能である。

#### 【図面の簡単な説明】

#### 【0049】

【図1】本発明の半導体記憶装置のセンスアンプ回路部分の基本的な構成を示す、第一の実施例である。

【図2】図1の実施例のセンスアンプ回路を用いて構成したバンクの一例である。

【図3】図1のセンスアンプの動作波形の一例を示す図である。

【図4】図2のセンスアンプアレイの平面レイアウトの一部を示す図である。

【図5】図2のセンスアンプアレイの平面レイアウトの一部を示す図である。

【図6】図1におけるメモリセルの平面レイアウトの一例を示す図である。

【図7】図2におけるバンクの一部分の断面構造例である。

【図8】図1のセンスアンプを用いて構成した半導体記憶装置のブロック図の一例である。

【図9】図2のセンスアンプアレイの平面レイアウトの変形例の一例を示す図である。

【図10】図9のセンスアンプのレイアウトを実施した場合の、センスアンプの動作波形の一例である。

【図11】ネガティブサブワードドライバの回路構成を示す図である。

【図12】図11のネガティブサブワードドライバを本発案のセンスアンプに実施した場合

10

20

20

30

40

50

の動作波形の一例を示す第二の実施例である。

【図13】本発明の半導体記憶装置のセンスアンプ回路部分の基本的な構成を示す、第三の実施例である。

【図14】図13のセンスアンプの動作波形の一例を示す図である。

【図15】図13のセンスアンプを複数用いて構成した、センスアンプアレイの平面レイアウトの一例を示す図である。

【図16】本発明の半導体記憶装置のセンスアンプ回路部分の基本的な構成を示す、第四の実施例である。

【図17】図16のセンスアンプの動作波形の一例を示す図である。

【図18】従来のセンスアンプ回路の一例を示す図である。

【図19】従来のセンスアンプ回路の動作波形の一例を示す図である。

#### 【符号の説明】

##### 【0050】

SA0-SA2 センスアンプ回路、SHR - スイッチトランジスタ、SHRL、SHRR - スイッチトランジスタ駆動線、YSW - カラムスイッチ、YS、YS0、YS1、YS2 カラムスイッチ駆動線、LIOT、LI00T、LI01T、LI0B、LI00B、LI01B ローカルデータ線、PCH プリチャージ回路、DLEQ プリチャージ回路駆動線、VDLR プリチャージ電圧、NDRV、NDRV0、NDRV1、NDRV2 ブルダウン回路、PDRV、PDRV0、PDRV1 ブルアップ回路、CSN、CSNO、CSN1、CSP、CSP0、CSP1 - コモンソース線、CSNO、CSN1、CSP コモンソース制御線、WL、WL0-WL5 サブワード線、DLT、DLT0-DLT2、DLB、DLB0-DLB1、データ線、MC メモリセル、CS0 セルキャパシタ、PLT プレート電極、TN0 - アクセストランジスタ、SAA-R、SAA-L - センスアンプアレイ、SARY、SARY0 - サブアレイ、VSS-U、VSS-D - 接地電圧、SWD - サブワードドライバ、SWDA-U、SWDA-D サブワードドライバアレイ、BANK、BANK0-BANK3 - バンク、VDL\_DRV、VDL\_DRV0、VDL\_DRV1、VSS\_DRV、VSS\_DRV0、VSS\_DRV1 コモンソースドライバ、CCNT セルコンタクト、FGCNT ゲートコンタクト、LCNT - 拡散層コンタクト、DLCNT - データ線コンタクト、SN - 蓄積ノード、SNCNT - 蓄積ノードコンタクト、LPAD - ランディングパッド、LN、LP、ACT 拡散層および拡散層配線層、FG - ゲート電極およびゲート配線層、M1 第一層の金属配線層、M2 第二層の金属配線層、M3 第三層の金属配線層、V1、V2 コンタクト、PW Pウェル基板、NW Nウェル基板、DNWELL ディープNウェル基板、PSUB P型基板、VBB - 基板電位、SDRAM シンクロナスダイナミックメモリ、AD DRESS BUFFER - アドレスバッファ、COLUMN ADDRESS BUFFER - カラムアドレスバッファ、COLUMN ADDRESS COUNTER - カラムアドレスカウンタ、ROW ADDRESS BUFFER - ロウアドレスバッファ、REFRESH COUNTER - リフレッシュカウンタ、BANK SELECT - バンクセレクト、MODE RESISTER - モードレジスタ、ROW DEC - ロウデコーダ、COLUMN DEC - カラムデコーダ、SENSE AMP - メインセンスアンプ、MEMORY CELL ARRAY - メモリセルアレイ、Din BUFFER - データ入力バッファ、Dout BUFFER - データ出力バッファ、DQS BUFFER - データバッファ、DLL ディレイロッドループ、CONTROL LOGIC - コントロールロジック、CLK、/CLK - クロック、CKE - クロックイネーブル信号、/CS - チップセレクト信号、/RAS - ロウアドレスストローブ信号、/CAS - カラムアドレスストローブ信号、/WE - ライトイネーブル信号、DW - データライト信号、DQS - データストローブ信号、DQ データ、INV0、INV1 インバータ、TN1-TN4 - NMOSトランジスタ、TP1-TP3 - PMOSトランジスタ、VPP ワード線電圧、VKK ネガティブワード線電圧、VDL データ線電圧、VSS 接地電圧、MWL メインワード線、FX、FXB サブワード線制御信号、NSWD - ネガティブサブワードドライバ。

10

20

30

40

〔 図 1 〕

1

【 図 2 】

三

( 3 )

3

( 5 )

【図8】

【図10】

図10

【図11】

【図12】

図12

【図 1 3】

図 13

【図 1 4】

図 14

【図 1 6】

図 16

【図 1 7】

図 17

【図18】

【図19】

図19

【図4】

【図6】

図6

【図7】

SAA - L

SARYO

SAA - R

図7

【図9】

【図15】

---

フロントページの続き

(72)発明者 河原 尊之

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 関口 知紀

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F083 AD24 AD31 AD48 GA01 GA09 LA03 LA04 LA05 LA06 LA07

LA09 LA10 LA14 MA06 MA17 MA20

5M024 AA93 BB08 BB14 BB35 CC38 CC39 CC40 CC63 CC65 CC74

CC77 CC83 LL01 LL13 PP01 PP02 PP03 PP04 PP05 PP07