(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5630552号

(P5630552)

(45) 発行日 平成26年11月26日(2014.11.26)

(24) 登録日 平成26年10月17日(2014.10.17)

(51) Int.Cl.

F 1

|               |           |              |         |

|---------------|-----------|--------------|---------|

| HO 1 L 29/78  | (2006.01) | HO 1 L 29/78 | 6 5 2 C |

| HO 1 L 29/12  | (2006.01) | HO 1 L 29/78 | 6 5 2 T |

| HO 1 L 21/336 | (2006.01) | HO 1 L 29/78 | 6 5 3 A |

| HO 1 L 21/28  | (2006.01) | HO 1 L 29/78 | 6 5 2 M |

| HO 1 L 29/417 | (2006.01) | HO 1 L 29/78 | 6 5 2 D |

請求項の数 4 (全 10 頁) 最終頁に続く

(21) 出願番号

特願2013-215126 (P2013-215126)

(22) 出願日

平成25年10月15日 (2013.10.15)

(62) 分割の表示

特願2009-109994 (P2009-109994)

の分割

原出願日 平成21年4月28日 (2009.4.28)

(65) 公開番号

特開2014-33223 (P2014-33223A)

(43) 公開日

平成26年2月20日 (2014.2.20)

審査請求日

平成25年10月15日 (2013.10.15)

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100104190

弁理士 酒井 昭徳

(72) 発明者 辻 崇

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

審査官 土谷 慎吾

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置およびその製造方法

(57) 【特許請求の範囲】

【請求項 1】

第1導電型炭化珪素半導体基板のおもて面側の全面に設けられた第1導電型ドリフト層と、

前記第1導電型ドリフト層の全面に設けられた第2導電型ベース層と、

前記第2導電型ベース層の表面層に選択的に設けられた第2導電型不純物領域と、

前記第2導電型ベース層の表面層に、前記第2導電型不純物領域と離れて設けられたトレンチと、

前記トレンチの内部に、ゲート酸化膜を介して埋め込まれたゲート電極と、

前記第2導電型ベース層の表面層に、前記トレンチと接し、前記第2導電型不純物領域と離れて設けられた第1導電型ソース領域と、 10

前記ゲート電極を覆うように設けられた絶縁膜と、

前記第2導電型不純物領域および前記第1導電型ソース領域に接するように設けられたソース電極と、

前記第1導電型炭化珪素半導体基板の裏面側に設けられたドレイン電極と、

を備え、

前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分の厚さは、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域の厚さよりも厚く、

前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層と 20

に挟まれた部分は、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域よりも前記ソース電極側に突出していることを特徴とする炭化珪素半導体装置。

#### 【請求項2】

前記第2導電型不純物領域の底部から前記第2導電型ベース層と前記第1導電型ドリフト層との界面までの距離は、 $4 \mu m$ 以上であることを特徴とする請求項1に記載の炭化珪素半導体装置。

#### 【請求項3】

第1導電型炭化珪素半導体基板のおもて面側の全面に第1導電型ドリフト層を積層する工程と、

10

前記第1導電型ドリフト層の全面に第2導電型ベース層を積層する工程と、

前記第2導電型ベース層を所定深さでかつ選択的にエッチングし、前記第2導電型ベース層の一部を突出領域として残す工程と、

前記突出領域の表面層に第2導電型不純物領域を形成する工程と、

前記第2導電型ベース層の表面層の、前記突出領域以外の領域に第1導電型ソース領域を形成する工程と、

前記第1導電型ソース領域および前記第2導電型ベース層を貫通するように第2トレンチを形成する工程と、

前記第2トレンチの内部に、ゲート酸化膜を介してゲート電極を形成する工程と、

前記第1導電型ソース領域および前記第2導電型不純物領域に接するようにソース電極を形成する工程と、

20

前記第1導電型炭化珪素半導体基板の裏面側にドレイン電極を形成する工程と、

を含むことを特徴とする炭化珪素半導体装置の製造方法。

#### 【請求項4】

前記第2導電型ベース層を積層する工程においては、厚さが $4 \mu m$ 以上となるように、前記第1導電型ドリフト層の全面に前記第2導電型ベース層を積層することを特徴とする請求項3に記載の炭化珪素半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

30

この発明は、半導体材料として炭化珪素(SiC)を用いた炭化珪素半導体装置およびその製造方法に関する。

##### 【背景技術】

##### 【0002】

従来、炭化珪素半導体材料は、シリコン半導体材料よりも大きなバンドギャップを有しているため、シリコン半導体材料よりも絶縁破壊電界強度が高いことが知られている。ここで、オン抵抗は、導通状態における抵抗であり、絶縁破壊電界強度の3乗に反比例する。このため、例えば広く用いられている4H型と呼ばれる炭化珪素半導体においては、オン抵抗をシリコン半導体の100分の1に抑制することができる。また、炭化珪素半導体は、熱伝導度が大きいため、放熱が容易である。これらの理由から、炭化珪素半導体を用いて作製される次世代の低損失な電力用半導体装置が期待されている。

40

##### 【0003】

近年、炭化珪素半導体材料を用いた炭化珪素ウエハ(半導体基板)の品質向上や大口径化の進展にともなって、シリコン半導体材料を用いたシリコン半導体装置の特性を大きく上回る金属酸化物半導体電界効果型トランジスタ(MOSFET)、バイポーラトランジスタ、接合型電界効果型トランジスタ(JFET)などの開発が盛んである。特にMOSFETは、電圧駆動型素子であるため、ゲート駆動回路を低成本に抑えることができる。また、MOSFETは、電子あるいは正孔のみの多数キャリア素子であって導通時の素子内にキャリアの蓄積がないため、ターンオフ時にそれらのキャリアを素子外に掃き出す時間を必要としない。したがって、例えば電子および正孔の両方が伝導に寄与するバイポ

50

ーラ型素子と比較して高速スイッチングが可能となる。

#### 【0004】

なお、本明細書において、nまたはpを冠した半導体は、それぞれ電子、正孔が多数キャリアであることを意味する。また、 $n^+$ や $n^-$ などのように、nやpに付す「+」または「-」は、それぞれそれらが付されていない半導体の不純物濃度よりも比較的高濃度または比較的低濃度であることを表す。

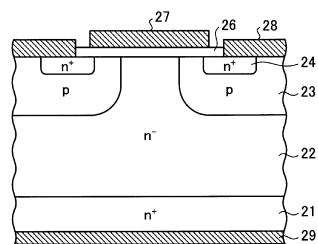

#### 【0005】

図6は、従来の一般的な縦型MOSFET(DIMOSFET)の断面構造について示す断面図である。図6に示すように、DIMOSFETは、 $n^+$ 型ドレイン層21の上に、 $n^-$ 型ドリフト層22が設けられており、 $n^-$ 型ドリフト層22の表面層に、選択的にp型ベース層23が設けられている。すなわち、おもて面側の表面付近において、 $n^-$ 型ドリフト層22がp型ベース層23に挟まれた構造となっている。そして、p型ベース層23の表面層に、 $n^-$ 型ドリフト層22と離れて $n^+$ 型ソース領域24が設けられている。また、p型ベース層23の $n^-$ 型ドリフト層22と $n^+$ 型ソース領域24に挟まれた領域と、 $n^-$ 型ドリフト層22との上に、ゲート酸化膜26を介してゲート電極27が設けられている。さらに、おもて面側にソース/ベース電極28が設けられ、裏面側にドレイン電極29が設けられている。

#### 【0006】

図6に示すDIMOSFETにおいては、 $n^-$ 型ドリフト層22においてゲート酸化膜26との界面近傍を電子が移動するときに蓄積層抵抗が生じる。また、 $n^-$ 型ドリフト層22内のゲート酸化膜26との界面近傍から裏面側のドレインに向かって電流が流れるとときに、 $n^-$ 型ドリフト層22がp型ベース層23に挟まれているために、JFET抵抗が発生しやすい。

#### 【0007】

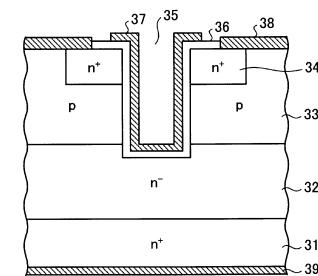

上述した蓄積層抵抗やJFET抵抗を生じさせないために、トレンチゲート構造を有するMOSFET(UMOSFET)が提案されている。図7は、従来の一般的なUMOSFETの断面構造を示す断面図である。UMOSFETは、正面に対して側壁が垂直なトレンチゲートを有するMOSFETである。図7においては、UMOSFETの1セルピッチの断面構造を示している。

#### 【0008】

図7に示すように、UMOSFETを作製する際には、 $n^+$ 型ドレイン層31となる比較的低い抵抗率の $n^+$ 型炭化珪素基板の上に、比較的高い抵抗率の $n^-$ 型ドリフト層32と、p型ベース層33とを、この順にエピタキシャルSiC成長により形成する。そして、p型ベース層33の表面からイオン注入を行うことで $n^+$ 型ソース領域34を形成する。このような炭化珪素ウェハに、 $n^-$ 型ドリフト層32に達するようなゲートトレンチ35を形成し、ゲートトレンチ35内部に、ゲート酸化膜36を介してゲート電極37を形成する。さらに、炭化珪素ウェハ30のおもて面側にソース/ベース電極38を形成し、裏面側にドレイン電極39を形成することで、UMOSFETが完成する。

#### 【0009】

図7に示すUMOSFETにおいては、オフ状態時に、ソース/ベース電極38をアース電位にしておき、ゲート電極37に十分に大きな負バイアスを印加することで、電流が流れなくなる。その理由は、p型ベース層33の $n^+$ 型ソース領域34と $n^-$ 型ドリフト層32に挟まれた領域と、ゲート酸化膜36との界面近傍において、正孔が誘起された蓄積状態となり、伝導キャリアである電子の経路が遮断されるためである。また、ドレイン電極39に正の高電圧を印加するとp型ベース層33と $n^-$ 型ドリフト層32間の接合が逆バイアス状態になるので、空乏層がp型ベース層33内と $n^-$ 型ドリフト層32内に広がり、電流を低く抑えたまま高電圧が維持される。

#### 【0010】

また、オン状態時に、ゲート電極37に十分に大きな正バイアスを印加することで、p型ベース層33の $n^+$ 型ソース領域34と $n^-$ 型ドリフト層32に挟まれた領域と、ゲート

10

20

30

40

50

酸化膜36との界面近傍において、電子が誘起された反転状態となる。そして、ソース/ベース電極38、n<sup>+</sup>型ソース領域34、p型ベース層33のゲート酸化膜36に接する反転層(不図示)、n<sup>-</sup>型ドリフト層32、n<sup>+</sup>型ドレイン層31、ドレイン電極39の順にキャリアが流れる。

#### 【0011】

このように、図6に示すDIMOSFETではセルピッチを小さくしていくと、所定のセルピッチ距離からJFET抵抗が現れて、オン抵抗が増加するのに対し、図7に示すUMOSFETではセルピッチを小さくすればするほどオン抵抗が単調に減少する。特に、約3kV以下の耐圧を持つMOSFETにおいては、MOSチャネル抵抗が無視できないために微細化によるセルピッチの縮小が必須であり、この場合UMOSFETの方が適している。10

#### 【0012】

しかしながら、UMOSFETにおいては、ゲートトレンチ35底部においてゲート酸化膜36(SiO<sub>2</sub>膜)に印加される電界強度が非常に大きくなる。その理由は、炭化珪素の比誘電率(4H-SiCの場合、例えば9.7)と、SiO<sub>2</sub>の比誘電率(例えば3.8)とが異なるためである。また、図示は省略したが、ゲートトレンチ35の角部の酸化膜に印加される電界強度は、電界集中のためにさらに大きくなる。

#### 【0013】

そして、p型ベース層33とn<sup>-</sup>型ドリフト層32との間のpn接合部における電界強度のピークが炭化珪素の絶縁破壊電界強度(例えば、約2MV/cm)に達する前に、ゲートトレンチ35底部のゲート酸化膜36が酸化膜の絶縁破壊電界強度(例えば、約10MV/cm)に先に達してしまい、理論耐圧よりも低い電圧で絶縁破壊を起こしてしまうという問題がある。20

#### 【0014】

このため、p型ベース層33のゲートトレンチ35同士の間の領域が、ゲートトレンチ35近傍よりも深く設けられたUMOSFETが提案されている(例えば、下記特許文献1参照。)。このUMOSFETでは、電界強度のピークがゲート酸化膜36から離れた位置になるので、ゲートトレンチ35の角部に電界集中するのを防ぐことができる。

#### 【0015】

ここで、UMOSFETにおいては、電位を保つためにp型ベース層33が外部端子とオーム接觸をする必要がある。さらに、オーム接觸における接触抵抗はできるだけ小さいことが望ましい。その理由は、接触抵抗が大きいと素子のRC回路の時定数が増加し、スイッチング損失となるからである。そのためには、比較的高いドーズ量のA1(アルミニウム)イオンを注入する必要がある。30

#### 【先行技術文献】

#### 【特許文献】

#### 【0016】

#### 【特許文献1】特開2001-267570号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0017】

しかしながら、上述した技術のように、高いドーズ量でA1イオンを注入すると、リーク電流が増加し、絶縁耐圧が低下するという問題がある。特に、基板表面をSi面またはC面とし、p型ベース層におけるボディコンタクト領域にらせん転位が含まれていると、高い確率でリーク電流が増加する。p型ベース層をエピタキシャル成長により形成する場合、p型ベース層の厚さを大きくすればリーク電流を減少させることはできるが、チャネル長が増加するため、チャネル抵抗が増加するという問題がある。40

#### 【0018】

この発明は、上述した従来技術による問題点を解消するため、リーク電流を抑え、かつチャネル抵抗を低減することができる炭化珪素半導体装置およびその製造方法を提供する50

ことを目的とする。

【課題を解決するための手段】

【0019】

上述した課題を解決し、目的を達成するため、この発明にかかる炭化珪素半導体装置は、第1導電型炭化珪素半導体基板のおもて面側の全面に設けられた第1導電型ドリフト層と、前記第1導電型ドリフト層の全面に設けられた第2導電型ベース層と、前記第2導電型ベース層の表面層に選択的に設けられた第2導電型不純物領域と、前記第2導電型ベース層の表面層に、前記第2導電型不純物領域と離れて設けられたトレンチと、前記トレンチの内部に、ゲート酸化膜を介して埋め込まれたゲート電極と、前記第2導電型ベース層の表面層に、前記トレンチと接し、前記第2導電型不純物領域と離れて設けられた第1導電型ソース領域と、前記ゲート電極を覆うように設けられた絶縁膜と、前記第2導電型不純物領域および前記第1導電型ソース領域に接するように設けられたソース電極と、前記第1導電型炭化珪素半導体基板の裏面側に設けられたドレイン電極と、を備え、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分の厚さは、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域の厚さよりも厚く、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分は、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域よりも前記ソース電極側に突出していることを特徴とする。

10

【0020】

また、この発明にかかる炭化珪素半導体装置は、上述した発明において、前記第2導電型不純物領域の底部から前記第2導電型ベース層と前記第1導電型ドリフト層との界面までの距離は、4μm以上であることを特徴とする。

20

【0021】

また、この発明にかかる炭化珪素半導体装置の製造方法は、第1導電型炭化珪素半導体基板のおもて面側の全面に第1導電型ドリフト層を積層する工程と、前記第1導電型ドリフト層の全面に第2導電型ベース層を積層する工程と、前記第2導電型ベース層を所定深さでかつ選択的にエッティングし、前記第2導電型ベース層の一部を突出領域として残す工程と、前記突出領域の表面層に第2導電型不純物領域を形成する工程と、前記第2導電型ベース層の表面層の、前記突出領域以外の領域に第1導電型ソース領域を形成する工程と、前記第1導電型ソース領域および前記第2導電型ベース層を貫通するように第2トレンチを形成する工程と、前記第2トレンチの内部に、ゲート酸化膜を介してゲート電極を形成する工程と、前記第1導電型ソース領域および前記第2導電型不純物領域に接するようにソース電極を形成する工程と、前記第1導電型炭化珪素半導体基板の裏面側にドレイン電極を形成する工程と、を含むことを特徴とする。

30

【0022】

また、この発明にかかる炭化珪素半導体装置の製造方法は、上述した発明において、前記第2導電型ベース層を積層する工程においては、厚さが4μm以上となるように、前記第1導電型ドリフト層の全面に前記第2導電型ベース層を積層することを特徴とする。

40

【0023】

上述した各請求項の発明によれば、第2導電型ベース層において、第2導電型ベース層よりも不純物濃度の高い第2導電型不純物領域が形成された領域は、第2導電型ベース層の表面から第2導電型ベース層と第1導電型ドリフト層との界面までの距離が比較的長い。具体的には、表面層に第2導電型不純物領域が形成された領域において、第2導電型ベース層の厚さが4μm以上である。したがって、リーク電流を減少することができる。また、第2導電型ベース層全体を厚くすると、チャネル抵抗が増加するという問題があるが、第2導電型ベース層において、表面層に第2導電型不純物領域が形成された領域以外は、第2導電型ベース層の表面から第2導電型ベース層と第1導電型ドリフト層との界面までの距離が比較的短いため、チャネル抵抗を低減することができる。

【発明の効果】

## 【0024】

本発明にかかる炭化珪素半導体装置およびその製造方法によれば、リーク電流を抑え、かつチャネル抵抗を低減することができるという効果を奏する。

## 【図面の簡単な説明】

## 【0025】

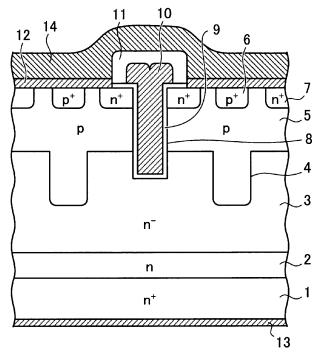

【図1】実施の形態1にかかる半導体装置の断面構造について示す断面図である。

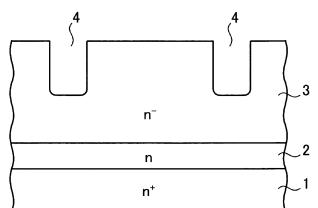

【図2】実施の形態1にかかる半導体装置の製造方法を示す断面図である。

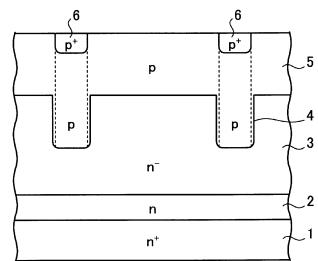

【図3】実施の形態1にかかる半導体装置の製造方法を示す断面図である。

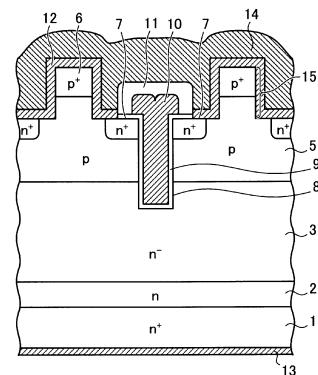

【図4】実施の形態2にかかる半導体装置の断面構造について示す断面図である。

【図5】実施の形態2にかかる半導体装置の製造方法を示す断面図である。

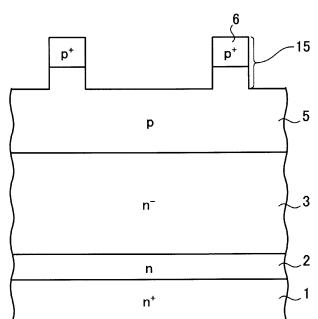

【図6】従来の一般的な縦型MOSFET(DIMOSFET)の断面構造について示す断面図である。

【図7】従来の一般的なUMOSFETの断面構造を示す断面図である。

## 【発明を実施するための形態】

## 【0026】

以下に添付図面を参照して、この発明にかかる炭化珪素半導体装置およびその製造方法の好適な実施の形態を詳細に説明する。なお、各実施の形態の説明およびすべての添付図面において、同様の構成には同一の符号を付し、重複する説明を省略する。

## 【0027】

## (実施の形態1)

まず、実施の形態1にかかる半導体装置について説明する。図1は、実施の形態1にかかる半導体装置の断面構造について示す断面図である。実施の形態1にかかる半導体装置は、エピタキシャルウェハーを用いて作製される。エピタキシャルウェハーは、n<sup>+</sup>型4H-SiC基板1の上に、n型バッファー層2と、n<sup>-</sup>型ドリフト層3とが、この順に積層されている。

## 【0028】

エピタキシャルウェハーには、第1主面から垂直に、第1トレンチ4が設けられている。そして、第1トレンチ4を有するエピタキシャルウェハーの全面にp型ベース層5が積層されている。したがって、第1トレンチ4には、p型ベース層5が埋め込まれている。

## 【0029】

p<sup>+</sup>型ボディコンタクト領域6は、第1トレンチ4が形成された領域の上の、p型ベース層5の表面層に設けられている。また、ゲートトレンチ(第2トレンチ)8は、第1トレンチ4が形成されていない領域に、p型ベース層5の表面層から設けられている。第2トレンチ8の内部には、ゲート酸化膜9を介してゲート電極10が埋め込まれている。また、n<sup>+</sup>型ソース領域7は、p型ベース層5の表面層に、第2トレンチ8と接し、p<sup>+</sup>型ボディコンタクト領域6と離れて設けられている。

## 【0030】

層間絶縁膜11は、ゲート電極10を覆うように設けられている。ソース電極12は、p<sup>+</sup>型ボディコンタクト領域6と、n<sup>+</sup>型ソース領域7とに接する。ドレイン電極13は、エピタキシャルウェハーの第2主面側に設けられている。ソース電極12および層間絶縁膜11の上にはメタル14が積層されている。

## 【0031】

つぎに、実施の形態1にかかる半導体装置の製造方法について説明する。図2および図3は、実施の形態1にかかる半導体装置の製造方法を順に示す断面図である。まず、図2に示すように、厚さが例えば約400μmであり、不純物濃度が例えば $1 \times 10^{18} \text{ cm}^{-3}$ であるn<sup>+</sup>型4H-SiC基板1を用意する。n<sup>+</sup>型4H-SiC基板1は、主面が例えば<11-20>方向に8度のオフ角を有する(0001)Si面または(000-1)C面である。

## 【0032】

そして、n<sup>+</sup>型4H-SiC基板1に、膜厚が例えば1μmであり、不純物濃度が例え

10

20

30

40

50

ば  $1 \times 10^{17} \text{ cm}^{-3}$  である n 型バッファー層 2 と、不純物濃度が例えば  $9 \times 10^{15} \text{ cm}^{-3}$  である n<sup>-</sup>型ドリフト層 3 をこの順にエピタキシャル成長により形成する。これにより、エピタキシャルウェハーが生成される。

#### 【 0 0 3 3 】

つぎに、例えば RIE ( Reactive Ion Etching ) によって、エピタキシャルウェハーの第 1 主面側から、第 1 主面と垂直に、幅が例えば 1 μm の第 1 トレンチ 4 を形成する。第 1 トレンチ 4 の深さは、例えば 2 . 5 μm 以上であり、n 型バッファー層 2 に達しない深さとする。

#### 【 0 0 3 4 】

ついで、図 3 に示すように、第 1 トレンチ 4 の形成されたエピタキシャルウェハーの第 1 主面側の全面に、不純物濃度が例えば  $2 \times 10^{17} \text{ cm}^{-3}$  であり、深さが例えば 2 μm である p 型ベース層 5 を堆積する。これによって、第 1 トレンチ 4 の内部に p 型ベース層 5 が埋め込まれ、p 型ベース層 5 の第 1 主面側が平坦となる。

#### 【 0 0 3 5 】

そして、イオン注入によって、p 型ベース層 5 の表面層の、第 1 トレンチ 4 の形成された上の領域に、比較的高濃度の Al イオンを注入する。そして、活性化アニール処理を行い、深さが例えば 0 . 5 μm であり、不純物濃度が  $2 \times 10^{20} \text{ cm}^{-3}$  である、p<sup>+</sup>型ボディコンタクト領域 6 を形成する。このとき、p<sup>+</sup>型ボディコンタクト領域 6 の底部から第 1 トレンチ 4 の底部の p n 接合 ( p 型ベース層 5 と n<sup>-</sup>型ドリフト層 3 との界面) までの距離を 4 μm 以上とする。

#### 【 0 0 3 6 】

さらに、p 型ベース層 5 の表面層に、p<sup>+</sup>型ボディコンタクト領域 6 と接しないように、n<sup>+</sup>型ソース領域 7 を形成し、p 型ベース層 5 の表面層の、第 1 トレンチ 4 の形成されていない上の領域から、第 2 トレンチ ( ゲートトレンチ ) 8 を形成する。そして、通常のトレンチゲート型 MOSFET を形成するように、ゲート酸化膜 9 、ゲート電極 10 、層間絶縁膜 11 、ソース電極 12 、ドレイン電極 13 およびメタル 14 を順次形成して、図 1 に示す半導体装置が完成する。

#### 【 0 0 3 7 】

ここで、例えば 1 . 2 kV クラスの MOSFET に実施の形態 1 の発明を適用した場合について検証を行った。実施の形態 1 の半導体装置では、リーク電流が  $10^{-8} \text{ A}$  となり、従来構造におけるリーク電流 ( $10^{-4} \text{ A}$ ) よりも低減した。また、実施の形態 1 の半導体装置では、チャネル抵抗が  $1 \text{ m} \Omega \text{ cm}^2$  となり、従来構造におけるチャネル抵抗 ( $2 \text{ m} \Omega \text{ cm}^2$ ) よりも低減した。

#### 【 0 0 3 8 】

実施の形態 1 によれば、p 型ベース層 5 において、p 型ベース層 5 よりも不純物濃度の高い p<sup>+</sup>型ボディコンタクト領域 6 が形成された領域は、p 型ベース層 5 の表面から p 型ベース層 5 と n<sup>-</sup>型ドリフト層 3 との界面までの距離が比較的長い。具体的には、表面層に p<sup>+</sup>型ボディコンタクト領域 6 が形成された領域において、p 型ベース層 5 の厚さが 4 μm 以上である。したがって、リーク電流を減少することができる。また、p 型ベース層 5 全体を厚くすると、チャネル抵抗が増加するという問題があるが、p 型ベース層 5 において、表面層に p<sup>+</sup>型ボディコンタクト領域 6 が形成された領域以外は、p 型ベース層 5 の表面から p 型ベース層 5 と n<sup>-</sup>型ドリフト層 3 との界面までの距離が比較的短いため、チャネル抵抗を低減することができる。

#### 【 0 0 3 9 】

##### ( 実施の形態 2 )

つぎに、実施の形態 2 にかかる半導体装置について説明する。図 4 は、実施の形態 2 にかかる半導体装置の断面構造について示す断面図である。図 4 に示すように、実施の形態 2 にかかる半導体装置は、第 1 トレンチが形成されず、p 型ベース層 5 の一部が、第 1 主面から突き出た形状である。そして、p 型ベース層 5 における突出領域 15 の表面層に、p<sup>+</sup>型ボディコンタクト領域 6 が設けられている。その他の構成は、実施の形態 1 と同様

10

20

30

40

50

のため説明を省略する。

#### 【0040】

つぎに、実施の形態2にかかる半導体装置の製造方法について説明する。図5は、実施の形態2にかかる半導体装置の製造方法を示す断面図である。図5に示すように、実施の形態2にかかる半導体装置は、まず、実施の形態1にかかる半導体装置と同様に、 $n^+$ 型4H-SiC基板1に、膜厚が例えば $1\text{ }\mu\text{m}$ であり、不純物濃度が例えば $1 \times 10^{17}\text{ cm}^{-3}$ であるn型バッファー層2と、膜厚が例えば $1\text{ }\mu\text{m}$ であり、不純物濃度が例えば $9 \times 10^{15}\text{ cm}^{-3}$ であるn<sup>-</sup>型ドリフト層3をこの順にエピタキシャル成長により形成する。これにより、エピタキシャルウェハーが生成される。

#### 【0041】

つぎに、エピタキシャルウェハーの全面に、深さが例えば $4\text{ . }5\text{ }\mu\text{m}$ 以上であり、不純物濃度が例えば $2 \times 10^{17}\text{ cm}^{-3}$ である、p型ベース層5を積層する。そして、p型ベース層5の一部を残して、p型ベース層5の厚さが例えば $2\text{ }\mu\text{m}$ になるまで、ドライエッチングを行う。これによって、残されたp型ベース層5が突出領域15となる。

#### 【0042】

つぎに、イオン注入によって、p型ベース層5の突出領域15の表面層に比較的高濃度のA1イオンを注入する。そして、活性化アニール処理を行うことで、深さが例えば $0\text{ . }5\text{ }\mu\text{m}$ であり、不純物濃度が例えば $2 \times 10^{20}\text{ cm}^{-3}$ である、p<sup>+</sup>型ボディコンタクト領域6を形成する。このとき、実施の形態1と同様に、p<sup>+</sup>型ボディコンタクト領域6の底部からpn接合(p型ベース層5とn<sup>-</sup>型ドリフト層3との界面)までの距離を $4\text{ }\mu\text{m}$ 以上とする。以降の処理は、実施の形態1と同様のため説明を省略する。

#### 【0043】

実施の形態2によれば、実施の形態1と同様の効果を得ることができる。

#### 【0044】

なお、本実施の形態においては、第1導電型をn型とし、第2導電型をp型としたが、これに限るものではない。例えば、第2導電型をp型とし、第1導電型をn型としてもよい。

#### 【産業上の利用可能性】

#### 【0045】

以上のように、本発明にかかる炭化珪素半導体装置は、トレンチゲート構造を有するMOSFETやIGBTなどの炭化珪素半導体装置に有用であり、特に、MOS型電力用炭化珪素半導体装置に適している。

#### 【符号の説明】

#### 【0046】

- 1 n<sup>+</sup>型4H-SiC基板

- 2 n型バッファー層

- 3 n<sup>-</sup>型ドリフト層

- 4 第1トレンチ

- 5 p型ベース層

- 6 p<sup>+</sup>型ボディコンタクト領域

- 7 n<sup>+</sup>型ソース領域

- 8 第2トレンチ

- 9 ゲート酸化膜

- 10 ゲート電極

- 11 層間絶縁膜

- 12 ソース電極

- 13 ドレイン電極

- 14 メタル

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 8 G |

| H 01 L | 29/78 | 6 5 8 A |

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 21/28 | 3 0 1 B |

| H 01 L | 29/50 | M       |

(56)参考文献 特開2008-235546(JP,A)

特開平09-102606(JP,A)

特開2003-158267(JP,A)

特開昭58-202575(JP,A)

米国特許第6509607(US,B1)

特表2005-525701(JP,A)

特開2002-026322(JP,A)

特開2004-221370(JP,A)

特開平09-097904(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| H 01 L | 21 / 336 |

| H 01 L | 29 / 12  |

| H 01 L | 29 / 417 |

| H 01 L | 29 / 66  |

| H 01 L | 29 / 739 |

| H 01 L | 29 / 78  |