(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6152547号

(P6152547)

(45) 発行日 平成29年6月28日(2017.6.28)

(24) 登録日 平成29年6月9日(2017.6.9)

(51) Int.Cl.

A 63 F 7/02 (2006.01)

F 1

A 63 F 7/02 326 Z

請求項の数 1 (全 98 頁)

|            |                                   |           |                                            |

|------------|-----------------------------------|-----------|--------------------------------------------|

| (21) 出願番号  | 特願2016-92298 (P2016-92298)        | (73) 特許権者 | 000132747<br>株式会社ソフィア<br>群馬県桐生市境野町7丁目201番地 |

| (22) 出願日   | 平成28年5月2日(2016.5.2)               | (74) 代理人  | 110002468<br>特許業務法人後藤特許事務所                 |

| (62) 分割の表示 | 特願2012-63787 (P2012-63787)<br>の分割 | (74) 代理人  | 100075513<br>弁理士 後藤 政喜                     |

| 原出願日       | 平成24年3月21日(2012.3.21)             | (74) 代理人  | 100120260<br>弁理士 飯田 雅昭                     |

| (65) 公開番号  | 特開2016-135432 (P2016-135432A)     | (72) 発明者  | 園田 欽章<br>群馬県太田市吉沢町990番地 株式会社<br>ソフィア内      |

| (43) 公開日   | 平成28年7月28日(2016.7.28)             | (72) 発明者  | 亀井 欽一<br>群馬県太田市吉沢町990番地 株式会社<br>ソフィア内      |

| 審査請求日      | 平成28年5月30日(2016.5.30)             |           |                                            |

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の始動条件の成立により変動表示ゲームを実行し、該変動表示ゲームが特別な結果となる場合に遊技者に特典を付与する特別遊技状態を発生させる遊技機において、

前記変動表示ゲームの進行を制御するとともに、前記特別遊技状態を発生させる制御を行う遊技制御装置と、

前記遊技制御装置からの指令により前記変動表示ゲームに関わる表示の制御を行う表示制御装置と、を備えるとともに、

前記遊技制御装置には、

遊技制御プログラムを記憶する遊技制御プログラム記憶手段と、

前記遊技制御プログラムにより所要の演算処理を行う演算処理手段と、

前記演算処理を行う際に値が記憶されるレジスタと、

前記演算処理手段によって更新される情報が記憶される更新情報記憶手段と、

が備えられ、

前記レジスタには、

第1のレジスタ群と、

前記第1のレジスタ群と同じ構成を有する第2のレジスタ群と、

前記演算処理手段による演算結果を記憶するためのフラグレジスタと、が含まれ、

前記フラグレジスタには、前記遊技制御プログラムによる演算処理でアクセス可能とするレジスタ群を特定可能なセレクト情報が含まれ、

10

20

前記演算処理手段は、

前記セレクト情報が示しているレジスタ群にアクセス可能に構成され、

所定の起動信号が発生すると、前記第1のレジスタ群にアクセス可能な状態に設定した後、前記遊技制御プログラムのリセットアドレスに設定された命令を実行し、

前記遊技制御プログラムは、

前記第1のレジスタ群にアクセス可能にするためのレジスタ群指定命令を使用せずに構成されることを特徴とする遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、レジスタを備えたプロセッサによって制御を行う遊技機に関する。

【背景技術】

【0002】

従来よりもプログラムコードを削減し、記憶手段の記憶容量を削減するために、CPUからI/O空間を介してアクセス可能な第1の記憶領域を少なくとも有する記憶手段を備える遊技機が知られている（例えば、特許文献1）。この特許文献1の遊技機では、特許文献1の段落[0137]～[0142]に記載があるように、LD命令、IN命令、OUT命令を適宜使い分けることで、プログラム全体のステート数やプログラムコード量を削減している。

【先行技術文献】

20

【特許文献】

【0003】

【特許文献1】特開2009-183500号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

呼び出し元のモジュールで用いられていたレジスタの値が、呼び出し先のサブモジュールで変更されてしまうと、CPUの演算処理に支障を来たす。そのため、従来の遊技機では、呼び出し先のモジュール内にて、PUSH命令やPOP命令を記述する必要があり、プログラム容量が増えてしまう要因となっていた。

30

【0009】

本発明は、上記のような問題点を解決するためになされたもので、遊技制御プログラムのコード量を削減することを目的とする。

【課題を解決するための手段】

【0010】

本発明の代表的な一形態では、所定の始動条件の成立により変動表示ゲームを実行し、該変動表示ゲームが特別な結果となる場合に遊技者に特典を付与する特別遊技状態を発生させる遊技機において、前記変動表示ゲームの進行を制御するとともに、前記特別遊技状態を発生させる制御を行う遊技制御装置と、前記遊技制御装置からの指令により前記変動表示ゲームに関わる表示の制御を行う表示制御装置と、を備えるとともに、前記遊技制御装置には、遊技制御プログラムを記憶する遊技制御プログラム記憶手段と、前記遊技制御プログラムにより所要の演算処理を行う演算処理手段と、前記演算処理を行う際に値が記憶されるレジスタと、前記演算処理手段によって更新される情報が記憶される更新情報記憶手段と、が備えられ、前記レジスタには、第1のレジスタ群と、前記第1のレジスタ群と同じ構成を有する第2のレジスタ群と、前記演算処理手段による演算結果を記憶するためのフラグレジスタと、が含まれ、前記フラグレジスタには、前記遊技制御プログラムによる演算処理でアクセス可能とするレジスタ群を特定可能なセレクト情報が含まれ、前記演算処理手段は、前記セレクト情報が示しているレジスタ群にアクセス可能に構成され、所定の起動信号が発生すると、前記第1のレジスタ群にアクセス可能な状態に設定した後、前記遊技制御プログラムのリセットアドレスに設定された命令を実行し、前記遊技制御

40

50

プログラムは、前記第1のレジスタ群にアクセス可能にするためのレジスタ群指定命令を使用せずに構成される。

【発明の効果】

【0011】

本発明の一形態によれば、遊技制御プログラムのコード量を削減することが可能となる。

【図面の簡単な説明】

【0012】

【図1】本発明の第1の実施の形態の遊技装置の構成を説明する図である。

【図2】本発明の第1の実施の形態の遊技機の背面図である。

10

【図3】本発明の第1の実施の形態の遊技盤の正面図である。

【図4】本発明の第1の実施の形態の遊技装置のブロック図である。

【図5】本発明の第1の実施の形態の遊技用演算処理装置（アミューズチップ）のブロック図である。

【図6】本発明の第1の実施の形態の遊技制御装置におけるシリアル送信回路の構成例を示すブロック図である。

【図7】本発明の第1の実施の形態の送信シリアルチャンネル設定レジスタの構成例を示す図である。

【図8】本発明の第1の実施の形態の送信制御レジスタの構成例を示す図である。

【図9】本発明の第1の実施の形態の送信データステータスレジスタの構成例を示す図である。

20

【図10】本発明の第1の実施の形態の送信データレジスタ（1段分）の構成例を示す図である。

【図11】本発明の第1の実施の形態の遊技制御装置に備わる遊技用演算処理装置（アミューズチップ）とその周辺のブロック図である。

【図12】本発明の第1の実施の形態のCPUコアの内部構成を説明するブロック図である。

【図13】本発明の第1の実施の形態のフラグレジスタの構成を説明する図である。

【図14】本発明の第1の実施の形態のユーザワークRAMの一例を示す図である。

【図15】本発明の第1の実施の形態のユーザワークRAMに割り当てられたワークエリアに格納されるデータの具体例を説明する図であり、保留カウンタ、各種乱数の生成領域及び普団乱数の保存領域を示す図である。

30

【図16】本発明の第1の実施の形態のユーザワークRAMに割り当てられたワークエリアに格納されるデータの具体例を説明する図であり、第1特図変動表示ゲームを実行するために必要な各種乱数の保存領域を示す図である。

【図17】本発明の第1の実施の形態のユーザワークRAMに割り当てられたワークエリアに格納されるデータの具体例を説明する図であり、第2特図変動表示ゲームを実行するために必要な各種乱数の保存領域を示す図である。

【図18】本発明の第1の実施の形態のスタック領域の一例を示す図である。

【図19】本発明の第1の実施の形態のスタック領域の一例を示す図である。

40

【図20】本発明の第1の実施の形態のスタック領域の変形例を示す図である。

【図21】本発明の第1の実施の形態のCPUコアによって実行される遊技制御プログラムを記述するためのアセンブリ言語の命令を説明する図であり、変換後のコードデータにアドレス部を含まない命令（変換後のコードデータが命令コード部のみで構成される命令）を示す図である。

【図22】本発明の第1の実施の形態のCPUコアによって実行される遊技制御プログラムを記述するためのアセンブリ言語の命令を説明する図であり、変換後のコードデータに命令コード部とアドレス部の各々を含む命令を示す図である。

【図23】本発明の第1の実施の形態の各装置（遊技制御装置、払出手制御装置、及び演出制御装置）の電源投入時処理のフローチャートである。

50

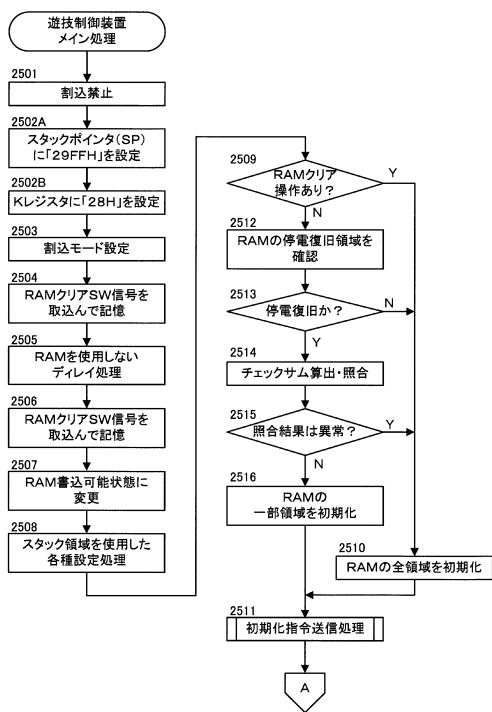

【図24】本発明の第1の実施の形態の遊技制御装置プログラム開始準備処理を説明するフローチャートである。

【図25】本発明の第1の実施の形態の遊技制御装置メイン処理の前半部のフローチャートである。

【図26】本発明の第1の実施の形態の遊技制御装置メイン処理の後半部のフローチャートである。

【図27】本発明の第1の実施の形態の遊技制御装置メイン処理におけるステップ2501からステップ2502Bまでの処理を説明する図である。

【図28】本発明の第1の実施の形態のディレイ処理を説明する図である。

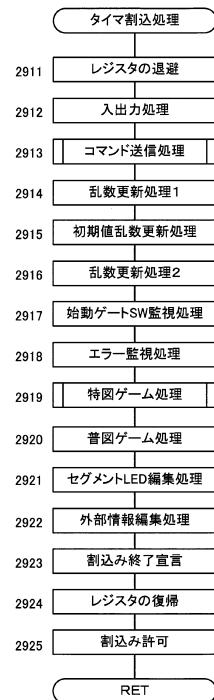

【図29】本発明の第1の実施の形態のタイマ割込処理を示すフローチャートである。 10

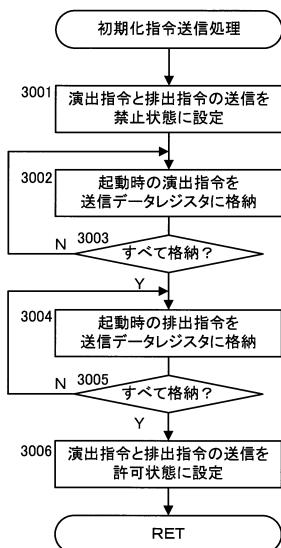

【図30】本発明の第1の実施の形態の遊技制御装置から、演出制御装置及び払出制御装置に初期化指令信号を送信する初期化指令送信処理の手順を示すフローチャートである。

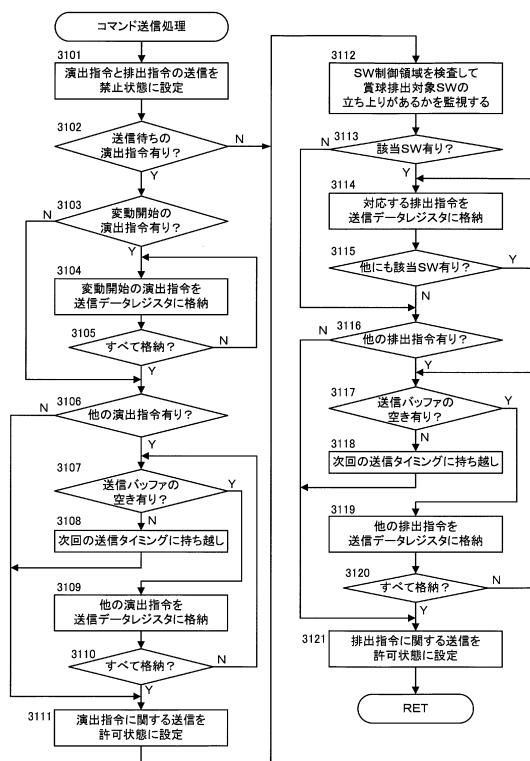

【図31】本発明の第1の実施の形態の遊技制御装置から、演出制御装置及び払出制御装置にコマンドを送信するためのコマンド送信処理の手順を示すフローチャートである。

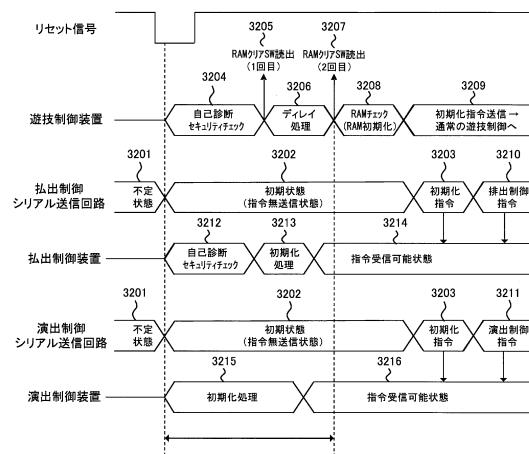

【図32】本発明の第1の実施の形態の電源投入時の遊技制御装置、払出制御装置、及び演出制御装置が行う処理、並びに、遊技制御装置に備わるシリアル送信回路の状態のタイミングチャートである。

【図33】本発明の第1の実施の形態の遊技制御装置から払出制御装置に送信される排出指令の一例を示す図である。

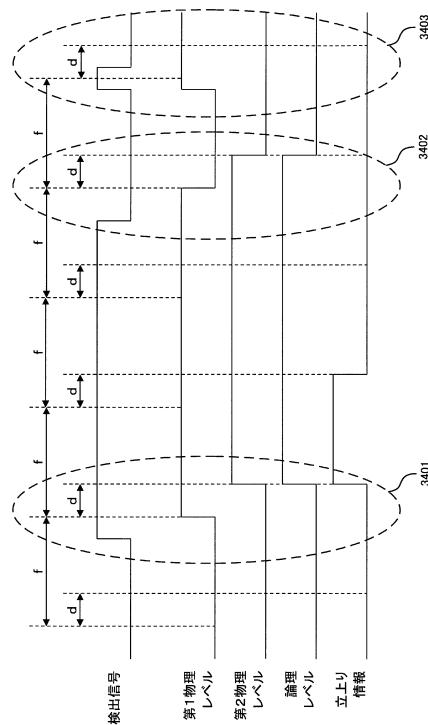

【図34】本発明の第1の実施の形態のスイッチの立ち上がりを検出する手順を示すタイミングチャートである。 20

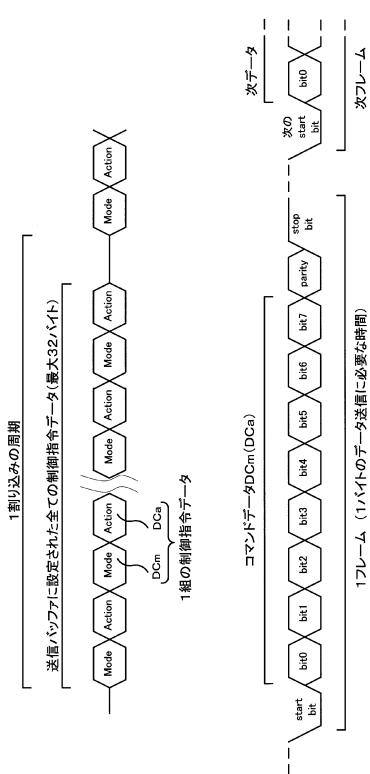

【図35】本発明の第1の実施の形態の遊技制御装置から演出制御装置に送信される演出制御コマンドの一例を示す図である。

【図36】本発明の第1の実施の形態の遊技制御装置から演出制御装置に送信される送信データの構成を示す説明図であり、(a)は送信データの概略構成を示し、(b)は送信データの詳細構成を示している。

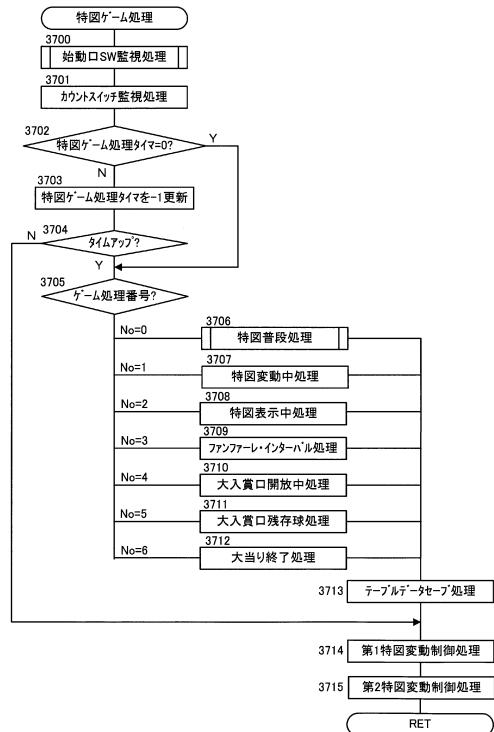

【図37】本発明の第1の実施の形態の特図ゲーム処理の手順を示すフローチャートである。

【図38】本発明の第1の実施の形態の特図ゲーム処理におけるゲーム処理番号に基づいた分岐の処理を説明する図である。 30

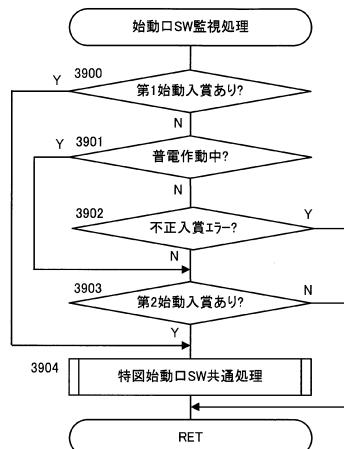

【図39】本発明の第1の実施の形態の始動口SW監視処理の手順を示すフローチャートである。

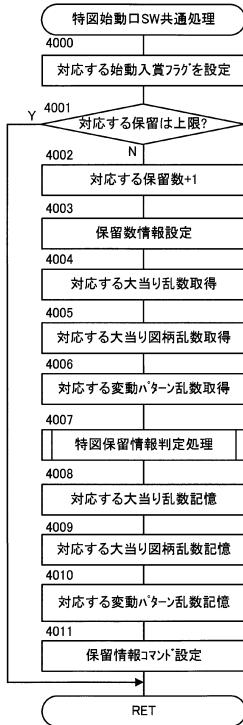

【図40】本発明の第1の実施の形態の特図始動口SW共通処理の手順を示すフローチャートである。

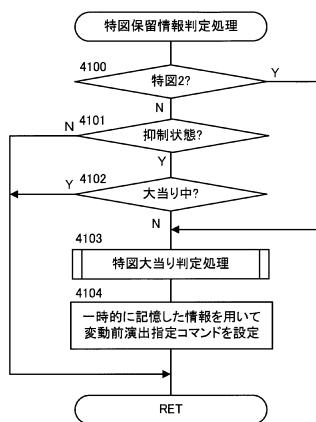

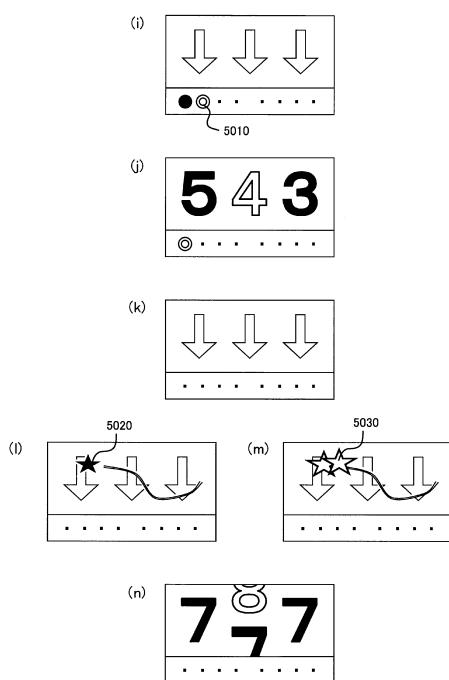

【図41】本発明の第1の実施の形態の特図保留情報判定処理の手順を示すフローチャートである。

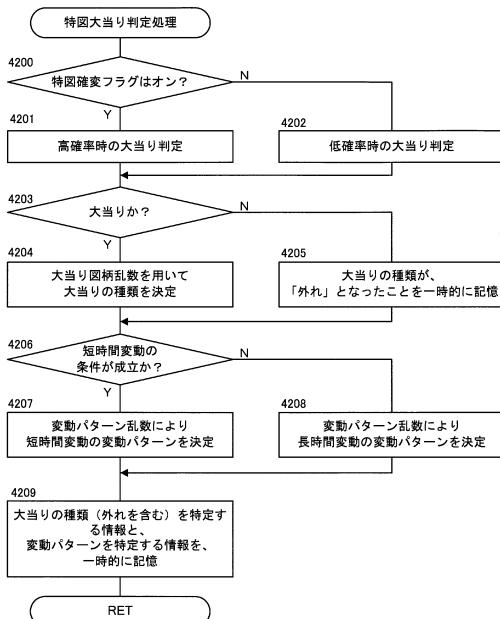

【図42】本発明の第1の実施の形態の特図大当たり判定処理の手順を示すフローチャートである。

【図43】本発明の第1の実施の形態の後半変動パターンテーブルである。

【図44】本発明の第1の実施の形態の前半変動パターンテーブルである。 40

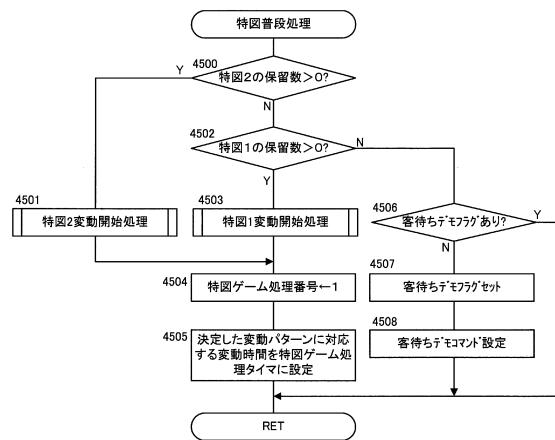

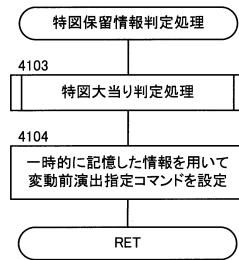

【図45】本発明の第1の実施の形態の特図普段処理の手順を示すフローチャートである。

【図46】本発明の第1の実施の形態の特図1/特図2変動開始処理の手順を示すフローチャートである。

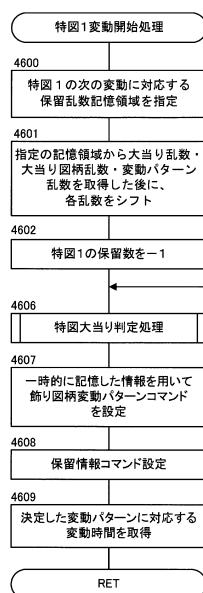

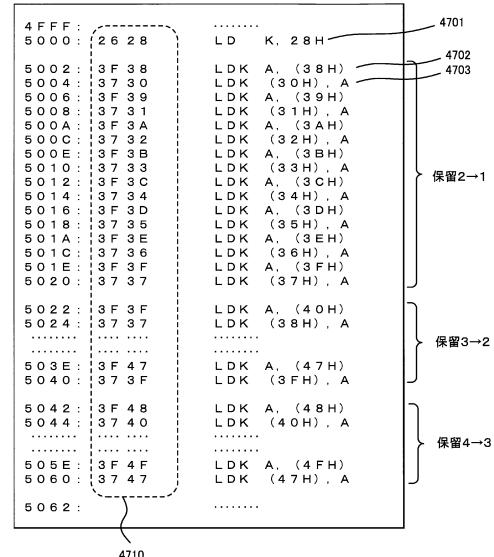

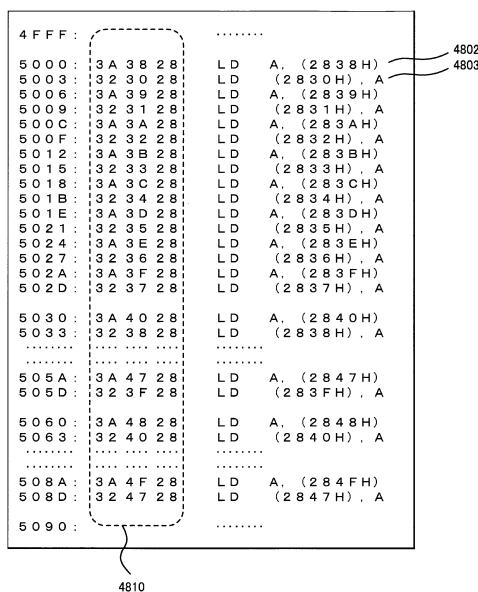

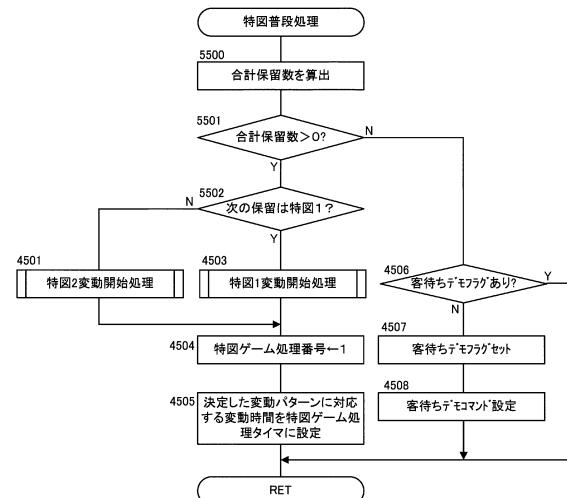

【図47】本発明の第1の実施の形態における始動記憶をシフトさせる処理のプログラムの一例を示す図であり、Kレジスタを利用して記憶容量を削減したプログラムである。

【図48】本発明の第1の実施の形態における始動記憶をシフトさせる処理のプログラムの一例を示す図であり、従来のプログラムである。

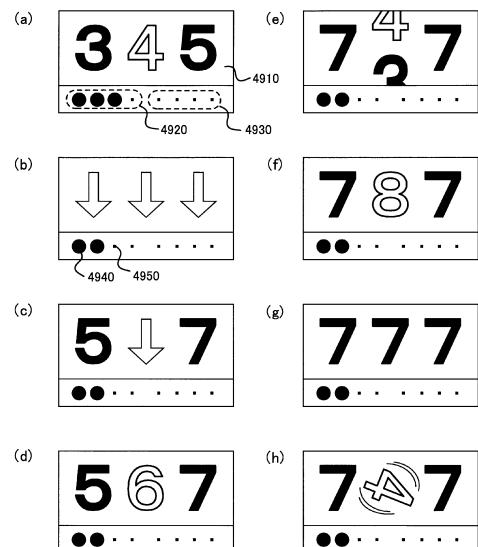

【図49】本発明の第1の実施の形態の変動表示ゲームにおける画面遷移を説明する図である。 50

【図50】本発明の第1の実施の形態の変動表示ゲームにおける画面遷移を説明する図である。

【図51】本発明の第1の実施の形態の変形例のユーザワークRAMの一例を示す図である。

【図52】本発明の第2の実施の形態の特図変動表示ゲームを実行するために必要な各種乱数の保留1から4までの保存領域を示す図である。

【図53】本発明の第2の実施の形態の特図変動表示ゲームを実行するために必要な各種乱数の保留5から8までの保存領域を示す図である。

【図54】本発明の第2の実施の形態の特図保留情報判定処理の手順を示すフローチャートである。

【図55】本発明の第2の実施の形態の特図普段処理の手順を示すフローチャートである。

#### 【発明を実施するための形態】

##### 【0013】

以下、本発明の実施の形態について、図面を参照しながら説明する。

##### 【0014】

なお、以下の実施の形態の説明における前後左右とは、遊技者から見た、つまり遊技盤（遊技機）に向かって見た方向を指すものとする。

##### 【0015】

（第1の実施の形態）

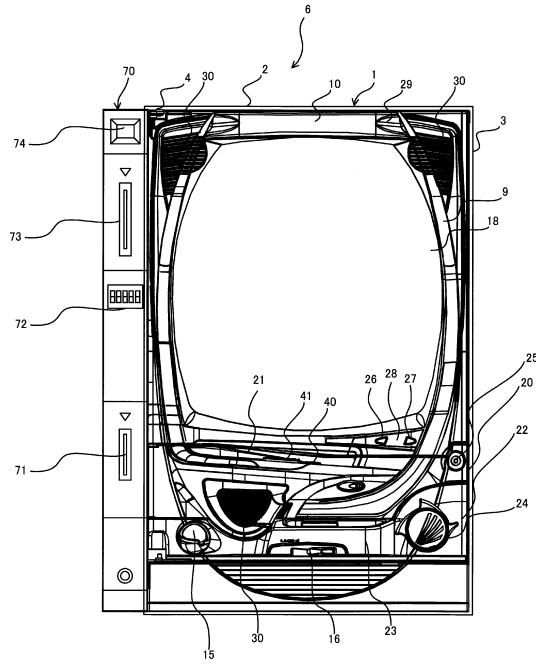

図1は、本発明の第1の実施の形態の遊技装置6の構成を説明する図である。

##### 【0016】

遊技装置6は、有価値を記憶する記憶媒体が挿入されるカードユニット70及び実際に遊技を行い、遊技媒体を払出可能な遊技機1を備える。

##### 【0017】

まず、遊技機1について説明する。

##### 【0018】

遊技機1の前面枠3は、本体枠（外枠）2にヒンジ4によって開閉回動可能に組み付けられる。遊技盤5（図3参照）は前面枠3の表側に形成された収納部（図示省略）に収装される。また、前面枠3には、遊技盤5の前面を覆うカバーガラス（透明部材）を備えたガラス枠18が取り付けられている。

##### 【0019】

ガラス枠18のカバーガラスの周囲には、装飾光が発光される装飾部材9が備えられている。この装飾部材9の内部にはランプやLED等からなる装飾装置が備えられている。この装飾装置を所定の発光態様によって発光させることによって、装飾部材9が所定の発光態様で発光する。

##### 【0020】

ガラス枠18の左右には、音響（例えば、効果音）を発するスピーカ30が備えられている。また、ガラス枠18の上方には照明ユニット10が備えられている。照明ユニット10の内部には、装飾装置が備えられている。

##### 【0021】

照明ユニット10の右側には、遊技機1のエラー発生や前面枠3の開放をホール店員に通知するためのエラー報知LED29が備えられている。

##### 【0022】

前面枠3の下部の開閉パネル20には図示しない打球発射装置に遊技球を供給する上皿21が備えられている。さらに、固定パネル22には灰皿15、下皿23及び打球発射装置の操作部24等が備えられている。下皿23には、下皿23に貯まった遊技球を排出するための下皿球抜き機構16が備えられる。前面枠3下部右側には、ガラス枠18を施錠するための鍵25が備えられている。

##### 【0023】

10

20

30

40

50

また、遊技者が操作部 24 を回動操作することによって、打球発射装置は、上皿 21 から供給される遊技球を発射する。

**【0024】**

また、上皿 21 の上縁部には、遊技者からの操作入力を受け付けるためのセレクトスイッチ 40 及び操作スイッチ 41 が備えられている。

**【0025】**

遊技者がセレクトスイッチ 40 を操作することによって、表示装置 8 (図 3 参照) における変動表示ゲームの演出内容を選択することができる。また、遊技者が操作スイッチ 41 を操作することによって、表示装置 8 における変動表示ゲームに、遊技者の操作を介入させた演出を行うことができる。

10

**【0026】**

上皿 21 の右上部には、遊技者が遊技媒体を借りる場合に操作する球貸ボタン 26、及び、カードユニット 70 からプリペイドカードを排出させるために操作される排出ボタン 27 が設けられている。これらのボタン 26、27 の間には、プリペイドカードの残高を表示する残高表示部 28 が設けられる。

**【0027】**

次に、カードユニット 70 について説明する。

**【0028】**

カードユニット 70 の下部には、プリペイドカード又は会員カード等のカードを挿入可能なカード挿入口 71 が設けられる。

20

**【0029】**

プリペイドカード又は会員カード等のカードには、当該カードの一意な識別子、当該カードの所有者(遊技者)の会員情報、及び残高等が記憶されている。会員情報には、カードの所有者の住所、氏名、年齢、及び職業等が含まれる。

**【0030】**

カード挿入口 71 にプリペイドカード又は会員カード等のカードが挿入された場合、図示しないカードリーダ・ライタによって、カードに記憶された情報が読み出される。そして、当該カードに記憶された残高が、遊技機 1 の残高表示部 28 及びカードユニット 70 の中央付近に設けられた残高表示部 72 に表示される。

30

**【0031】**

残高表示部 72 の上方には、紙幣を挿入可能な紙幣挿入口 73 が設けられる。紙幣挿入口 73 に挿入された紙幣の有価価値は、カードに残高として記憶される。

**【0032】**

紙幣挿入口 73 の上方には、動作表示部 74 が設けられる。動作表示部 74 は、カードユニット 70 の動作に対応して色で点灯する。

**【0033】**

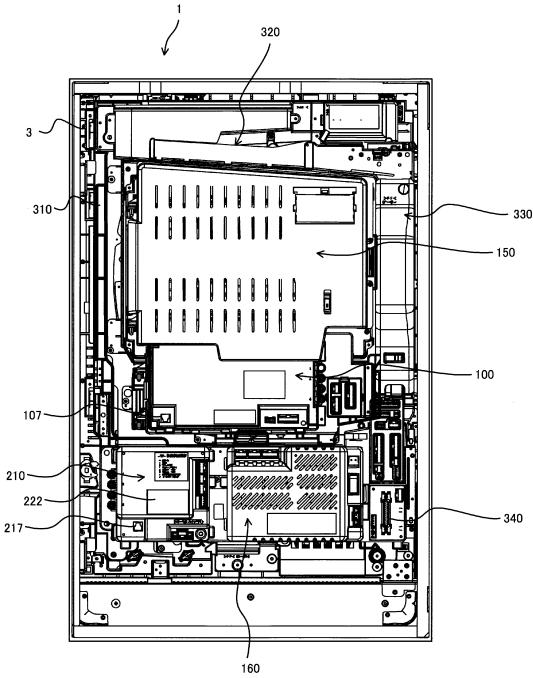

次に、図 2 を参照しながら遊技機 1 の裏面側について説明する。図 2 は、本発明の第 1 の実施の形態の遊技機 1 の背面図である。

**【0034】**

遊技機 1 の裏面側、具体的には、前面枠 3 の裏面側には、中央に略正方形状の開口部を有する枠状の裏機構盤 310 が取り付けられる。

40

**【0035】**

裏機構盤 310 の上部には、島設備に設けられた補給装置(図示省略)から補給された遊技球を貯留すると共に、貯留した遊技球を流下させる球貯留ユニット 320 が配設される。

**【0036】**

裏機構盤 310 の側部(図 2 中右側)には、球貯留ユニット 320 から流下してきた遊技球を、遊技機前面に配設された上皿 21 及び下皿 23 に払い出す球排出ユニット 330 が配設される。

**【0037】**

50

裏機構盤310の中央部には、遊技を統括的に制御する遊技制御装置100と、遊技制御装置100から送信される演出制御指令に基づいて変動表示ゲームの演出を制御する演出制御装置150とが配設される。

【0038】

遊技制御装置100には、図示しない検査装置に接続される検査装置接続端子107が配設される。

【0039】

裏機構盤310の下部には、遊技制御装置100から送信されるデータに基づいて球排出ユニット330の動作を制御し、遊技者に賞球を付与する払出制御装置(付与制御装置)210と、電源装置160とが配設される。

10

【0040】

払出制御装置210には、図示しない検査装置に接続される検査装置接続端子217及び払出制御装置210に発生したエラーの種類を数字で表示するエラーナンバー表示器222が配設される。

【0041】

また、電源装置160の右側の裏機構盤310には、遊技機1をカードユニット70に接続するためのカードユニット接続端子340が配設される。

【0042】

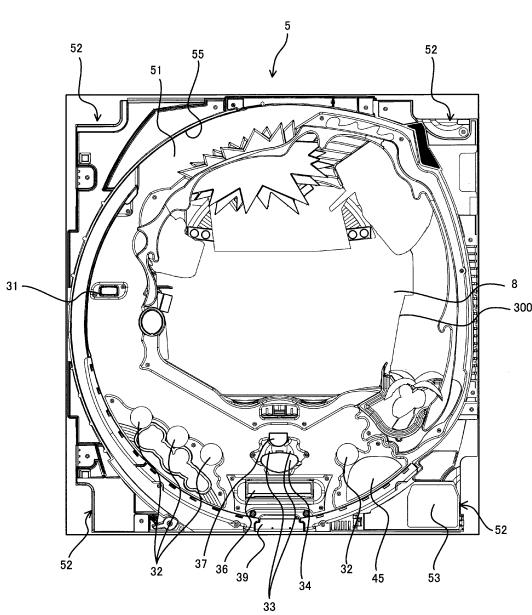

次に、遊技盤5について、図3を参照しながら説明する。図3は、本発明の第1の実施の形態の遊技盤5の正面図である。

20

【0043】

遊技盤5の表面には、ガイドレール55で囲われた略円形状の遊技領域51が形成される。遊技領域51は、遊技盤5の四方に各々設けられた樹脂製のサイドケース52及びガイドレール55によって構成される。遊技領域51の右下側のサイドケース52は、前面の中央部が黒色透明の証紙プレート53で覆われている。

【0044】

遊技領域51には、ほぼ中央に表示装置8が設けられるセンターケース300が配置される。表示装置8はセンターケース300に設けられた凹部に、センターケース300の前面より奥まった位置に取り付けられている。すなわち、センターケース300は表示装置8の表示領域の周囲を囲い、表示装置8の表示領域から突出して設けられている。

30

【0045】

また、遊技領域51の右下の領域には、図4で後述する特図表示器120及び普図表示器121を一体化した、図柄表示ユニット45が備えられる。

【0046】

表示装置8は、例えば、LCD(液晶表示器)、CRT(ブラウン管)等で表示画面が構成されている。表示画面の画像を表示可能な領域(表示領域)には、複数の変動表示領域が設けられており、各変動表示領域に識別情報(特別図柄)や特図(特別図柄)変動表示ゲームを演出するキャラクタが表示される。表示画面の変動表示領域には、識別情報として割り当てられた三つの特別図柄が変動表示(可変表示)して特図変動表示ゲームが行われる。その他、表示画面には遊技の進行に基づく画像(例えば、大当たり表示、ファンファーレ表示、エンディング表示等)が表示される。

40

【0047】

センターケース300の左側には、普通図柄始動ゲート31が設けられる。センターケース300の左下側には、三つの一般入賞口32が備えられ、センターケース300の右下側には、一つの一般入賞口32が備えられている。

【0048】

センターケース300の下方には、第1始動入賞口37と、第1始動入賞口37の直下に配設され、上部に逆「ハ」の字状に開いて遊技球が流入し易い状態に変換する一対の開閉部材を含む普通変動入賞装置33を備える第2始動入賞口34とが配置される。そして、遊技球が第1始動入賞口37又は第2始動入賞口34に入賞した場合には、補助遊技と

50

して特図変動表示ゲームが実行される。すなわち、第1始動入賞口37又は第2始動入賞口34に遊技球が入賞することが特図変動表示ゲームを開始するための始動条件となっており、第1始動入賞口37及び第2始動入賞口34が当該始動条件を発生させる変動始動入賞装置をなしている。なお、第1始動入賞口37に遊技球が入賞したことによって実行される特図変動表示ゲームを第1特図変動表示ゲームとし、第2始動入賞口34に遊技球が入賞したことによって実行される特図変動表示ゲームを第2特図変動表示ゲームとする。

#### 【0049】

また、センターケース300に設けられた始動入賞口の下方には、表示装置8の作動結果(特図変動表示ゲームの結果)によって遊技球を受け入れない状態と受け入れ易い状態とに変換可能な特別変動入賞装置(大入賞口)36が配設される。10

#### 【0050】

遊技機1では、図示しない発射装置から遊技領域51に向けて遊技球(パチンコ球)が打ち出されることによって遊技が行われる。打ち出された遊技球は、遊技領域51内の各所に配置された釘や風車等の方向転換部材によって転動方向を変えながら遊技領域51を流下する。そして、普通図柄始動ゲート31、一般入賞口32、第1始動入賞口37、第2始動入賞口34、又は特別変動入賞装置36に入賞するか、遊技領域51の最下部に設けられたアウトロ39から排出される。

#### 【0051】

また、第2始動入賞口34の状態には、普通変動入賞装置33の開閉によって、遊技球が入賞しやすい状態(入賞容易状態)と遊技球が入賞しにくい状態(非入賞容易状態)とがある。20

#### 【0052】

通常、普通変動入賞装置33が閉状態の場合には、第2始動入賞口34は、遊技球が入賞しにくい状態となる。普通図柄始動ゲート31を遊技球が通過することによって、普図変動表示ゲームが実行され、普図変動表示ゲームの結果が当りとなると、普通変動入賞装置33が開状態に変換され、第2始動入賞口34は遊技球が入賞し易い状態となる。

#### 【0053】

一般入賞口32への遊技球の入賞は、一般入賞口32に備えられた入賞口SW(スイッチ)32A～32N(図4参照)によって検出される。30

#### 【0054】

第1始動入賞口37への遊技球の入賞は第1特図始動SW(スイッチ)37A(図4参照)によって検出される。この遊技球の通過タイミングによって抽出された各種乱数は、遊技制御装置100内の特図1始動記憶領域に特別図柄入賞記憶として所定回数(例えば、最大で4回分)を限度に記憶される。

#### 【0055】

また、第2始動入賞口34への遊技球の入賞は第2特図始動SW(スイッチ)34A(図4参照)によって検出される。この遊技球の通過タイミングによって抽出された各種乱数は、遊技制御装置100内の特図2始動記憶領域に特別図柄入賞記憶として所定回数(例えば、最大で4回分)を限度に記憶される。40

#### 【0056】

遊技制御装置100は、これらの特別図柄入賞記憶に基づき、図柄表示ユニット45を形成する特図表示器120(図4参照)にて、第1特図動表示ゲーム及び第2特図動表示ゲームを行う。

#### 【0057】

ここで特図表示器120について説明する。特図表示器120は、図示しない第1特図図柄表示部、第1特図入賞記憶数表示部、第2特図図柄表示部、及び第2特図入賞記憶数表示部を有する。

#### 【0058】

そして、遊技球が第1始動入賞口37に入賞して特別図柄入賞記憶が発生すると、第150

特図入賞記憶数表示部に特別図柄入賞記憶の記憶数が表示され、第1特図図柄表示部にて第1特図変動表示ゲームが実行される。同様に、遊技球が第2始動入賞口34に入賞して特別図柄入賞記憶が発生すると、第2特図入賞記憶数表示部に特別図柄入賞記憶の記憶数が表示され、第2特図図柄表示部にて第2特図変動表示ゲームが実行される。

#### 【0059】

なお、第1始動入賞口37への入賞が所定のタイミングでなされたとき（具体的には、入賞検出時の当り乱数値が当り値であるとき）には、第1特図変動表示ゲームの結果として表示図柄により特別結果態様が導出される。具体的には、第1図柄表示部にて、対応する特定の図柄（例えば、「1」～「9」までのいずれかの数字等）が停止表示される。なお、第1特図変動表示ゲームがはずれの場合には、第1特図図柄表示部にて、はずれに対応する図柄（例えば「0」等）が停止表示される。10

#### 【0060】

同様に、第2始動入賞口34への入賞が所定のタイミングでなされたとき（具体的には、入賞検出時の当り乱数値が当り値であるとき）には、第2特図変動表示ゲームの結果として表示図柄により特別結果態様が導出される。具体的には、第2特図図柄表示部にて、対応する特定の図柄（例えば、「1」～「9」までのいずれかの数字等）が停止表示される。なお、第2特図変動表示ゲームがはずれの場合には、第2特図図柄表示部にて、はずれに対応する図柄（例えば「0」等）が停止表示される。

#### 【0061】

そして、第1特図変動表示ゲームの結果として特別結果態様が導出された場合、或いは、第2特図変動表示ゲームの結果として特別結果態様が導出された場合には、大当たり状態（特別遊技状態）が発生する。このとき、特別変動入賞装置36は、大入賞口ソレノイド38（図4参照）への通電によって、所定の時間（例えば、30秒）だけ、遊技球を受け入れない閉状態から遊技球を受け入れやすい開状態に変換される。すなわち、特別変動入賞装置36が所定の時間又は所定数の遊技球が入賞するまで大きく開くので、この間遊技者は多くの遊技球を獲得することができるという特典が付与される。20

#### 【0062】

なお、表示装置8においても、図柄表示ユニット45の特図表示器120で実行される第1特図変動表示ゲームと第2特図変動表示ゲームに同期して、飾り特図変動表示ゲームが実行される。このとき、前述した数字等で構成される特別図柄（識別情報）が左（第一特別図柄）、右（第二特別図柄）、中（第三特別図柄）の順に変動表示を開始して、飾り特図変動表示ゲームに関する画像が表示される。30

#### 【0063】

第1特図変動表示ゲーム若しくは第2特図変動表示ゲームが特別結果態様を導出する場合は、表示装置8でも特定態様の図柄が導出されて停止表示する。具体的には、表示装置8では、三つの特別図柄が揃った状態（大当たり図柄）で停止する。第1特図変動表示ゲーム及び第2特図変動表示ゲームが特別結果態様を導出しない場合は、表示装置8でも特定態様の図柄を停止表示しないように制御される。

#### 【0064】

なお、本実施形態では、図柄表示ユニット45で実行される第1特図変動表示ゲーム及び第2特図変動表示ゲームと、表示装置8で実行される飾り特図変動表示ゲームのいずれをも特図変動表示ゲームとして扱うものとする。40

#### 【0065】

特別変動入賞装置36への遊技球の入賞は、カウントSW（スイッチ）36A（図4参照）によって検出される。

#### 【0066】

普通図柄始動ゲート31への遊技球の通過は、普図始動SW（スイッチ）31A（図4参照）で検出される。この遊技球の通過タイミングによって抽出された普図乱数は、遊技制御装置100内の普図始動記憶領域に普通図柄入賞記憶として所定回数（例えば、最大で4回分）を限度に記憶される。遊技制御装置100は、この普通図柄入賞記憶に基づき50

、図柄表示ユニット45を形成する普図表示器121(図4参照)にて、普図変動表示ゲームを行う。

#### 【0067】

ここで普図表示器121について説明する。普図表示器121は、図示しない普図図柄表示部と普図入賞記憶数表示部を有する。前述したように、遊技球が普通図柄始動ゲート31を通過して普通図柄入賞記憶が発生すると、この普図図柄表示部にて普図変動表示ゲームが実行される。また、普図入賞記憶数表示部には、普通図柄入賞記憶の記憶数が表示される。

#### 【0068】

そして、遊技球が普通図柄始動ゲート31を通過して普通図柄入賞記憶が発生すると、普図入賞記憶数表示部に普通図柄入賞記憶の記憶数が表示され、普図図柄表示部にて普図変動表示ゲームが実行される。

10

#### 【0069】

なお、普通図柄始動ゲート31の通過が所定のタイミングでなされたとき(具体的には、通過検出時の当り乱数値が当り値であるとき)には、普図図柄表示部に表示される普通図柄が当り状態で停止し、普図変動表示ゲームが当りとなる。このとき、普通変動入賞装置33は、普電ソレノイド90(図4参照)への通電により、第2始動入賞口34への入口が所定の時間(例えば、0.5秒~2.9秒の範囲内で予め定められた時間)だけ開放するように変換され、遊技球の第2始動入賞口34への入賞が許容される。これによって、遊技球が第2始動入賞口34へ入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

20

#### 【0070】

このようにして、一般入賞口32、第1始動入賞口37、第2始動入賞口34、又は特別変動入賞装置36に遊技球が入賞すると、入賞した入賞口の種類に応じた数の賞球が払出制御装置210によって制御される払出ユニットから、前面枠3の上皿21又は下皿23に排出される。

#### 【0071】

なお、本実施形態のパチンコ遊技機は、特図変動表示ゲームの結果に対応して(厳密には、特図変動表示ゲームの結果として特図表示器120に停止表示される図柄に対応して)、以後の特図変動表示ゲームの当り確率が変化する場合があり、遊技状態は、常時、特図変動表示ゲームが低確率で大当りとなる低確率状態か、当該低確率状態よりも特図変動表示ゲームが大当りとなる確率の高い高確率状態のいずれかに設定されている。なお、低確率状態を通常状態や非確変遊技状態と称したり、高確率状態を確変遊技状態(確変状態)と称したりする場合もある。

30

#### 【0072】

さらに、本実施形態のパチンコ遊技機の遊技状態は、特図変動表示ゲームの結果に対応して、普通変動入賞装置33の開放頻度が変化する場合があり、遊技状態は、常時、普通変動入賞装置33の開放頻度が低い入賞抑制状態か、当該入賞抑制状態よりも普通変動入賞装置33の開放頻度が高い入賞促進状態のいずれかに設定されている。なお、入賞抑制状態を通常状態や非時短遊技状態と称したり、入賞促進状態を時短遊技状態(時短状態)と称したりする場合もある。

40

#### 【0073】

この入賞促進状態においては、普図変動表示ゲームの実行時間が入賞抑制状態における実行時間より短くなるように制御される(例えば、入賞抑制状態で10秒に対し、入賞促進状態で1秒)。これによって、単位時間当たりの普通変動入賞装置33の開放回数が実質的に多くなるように制御される。

#### 【0074】

また、入賞促進状態においては、普図変動表示ゲームが当り結果となって普通変動入賞装置33が開放される場合に、開放時間が通常遊技状態の開放時間より長くなるように制御されてもよい(例えば、入賞抑制状態で0.5秒に対し、入賞促進状態で2.9秒)。

50

また、入賞促進状態においては、普通図柄変動表示ゲームの1回の当り結果に対して、普通変動入賞装置33が1回ではなく、複数回（例えば、2回）開放してもよい。さらに、入賞促進状態においては、普図変動表示ゲームの結果が当りとなる確率が入賞抑制状態より高くなるように制御してもよい。すなわち、入賞促進状態では、入賞抑制状態よりも普通変動入賞装置33の開放頻度が増加し、普通変動入賞装置33に遊技球が入賞しやすくなり、特図変動表示ゲームの始動が容易となる特典が付与される。

#### 【0075】

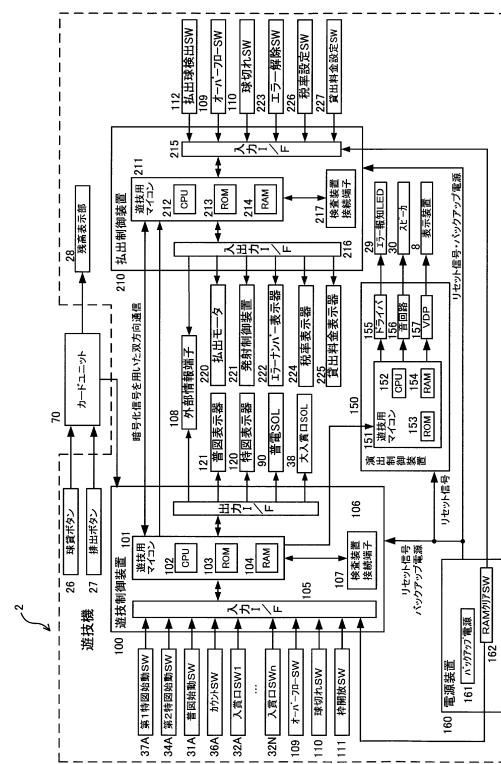

図4は、本発明の第1の実施の形態の遊技装置6のブロック図である。

#### 【0076】

遊技制御装置100は、遊技用マイコン（遊技用演算処理装置600）101、入力I/F（Interface）105、出力I/F（Interface）106及び検査装置接続端子107を備える。

10

#### 【0077】

遊技用マイコン101は、CPU102、ROM（Read Only Memory）103及びRAM（Random Access Memory）104を備える。

#### 【0078】

CPU102は、遊技を統括的に制御する主制御装置であって、遊技制御を行う。ROM103は、遊技制御のための不变の情報（プログラム、データ等）を記憶する。RAM104は、遊技制御時にワークエリアとして利用される。

20

#### 【0079】

遊技制御装置100には、遊技用マイコン101に一意に設定された識別番号を出力することが可能な検査装置接続端子107が設けられている。検査装置接続端子107に図示しない検査装置を接続すると、検査装置は遊技機1を識別することができる。

#### 【0080】

CPU102は、入力I/F105を介して各種検出器（第1特図始動SW37A、第2特図始動SW34A、普図始動SW31A、カウントSW36A、及び入賞口SW32A～入賞口SW32N、オーバーフローSW（スイッチ）109、球切れSW（スイッチ）110、及び枠開放SW（スイッチ）111）からの検出信号を受けて、大当たり抽選等、種々の処理を行う。

#### 【0081】

オーバーフロースイッチ109は、下皿23に遊技球が所定数以上貯留されていることを検出する。球切れスイッチ110は、球貯留ユニット320に配設され、球貯留ユニット320に貯留される遊技球が所定数以下になることを検出する。枠開放スイッチ111は、前面枠3の開放を検出する。

30

#### 【0082】

また、CPU102は、出力I/F106を介して、普図表示器121、特図表示器120、普電SOL（ソレノイド）90、大入賞口SOL（ソレノイド）38、払出制御装置210及び演出制御装置150に指令信号を送信し、遊技を統括的に制御する。

#### 【0083】

普図表示器121は、前述したように、普図変動表示ゲームが表示される。特図表示器120は、前述したように、第1特図変動表示ゲームと第2特図変動表示ゲームとが表示される。

40

#### 【0084】

普電SOL90は、第2始動入賞口34に遊技球が入賞可能となるように、第2始動入賞口34に備えられた開閉部材で構成された普通変動入賞装置33を所定の時間だけ開放させる。

#### 【0085】

大入賞口SOL38は、特別変動入賞装置36の大入賞口を所定の時間だけ、遊技球を受け入れない閉状態（遊技者に不利な状態）から遊技球を受け入れやすい開状態（遊技者に有利な状態）にする。

50

## 【0086】

また、遊技制御装置100は、遊技機1に関する情報を、外部情報端子108を介して、遊技店に設置された情報収集端末や遊技場内部管理装置（図示省略）に出力する。

## 【0087】

遊技制御装置100は、変動開始コマンド、客待ちデモコマンド、ファンファーレコマンド、確率情報コマンド、及びエラー指定コマンド等を、演出制御指令信号として、演出制御装置150へ送信する。

## 【0088】

次に、払出制御装置210及び演出制御装置150について説明する。

## 【0089】

演出制御装置（表示制御装置）150は、遊技制御装置100から入力される各種信号に基づいて、エラー報知LED29、スピーカ30、発光により遊技演出を行う装飾部材9（図1）及び表示装置8を制御する。

10

## 【0090】

演出制御装置150は、遊技用マイコン（遊技用演算処理装置600）151、ドライバ155、音回路156、及びVDP157を備える。

## 【0091】

遊技用マイコン151は、CPU152、ROM153及びRAM154を備える。

## 【0092】

CPU152は、演出制御を行う制御装置である。ROM153は、演出制御に必要な不变の情報（プログラム、データ等）を記憶している。RAM154は、演出制御時にワークエリアとして利用される。

20

## 【0093】

ドライバ155は、CPU152からの指令により、エラー報知LED29及び装飾部材9を制御する。音回路156は、CPU152からの指令により、効果音を生成してスピーカ30から出力する。VDP157は、CPU152からの指令により、画像データを生成して表示装置8へ出力する。

## 【0094】

払出制御装置210は、遊技制御装置100からの賞球指令信号に基づいて、払出装置の払出モータ220を駆動させ、賞球を払い出させるための制御を行う。また、払出制御装置210は、カードユニット70からの貸球要求信号に基づいて、遊技制御装置100が送信する排出指令信号に基づいて、払出装置の払出モータ220を駆動させ、貸球を払い出させるための制御を行う。

30

## 【0095】

払出制御装置210は、遊技用マイコン（遊技用演算処理装置600）211、入力I/F（Interface）215、入出力I/F（Interface）216及び検査装置接続端子217を備える。

## 【0096】

遊技用マイコン211は、CPU212、ROM213及びRAM214を備える。

## 【0097】

CPU212は、払い出しを統括的に制御する制御装置であって、払出制御を司る。ROM213は、払出制御のための不变の情報（プログラム、データ等）を記憶している。RAM214は、払出制御時にワークエリアとして利用される。

40

## 【0098】

CPU212は、入力I/F215を介して払出球検出スイッチ112、オーバーフロースイッチ109、球切れスイッチ110、エラー解除スイッチ223、税率設定スイッチ226、及び貸出料金設定スイッチ227からの入力を受ける。

## 【0099】

エラー解除スイッチ223は、払出制御装置210にエラーが発生した場合に、遊技店の店員等が発生したエラーの原因を解消した際に、遊技店の店員等によって操作され、工

50

ラー状態を解除するためのスイッチである。

【0100】

税率設定スイッチ226は、遊技球の貸し出しに対して課税される間接税の税率を設定するスイッチである。貸出料金設定スイッチ227は、貸し出される遊技球の有価価値を設定するためのスイッチである。

【0101】

また、CPU212は、入出力I/F216を介して、払出モータ220、発射制御装置221、エラーナンバー表示器222、税率表示器224及び貸出料金表示器225に指令信号を送信する。また、CPU212は、入出力I/F216を介して遊技制御装置100から送信された各種信号を受信する。

10

【0102】

払出モータ220は、実際に払出装置で遊技球を払い出すために駆動されるモータである。具体的には、払出モータ220は、1個の遊技球を貯留可能な凹部を所定個数有するスプロケットを回転させることによって、遊技球を払い出す。

【0103】

発射制御装置221は、遊技球を遊技盤5に発射するための発射装置を制御する。エラーナンバー表示器222は、払出制御装置210の裏面側に配設され、払出制御装置210で発生したエラーの種類を特定可能に表示する。

【0104】

税率表示器224は、払出制御装置210の裏面側に配設され、税率設定スイッチ226によって設定された間接税の税率を表示する。貸出料金表示器225は、払出制御装置210の裏面側に配設され、貸出料金設定スイッチ227によって設定された貸し出される遊技球の有価価値を表示する。

20

【0105】

電源装置160は、バックアップ電源161、RAMクリアスイッチ162を備える。遊技制御装置100、演出制御装置150、及び払出制御装置210は、電源装置160に接続される。

【0106】

バックアップ電源161は、停電時においても、遊技制御装置100、演出制御装置150、及び払出制御装置210に電源を供給する。なお、演出制御装置150には必ずしも電源を供給しなくてもよく、停電復帰後、遊技制御装置100からコマンドを送信するようにしてもよい。

30

【0107】

RAMクリアスイッチ162は、遊技制御装置100に備わるRAM104及び払出制御装置210に備わるRAM214に記憶されている情報を初期化するスイッチである。

【0108】

また、遊技機1に備わる球貸ボタン26が操作されると、カードユニット70は、プリペイドカード又は会員カード等のカードに記憶されている有価価値から貸し出される遊技球分の有価価値を減算して、減算した有価価値の値を遊技機1の残高表示部28に表示する。また、遊技機1に備わる排出ボタン27が操作されると、カードユニット70は、カード挿入口71に挿入されたカードを排出する。

40

【0109】

遊技制御装置100に備わる遊技用マイコン101と払出制御装置210に備わる遊技用マイコン211とは、暗号化された暗号化信号（暗号化データ）を双方向通信可能に接続される。また、暗号化されない非暗号化信号（平文データ）については、遊技制御装置100に備わる遊技用マイコン101から払出制御装置210に備わる遊技用マイコン211に単方向通信が可能に接続される。

【0110】

また、遊技制御装置100に備わる遊技用マイコン101と演出制御装置150に備わる遊技用マイコン151とは、暗号化されない非暗号化信号（平文データ）を遊技制御装

50

置 100 から演出制御装置 150 への単方向で通信可能に接続される。

**【0111】**

なお、遊技制御装置 100 に備わる遊技用マイコン 101、演出制御装置 150 に備わる遊技用マイコン 151 及び払出制御装置 210 に備わる遊技用マイコン 211 は、これらの接続に必要なポートを備えている。

**【0112】**

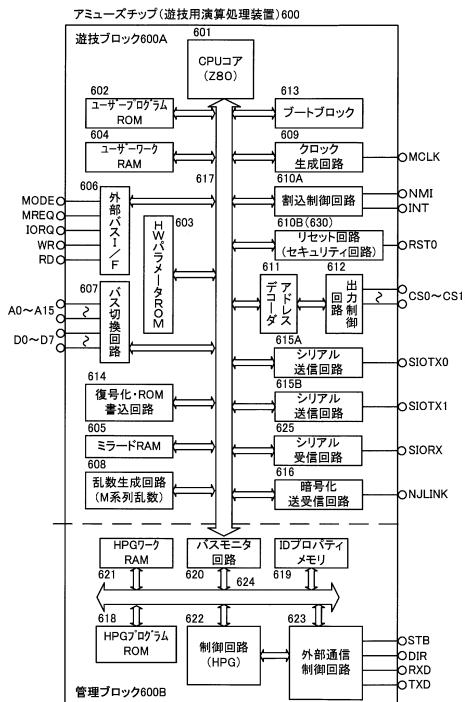

次に、遊技制御装置 100 に備わる遊技用マイコン 101、演出制御装置 150 に備わる遊技用マイコン 151 及び払出制御装置 210 に備わる遊技用マイコン 211（以下、総称して遊技用演算処理装置 600 という）について、図 5 を用いて詳細に説明する。

**【0113】**

図 5 は、本発明の第 1 の実施の形態の遊技用演算処理装置（アミューズチップ）600 のブロック図である。

**【0114】**

遊技用演算処理装置 600 はいわゆるアミューズチップ用の IC として製造され、遊技制御を行う遊技領域部 600A と情報管理を行う情報領域部 600B とに区分される。

**【0115】**

まず、遊技領域部 600A は CPU コア 601、ユーザプログラム ROM 602、HW パラメータ ROM 603、ユーザワーク RAM 604、ミラード RAM 605、外部バスインターフェース（I/F）606、バス切替回路 607、乱数生成回路 608、クロック生成回路 609、割込制御回路 610A、リセット回路 610B、アドレスデコーダ 611、出力制御回路 612、ポートブロック 613、復号化・ROM 書回路 614、シリアル送信回路 615A、シリアル送信回路 615B、シリアル受信回路 625、暗号化送受信回路 616、及びバス 617 によって構成される。なお、シリアル送信回路 615A 及びシリアル送信回路 615B を総称して、シリアル送信回路 615 という。

**【0116】**

CPU コア 601 は、図 4 の CPU 102、CPU 152 又は CPU 212 に相当する。ユーザプログラム ROM 602 は、図 4 の ROM 103、ROM 153 又は ROM 213 に相当する。また、ユーザプログラム ROM 602 及び HW パラメータ ROM 603 を総称して、ROM（不揮発性記憶手段）という。

**【0117】**

ユーザワーク RAM 604 は、図 4 の RAM 104、RAM 154 又は RAM 214 に相当する。また、ユーザワーク RAM 604 及びミラード RAM 605 を総称して、RAM（揮発性記憶手段）という。

**【0118】**

CPU コア 601 は、遊技制御のための演算処理を行う演算処理手段として機能する。ユーザプログラム ROM 602 は、制御プログラムを格納する。制御プログラムは、遊技用演算処理装置 600 が遊技制御装置 100 に備わる遊技用マイコン 101 である場合には、遊技の制御を行うための遊技制御プログラムである。また、遊技用演算処理装置 600 が払出制御装置 210 に備わる遊技用マイコン 211 である場合には、遊技球の払い出しを行うための払出制御プログラムである。さらに、遊技用演算処理装置 600 が演出制御装置 150 に備わる遊技用マイコン 151 である場合には、演出の制御を行うための演出制御プログラムである。

**【0119】**

HW パラメータ ROM 603 は、正当性確認情報を格納する。正当性確認情報とは、遊技用演算処理装置 600 の正当性の簡易チェックを行う場合の情報であり、例えば、遊技機 1 の一意な識別子を示す固有 ID、メーカーコード（遊技機 1 の製造メーカー毎に割り振られた固有の製造メーカーの一意な識別子）、遊技機 1 のランク（1 種、2 種等）を示すランクコード、製造メーカーが遊技機 1 の種類に設定する機種コード、検査番号を示す検査コード、電源投入時に RAM をバックアップするか否かを示す RAM バックアップコード、税率設定スイッチ 226 によって設定された税率、貸出料金設定スイッチ 227 によって設

10

20

30

40

50

定された貸出料金等である。また、HWパラメータROM603には、最初に貸出情報要求を送信した検査装置の一意な識別子である固有IDが一つのみ記憶される。

#### 【0120】

第三者機関又は遊技機1の製造メーカーがユーザプログラムROM602にプログラムを書き込む際に、正当性確認情報がHWパラメータROM603に書き込まれる。遊技用演算処理装置600は、電源立ち上がり時に、ユーザプログラムROM602に書き込まれたプログラムが正当であるか否かについて簡易チェックを行うことができる。具体的には、遊技用演算処理装置600の電源立ち上がり時に、遊技用演算処理装置600自身が演算した演算値と、正当性確認情報（すなわち、第三者機関等によって予め設定された結果値）とを比較判定することで、簡易的な遊技用演算処理装置600のチェックを行うことが可能になっている。10

#### 【0121】

ユーザワークRAM604は、遊技領域部600Aにおけるプログラムに基づく処理を実行する際にワークエリア（作業領域）として用いられるものである。このユーザワークRAM604には、バックアップ電源161（図4）からのバックアップ電源が供給されているので、遊技機1への電源供給が途絶えても、記憶データが保持されるように構成されている。ミラードRAM605は、クロックの立ち下がり時にユーザワークエリアに記憶された情報を複製し、複製した情報を記憶する（CPUコアがZ80の場合には、クロックの立ち上がり時に処理を実行するため、同期して動くことがないようにしている）。20

#### 【0122】

外部バスインターフェース606は、メモリリクエスト信号MR EQ、入出力リクエスト信号IORQ、メモリ書き込み信号WR、メモリ読み出し信号RD及びモード信号MODEなどのインターフェースであり、また、バス切替回路607は、16ビットのアドレス信号A0～A15や8ビットのデータ信号D0～D7のインターフェースである。20

#### 【0123】

例えば、MODE信号をハイレベルにした状態で、アドレス信号A0～A15を順次にインクリメントしながら、データ信号D0～D7を加えると、ユーザプログラムROM602への書き込みモードとなって遊技機1の製造メーカー又は第三者機関によるプログラムの書き込みが可能になる。なお、書き込みモードはプログラムの書き込みを可能にするものであり、ブートブロック613に記憶されるブートプログラムを書き込みできるようにするものではない。30

#### 【0124】

また、ユーザプログラムROM602へのプログラムの書き込みが終了すると、HWパラメータROM603の所定領域に書込終了コードが記録（例えば、所定のコード若しくは所定ビットを物理的に切断することで記録）されるようになっており、HWパラメータROM603に書込終了コードが記録されている場合には、ユーザプログラムROM602への新たなプログラムの書き込みができないようになっている。

#### 【0125】

乱数生成回路608は遊技の実行過程において遊技価値（例えば、大当たり）を付加するか否か等に係わる乱数（乱数は、大当たりの決定や停止時の図柄の決定等に使用）を生成するもので、一様性乱数を生成する数学的手法（例えば、合同法又はM系列法等）を利用している。なお、遊技用演算処理装置600が払出制御装置210に備わる遊技用マイコン211である場合には、乱数生成回路608は必要ない。40

#### 【0126】

クロック生成回路609は、遊技用演算処理装置600の外部から入力されたシステムクロック信号を分周して、遊技制御に必要な各種の周期的な信号を生成する。具体的には、CPUコア102を動作させるためのクロック信号、乱数生成回路608の乱数カウンタ値を更新するためのクロック信号、及びシリアル送受信を行う際のタイミング信号などを生成する。なお、クロック生成回路609は、CTC（Counter Timer Circuit）の機能を有しており、CPUコア102にて所定期間（例えば、4ミリ秒）のタイマ割込処理50

を行わせるためのタイマ割込信号も生成している。

**【0127】**

割込制御回路 610A は、所定の割り込み条件の成立に基づいて、割り込みの発生を C P U コア 102 に知らせる。なお、所定の割り込み条件は、遊技用演算処理装置 600 の外部から割込要求信号 (INT 信号、NMI 信号) が入力された場合や、クロック生成回路 609 の CTC からタイマ割込信号が出力された場合などが相当する。

**【0128】**

C P U コア 102 は、INT 信号や NMI 信号が入力された場合には、現在実行中の処理を中断して予め定められた割込処理を実行する。なお、INT 信号による割込 (マスカブル割込) は、プログラムの設定により禁止できるが、NMI 信号による割込 (ノンマスカブル割込) はプログラムの設定により禁止できない。また、C P U コア 102 は、タイマ割込信号が出力された場合には、図 29 に示すタイマ割込処理を実行する。10

**【0129】**

また、リセット回路 610B は、外部から入力されたリセット信号 (RST0 端子からの信号 RST0) を検出すると、遊技用演算処理装置 600 の内部に備えられた各回路と C P U コア 102 にリセット信号を伝達する。

**【0130】**

なお、リセット回路 610B は、セキュリティ回路 630 (図 11 参照) としても機能する。このセキュリティ回路 630 は、遊技用演算処理装置 600 の内部に備えられた各回路に対して異常なアクセスが発生したことを検出する機能を有しており、異常を検出すると C P U コア 102 にリセット信号を伝達する。20

**【0131】**

アドレスデコーダ 611 は、内蔵デバイス及び内蔵コントロール / ステータスレジスタ群のロケーションをメモリマップド I/O 方式及び I/O マップド I/O 方式によりデコードする。

**【0132】**

出力制御回路 612 は、アドレスデコーダ 611 からの信号制御を行って外部端子より 8 ビットのチップセレクト信号 (CS0 ~ CS7) を外部に出力するとともに、遊技用演算処理装置 600 の内部に備えた回路を選択するチップセレクト信号を発生する機能を有する。ブートブロック 613 は、ブートプログラムを記憶し、電源投入時に遊技用演算処理装置 600 の初期化に係わる処理を行う。30

**【0133】**

復号化・ROM 書込回路 614 は、ユーザプログラム ROM602 及び HW パラメータ ROM603 への書き込みモードの際に使用されるもので、モード信号 MODE が [H] レベルになっている間、バス切替回路 607 を介してアドレス信号 A0 ~ A15 やデータ信号 D0 ~ D7 を取り込み、そのデータ信号 D0 ~ D7 に含まれる情報 (暗号化されたプログラム及び暗号化された変更後の固有 ID) を復号化処理した後、バス 617 を介してユーザプログラム ROM602 及び HW パラメータ ROM603 に出力する (書き込む)。

**【0134】**

シリアル送信回路 615A 及びシリアル送信回路 615B は、暗号化されていない平文データを送信するための回路である。シリアル送信回路 615A は、SIOTX0 端子を介して演出制御装置 150 に接続される。また、シリアル送信回路 615B は、SIOTX1 端子を介して払出制御装置 210 に接続される。シリアル受信回路 625 は、暗号化されていない平文データを、SIORX 端子を介して受信するための回路である。40

**【0135】**

暗号化送受信回路 616 は、NJLINK 端子を介して暗号化された暗号化データを送受信する回路である。例えば、遊技制御装置 100 から払出制御装置 210 にデータを送信する場合に使用される、また、遊技制御装置 100 と払出制御装置 210 との間は、NJLINK 接続で接続され、暗号化送受信回路 616 には、NJLINK 信号線が接続される。暗号化送受信回路 616 は、NJLINK 信号線を介してデータを送受信する。50

**【 0 1 3 6 】**

バス 617 はデータバス（図 11 のデータバス 660）、アドレスバス（図 11 のアドレスバス 650）及び制御バスを含むものであり、情報領域部 600B まで延びている。

**【 0 1 3 7 】**

次に、遊技用演算処理装置 600 における情報管理を行う情報領域部 600B は、HPG プログラム ROM 618、ID プロパティメモリ 619、バスモニタ回路 620、HPG ワーク RAM 621、制御回路 622、外部通信制御回路 623、バス 624、及び遊技領域部 600A から延びるバス 617 の一部を含んで構成される。

**【 0 1 3 8 】**

HPG プログラム ROM 618 には、各種検査動作を行う HPG プログラムが格納される。10

**【 0 1 3 9 】**

ID プロパティメモリ 619 には、図示しない検査装置から外部通信制御回路 623 を介して受信した要求に基づいて、HW パラメータ ROM 603 に記憶されている情報を図示しない検査装置にすぐに出力できるように、遊技用演算処理装置 600 の電源投入時（システムリセット時）に HW パラメータに記憶されている情報を複製して記憶する。なお、ID プロパティメモリ 619 は、遊技領域部 600A 側及び情報領域部 600B 側の双方よりアクセスが可能な構成になっている。

**【 0 1 4 0 】**

バスモニタ回路 620 は、情報領域部 600B 側より遊技領域部 600A 側のバス 617 の状態監視及び制御を行う。ここでの制御とは、HW パラメータ ROM 603 の内容を ID プロパティメモリ 619 に複写する際のタイミング制御や、ユーザプログラム ROM 602 に格納されたプログラムを外部に出力する際（遊技領域部 600A 側のバス 617 を開放してユーザプログラム ROM 602 からプログラムを読み込んで情報領域部 600B 側より外部に出力する際）のタイミング制御である。なお、プログラムは、外部通信制御回路 623 で暗号化されてから出力される。20

**【 0 1 4 1 】**

HPG ワーク RAM 621 は、情報領域部 600B におけるプログラムに基づく処理を実行する際にワークエリア（作業領域）として用いられるものである。

**【 0 1 4 2 】**

制御回路 622 は情報領域部 600B 側を制御するもので、バッファメモリを有している。制御回路 622 は、例えば、バスモニタ回路 620 を介して CPU コア 102 の動作を監視し、非動作中に遊技領域部 600A のユーザワーク RAM 604 に記憶された内容をミラード RAM 605 へコピーする。また、図示しない検査装置からの要求に応答して情報領域部 600B の ID プロパティメモリ 619 の内容を外部へ転送したり、プログラム要求に応答してバスモニタ回路 620 を介してユーザプログラム ROM 602 内のプログラムを外部へ転送したりする。制御回路 622 のメモリは、転送時のタイミング調節のために用いられる。30

**【 0 1 4 3 】**

外部通信制御回路 623 は図示しない検査装置との通信を行うもので、例えば、外部からの指令に基づいて遊技用演算処理装置 600 内に格納されている情報（例えば、固有 ID、プログラム、実払込数等）を暗号化した後、外部へ転送する等の処理を行う。40

**【 0 1 4 4 】**

遊技用演算処理装置 600 では、遊技領域部 600A と情報領域部 600B がバスモニタ回路 620 を介して独立して動作する。すなわち、情報領域部 600B 側は遊技領域部 600A における CPU コア 102 の作動に關係なく（プログラム実行に關係なく）動作可能である。

**【 0 1 4 5 】**

なお、図 5 では図示されていないが、遊技用演算処理装置 600 には、図 11 にて後述する RAM アクセス規制回路（更新規制手段）640 を備えている。50

**【 0 1 4 6 】**

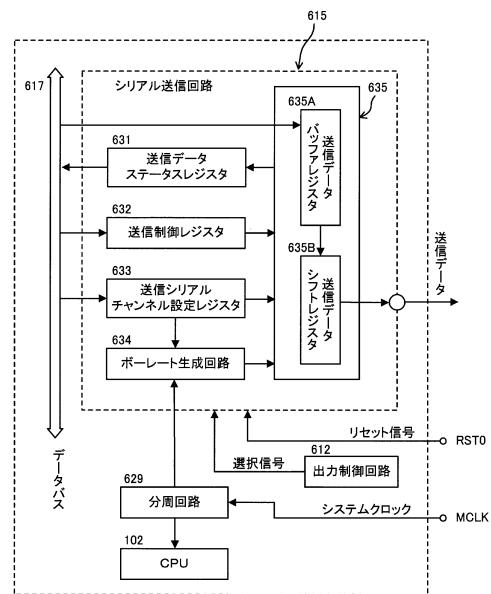

図6は、本発明の第1の実施の形態の遊技制御装置100におけるシリアル送信回路615の構成例を示すプロック図である。

**【 0 1 4 7 】**

シリアル送信回路615は、送信シリアルチャンネル設定レジスタ633、送信データステータスレジスタ631、送信制御レジスタ632、送信データレジスタ635（送信データバッファレジスタ635A、送信データシフトレジスタ635B）、ボーレート生成回路（送信速度設定手段）634を含んで構成される。

**【 0 1 4 8 】**

シリアル送信回路615は、出力制御回路612から入力された選択信号に基づいて、

送信先を選択する。また、リセット信号の入力を受け付けると、各種レジスタに設定された値を0クリアする。

10

**【 0 1 4 9 】**

送信シリアルチャンネル設定レジスタ633は、データ送信時の通信速度及び通信フォーマットを指定するレジスタである。送信シリアルチャンネル設定レジスタ633には、後述するメイン処理におけるシリアル通信設定処理によって各値が設定される。

**【 0 1 5 0 】**

図7は、本発明の第1の実施の形態の送信シリアルチャンネル設定レジスタ633の構成例を示す図である。図7に示すように、送信シリアルチャンネル設定レジスタ633は、16ビットで構成されており、ビット0～15はすべて書き込み／読み出し可能とされる。

20

**【 0 1 5 1 】**

送信シリアルチャンネル設定レジスタ633において、ビット0～12には、送信ボーレート（通信速度）を算出するためのボーレート設定値（例えば、分周比）が設定される。

。

**【 0 1 5 2 】**

具体的には、遊技用演算処理装置600に入力されるシステムクロック（MCLK）の周波数（単位Hz：ヘルツ）を32で除した値を、さらに、このボーレート設定値で除した値が、送信ボーレート（1秒間に送信されるデータのビット数）として設定される。例えば、ボーレート設定値として100を設定すると、システムクロックの周波数が20MHzであった場合には、送信ボーレートは、 $20,000,000 \div 32 \div 100 = 6250$ （bps）となる。

30

**【 0 1 5 3 】**

ビット13には、送信データ長を8ビットとする場合に“0”が設定され、9ビットとする場合に“1”が設定される。

**【 0 1 5 4 】**

ビット14には、送信データにパリティを付加しない場合に“0”が設定され、パリティを付加する場合に“1”が設定される。ビット15には、送信データに付加するパリティを偶数パリティとする場合に“0”が設定され、奇数パリティとする場合に“1”が設定される。なお、ビット15は、ビット14に“1”（パリティ有り）が設定されている場合に有効となる。

40

**【 0 1 5 5 】**

なお、遊技用演算処理装置600にリセット信号（RST0）が入力されると、シリアル送信回路615がリセットされ、送信シリアルチャンネル設定レジスタ633の全ビットが“0”に設定される（図6等も参照）。

**【 0 1 5 6 】**

図6の説明に戻り、送信制御レジスタ632は、シリアル送信回路615の動作を制御するためのレジスタである。

**【 0 1 5 7 】**

図8は、本発明の第1の実施の形態の送信制御レジスタ632の構成例を示す図である

50

。図8に示すように、送信制御レジスタ632は、例えば8ビットで構成され、ビット6は読み出し専用とされ、他のビット0、4、5、7は書き込み／読み出し可能とされる。なお、本実施形態では送信制御レジスタ632のビット1～3は未使用としているため、図8では記載を省略している。

#### 【0158】

送信制御レジスタ632のビット0には、送信回路（シリアル送信回路615）を初期化する場合に“1”が設定される。送信回路が初期化されると送信データレジスタ635のデータも含めて全てのレジスタが初期値とされる。

#### 【0159】

ビット4には、送信データレジスタ635（送信データシフトレジスタ635B）からのデータ送信を禁止する場合に“0”が設定され、データ送信を許可する場合に“1”が設定される。

#### 【0160】

ビット5には、送信データレジスタ635が空になったときに送信割り込みを要求しない場合に“0”が設定され、送信割り込みを要求する場合に“1”が設定される。

#### 【0161】

ビット6には、送信割り込み要求が発生しているか否か（送信割り込み状態）を示す値が設定される。ビット6に“0”が設定されている場合には送信割り込みを要求していない状態であることを示し、“1”が設定されている場合には送信割り込みを要求している状態であることを示す。

#### 【0162】

ビット7には、送信データレジスタのビット8の値（データ長が9ビットの場合）が設定される。

#### 【0163】

なお、遊技用演算処理装置600にリセット信号（RST0）が入力されると、シリアル送信回路615がリセットされ、送信制御レジスタ632の全ビットが“0”に設定される（図6等も参照）。その結果、送信制御レジスタ632のビット4が“0”になるので、送信データレジスタ635（送信データシフトレジスタ635B）からのデータ送信が禁止され、データ出力がオフされた状態になる。

#### 【0164】

図6の説明に戻り、送信データステータスレジスタ631は、送信データレジスタ635の状態を示すレジスタである。CPU102は、送信データステータスレジスタ631の設定値によって、送信データレジスタ635の状態を確認することができる。

#### 【0165】

図9は、本発明の第1の実施の形態の送信データステータスレジスタ631の構成例を示す図である。送信データステータスレジスタ631は、例えば8ビットで構成され、ビット0～5、7はすべて読み出し専用とされる。なお、本実施形態では送信データステータスレジスタ631のビット6は未使用としているため、図9では省略している。

#### 【0166】

送信データステータスレジスタ631において、ビット0～5には、送信データの残量を示す値が設定される。例えば、ビット0～5に“00h”（16進数の“0”）が設定されると送信データがないことを示し、“01h”が設定されると送信データが1バイト残っていることを示し、“20h”が設定されると送信データが32バイト残っていることを示す。

#### 【0167】

ビット7には、送信データレジスタ635におけるデータの送信状態を示す値が設定される。ビット7に“1”が設定されているとデータを送信していない状態であることを示し、“0”が設定されているとデータを送信している状態であることを示す。

#### 【0168】

なお、遊技用演算処理装置600にリセット信号（RST0）が入力されると、シリアル

10

20

30

40

50

ル送信回路 615 がリセットされ、送信データステータスレジスタ 631 の全ビットが “0” に設定される（図 6 等も参照）。その結果、送信データステータスレジスタ 631 のビット 0 ~ 5 が “00h” となり、送信データの残量がない状態となる。

#### 【0169】

図 6 の説明に戻り、送信データレジスタ 635 は、シリアル送信回路 615 が送信するデータを格納するレジスタである。送信データレジスタ 635 は、例えば、1 段の送信データシフトレジスタ 635B と、31 段の送信データバッファレジスタ 635A で構成される。

#### 【0170】

図 10 は、本発明の第 1 の実施の形態の送信データレジスタ 635（1 段分）の構成例を示す図である。1 段の送信データレジスタ 635 は、例えば 8 ビットで構成され、ビット 0 ~ 7 はすべて書き込み専用とされる。10

#### 【0171】

この送信データレジスタ 635 には、タイマ割り込み処理で生成される制御指令データが格納され、送信制御レジスタのビット 4 に “1”（送信許可）が設定されていれば、格納された制御指令データは自動的に演出制御装置 150 に送信される。

#### 【0172】

制御指令データは、例えば、1 バイトのモードデータと 1 バイトのアクションデータの 2 バイトで構成されるので、2 段の送信データレジスタ 635 に 1 つの制御指令データが格納されることとなる。そして、本実施形態では、送信データレジスタ 635 を 32 段で構成しているので、1 回のタイマ割り込み処理で最大 16 の制御指令データが生成される場合、これをすべて送信データレジスタ 635 に格納することができる。20

#### 【0173】

ただし、CPU102 によって、新たな送信データを送信データレジスタ 635 に格納できるのは、送信データステータスレジスタ 631 のビット 0 ~ 5 の値（送信データの残量を示す値）が “00h” ~ “1Fh” の場合（送信データレジスタ 635 に、0 ~ 31 バイトの未送信データが残っている場合）に限られる。

#### 【0174】

送信データステータスレジスタ 631 のビット 0 ~ 5 の値が “20h” の場合は、送信データレジスタ 635 に空きがないので、CPU102 によって送信データレジスタ 635 に書き込もうとされたデータは廃棄される。これにより、送信データレジスタ 635 が満杯のときは、誤って CPU102 によるデータ書き込みが発生しても、既に格納されている送信データレジスタ 635 のデータが破壊されないようになっている。30

#### 【0175】

なお、遊技用演算処理装置 600 にリセット信号（RST0）が入力されると、シリアル送信回路 615 がリセットされ、送信データレジスタ 635 の全ビットが “0” に設定される（図 6 等も参照）。

#### 【0176】

図 6 の説明に戻り、ボーレート生成回路 634 は、クロック生成回路 609 から分周回路 629 を介して出力されるクロック信号（遊技用演算処理装置 600 に入力されるシステムクロック（MCLK）を分周した信号）及び送信シリアルチャンネル設定レジスタ 633 に設定されている設定値（ボーレート設定値）に基づいて、シリアル送信回路 615 が用いる送信ボーレートを生成する。このとき、ボーレート生成回路 634 は、クロック信号及びボーレート設定値に基づいて、前述の計算式を用いて送信ボーレートを求める。また、分周回路 629 は、CPU102 にも分周されたクロック信号を入力する。なお、分周回路 629 は、クロック生成回路 609 に含まれるように構成してもよい。40

#### 【0177】

シリアル送信回路 615 では、送信許可の設定（送信制御レジスタ 632 のビット 4 を “1”）がなされた後、送信するデータを送信データレジスタ 635（送信データバッファレジスタ 635A）に書き込む、又は、送信するデータを送信データレジスタ 635 に50

書き込んだ後、送信許可の設定がなされると、自動的に送信が開始される。送信が開始されると、送信データバッファレジスタ 635A のデータが送信データシフトレジスタ 635B に転送され、送信データシフトレジスタ 635B からシリアル変換されて、最下位ビット（ビット 0）から 1 ビットずつ順次出力される。そして、データの送信が完了すると送信データシフトレジスタ 635B は空になるので、送信データバッファレジスタ 635A に書き込まれている次のデータが送信データシフトレジスタ 635B に転送され、出力される。

#### 【 0178 】

したがって、シリアル送信回路 615 では、送信データレジスタ 635（送信データシフトレジスタ 635B、送信データバッファレジスタ 635A）に書き込まれたデータ（制御指令データ）が、演出制御装置 150 に 1 ビットずつ順次送信されることとなる。10

#### 【 0179 】

このように、シリアル送信回路（制御指令送信手段）615 は、送信データ（例えば、制御指令データ）を格納する送信データレジスタ 635 を備え、送信データレジスタ 635 に送信データが格納されると、遊技制御装置 100 から演出制御装置 150 へ向かう方向に、格納された送信データを 1 ビットずつ順次送信する（いわゆるシリアル通信）よう構成されている。

#### 【 0180 】

具体的には、送信データレジスタ 635 は、格納されたデータをすぐに送信する送信データシフトレジスタ 635B と、格納されたデータを保持するとともに、送信データシフトレジスタ 635B がデータを格納可能な状態（データの送信が完了した状態）となったときに、保持しているデータを送信データシフトレジスタ 635B に転送する送信データバッファレジスタ 635A と、で構成される。20

#### 【 0181 】

これにより、従来のパラレル通信では必須とされていたタイマ割り込み処理における制御指令データの送信処理を省略できるので、CPU102 の負担を軽減することができる。。

#### 【 0182 】

また、シリアル通信とすることで、制御指令データを送信するための配線本数を比較的少なくすることができる。30

#### 【 0183 】

また、遊技制御装置 100 と演出制御装置 150 との間の通信は、遊技制御装置 100 から演出制御装置 150 へのみデータを送信可能な单方向通信とされ、遊技制御装置 100 にデータは入力されないので、不正が行われることを防止できる。

#### 【 0184 】

なお、本実施形態においては、送信データレジスタ 635 に最大で 32 バイトの送信データが格納可能であるが、この 32 バイトのデータが、1 回のタイマ割り込み処理において全て出力できるように、ボーレート設定値（送信シリアルチャンネル設定レジスタ 633 のビット 0 ~ 12）の値が設定されている。

#### 【 0185 】

具体的には、送信データレジスタ 635 から出力される 1 バイトあたりのデータ送信に必要な時間 T<sub>b</sub> と、タイマ割込信号の発生周期 F と、送信データレジスタ 635 に格納できるデータの上限バイト数 B との関係が、F / B > T<sub>b</sub> となるように、ボーレート設定値を設定して送信の速度を決めればよい。40

#### 【 0186 】

例えば、タイマ割込信号の発生周期 F = 4 ミリ秒で、送信データレジスタ 635 に格納できるデータの上限バイト数 B = 32 バイトであれば、F / B = 4000 / 32 = 125 マイクロ秒よりも短くなるように T<sub>b</sub> の値を決定し、遊技用演算処理装置 600 に入力されるシステムクロック（MCLK）の周波数を考慮したうえで、ボーレート設定値の値を定めればよい。50

**【0187】**

このような構成とすることで、シリアル送信回路（制御指令送信手段、送信手段）615は、1回のタイマ割り込み処理において生成される一連の制御指令データをすべて格納することができるとなり、タイマ割り込み毎に生成される制御指令データを確実に送信することができる。

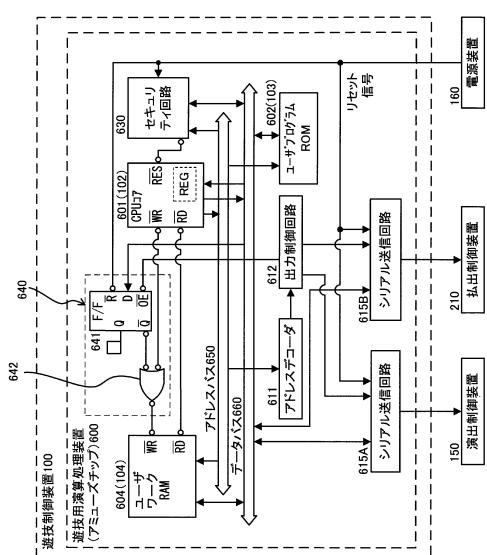

**【0188】**

図11は、本発明の第1の実施の形態の遊技制御装置100に備わる遊技用演算処理装置（アミューズチップ）600とその周辺のブロック図である。

**【0189】**

遊技用演算処理装置600は、セキュリティ回路630、CPUコア102（図11では601）、RAMアクセス規制回路640、ユーザワークRAM104（図11では604）、アドレスデコーダ611、出力制御回路612、及び、ユーザプログラムROM103（図11では602）を備える。

10

**【0190】**

なお、遊技用演算処理装置600に備わるこれらの回路等は、アドレスバス650及びデータバス660を介して接続されている。アドレスバス650は、A0～A15の16ビットの信号線によって構成され、データバス660は、D0～D7の8ビットの信号線によって構成される。

**【0191】**

また、遊技制御装置100は、演出制御装置150に接続されるシリアル送信回路615A、及び、払出制御装置210に接続されるシリアル送信回路615Bを備える。

20

**【0192】**

なお、演出制御装置150及び払出制御装置210には、シリアル受信回路625（図5）に相当する受信回路が備えられていて、シリアル送信回路615A、615Bから出力されたシリアルのデータを、それぞれが受信する構成となっている。

**【0193】**

遊技用演算処理装置600に電源が投入される際には、RST0端子（図5）を介して電源装置160からリセット信号（起動信号）が入力され、リセット回路610B（図5）が作動する。

**【0194】**

セキュリティ回路630は、このリセット信号が入力されるとHWパラメータROM603に記憶された正当性確認情報を用いて、セキュリティチェック処理を実行する。このセキュリティチェック処理は、ユーザプログラムROM103に記憶されたプログラムの正当性の判定を行う処理である。

30

**【0195】**

セキュリティ回路630は、このセキュリティチェック処理を実行している間は、CPUコア102のリセット端子（RES0（負論理））にリセット信号を継続して出力することで、CPUコア102の起動を待機させる。

**【0196】**

CPUコア102は、前述のリセット端子（RES0（負論理））と、書き指令出力端子（WR（負論理））、及び読み出指令出力端子（RD（負論理））を備える。リセット端子はセキュリティ回路630に接続されており、遊技用演算処理装置600にリセット信号が入力されると、前述のように、セキュリティチェック処理を実行している間、CPUコア102に対するリセット信号がリセット端子に入力される。

40

**【0197】**

CPUコア102のリセット端子にリセット信号が入力されると、CPUコア102は、CPUコア102に備わるレジスタ（REG）を初期化する。

**【0198】**

また、CPUコア102がユーザワークRAM104にデータの書き込みを指令する書き指令を出力する場合には、CPUコア102の書き指令出力端子からは所定値よりも低

50

い電圧のローレベルの信号が出力される。同様に、C P Uコア102がユーザワークRAM104からデータの読み出しを指令する読出指令を出力する場合には、C P Uコア102の読出指令出力端子からは所定値よりも低い電圧のローレベルの信号が出力される。

#### 【0199】

つまり、書込指令出力端子及び読出指令出力端子は、通常電圧がハイレベルに維持されており、ユーザワークRAM104への読み書きを行うときにのみ電圧がローレベルになる。

#### 【0200】

また、C P Uコア102は、アドレスバス650に指定したアドレスを出力し、データバス660を介して指定したアドレスに格納されたデータを入出力する。

10

#### 【0201】

まず、ユーザワークRAM104のデータの読み出しについて説明する。

#### 【0202】

C P Uコア102から、ユーザワークRAM104の読出指令入力端子（R D（負論理））に読出指令が入力されると、アドレスバス650及びデータバス660を介してC P Uコア102に読出データが出力される。

#### 【0203】

このとき、C P Uコア102からアドレスバス650へは、ユーザワークRAM104のアドレスが出力され、アドレスデコーダ611からユーザワークRAM104のチップ選択端子（所謂C S端子に相当、図示は略）に選択信号が入力されることによって、ユーザワークRAM104が選択される。次いで、選択されたユーザワークRAM104は、アドレスバス650が指定する記憶領域のデータをデータバス660へ出力する。次いで、C P Uコア102は、データバス660へ出力されたデータを内部へ取り込む。このような手順により、C P Uコア102はユーザワークRAM104からデータを読み出す。

20

#### 【0204】

次に、ユーザワークRAM104へのデータの書き込みについて説明する。

#### 【0205】

C P Uコア102に備わる書込指令出力端子は、RAMアクセス規制回路640のORゲート回路642に備わる二つの入力端子のうち一方の入力端子に接続される。ORゲート回路642の他方の入力端子は、RAMアクセス規制回路640のフリップフロップ回路641の出力端子（Q（負論理））に接続され、ORゲート回路642の出力端子は、ユーザワークRAM104の書込指令入力端子（W R（負論理））に接続されている。

30

#### 【0206】

また、ユーザワークRAM104の書込指令入力端子に所定値以下の電圧であるローレベルの信号が入力されると、ユーザワークRAM104への書き込みが許容される。

#### 【0207】

このため、ORゲート回路642の二つの入力端子にそれぞれローレベルの信号が入力されなければ、ユーザワークRAM104への書き込みが許容されない。言い換えれば、ORゲート回路642の少なくとも一方の入力端子にハイレベルの信号が入力されていると、ユーザワークRAM104への書き込みが規制（禁止）される。

40

#### 【0208】

ここで、RAMアクセス規制回路640のフリップフロップ回路641について説明する。

#### 【0209】

フリップフロップ回路641は、D型のフリップフロップ回路であり、入力端子として、データ端子（D）、リセット端子（R（負論理））、及び出力イネーブル端子（O E（負論理））を備えるとともに、出力端子（Q（正論理），Q（負論理））を備える。

#### 【0210】

データ端子には、データバス660を構成する信号線D0～D7のうち所定の一本の信号線（例えば、D0）が接続されている。

50

**【0211】**

リセット端子には電源装置 160 からリセット信号線が接続され、リセット信号が入力されるとリセット端子はローレベルとなる。このときフリップフロップ回路 641 は、出力端子 Q (正論理) からローレベルの信号を出力させ、出力端子 Q (負論理) からハイレベルの信号を出力させる。出力端子 Q (正論理) からの出力と、出力端子 Q (負論理) からの出力は、相互に反転するレベルとなっている。

**【0212】**

また、出力イネーブル端子は、出力制御回路 612 から送信された出力イネーブル信号が入力される。出力イネーブル信号がハイレベルの場合には、出力端子から信号の出力が可能な状態となる。

10

**【0213】**

このフリップフロップ回路 641 に備えた出力端子 Q (負論理) からの信号レベルは、CPU コア 102 によって、自在に設定できるようになっている。この設定は、CPU コア 102 が、フリップフロップ回路 641 に割り当てられたアドレスの記憶領域に所定のデータを書き込むことで実現される。

**【0214】**

具体的には、CPU コア 102 によってフリップフロップ回路 641 に割り当てられたアドレスの記憶領域にデータを書き込む処理が行われると、CPU コア 102 からアドレスバス 650 へは、フリップフロップ回路 641 のアドレスが出力される。次に、アドレスデコーダ 611 から、出力制御回路 612 を介して、フリップフロップ回路 641 の出力イネーブル端子にクロック信号が入力され、出力イネーブル端子の電圧レベルが立ち上がり、ハイレベルとなる。

20

**【0215】**

このときフリップフロップ回路 641 は、データ端子に入力されている信号を取り込んで、取り込んだ信号を出力端子 Q (正論理) から出力し、取り込んだ信号の反転値を出力端子 Q (負論理) から出力する。

**【0216】**

また、フリップフロップ回路 641 は、出力制御回路 612 がクロック信号の入力を終了した場合には、出力イネーブル端子の電圧レベルは立ち下がりローレベルとなり、出力端子 Q (正論理) 及び出力端子 Q (負論理) の電圧レベルを保持する。

30

**【0217】**

また、出力端子 Q (負論理) は、OR ゲート回路 642 の入力端子に信号を出力する。出力端子 Q (正論理) には何も接続されない。

**【0218】**

次に、フリップフロップ回路 641 の入力状態に応じた各種動作について説明する。

**【0219】**

フリップフロップ回路 641 は、前述したように、出力イネーブル端子の電圧レベルの立ち上り、つまり出力イネーブル信号の入力開始時に、データ端子の電圧レベルを読み取り、読み取った電圧レベルの反転値を出力端子 Q (負論理) から出力する。

40

**【0220】**

一方、フリップフロップ回路 641 は、出力イネーブル端子の電圧レベルの立ち下がり、つまり、出力イネーブル信号の入力終了時に、出力イネーブル端子の電源レベルの立ち上がり時の出力端子 Q (負論理) からの出力を保持する。

**【0221】**

出力端子 Q (負論理) からハイレベルの信号が OR ゲート回路 642 の入力端子に出力されていると、OR ゲート回路 642 の他方の入力端子にローレベル及びハイレベルのいずれの信号が入力されても、OR ゲート回路 642 の出力端子からはハイレベルの信号が出力される。

**【0222】**

このため、フリップフロップ回路 641 の出力端子 Q (負論理) からハイレベルの信号

50

が出力されていれば、ORゲート回路642の他方の入力端子に書き指令信号が入力されても（当該他方の入力端子にローレベルの信号が入力されても）、ユーザワークRAM104の書き指令入力端子にはローレベルが入力されなくなり、RAM書き禁止状態が発生する。

#### 【0223】

RAMアクセス規制回路640をRAM書き禁止状態にするかRAM書き許可状態にするかは、クロック信号がフリップフロップ回路641に入力されたときのフリップフロップ回路641のデータ端子に入力される電圧レベル、又はリセット信号の入力の有無に基づく。

#### 【0224】

前述のようにCPUコア102は、出力制御回路612を制御してクロック信号の出力を制御でき、データバス660の信号線の出力も制御できるので、フリップフロップ回路641の出力端子Q（負論理）から出力される信号は、CPUコア102によって制御可能である。言い換えると、CPUコア102は、データバス660の信号レベルを制御することによってRAMアクセス規制回路640の書き状態を制御できる。

#### 【0225】

さらに、前述のようにフリップフロップ回路641のリセット端子にリセット信号が入力された場合には、フリップフロップ回路641は、出力端子Qの電圧レベルをローにするため、出力端子Q（負論理）の電圧レベルはハイになる。このため、フリップフロップ回路641にリセット信号が入力された場合には、RAMアクセス規制回路640では、RAM書き禁止状態が発生することになる。

#### 【0226】

前述のように、出力制御回路612が払出制御装置210に接続されるシリアル送信回路615Bにクロック信号を入力すると、シリアル送信回路615Bは、クロック信号が入力されたタイミングで、データバス617からデータを読み取り、読み取ったデータを送信データバッファレジスタ635Aに格納する。そして、送信データバッファレジスタ635Aに格納されたデータを送信データシフトレジスタ635Bに格納し、払出制御装置210に順次出力する。

#### 【0227】

なお、前述したセキュリティ回路630、RAMアクセス規制回路640、及びシリアル送信回路615の起動（リセット）は、電源装置160からのリセット信号を、前述のリセット回路610B（図5）を介して受け入れた場合に実行される。ただし、電源装置160からのリセット信号は、必ずしもリセット回路610Bを介して各回路に入力される必要はなく、リセット回路610Bを経由しない別個の信号線を介して各回路に入力されるような構成でもよい。

#### 【0228】

なお、シリアル送信回路615（615A、615B）においては、図7～図10の説明で前述したように、リセット信号によって、演出制御装置150や払出制御装置210へのデータ出力がオフ状態となる。

#### 【0229】

また、払出制御装置210は、シリアル送信回路615を備えてはいない点が、図6に示した遊技制御装置100と異なっている。その他の構成は、図11に示した遊技制御装置100と同じ構成である。

#### 【0230】

また、演出制御装置150は、シリアル送信回路615を備えてはいない点、さらに、遊技用演算処理装置600にRAMアクセス規制回路640を備えていない点が、図6に示した遊技制御装置100と異なっている。その他の構成については、図11に示した遊技制御装置100と同じ構成である。

#### 【0231】

なお、払出制御装置210及び演出制御装置150に備えたシリアル受信回路625は

10

20

30

40

50

、払出制御装置 210（又は演出制御装置 150）のCPU102が起動した後であれば、遊技制御装置 100 のシリアル送信回路 615 からの信号を受け入れられる状態となっている。なお、払出制御装置 210（又は演出制御装置 150）のシリアル受信回路 625 と CPU102 とは、データバス 617 によって相互に接続される構成となっている。

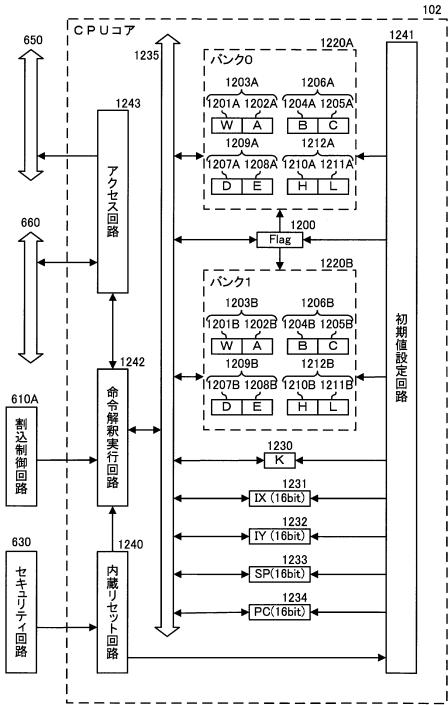

#### 【0232】

図 12 は、本発明の第 1 の実施の形態の CPU コア 102 の内部構成を説明するプロック図である。CPU コア 102 は Z80 系の CPU として構成されている。

#### 【0233】

図 12 に示す CPU コア 102 は、それぞれ 8 ビットの幅を有する、W レジスタ 1201A、A レジスタ 1202A、B レジスタ 1204A、C レジスタ 1205A、D レジスタ 1207A、E レジスタ 1208A、H レジスタ 1210A、L レジスタ 1211A を備えている。

#### 【0234】

これらの汎用レジスタは、W レジスタ 1201A と A レジスタ 1202A とを組み合わせて、16 ビットの幅を有する WA レジスタ 1203A として使用することも可能である。同様に、B レジスタ 1204A と C レジスタ 1205A とを組み合わせた BC レジスタ 1206A、D レジスタ 1207A と E レジスタ 1208A とを組み合わせた DE レジスタ 1209A、H レジスタ 1210A と L レジスタ 1211A とを組み合わせた HL レジスタ 1212A を使用することも可能である。

#### 【0235】

なお、これらの汎用レジスタは、1 つの汎用レジスタ群（バンク 0 のレジスタ群）1220A を形成している。一方、CPU コア 102 は、バンク 0 のレジスタ群 1220A に含まれる汎用レジスタと同様の構成を有する、もう 1 つの汎用レジスタ群（バンク 1 のレジスタ群）1220B を備えている。

#### 【0236】

このバンク 1 のレジスタ群 1220B には、バンク 0 の W レジスタ 1201A ~ L レジスタ 1211A と同一の機能を有する、W レジスタ 1201B ~ L レジスタ 1211B を備えている。これらのレジスタも、バンク 0 同様に、WA レジスタ 1203B ~ HL レジスタ 1212B として、16 ビットのレジスタとして使用することが可能である。

#### 【0237】

さらに、CPU コア 102 は、8 ビットの幅を有するフラグレジスタ 1200 を備えている。

#### 【0238】

フラグレジスタ 1200 は、図 13 で詳細を説明するが、レジスタを用いた演算結果が格納される。また、フラグレジスタ 1200 の、レジスタバンクセレクタ (RBS) 1301（図 13 で後述）によって、2 つの汎用レジスタ群 1220A、1220B のうちのいずれを、演算対象として用いるかが選択される。

#### 【0239】

レジスタバンクセレクタ (RBS) 1301 により選択されたレジスタ群に属する各レジスタは、後述の命令解釈実行回路 1242 によって演算に用いられる。一方、選択されていないレジスタ群に属する各レジスタは、レジスタバンクセレクタ (RBS) 1301 の値が変更されて選択対象となるまでは、値を保持する。

#### 【0240】

また、CPU コア 102 は、8 ビットの幅を有して、上位アドレス指定レジスタとして機能する K レジスタ 1230 を備えている。このレジスタは、後述の命令解釈実行回路 1242 が、所定の 16 ビットのアドレスに記憶されたデータにアクセスする際の上位 8 ビットのアドレスを指定する上位アドレス指定レジスタである。

#### 【0241】

さらに、CPU コア 102 は、それぞれ 16 ビットの幅を有する、IX レジスタ 1231、IY レジスタ 1232、スタックポインタとして機能する SP レジスタ 1233、及

10

20

30

40

50

びプログラムカウンタとして機能する P C レジスタ 1 2 3 4 を備えている。

【 0 2 4 2 】

I X レジスタ 1 2 3 1 、 I Y レジスタ 1 2 3 2 は、後述の命令解釈実行回路 1 2 4 2 がデータをアクセスする際のインデックスとして用いられる。スタックポインタ 1 2 3 3 は、スタックエリア（図 1 8 で後述）にデータを格納する（又はデータを取り出す）際の領域の位置を示す。プログラムカウンタ 1 2 3 4 は、後述の命令解釈実行回路 1 2 4 2 で実行されている命令が格納されているアドレスを示している。

【 0 2 4 3 】

命令解釈実行回路 1 2 4 2 は、遊技制御プログラムを実行して、C P U コア 1 0 2 内部の各レジスタを用いた演算処理を行う。具体的には、ユーザプログラム ROM 1 0 3 にて、プログラムカウンタ 1 2 3 4 に示されるアドレスに記憶されたデータを読み出すとともに、読み出したデータをコードと見なして、コードに対応する命令を実行する。

10

【 0 2 4 4 】

故に、本実施形態においては、C P U コア 1 0 2 自体を演算処理手段として例示しているが、C P U コア 1 0 2 の内部では、命令解釈実行回路 1 2 4 2 が主体となって演算処理手段の機能を果たしている。

【 0 2 4 5 】

なお、命令解釈実行回路 1 2 4 2 は、遊技制御プログラムの命令に対応して、アクセス回路 1 2 4 3 、アドレスバス 6 5 0 、及びデータバス 6 6 0 を介して、C P U コア 1 0 2 外部のユーザプログラム ROM 1 0 3 、ユーザワーク RAM 6 0 4 、及び他の回路との間で、データの授受を行う場合もある。

20

【 0 2 4 6 】

また、命令解釈実行回路 1 2 4 2 は、ユーザプログラム ROM 1 0 3 の命令を 1 つずつ実行する毎に、次の命令が格納されているアドレスをプログラムカウンタ 1 2 3 4 に格納する。このようにして命令の実行と、プログラムカウンタ 1 2 3 4 の更新を繰り返すことで、遊技制御プログラムが順次実行される。なお、割込制御回路 6 1 0 A からの割込信号を受け付けると、プログラムカウンタ 1 2 3 4 の値は、予め設定された割込処理のアドレスの値に切り替えられる。

【 0 2 4 7 】

この命令解釈実行回路 1 2 4 2 及び C P U コア 1 0 2 に備える各レジスタは、内部バス 1 2 3 5 によって、データが授受される。

30

【 0 2 4 8 】

初期値設定回路 1 2 4 1 は、C P U コア 1 0 2 に備える各レジスタに初期値をハード的に設定する回路である。

【 0 2 4 9 】

内蔵リセット回路 1 2 4 0 は、セキュリティ回路 6 3 0 からのリセット信号を受信すると、初期値設定回路 1 2 4 1 を起動させ、C P U コア 1 0 2 に備える各レジスタに初期値を設定させたのちに、命令解釈実行回路 1 2 4 2 を起動させる。

【 0 2 5 0 】

図 1 3 は、本発明の第 1 の実施の形態のフラグレジスタ 1 2 0 0 の構成を説明する図である。フラグレジスタ 1 2 0 0 の各ビットの値は、図 1 2 における命令解釈実行回路 1 2 4 2 によって設定される。

40

【 0 2 5 1 】

割込マスク許可フラグ ( I M F ) 1 3 0 0 は、割込信号による割込処理の許否を設定するフラグであり、セット（値が「 1 」）で許可、クリア（値が「 0 」）で禁止となる。

【 0 2 5 2 】

レジスタバンクセレクタ ( R B S ) 1 3 0 1 は、図 1 2 における命令解釈実行回路 1 2 4 2 が演算処理を行う際に、2 つの汎用レジスタ群 1 2 2 0 A 、 1 2 2 0 B のうちのいずれを用いるかを選択するフラグであり、セット（値が「 1 」）でバンク 1 のレジスタ群 1 2 2 0 B 、クリア（値が「 0 」）でバンク 0 のレジスタ群 1 2 2 0 A が選択される。

50

**【0253】**

オーバーフローフラグ (V F) 1302 は、所定の演算によって演算対象の汎用レジスタに桁溢れ (オーバーフロー) が発生するとセット (値が「1」) され、他の場合はクリア (値が「0」) される。

**【0254】**

サインフラグ (S F) 1303 は、所定の演算によって演算対象の汎用レジスタの最上位ビットが「1」になるとセット (値が「1」) され、他の場合はクリア (値が「0」) される。

**【0255】**

ハーフキャリーフラグ (H F) 1304 は、8ビット演算を行った結果として演算対象の汎用レジスタの4ビット目に桁上がり (キャリー) や桁借り (ボロー) が発生するとセット (値が「1」) され、他の場合はクリア (値が「0」) される。 10

**【0256】**

キャリーフラグ (C F) 1305 は、所定の演算によって桁上がり (キャリー) や桁借り (ボロー) が発生するとセット (値が「1」) され、他の場合はクリア (値が「0」) される。

**【0257】**

ゼロフラグ (Z F) 1306 は、所定の演算算結果が「0」となった場合にセット (値が「1」) され、他の場合はクリア (値が「0」) される。

**【0258】**

ジャンプステータスフラグ (J F) 1307 は、キャリーフラグ (C F) 1305 又はゼロフラグ (Z F) 1306 の少なくとも一方がセットされた場合にはセット (値が「1」) される。若しくは、演算処理を行わない場合であっても、汎用レジスタの値が「00H」の値になった場合は、セット (値が「1」) される。このような条件をいずれも満たさない場合は、クリア (値が「0」) される。 20

**【0259】**

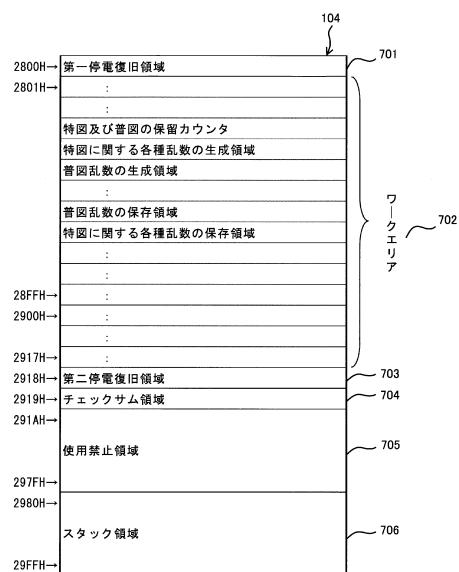

図14は、本発明の第1の実施の形態のユーザワークRAM104の一例を示す図である。

**【0260】**

ユーザワークRAM104は、第1停電復旧領域701、ワークエリア702、第2停電復旧領域703、チェックサム領域704、使用禁止領域（アクセス禁止領域）705、及びスタック領域706を有する。 30

**【0261】**

ユーザワークRAM104には、アドレス「2800H」～「29FFH」が割り当てられており、第1停電復旧領域701にはアドレス「2800H」が割り当てられ、ワークエリア702にはアドレス「2801H」～「2917H」が割り当てられ、第2停電復旧領域703にはアドレス「2918H」が割り当てられ、チェックサム領域704にはアドレス「2919H」が割り当てられ、使用禁止領域705にはアドレス「291AH」～「297FH」が割り当てられ、スタック領域706にはアドレス「2980H」～「29FFFH」が割り当てられる。 40

**【0262】**

ユーザワークRAM104の各領域について説明する。

**【0263】**

第1停電復旧領域701及び第2停電復旧領域703は、遊技機1への電源供給開始時に参照される情報が格納されており、直前の電源供給停止のとき（停電発生や遊技機1の電源スイッチをオフにしたとき）に、電源遮断の処理が正しく実行されていたか否かを示す情報（電源遮断確認フラグ）が格納されている。

**【0264】**

ワークエリア702には、遊技制御で必要な変数等が格納され、図25及び図26に示す遊技制御装置メイン処理並びに図29に示すタイマ割込処理等で、これらの変数が更新

される。具体的には、特図変動表示ゲーム及び普図変動表示ゲームの保留数を格納する保留カウンタ、特図変動表示ゲームを実行するために必要な各種乱数の生成領域、普図変動表示ゲームを抽選するために必要な乱数（普図乱数）の生成領域、普図乱数の保存領域、特図変動表示ゲームを実行するために必要な各種乱数の保存領域などがワークエリア702に記憶される。これらの詳細については、図15から図17を参照して後述する。

#### 【0265】

チェックサム領域704には、停電発生時に算出されたユーザワークRAM104の第1停電復旧領域701、ワークエリア702、及び第2停電復旧領域703のチェックサムが格納される。

#### 【0266】

使用禁止領域705は使用されない記憶領域であり、当該領域へのアクセスがあると、セキュリティ回路630（図6）によって、CPUコア102がリセットされるようになっている。

#### 【0267】

スタック領域706には、CPUコア102で演算されているデータの一部を一時的に退避させる場合に、退避データが格納される。また、割込みが発生した場合の戻りアドレスや、サブルーチンや関数を呼び出す場合の戻りアドレスも格納される。

#### 【0268】

なお、本実施形態では、ワークエリア702のうち遊技制御に用いられる各種乱数の生成及び保存領域の上位アドレスと、スタック領域706が割り当てられている領域の上位アドレスが異なるように設定されている。具体的には、ワークエリア702の各種乱数の生成及び保存領域の上位アドレスが「28H」、スタック領域の上位アドレスが「29H」となっており、乱数更新時にスタック領域の値を誤って更新してしまったり、スタック領域更新時に乱数の値を誤って更新してしまったりすることを防止している。

#### 【0269】

さらに、上位アドレスが誤って設定されてしまった場合であっても誤作動を生じさせないように、各種乱数の生成及び保存領域の下位アドレスがスタック領域の下位アドレスと重ならないように設定している。

#### 【0270】

具体的には、図15から図17で後述する、特図変動表示ゲームを実行するための各種乱数（始動記憶）の生成領域（2820H～2827H）、普図乱数の生成領域（2828H）及び普図乱数の保存領域（282CH～282FH）、第1特図変動表示ゲームを実行するための各種乱数（始動記憶）の保存領域（2830H～284FH）、及び、第2特図変動表示ゲームを実行するための各種乱数（始動記憶）の保存領域（2850H～286FH）などが該当する。これらの領域の上位アドレスを「28H」から「29H」に置換した領域（即ち2920H～296FHの領域）は、図14に示すように、使用禁止領域705として設定されている。

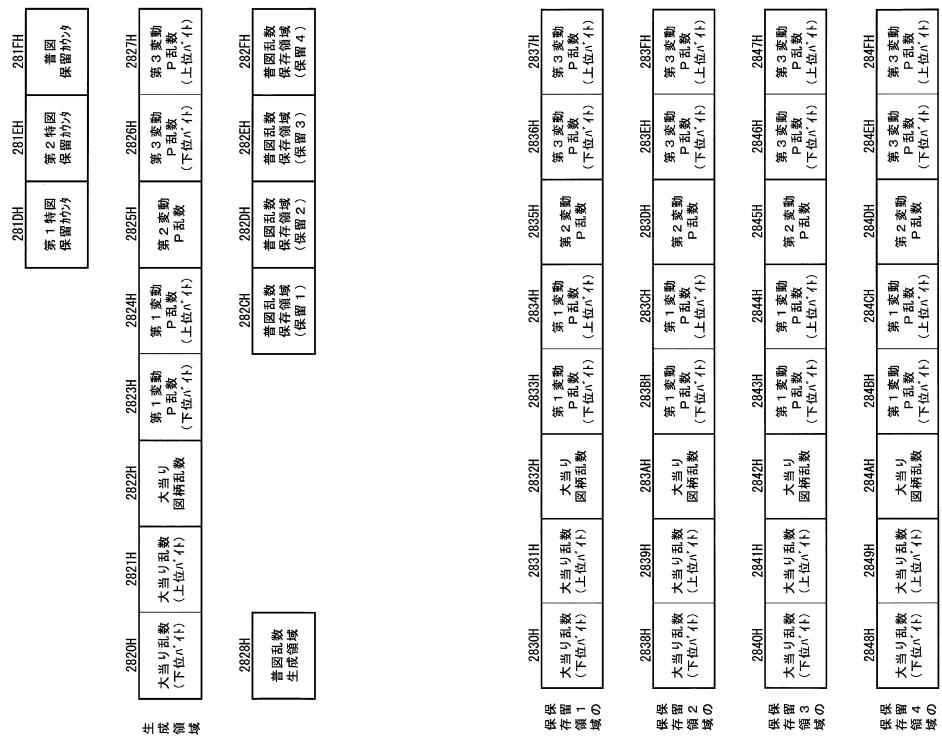

#### 【0271】

図15から図17は、本発明の第1の実施の形態のユーザワークRAM104に割り当てられたワークエリア702に格納されるデータの具体例を説明する図である。図15は保留カウンタ、各種乱数の生成領域及び普図乱数の保存領域を示す。図16は第1特図変動表示ゲームを実行するために必要な各種乱数の保存領域、図17は第2特図変動表示ゲームを実行するために必要な各種乱数の保存領域を示す。

#### 【0272】

図15を参照すると、保留カウンタを格納する領域として281DHから281FHが割り当てられている。具体的には、第1特図変動表示ゲームの保留記憶数を格納する第1特図保留カウンタ（281DH）、第2特図変動表示ゲームの保留記憶数を格納する第1特図保留カウンタ（281EH）、普図変動表示ゲームの保留記憶数を格納する普図保留カウンタ（281FH）となっている。さらに、特図変動表示ゲームを実行するための各種乱数（始動記憶）の生成領域（2820H～2827H）、普図乱数の生成領域（28

10

20

30

40

50

28H) 及び普図乱数の保存領域(282CH~282FH)が割り当てられている。

#### 【0273】

特図変動表示ゲームを実行するための各種乱数には、特図変動表示ゲームの大当たりを決定するための大当たり乱数(2バイト)、特図変動表示ゲームの大当たり図柄を決定するための大当たり図柄乱数、特図変動表示ゲームの変動パターンを決定するための第1変動P(パターン)乱数(2バイト)、第2変動P(パターン)乱数、第3変動P(パターン)乱数(2バイト)が含まれる。

#### 【0274】

図16を参照すると、第1特図変動表示ゲームを実行するための各種乱数を格納する領域が割り当てられている。本実施形態では、第1特図変動表示ゲームの始動記憶(特図1始動記憶)を最大4回分保持可能となっている。そして、これら乱数値は、特図始動口SW共通処理(図40)において設定される。

10

#### 【0275】

具体的には、記憶された特図1始動記憶の保留順に領域が割り当てられる。具体的には、保留1は2830Hから2837H、保留2は2838Hから283FH、保留3は2840Hから2847H及び保留4は2848Hから284FHの各領域が割り当てられている。また、各領域には、前述した特図変動表示ゲームを実行するための各種乱数に応じた領域がさらに割り当てられている。

#### 【0276】

そして、保留1個目の特図1始動記憶に対応する第1特図変動表示ゲームが実行される場合には、後述する特図普段処理の特図1変動開始処理(図45)において、保留1個目の各乱数を取得(一時的に退避)した後に、保留2個目~4個目の特図1始動記憶に対応する領域に記憶された各乱数を保留1個目~3個目の特図1始動記憶に対応する領域にシフトする。

20

#### 【0277】

そして、遊技制御装置100は、後述する特図大当たり判定処理(図42)において、取得した各乱数(一時的に退避していた保留1個目の各乱数)の値と、予め定義された特図1変動表示ゲーム用の大当たり判定値とを比較して、特図1変動表示ゲームが大当たりか否かを判定し、特図1始動記憶数(第1特図保留カウンタに記憶された値)を1減算する。

#### 【0278】

30

図17を参照すると、図16に示した第1特図変動表示ゲームの場合と同様に、第2特図変動表示ゲームを実行するための各種乱数(特図2始動記憶)を格納する領域が割り当てられている。特図2始動記憶に含まれる各種乱数は、特図1始動記憶と同様に処理される。

#### 【0279】

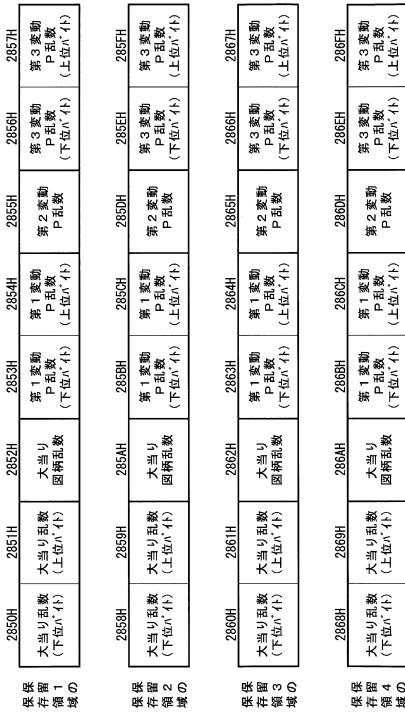

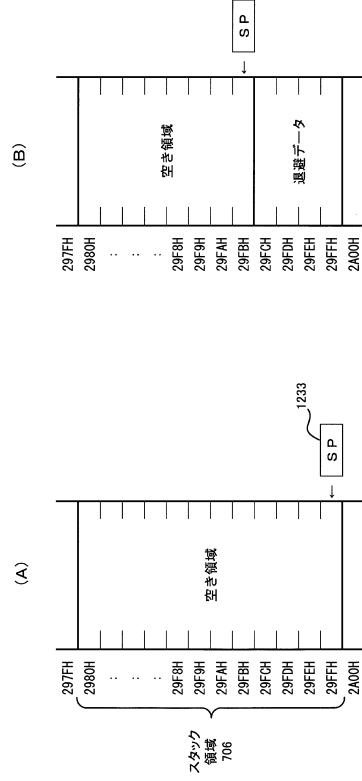

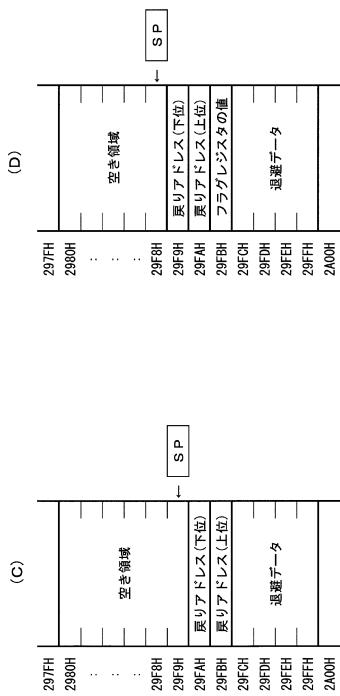

図18及び図19は、本発明の第1の実施の形態のスタック領域706の一例を示す図である。図18及び図19では、スタック領域706に戻アドレスや所定のレジスタの値が格納される場合について説明する。

#### 【0280】

まず、図18(A)は、遊技機1に電源が投入された直後の状態であり、スタック領域706に何もデータが格納されていない状態を示している。この場合、スタックポインタ(SP)1233は、スタック領域の最終領域(29FFFH)をスタックポインタ初期値として示している。

40

#### 【0281】

図18(B)は、スタック領域706に退避データが格納されたり、割込み発生やサブルーチン呼び出しによって、スタック領域706に戻アドレスなどのデータが格納された状態を示している。この場合、最後にデータ(又はアドレス)が格納された領域の1つ上のアドレスを、スタックポインタ1233によって示すことになる。

#### 【0282】

なお、スタック領域706に戻アドレスが格納される場合としては、割込みが発生し

50

た場合と、後述する「CALL」命令を実行して通常のサブルーチン呼び出しを行った場合とがあるが、本実施形態では、前者の場合と後者の場合とで、スタック領域706に格納されるデータが異なる。

#### 【0283】

図19(C)は、呼出元のルーチンにて後述する「CALL」命令を実行して通常のサブルーチン呼び出しを行った場合において、スタック領域706にデータが退避する様子を示している。なお、この図は、図18(B)の状態にて「CALL」命令を実行した直後の様子を示している。

#### 【0284】

図18(B)において、「CALL」命令を実行すると、スタック領域706に、呼出元のルーチンの戻りアドレスが上位バイトと下位バイトに分離して格納される。このとき、最後にアドレスが格納された領域の1つ上のアドレスが、スタックポインタ1233によって示される。10

#### 【0285】

なお、呼出先のサブルーチンの処理の最後にて、後述する「RET」命令が実行されると、この戻りアドレスがプログラムカウンタ1234に戻されるとともに、スタックポインタ1233の値も、「CALL」命令実行前の値に戻される(図18(B)の状態に戻る)。これにより、呼出元のルーチンに処理を戻すことができる。

#### 【0286】

一方、図19(D)は、呼出元のルーチンにて割込みが発生して、呼出先の割込処理のルーチンが実行される場合において、スタック領域706にデータが退避する様子を示している。なお、図19(D)は、図18(B)の状態にて割込みが発生した直後の様子を示している。20

#### 【0287】

図18(B)において、割込みが発生すると、スタック領域706に、まず、呼出元のルーチンで設定されていたフラグレジスタ1200の値が格納され、次に、呼出元のルーチン戻りアドレスが上位バイトと下位バイトに分離して格納される。このとき、最後にアドレスが格納された領域の1つ上のアドレスが、スタックポインタ1233によって示される。

#### 【0288】

なお、呼出先の割込処理ルーチンの最後にて、後述する「RETI」若しくは「RETN」命令が実行されると、スタック領域706に格納していた戻りアドレスがプログラムカウンタ1234に戻され、スタック領域706に格納していたフラグレジスタの値も、フラグレジスタ1200に戻される。さらに、スタックポインタ1233の値も、割込みが発生する前の値に戻される(図18(B)の状態に戻る)。これにより、呼出元のルーチンに処理を戻すことができる。30

#### 【0289】

このようにして、スタック領域706に格納された戻りアドレス等のデータは、後に格納された戻りアドレスから先に読み出される。

#### 【0290】

なお、後述する「PUSH」命令を実行すると、命令で指定されたレジスタの値がスタック領域706に格納され、スタックポインタ1233の値も、図19(C)や図19(D)と同様に、最後にデータが格納された領域の1つ上のアドレスを示すことになる。40

#### 【0291】

一方、後述する「POP」命令を実行すると、スタック領域706に格納されていた値を取り出して、命令で指定されたレジスタに格納され、スタックポインタ1233の値も、図19(C)から図18(B)に変化するように、最後にデータが取り出された領域のアドレスを示すことになる。

#### 【0292】

このように、本実施形態では、スタック領域706において最後にデータが格納された50

アドレスの1つ上のアドレス（言い換えれば、最後に取り出されたデータのアドレス）を、スタックポインタ1233によって示している。すなわち、現時点でのスタックポインタ1233は、次のスタック領域706に格納されるデータのアドレスを示している。

#### 【0293】

なお、別の方法として、現時点でのスタックポインタ1233によって、次にスタック領域706から取り出されるデータのアドレスを示すような方法も考えられる。このような変形例を図20に示す。

#### 【0294】

図20(E)は、遊技機1に電源が投入された直後の状態であり、スタック領域706に何もデータが格納されていない状態を示している。この場合、スタックポインタ(SP)1233は、スタック領域の最終領域(29FFFH)の1つ下のアドレス(2A00H)をスタックポインタ初期値として示している。なお、このスタックポインタ初期値が示す領域は、スタック領域には含まれない領域(本実施形態では、ユーザワークRAM104の記憶領域にも含まれていない領域)である。

10

#### 【0295】

図20(F)は、スタック領域706に退避データが格納されたり、割込み発生やサブルーチン呼び出しによって、スタック領域706に戻りアドレスなどのデータが格納された状態を示している。この場合、最後にデータ(又はアドレス)が格納された領域を、スタックポインタ1233によって示すことになる。スタック領域706からデータを取り出す場合は、現時点でスタックポインタ1233が示しているアドレスからデータを取り出せばよい。

20

#### 【0296】

なお、スタック領域706の割り当てが、上位アドレスが同じ領域に限定されている(例えば、2900H~29FFFHの領域に割り当てられることが限定されている)のであれば、スタックポインタ1233は下位のアドレスのみを指定するだけで機能を発揮する。このような構成においては、スタックポインタ1233を1バイトのレジスタで構成することが可能であり、図20の方法よりも、図18及び図19の方法にてスタックポインタ1233によるアドレス指定を行う構成が効果的である。

#### 【0297】

図21及び図22は、本発明の第1の実施の形態のCPUコア102によって実行される遊技制御プログラムを記述するためのアセンブリ言語の命令を説明する図である。各命令は、対応するコードデータに変換されて、ユーザプログラムROM103の所定のアドレスに記憶されている。図21は、変換後のコードデータにアドレス部を含まない命令(変換後のコードデータが命令コード部のみで構成される命令)を示し、図22は、変換後のコードデータに命令コード部とアドレス部の各々を含む命令を示している。なお、ここで対象となるレジスタは、図12に示すレジスタである。

30

#### 【0298】

図21において、命令2100は、指定するレジスタの値を、Aレジスタ1202Aに格納する命令である。例えば、「LD A, B」は、Bレジスタ1204Aの値を、Aレジスタ1202Aに格納する命令である。他の「LD A, C」~「LD A, L」の命令も同様に、対応するCレジスタ1205A~Lレジスタ1211Aから値を抽出して、Aレジスタ1202Aに格納する命令である。

40

#### 【0299】

命令2101は、Aレジスタ1202Aの値を、指定するレジスタに格納する命令である。例えば、「LD B, A」は、Aレジスタ1202Aの値を、Bレジスタ1204Aの値に格納する命令である。他の「LD C, A」~「LD L, A」の命令も同様に、Aレジスタ1202Aから値を抽出して、対応するCレジスタ1205A~Lレジスタ1211Aに格納する命令である。

#### 【0300】

命令2102は、Aレジスタ1202Aの値と指定するレジスタの値とで論理和演算を

50

行い、演算結果を A レジスタ 1202A に格納する命令である。例えば、「OR B」は、A レジスタ 1202A の値と B レジスタ 1204A の値とで、各ビット毎に論理和演算を行い、演算結果を A レジスタ 1202A に格納する命令である。他の「OR C」～「OR L」の命令も同様に、A レジスタ 1202A の値と、対応する C レジスタ 1205A ～ L レジスタ 1211A の値とで論理和演算を行い、演算結果を A レジスタ 1202A に格納する命令である。

#### 【0301】

命令 2103 の「ADD A, A」は、A レジスタ 1202A の値に、同じ A レジスタ 1202A の値を加算して、演算結果を A レジスタ 1202A に格納する命令である。実質的には、A レジスタ 1202A の値が 2 倍される演算が行われる命令である。命令 2104 の「ADD HL, BC」は、HL レジスタ 1212A の値に BC レジスタ 1206A の値を加算して、演算結果を HL レジスタ 1212A に格納する命令である。10

#### 【0302】

命令 2105 の「PUSH HL」は、HL レジスタ 1212A の値を、スタックエリアに格納する命令である。命令 2106 の「POP HL」は、スタックエリアから取り出した値を HL レジスタ 1212A の値に格納する命令である。

#### 【0303】

命令 2107 の「INC HL」は、HL レジスタ 1212A の値を「1」だけ加算する命令である。命令 2108 の「DEC HL」は、HL レジスタ 1212A の値を「1」だけ減算する命令である。20

#### 【0304】

命令 2109 の「JP (HL)」は、HL レジスタ 1212A の値をアドレスと見なして、そのアドレス先に分岐する命令である。例えば、HL レジスタ 1212A の値が「1234H」であれば、命令解釈実行回路 1242 は、プログラムカウンタ 1234 の値を「1234H」に変更する。これにより、次に、命令解釈実行回路 1242 が実行する命令は、アドレスが「1234H」となる領域に格納されているコードを変換した命令となる。以降、命令解釈実行回路 1242 は、変更後のアドレス以降の命令を順次実行する。

#### 【0305】

命令 2110 は、スタックエリアに格納された値をプログラムカウンタ 1234 に戻すことで、呼び出し先の処理ルーチンから、呼び出し元の処理ルーチンに復帰する命令である。ここで、「RET」は、図 22 で後述する「CALL nn」命令の実行により呼び出された処理ルーチンから復帰する命令であり、「RETI」は、INT 割込により呼び出された処理ルーチンから復帰する命令であり、「RETN」は、NMI 割込により呼び出された処理ルーチンから復帰する命令である。30

#### 【0306】

命令 2111 は、割込を受け付けるか否かを設定する命令である。「DI」は割り込みの禁止を設定する命令であり、「EI」は割り込みの許可を設定する命令である。

#### 【0307】

命令 2112 は、K レジスタ 1230 に格納されている値を上位バイトとし、L レジスタ 1211A に格納されている値を下位バイトとして合成した 2 バイトの値をアドレスと見なして、そのアドレスの領域に記憶されている値を、A レジスタ 1202A に設定する命令である。具体的には、「2803H」のアドレスに記憶された値を A レジスタ 1202A に設定したいときは、予め、K レジスタ 1230 に「28H」の値を格納するとともに、L レジスタ 1211A に「03H」の値を格納し、その状態で「LDK A, (L)」という命令を実行する。40

#### 【0308】

なお、A レジスタ 1202A の値を、所望のアドレスの領域に格納する場合は、予め格納先の上位アドレスを K レジスタ 1230 に設定し、下位アドレスを L レジスタ 1211A に設定した状態で、図に示す「LDK (L), A」という形式の命令を実行する。50

**【0309】**

命令2113の「INC L」は、Lレジスタ1211Aに格納されている値を「1」だけ加算する命令である。ただし、Lレジスタ1211Aの値が「FFH」のときに、「INC L」命令を実行すると、命令実行後のLレジスタ1211Aの値が「00H」になる。

**【0310】**

命令2114の「DEC L」は、Lレジスタ1211Aに格納されている値を「1」だけ減算する命令である。ただし、Lレジスタ1211Aの値が「00H」のときに、「DEC L」命令を実行すると、命令実行後のLレジスタ1211Aの値が「FFH」になる。

10

**【0311】**

命令2115は、図13で前述したフラグレジスタ1200の「レジスタバンクセレクタ」のビットに値を設定するための命令である。「LD RAS, 0」は該当ビットに「0」の値を設定する命令であり、「LD RAS, 1」は該当ビットに「1」の値を設定する命令である。

**【0312】**

命令2106の「PUSH FLG」は、フラグレジスタ1200の値を、スタックエリアに格納する命令である。命令2107の「POP FLG」は、スタックエリアから取り出した値をフラグレジスタ1200に格納する命令である。

20

**【0313】**

図21に示す命令のうち、図に示すように、命令2100から命令2114までの命令は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部を構成するコードデータに変換される。例えば、「LD A, B」の命令は、「78H」という1バイトのコードデータに変換されて、ユーザプログラムROM103の所定アドレスに記憶されている。

**【0314】**

一方、図21に示す命令のうち、命令2115から命令2117までの命令は、ユーザプログラムROM103に記憶される際に、2バイトの命令コード部を構成するコードデータに変換される。例えば、「LD RAS, 0」は、「CBH」「00H」という2バイトのコードデータに変換され、ユーザプログラムROM103の連続する所定のアドレスに記憶されている。

30

**【0315】**

次に、図22において、命令2200は、指定するレジスタに任意の1バイトの値を設定する命令である。図中の「n」はレジスタに設定する値を示しており、例えば、Aレジスタ1202Aに「42H」の値を設定したいときは、「LD A, 42H」という命令になる。

**【0316】**

なお、この命令2200は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、1バイトのアドレス部とからなる計2バイトのコードデータに変換される。例えば、「LD A, 42H」の命令は、1バイトの命令コード部のデータ「3EH」と、1バイトのアドレス部のデータ「42H」とに変換され、ユーザプログラムROM103の連続する所定のアドレスに「3EH」、「42H」の順で記憶されている。

40

**【0317】**

同様に、「LD B, n」は、Bレジスタ1204Aに任意の1バイトの値(n)を設定する命令であり、「LD K, n」は、Kレジスタ1230に任意の1バイトの値(n)を設定する命令である。これらの命令も、1バイトの命令コード部と、1バイトのアドレス部のデータに変換されて、ユーザプログラムROM103の連続する所定のアドレスに記憶されている。

**【0318】**

命令2201は、任意のアドレスの領域に記憶されている値を、Aレジスタ1202A

50

に設定する命令である。図中の「nn」は2バイトのアドレス値を示しており、例えば、「2901H」のアドレスに記憶された値をAレジスタ1202Aに設定したいときは、「LD A, (2901H)」という命令になる。

#### 【0319】

なお、Aレジスタ1202Aの値を、任意のアドレスの領域に格納する場合は、図に示すように「LD (nn), A」という形式の命令になる。例えば、Aレジスタ1202Aの値を「2901H」のアドレスの領域に格納したいときは、「LD (2901H), A」という命令になる。

#### 【0320】

この命令2201は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、2バイトのアドレス部とからなる計3バイトのコードデータに変換される。例えば、「LD A, (2901H)」の命令は、1バイトの命令コード部のデータ「3AH」と、2バイトのアドレス部のデータ「01H」「29H」とに変換され、ユーザプログラムROM103の連続する所定のアドレスに、「3AH」、「01H」、「29H」の順で記憶されている。

#### 【0321】

命令2202は、Kレジスタ1230に格納されている値を上位バイトとし、任意の1バイトの値で示される値を下位バイトとして合成した2バイトの値をアドレスと見なして、そのアドレスの領域に記憶されている値を、Aレジスタ1202Aに設定する命令である。この場合の任意の1バイトの下位アドレスは、図中の「n」に対応している。

#### 【0322】

具体的には、「2803H」のアドレスに記憶された値をAレジスタ1202Aに設定したいときは、予めKレジスタ1230に「28H」の値を格納しておき、その状態で「LDK A, (03H)」という命令を実行する。

#### 【0323】

なお、Aレジスタ1202Aの値を、所望のアドレスの領域に格納する場合は、予め格納先の上位アドレスをKレジスタ1230に設定した状態で、図に示す「LDK (n), A」という形式の命令を実行する。例えば、Aレジスタ1202Aの値を「2803H」のアドレスの領域に格納したいときは、Kレジスタ1230の値を「28H」に設定した状態で、「LDK (03H), A」という命令を実行する。

#### 【0324】

この命令2202は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、1バイトのアドレス部とからなる計2バイトのコードデータに変換される。例えば、「LDK A, (03H)」の命令は、1バイトの命令コード部のデータ「3FH」と、1バイトのアドレス部のデータ「03H」とに変換され、ユーザプログラムROM103の連続する所定のアドレスに、「3FH」、「03H」の順で記憶されている。

#### 【0325】

命令2203は、指定するレジスタに任意の2バイトの値を設定する命令である。図中の「nn」はレジスタに設定する2バイトの値を示しており、例えば、HLレジスタ1212Aに「5678H」の値を設定したいときは、「LD HL, 5678H」という命令になる。

#### 【0326】

なお、この命令2203は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、2バイトのアドレス部とからなる計2バイトのコードデータに変換される。例えば、「LD HL, 5678H」の命令は、1バイトの命令コード部のデータ「21H」と、2バイトのアドレス部のデータ「78H」「56H」とに変換され、ユーザプログラムROM103の連続する所定のアドレスに「21H」、「78H」、「56H」の順で記憶されている。

#### 【0327】

10

20

30

40

50

同様に、「LD SP, nn」は、スタックポインタ1233に任意の2バイトの値(nn)を設定する命令である。これらの命令も、1バイトの命令コード部と、2バイトのアドレス部のデータに変換されて、ユーザプログラムROM103の連続する所定のアドレスに記憶されている。

#### 【0328】

命令2204は、任意の連続するアドレスの領域に記憶されている2バイトの値を、HLレジスタ1212Aに設定する命令である。図中の「nn」は連続する小さいほうのアドレス値を示しており、例えば、「2901H」と「2902H」の各アドレスに記憶された値をHLレジスタ1212Aに設定したいときは、「LD HL, (2901H)」という命令になる。このとき、「2901H」のアドレスに格納されている値がHLレジスタ1211Aに格納され、「2902H」のアドレスに格納されている値がHLレジスタ1210Aに格納される。

10

#### 【0329】

なお、HLレジスタ1212Aの値を、任意の連続するアドレスの領域に格納する場合は、図に示すように「LD (nn), HL」という形式の命令になる。例えば、HLレジスタ1212Aの値を、「2901H」と「2902H」の各アドレスの領域に格納したいときは、「LD (2901H), HL」という命令になる。このとき、Lレジスタ1211Aの値が「2901H」のアドレスに格納され、HLレジスタ1210Aの値が「2902H」のアドレスに格納される。

#### 【0330】

この命令2204は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、2バイトのアドレス部とからなる計3バイトのコードデータに変換される。例えば、「LD HL, (2901H)」の命令は、1バイトの命令コード部のデータ「2AH」と、2バイトのアドレス部のデータ「01H」「29H」とに変換され、ユーザプログラムROM103の連続する所定のアドレスに、「2AH」、「01H」、「29H」の順で記憶されている。

20

#### 【0331】

命令2205は、Kレジスタ1230に格納されている値を上位バイトとし、任意の1バイトの値で示される値を下位バイトとして合成した2バイトの値をアドレスと見なして、そのアドレスの領域に記憶されている値と、当該アドレスに続くアドレスに記憶されている値の各々を、HLレジスタ1212Aに設定する命令である。この場合の任意の1バイトの下位アドレスは、図中の「n」に対応している。

30

#### 【0332】

具体的には、「2803H」及び「2804H」のアドレスに記憶された値をHLレジスタ1212Aに設定したいときは、予めKレジスタ1230に「28H」の値を格納しておき、その状態で「LD K HL, (03H)」という命令を実行する。これにより、「2803H」のアドレスに格納されている値がLレジスタ1211Aに格納され、「2804H」のアドレスに格納されている値がHLレジスタ1210Aに格納される。

#### 【0333】

なお、HLレジスタ1212Aの値を、所望のアドレスの領域に格納する場合は、予め格納先の上位アドレスをKレジスタ1230に設定した状態で、図に示す「LD K (n), HL」という形式の命令を実行する。例えば、HLレジスタ1212Aの値を「2803H」及び「2804H」のアドレスの領域に格納したいときは、Kレジスタ1230の値を「28H」に設定した状態で、「LD K (03H), HL」という命令を実行する。

40

#### 【0334】

この命令2205は、ユーザプログラムROM103に記憶される際に、1バイトの命令コード部と、1バイトのアドレス部とからなる計2バイトのコードデータに変換される。例えば、「LD K HL, (03H)」の命令は、1バイトの命令コード部のデータ「2FH」と、1バイトのアドレス部のデータ「03H」とに変換され、ユーザプログラム

50

R O M 1 0 3 の連続する所定のアドレスに、「3 F H」、「0 3 H」の順で記憶されている。

#### 【0 3 3 5】

命令 2 2 0 6 は、指定するアドレスに処理を分岐させる命令である。図中の「n n」は分岐先のアドレスを示しており、例えば、「5 6 7 8 H」のアドレスに処理に分岐させるときは、「J P 5 6 7 8 H」という命令になる。この命令を実行すると、命令解釈実行回路 1 2 4 2 は、指定するアドレスの値をプログラムカウンタ 1 2 3 4 に設定する。

#### 【0 3 3 6】

なお、この「J P n n」の形式で示される命令は、フラグレジスタ 1 2 0 0 の内容にかかわらず、指定するアドレスに処理を分岐する。フラグレジスタ 1 2 0 0 のゼロフラグ 1 3 0 6 (図 1 3) がセットされているときのみ分岐を行いたい場合は「J P Z, n n」の命令を用い、このゼロフラグ 1 3 0 6 がクリアされているときのみ分岐を行いたい場合は「J P N Z, n n」の命令を用いる。

#### 【0 3 3 7】

なお、この命令 2 2 0 6 は、ユーザプログラム R O M 1 0 3 に記憶される際に、1 バイトの命令コード部と、2 バイトのアドレス部とからなる計 2 バイトのコードデータに変換される。例えば、「J P 5 6 7 8 H」の命令は、1 バイトの命令コード部のデータ「C 3 H」と、2 バイトのアドレス部のデータ「7 8 H」「5 6 H」とに変換され、ユーザプログラム R O M 1 0 3 の連続する所定のアドレスに「C 3 H」、「7 8 H」、「5 6 H」の順で記憶されている。

10

20

#### 【0 3 3 8】

命令 2 2 0 7 の「C A L L n n」は、指定するアドレスの処理を呼び出して、呼び出し先の処理ルーチンに一時的に分岐させる命令である。図中の「n n」は呼び出し先のアドレスを示しており、例えば、「5 6 7 8 H」のアドレスの処理を呼び出すときは、「C A L L 5 6 7 8 H」という命令になる。この命令を実行すると、命令解釈実行回路 1 2 4 2 は、現在実行中の命令の次のステップに位置するアドレスの値を、戻り先のアドレスとしてスタックエリアに格納した上で、分岐先のアドレスの値をプログラムカウンタ 1 2 3 4 に設定する。

#### 【0 3 3 9】

なお、呼び出し先の処理ルーチンの最終ステップでは、前述の「R E T」命令を実行することで、プログラムカウンタ 1 2 3 4 には、スタックエリアに格納された戻り先のアドレスの値を復帰させることができる。これにより、呼び出し元の処理ルーチンのアドレスに処理を戻すことができる。

30

#### 【0 3 4 0】

なお、この命令 2 2 0 7 は、ユーザプログラム R O M 1 0 3 に記憶される際に、1 バイトの命令コード部と、2 バイトのアドレス部とからなる計 2 バイトのコードデータに変換される。例えば、「C A L L 5 6 7 8 H」の命令は、1 バイトの命令コード部のデータ「C D H」と、2 バイトのアドレス部のデータ「7 8 H」「5 6 H」とに変換され、ユーザプログラム R O M 1 0 3 の連続する所定のアドレスに「C 3 H」、「7 8 H」、「5 6 H」の順で記憶されている。

40

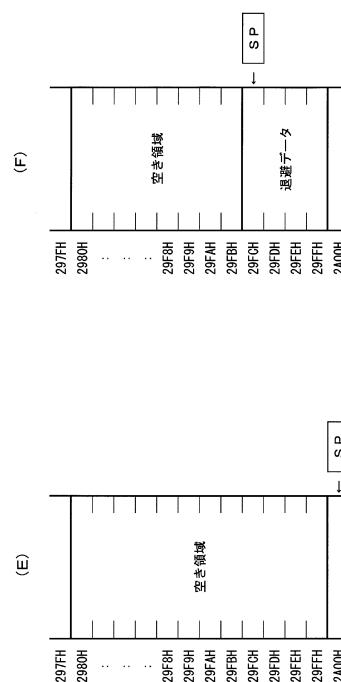

#### 【0 3 4 1】

図 2 3 は、本発明の第 1 の実施の形態の各装置（遊技制御装置 1 0 0 、払出制御装置 2 1 0 、及び演出制御装置 1 5 0 ）の電源投入時処理のフローチャートである。

#### 【0 3 4 2】

具体的には、図 2 3 (A) は、遊技制御装置 1 0 0 の電源投入時処理のフローチャートであり、図 2 3 (B) は、払出制御装置 2 1 0 の電源投入時処理のフローチャートであり、図 2 3 (C) は、演出制御装置 1 5 0 の電源投入時処理のフローチャートである。

#### 【0 3 4 3】

最初に、遊技制御装置 1 0 0 の電源投入時処理（図 2 3 (A)）から説明する。この電源投入時処理は、ユーザプログラム R O M 6 0 2 (図 5 参照) に記憶された遊技制御プロ

50

グラムによって実行される処理ではなく、遊技制御装置 100 に備わる各種ハードウェア (C P U コア 102 周辺のハードウェア) によって実行される処理である。

#### 【0344】

まず、遊技制御装置 100 は、電源装置 160 から出力されたリセット信号が伝達される (2301)。

#### 【0345】

このリセット信号は、電源装置 160 から、セキュリティ回路 630 (図 11 参照)、RAM アクセス規制回路 640 のフリップフロップ回路 641 のリセット端子 (図 11 参照)、及びシリアル送信回路 615 のリセット端子に入力される。具体的には、これらのリセット端子には、電源が投入されると、所定時間、所定の電圧 (例えば、5V) 以下の電圧が印加されることによってリセット信号が入力され、所定時間経過後に所定の電圧が印加されることによって、リセット信号が入力されなくなる。10

#### 【0346】

なお、セキュリティ回路 630 は、電源装置 160 からリセット信号が入力されると、後述のセキュリティチェック処理が終了するまで C P U コア 102 のリセット端子にリセット信号を出力し続けて、C P U コア 102 の起動を待機させる。

#### 【0347】

そして、シリアル送信回路 615 のリセット端子にリセット信号が入力されると、シリアル送信回路 615 の入力端子及び出力端子の電圧レベルがローに制御され、各種装置 (普電 S O L 90、大入賞口 S O L 38 等) に接続される出力 I / F 106 のポートをすべて 0 に設定することにより、シリアル送信回路 615、及び出力 I / F 106 がハードウェアにより初期化される (2302)。20

#### 【0348】

次に、RAM アクセス規制回路 640 によって、ユーザワーク RAM 104 への書き込み規制される RAM 書込禁止状態が発生する (2303)。

#### 【0349】

具体的には、図 11 で説明したように、フリップフロップ回路 641 のクリア端子にはリセット信号が入力されるため、フリップフロップ回路 641 の出力端子 Q (負論理) からハイレベルの信号が出力される状態となる。これにより、OR ゲート回路 642 の他方の入力端子にハイレベルの信号が入力されても、ローレベルの信号が入力されても、ユーザワーク RAM 104 の書込指令入力端子にはハイレベルの信号が入力されることになるため、RAM 書込禁止状態が発生する。このように、電源投入時に RAM 書込禁止状態を発生させることによって、誤ったタイミングでユーザワーク RAM 104 が更新されることを防ぐことが可能となる。30

#### 【0350】

次に、リセット信号が入力された図 11 に示すセキュリティ回路 630 が自己診断処理を実行する (2304)。自己診断処理は、セキュリティ回路 630 が初期化されているか否かを判定する処理である。

#### 【0351】

そして、自己診断処理によって、セキュリティ回路 630 が初期化されていると判定された場合には、セキュリティ回路 630 は、セキュリティチェック処理を実行する (2305)。セキュリティチェック処理は、図 11 で説明したように、HW パラメータ ROM 603 (図 5 参照) に記憶された正当性確認情報を用いて、ユーザプログラム ROM 602 (図 5 参照) に記憶されたプログラムの正当性の判定を行う処理である。40

#### 【0352】

ステップ 2305 の処理で、セキュリティチェック処理を実行すると、遊技制御装置プログラム開始準備処理へ移行する。このとき、セキュリティ回路 630 は、C P U コア 102 のリセット端子に出力していたリセット信号を停止することで、C P U コア 102 が起動する。このため、遊技制御装置プログラム開始準備処理は、C P U コア 102 によって実行される。遊技制御装置プログラム開始準備処理は図 24 にて後述する。50

**【0353】**

次に、払出制御装置210の電源投入時処理(図23(B))を説明する。前述したように、払出制御装置210は、シリアル送信回路615を備えていない点を除き、図11に示した遊技制御装置100と同じ構成である。図11に示す遊技制御装置100の構成部と同じ構成部については、同じ符号を付与して説明する。

**【0354】**

まず、払出制御装置210は、電源装置160から出力されたリセット信号が伝達される(2311)。なお、ステップ2311の処理は、ステップ2301の処理と同じである。

**【0355】**

そして、払出制御装置210にリセット信号が入力されると、払出制御装置210の出力ポート(図4の入出力I/F216に含まれる)の電圧レベルが0に設定され、各種装置(払出モータ220、及び発射制御装置221等)に接続される入出力I/F216のポートがすべて0に設定され、入出力I/F216がハードウェアにより初期化される(2312)。

**【0356】**

次に、払出制御装置210のRAMアクセス規制回路640によって、RAM214への書き込み規制されるRAM書き禁止状態が発生する(2313)。なお、ステップ2313の処理の具体的な説明は、ステップ2303の処理と同じである。

**【0357】**

次に、リセット信号が入力された払出制御装置210のセキュリティ回路630が自己診断処理を実行する(2314)。なお、ステップ2314の処理の具体的な説明は、ステップ2304の処理と同じである。

**【0358】**

そして、自己診断処理によって、セキュリティ回路630が初期化されていると判定された場合には、セキュリティ回路630は、セキュリティチェック処理を実行する(2315)。なお、ステップ2315の処理の具体的な説明は、ステップ2305の処理と同じである。

**【0359】**

そして、払出制御装置210は、電源投入時の初期化処理を実行する(2316)。電源投入時の初期化処理は、RAM214等を初期化する処理であって、CPU212によって実行される。また、RAM214を初期化する前に、ステップ2313の処理で発生したRAM書き禁止状態が解除されて、RAM214はRAM書き可能状態となる。

**【0360】**

次に、払出制御装置210は、遊技制御装置100からの指令を受信可能な状態を発生させる(2317)。そして、払出制御装置210のCPU212は、遊技制御装置100から送信された指令が初期化指令であるか否かを判定する(2319)。ステップ2319の処理で、遊技制御装置100から送信された指令が初期化指令でないと判定された場合には(2319の結果が「N」)、初期化指令が取り込まれるまで待機する。

**【0361】**

一方、遊技制御装置100から送信された指令が初期化指令であると判定された場合には(2319の結果が「N」)、払出制御装置210は通信開始時の初期化処理を実行し(2320)、払出制御装置メイン処理へ移行する。

**【0362】**

次に、演出制御装置150の電源投入時処理(図23(C))を説明する。前述したように、演出制御装置150は、シリアル送信回路615を備えていない点、及び、遊技用演算処理装置600がRAMアクセス規制回路640を備えていない点以外は、図11に示した遊技制御装置100と同じ構成である。図11に示す遊技制御装置100の構成部と同じ構成部については、同じ符号を付与して説明する。

**【0363】**

10

20

30

40

50

まず、演出制御装置 150 は、電源装置 160 から出力されたリセット信号が伝達される（2321）。なお、ステップ 2321 の処理は、ステップ 2301 の処理と同じである。

#### 【0364】

そして、演出制御装置 150 にリセット信号が入力されると、演出制御装置 150 の出力ポートがハードウェアにより初期化される（2322）。

#### 【0365】

そして、演出制御装置 150 は、電源投入時の初期化処理を実行する（2323）。電源投入時の初期化処理は、RAM 154 等を初期化する処理であって、CPU 152 によって実行される。

10

#### 【0366】

次に、演出制御装置 150 は、遊技制御装置 100 からの指令を受信可能な状態を発生させる（2324）。そして、遊技制御装置 100 から送信された指令が初期化指令であるか否かを判定する（2326）。

#### 【0367】

演出制御装置 150 は、遊技制御装置 100 から送信された指令が初期化指令でないと判定された場合には（2326 の結果が「N」）、初期化指令が取り込まれるまで待機する。

#### 【0368】

一方、演出制御装置 150 は、遊技制御装置 100 から送信された指令が初期化指令であると判定された場合（2326 の結果が「Y」）、演出制御装置 150 は通信開始時の初期化処理を実行し（2327）、演出制御装置メイン処理へ移行する。

20

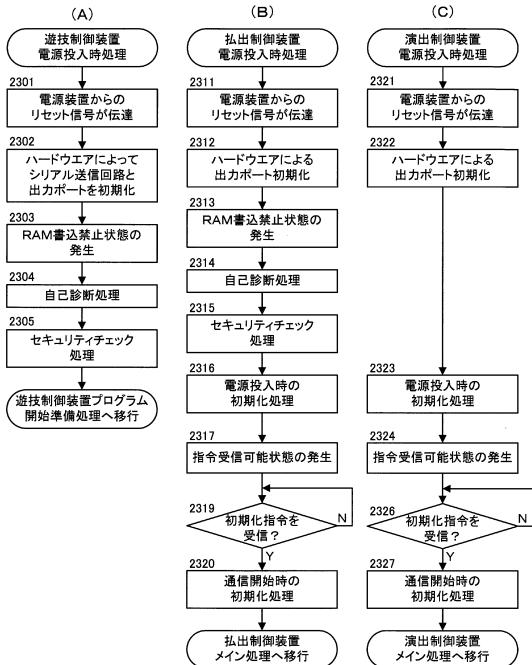

#### 【0369】

図 24 は、本発明の第 1 の実施の形態の遊技制御装置プログラム開始準備処理を説明するフローチャートである。なお、遊技制御装置プログラム開始準備処理の前半（プログラムカウンタ 1234 にリセットアドレスを設定するまでの間）は、ユーザプログラム ROM 602（図 5 参照）に記憶された遊技制御プログラムによって実行される処理ではなく、CPU コア 102 に備わる初期値設定回路 124（図 12 参照）によって実行される処理である。

#### 【0370】

30

CPU コア 102 は、セキュリティ回路 630 からのリセット信号を受け入れると、内蔵リセット回路 1240 により、初期値設定回路 1241 を動作させる。このとき、内蔵リセット回路 1240 は、初期値設定回路 1241 が各レジスタに初期値を設定するまで、命令解釈実行回路 1242 の動作を待機させる。

#### 【0371】

初期値設定回路 1241 が動作を開始すると、スタックポインタ 1233 に初期値「29FFH」を設定し、K レジスタ 1230 に「28H」を設定し、HL レジスタ 1212 A にリセットアドレスである「4000H」を設定し、他のレジスタには「00H」の値（16 ビットレジスタには「0000H」の値）を設定する（2401）。なお、リセットアドレスは「0000H」としてもよい。

40

#### 【0372】

次いで、初期値設定回路 1241 は、プログラムカウンタ 1234 に、リセットアドレスである「4000H」の値を設定する（2402）。これにより、各レジスタに初期値が設定される。次いで、内蔵リセット回路 1240 は、待機させていた命令解釈実行回路 1242 を動作させると、命令解釈実行回路 1242 は、プログラムカウンタ 1234 が示すアドレス（遊技制御プログラムが記憶されたユーザプログラム ROM 602 のリセットアドレスに相当）からプログラムの実行を開始する。命令解釈実行回路 1242 がプログラムを実行開始した後の処理は、図 25 の遊技制御装置メイン処理にて説明する。

#### 【0373】

次に、遊技制御装置 100 の CPU 102 によって実行される遊技制御装置メイン処理

50

を、図25及び図26を用いて説明する。

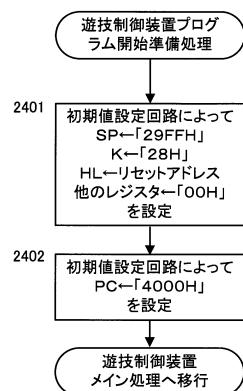

**【0374】**

図25は、本発明の第1の実施の形態の遊技制御装置メイン処理の前半部のフローチャートであり、図26は、本発明の第1の実施の形態の遊技制御装置メイン処理の後半部のフローチャートである。なお、これらの処理は遊技制御装置100によって実行されるが、厳密には、命令解釈実行回路1242が、CPUコア102内部の各レジスタを参照しながら、遊技制御プログラムを実行することで実現される。

**【0375】**

まず、遊技制御装置100は、CPU102への割込みを禁止する(2501)。そして、遊技制御装置100は、スタックポインタ1233(図12)に初期値「29FFFH」を設定する(2502A)。これにより、スタックポインタ1233の値が「29FFFH」でなければ「29FFFH」に変更される。なお、スタックポインタ1233に初期値「29FFFH」が既に設定されていても、再度「29FFFH」の値が設定される。

**【0376】**

次いで、遊技制御装置100は、Kレジスタ1230に「28H」の値を設定する(2502B)。これにより、Kレジスタ1230の値が「28H」でなければ「28H」に変更される。なお、Kレジスタ1230に初期値「28H」が既に設定されていても、再度「28H」の値が設定される。

**【0377】**

次いで、遊技制御装置100は、割込モードを設定する(2503)。割込モードは、CPU102が内蔵デバイスからの割込要求の処理を可能とし、また、プログラムにおいて割込要求の処理を実行する位置を設定することを可能とするものである。

**【0378】**

次に、遊技制御装置100は、入力I/F105からRAMクリアSW信号の状態を取り込み、取り込んだRAMクリアSW信号の状態をCPU102のレジスタに記憶する(2504)。

**【0379】**

そして、遊技制御装置100は、RAM104を使用しないディレイ処理を実行する(2505)。このディレイ処理は、所定時間、処理を待機させる処理であり、具体的には、チェックサムが算出されない記憶領域にて、所定の数が0になるまでデクリメントし続ける処理である。ディレイ処理は、この所定の数を待機させる時間に対応する時間に設定することによって、所定時間を計時するタイマ計時手段となる。なお、ディレイ処理の詳細については、図28にて後述する。

**【0380】**

次に、遊技制御装置100は、再度、入力I/F105からRAMクリアSW信号の状態を取り込み、取り込んだRAMクリアSW信号の状態をCPU102のレジスタに記憶する(2506)。なお、CPU102が二つのRAMクリア信号の状態を比較できるように、ステップ2504の処理でRAMクリアSW信号の状態を記憶するレジスタの領域、及び、ステップ2506の処理でRAMクリアSW信号の状態を記憶するレジスタの領域は、異なる領域である。

**【0381】**

次に、遊技制御装置100は、図23のステップ2303の処理で発生したRAM書き禁止状態をRAM書き可能状態にする(2507)。

**【0382】**

具体的には、CPU102の指令によって、フリップフロップ回路641のクロック端子にクロック信号を出力制御回路612から入力させ、かつ、フリップフロップ回路641のデータ端子に接続された信号線の信号レベルをハイレベルにする。これにより、フリップフロップ回路641の出力端子Q(正論理)からハイレベルの信号が出力され、出力端子Q(負論理)からローレベルの信号が出力されるため、ORゲート回路642の入力端子にローレベルの信号が入力されることにより、RAM書き可能状態になる。

10

20

30

40

50

**【0383】**

次に、遊技制御装置100は、スタック領域706を使用して、各種設定処理を実行する(2508)。この設定処理は、例えば、サブルーチンや関数を呼び出して、遊技制御に必要な各種記憶領域に初期データを設定する処理である。この設定処理において、CPU102により、図7～図9で前述した、送信シリアルチャンネル設定レジスタ633、送信制御レジスタ632、送信データステータスレジスタ631の各ビットの初期値が設定されることで、送信ボーレート等の設定が行われる。

**【0384】**

これらのサブルーチンや関数は、遊技制御プログラムに記述した複数箇所から呼び出される形態となっており、遊技制御プログラムの容量削減に貢献している。一方で、サブルーチンや関数を呼び出す際には、前述したように、戻りアドレスをスタック領域706に待避する処理を必要とする。

10

**【0385】**

そして、遊技制御装置100は、ステップ2504の処理でレジスタに記憶されたRAMクリアSW信号の状態とステップ2508の処理でレジスタに記憶されたRAMクリアSW信号の状態とを比較して、どちらのRAMクリアSW信号の状態も、RAMクリアSW162が操作されたことを示しているか否かを判定する(2509)。

**【0386】**

ステップ2509の処理では、異なるタイミングで取得したRAMクリア信号の状態に基づいてRAMクリアSW162が操作されたか否かを判定しているので、ノイズ等による誤判定を防止できる。

20

**【0387】**

ステップ2509の処理で、RAMクリアSW162が操作されたと判定された場合、遊技制御装置100は、ユーザワークRAM104のすべての記憶領域を初期化する(2510)。

**【0388】**

そして、遊技制御装置100は、初期化指令信号を払出制御装置210及び演出制御装置150へ送信し(2511)、図26に示すステップ2517の処理に進む。

**【0389】**

一方、ステップ2509の処理で、RAMクリアSW162が操作されていないと判定された場合、遊技制御装置100は、ユーザワークRAM104の第1停電復旧領域701及び第2停電復旧領域703に、電源遮断確認フラグが格納されているか(正確には、電源遮断確認フラグがオンとなっているか)を確認する(2512)。

30

**【0390】**

そして、遊技制御装置100は、直前の電源供給停止のときに、電源遮断の処理が正しく実行されていたか否かを判定する(2513)。具体的には、遊技制御装置100は、第1停電復旧領域701及び第2停電復旧領域703の両方に電源遮断確認フラグが格納されている場合には、電源遮断の処理が正しく実行されているものであると判定し、一方、第1停電復旧領域701及び第2停電復旧領域703の少なくとも一方に電源遮断確認フラグが格納されていない場合(少なくとも一方の電源遮断確認フラグがオフの場合)には、電源遮断の処理が正しく実行されていないと判定する。

40

**【0391】**

ステップ2513の処理で電源遮断の処理が正しく実行されていたと判定された場合には、遊技制御装置100は、ユーザワークRAM104の第1停電復旧領域701、ワークエリア702、及び第2停電復旧領域703を用いてチェックサムを算出して、算出したチェックサムがチェックサム領域704に格納されているチェックサムと一致するか否かを照合する(2514)。

**【0392】**

なお、チェックサム領域704に格納されているチェックサムは、停電検出時のユーザワークRAM104の第1停電復旧領域701、ワークエリア702、及び第2停電復旧

50

領域 703 を用いてチェックサムを算出して、格納されたものである。

#### 【0393】

つまり、ステップ 2514 の処理は、停電検出時のユーザワーク RAM104 に格納された情報と電源投入時のユーザワーク RAM104 に格納された情報とが一致するか否かを照合する処理である。

#### 【0394】

そして、ステップ 2514 の処理の照合結果が、算出したチェックサムとチェックサム領域 704 に格納されたチェックサムとが一致するものであるか否かを判定する (2515)。

#### 【0395】

ステップ 2514 の処理で算出したチェックサムとチェックサム領域 704 に格納されたチェックサムとが一致しないとステップ 2515 の処理で判定された場合、つまり、停電検出時のユーザワーク RAM104 に格納された情報と電源投入時のユーザワーク RAM104 に格納された情報とが一致しない場合には、遊技制御装置 100 は、ステップ 2510 の処理に進み、ユーザワーク RAM104 のすべての領域を初期化し、ステップ 2511 の処理にて初期化指令を払出制御装置 210 及び演出制御装置 150 に送信する。

#### 【0396】

一方、ステップ 2514 の処理で算出したチェックサムとチェックサム領域 704 に格納されたチェックサムとが一致するとステップ 2515 の処理で判定された場合、つまり、停電検出時のユーザワーク RAM104 に格納された情報と電源投入時のユーザワーク RAM104 に格納された情報とが一致する場合には、遊技制御装置 100 は、遊技制御装置 100 の起動に必要な領域 (ユーザワーク RAM104 の一部の領域) を初期化する (2516)。このとき、ユーザワーク RAM104 の第 1 停電復旧領域 701 及び第 2 停電復旧領域 703 の各々にて、電源遮断確認フラグが消去 (正確には、各領域にて電源遮断確認フラグがオフ) される。そして、遊技制御装置 100 は、初期化指令を払出制御装置 210 及び演出制御装置 150 に送信する (2511)。

#### 【0397】

これらの処理が完了すると、遊技制御装置 100 に関する初期化処理が完了となる。次いで、図 26 に示すステップ 2517 の処理に進む。

#### 【0398】

次に、ステップ 2511 の処理で初期化指令が払出制御装置 210 及び演出制御装置 150 に送信された後、遊技制御装置 100 は、各種時間を計測やタイマ割込みを行うための CTC (Counter Timer Circuit) を起動し (2517)、遊技制御に関する乱数を生成する乱数生成回路 608 (図 5) を初期化する (2518)。そして、遊技制御装置 100 は、ステップ 2501 の処理で禁止された CPU102 への割込みを許可する (2519)。

#### 【0399】

次に、遊技制御装置 100 は、初期値乱数を更新する初期値乱数更新処理を実行する (2520)。初期値乱数とは、遊技制御に関する乱数のカウンタ (例えば、始動入賞口へ入賞したタイミングで取得される乱数のカウンタ) が上限値に達した場合に初期値に戻るが、その初期値を決定するための乱数である。

#### 【0400】

そして、遊技制御装置 100 は、停電検出信号が入力されたか否かを確認し (2521)、ステップ 2521 の処理での確認結果が、停電検出信号が入力されたことを示すか否かを判定する (2522)。

#### 【0401】

遊技制御装置 100 は、停電検出信号が入力されていないと判定した場合には (ステップ 2522 の結果が「N」)、停電は発生していないので、ステップ 2520 の処理に戻る。

#### 【0402】

10

20

30

40

50

一方、ステップ 2522 の処理で、停電検出信号が入力されたと判定された場合、遊技制御装置 100 は、CPU102 への割込みを禁止し(2523)、出力 I/F106 に備わる出力ポートの電圧レベルをローレベルに設定する(2524)。

#### 【0403】

次に、遊技制御装置 100 は、ユーザワーク RAM104 の第 1 停電復旧領域 701 及び第 2 停電復旧領域 703 に、電源遮断確認フラグを格納(正確には、各領域にて電源遮断確認フラグをオン)し(2525)、ユーザワーク RAM104 の第 1 停電復旧領域 701、ワークエリア 702、及び第 2 停電復旧領域 703 を用いてチェックサムを算出して、算出したチェックサムをチェックサム領域 704 に格納する(2526)。

#### 【0404】

次に、遊技制御装置 100 は、RAM アクセス規制回路 640 によってユーザワーク RAM104 を RAM 書込禁止状態にする(2527)。

#### 【0405】

具体的には、CPU102 の指令によって、フリップフロップ回路 641 のクロック端子にクロック信号を出力制御回路 612 から入力させ、かつ、フリップフロップ回路 641 のデータ端子に接続された信号線の信号レベルをローレベルにする。これにより、フリップフロップ回路 641 の出力端子 Q(正論理) からローレベルの信号が出力され、出力端子 Q(負論理) からハイレベルの信号が出力されるため、OR ゲート回路 642 の入力端子にハイレベルの信号が入力されることにより、RAM 書込禁止状態になる。

#### 【0406】

そして、遊技制御装置 100 は、遊技機 1 の電源が切れるまで待機する(2528)。なお、遊技制御装置 100 には、バックアップ電源が接続されているので、停電が発生しても、すぐに電源が切れることはない。

#### 【0407】

なお、本実施形態では、ステップ 2514 の処理で電源断時のユーザワーク RAM104 と電源投入時のユーザワーク RAM104 との正当性を判定する前のステップ 2507 の処理で RAM 書込可能状態にしたが、RAM 書込可能状態にするタイミングは、遅くともステップ 2514 の処理の正当性に応じて行われるステップ 2510 又は 2516 の処理におけるユーザワーク RAM104 の初期化処理の実行直前であればよい。

#### 【0408】

このように、遊技機 1 にて電源供給が遮断した場合には、必要な電源遮断処理を実行した後は、ユーザワーク RAM104 を RAM 書込禁止状態に設定し、遊技機 1 にて再度電源供給が復帰したときでも、すぐにユーザワーク RAM104 を RAM 書込可能状態としないで、ハードウェアに関する初期化処理を一定時間実行し、ステップ 2514 の処理の正当性に応じて行われるステップ 2510 又は 2516 の処理におけるユーザワーク RAM104 の初期化処理の実行直前になって、ようやく RAM 書込可能状態にすることによって、ユーザワーク RAM104 の初期化まで不用意なユーザワーク RAM104 の書き込みを防止できる。

#### 【0409】

そのため、ステップ 2514 の処理における正当性判定が行われる直前には、RAM 書込禁止状態になっているので、電源投入後にユーザワーク RAM104 に誤った書き込みがなされ、ステップ 2514 の処理で誤った判定がされることを防止できる。

#### 【0410】

なお、本実施形態では、ステップ 2508 の処理でスタック領域 706 を用いた各種設定処理を実行するために、ステップ 2514 の処理における正当性判定処理の前のステップ 2507 の処理で RAM 書込可能状態にしている。

#### 【0411】

これによって、正当性判定を行う前に正当性判定の対象とはならないスタック領域 706 を用いた各種設定処理を行うことができるようになるため、遊技制御装置 100 の各種設定を早い段階で行うことができるので遊技制御装置 100 の起動を高速化でき、また、

10

20

30

40

50

スタック領域 706 を用いるので処理プログラムが共通化でき、プログラム容量を削減できる。

#### 【0412】

なお、図15では、ステップ2510又は2516の処理でユーザワークRAM104を初期化した後、ステップ2515の処理で初期化指令信号を送信しているが、ステップ2514における正当性判定の実行前のステップ2508の処理の実行後に初期化指令信号を送信してもよい。

#### 【0413】

この場合には、ステップ2514の処理における正当性判定の実行前であるので、正当性判定に寄与しないスタック領域706又はCPU102に備わるレジスタを用いて、初期化指令信号を送信する。

10

#### 【0414】

なお、CPU102に備わるレジスタを用いなくても、例えば、ユーザワークRAM104とは別個に、遊技制御装置100に所定のタイマ回路などを設けて、このタイマ回路に備えられた記憶領域を更新させるような方法でも実現可能である。言い換れば、正当性判定に影響のない記憶領域であれば、どのようなものを用いても適用が可能であり、好みしくは、ユーザワークRAM104と記憶領域とを分離できれば、CPU102のプログラムも簡素化されるということである。

#### 【0415】

ステップ2510又は2516の処理では、RAM104の一部領域を初期化する処理であるステップ2516の処理が、RAM104の全領域を初期化する処理であるステップ2510の処理よりも実行時間が長いため、ステップ2510の処理を実行するかステップ2516の処理を実行するかによって、初期化指令信号が送信される時間が異なってしまう。

20

#### 【0416】

ステップ2514の処理における正当性判定の実行前に初期化指令信号を送信することによって、ステップ2511の処理で初期化指令信号を送信するよりも早く初期化指令信号を送信できる。また、電源投入から一定時間で初期化指令信号を送信することができる。

#### 【0417】

30

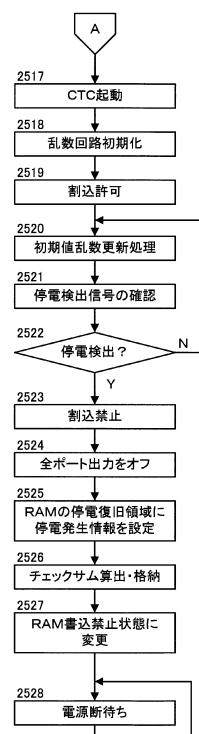

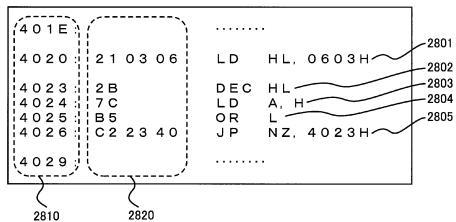

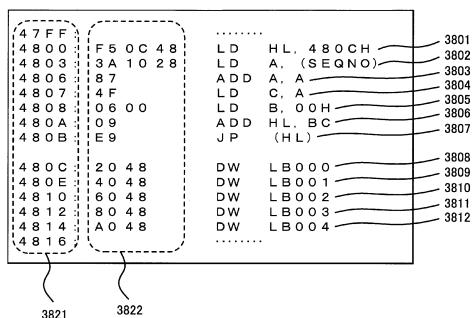

図27は、本発明の第1の実施の形態の遊技制御装置メイン処理(図25)におけるステップ2501からステップ2502Bまでの処理を説明する図である。ここでは、図12で前述した各種レジスタ、図21及び図22で前述したアセンブリ言語を用いて説明を行うこととする。

#### 【0418】

なお、図27における列2710は、遊技制御プログラムが格納されているユーザプログラムROM103のアドレスを示し、列2720は、当該アドレスに格納されているデータを示している。例えば、ユーザプログラムROM103の「4000H」のアドレスには「F3H」のデータが格納され、続く「4001H」のアドレスには「31H」のデータが格納され、続く「4002H」のアドレスには「00H」のデータが格納され、続く「4003H」のアドレスには「2AH」のデータが格納されている。

40

#### 【0419】

行2701の「D I」命令は、遊技制御装置メイン処理(図25)のステップ2501の割込禁止処理に対応し、この命令に対応するコード「F3H」の値がアドレス「4000H」の領域に格納される。

#### 【0420】

行2702の命令は、同じくステップ2502Aの処理に対応し、スタックポインタ(S P)に対応するS Pレジスタ1233に初期アドレスとして「29FFFH」を設定する。

#### 【0421】

50

行2703の命令は、同じくステップ2502Bの処理に対応し、Kレジスタ1230に、上位アドレスのデフォルトの初期値「28H」を設定する。このように、Kレジスタ1230に予め「28H」を設定しておくことによって、「28H」を上位バイトとし、さらに任意の1バイトの値で示される値を下位バイトとして合成した2バイトの値をアドレスと見なして、そのアドレスの領域に記憶されている値を所定のレジスタに設定することができる。例えば、「2803H」のアドレスに記憶された値をAレジスタ1202Aに設定したい場合には、「LDKA,(03H)」という命令を実行すればよい。こうすることによって、2バイトのアドレスの全てを直接指定する場合よりもコード量を1バイト分削減することができる。特に、特定の領域を指定する頻度が大きいほど削減されるコード量を大きくすることができる。本実施形態では、例えば、変動表示ゲームが実行されるたびにシフトされ、アクセス頻度の多い始動記憶を格納するアドレスを指定する場合に使用される。また、Kレジスタを有効に活用するために、これらの始動記憶の上位アドレスは「28H」となるように配置されている。10

#### 【0422】

なお、ユーザプログラムROM103の「4000H」のアドレスは、前述のように、リセットアドレスである。よって、リセット信号の発生時には、まず、この「4000H」に配置されたコードの命令が実行され、その後は、以降のアドレスに配置された命令が順次実行される。

#### 【0423】

ちなみに、リセット信号が発生すると、初期値設定回路1241によってKレジスタ1230に「28H」がハード的に設定されるので、行2703の命令は、省略（言い換えれば、図25のステップ2502Bを省略）することも可能である。ただし、初期値設定回路1241が機能せずに、プログラムカウンタ1234の値のみがリセットアドレスの値に変更される事態を想定するのであれば、行2703の命令を配置しておくことにも意味がある。20

#### 【0424】

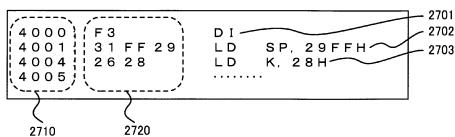

図28は、本発明の第1の実施の形態のディレイ処理を説明する図である。

#### 【0425】

図28に示すディレイ処理は、図25のステップ2505で実行されるが、当該ディレイ処理を実行している時点では、ユーザワークRAM104の値が更新できないようにRAM書き禁止状態となっている。これは、直前の停電発生時に格納されたチェックサムと、電源投入直後となる現時点でのチェックサムとの照合を行うためである。30

#### 【0426】

このため、図25に示すステップ2505におけるディレイ処理では、正当性の判定が行われる記憶領域が含まれたユーザワークRAM104を用いずに、他の記憶領域（正当性判定の対象とならない判定対象外記憶領域）を用いてディレイ処理を実行しなければならない。そこで、本実施形態のディレイ処理は、CPUコア102に備わるレジスタ（汎用レジスタ）を用いて実行される。

#### 【0427】

以下に、判定対象外記憶領域を含むユーザワークRAM104の記憶領域をまったく利用せずに、レジスタを用いたディレイ処理を説明する。なお、CPUコア102として、Z80系のCPUを用いるものとするので、Z80系のCPUで使用されるレジスタ及びアセンブリ言語を用いて説明を行う。40

#### 【0428】

なお、図28における列2810は、図27の列2710同様に遊技制御プログラムが格納されているユーザプログラムROM103のアドレスを示し、列2820は、図27の列2720同様に、当該アドレスに格納されているデータを示している。

#### 【0429】