(12)发明专利

(10)授权公告号 CN 106992113 B

(45)授权公告日 2020.03.03

(21)申请号 201710009776.3

(51)Int.CI.

(22)申请日 2017.01.06

H01L 21/02(2006.01)

(65)同一申请的已公布的文献号

H01L 23/544(2006.01)

申请公布号 CN 106992113 A

(56)对比文件

(43)申请公布日 2017.07.28

JP 2003045788 A, 2003.02.14, 全文.

(30)优先权数据

US 2004129940 A1, 2004.07.08, 全文.

10-2016-0002779 2016.01.08 KR

CN 103854991 A, 2014.06.11, 全文.

(73)专利权人 三星电子株式会社

审查员 周忠饶

地址 韩国京畿道

(72)发明人 金钟洙 崔三宗 金秀莲 具泰亨

权利要求书2页 说明书7页 附图5页

朱炫姬 金清俊 俞智原

(74)专利代理机构 北京市柳沈律师事务所

11105

代理人 屈玉华

(54)发明名称

半导体晶片、半导体结构及制造半导体晶片的方法

(57)摘要

本发明公开了半导体晶片、半导体结构及制造半导体晶片的方法。该半导体晶片包括：包含彼此相对的第一和第二表面的主体；包含在外周上的凹陷的凹口；沿主体的外周形成的第一倒角区域，第一倒角区域包括第一斜坡，第一斜坡连接第一和第二表面并且相对于从第一表面和第一斜坡交汇的第一点到第二表面和第一斜坡交汇的第二点延伸的直线具有第一高度；以及与凹陷或开口接触的第二倒角区域，第二倒角区域包括第二斜坡，第二斜坡连接第一和第二表面并且相对于从第一表面和第二斜坡交汇的第三点到第二表面和第二斜坡交汇的第四点延伸的直线具有不同于第一高度的第二高度。

1. 一种制造半导体晶片的方法,所述方法包括:

提供半导体晶片,所述半导体晶片包括彼此相对的第一表面和第二表面以及在所述半导体晶片的外周上的凹口,所述凹口包括朝向所述半导体晶片的中心部分的在所述外周上的凹陷;

通过处理所述半导体晶片的所述外周形成第一倒角区域,所述第一倒角区域包括连接所述第一表面和所述第二表面的第一斜坡,所述第一斜坡相对于从第一点到第二点延伸的直线具有第一高度,所述第一点是所述第一表面和所述第一斜坡交汇的点,所述第二点是所述第二表面和所述第一斜坡交汇的点;以及

通过处理所述凹口形成第二倒角区域,所述第二倒角区域形成在所述凹口中以接触所述凹陷并且被连接到沿所述半导体晶片的所述外周形成的所述第一倒角区域,所述第二倒角区域包括连接所述第一表面和所述第二表面的第二斜坡,所述第二斜坡相对于从第三点到第四点延伸的直线具有不同于所述第一高度的第二高度,所述第三点是所述第一表面和所述第二斜坡交汇的点,以及所述第四点是所述第二表面和所述第二斜坡交汇的点。

2. 如权利要求1所述的方法,其中所述第二高度小于所述第一高度。

3. 如权利要求1所述的方法,其中所述半导体晶片的主体的厚度是所述第二高度的至少三倍大。

4. 如权利要求1所述的方法,其中所述凹陷的深度是0.4微米到1.0微米。

5. 如权利要求1所述的方法,其中形成所述第二倒角区域包括:

使用具有第一网格的抛光表面的棘轮对所述凹口进行第一磨削;以及

使用具有第二网格的抛光表面的棘轮对所述凹口进行第二磨削,所述第二网格大于所述第一网格。

6. 如权利要求5所述的方法,其中所述第二网格包括2000个网格到10000个网格。

7. 如权利要求1所述的方法,还包括:

在形成所述第二倒角区域之后通过在所述半导体晶片上执行热处理而检查所述半导体晶片是否有缺陷,所述检查包括:

在第一温度下在所述半导体晶片上执行所述热处理;以及

在第二温度下在所述半导体晶片上执行所述热处理,所述第二温度大于所述第一温度。

8. 如权利要求7所述的方法,其中所述第一温度在1000℃和1150℃之间。

9. 如权利要求7所述的方法,其中所述检查还包括:

在所述第一温度下在所述半导体晶片上执行所述热处理之前,在所述半导体晶片上形成外延层。

10. 一种半导体晶片,包括:

包含彼此相对的第一表面和第二表面的主体;

在所述半导体晶片的外周上的凹口,所述凹口包括朝向所述半导体晶片的中心部分的在所述外周上的凹陷;

沿所述主体的所述外周的第一倒角区域,所述第一倒角区域包括连接所述第一表面和所述第二表面的第一斜坡,所述第一斜坡相对于从第一点到第二点延伸的直线具有第一高度,所述第一点是所述第一表面和所述第一斜坡交汇的点,以及所述第二点是所述第二表

面和所述第一斜坡交汇的点；以及

第二倒角区域，形成在所述凹口中以与所述凹陷接触并且被连接到沿所述半导体晶片的所述外周形成的所述第一倒角区域，所述第二倒角区域包括连接所述第一表面和所述第二表面的第二斜坡，所述第二倒角区域相对于从第三点到第四点延伸的直线具有不同于所述第一高度的第二高度，所述第三点是所述第一表面和所述第二斜坡交汇的点，所述第四点是所述第二表面和所述第二斜坡交汇的点。

11. 如权利要求10所述的半导体晶片，其中所述主体包括芯片形成区域以及围绕所述芯片形成区域的边缘区域，所述凹口在所述边缘区域中。

12. 如权利要求10所述的半导体晶片，其中所述第二高度小于所述第一高度。

13. 如权利要求10所述的半导体晶片，其中所述主体的厚度是所述第二高度的至少三倍。

14. 如权利要求10所述的半导体晶片，其中所述凹陷的深度是0.4微米到1.0微米。

15. 如权利要求10所述的半导体晶片，其中在垂直于所述主体的所述第一表面的视图中，所述凹口的一端具有弯曲形状。

16. 一种制造半导体晶片的方法，所述半导体晶片包括彼此相对的第一表面和第二表面以及在所述半导体晶片的外周上的凹口，所述方法包括：

对所述半导体晶片的所述外周进行第一处理以形成第一倒角区域，所述第一倒角区域在所述第一表面和所述第二表面之间的第一斜坡处被凸出地倒角，所述第一倒角区域相对于所述第一倒角区域的起点在它的最高点处具有第一高度；以及

对所述凹口进行第二处理以形成第二倒角区域，所述第二倒角区域形成在所述凹口中并且被连接到沿所述半导体晶片的所述外周形成的所述第一倒角区域，所述第二倒角区域具有在所述第一表面和所述第二表面之间的第二斜坡，所述第二斜坡相对于所述第二倒角区域的起点在它的最高点处具有第二高度，所述第二高度不同于所述第一高度。

17. 如权利要求16所述的方法，其中所述第二处理包括使用不同网格磨削所述凹口。

18. 如权利要求17所述的方法，其中所述第二处理包括：

使用具有第一网格的抛光表面磨削所述凹口；以及

使用具有第二网格的抛光表面磨削所述凹口，所述第二网格大于所述第一网格。

19. 如权利要求16所述的方法，还包括：

对所述半导体晶片进行第一加热至第一温度；

对所述半导体晶片进行第二加热至第二温度，所述第二温度高于所述第一温度；以及在所述第二加热之后检查所述半导体晶片是否有缺陷。

20. 如权利要求19所述的方法，还包括：

在所述第一加热之前在所述半导体晶片上形成外延层。

## 半导体晶片、半导体结构及制造半导体晶片的方法

### 技术领域

[0001] 本发明构思的示例实施方式涉及半导体晶片、半导体结构和/或制造半导体晶片的方法。

### 背景技术

[0002] 由于关于半导体电路的微加工和复杂化,制造半导体器件的工艺可以在相对高的温度下被执行,这会导致在它的设计规则上的减少。当工艺温度增加时,大量的热可以被施加到半导体晶片上,并且因此半导体晶片可以被损坏。

[0003] 同时,凹口可以主要被用于指示具有300微米或更大的直径的半导体晶片的晶向,并且凹口可以被用于在半导体制造工艺过程中对准半导体晶片。

### 发明内容

[0004] 本发明构思的示例实施方式提供配置为在高温工艺过程中减小(或替代地,消除)出现在凹口上的损坏的半导体晶片、包括半导体晶片的半导体结构以及制造半导体晶片的方法。

[0005] 根据本发明构思的一示例实施方式,此处提供制造半导体晶片的方法,该方法包括:准备半导体晶片,半导体晶片包括彼此相对的第一和第二表面以及在半导体晶片的外周上的凹口,凹口包括朝向半导体晶片的中心部分的在外周上的凹陷;通过处理半导体晶片的外周形成第一倒角区域,第一倒角区域包括连接第一和第二表面的第一斜坡,第一斜坡相对于从第一点到第二点延伸的直线具有第一高度,第一点是第一表面和第一斜坡交汇的点,并且第二点是第二表面和第一斜坡交汇的点;以及通过处理凹口形成第二倒角区域,第二倒角区域接触凹陷,第二倒角区域包括连接第一和第二表面的第二斜坡,第二斜坡相对于从第三点到第四点延伸的直线具有不同于第一高度的第二高度,第三点是第一表面和第二斜坡交汇的点,并且第四点是第二表面和第二斜坡交汇的点。

[0006] 根据本发明构思的另一示例实施方式,此处提供半导体晶片,包括:包含彼此相对的第一和第二表面的主体;在半导体晶片的外周上的凹口,凹口包括朝向半导体晶片的中心部分的在外周上的凹陷;沿主体的外周的第一倒角区域,第一倒角区域包括连接第一和第二表面的第一斜坡,第一斜坡相对于从第一点到第二点延伸的直线具有第一高度,第一点是第一表面和第一斜坡交汇的点,并且第二点是第二表面和第一斜坡交汇的点;以及与凹陷接触的第二倒角区域,第二倒角区域包括连接第一和第二表面的第二斜坡,第二倒角区域相对于从第三点到第四点延伸的直线具有不同于第一高度的第二高度,第三点是第一表面和第二斜坡交汇的点,第四点是第二表面和第二斜坡交汇的点。

[0007] 根据本发明构思的另一示例实施方式,此处提供包括具有彼此相对的第一和第二表面的半导体晶片的半导体结构,半导体晶片包括:芯片形成区域,以及围绕芯片形成区域的边缘区域;布置在芯片形成区域中的半导体芯片;在半导体晶片的外周上的凹口,凹口包括朝向半导体晶片的中心部分的在外周上的凹陷;沿半导体晶片的外周的第一倒角区域,

第一倒角区域具有连接第一和第二表面的第一斜坡，并且第一倒角区域相对于从第一点到第二点延伸的直线具有第一高度，第一点是第一表面和第一斜坡交汇的点，第二点是第二表面和第一斜坡交汇的点；以及具有连接第一和第二表面的第二斜坡的第二倒角区域，并且第二倒角区域相对于从第三点到第四点延伸的直线具有不同于第一高度的第二高度，第三点是第一表面和第二斜坡交汇的点，并且第四点是第二表面和第二斜坡交汇的点。

[0008] 根据本发明构思的另一示例实施方式，此处提供制造半导体晶片的方法，半导体晶片包括彼此相对的第一和第二表面以及在半导体晶片的外周上的凹口。该方法包括：对半导体晶片的外周进行第一处理以形成第一倒角区域，第一倒角区域在第一和第二表面之间的第一斜坡处被凸出地倒角，第一倒角区域相对于第一倒角区域的起点在它的最高点处具有第一高度；以及对凹口进行第二处理以形成第二倒角区域，第二倒角区域接触凹陷，第二倒角区域在第一和第二表面之间具有第二斜坡，第二斜坡相对于第二倒角区域的起点在它的最高点处具有第二高度，第二高度不同于第一高度。

## 附图说明

- [0009] 由以下结合附图的详细描述，本发明构思的示例实施方式将更加容易理解，其中：

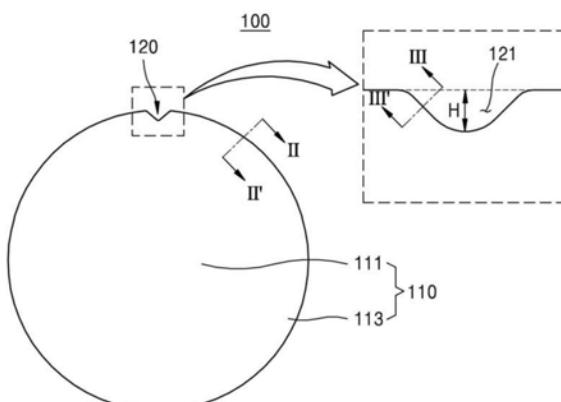

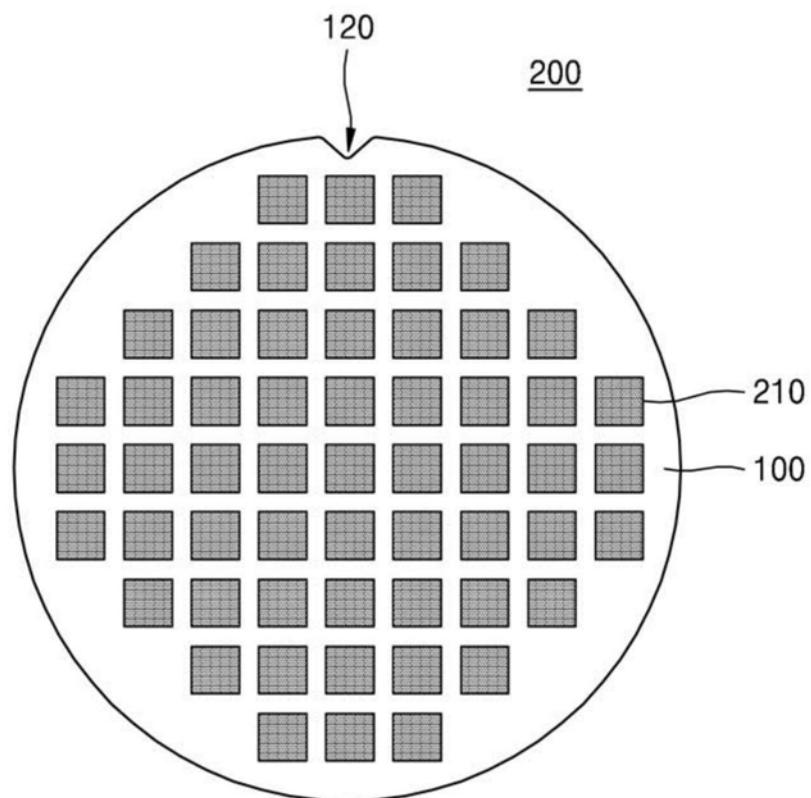

- [0010] 图1是示出根据一示例实施方式的半导体晶片的平面图；

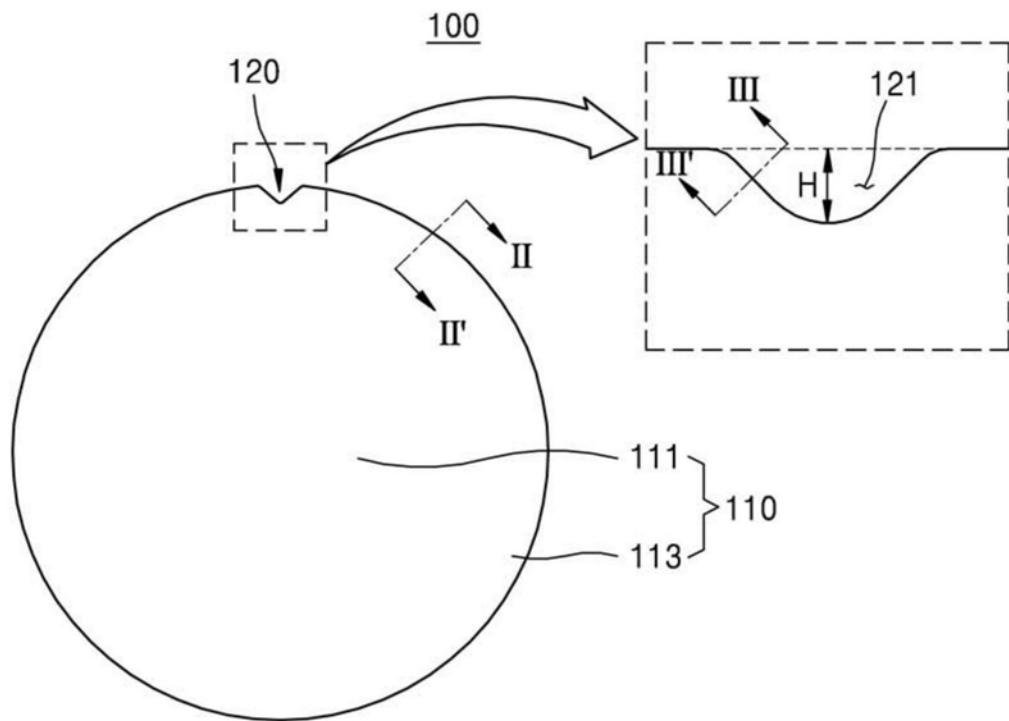

- [0011] 图2是示出沿线II-II'截取的图1的半导体晶片的截面图；以及

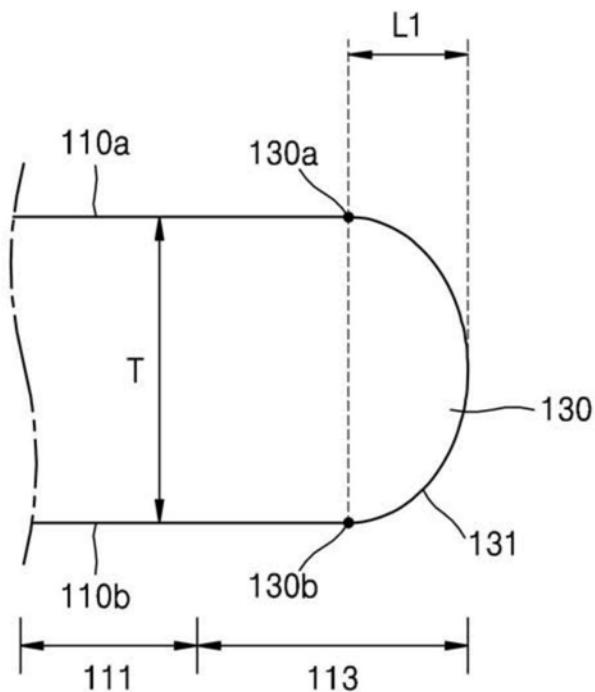

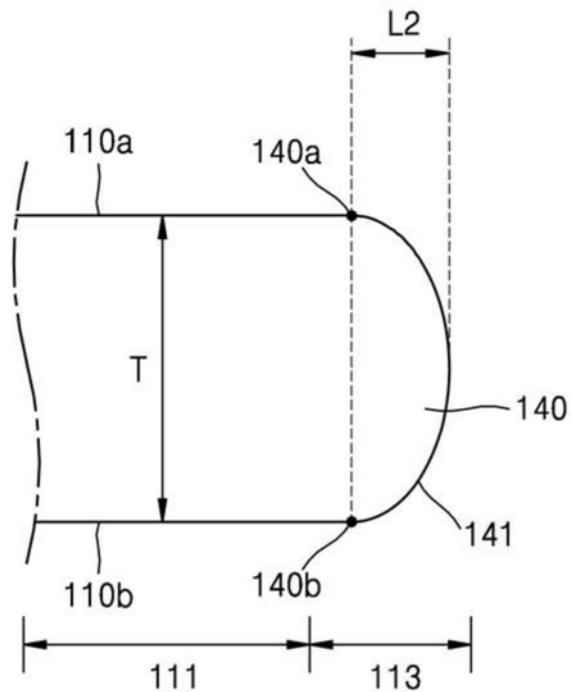

- [0012] 图3是示出沿线III-III'截取的图1的半导体晶片的截面图；

- [0013] 图4是示出根据一示例实施方式的半导体结构的平面图；

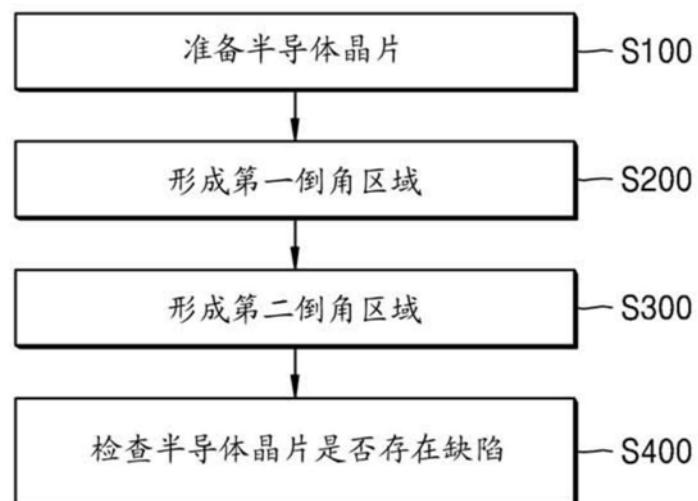

- [0014] 图5是根据一示例实施方式的制造半导体晶片的方法的流程图；

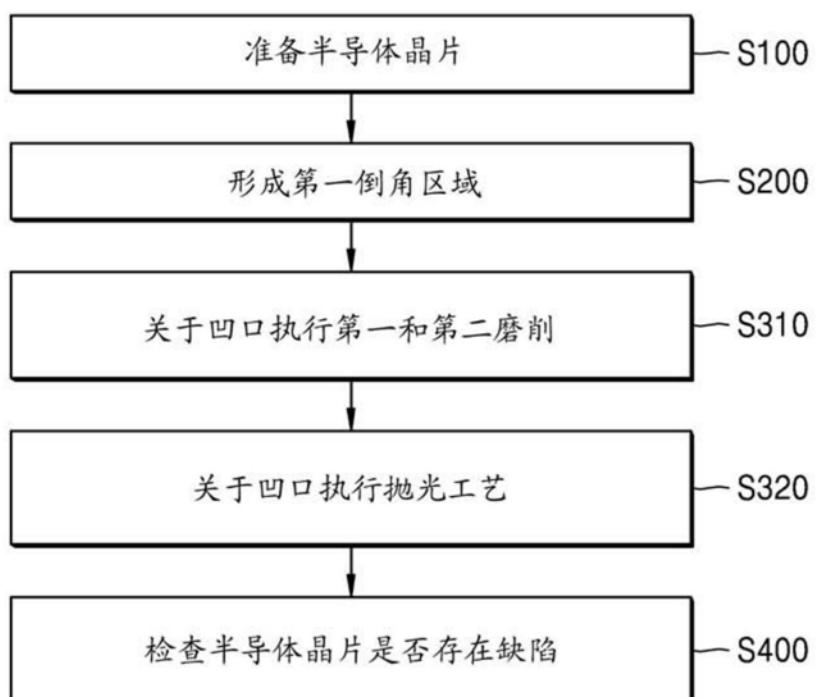

- [0015] 图6是根据一示例实施方式的制造半导体晶片的方法的流程图；

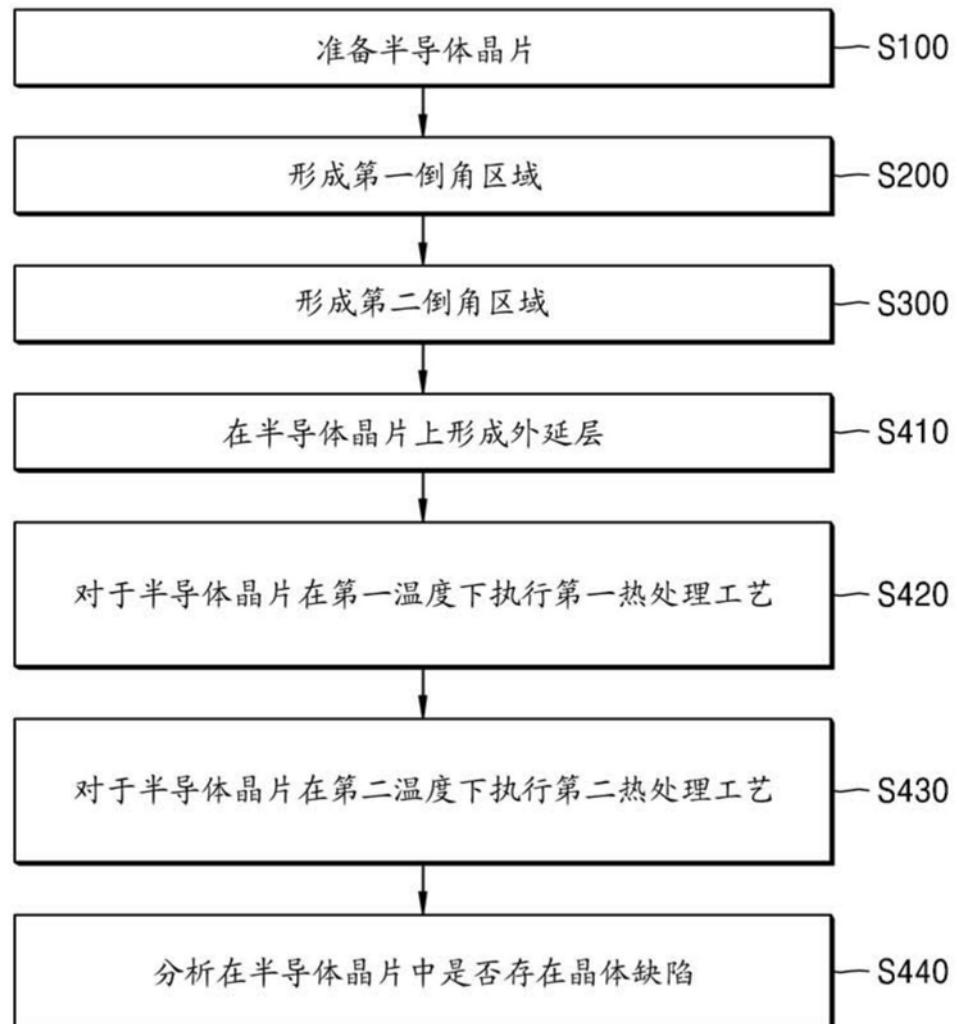

- [0016] 图7是示出根据一示例实施方式的制造半导体晶片的方法的流程图；及

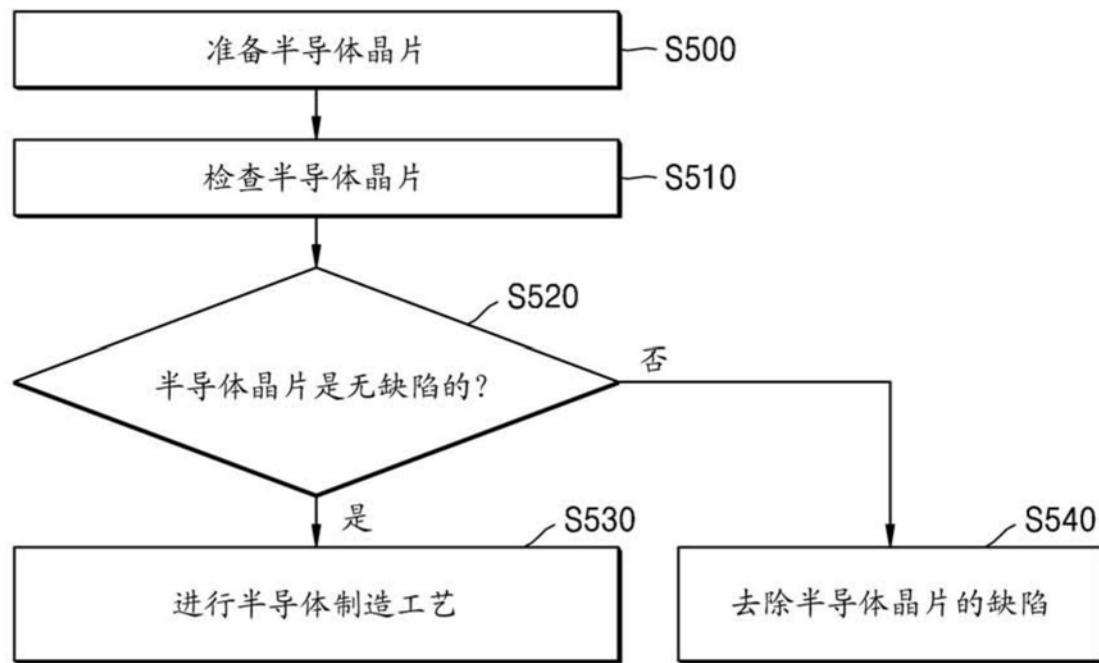

- [0017] 图8是根据一示例实施方式的制造半导体器件的方法的流程图。

## 具体实施方式

[0018] 图1是示出根据本公开的一实施方式的半导体晶片100的平面图。图2是示出沿线II-II'截取的图1的半导体晶片100的截面图。图3是示出沿线III-III'截取的图1的半导体晶片100的截面图。

[0019] 参考图1到3，半导体晶片100可以包括主体100、凹口120以及第一和第二倒角(bevel)区域130和140。

[0020] 半导体晶片100可以是硅晶片，或者可以包括诸如锗(Ge)的半导体元素或者诸如碳化硅(SiC)、砷化镓(GaAs)、砷化铟(InAs)以及磷化铟(InP)的化合物半导体。此外，半导体晶片100可以是绝缘体上硅。

[0021] 主体110可以确定半导体晶片100的整体形状。主体110可以包括无源器件、有源器件或集成电路在其中被形成的芯片形成区域111，以及围绕芯片形成区域111的边缘区域113。主体110可以包括彼此相对且基本彼此平行的第一和第二表面110a和110b。主体110可以具有某一厚度(例如在主体110的第一表面110a和第二表面110b之间的距离)。

[0022] 凹口120可以被用于包括半导体晶片100的晶向并且可以被形成在主体110的边缘区域113中。凹口120可以包括在从主体110的外周向主体110的中心部分的方向上形成至某

一深度的凹陷或开口121。凹陷或开口121可以在半导体晶片100的厚度方向上延伸。

[0023] 凹口120可以被形成在半导体晶片100中以在半导体制造工艺过程中对准半导体晶片100。例如,在被安装到可旋转支撑装置之后,半导体晶片100可以通过旋转半导体晶片100并且由诸如激光传感器的探测传感器探测凹口120而被对准。

[0024] 此外,如图1所示,在垂直于主体110的第一表面110a的视图中,凹口120可以包括具有弯曲形状(例如“U”形)的一端。例如,凹陷或开口121与主体110的接触部分可以在垂直于主体110的第一表面110a的方向上形成弯曲形状。

[0025] 然而,示例实施方式不限于此。例如,不同于图1,在垂直于主体110的第一表面110a的视图中,凹口120可以包括具有尖锐形状,例如“V”形的一端。例如,凹陷或开口121与主体110的接触部分可以在垂直于主体110的第一表面110a的方向上形成“V”形。

[0026] 根据示例实施方式,凹陷或开口121的从主体110的外周向主体110的中心部分的深度H可以是约0.4微米到约1.0微米。凹陷或开口121的在垂直于第一表面110a的方向上的深度H可以表示从主体110的外周延伸到最接近主体110的中心部分的距离。凹陷或开口121的深度H可以是凹口120的深度。当凹陷或开口121的深度H小于约0.4微米时,诸如激光传感器的探测传感器可能不精确地探测凹口120,并且因此半导体晶片100可能不被对准。

[0027] 此外,凹陷或开口121的深度H可以是约1.0微米或更小以便于减小对凹口120或邻近于凹口120的区域的损坏。由于半导体电路的微制造和复杂化,在制造半导体器件的工艺中的温度和/或压力可以增加,其可以导致在它的设计规则上的减少以及在关于制造工艺的要求上的增加。

[0028] 工艺的高温度和/或高压力可以损坏凹口120以及邻近于凹口120的区域,并且结果半导体制造工艺的产量可以被减少。因此,需要凹口120具有小于某一水平的尺寸以减小对凹口120的损坏。根据一些示例实施方式,在半导体制造工艺过程中凹口120或邻近于凹口120的区域的缺陷可以通过将凹陷或开口121的深度H减小到1.0微米或更小而被减少。

[0029] 在主体110的边缘区域113中的第一倒角区域130可以沿主体110的外周形成。第一倒角区域130可以包括连接主体110的第一和第二表面110a和110b的第一斜坡(slope)131。第一斜坡131可以具有凸形。

[0030] 相对于从第一表面110a和第一斜坡131交汇的在图2的截面图中的第一点130a到第二表面110b和第一斜坡131交汇的在图2的截面图中的第二点130b延伸的直线,第一倒角区域130在半导体晶片100的径向方向上可以具有第一高度L1。第一高度L1可以是倒角长度。

[0031] 换言之,半导体晶片100的厚度可以从第一点130a和第二点130b被减小,并且相对于连接第一点130a和第二点130b的直线作为参考,半导体晶片100的厚度可以在半导体晶片100的径向方向上被减小。半导体晶片100的厚度可以随着第一倒角区域130相对于连接第一点130a和第二点130b的直线的高度的增加而被减小。如图2所示,芯片形成区域111和边缘区域113的边界可以与第一斜坡131开始的第一点130a或第二点130b间隔开。然而,不同于图2,芯片形成区域111和边缘区域113的边界可以与第一点130a或第二点130b几乎相同。

[0032] 从半导体晶片100的中心到第一倒角区域130的高度是第一高度L1的点的距离可以是半导体晶片100的径向长度。

[0033] 例如,通过执行单晶锭切片工艺,半导体晶片100在第一倒角区域130中可以具有某一厚度,并且由于第一倒角区域130,半导体晶片100的拐角可以是倒圆的。此外,由于第一倒角区域130,半导体晶片100的尖锐边缘可以是倒圆的,并且因此在以下制造半导体晶片100或半导体器件的工艺中,可以防止半导体晶片100被损坏。

[0034] 同时,参考图3,第二倒角区域140可以沿由凹陷或开口121提供的凹口120的一端形成在凹口120中。第二倒角区域140可以包括连接主体110的第一表面110a和第二表面110b的第二斜坡141,其中第二斜坡141可以具有凸形。第二斜坡141可以具有不同于第一倒角区域130中提供的第一斜坡131的轮廓。

[0035] 相对于从第一表面110a和第二斜坡141交汇的在图3的截面图中的第三点140a到第二表面110b和第二斜坡141交汇的在图3的截面图中的第四点140b延伸的直线,第二倒角区域140从主体110在凹陷或开口121的方向上可以具有第二高度L2。第二高度L2可以是倒角长度。第二倒角区域140的第二高度L2可以不同于第一倒角区域130的第一高度L1。

[0036] 换言之,半导体晶片100的厚度可以从第三点140a和第四点140b被减小,并且以连接第三点140a和第四点140b的直线作为参考,半导体晶片100的厚度可以在从主体110向凹陷或开口121的方向上被减小。半导体晶片100的厚度可以随着第二倒角区域140相对于连接第三点140a和第四点140b的直线作为参考的高度的增加而被减小。

[0037] 如图3所示,芯片形成区域111和边缘区域113的边界可以与第二斜坡132开始的第三点140a或第四点140b间隔开。然而,不同于图3,芯片形成区域111和边缘区域113的边界可以与第三点140a或第四点140b几乎相同。

[0038] 例如,第二倒角区域140可以通过在凹口120上执行磨削工艺和抛光工艺而形成。由于第二倒角区域140,由凹陷或开口121提供的凹口120的一端可以被倒圆,并且因此在半导体制造工艺过程中可以防止凹口120被损坏。

[0039] 此外,在凹口120中形成的第二倒角区域140可以被连接到沿半导体晶片100的外周形成的第一倒角区域130。在第一和第二倒角区域130和140彼此相邻的部分,第一倒角区域130的高度可以从第一高度L1变为第二高度L2并且第二倒角区域140的高度可以从第二高度L2变为第一高度L1。例如,在第一和第二倒角区域130和140彼此相邻的部分,第一倒角区域130或第二倒角区域140的高度可以在第一高度L1和第二高度L2之间。

[0040] 在一些示例实施方式中,第二倒角区域140的第二高度L2可以小于第一倒角区域130的第一高度L1。例如,第二倒角区域140的第二高度L2可以小于第一倒角区域130的第一高度L1的约90%。如图2和3所示,关于垂直于主体110的第一表面110a的剖面比较第一倒角区域130和第二倒角区域140,第二倒角区域140的一端可以具有几乎垂直于第一倒角区域130的轮廓。因此,在制造半导体晶片100或半导体器件的工艺过程中产生的在凹口120中的碎片可以被减少。

[0041] 此外,在一些示例实施方式中,主体110的厚度T也就是第一和第二表面110a和110b之间的距离可以与第二倒角区域140的第二高度L2的三倍或更多倍一样大。例如,直径约300毫米的半导体晶片可以具有约775微米的厚度,并且第二倒角区域140的第二高度L2可以是250微米或更小。

[0042] 图4是根据本公开的一示例实施方式的半导体结构200的平面图。

[0043] 参考图4,半导体结构200可以包括半导体晶片100、形成在半导体晶片100的边缘

上的凹口120、(图2的)第一倒角区域130、(图3的)第二倒角区域140以及形成在半导体晶片100的表面上的半导体芯片210。半导体晶片100、凹口120、第一倒角区域130以及第二倒角区域140与图1至3中描述的基本相同，并且因此为了描述的方便，其详细描述将不被给出。

[0044] 除半导体晶片100的外部区域的一部分之外，半导体芯片210可以被布置在半导体晶片100的整个表面上。例如，半导体芯片210可以被形成在半导体晶片100的(图1的)芯片形成区域111中。半导体芯片210中的每个可以包括集成电路。例如，集成电路可以包括存储电路或逻辑电路。此外，半导体芯片210可以包括各种类型的单独器件。单独器件可以包括多种微电子元件，例如诸如互补金属氧化物半导体(CMOS)晶体管的金属氧化物半导体场效应晶体管(MOSFET)、诸如系统大规模集成(LSI)或CMOS图像传感器(CIS)的图像传感器、微机电系统(MEMS)、有源器件以及无源器件。

[0045] 图5是根据一示例实施方式的制造半导体晶片100的方法的流程图。

[0046] 结合图1至3参考图5，在操作S100中，可以提供半导体晶片100。半导体晶片100可以包括彼此相对的第一和第二表面110a和110b。包括从半导体晶片100的外周向半导体晶片100的中心部分形成的凹陷或开口121的凹口120可以被包括在半导体晶片100的外周中。

[0047] 例如，半导体晶片100可以是硅晶片并且半导体晶片100可以通过形成单晶锭并且以某一厚度切片单晶锭而提供。详细地，单晶锭可以通过融化高纯度多晶硅，将单晶籽晶接触到处于液态的多晶硅并且缓慢提起籽晶而形成。此后，通过切割单晶锭的两端以及通过磨削单晶锭的侧表面，凹口120可以沿单晶锭的长度方向形成。此后，单晶锭可以通过切片被切割为某一厚度。

[0048] 然后，在操作S200中，第一倒角区域130可以被形成在半导体晶片100的边缘上。第一倒角区域130可以沿半导体晶片100的除凹口120外的外周形成。第一倒角区域130可以通过倒圆半导体晶片100的外周的拐角而形成。

[0049] 第一倒角区域130可以包括连接半导体晶片100的第一表面110a和第二表面110b的凸形的第一斜坡131，并且因此可以防止半导体晶片100在半导体制造工艺过程中被损坏。第一倒角区域130可以具有在半导体晶片100的径向方向上的第一高度L1，以从半导体晶片100的第一表面110a和第一斜坡131交汇的第一点130a到半导体晶片100的第二表面110b和第一斜坡131交汇的第二点130b延伸的直线作为参考。

[0050] 在操作S300中，第二倒角区域140可以被形成在凹口120的凹陷或开口121与主体110的接触部分上。例如，第二倒角区域140可以通过在凹口120上执行磨削工艺和/或抛光工艺而形成。第二倒角区域140可以包括通过磨削工艺和抛光工艺连接半导体晶片100的第一表面100a和第二表面100b的凸形的第二斜坡141。第二倒角区域140可以具有在从主体110向凹陷或开口121的方向上的第二高度L2，以从半导体晶片100的第一表面110a和第二斜坡141交汇的第三位置140a到半导体晶片100的第二表面110b和第二斜坡141交汇的第四位置140b延伸的直线作为参考。第二倒角区域140的第二高度L2可以不同于第一倒角区域130的第一高度L1。然后，研磨(lapping)工艺和/或抛光工艺可以被执行以平坦化半导体晶片100的表面并且去除缺陷。

[0051] 在操作S400中，半导体晶片100可以被检查以确定是否存在缺陷。半导体晶片100的检查可以仅在由单晶锭形成的多个半导体晶片100中的一些上被执行。检查可以在关于半导体晶片100的后续工艺之前被执行，并且在后续工艺过程中可以提前确定是否发生缺

陷，并且因此可以防止有缺陷的半导体晶片100被应用于后续工艺中。因此，半导体制造工艺的可靠性和产量可以被改善。

[0052] 图6是根据一示例实施方式的制造半导体晶片100的方法的流程图。

[0053] 参考图6，提供半导体晶片100的操作S100、形成第一倒角区域130的操作S200以及检查半导体晶片100的操作S400与图5中描述的基本相同，并且因此为了描述的方便，其详细描述将不被给出。

[0054] 在下文中，形成第二倒角区域140的操作S310和S320将参考图1至3和6被详细描述。

[0055] 在操作S310中，可以对于凹口120执行第一和第二磨削。

[0056] 第一磨削可以通过使用具有第一网格的抛光表面的棘轮(notch wheel)执行，例如其中棘轮可以通过使用用于抛光金刚石的800个网格(mesh)的颗粒(particle)来抛光凹口120。

[0057] 然后，第二磨削可以通过使用具有比于第一网格更大的第二网格的抛光表面的棘轮执行。例如，第二网格可以是2000个网格或更多，更详细地，可以是约2000个网格到约10000个网格。在本公开的实施方式中，在凹口120上的损坏可以通过使用用于凹口120的第二磨削的细颗粒而减小，并且因此在高温半导体制造工艺过程中凹口120可以不被损坏。

[0058] 在操作S320中，第二倒角区域140可以通过执行抛光工艺形成在凹口120中。凹口120的表面可以通过抛光工艺被平坦化并且凹口120中的缺陷可以通过磨削工艺被去除。

[0059] 图7是根据一示例实施方式的制造半导体晶片100的方法的流程图。

[0060] 参考图7，提供半导体晶片100的操作S100、形成第一倒角区域130的操作S200以及形成第二倒角区域140的操作S300可以与图5和6中描述的基本相同，并且因此为了描述的方便，其详细描述将不被给出。

[0061] 在下文中，检查半导体晶片100的操作S410至S440将参考图1至3和7被详细描述。

[0062] 在操作S410中，外延层可以被形成在半导体晶片100上。例如，外延层可以具有约4微米的厚度并且可以通过在约1150°C的温度下在反应器中被气相沉积来生长。外延层可以是具有与半导体晶片100相同的晶体结构的单晶层。外延层可以由与半导体晶片100相同的材料或不同的材料形成。外延层可以被形成以容易地检查在半导体晶片100表面上的晶体缺陷。

[0063] 此后，在操作S420中，在第一温度下进行的第一热处理工艺可以对于半导体晶片100执行。第一热处理工艺的第一温度可以低于第二热处理工艺的第二温度并且第一热处理工艺可以进行例如约2到3小时。第一温度可以是1000°C或更高并且小于1150°C。第一热处理工艺可以在低于后续第二热处理工艺的温度的温度下进行，并且可以防止半导体晶片100由于快速温度升高而被损坏。

[0064] 在操作S430中，在第二温度下进行的第二热处理工艺可以对于半导体晶片100执行。第二热处理工艺的第二温度可以在1150°C或更高温度下被执行并且第二热处理工艺可以进行约1小时到2小时。第二热处理工艺可以在比诸如半导体制造工艺的后续工艺中更严格的条件下在半导体晶片100上被执行，并且可以提前测试半导体晶片100来看半导体晶片100是否能承受后续工艺。具体地，第二热处理工艺可以提前测试容易引起晶体缺陷的凹口120和邻近于凹口120的部分。

[0065] 在操作S440中，第二热处理工艺可以分析在半导体晶片100中是否存在晶体缺陷。X射线照相装置可以被用于分析半导体晶片100的晶体缺陷。检查半导体晶片100的操作可以对于单个单元的半导体晶片的被选择的部分进行。有缺陷的半导体晶片100可以通过检查半导体晶片100被提前扫描，并且因为检查工序仅对于无缺陷的半导体晶片100被执行，工艺可靠性可以被改善。

[0066] 图8是根据一示例实施方式的制造半导体器件的方法的流程图。

[0067] 在操作S500中，可以提供半导体晶片。半导体晶片可以是通过图5的操作S100至S300形成的半导体晶片，或者可以是通过图6的操作S100至S320形成的半导体晶片。

[0068] 在操作S510中，半导体晶片可以被检查。检查半导体晶片的操作可以与图7的操作S410至S440相同。

[0069] 在操作S520中，可以基于检查半导体晶片的结果来确定半导体晶片是有缺陷的还是无缺陷的。然后检查半导体晶片的操作可以对于单个单元的多个半导体晶片中的一些进行。

[0070] 在操作S530中，当根据检查结果半导体晶片被确定为无缺陷的时，半导体制造工艺可以被进行。

[0071] 相反，当半导体晶片被确定为有缺陷的时，在操作S540中，检查半导体晶片的操作可以去除半导体晶片的缺陷或抛弃半导体晶片。

[0072] 详细地，半导体制造工艺可以如下文被进行。半导体制造工艺可以包括形成薄膜的操作。薄膜可以由导电材料、绝缘材料或半导体材料形成。半导体制造工艺还可以包括在薄膜上形成掩模图案的操作。掩模图案可以是光致抗蚀剂图案。此外，使用掩模图案作为蚀刻掩模的半导体制造工艺还可以包括通过去除薄膜的一部分而形成图案的操作。此外，使用掩模图案作为蚀刻掩模的半导体制造工艺还可以包括通过去除薄膜的一部分而形成孔的操作。孔可以包括例如接触孔或通路孔。

[0073] 半导体制造工艺还可以包括清洗薄膜的操作。半导体制造工艺还可以包括平坦化薄膜的操作。平坦化薄膜的操作可以包括化学机械抛光(CMP)工艺或回蚀刻工艺。此外，即使描述中未提到，半导体制造工艺可以包括可以在半导体元件制造工艺中被执行的其它操作。因此，半导体制造工艺还可以包括转移或储存半导体晶片的操作。

[0074] 尽管本发明构思的示例实施方式已经参考其示例实施方式被具体示出和描述，但是将理解可以在此进行在形式和细节上的各种改变而不背离所附权利要求的精神和范围。

[0075] 本申请要求享有2016年1月8日在韩国知识产权局提交的韩国专利申请第10-2016-0002779号的权益，其公开通过全文引用合并于此。

图1

图2

图3

图4

图5

图6

图7

图8