(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년01월26일

(11) 등록번호 10-1485917

(24) 등록일자 2015년01월19일

- (51) 국제특허분류(Int. Cl.)

*H03F 1/22* (2006.01) *H03F 3/68* (2006.01)

- (21) 출원번호 10-2013-0132680

- (22) 출원일자 2013년11월04일

심사청구일자 2013년11월04일

- (65) 공개번호 10-2014-0060231

- (43) 공개일자 2014년05월19일

- (30) 우선권주장

JP-P-2012-247144 2012년11월09일 일본(JP)

- (56) 선행기술조사문현

US20040070455 A1\*

- \*는 심사관에 의하여 인용된 문현

- (73) 특허권자

미쓰비시덴키 가부시키가이샤

일본국 도쿄도 지요다구 마루노우치 2쵸메 7반 3

고

- (72) 발명자

미야시타 미요

일본국 도쿄도 지요다구 마루노우치 2쵸메 7반 3

고 미쓰비시덴키 가부시키가이샤 나이

야마모토 카즈야

- (74) 대리인

이화익, 김홍두

전체 청구항 수 : 총 6 항

심사관 : 강현일

(54) 발명의 명칭 캐스코드 앰프

**(57) 요약**

배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있는 캐스코드 앰프를 얻는다. 트랜지스터 Tr1a~Tr1f가 트랜지스터 Tr2a~Tr2f에 각각 캐스코드 접속되어 있다. 배선 Wg1이 트랜지스터 Tr1a~Tr1f의 게이트에 순서대로 접속되어 있다. 병렬로 접속된 배선 Wg2, Wg3가 트랜지스터 Tr2a~Tr2f의 게이트에 순서대로 접속되어 있다. 용량 C1이 배선 Wg2의 일단과 접지점 사이에 접속되어 있다. 용량 C1이 배선 Wg2의 일단과 접지점 사이에 접속되어 있다.

**대 표 도**

(72) 발명자

**키타바야시 후미마사**

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 7반 3고

미쓰비시텐키 가부시키가이샤 나이

**마키 수구루**

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 7반 3고

미쓰비시텐키 가부시키가이샤 나이

---

**후쿠다 에리**

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 7반 3고

미쓰비시텐키 가부시키가이샤 나이

**카토 카쓰야**

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 7반 3고

미쓰비시텐키 가부시키가이샤 나이

## 특허청구의 범위

### 청구항 1

복수의 제1트랜지스터와,

상기 복수의 제1트랜지스터에 각각 캐스코드 접속된 복수의 제2트랜지스터와,

상기 복수의 제1트랜지스터의 제어 단자가 순서대로 연결된 제1 배선과,

상기 복수의 제2트랜지스터의 제어 단자가 순서대로 연결된 제2 배선과,

상기 제2 배선의 일단과 접지점 사이에 접속된 용량을 구비하고,

상기 제1 배선은, 상기 복수의 제1트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제1 배선 저항을 갖으며,

상기 제2 배선은 제2트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제2 배선 저항을 갖고,

상기 제2 배선은 병렬로 접속된 2개 이상의 배선을 갖는 것을 특징으로 하는 캐스코드 앰프.

### 청구항 2

제 1항에 있어서,

상기 제1 배선은 병렬로 접속된 2개 이상의 배선을 갖는 것을 특징으로 하는 캐스코드 앰프.

### 청구항 3

복수의 제1트랜지스터와,

상기 복수의 제1트랜지스터에 각각 캐스코드 접속된 복수의 제2트랜지스터와,

상기 복수의 제1트랜지스터의 제어 단자가 순서대로 연결된 제1 배선과,

상기 복수의 제2트랜지스터의 제어 단자가 순서대로 연결된 제2 배선과,

상기 제2 배선의 일단과 접지점 사이에 접속된 제1용량과,

상기 제2 배선의 타단과 접지점 사이에 접속된 제2용량을 구비하고,

상기 제1 배선은, 상기 복수의 제1트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제1 배선 저항을 갖으며,

상기 제2 배선은, 상기 복수의 제2트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제2 배선 저항을 갖는 것을 특징으로 하는 캐스코드 앰프.

### 청구항 4

복수의 제1트랜지스터와,

상기 복수의 제1트랜지스터에 각각 캐스코드 접속된 복수의 제2트랜지스터와,

상기 복수의 제1트랜지스터의 제어 단자가 순서대로 연결된 제1 배선과,

상기 복수의 제2트랜지스터의 제어 단자가 순서대로 연결된 제2 배선과,

상기 복수의 제2트랜지스터의 상기 제어 단자와 접지점 사이에 각각 접속된 복수의 용량을 구비하고,

상기 제1 배선은, 상기 복수의 제1트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제1 배선 저항을 갖으며,

상기 제2 배선은, 상기 복수의 제2트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제2 배선 저항을 갖는 것을 특징으로 하는 캐스코드 앰프.

## 청구항 5

제 4항에 있어서,

상기 캐스코드 앰프는 차동 앰프인 것을 특징으로 하는 캐스코드 앰프.

## 청구항 6

제 1항 내지 제 5항 중 어느 한 항에 있어서,

상기 복수의 제1트랜지스터 및 상기 복수의 제2트랜지스터는 n채널 MOS 트랜지스터인 것을 특징으로 하는 캐스코드 앰프.

## 명세서

### 기술 분야

[0001]

본 발명은, 주로 휴대전화 등의 이동통신 기기에 사용되는 캐스코드 앰프에 관한 것이다.

### 배경기술

[0002]

현재, CDMA를 비롯한 휴대전화용 전력증폭기에 있어서 저코스트화를 실현하는 한가지 수단으로서, CMOS 프로세스를 사용한 캐스코드 앰프의 개발이 활발히 행해져 왔다(예를 들면, 특허문현 1 참조).

[0003]

도 16은, 캐스코드 앰프의 기본 구성을 나타낸 회로도다. 접선 틀 내부가 캐스코드 앰프이고, 그것 이외는 전력증폭기를 구성하기 위해 필요한 회로 소자이다. 트랜지스터 Tr1, Tr2은 n채널 MOS 트랜지스터로서, 캐스코드 접속되어 있다. 캐스코드 접속된 트랜지스터를 사용한 증폭기를 캐스코드 앰프라고 부른다.

[0004]

트랜지스터 Tr1의 게이트가 입력 정합회로를 거쳐 RF 입력 신호 단자 IN에 접속되고, 또한 게이트 바이어스 단자 Vg1에 접속되어 있다. 트랜지스터 Tr1의 소스는 접지되어 있다. 즉, 트랜지스터 Tr1은 소스 접지 트랜지스터이다.

[0005]

트랜지스터 Tr2의 게이트가 용량 C1을 거쳐 접지되고, 또한 게이트 바이어스 단자 Vg2에 접속되어 있다. 즉, 트랜지스터 Tr2은 게이트 접지 트랜지스터이다. 트랜지스터 Tr2의 소스가 트랜지스터 Tr1의 드레인에 접속되어 있다. 트랜지스터 Tr2의 드레인은 선로 L1을 거쳐 캐스코드 앰프의 드레인 전원단자 Vd에 접속되고, 또한 출력 정합회로를 거쳐 RF 출력 신호 단자 OUT에 접속되어 있다. 선로 L1은 특정한 전기 길이를 갖고 인덕터로서 작용한다.

### 선행기술문헌

#### 특허문현

[0006]

(특허문현 0001) 일본국 특개평 5-259765호 공보

### 발명의 내용

### 해결하려는 과제

[0007]

전력증폭기를 구성하는 캐스코드 앰프의 트랜지스터는, 게이트 폭이 크고, 복수의 셀로 분할된다. 이 경우, 각 셀의 게이트 접지 트랜지스터의 게이트는 게이트 배선에 의해 접속되고, 그 게이트 배선의 일단과 접지점 사이에 용량이 접속된다. 그러나, 게이트 배선의 배선 저항이 게이트 폭(트랜지스터 사이즈)의 확대와 함께 커지기 때문에, 게이트 폭을 확대해도 출력 전력이 증가하지 않는다고 하는 문제가 있었다.

[0008]

본 발명은, 전술한 것과 같은 과제를 해결하기 위해 이루어진 것으로서, 그 목적은 배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있는 캐스코드 앰프를 얻는 것이다.

### 과제의 해결 수단

[0009]

본 발명에 관한 캐스코드 앰프는, 복수의 제1트랜지스터와, 상기 복수의 제1트랜지스터에 각각 캐스코드 접속된 복수의 제2트랜지스터와, 상기 복수의 제1트랜지스터의 제어 단자가 순서대로 연결된 제1 배선과, 상기 복수의 제2트랜지스터의 제어 단자가 순서대로 연결된 제2 배선과, 상기 제2 배선의 일단과 접지점 사이에 접속된 용량을 구비하고, 상기 제1 배선은, 상기 복수의 제1트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제1 배선 저항을 갖으며, 상기 제2 배선은, 상기 복수의 제2트랜지스터의 제어 단자 사이에 각각 접속되고, 또한 서로 직렬로 접속된 복수의 제2 배선 저항을 갖고, 상기 제2 배선은 병렬로 접속된 2개 이상의 배선을 갖는 것을 특징으로 한다.

### 발명의 효과

[0010]

본 발명에 의해, 배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있다.

### 도면의 간단한 설명

[0011]

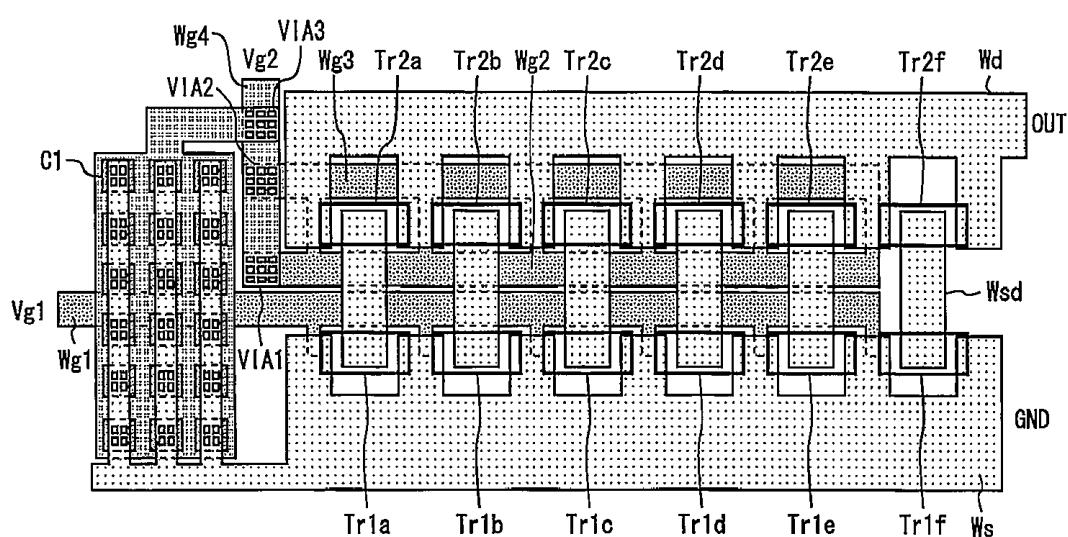

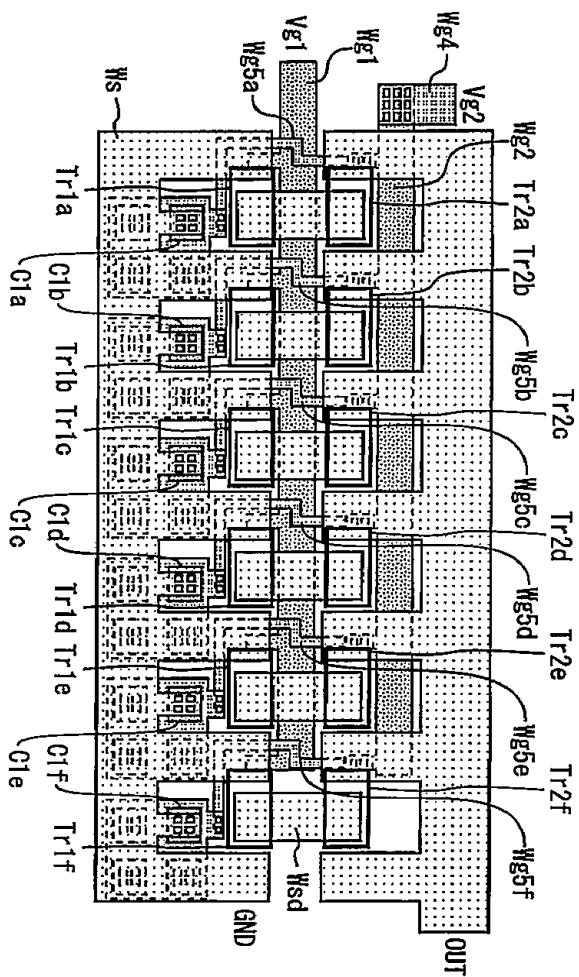

도 1은 본 발명의 실시형태 1에 관한 캐스코드 앰프를 나타낸 평면도다.

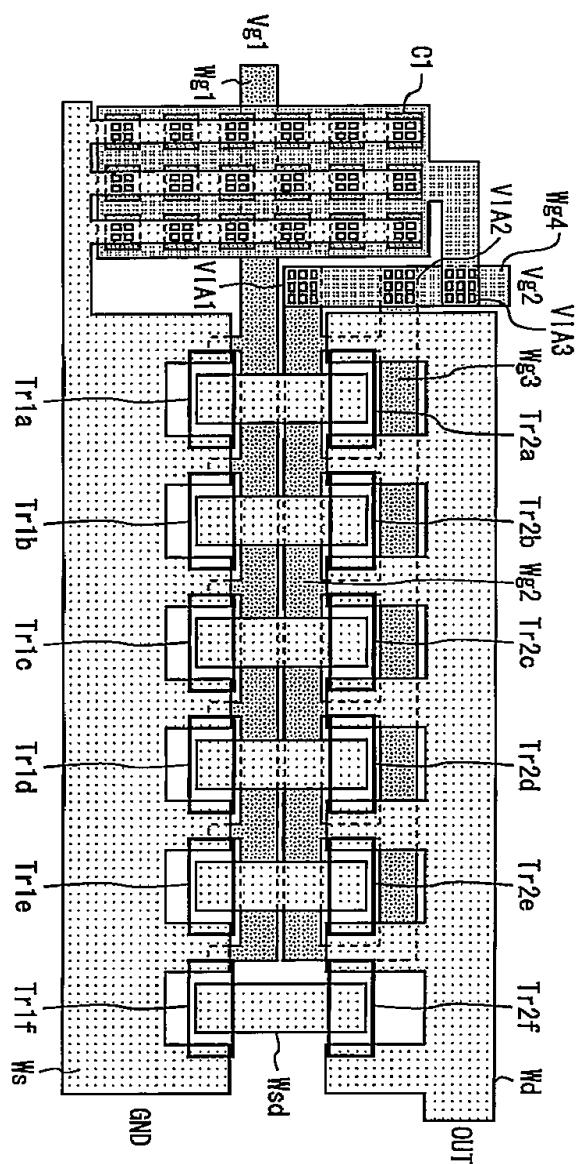

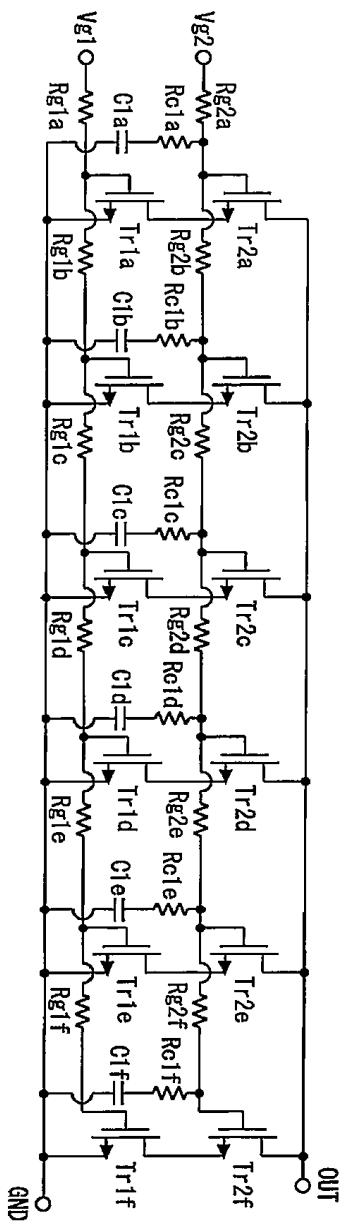

도 2는 본 발명의 실시형태 1에 관한 캐스코드 앰프를 나타낸 회로도다.

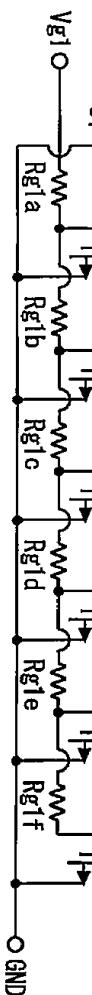

도 3은 비교예 1에 관한 캐스코드 앰프를 나타낸 평면도다.

도 4는 비교예 1에 관한 캐스코드 앰프를 나타낸 회로도다.

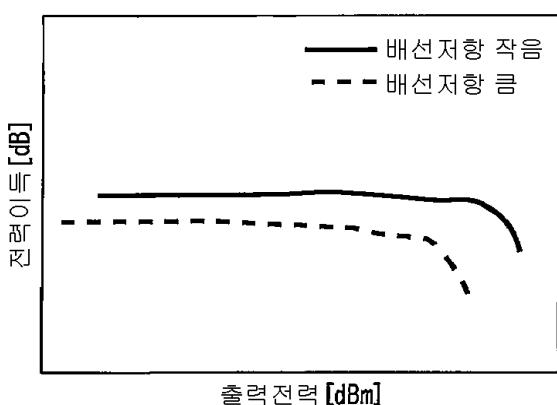

도 5는 비교예 1에 관한 캐스코드 앰프의 배선 저항과 전력 이득의 관계를 도시한 도면이다.

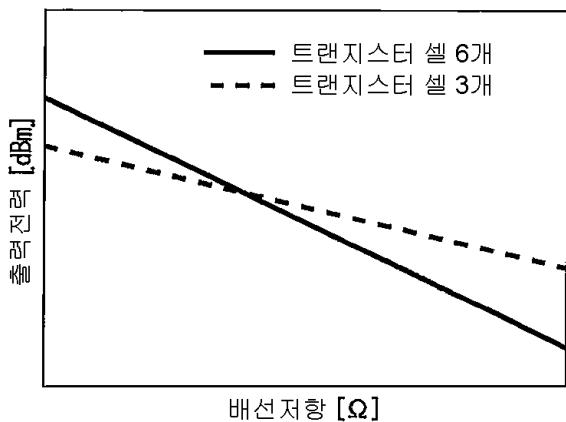

도 6은 비교예 1에 관한 캐스코드 앰프의 배선 저항과 출력 전력의 관계를 도시한 도면이다.

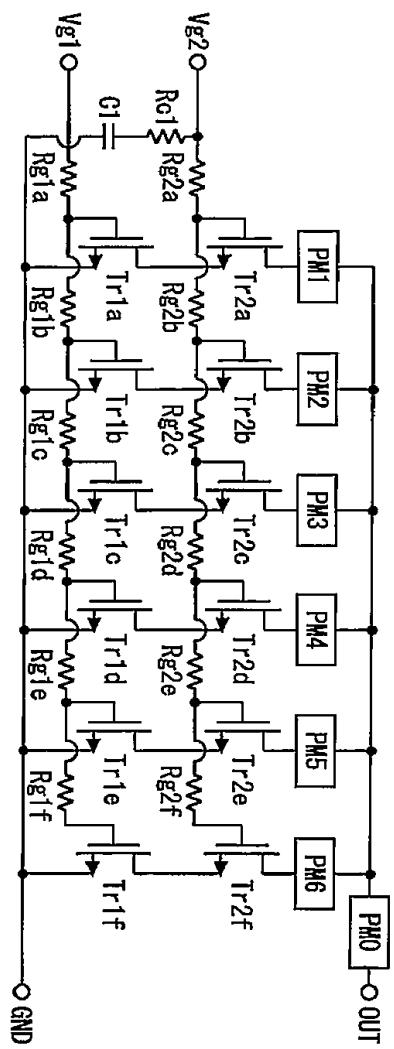

도 7은 비교예 2에 관한 캐스코드 앰프를 나타낸 회로도다.

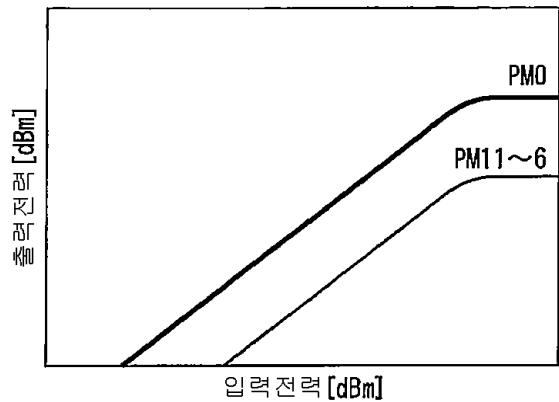

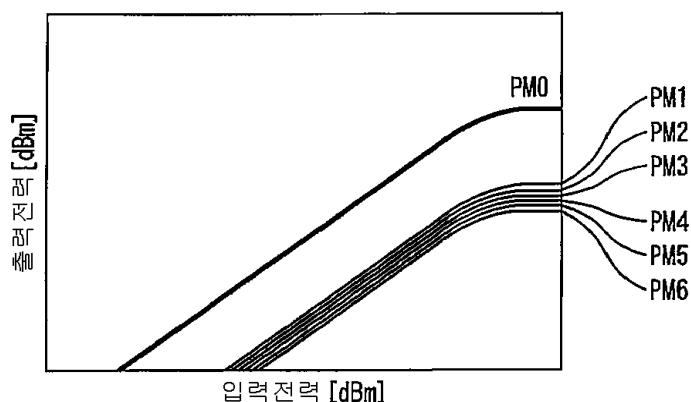

도 8은 배선 저항을 무시할 수 있는 이상 상태에서의 비교예 2에 관한 캐스코드 앰프의 입력 전력과 출력 전력의 관계를 도시한 도면이다.

도 9는 배선 저항을 고려한 경우의 비교예 2에 관한 캐스코드 앰프의 입력 전력과 출력 전력의 관계를 도시한 도면이다.

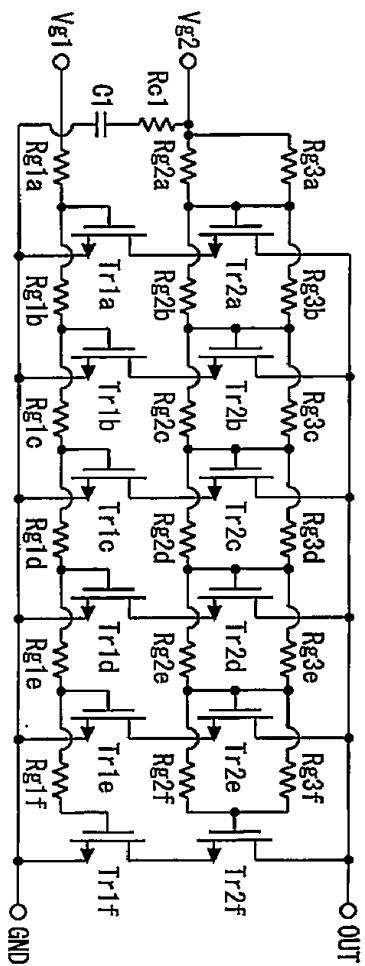

도 10은 본 발명의 실시형태 2에 관한 캐스코드 앰프를 나타낸 평면도다.

도 11은 본 발명의 실시형태 2에 관한 캐스코드 앰프를 나타낸 회로도다.

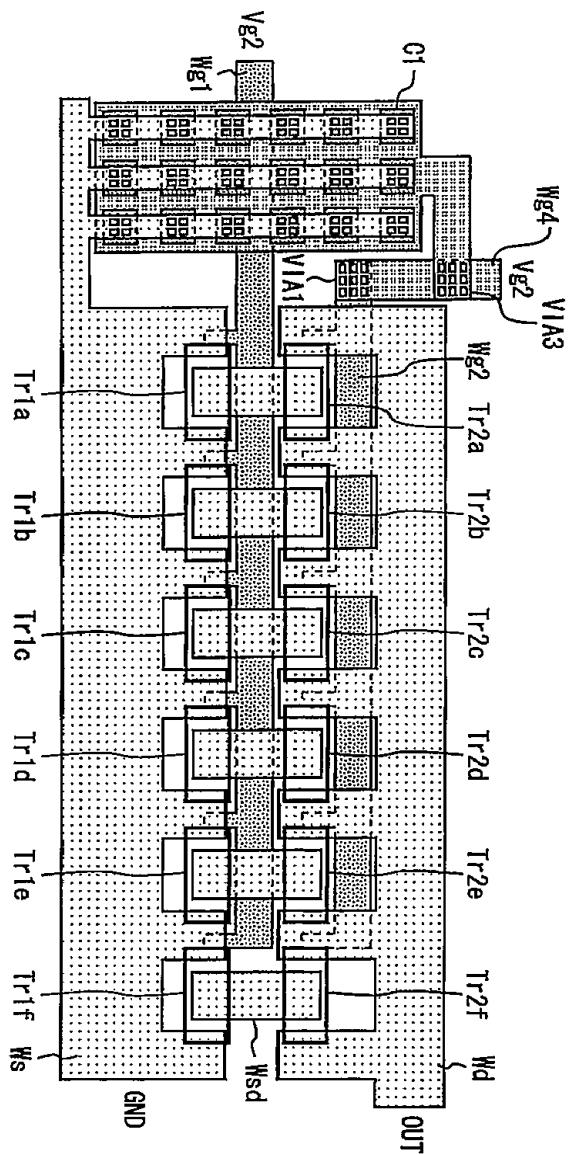

도 12는 본 발명의 실시형태 3에 관한 캐스코드 앰프를 나타낸 평면도다.

도 13은 본 발명의 실시형태 3에 관한 캐스코드 앰프를 나타낸 회로도다.

도 14는 본 발명의 실시형태 4에 관한 캐스코드 앰프를 나타낸 회로도다.

도 15는 비교예 3에 관한 캐스코드 앰프를 나타낸 회로도다.

도 16은 캐스코드 앰프의 기본구성을 나타낸 회로도다.

### 발명을 실시하기 위한 구체적인 내용

[0012] 본 발명의 실시형태에 관한 캐스코드 앰프에 대해 도면을 참조해서 설명한다. 동일 또는 대응하는 구성요소에는 동일한 부호를 붙이고, 설명의 반복을 생략하는 경우가 있다.

[0013] 실시형태 1.

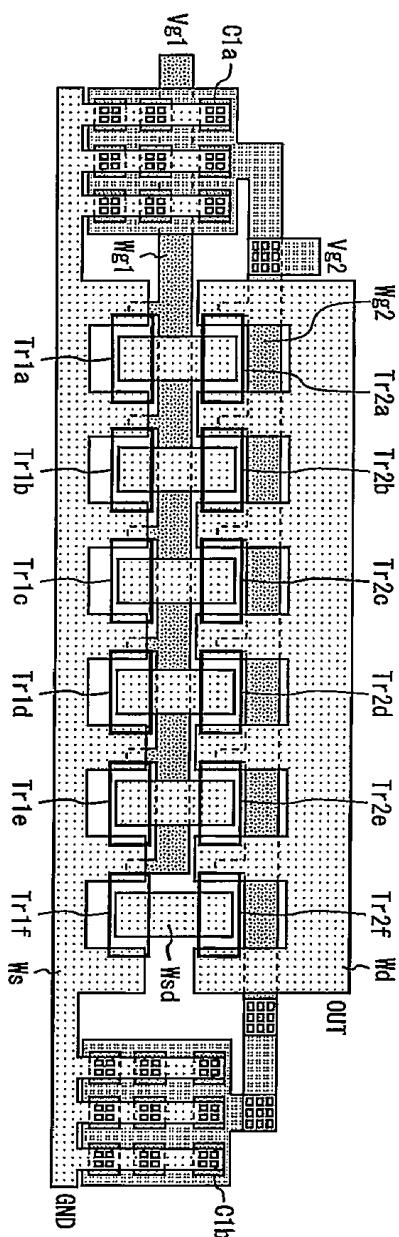

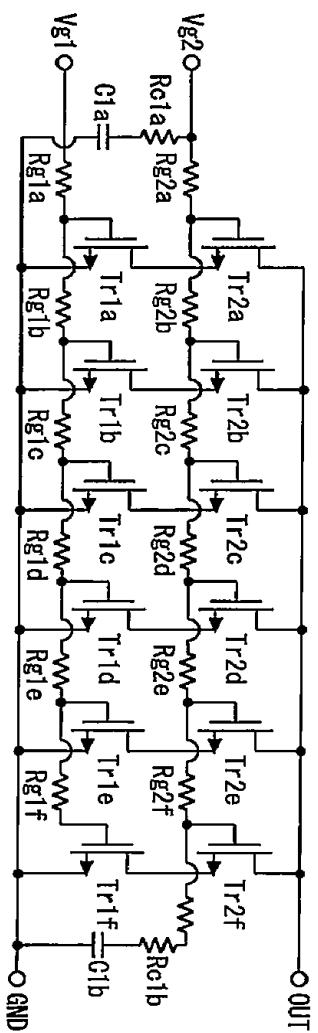

[0014] 도 1은, 본 발명의 실시형태 1에 관한 캐스코드 앰프를 나타낸 평면도다. 도 2는, 본 발명의 실시형태 1에 관한 캐스코드 앰프를 나타낸 회로도다. 트랜지스터 Tr1a~Tr1f가 트랜지스터 Tr2a~Tr2f에 각각 캐스코드 접속되어 있다. 이들 트랜지스터는 n채널 MOS 트랜지스터다.

[0015] 배선 Wg1이 Tr1a~Tr1f의 게이트에 순서대로 접속되어 있다. 배선 Wg2, Wg3가 Tr2a~Tr2f의 게이트에 순서대로 접속되어 있다. 배선 Wg2, Wg3은 서로 병렬로 접속되어 있다. 용량 C1이 배선 Wg2, Wg3의 일단과 GND 사이에 접속되어 있다.

[0016] Tr1a~Tr1f의 소스가 배선 Ws을 거쳐 GND에 접속되어 있다. Tr1a~Tr1f의 드레인이 배선 Wsd을 거쳐 각 Tr2a~Tr2f의 소스에 접속되어 있다. Tr2a~Tr2f의 드레인이 배선 Wd을 거쳐 RF 출력 신호 단자 OUT에 접속되어 있다.

[0017] 배선 Wg2은 비아 VIA1, VIA3 및 배선 Wg4을 거쳐 Vg2 단자에 접속되고, 배선 Wg3은 비아 VIA2, VIA3 및 배선 Wg4을 거쳐 Vg2 단자에 접속되어 있다. 이때, 비아 VIA1~VIA3은 LSI 프로세스의 다층 배선 프로세스로 상층 배선과 하층 배선 사이를 접속하기 위한 비아이다.

[0018] 배선 Wg1은 각 트랜지스터의 게이트 사이에서 배선 저항 Rg1a~Rg1f를 갖는다. 배선 Wg2은 각 트랜지스터의 게이트 사이에서 배선 저항 Rg2a~Rg2f를 갖는다. 배선 Wg3은 각 트랜지스터의 게이트 사이에서 배선 저항 Rg3a~Rg3f를 갖는다. 저항 Rc1은 Vg2 단자로부터 용량 C1까지의 배선 저항과 용량 C1 자신의 기생 저항의 합계이다. 저항 Rg1a는 Vg1 단자로부터 Tr1a의 게이트까지의 배선 저항이다. 저항 Rg2a는 Vg2 단자로부터 Tr2a의 게이트까지의 배선 저항과 비아 VIA1, VIA3의 콘택 저항의 합계이다. 저항 Rg3a는 Vg2 단자로부터 Tr2a의 게이트까지의 배선 저항과 비아 VIA2, VIA3의 콘택 저항의 합계이다.

[0019] 이어서, 본 실시형태의 효과를 비교예 1, 2와 비교해서 설명한다. 도 3은, 비교예 1에 관한 캐스코드 앰프를 나타낸 평면도다. 도 4는, 비교예 1에 관한 캐스코드 앰프를 나타낸 회로도다. 비교예 1에서는, 실시형태 1의 배선 Wg3가 없고, 배선 Wg2만이 Tr2a~Tr2f의 게이트에 순서대로 접속되어 있다.

[0020] 도 5는, 비교예 1에 관한 캐스코드 앰프의 배선 저항과 전력 이득의 관계를 도시한 도면이다. 배선 Wg2의 배선 저항이 커지면 전력 이득이 저하하는 동시에, 출력 전력의 최대값이 저하하는 것을 알 수 있다.

[0021] 도 6은, 비교예 1에 관한 캐스코드 앰프의 배선 저항과 출력 전력의 관계를 도시한 도면이다. 트랜지스터 셀이 6개인 경우의 쪽이 3개인 경우보다도 출력 전력이 작아지는 것을 알 수 있다. 즉, 비교예 1에서는, 게이트 폭(트랜지스터 사이즈)을 크게 해도, 오히려 출력 전력이 작아져 버린다.

[0022] 도 7은, 비교예 2에 관한 캐스코드 앰프를 나타낸 회로도다. 이 회로는, 비교예 1의 회로에, 캐스코드 앰프 전체로부터 출력되는 전력을 모니터하는 전력계 PM0과, 캐스코드 앰프의 각 셀로부터 출력되는 전력을 모니터하는 전력계 PM1~PM6을 추가한 것이다.

[0023] 도 8은, 배선 저항을 무시할 수 있는 이상 상태에서의 비교예 2에 관한 캐스코드 앰프의 입력 전력과 출력 전력의 관계를 도시한 도면이다. 전력계 PM1~6에서 모니터되는 전력은 동일하다.

[0024] 도 9는, 배선 저항을 고려한 경우의 비교예 2에 관한 캐스코드 앰프의 입력 전력과 출력 전력의 관계를 도시한 도면이다. 전력계 PM1~6에서 모니터되는 전력은 달라, 캐스코드 앰프의 각 셀이 불균일 동작하고 있다.

[0025] 이와 같이 비교예 1, 2에서는, 배선 Wg2의 배선 저항을 무시할 수 있는 이상 상태에서는 게이트 폭이 클수록 출력 전력이 커지지만, 배선 저항을 고려하면 게이트 폭이 클수록 출력 전력이 작아진다고 하는 문제가 있다. 예를 들면, Tr2a와 Tr2f에 대해 게이트와 용량 C1 사이의 배선 저항을 비교한 경우, Tr2f의 쪽이 Tr2a보다 Rg2b+Rg2c+Rg2d+Rg2e+Rg2f 만큼 저항값이 높아진다. 이 때문에, Tr1f와 Tr2f로 구성되는 캐스코드 앰프의 전

력 이득이 저하하고, 또한 추출할 수 있는 최대 출력 전력이 저하한다.

[0026] 이에 대해, 본 실시형태에서는, 2개의 배선 Wg2, Wg3가 Tr2a~Tr2f의 게이트에 병렬로 접속되어 있다. 이에 따라 배선 저항을 절반으로 할 수 있으므로, 게이트 폭이 큰 캐스코드 앰프에서도 배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있다. 또한, 게이트 사이에서의 배선 저항의 차이가 작아지기 때문에, 캐스코드 앰프의 각 셀 사이의 불균일 동작도 억제할 수 있다.

[0027] 이때, 본 실시형태에서는 2개의 배선 Wg2, Wg3가 Tr2a~Tr2f의 게이트에 병렬로 접속되어 있지만, 이것에 한정되지 않고 2개 이상의 배선을 Tr2a~Tr2f의 게이트에 병렬로 접속함으로써 효과를 얻을 수 있다.

[0028] 또한, Tr1a~Tr1f의 게이트에 접속된 배선 Wg1의 배선 저항에 의해서도, 각 트랜지스터의 게이트에 입력되는 전력에 차이가 생겨 불균일 동작의 원인으로 될 수 있다. 따라서, 마찬가지로, 2개 이상의 배선을 Tr1a~Tr1f의 게이트에 병렬로 접속함으로써, 입력 전력의 차이가 작아져 불균일 동작을 억제할 수 있다.

[0029] 실시형태 2.

[0030] 도 10은, 본 발명의 실시형태 2에 관한 캐스코드 앰프를 나타낸 평면도다. 도 11은, 본 발명의 실시형태 2에 관한 캐스코드 앰프를 나타낸 회로도다. 실시형태 1과는 다르게, 제1용량 C1a가 배선 Wg2의 일단과 접지 점 사이에 접속되고, 제2용량 C1b가 배선 Wg2의 타단과 접지 점 사이에 접속되어 있다. 저항 Rc1a는 Vg2 단자와 제1용량 C1a 사이의 배선과 비아 훌의 기생 저항의 합계이고, 저항 Rc1b은 Tr2f의 게이트와 제2용량 C1b 사이의 배선과 비아 훌의 기생 저항의 합계이다.

[0031] 본 실시형태에서는 RF 접지용의 용량을 2개로 분할함으로써, 용량 1개당의 기생 저항을 저감할 수 있다. 그리고, 배선 Wg2의 양단에 용량 C1a, C1b를 배치함으로써, 레이아웃 중심 부근의 Tr2c과 용량 C1a 또는 C1b 사이의 배선 저항을 비교예 1의 Tr2f와 용량 C1 사이의 배선 저항의 절반으로 할 수 있다. 이 때문에, 배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있다. 또한, 게이트 사이에서의 배선 저항의 차이가 작아지기 때문에, 캐스코드 앰프의 각 셀 사이의 불균일 동작도 억제할 수 있다.

[0032] 실시형태 3.

[0033] 도 12는, 본 발명의 실시형태 3에 관한 캐스코드 앰프를 나타낸 평면도다. 도 13은, 본 발명의 실시형태 3에 관한 캐스코드 앰프를 나타낸 회로도다. 실시형태 1과는 다르게, 용량 C1a~C1f가 Tr2a~Tr2f의 게이트와 GND 사이에 각각 접속되어 있다. 배선 Wg5a~Wg5f가 Tr2a~Tr2f의 게이트와 용량 C1a~C1f를 각각 접속한다. 저항 Rc1a~Rc1f는 각각 배선 Wg5a~Wg5f의 기생 저항과 비아 훌의 기생 저항의 합계이다.

[0034] 본 실시형태에서는 접지 용량을 셀마다 6개로 분할함으로써, 용량 1개당의 레이아웃 면적이 작아져 배선 저항을 저감할 수 있다. 그리고, 게이트와 접지 용량을 접속하는 배선이 복수개로 되기 때문에 배선 저항을 작게 할 수 있다. 이 때문에, 배선 저항에 기인하는 출력 전력의 저하를 억제할 수 있다. 더구나, 트랜지스터 셀마다 접지 용량을 설치함으로써, 트랜지스터 사이를 속하는 배선 Wg2의 배선 저항 Rg2b~Rg2f의 영향을 무시할 수 있기 때문에, 캐스코드 앰프의 각 셀 사이의 불균일 동작도 억제할 수 있다.

[0035] 실시형태 4.

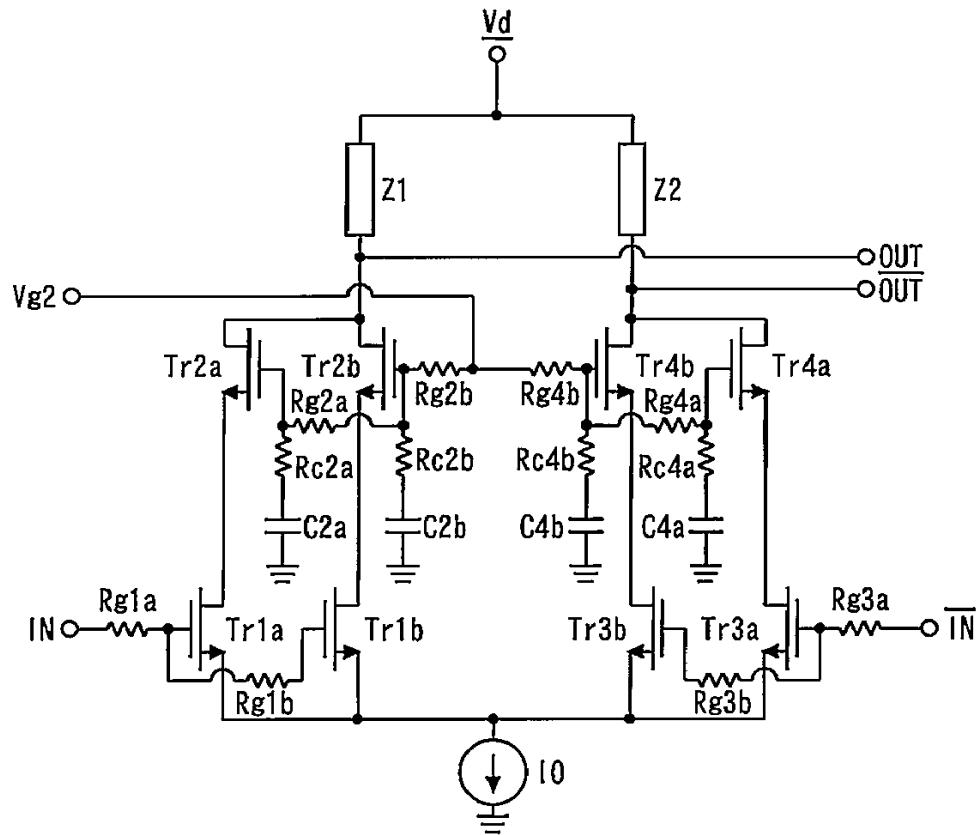

[0036] 도 14는, 본 발명의 실시형태 4에 관한 캐스코드 앰프를 나타낸 회로도다. 이 캐스코드 앰프는 차동 앰프이다. 트랜지스터 Tr1a, Tr1b과 트랜지스터 Tr2a, Tr2b의 캐스코드 앰프와 트랜지스터 Tr3a, Tr3b과 트랜지스터 Tr4a, Tr4b의 캐스코드 앰프가 차동 페어를 형성하고 있다. 용량 C2a, C2b, C4a, C4b가 각각 Tr2a, Tr2b, Tr4a, Tr4b의 게이트와 GND 사이에 각각 접속되어 있다.

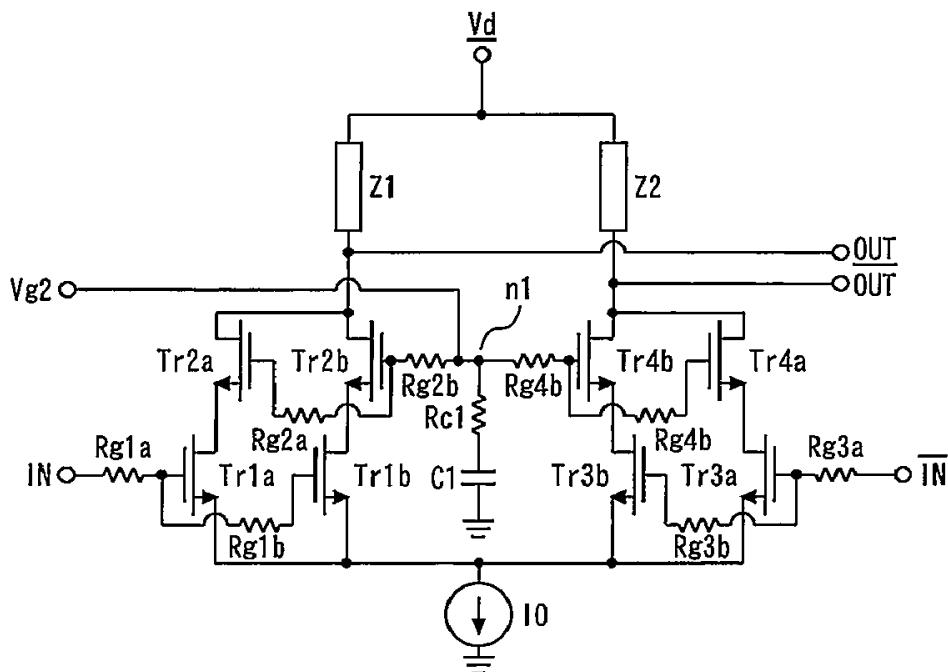

[0037] 본 실시형태의 효과를 비교예 3과 비교해서 설명한다. 도 15는, 비교예 3에 관한 캐스코드 앰프를 나타낸 회로도다. 비교예 3에서는, Tr2a, Tr2b, Tr4a, Tr4b의 게이트의 접속점 n1과 접지 점 사이에 접지 용량으로서 1개의 용량 C1이 접속되어 있다. 그러나, 게이트 폭(트랜지스터 사이즈)의 확대와 함께 배선 저항 Rc1, Rg2a, Rg2b, Rg4a, Rg4b의 영향이 커지기 때문에, 접지 용량을 크게 하지 않으면 가상 접지를 실현할 수 없다.

[0038] 이에 대해, 본 실시형태에서는 접지 용량을 셀마다 4개로 분할함으로써, 용량 1개당의 레이아웃 면적이

작아져 배선 저항을 저감할 수 있다. 그리고, 게이트와 접지 용량을 접속하는 배선이 복수개로 되기 때문에 배선 저항을 작게 할 수 있다. 이 때문에, 비교적 작은 접지 용량으로 차동 앰프의 게이트의 접속점 n1에서의 가상 접지를 실현할 수 있다.

### 부호의 설명

[0039]

C1, C1a, C1b, C1a~C1f 용량

Tr1a~Tr1f 트랜지스터(제1트랜지스터)

Tr2a~Tr2f 트랜지스터(제2트랜지스터)

Wg1, Wg2, Wg3 배선

### 도면

#### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16