(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

**特許第5121926号

(P5121926)**

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年11月2日(2012.11.2)

(51) Int.Cl.

F 1

|             |             |                  |      |      |         |

|-------------|-------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b> | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/22</b> | <b>(2006.01)</b> | G09G | 3/22 | E       |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

|             |             |                  | G09G | 3/20 | 6 4 2 A |

|             |             |                  | G09G | 3/20 | 6 1 1 A |

請求項の数 11 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2010-512952 (P2010-512952)

(86) (22) 出願日 平成21年2月16日 (2009.2.16)

(86) 国際出願番号 PCT/JP2009/052477

(87) 国際公開番号 WO2009/142033

(87) 国際公開日 平成21年11月26日 (2009.11.26)

審査請求日 平成22年9月14日 (2010.9.14)

(31) 優先権主張番号 特願2008-131568 (P2008-131568)

(32) 優先日 平成20年5月20日 (2008.5.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100104695

弁理士 島田 明宏

(74) 代理人 100121348

弁理士 川原 健児

(72) 発明者 大橋 誠二

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】表示装置、画素回路およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電流駆動型の表示装置であって、

複数の走査線と複数のデータ線の各交差点に対応して配置された複数の画素回路と、

前記走査線を用いて、書き込み対象の画素回路を選択する走査信号出力回路と、

前記データ線に対して、表示データに応じた電位を与える表示信号出力回路とを備え、

前記画素回路は、

第1の配線と第2の配線とを結ぶ経路上に設けられ、制御端子、第1の端子および第2の端子を有し、前記経路を流れる電流を制御する駆動素子と、

前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、 10

前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、

前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、

前記駆動素子の第2の端子と前記第1の配線との間に設けられた第3のスイッチング素子と、

前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサとを含み、

前記表示信号出力回路は、前記データ線に対して、前記電気光学素子への印加電圧が発光閾値電圧以下となる電位を与え、

前記走査信号出力回路は、前記第3の配線の電位を2段階に変化させることを特徴とする、表示装置。

### 【請求項 2】

前記画素回路は、前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子をさらに含む、請求項1に記載の表示装置。

### 【請求項3】

前記第4のスイッチング素子の制御端子は、前記第4の配線に接続されていることを特徴とする、請求項2に記載の表示装置。

【請求項4】

前記第4の配線には、前記駆動素子が導通状態となる電位が与えられることを特徴とする、請求項2に記載の表示装置。

【請求項 5】

前記画素回路に対する書き込み時には、前記第1および第2のスイッチング素子は導通状態に、前記第3のスイッチング素子は非導通状態に制御されることを特徴とする、請求項1に記載の表示装置。

【請求項 6】

前記走査信号出力回路は、前記第3の配線の電位の変化タイミングを調整する機能を有することを特徴とする、請求項1に記載の表示装置。

【請求項 7】

前記走査信号出力回路は、前記第3のスイッチング素子の制御端子に与える電位の変化タイミングを調整する機能を有することを特徴とする、請求項1に記載の表示装置。

【請求項 8】

前記電気光学素子は有機EL素子で構成されていることを特徴とする、請求項1に記載の表示装置。

【請求項 9】

電流駆動型の表示装置に複数の走査線と複数のデータ線の各交差点に対応して複数個配置される画素回路であって、

第1の配線と第2の配線とを結ぶ経路上に設けられ、制御端子、第1の端子および第2の端子を有し、前記経路を流れる電流を制御する駆動素子と、

前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、

前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、

前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、前記駆動素子の第2の端子と前記第1の配線との間に設けられた第3のスイッチング素

子と、

前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサと、

前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子とを

備え、

前記第4のスイッチング素子の制御端子は、前記第4の配線に接続されていることを特徴とする、画素回路。

【請求項 10】

電流駆動型の表示装置に複数の走査線と複数のデータ線の各交差点に対応して複数個配置される画素回路の駆動方法であって、

前記画素回路が、第1の配線と第2の配線とを結ぶ経路上に設けられ、制御端子、第1の端子および第2の端子を有し、前記経路を流れる電流を制御する駆動素子と、前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、前記駆動素子の第2の端子と前記第1

の配線との間に設けられた第3のスイッチング素子と、前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサとを含む場合に、

前記第1および第2のスイッチング素子を導通状態に、前記第3のスイッチング素子を非導通状態に制御し、前記データ線に対して、表示データに応じて変化し、かつ、前記電気光学素子への印加電圧が発光閾値電圧以下となる電位を与えるステップと、

前記第3の配線の電位を2段階に変化させるステップと、

前記第1および第2のスイッチング素子を非導通状態に、前記第3のスイッチング素子を導通状態に制御するステップとを備えた、画素回路の駆動方法。

#### 【請求項1】

前記画素回路が、前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子をさらに含む場合に、10

前記第4の配線に前記駆動素子が導通状態となる電位を与えておき、前記第1および第2のスイッチング素子が導通状態で、前記第3のスイッチング素子が非導通状態である間に、前記第4のスイッチング素子を導通状態に制御するステップをさらに備えた、請求項1\_0に記載の画素回路の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、表示装置に関し、より特定的には、有機ELディスプレイやFEDなどの電流駆動型の表示装置、表示装置の画素回路、および、画素回路の駆動方法に関する。20

##### 【背景技術】

##### 【0002】

近年、薄型、軽量、高速応答可能な表示装置の需要が高まり、これに伴い、有機EL(Electro Luminescence)ディスプレイやFED(Field Emission Display)に関する研究開発が活発に行われている。

##### 【0003】

有機ELディスプレイに含まれる有機EL素子は、印加される電圧が高く、流れる電流が多いほど、高い輝度で発光する。ところが、有機EL素子の輝度と電圧の関係は、駆動時間や周辺温度などの影響を受けて容易に変動する。このため、有機ELディスプレイに電圧制御型の駆動方式を適用すると、有機EL素子の輝度のばらつきを抑えることが非常に困難になる。これに対して、有機EL素子の輝度は電流にほぼ比例し、この比例関係は周辺温度などの外的要因の影響を受けにくい。したがって、有機ELディスプレイには電流制御型の駆動方式を適用することが好ましい。30

##### 【0004】

一方、表示装置の画素回路や駆動回路は、アモルファスシリコン、低温多結晶シリコン、CG(Continuous Grain)シリコンなどで構成されたTFT(Thin Film Transistor: 薄膜トランジスタ)を用いて構成される。ところが、TFTの特性(例えば、閾値電圧や移動度)には、ばらつきが生じやすい。そこで、有機ELディスプレイの画素回路にはTFTの特性のばらつきを補償する回路が設けられ、この回路の作用により有機EL素子の輝度のばらつきが抑えられる。40

##### 【0005】

電流制御型の駆動方式においてTFTの特性のばらつきを補償する方式は、駆動用TFTに流れる電流の量を電流信号で制御する電流プログラム方式と、この電流の量を電圧信号で制御する電圧プログラム方式とに大別される。電流プログラム方式を用いれば閾値電圧と移動度のばらつきを補償することができ、電圧プログラム方式を用いれば閾値電圧のばらつきのみを補償することができる。

##### 【0006】

ところが、電流プログラム方式には、第1に、非常に微少な量の電流を扱うので画素回路や駆動回路の設計が困難である、第2に、電流信号を設定する間に寄生容量の影響を受けやすいので大面積化が困難であるという問題がある。これに対して、電圧プログラム方50

式では、寄生容量などの影響は軽微であり、回路設計も比較的容易である。また、移動度のばらつきが電流量に与える影響は、閾値電圧のばらつきが電流量に与える影響よりも小さく、移動度のばらつきは TFT 作製工程である程度抑えることができる。したがって、電圧プログラム方式を適用した表示装置でも、十分な表示品位が得ることができる。

#### 【0007】

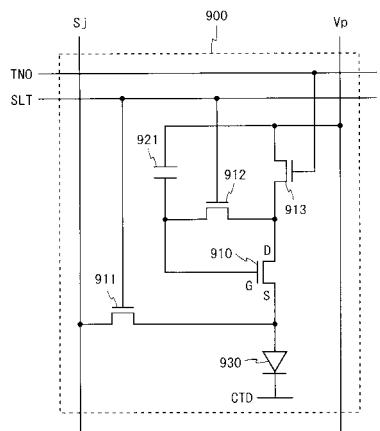

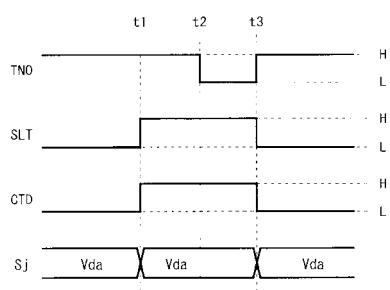

電流制御型の駆動方式を採用した有機ELディスプレイについては、従来から各種の画素回路が知られている（例えば、非特許文献1～4）。図8は、非特許文献4に記載された画素回路の回路図である。図8に示す画素回路900は、駆動用TFT910、スイッチ用TFT911～913、コンデンサ921、および、有機EL素子930を備えている。画素回路900に含まれるTFTは、いずれもnチャネル型である。

10

#### 【0008】

画素回路900では、電位VDDを有する電源配線Vpと有機EL素子930の陰極CTDとの間に、スイッチ用TFT913、駆動用TFT910および有機EL素子930が直列に設けられている。駆動用TFT910のソース端子とデータ線Sjとの間にはスイッチ用TFT911が設けられ、駆動用TFT910のゲート端子とドレイン端子との間にはスイッチ用TFT912が設けられ、駆動用TFT910のゲート端子と電源配線Vpとの間にはコンデンサ921が設けられている。スイッチ用TFT911、912のゲート端子はいずれも制御配線SLTに接続され、スイッチ用TFT913のゲート端子は制御配線TNOに接続されている。

#### 【0009】

20

図9は、画素回路900のタイミングチャートである。図9に示すように、まず時刻t1において、制御配線SLTの電位がハイレベルに変化する。このため、スイッチ用TFT911、912は導通状態になり、データ線Sjからスイッチ用TFT911を経由して駆動用TFT910のソース端子にデータ電位Vdaが印加される。また時刻t1では、有機EL素子930の陰極CTDの電位もハイレベルに変化する。このため、有機EL素子930の陽極と陰極の間には逆方向バイアス電圧が印加され、有機EL素子930は非発光状態となる。また時刻t1から時刻t2までの間、スイッチ用TFT912、913は共に導通状態にあるので、駆動用TFT910のゲート電位は電源配線Vpの電位VDに等しくなる。

#### 【0010】

30

次に時刻t2において、制御配線TNOの電位がローレベルに変化する。このため、スイッチ用TFT913は非導通状態になり、駆動用TFT910のゲート端子（および、これに短絡されたドレイン端子）から駆動用TFT910とスイッチ用TFT911を経由してデータ線Sjに電流が流れ、駆動用TFT910のゲート電位は徐々に下降する。駆動用TFT910のゲート・ソース間電圧が駆動用TFT910の閾値電圧Vthに等しくなったときに（すなわち、ゲート電位が（Vda + Vth）になったときに）、駆動用TFT910は非導通状態になる。この時点で、コンデンサ921の電極間の電位差は{Vp - (Vda + Vth)}になる。これ以降、コンデンサ921には、この電位差が保持される。

#### 【0011】

40

次に時刻t3において、制御配線TNOの電位はハイレベルに変化し、制御配線SLTの電位はローレベルに変化する。このため、スイッチ用TFT911、912は非導通状態になり、スイッチ用TFT913は導通状態になる。コンデンサ921には電位差{Vp - (Vda + Vth)}が保持されているので、駆動用TFT910のゲート電位は時刻t3以降も(Vda + Vth)となる。また時刻t3では、有機EL素子930の陰極CTDの電位はローレベルに変化する。このため、駆動用TFT910から有機EL素子930には、駆動用TFT910のゲート電位(Vda + Vth)から駆動用TFT910の閾値電圧Vthを引いた電位Vda（データ電位に等しい）に応じた電流が流れ、有機EL素子930は当該電流に応じた輝度で発光する。

#### 【0012】

50

このように画素回路 900 では、時刻  $t_3$  以降に駆動用 TFT910 から有機 EL 素子 930 に流れる電流は、データ電位  $V_{da}$  によって定まり、駆動用 TFT910 の閾値電圧  $V_{th}$  の影響を受けない。したがって、画素回路 900 を備えた表示装置によれば、駆動用 TFT910 の閾値電圧  $V_{th}$  にばらつきがある場合でも、データ電位  $V_{da}$  と閾値電圧  $V_{th}$  に応じた電流を有機 EL 素子 930 に流し、有機 EL 素子 930 を所望の輝度で発光させることができる。

【非特許文献 1】“4.0-in. TFT-OLED Displays and a Novel Digital Driving Method”、SID'00 Digest、pp. 924-927、半導体エネルギー研究所

【非特許文献 2】“Continuous Grain Silicon Technology and Its Applications for Active Matrix Display”、AM-LCD 2000、pp. 25-28、半導体エネルギー研究所 10

【非特許文献 3】“Polymer Light-Emitting Diodes for Use in Flat Panel Display”、AM-LCD' 01、pp. 211-214、半導体エネルギー研究所

【非特許文献 4】“A new a-Si:H Thin-Film Transistor Pixel Circuit for Active-Matrix Organic Light-Emitting Diodes”、Electron Device Letters、IEEE、Volume 24、Issue 9、pp. 583-585、Korea Advanced Institute of Science and Technology

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0013】

上述したように、画素回路 900 を備えた表示装置では、駆動用 TFT910 のゲート・ソース間電圧を駆動用 TFT910 の閾値電圧  $V_{th}$  に一致させる期間（時刻  $t_1$  から  $t_3$  までの期間）に、有機 EL 素子 930 の陰極 CTD の電位をハイレベルにする必要がある。また、一般的なアクティブマトリクス型の表示装置は、すべての表示素子に共通する陰極を 1 個だけ備えている。そこで、画素回路 900 を用いる場合にも、すべての有機 EL 素子 930 に共通する陰極を 1 個だけ備えた表示装置（以下、第 1 の表示装置という）を考えることができる。

##### 【0014】

しかしながら、上記第 1 の表示装置では、ある画素回路 900 に対してデータ電位  $V_{da}$  を書き込むときに、表示装置内のすべての有機 EL 素子 930 に逆方向バイアス電圧が印加されるので、すべての有機 EL 素子 930 がこの期間では発光しない。このため、第 1 の表示装置には、十分な発光デューティー比が得られず、表示品位が低くなるという問題がある。

##### 【0015】

この問題を解決するために、有機 EL 素子 930 の陰極 CTD を画素回路の行ごとに備えた表示装置（陰極 CTD を制御配線 SLT と同数だけ設けた表示装置。以下、第 2 の表示装置という）を考えることができる。しかしながら、第 2 の表示装置を製造するためには、有機 EL 素子 930 を形成するときに有機 EL 素子 930 の陰極 CTD をパターニングする必要がある。このため、第 2 の表示装置には、有機 EL 素子 930 の作成工程が 1 つ余分に増え、製造コストが高くなるという問題がある。また、有機 EL 素子 930 の陰極 CTD をパターニングするので、開口率が低下し画面が暗くなるという問題もある。

##### 【0016】

それ故に、本発明は、発光デューティー比が高く、電気光学素子の一方の電極のパターニングが不要な、高表示品位かつ低コストの表示装置を提供することを目的とする。

##### 【課題を解決するための手段】

##### 【0017】

本発明の第 1 の局面は、電流駆動型の表示装置であって、複数の走査線と複数のデータ線の各交差点に対応して配置された複数の画素回路と、前記走査線を用いて、書き込み対象の画素回路を選択する走査信号出力回路と、前記データ線に対して、表示データに応じた電位を与える表示信号出力回路とを備え、前記画素回路は、

第 1 の配線と第 2 の配線とを結ぶ経路上に設けられ、制御端子、第 1 の端子および第 50

2の端子を有し、前記経路を流れる電流を制御する駆動素子と、

前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、

前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、

前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、

前記駆動素子の第2の端子と前記第1の配線との間に設けられた第3のスイッチング素子と、

前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサとを含み、

10

前記表示信号出力回路は、前記データ線に対して、前記電気光学素子への印加電圧が発光閾値電圧以下となる電位を与え、

前記走査信号出力回路は、前記第3の配線の電位を2段階に変化させることを特徴とする。

#### 【0018】

本発明の第2の局面は、本発明の第1の局面において、

前記画素回路は、前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子をさらに含む。

#### 【0019】

本発明の第3の局面は、本発明の第2の局面において、

20

前記第4のスイッチング素子の制御端子は、前記第4の配線に接続されていることを特徴とする。

#### 【0020】

本発明の第4の局面は、本発明の第2の局面において、

前記第4の配線には、前記駆動素子が導通状態となる電位が与えられることを特徴とする。

#### 【0021】

本発明の第5の局面は、本発明の第1の局面において、

前記画素回路に対する書き込み時には、前記第1および第2のスイッチング素子は導通状態に、前記第3のスイッチング素子は非導通状態に制御されることを特徴とする。

30

#### 【0022】

本発明の第6の局面は、本発明の第1の局面において、

前記走査信号出力回路は、前記第3の配線の電位の変化タイミングを調整する機能を有することを特徴とする。

#### 【0023】

本発明の第7の局面は、本発明の第1の局面において、

前記走査信号出力回路は、前記第3のスイッチング素子の制御端子に与える電位の変化タイミングを調整する機能を有することを特徴とする。

#### 【0024】

本発明の第8の局面は、本発明の第1の局面において、

40

前記電気光学素子は有機EL素子で構成されていることを特徴とする。

#### 【0025】

本発明の第9の局面は、電流駆動型の表示装置に複数の走査線と複数のデータ線の各交差点に対応して複数個配置される画素回路であって、

第1の配線と第2の配線とを結ぶ経路上に設けられ、制御端子、第1の端子および第2の端子を有し、前記経路を流れる電流を制御する駆動素子と、

前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、

前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、

50

前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、前記駆動素子の第2の端子と前記第1の配線との間に設けられた第3のスイッチング素子と、

前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサと、

前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子とを備え、

前記第4のスイッチング素子の制御端子は、前記第4の配線に接続されていることを特徴とする。

#### 【0028】

本発明の第1\_0の局面は、電流駆動型の表示装置に複数の走査線と複数のデータ線の各交差点に対応して複数個配置される画素回路の駆動方法であって、

10

前記画素回路が、第1の配線と第2の配線とを結ぶ経路上に設けられ、制御端子、第1の端子および第2の端子を有し、前記経路を流れる電流を制御する駆動素子と、前記駆動素子の第1の端子に接続して前記経路上に前記駆動素子と直列に設けられ、前記経路を流れる電流に応じた輝度で発光する電気光学素子と、前記駆動素子の第1の端子と前記データ線との間に設けられた第1のスイッチング素子と、前記駆動素子の制御端子と第2の端子との間に設けられた第2のスイッチング素子と、前記駆動素子の第2の端子と前記第1の配線との間に設けられた第3のスイッチング素子と、前記駆動素子の制御端子と第3の配線との間に設けられたコンデンサとを含む場合に、

前記第1および第2のスイッチング素子を導通状態に、前記第3のスイッチング素子を非導通状態に制御し、前記データ線に対して、表示データに応じて変化し、かつ、前記電気光学素子への印加電圧が発光閾値電圧以下となる電位を与えるステップと、

20

前記第3の配線の電位を2段階に変化させるステップと、

前記第1および第2のスイッチング素子を非導通状態に、前記第3のスイッチング素子を導通状態に制御するステップとを備える。

#### 【0029】

本発明の第1\_1の局面は、本発明の第1\_0の局面において、

前記画素回路が、前記駆動素子の制御端子と第4の配線との間に設けられた第4のスイッチング素子をさらに含む場合に、

前記第4の配線に前記駆動素子が導通状態となる電位を与えておき、前記第1および第2のスイッチング素子が導通状態で、前記第3のスイッチング素子が非導通状態である間に、前記第4のスイッチング素子を導通状態に制御するステップをさらに備える。

30

#### 【発明の効果】

#### 【0030】

本発明の第1の局面によれば、データ線には電気光学素子への印加電圧が発光閾値電圧以下となる電位が与えられるので、データ線の電位を画素回路に書き込んだだけでは電気光学素子は発光せず、第3の配線の電位が変化した後に電気光学素子は発光する。また、第2のスイッチング素子を導通状態に、第3のスイッチング素子を非導通状態に制御すれば、駆動素子の制御端子と第1の端子との間に閾値電圧を印加することができ、その後に第3の配線の電位を変化させることにより、駆動素子の閾値電圧にかかわらず、電気光学素子を所望の輝度で発光させることができる。このように、駆動素子の閾値電圧のばらつきを補償しながら、表示データに応じた電位を画素回路に書き込むときに、第2の配線の電位を固定したまま電気光学素子を非発光状態にすることができる。このため、ある画素回路に書き込みを行っている間も他の画素回路の電気光学素子は発光し続けるので、ある画素回路に書き込みを行っている間は他の画素回路の電気光学素子が発光しなくなる場合よりも、発光デューティー比は高くなり、表示品位も高くなる。また、第2の配線の電位を分割して制御する必要はないので、電気光学素子の第2の配線側の電極をパターニングする必要もなく、その分だけ表示装置のコストは低くなる。また、第3の配線の電位を2段階に変化させる走査信号出力回路は簡単に構成することができる。したがって、発光デューティー比が高く、電気光学素子の一方の電極のパターニングが不要な、高表示品位

40

50

かつ低コストの表示装置を得ることができる。

**【0031】**

本発明の第2の局面によれば、第4の配線に好適な電位を印加し、第4のスイッチング素子を導通状態に制御することにより、第1の配線の電位を駆動素子の制御端子に印加することなく、駆動素子の制御端子と第1の端子との間に閾値電圧を印加することができる。これにより、表示装置の消費電力を削減することができる。

**【0032】**

本発明の第3の局面によれば、第4のスイッチング素子の制御端子を他の端子と同じ配線に接続することにより、配線を1本削減し、表示装置の開口率や歩留りを高くすることができます。

10

**【0033】**

本発明の第4の局面によれば、第4の配線に駆動素子が導通状態となる電位を与えることにより、駆動素子の制御端子と第1の端子との間に閾値電圧を印加するまでの時間を短縮することができる。これにより、解像度の高い表示装置を構成することが可能となる。

**【0034】**

本発明の第5の局面によれば、第2のスイッチング素子を導通状態に、第3のスイッチング素子を非導通状態に制御することにより、駆動素子の制御端子と第1の端子との間に閾値電圧を印加することができる。その後に、駆動素子が導通状態となる電位を第3の配線に与えることにより、駆動素子の閾値電圧にかかわらず、電気光学素子を所望の輝度で発光させることができます。

20

**【0035】**

本発明の第6の局面によれば、走査信号出力回路において第3の配線の電位の変化タイミングを調整することにより、発光デューティー比を調整し、ホールド型表示を行う表示装置の欠点である動画ぼやけを解消することができます。

**【0036】**

本発明の第7の局面によれば、走査信号出力回路において第3のスイッチング素子の制御端子に与える電位の変化タイミングを調整することにより、発光デューティー比を調整し、ホールド型表示を行う表示装置の欠点である動画ぼやけを解消することができます。

**【0037】**

本発明の第8の局面によれば、発光デューティー比が高く、有機EL素子の陰極のパターニングが不要な、高表示品位かつ低コストの有機ELディスプレイを構成することができる。

30

**【0038】**

本発明の第9の局面によれば、本発明の第3の局面に係る表示装置に含まれる画素回路を構成し、これを用いて、発光デューティー比が高く、電気光学素子の一方の電極のパターニングが不要な、高表示品位かつ低コストの表示装置を得ることができます。

**【0039】**

本発明の第10の局面によれば、本発明の第1の局面と同様の理由により、電気光学素子の一方の電極のパターニングが行われていない低成本の表示装置において、発光デューティー比を高くし、表示品位を高くすることができます。

40

**【0040】**

本発明の第11の局面によれば、第4の配線に駆動素子が導通状態となる電位を与え、第4のスイッチング素子を導通状態に制御することにより、第1の配線の電位を駆動素子の制御端子に印加することなく、短時間で、駆動素子の制御端子と第1の端子との間に閾値電圧を印加することができる。これにより、表示装置の消費電力を削減すると共に、解像度の高い表示装置を構成することが可能となる。

**【図面の簡単な説明】**

**【0041】**

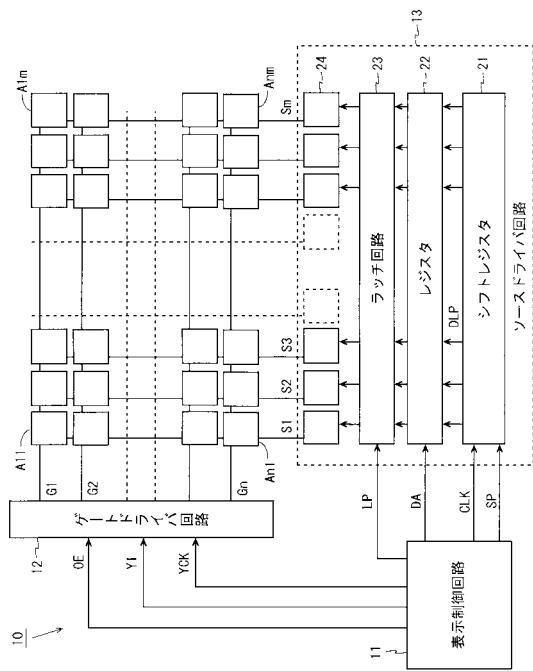

【図1】本発明の第1および第2の実施形態に係る表示装置の構成を示すブロック図である。

50

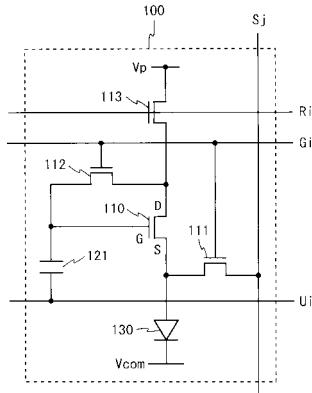

【図2】本発明の第1の実施形態に係る表示装置に含まれる画素回路の回路図である。

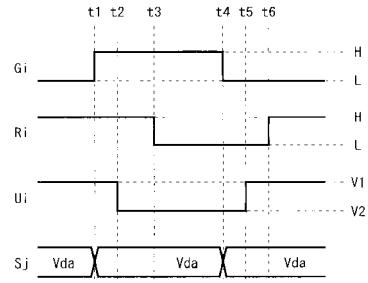

【図3】図2に示す画素回路のタイミングチャートである。

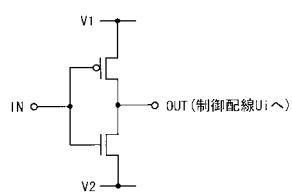

【図4】インバータの回路図である。

【図5】本発明の第2の実施形態に係る表示装置に含まれる画素回路の回路図である。

【図6】図5に示す画素回路のタイミングチャートである。

【図7】本発明の変形例に係る表示装置に含まれる画素回路の回路図である。

【図8】従来の表示装置に含まれる画素回路の回路図である。

【図9】図8に示す画素回路のタイミングチャートである。

【符号の説明】

【0042】

10

10 ... 表示装置

11 ... 表示制御回路

12 ... ゲートドライバ回路

13 ... ソースドライバ回路

21 ... シフトレジスタ

22 ... レジスタ

23 ... ラッチ回路

24 ... D / A 変換器

100、200、250 ... 画素回路

110 ... 駆動用 TFT

20

111、112、113、214 ... スイッチ用 TFT

121 ... コンデンサ

130 ... 有機EL素子

G<sub>i</sub> ... 走査線

R<sub>i</sub>、U<sub>i</sub>、W<sub>i</sub> ... 制御配線

S<sub>j</sub> ... データ線

V<sub>p</sub>、V<sub>ref</sub> ... 電源配線

V<sub>com</sub> ... 共通陰極

【発明を実施するための最良の形態】

【0043】

30

以下、図1～図7を参照して、本発明の第1および第2の実施形態に係る表示装置について説明する。各実施形態に係る表示装置は、電気光学素子、駆動素子、コンデンサおよび複数のスイッチング素子を含む画素回路を備えている。スイッチング素子は、低温ポリシリコンTFTやCGシリコンTFTやアモルファスシリコンTFTなどで構成することができる。これらTFTの構成や製造プロセスは公知であるので、ここではその説明を省略する。また、電気光学素子には有機EL素子が使用される。有機EL素子の構成も公知であるので、ここではその説明を省略する。

【0044】

図1は、本発明の第1および第2の実施形態に係る表示装置の構成を示すブロック図である。図1に示す表示装置10は、複数の画素回路A<sub>i</sub><sub>j</sub>（iは1以上n以下の整数、jは1以上m以下の整数）、表示制御回路11、ゲートドライバ回路12、および、ソースドライバ回路13を備えている。表示装置10には、互いに平行に配置された複数の走査線G<sub>i</sub>と、走査線G<sub>i</sub>に直交するように互いに平行に配置された複数のデータ線S<sub>j</sub>とが設けられる。画素回路A<sub>i</sub><sub>j</sub>は、走査線G<sub>i</sub>とデータ線S<sub>j</sub>の各交差点に対応してマトリクス状に配置されている。

【0045】

これに加えて表示装置10には、複数の制御配線（R<sub>i</sub>、U<sub>i</sub>、W<sub>i</sub>など；図示せず）が走査線G<sub>i</sub>と平行に配置されている。また、図1では省略されているが、画素回路A<sub>i</sub><sub>j</sub>の配置領域には電源配線V<sub>p</sub>と共通陰極V<sub>com</sub>が配置されており、実施形態によっては電源配線V<sub>ref</sub>が配置されていることもある。走査線G<sub>i</sub>と制御配線はゲートドライ

40

50

バ回路 1 2 に接続され、データ線 S<sub>j</sub> はソースドライバ回路 1 3 に接続される。

#### 【0046】

表示制御回路 1 1 は、ゲートドライバ回路 1 2 に対してタイミング信号 O\_E、スタートパルス Y\_I およびクロック Y\_C\_K を出力し、ソースドライバ回路 1 3 に対してスタートパルス S\_P、クロック C\_L\_K、表示データ D\_A およびラッチパルス L\_P を出力する。

#### 【0047】

ゲートドライバ回路 1 2 は、シフトレジスタ回路、論理演算回路、および、バッファ（いずれも図示せず）を含んでいる。シフトレジスタ回路は、クロック Y\_C\_K に同期してスタートパルス Y\_I を順次転送する。論理演算回路は、シフトレジスタ回路の各段から出力されたパルスとタイミング信号 O\_E の間で論理演算を行う。論理演算回路の出力は、バッファを経由して、対応する走査線 G\_i と制御配線に与えられる。このようにゲートドライバ回路 1 2 は、走査線 G\_i を用いて書き込み対象の画素回路を選択する走査信号出力回路として機能する。10

#### 【0048】

ソースドライバ回路 1 3 は、m ビットのシフトレジスタ 2 1、レジスタ 2 2、ラッチ回路 2 3、および、m 個の D / A 変換器 2 4 を含んでいる。シフトレジスタ 2 1 は、縦続接続された m 個の 1 ビットレジスタを含んでいる。シフトレジスタ 2 1 は、クロック C\_L\_K に同期してスタートパルス S\_P を順次転送し、各段のレジスタからタイミングパルス D\_L\_P を出力する。タイミングパルス D\_L\_P の出力タイミングに合わせて、レジスタ 2 2 には表示データ D\_A が供給される。レジスタ 2 2 は、タイミングパルス D\_L\_P に従い、表示データ D\_A を記憶する。レジスタ 2 2 に 1 行分の表示データ D\_A が記憶されると、表示制御回路 1 1 はラッチ回路 2 3 に対してラッチパルス L\_P を出力する。ラッチ回路 2 3 は、ラッチパルス L\_P を受け取ると、レジスタ 2 2 に記憶された表示データを保持する。D / A 変換器 2 4 は、各データ線 S<sub>j</sub> に 1 つずつ設けられる。D / A 変換器 2 4 は、ラッチ回路 2 3 に保持された表示データをアナログ信号電圧に変換し、対応するデータ線 S<sub>j</sub> に与える。このようにソースドライバ回路 1 3 は、データ線 S<sub>j</sub> に対して表示データに応じた電位を与える表示信号出力回路として機能する。20

#### 【0049】

なお、ここではソースドライバ回路 1 3 は、1 本の走査線に接続された画素回路に対して 1 行分の表示データに応じた電位を同時に供給する線順次走査を行うこととしたが、これに代えて、各画素回路に対して表示データに応じた電位を順に供給する点順次走査を行ってもよい。点順次走査を行うソースドライバ回路の構成は公知であるので、ここでは説明を省略する。30

#### 【0050】

以下、各実施形態に係る表示装置に含まれる画素回路 A<sub>i</sub><sub>j</sub> の詳細を説明する。画素回路 A<sub>i</sub><sub>j</sub> に含まれる駆動用 TFT、スイッチ用 TFT および有機 E\_L 素子は、それぞれ、駆動素子、スイッチング素子および電気光学素子として機能する。電源配線 V\_p は第 1 の配線に相当し、共通陰極 V\_com は第 2 の配線に相当する。

#### 【0051】

（第 1 の実施形態）40

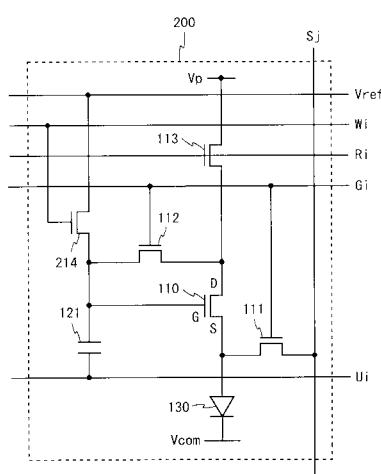

図 2 は、本発明の第 1 の実施形態に係る表示装置に含まれる画素回路の回路図である。図 2 に示す画素回路 1 0 0 は、駆動用 TFT 1 1 0、スイッチ用 TFT 1 1 1 ~ 1 1 3、コンデンサ 1 2 1、および、有機 E\_L 素子 1 3 0 を備えている。画素回路 1 0 0 に含まれる TFT は、いずれも n チャネル型である。

#### 【0052】

画素回路 1 0 0 は、電源配線 V\_p、共通陰極 V\_com、走査線 G\_i、制御配線 R\_i、U\_i およびデータ線 S<sub>j</sub> に接続されている。このうち、電源配線 V\_p と共に共通陰極 V\_com には、それぞれ、一定の電位 V\_DD、V\_SS（ただし、V\_DD > V\_SS）が印加される。共通陰極 V\_com は、表示装置内のすべての有機 E\_L 素子 1 3 0 に共通する陰極である。

#### 【0053】

50

30

40

50

図2でG、SおよびDと記載した駆動用TFT110の端子を、それぞれ、ゲート端子、ソース端子およびドレイン端子という。一般にnチャネル型TFTでは、2個の電流入出力端子のうち、印加電圧の低いほうをソース端子といい、印加電圧の高いほうをドレイン端子という。また、pチャネル型TFTでは、2個の電流入出力端子のうち、印加電圧の低いほうをドレイン端子といい、印加電圧の高いほうをソース端子という。しかし、電圧の大小関係に応じて端子名を変更すると説明が複雑になるので、電圧の大小関係が逆になります。2個の電流入出力端子を逆の名称で呼ぶべき場合でも、2個の端子を便宜上図示した名称で呼ぶこととする。また、本実施形態では、すべてのTFTにnチャネル型を用いているが、スイッチ用TFTにpチャネル型を用いてもよい。この場合、ローレベル電位が導通状態に、ハイレベル電位が非導通状態に対応し、導通状態の電位と非導通状態の電位は、スイッチ用TFTにnチャネル型を用いた場合と比べて逆になる。以上の点は、第2の実施形態でも同様である。10

#### 【0054】

画素回路100では、電源配線V<sub>p</sub>と共に陰極V<sub>com</sub>とを結ぶ経路上に電源配線V<sub>p</sub>側から順に、スイッチ用TFT113、駆動用TFT110および有機EL素子130が直列に設けられている。駆動用TFT110のソース端子とデータ線S<sub>j</sub>との間にはスイッチ用TFT111が設けられ、駆動用TFT110のゲート端子とドレイン端子との間にはスイッチ用TFT112が設けられ、駆動用TFT110のゲート端子と制御配線U<sub>i</sub>との間にはコンデンサ121が設けられている。スイッチ用TFT111、112のゲート端子はいずれも走査線G<sub>i</sub>に接続され、スイッチ用TFT113のゲート端子は制御配線R<sub>i</sub>に接続されている。画素回路100の動作は、表示制御回路11から供給された信号に基づき動作するゲートドライバ回路12とソースドライバ回路13によって制御される。20

#### 【0055】

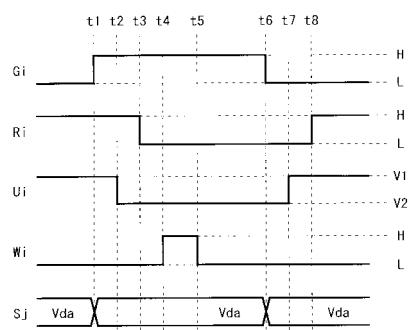

図3は、画素回路100のタイミングチャートである。図3には、走査線G<sub>i</sub>、制御配線R<sub>i</sub>、U<sub>i</sub>およびデータ線S<sub>j</sub>の電位の変化が記載されている。なお、以下の説明において、走査線G<sub>i</sub>の電圧がハイレベルである期間では有機EL素子130を非発光状態に制御する理由は、この期間に有機EL素子130が発光すると、黒表示を行うときの輝度がその分だけ上昇し、画面のコントラストが低下するからである。

#### 【0056】

時刻t1より前では、走査線G<sub>i</sub>の電位はローレベルに、制御配線R<sub>i</sub>の電位はハイレベルに、制御配線U<sub>i</sub>の電位は相対的に高い電位V<sub>1</sub>に制御される。このため、スイッチ用TFT111、112は非導通状態、スイッチ用TFT113は導通状態にある。このとき駆動用TFT110は導通状態にあるので、電源配線V<sub>p</sub>からスイッチ用TFT113と駆動用TFT110を経由して有機EL素子130に電流が流れ、有機EL素子130は所定の輝度で発光する。30

#### 【0057】

次に時刻t1において、走査線G<sub>i</sub>の電位がハイレベルに変化すると共に、データ線S<sub>j</sub>に新たなデータ電位V<sub>da</sub>が印加される。このため、スイッチ用TFT111、112は導通状態になり、データ線S<sub>j</sub>からスイッチ用TFT111を経由して駆動用TFT110のソース端子にデータ電位V<sub>da</sub>が印加される。40

#### 【0058】

ただし、このときに印加されるデータ電位V<sub>da</sub>は、有機EL素子130が非発光状態となるように決定される。具体的には、共通陰極V<sub>com</sub>の電位をV<sub>SS</sub>、有機EL素子130の発光閾値電圧をV<sub>th\_oled</sub>としたとき、データ電位V<sub>da</sub>は、電位V<sub>SS</sub>との差が発光閾値電圧V<sub>th\_oled</sub>以下になるように決定される。これを式で表すと、次式(1)のようになる。

$$V_{th\_oled} \leq V_{da} - V_{SS} \dots (1)$$

#### 【0059】

また、スイッチ用TFT112が導通状態にあるので、駆動用TFT110のゲート・50

ドレイン間は短絡され、駆動用 TFT110 のゲート端子とドレイン端子には電源配線 V<sub>p</sub> から電位 V<sub>DD</sub> が印加される。したがって、駆動用 TFT110 のゲート・ソース間電圧 V<sub>gs</sub> は、次式(2)のようになる。

$$V_{gs} = V_{DD} - V_{da} \dots (2)$$

#### 【0060】

次に時刻 t<sub>2</sub>において、制御配線 U<sub>i</sub> の電位が相対的に低い電位 V<sub>2</sub> に変化する。次に時刻 t<sub>3</sub>において、制御配線 R<sub>i</sub> の電位がローレベルに変化する。このため、スイッチ用 TFT113 は非導通状態になり、駆動用 TFT110 のゲート端子（および、これに短絡されたドレイン端子）からソース端子に電流が流れ、駆動用 TFT110 のゲート電位は徐々に下降する。駆動用 TFT110 のゲート・ソース間電圧が駆動用 TFT110 の閾値電圧 V<sub>th</sub> に等しくなったときに（すなわち、ゲート電位が (V<sub>da</sub> + V<sub>th</sub>) になったときに）、駆動用 TFT110 は非導通状態になり、駆動用 TFT110 のゲート電位はその後は下降しなくなる。この時点で、駆動用 TFT110 は、閾値電圧 V<sub>th</sub> にかかるわらず、ゲート・ソース間に閾値電圧 V<sub>th</sub> が印加された状態になる。また、コンデンサ S121 の電極間の電位差は (V<sub>da</sub> + V<sub>th</sub> - V<sub>2</sub>) になる。これ以降、コンデンサ S121 にはこの電位差が保持される。10

#### 【0061】

次に時刻 t<sub>4</sub>において、走査線 G<sub>i</sub> の電位がローレベルに変化する。このため、スイッチ用 TFT111、112 は非導通状態になる。次に時刻 t<sub>5</sub>において、制御配線 U<sub>i</sub> の電位が V<sub>2</sub> から V<sub>1</sub> に変化する。制御配線 U<sub>i</sub> と駆動用 TFT110 のゲート端子はコンデンサ S121 を介して接続されているので、制御配線 U<sub>i</sub> の電位が変化すると、駆動用 TFT110 のゲート電位は同じ量 (V<sub>1</sub> - V<sub>2</sub>) だけ変化する。このため、駆動用 TFT110 のゲート電位 V<sub>g</sub> は、次式(3)のようになる。20

$$V_g = V_{da} + V_{th} + V_1 - V_2 \dots (3)$$

#### 【0062】

最後に時刻 t<sub>6</sub>において、制御配線 R<sub>i</sub> の電位がハイレベルに変化する。このため、スイッチ用 TFT113 が導通状態になり、駆動用 TFT110 のドレイン端子には電源配線 V<sub>p</sub> から電位 V<sub>DD</sub> が印加される。また、コンデンサ S121 には電位差 (V<sub>da</sub> + V<sub>th</sub> - V<sub>2</sub>) が保持されているので、駆動用 TFT110 のゲート電位は時刻 t<sub>6</sub> 以降も (V<sub>da</sub> + V<sub>th</sub> + V<sub>1</sub> - V<sub>2</sub>) となる。このため、電源配線 V<sub>p</sub> から共通陰極 V<sub>com</sub> には、駆動用 TFT110 のゲート電位 (V<sub>da</sub> + V<sub>th</sub> + V<sub>1</sub> - V<sub>2</sub>) から駆動用 TFT110 の閾値電圧 V<sub>th</sub> を引いた電圧 (V<sub>da</sub> + V<sub>1</sub> - V<sub>2</sub>) に応じた電流が流れ、有機 EL 素子 S130 は当該電流に応じた輝度で発光する。30

#### 【0063】

そこで、走査線 G<sub>i</sub> の電位がハイレベルである期間（時刻 t<sub>1</sub> から時刻 t<sub>4</sub>）にデータ線 S<sub>j</sub> に印加されるデータ電位 V<sub>da</sub> は、有機 EL 素子 S130 を所望の輝度で発光させるために本来印加すべきデータ電位 V<sub>da'</sub> から制御配線 U<sub>i</sub> の電位の振幅分 (V<sub>1</sub> - V<sub>2</sub>) を引いた電位に設定される。これを式で表すと、次式(4)のようになる。

$$V_{da} = V_{da'} - (V_1 - V_2) \dots (4)$$

#### 【0064】

式(4)で求めたデータ電位 V<sub>da</sub> をデータ線 S<sub>j</sub> に印加し、制御配線 U<sub>i</sub> の電位を (V<sub>1</sub> - V<sub>2</sub>) だけ変化させることにより、駆動用 TFT110 の閾値電圧 V<sub>th</sub> のばらつきを補償しながら、有機 EL 素子 S130 を所望の輝度で発光させることができる。40

#### 【0065】

図 3 に示すように、ゲートドライバ回路 12 は、制御配線 U<sub>i</sub> の電位を 2 段階 (V<sub>1</sub> と V<sub>2</sub>) に変化させる。このため、ゲートドライバ回路 12 の最終段には、バッファ回路として、図 4 に示すインバータ回路が設けられる。図 4 に示すインバータ回路は、入力信号 IN に応じて、制御配線 U<sub>i</sub> の電位を 2 段階に変化させる。

#### 【0066】

制御配線 U<sub>i</sub> の電位を 3 段階以上に変化させるためには、図 4 よりも複雑な回路が必要50

になり、ドライバ回路の面積が増大する。このため、ドライバ回路をガラス基板上に形成する場合には、額縁の拡大と歩留りの低下が問題になり、ドライバ回路を I C に内蔵する場合には、チップ面積の増大に伴うコストの上昇と歩留りの低下、および、回路の複雑化に伴う消費電力の増大が問題となる。本実施形態に係る表示装置は、制御配線 U i の電位を 2 段階に変化させるゲートドライバ回路 1 2 を備えている。このようなゲートドライバ回路は、簡単に構成することができる。

#### 【 0 0 6 7 】

以上に示すように、本実施形態に係る表示装置は、複数の画素回路 1 0 0 、ゲートドライバ回路 1 2 およびソースドライバ回路 1 3 を備え、画素回路 1 0 0 は、駆動用 TFT 1 1 0 、スイッチ用 TFT 1 1 1 ~ 1 1 3 、コンデンサ 1 2 1 および有機 EL 素子 1 3 0 を含んでいる。また、ソースドライバ回路 1 3 は、データ線 S j に対して有機 EL 素子 1 3 0 への印加電圧が発光閾値電圧 V t h \_ o l e d 以下となる電位を与え、ゲートドライバ回路 1 2 は、制御配線 U i の電位を 2 段階 ( V 1 と V 2 ) に変化させる。10

#### 【 0 0 6 8 】

このようにデータ線 S j には有機 EL 素子 1 3 0 への印加電圧が発光閾値電圧 V t h \_ o l e d 以下となる電位が与えられるので、データ線 S j の電位を画素回路 1 0 0 に書き込んだだけでは有機 EL 素子 1 3 0 は発光せず、制御配線 U i の電位が V 1 に変化した後に有機 EL 素子 1 3 0 は発光する。また、スイッチ用 TFT 1 1 2 を導通状態に、スイッチ用 TFT 1 1 3 を非導通状態に制御することにより、駆動用 TFT 1 1 0 のゲート・ソース間に閾値電圧 V t h を印加することができる。その状態で、駆動用 TFT 1 1 0 が導通状態となる電位を制御配線 U i に印加することにより、駆動用 TFT 1 1 0 の閾値電圧 V t h にかかわらず、駆動用 TFT 1 1 0 を所望の輝度で発光させることができる。このように、駆動用 TFT 1 1 0 の閾値電圧 V t h のばらつきを補償しながら、データ電位 V d a を画素回路 1 0 0 に書き込むときに、共通陰極 V c o m の電位を固定したままで有機 EL 素子 1 3 0 を非発光状態にすることができる。20

#### 【 0 0 6 9 】

このため、ある画素回路 1 0 0 に書き込みを行っている間も他の画素回路 1 0 0 の有機 EL 素子 1 3 0 は発光し続けるので、ある画素回路に書き込みを行っている間は他の画素回路の有機 EL 素子が発光しなくなる表示装置よりも、発光デューティー比は高くなり、表示品位も高くなる。また、共通陰極 V c o m の電位を分割して制御する必要はないので、有機 EL 素子 1 3 0 の陰極をパターニングする必要もなく、その分だけ表示装置のコストは低くなる。また、制御配線 U i の電位を 2 段階に変化させるゲートドライバ回路 1 2 は簡単に構成することができる。したがって、発光デューティー比が高く、有機 EL 素子 1 3 0 の陰極のパターニングが不要な、高表示品位かつ低コストの表示装置（有機 EL ディスプレイ）を得ることができる。30

#### 【 0 0 7 0 】

また、駆動用 TFT 1 1 0 と画素回路 1 0 0 内のすべてのスイッチング素子（スイッチ用 TFT 1 1 1 ~ 1 1 3 ）を TFT で構成することにより、表示装置を容易かつ高性能に製造することができる。特に、駆動用 TFT 1 1 0 と画素回路 1 0 0 内のすべてのスイッチング素子を n チャネル型トランジスタで構成することにより、すべてのトランジスタを同じマスクを用いて同じプロセスで製造し、表示装置のコストを下げることができる。また、同じチャネル型のトランジスタは異なるチャネル型のトランジスタよりも接近して配置できるので、同じ面積により多くのトランジスタを配置することができる。40

#### 【 0 0 7 1 】

なお、本実施形態に係る表示装置については、各種の変形例を構成することができる。例えば、画素回路 1 0 0 ではスイッチ用 TFT 1 1 1 、 1 1 2 のゲート端子を同じ配線（走査線 G i ）に接続することとしたが、スイッチ用 TFT 1 1 1 、 1 1 2 のゲート端子を別の制御配線に接続し、2 本の制御配線の電位をほぼ同じタイミングで変化させてもよい（第 1 の変形例）。

#### 【 0 0 7 2 】

50

また、時刻  $t_1$  から時刻  $t_4$ までの間（スイッチ用 TFT111 が導通状態にある間）に駆動用 TFT110 のソース端子まで流れた電流は、有機 EL 素子 130 の抵抗成分とスイッチ用 TFT111 の導通時の抵抗成分とに応じて、有機 EL 素子 130 とスイッチ用 TFT111 に流れる。一般に、有機 EL 素子の寿命は、電流を多く流すほど短くなる。そこで、有機 EL 素子 130 に電流が流れることを防止するために、データ電位  $V_{da}$  を共通陰極  $V_{com}$  の電位  $V_{SS}$  以下にしてもよい（第 2 の変形例）。これを式で表すと、次式（5）のようになる。

$$V_{da} < V_{SS} \dots (5)$$

#### 【0073】

式（5）を満たすデータ電位  $V_{da}$  を使用すれば、有機 EL 素子 130 の陽極と陰極は同電位になるか、有機 EL 素子 130 に逆方向バイアス電圧が印加されるかのいずれかになる。したがって、時刻  $t_1$  から時刻  $t_4$ までの間（スイッチ用 TFT111 が導通状態にある間）に有機 EL 素子 130 に電流が流れることを防止し、有機 EL 素子 130 の寿命を延ばすことができる。10

#### 【0074】

また、図 3 では、走査線  $G_i$  の電位をハイレベルに変化させた後に、制御配線  $U_i$  の電位を低くする（ $V_1$  から  $V_2$  に変化させる）こととしたが、走査線  $G_i$  の電位をハイレベルに変化させるより前に、制御配線  $U_i$  の電位を低くしてもよい（第 3 の変形例）。この方法によれば、走査線  $G_i$  の本数が多く、走査線  $G_i$  の電位がハイレベルである時間が短い場合でも、駆動用 TFT110 の閾値電圧  $V_{th}$  のばらつきを補償することができる。20

ただし、この方法を用いると、有機 EL 素子 130 に順方向バイアス電圧が印加されて、有機 EL 素子 130 が不要に発光し、画面のコントラストが低下することがある。したがって、図 3 に示すように、走査線  $G_i$  の電位をハイレベルに変化させた後に、制御配線  $U_i$  の電位を低くするほうがより好ましい。

#### 【0075】

また、ゲートドライバ回路 12 に、制御配線  $U_i$  の電位を高くするタイミング（図 3 では時刻  $t_5$ ）を調整する機能を設けてもよい（第 4 の変形例）。このように制御配線  $U_i$  の電位の変化タイミングを調整することにより、有機 EL 素子 130 の発光期間の長さを調整し、有機 EL 素子 130 の発光デューティー比を調整することができる。したがって、有機 EL ディスプレイのように、ホールド型表示を行う表示装置の欠点である動画ぼやけを解消することができる。30

#### 【0076】

また、ゲートドライバ回路 12 に、制御配線  $R_i$  の電位をハイレベルにするタイミング（図 3 では時刻  $t_6$ ）を調整する機能を設けてもよい（第 5 の変形例）。このように制御配線  $R_i$  の電位の変化タイミングを調整することにより、有機 EL 素子 130 の発光期間の長さを調整し、有機 EL 素子 130 の発光デューティー比を調整することができる。したがって、第 4 の変形例に係る表示装置と同様の効果が得られる。

#### 【0077】

##### （第 2 の実施形態）

図 5 は、本発明の第 2 の実施形態に係る表示装置に含まれる画素回路の回路図である。40

図 5 に示す画素回路 200 は、駆動用 TFT110、スイッチ用 TFT111～113、214、コンデンサ 121、および、有機 EL 素子 130 を備えている。画素回路 200 に含まれる TFT は、いずれも n チャネル型である。本実施形態の構成要素のうち、第 1 の実施形態と同一の要素については、同一の参照符号を付して説明を省略する。

#### 【0078】

画素回路 200 は、第 1 の実施形態に係る画素回路 100 に対して、電源配線  $V_{ref}$  と制御配線  $W_i$  を追加し、電源配線  $V_{ref}$  と駆動用 TFT110 のゲート端子との間にスイッチ用 TFT214 を設け、スイッチ用 TFT214 のゲート端子を制御配線  $W_i$  に接続する変更を施したものである。電源配線  $V_{ref}$  には、一定の初期電位  $V_{ini}$  が印加される。50

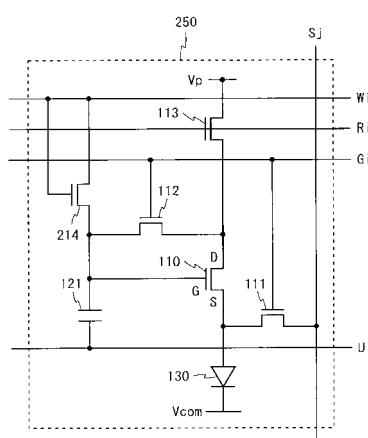

### 【0079】

図6は、画素回路200のタイミングチャートである。図6には、走査線G<sub>i</sub>、制御配線R<sub>i</sub>、U<sub>i</sub>、W<sub>i</sub>およびデータ線S<sub>j</sub>の電位の変化が記載されている。時刻t4より前では、制御配線W<sub>i</sub>の電位はローレベルに制御される。このため、スイッチ用TFT214は非導通状態であり、画素回路200は画素回路100と同様に動作する。ただし、画素回路100では時刻t3から時刻t4までの間に駆動用TFT110のゲート・ソース間に閾値電圧V<sub>th</sub>が印加される必要があるが、画素回路200ではその必要はない。

### 【0080】

次に時刻t4において、制御配線W<sub>i</sub>の電位がハイレベルに変化する。このため、スイッチ用TFT214は導通状態になり、電源配線V<sub>ref</sub>からスイッチ用TFT214を経由して駆動用TFT110のゲート端子とドレイン端子に初期電位V<sub>ini</sub>が印加される。ただし、初期電位V<sub>ini</sub>は、駆動用TFT110が導通状態となるように決定される。具体的には、初期電位V<sub>ini</sub>は、すべての画素回路200において、駆動用TFT110のソース電位V<sub>da</sub>との差が駆動用TFT110の閾値電圧V<sub>th</sub>以上となるよう决定される。これを式で表すと、次式(6)のようになる。

$$V_{th} \leq V_{ini} - (V_{da} \text{ の最大値}) \dots (6)$$

### 【0081】

次に時刻t5において、制御配線W<sub>i</sub>の電位がローレベルに変化する。このため、スイッチ用TFT214は非導通状態になり、駆動用TFT110のゲート端子（および、これに短絡されたドレイン端子）からソース端子に電流が流れ、駆動用TFT110のゲート電位は徐々に下降する。駆動用TFT110のゲート・ソース間電圧が駆動用TFT110の閾値電圧V<sub>th</sub>に等しくなったときに、駆動用TFT110は非導通状態になり、駆動用TFT110のゲート電位はその後は下降しなくなる。この時点で、駆動用TFT110は、閾値電圧V<sub>th</sub>にかかわらず、ゲート・ソース間に閾値電圧V<sub>th</sub>が印加された状態になる。また、コンデンサ121の電極間の電位差は(V<sub>da</sub> + V<sub>th</sub> - V<sub>2</sub>)になる。これ以降、コンデンサ121にはこの電位差が保持される。時刻t6以降、画素回路200は、画素回路100の時刻t4以降と同様に動作する。

### 【0082】

以上に示すように、画素回路200は駆動用TFT110のゲート端子と電源配線V<sub>ref</sub>との間にスイッチ用TFT214を備え、電源配線V<sub>ref</sub>には駆動用TFT110が導通状態となる電位が与えられる。したがって、スイッチ用TFT214を導通状態に制御することにより、電源配線V<sub>p</sub>の電位V<sub>DD</sub>を駆動用TFT110のゲート端子に印加することなく、駆動用TFT110のゲート・ソース間の閾値電圧V<sub>th</sub>を印加することができる。したがって、本実施形態に係る表示装置によれば、消費電力を削減することができる。また、電源配線V<sub>ref</sub>に駆動用TFT110が導通状態となる電位を与えることにより、駆動用TFT110のゲート・ソース間に閾値電圧V<sub>th</sub>を印加するまでの時間を短縮し、解像度の高い表示装置を構成することが可能となる。

### 【0083】

なお、本発明の表示装置については、各種の変形例を構成することができる。例えば、第2の実施形態に係る表示装置についても、第1の実施形態と同様に、第1～第5の変形例を構成してもよい。

### 【0084】

また、本発明の表示装置は、図7に示す画素回路を備えていてもよい。図7に示す画素回路250は、画素回路200に対して、スイッチ用TFT214の一端を制御配線W<sub>i</sub>に接続し、電源配線V<sub>ref</sub>を削除する変更を施したものである。このようにスイッチ用TFT214のゲート端子を他の端子と同じ配線に接続することにより、配線を1本削減し、表示装置の開口率や歩留まりを高くすることができる。

### 【0085】

また、以上の説明では、画素回路は電気光学素子として有機EL素子を含むこととしたが、画素回路は電気光学素子として、半導体LED(Light Emitting Diode)やFEDの

10

20

30

40

50

発光部など、有機 E L 素子以外の電流駆動型の電気光学素子を含んでいてもよい。

#### 【 0 0 8 6 】

また、以上の説明では、画素回路は、電気光学素子の駆動素子として、ガラス基板などの絶縁基板上に形成されるMOSトランジスタ（ここでは、シリコンゲートMOS構造を含めて、MOSトランジスタという）であるTFTを含むこととした。これに限らず、画素回路は、電気光学素子の駆動素子として、電流制御端子に印加する制御電圧に応じて出力電流が変化し、出力電流がゼロとなる制御電圧（閾値電圧）を有する任意の電圧制御型の素子を含んでいてもよい。このため、電気光学素子の駆動素子には、例えば、半導体基板上に形成されるMOSトランジスタなども含む、一般的の絶縁ゲート型電界効果トランジスタを用いることができる。駆動素子として絶縁ゲート型電界効果トランジスタを用いることにより、駆動素子の閾値電圧のばらつきを補償するときに、駆動素子を流れる電流が電気光学素子に流れることを防止することができる。これにより、電気光学素子の不要な発光を防止し、画面のコントラストを高め、電気光学素子の劣化を抑制することができる。

。

#### 【 0 0 8 7 】

また、以上の説明では、画素回路はスイッチング素子としてTFTを含むこととしたが、画素回路はスイッチング素子として、半導体基板上に形成されるMOSトランジスタなども含む、一般的の絶縁ゲート型電界効果トランジスタを含んでいてもよい。

#### 【 0 0 8 8 】

また、本発明は上述した各実施形態に限定されるものではなく、種々の変更が可能である。異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態も、本発明の技術的範囲に含まれる。

20

#### 【 産業上の利用可能性 】

#### 【 0 0 8 9 】

本発明の表示装置は、発光デューティー比が高く、電気光学素子の一方の電極のパターニングが不要で、高表示品位かつ低コストであるという効果を奏するので、有機 E L ディスプレイや FED など、電流駆動型の表示素子を備えた各種の表示装置に利用することができる。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 2 D

G 09 G 3/20 6 6 0 V

G 09 G 3/20 6 2 2 C

G 09 G 3/20 6 2 2 D

G 09 G 3/20 6 2 4 B

(56)参考文献 特開2006-047787(JP,A)

特開2008-009080(JP,A)

特開2007-025192(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30

G09G 3/20

G09G 3/22