(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-103863

(P2007-103863A)

(43) 公開日 平成19年4月19日(2007.4.19)

| (51) Int.C1. | F 1 | HO 1 L 21/82 (2006.01)   | HO 1 L 21/82 | W       | 5 F 0 3 8 | テーマコード (参考) |

|--------------|-----|--------------------------|--------------|---------|-----------|-------------|

|              |     | HO 1 L 21/8238 (2006.01) | HO 1 L 27/08 | 3 2 1 F | 5 F 0 4 8 |             |

|              |     | HO 1 L 27/092 (2006.01)  | HO 1 L 27/08 | 3 2 1 D | 5 F 0 6 4 |             |

|              |     | HO 1 L 21/822 (2006.01)  | HO 1 L 27/04 | D       |           |             |

|              |     | HO 1 L 27/04 (2006.01)   | HO 1 L 21/82 | L       |           |             |

審査請求 未請求 請求項の数 6 O L (全 17 頁) 最終頁に続く

|           |                              |            |                                |

|-----------|------------------------------|------------|--------------------------------|

| (21) 出願番号 | 特願2005-295285 (P2005-295285) | (71) 出願人   | 302062931                      |

| (22) 出願日  | 平成17年10月7日 (2005.10.7)       |            | N E C エレクトロニクス株式会社             |

|           |                              |            | 神奈川県川崎市中原区下沼部1753番地            |

|           |                              | (74) 代理人   | 100102864                      |

|           |                              |            | 弁理士 工藤 実                       |

|           |                              | (72) 発明者   | 吉田 正利                          |

|           |                              |            | 神奈川県川崎市中原区下沼部1753番地            |

|           |                              |            | N E C エレクトロニクス株式会社内            |

|           |                              | F ターム (参考) | 5F038 BB01 BH10 BH19 CD02 CD03 |

|           |                              |            | CD04 CD06 DF01 DF14 EZ08       |

|           |                              |            | EZ20                           |

|           |                              |            | 5F048 AA01 AB03 AB08 AB10 AC03 |

|           |                              |            | BB05 BB14 BE02 BE03 BE05       |

|           |                              |            | BE09 BF12 BF18 BH01            |

|           |                              |            | 5F064 BB26 CC12 EE03 EE14 EE16 |

|           |                              |            | EE19 EE45 EE52 EE54            |

(54) 【発明の名称】半導体デバイス

## (57) 【要約】

【課題】半導体デバイスの閾値電圧の制御を実現しつつ、より小さな回路面積の半導体デバイスを提供する。

【解決手段】印加される基板バイアス ( $V_{nw}$ ) ( $V_{pw}$ ) に応答してMOSトランジスタ (14) (15) の閾値電圧を決定する半導体デバイス (1) において、前記半導体デバイス (1) は、基板バイアス ( $V_{nw}$ ) ( $V_{pw}$ ) を生成する基板バイアス生成部を具備する。また、前記半導体デバイス (1) は、クロック信号線 (3) と他の配線とをシールドするシールド配線 (4) (5) を具備する。そして、その基板バイアス生成部は、前記シールド配線 (4) (5) を介して前記基板バイアス ( $V_{nw}$ ) ( $V_{pw}$ ) を半導体基板 (12) (13) に印加する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

半導体基板に形成されたMOSトランジスタを有する半導体領域と、

クロック信号線と他の配線とをシールドするシールド配線と、

基板バイアスを生成し、前記シールド配線を介して前記基板バイアスを前記半導体領域

に印加する基板バイアス生成部と

を具備し、

印加される前記基板バイアスに応答して前記MOSトランジスタの閾値電圧を決定する

半導体デバイス。

**【請求項 2】**

請求項1に記載の半導体デバイスにおいて、

前記シールド配線は、

前記半導体基板表面の所定の領域を示す基板バイアス印加領域に対応して配置され、

前記基板バイアス生成部は、

前記シールド配線に接続され、前記シールド配線を介して前記基板バイアスを前記基板

バイアス印加領域に印加する

半導体デバイス。

**【請求項 3】**

請求項1または2に記載の半導体デバイスにおいて、

前記基板バイアス生成部は、

複数のバイアス生成回路を含み、

前記複数のバイアス生成回路の各々は、所定のシールド配線に接続され、前記所定のシ

ールド配線を介して前記基板バイアスを前記半導体領域に印加する

半導体デバイス。

**【請求項 4】**

請求項1から3の何れか1項に記載の半導体デバイスにおいて、

第1基板バイアスに応答して前記閾値電圧が決定される第1領域と、

第2基板バイアスに応答して前記閾値電圧が決定される第2領域と

を含み、

前記基板バイアス生成部は、

前記第1基板バイアスを生成する第1基板バイアス生成回路と、

前記第2基板バイアスを生成する第2基板バイアス生成回路と

を含み、

前記シールド配線は、

前記第1領域に配置される第1領域側シールド配線と、

前記第2領域に配置される第2領域側シールド配線と

を含み、

前記第1基板バイアス生成回路は、前記第1領域側シールド配線に接続され、前記第1

領域側シールド配線を介して前記第1基板バイアスを前記半導体領域に印加し、

前記第2基板バイアス生成回路は、前記第2領域側シールド配線に接続され、前記第2

領域側シールド配線を介して前記第2基板バイアスを前記半導体領域に印加する

半導体デバイス。

**【請求項 5】**

請求項1から4の何れか一項に記載の半導体デバイスにおいて、

前記シールド配線は、

前記クロック配線に沿って延伸する第1シールド配線と、

前記クロック配線を間に挟んで、前記第1シールド配線に沿って延伸する第2シール

ド配線と

を含み、

前記基板バイアス生成部は、

10

20

30

40

50

前記第1シールド配線と前記第2シールド配線の少なくとも一方に前記基板バイアスを印加する

半導体デバイス。

【請求項6】

印加される基板バイアスに応答してMOSトランジスタの閾値電圧を決定する半導体デバイスであって、

前記半導体デバイスは、

半導体基板と、

クロック信号線と他の配線とをシールドするシールド配線と、

前記基板バイアスを受ける基板バイアス供給端と

を具備し、

前記基板バイアス供給端を介して供給される前記基板バイアスは、前記シールド配線を介して前記半導体基板に印加される

半導体デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスに関する。

【背景技術】

【0002】

半導体製造技術の進歩に伴って、製造される半導体デバイスの微細化が進み、単位面積当たりの素子数を増加させることができが可能となってきている。例えば、同一記憶容量のメモリを作った場合において、1枚のシリコンウェハから取れるチップの数を増加させることができになり、それによって、1チップ当たりのコストを安くすることができる。また、同一面積のチップを作製した場合には、1チップ当たりの記憶容量を増加させ、より多くの情報を格納させることができとなっている。

【0003】

微細化によりトランジスタの動作時の電流密度及び静的なリーク電流が増大し、結果として半導体デバイスの消費電力が増大する場合がある。また、通常、半導体デバイスを高性能化するためには基本的には動作周波数を大きくしていくが、これに伴って消費電力が増えていく。

【0004】

消費電力を抑えるためには、微細化に応じて電源電圧及びしきい値電圧を低減させる技術が知られている。しかしながら、電源電圧の低減に対応させてトランジスタのしきい値電圧を低減させると、トランジスタのソース・ドレン間のオフリーケ電流が増大してしまう。

【0005】

リーク電流を抑えるために、基板バイアス(Body Bias)を用いる技術が知られている(例えば、特許文献1、2参照)。基板バイアスとは、MOSトランジスタの基板端子に印加する弱いバイアス電圧である。以下の説明においては、トランジスタに流れる電流が流れやすくなるような方向のバイアスを順方向基板バイアス、トランジスタに流れる電流が流れにくくなるような方向のバイアスを逆方向基板バイアスと呼ぶ。つまり、半導体デバイスに順方向基板バイアスを印加するとトランジスタのチャネル部に電流が流れやすくなり、トランジスタはより高速化、もしくは低電圧で動作する。また、半導体デバイスが停止しているとき(一般的に、待機モードなどと呼ばれているとき)に、逆方向基板バイアスを印加することで、リーク電流を減少させることができる。

【0006】

一般的に、半導体デバイスはPチャネルMOSトランジスタ(以下、PMOSトランジスタと呼ぶ)とNチャネルMOSトランジスタ(以下、NMOSトランジスタと呼ぶ)との少なくとも一方を含んで構成されている。通常、PMOSトランジスタは、P型半導体

10

20

30

40

50

基板に形成されるNウェル内部に構成され、そのNウェルを介してPMOSトランジスタ用基板バイアス（以下、Nウェル側基板バイアスV<sub>nw</sub>と呼ぶ）が印加される。また、NMOSトランジスタは、P型半導体基板またはPウェル内部に構成され、そのP型半導体基板またはPウェルを介してNMOSトランジスタ用基板バイアス（以下、Pウェル側基板バイアスV<sub>pw</sub>と呼ぶ）が印加されている。

#### 【0007】

順方向基板バイアスを印加する場合、MOSトランジスタの基板端子を構成しているP型半導体を高電位にするような電圧を印加し、また、n型半導体を低電位にするような電圧を印加する。つまり、各MOSトランジスタ（NMOSトランジスタ、及びPMOSトランジスタ）のソース電位を基準としてソース電位と基板電位との電位差を電圧V<sub>bs</sub>とすると、順方向基板バイアスとして、NMOSトランジスタでは、

電圧V<sub>bs</sub> > 0

また、PMOSトランジスタでは、

電圧V<sub>bs</sub> < 0

となるような電圧が印加される。

#### 【0008】

換言すると、PMOSトランジスタの基板端子を形成するNウェルでは、順方向基板バイアスとして電源電圧よりも低い電圧（以下、第1順方向基板バイアスV<sub>nw1</sub>と呼ぶ）が印加されることで電流が流れやすくなる。また、NMOSトランジスタの基板端子を形成するp型半導体基板（またはPウェル）では、順方向基板バイアスとして接地電圧よりも高い電圧（以下、第2順方向基板バイアスV<sub>pw1</sub>と呼ぶ）が印加されることで電流が流れやすくなり、それによって各トランジスタの高速動作が可能となる。

#### 【0009】

その逆に、逆方向基板バイアスを印加するときは、MOSトランジスタの基板端子を構成するp型半導体を低電位に、n型半導体を高電位にするような基板バイアスを印加する。つまり、各MOSトランジスタ（NMOSトランジスタ、及びPMOSトランジスタ）のソース電位を基準電位として、ソース電位と基板電位との電位差を電圧V<sub>bs</sub>とすると、逆方向基板バイアスとして、NMOSトランジスタでは、

電圧V<sub>bs</sub> < 0

また、PMOSトランジスタでは、

電圧V<sub>bs</sub> > 0

となるような電圧が印加される。

#### 【0010】

換言すると、PMOSトランジスタの基板端子を形成するNウェルでは、逆方向基板バイアスとして電源電圧よりも高い電圧（以下、第1逆方向基板バイアスV<sub>nw2</sub>と呼ぶ）が印加されることでリーク電流を抑制することが可能となる。同様に、NMOSトランジスタの基板端子を形成するP型半導体基板（またはPウェル）では、逆方向基板バイアスとして接地電圧よりも低い電圧（以下、第2逆方向基板バイアスV<sub>pw2</sub>と呼ぶ）が印加されることでリーク電流を抑制することが可能となる。

#### 【0011】

一方で、半導体デバイスの微細化、高集積化に伴って、隣接信号ネット間のカップリング容量などによるクロストークやスキューの影響は、無視できない状況となってきた。そのため、クロストークやスキューの影響を低減させるために、他の信号ネットへ交差する信号ネットや、他の信号ネットからの交差を防ぐ必要のある信号ネットの配線経路に對しては、これら各信号ネットの両側に電源ネットやグランドネットを配線してシールドする技術が知られている（例えば、特許文献3参照。）。

#### 【0012】

また、近年、半導体製造に関する多種多様な技術が提供されることで、従来に比べて比較的安価に半導体装置を製造することが可能になってきている。例えば、ゲートアレイなどにおいては、あらかじめ基本的な論理回路（ゲート）をチップ内部にアレイ状（配列状

10

20

30

40

50

)に作成して準備しておき、ユーザの要求に基づいて、配線層だけを設計、製造している。これによって、短期間かつ低コストで半導体装置を製造することが可能になってきている。このような状況の中で、ユーザの要求に対応して設計者が一から半導体の設計を行って製造される半導体装置の価値が高まっている。そのようなハンドメイドに近い状態で半導体装置を製造することによって、ユーザの要求を十分に満たすことが可能となる。そのような半導体装置において、上述のゲートアレイのように論理回路がアレイ状に配置されることは稀であり、所望の機能ブロックが偏在して配置される場合がある。

【0013】

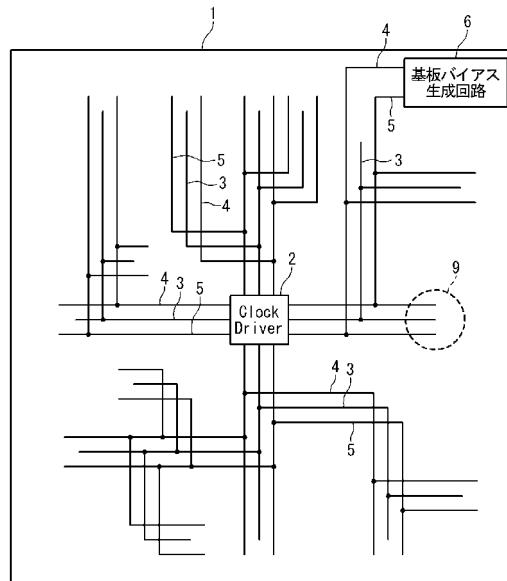

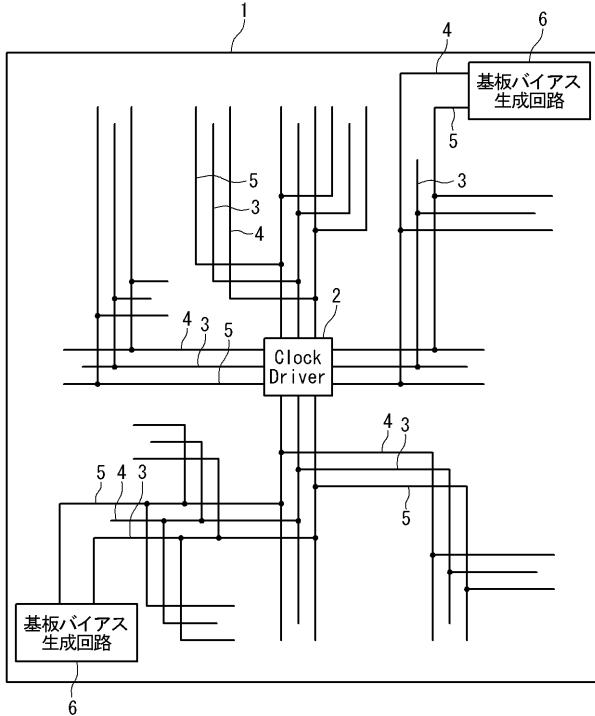

図1は、ハンドメイドに近い状態で製造され、上述の基板バイアスを供給する機能を有する従来の半導体チップ101の構成を示す平面図である。図1を参照すると、従来の半導体チップ101は、クロックドライバ102が outputするクロックを伝送するクロック配線103と、そのクロック配線103に伝わるクロックが他の信号線に与える影響を低減させるシールド配線(107、108)が備えられている。従来の半導体チップ101には、Nウェル側基板バイアスVnwを供給するVnwバイアスノード104と、Pウェル側基板バイアスVpwを供給するVpwバイアスノード105が備えられ、それぞれのバイアスノード(104、105)はメタル配線で構成されている。また、図1に示されているように、Vnwバイアスノード104とVpwバイアスノード105は、基板バイアス生成回路106に接続されている。

【0014】

上述のように、ハンドメイドに近い状態で半導体装置を製造する場合、論理回路がアレイ状に配置されることは稀であり、所望の機能ブロックが偏在して配置される場合がある。したがって、基板バイアスを供給するには、それぞれのバイアスノード(104、105)を、チップの空き領域を用いて所望の領域まで配線し、コンタクト110を介して基板バイアスを印加している。

【0015】

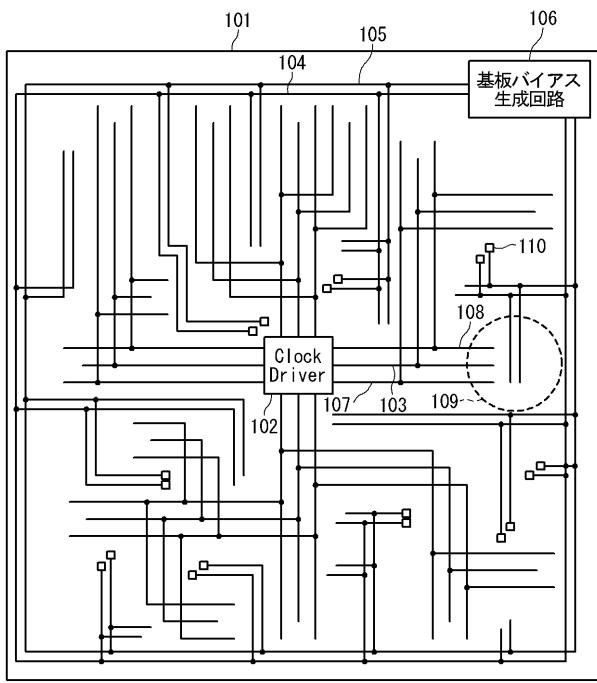

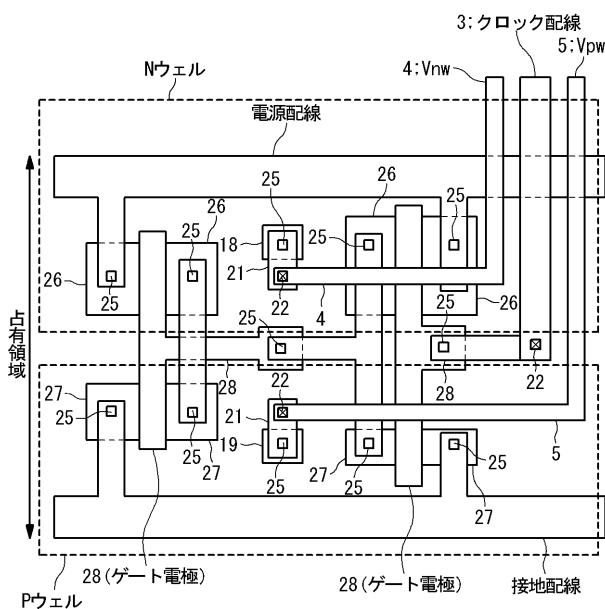

図2は、従来の半導体チップ101の一部(図1に示されている領域109)に備えられた半導体回路の構成を示す平面図である。図2に示されているように、従来の半導体回路は、p型半導体基板に形成されたNウェルを有し、そのNウェルにP拡散領域126を備えている。またp型半導体基板にはN拡散領域127が形成されている。従来の半導体チップ101は、N拡散領域127内のNMOSトランジスタとP拡散領域126内のPMOSトランジスタとで形成されるCMOSを含む半導体回路を構成している。図2に示されているように、CMOSを構成しているトランジスタはポリシリコン128で構成されたゲート電極を備え、そのゲート電極には、クロック配線103を介して供給される信号が印加されている。図2を参照すると、従来のチップ101において、それぞれのバイアスノード(104、105)を備えるためには、配線用の領域を確保する必要があった。つまり、従来の半導体デバイスにおいて、Vnwバイアスノード104とVpwバイアスノード105は、チップ配線(上述のクロック配線103、シールド配線107およびシールド配線108)とは異なるメタル配線で構成されていた。

【0016】

図2を参照すると、PMOSトランジスタを有するNウェルには、N+領域118が形成されている。そのN+領域118は、コンタクト110を介して基板バイアス供給ノード104に接続されている。つまり基板バイアス供給ノード104は、基板バイアス生成回路106から供給されるNウェル側基板バイアスVnwを、N+領域118を介してNウェルに印加している。また、同様に、従来の半導体チップ101は、p型半導体基板に形成されたP+領域119を備えて構成されている。図2に示されているように、そのP+領域119は、コンタクト110を介して基板バイアス供給ノード105に接続されている。基板バイアス供給ノード105は基板バイアス供給ノード104と同様に基板バイアス生成回路106に接続され、基板バイアス生成回路106から供給されるPウェル側基板バイアスVpwをP+領域を介してp型半導体基板に印加している。

【0017】

10

20

30

40

50

【特許文献1】特開2004-207749号公報

【特許文献2】特許第3184265号公報

【特許文献3】特許第3293588号公報

【発明の開示】

【発明が解決しようとする課題】

【0018】

上述したように、従来の技術において、 $V_{nw}$ バイアスノード104と $V_{pw}$ バイアスノード105を備えるためには、配線用の領域を確保することが必要であった。半導体デバイスが微細化されることに伴って、基板バイアスによる閾値電圧の制御を実現しつつ、回路が占有する面積を、より小さくすることが求められている。

10

【0019】

本発明が解決しようとする課題は、基板バイアスに基づいてトランジスタの閾値電圧が変わる半導体デバイスにおいて、基板バイアスによる閾値電圧の制御を実現しつつ、より小さな回路面積の半導体デバイスを提供することにある。

【課題を解決するための手段】

【0020】

以下に、[発明を実施するための最良の形態]で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

20

【0021】

上記課題を解決するために、以下のように半導体デバイスを構成する。そのデバイスは、印加される基板バイアス( $V_{nw}$ )( $V_{pw}$ )に応答してMOSトランジスタ(14)(15)の閾値電圧を決定する半導体デバイス(1)であって、前記半導体デバイス(1)は、半導体基板(11)と、クロック信号線(3)と他の配線とをシールドするシールド配線(4)(5)と、前記基板バイアス( $V_{nw}$ )( $V_{pw}$ )を生成し、前記シールド配線(4)(5)を介して前記基板バイアス( $V_{nw}$ )( $V_{pw}$ )を上記のMOSトランジスタ(14)(15)を有する半導体領域(12)(13)に印加する基板バイアス生成部とを具備する半導体デバイスであることが好ましい。ここで、上記シールド配線は、クロック信号線(3)を介して送られるクロック信号が他の配線に与える影響を抑制する機能と、他の配線を伝送する信号が、クロック信号線に与える影響をシールドする機能を有するメタル配線であることが好ましい。

30

【発明の効果】

【0022】

本発明によると、基板バイアスに基づいてトランジスタの閾値電圧が変わる半導体デバイスの閾値電圧の制御を実現しつつ、より小さな回路面積の半導体デバイスを提供することが可能となる。

40

【0023】

また、従来技術では、小さな配線領域にメタル配線を施すには、配線自身を細くするか、配線間隔を狭くする必要があり、どちらにしても応答遅延を発生させてしまう場合がある。本発明によると、半導体デバイスの微細化を実現しつつ、基板バイアスを印加するときの応答遅延が発生しにくい半導体デバイスを提供することが可能となる。

【発明を実施するための最良の形態】

【0024】

[第1の実施形態]

以下に、図面を参照して、本発明の半導体デバイスの実施形態について説明を行う。ここで、以下に述べる実施形態において、本発明の構成を採用する半導体デバイスが、1つのチップで構成され、通常動作を行なう場合の通常モードと、消費電力を低減させるために動作を停止する場合の待機モードとを有するデバイスである場合を例に説明をおこなう

50

。

## 【0025】

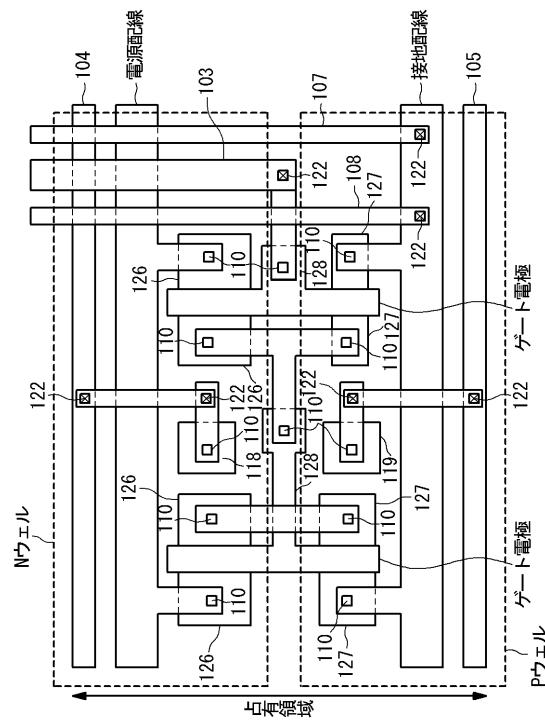

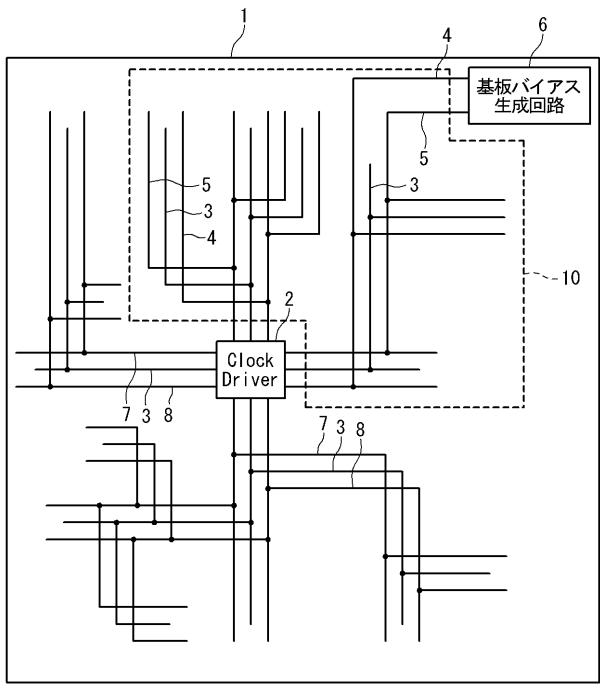

図3は、第1の実施形態における半導体デバイス1の構成を例示する平面図である。図3を参照すると、第1の実施形態の半導体デバイス1はクロックドライバ2と、そのクロックドライバ2から出力されるクロックを伝えるクロック配線3とを備えている。また、半導体デバイス1は、クロック配線3に沿って延伸されて配置されるNウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5とを備えている。図3に示されているように、Nウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5は、それぞれ基板バイアス生成回路6に接続されている。

## 【0026】

基板バイアス生成回路6は、半導体デバイス1を構成する半導体基板に形成されるMOSトランジスタに供給される基板バイアスを生成する回路である。以下の実施形態においては、基板バイアス生成回路6がチャージポンプ回路を含んで構成されていることを前提に説明を行う。なお、これは、本発明の半導体デバイス1を構成する基板バイアス生成回路6がチャージポンプ回路に限定されることを意味するものではない。また、以下の実施形態において、基板バイアスが供給されるMOSトランジスタは、基板に生成されるウェル内部に備えられていることを前提に説明を行う。

## 【0027】

基板バイアス生成回路6は、上述の通常モード時に順方向基板バイアス( $V_{nw1}$ 、 $V_{pw1}$ )を生成し、待機モード時に逆方向基板バイアス( $V_{nw2}$ 、 $V_{pw2}$ )を生成している。待機モード時には、それぞれの基板バイアス( $V_{nw}$ 、 $V_{pw}$ )が、Nウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5を介して上記ウェル内部のMOSトランジスタに供給されている。また、通常モード時には、Nウェル側基板バイアス供給ノード4を介して電源電位VDDを供給し、Pウェル側基板バイアス供給ノード5を介して接地電位GNDを供給することも可能である。

## 【0028】

以下に、本発明の半導体デバイス1における、各配線の構成について説明を行う。図4は、第1の実施形態の半導体デバイス1の一部(図3における領域9)に形成される半導体回路の構成を例示する平面図である。以下の実施形態において、その半導体回路が、p型半導体基板に形成されたPウェル内のNMOSトランジスタ15と、そのp型半導体基板に形成されたNウェル内のPMOSトランジスタ14とで構成されたCMOSを備える半導体回路である場合を例示して説明を行う。なお、この構成は、本発明を適用する半導体回路の構成を限定するものではない。

## 【0029】

図4を参照すると、第1の実施形態の半導体デバイス1に形成される半導体回路は、クロック配線3を挟むように配置されたNウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5を備えている。N拡散領域27はNウェルに形成されるN拡散領域を示し、P拡散領域26はNウェルに形成されるP拡散領域を示している。N+半導体領域18はNウェルに形成されるN+領域であり、P+半導体領域19はP+領域である。図4に示されているように、Nウェル側基板バイアスノード4は、メタル配線21を介してN+半導体領域18に接続されている。Nウェル側基板バイアスノード4とメタル配線21とはビア22を介して接続され、そのメタル配線21とN+半導体領域18とはコンタクト25を介して接続されている。同様に、Pウェル側基板バイアス供給ノード5は、メタル配線21を介してP+半導体領域19に接続されている。Pウェル側基板バイアス供給ノード5とメタル配線21とはビア22を介して接続され、そのメタル配線21とP+半導体領域19もコンタクト25を介して接続されている。また、図4に示されているように、CMOSを構成しているトランジスタはポリシリコン28で構成されたゲート電極を備え、そのゲート電極には、クロック配線3を介して供給される信号が印加されている。

## 【0030】

10

20

30

40

50

Nウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5によって、クロック配線3を伝わるクロックが他の信号線に与える影響を低減させるには、Nウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5が静電シールドの役割を果たせばよい。したがって、Nウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5の電位は、必ずしもグラウンド・レベルである必要がない。本実施形態の半導体デバイス1は、シールド配線を基板バイアス供給ノードとして作用させている。そのため、基板バイアスを供給する専用のメタル配線を構成する必要がないので、回路が占有するチップ面積の増加を抑制することが可能となる。

#### 【0031】

また、従来の半導体デバイス（例えば図1に示されるチップ101）では、上述したようにチップ配線とは異なる基板バイアスノードを備えて構成されている。そのため、従来の半導体デバイスでは、その設計段階において、設計者はチップ配線が施されていない空き領域を特定し、その空き領域に基板バイアスノードを配置させている。本実施形態の半導体デバイス1は、設計段階における新たな基板バイアスノードの配置作業を行う必要がないため、半導体設計にかかる時間を短縮することができる。

#### 【0032】

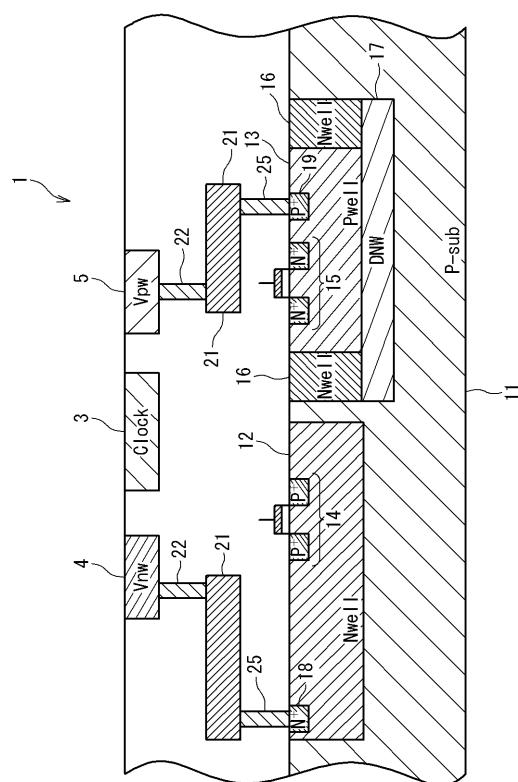

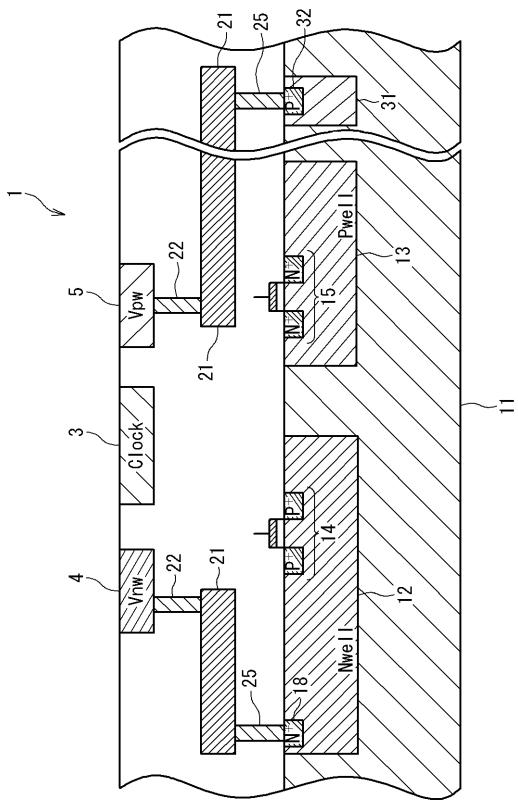

ここで、本実施形態の半導体デバイス1の構成に関して、断面図を用いて説明を行う。なお、以下の実施形態においては、本願発明の理解を容易にするために、一般的な構成の半導体デバイスに本願発明を適用した場合の断面図を用いて説明を行う。図5は、本実施形態における半導体デバイス1の断面の構成を例示する断面図である。以下の実施形態においては、半導体デバイス1が、p型半導体基板に形成されるNウェル12とPウェル13とを備え、それぞれのウェルにMOSトランジスタが形成されるデバイスである場合を例示して説明を行う。なお、これは本発明を適用する半導体デバイスが、図5に示されるような3層構成のデバイスにのみ用いられることを意味するものではない。

#### 【0033】

また詳細は後述するが、図5に示されるように、Pウェル13は半導体基板11から電気的に絶縁されている。したがって、複数のPウェル13が形成される場合に、それらが互いに半導体基板11から電気的に絶縁されることで、各Pウェル13に異なる電圧の基板バイアスを供給することが可能となる。同様に、半導体基板11に複数のNウェル12が形成される場合に、それら複数のNウェル12は互いに電気的に絶縁されることとなるので、したがって、各Nウェル12に対しても、異なる電圧の基板バイアスを供給することが可能である。

#### 【0034】

図5を参照すると、第1の実施形態の半導体デバイス1は、半導体基板11と、その半導体基板11の上部に形成されるメタル配線層とクロック配線層とを備えて構成されている。図5に示されているように、半導体基板11は、NMOSトランジスタ14を有するNウェル12を含んで構成されている。また同様に、半導体基板11は、PMOSトランジスタ15を有するPウェル13を含んで構成されている。図5に示されているように、Pウェル13は、Nウェル16およびディープNウェル17に囲まれた領域に備えられている。さらに、Nウェル12は、Nウェル側基板バイアスVnwを受けるN+半導体領域18を備え、Pウェル13は、Pウェル側基板バイアスVpwを受けるP+半導体領域19を備えている。

#### 【0035】

図5を参照すると、本実施形態の半導体デバイス1において、Nウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5とは、コンタクト25を介して各ウェル（12, 13）に接続されている。図5に示されているように、Nウェル側基板バイアス供給ノード4はビア22を介して下層に形成されているメタル配線21に接続され、そのメタル配線21は、コンタクト25を介してNウェル12のN+半導体領域18に接続されている。同様に、Pウェル側基板バイアス供給ノード5は、ビア22を介してメタル配線21に接続されている。そのメタル配線21は、コンタクト25を介してPウェル

10

20

30

40

50

13のP+半導体領域19に接続されている。

【0036】

上述したように、本実施形態における半導体デバイス1に備えられている基板バイアス生成回路6は、Nウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5に接続されている。基板バイアス生成回路6は、半導体デバイス1の動作状態が通常モードであるのか待機モードであるのかを示す制御信号に応答して、Nウェル側基板バイアスVnwとPウェル側基板バイアスVpwとを生成している。基板バイアス生成回路6から出力されるNウェル側基板バイアスVnwは、Nウェル側基板バイアス供給ノード4伝わって半導体基板11に形成されているNウェル12に供給される。同様に、基板バイアス生成回路6から出力されるPウェル側基板バイアスVpwは、Pウェル側基板バイアス供給ノード5を伝わってPウェル13に供給される。

【0037】

以下に、MOSトランジスタに印加される基板バイアスと、その時のMOSトランジスタの性能について説明を行う。上述したように、半導体デバイスに順方向基板バイアスを印加するとトランジスタのチャネル部に電流が流れやすくなり、トランジスタはより高速化、もしくは低電圧で動作する。また、半導体デバイスが停止しているとき（つまり、待機モードのとき）に、逆方向基板バイアスを印加することで、リーコンデンサ電流を減少させることができる。

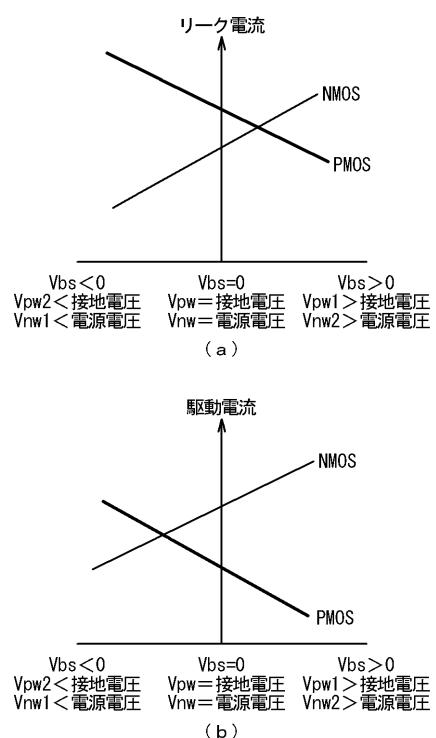

【0038】

図6は、基板バイアスとMOSトランジスタの性能との関連性を示すグラフである。図6には上述の電圧Vbsを変化させた場合におけるMOSトランジスタの性能の変化が示されている。ここで、図6(a)は、印加される基板バイアスとリーコンデンサ電流との関連を示すグラフであり、図6(b)は、印加される基板バイアスとMOSトランジスタの駆動電流との関連を示すグラフである。図6の横軸は、電圧Vbsを示し、中心が0、右側が正側の大きさ、左側が負側の大きさを示している。換言すると、横軸右側は、第1逆方向基板バイアスVnw2を電源電圧より大きくしていった場合（または第2逆方向基板バイアスVpw2を接地電圧より小さくしていった場合）を示している。

【0039】

上述したように、逆方向基板バイアスを印加するときは、MOSトランジスタの基板端子を構成するp型半導体を低電位に、n型半導体を高電位にするような基板バイアスを印加する。つまり、ソース電位を基準電位としたとき、各MOSトランジスタ（NMOSトランジスタ、及びPMOSトランジスタ）の基板電位のソース電位との電位差を電圧Vbsとすると、NMOSトランジスタでは、

電圧Vbs < 0

また、PMOSトランジスタでは、

電圧Vbs > 0

となるような電圧が逆方向基板バイアスとして作用する。

【0040】

図6(a)を参照すると、第1逆方向基板バイアスVnw2を電源電圧より大きくしていった場合（または第2逆方向基板バイアスVpw2を接地電圧より小さくしていった場合）に、リーコンデンサ電流を減少させることができる。このとき、図6(b)に示されているようにMOSトランジスタのパフォーマンスは低下してしまう。半導体デバイス1が待機モードの場合には、パフォーマンスの向上が要求されることが少ない。そのため、半導体デバイス1の動作状態に対応して基板バイアスを変化させることにより、パフォーマンスと消費電力の最適なバランスを設定することが可能になる。

【0041】

換言すると、必要なパフォーマンスにあわせて基板バイアスを変化させることで、消費電力を最小化させることができる。つまり、パフォーマンスが要求されているときには、基板バイアス（逆方向基板バイアス）を印加しないことでMOSトランジスタの駆動能力を向上させている。反対に、パフォーマンスが要求されていない場合には、逆方向基板バ

イアスを印加する。逆方向基板バイアスの作用によって、リーク電流を減少させ結果として消費電力を低減させることが可能になる。特に、基板バイアスの制御を段階的に行うこととで、よりきめの細やかなパフォーマンスと消費電力のコントロールが可能になる。

#### 【0042】

本実施形態の半導体デバイス1は、上述してきたようにシールド配線として作用するNウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5を介してNウェル側基板バイアスV<sub>n w</sub>とPウェル側基板バイアスV<sub>p w</sub>とを印加し、それによってMOSトランジスタのパフォーマンスと消費電力のコントロール（リーク電流と工藤電流の最適化）を行っている。これによって、本実施形態の半導体デバイス1はチップ面積の増加を抑制しつつ、最適化されたパフォーマンスで動作する半導体デバイスを提供することが可能となる。また、順方向基板バイアス（V<sub>n w 1</sub>、V<sub>p w 1</sub>）を用いて半導体デバイスの性能を向上させる場合においても、当然に本発明の構成を適用することが可能である。

#### 【0043】

##### 〔第2の実施形態〕

以下に、図面を参照して、本発明の第2の実施形態について説明を行う。以下の説明において、第1の実施形態の説明に使用した符号と同じ符号が付されているものは、同様の構成・動作を有するものであるので、その詳細な説明に関しては省略する。

#### 【0044】

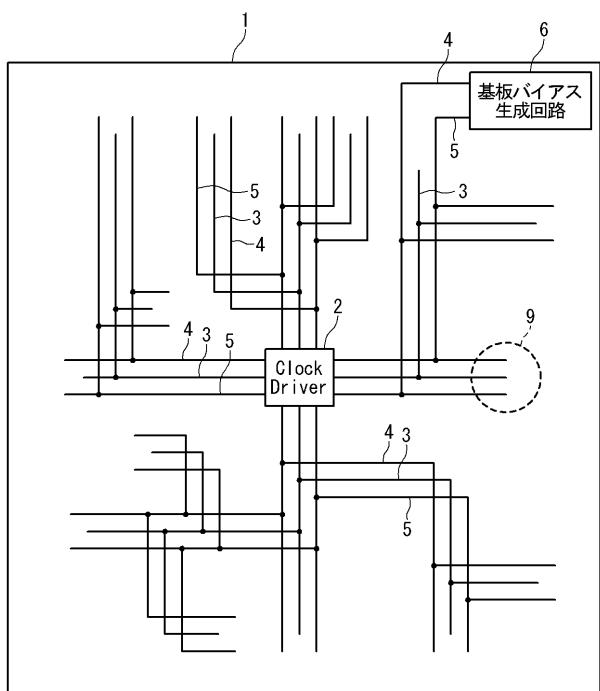

図7は、本発明の半導体デバイス1における第2の実施形態の構成を例示する平面図である。図7を参照すると、第2の実施形態の半導体デバイス1に備えられた基板バイアス生成回路6は、特定の領域（例えば、図7に示されている基板バイアス印加領域10）に基板バイアスを供給している。半導体デバイスの中には、基板バイアスによる閾値電圧の制御が必要な領域と、必要としない領域とが混在して構成されているものも存在する。第2の実施形態では、半導体デバイス1がそのような半導体デバイスであった場合に、基板バイアスの印加が要求される領域にNウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5とを備え、それ以外の領域には、シールド配線（7、8）を介してグランドレベルの電圧を供給している。

#### 【0045】

また、第2の実施形態における半導体デバイス1は、図5に示されているような構成であることが好ましい。つまり、複数のPウェル13が形成される場合に、そのPウェル13が半導体基板11から電気的に絶縁されることで、各Pウェル13に異なる電圧の基板バイアスを供給することが可能となる。同様に、半導体基板11に複数のNウェル12が形成される場合に、それら複数のNウェル12は互いに電気的に絶縁されることとなるので、各Nウェル12に対しても、異なる電圧の基板バイアスを供給することが可能である。第2の実施形態の半導体デバイス1では、シールド配線7とシールド配線8はN+半導体領域18やP+半導体領域19と接続することなく構成されている。これによって、半導体デバイス1全体に基板バイアスを供給する場合に比較して、消費される電力を低減させることが可能となる。

#### 【0046】

##### 〔第3の実施形態〕

以下に、図面を参照して、本発明の第3の実施形態について説明を行う。以下の説明において、上述してきた他の実施形態の説明に使用した符号と同じ符号が付されているものは、同様の構成・動作を有するものであるので、その詳細な説明に関しては省略する。

#### 【0047】

図8は、本発明の半導体デバイス1における第3の実施形態の構成を例示する平面図である。図8を参照すると、第3の実施形態における半導体デバイス1は、複数の基板バイアス生成回路6を備えて構成されている。なお、図8には二つの基板バイアス生成回路6を備えている半導体デバイス1の構成が例示されているが、これは本実施形態における基板バイアス生成回路6の数を制限するものではない。半導体装置の微細化に対応して信号

遅延が発生する場合において、基板バイアス生成回路 6 の近傍に形成されているトランジスタと、基板バイアス生成回路 6 からの距離が遠い位置に形成されているトランジスタとで、応答速度に差が発生してしまう場合が有る。第 3 の実施形態に示される半導体デバイス 1 は、複数の基板バイアス生成回路 6 を備えることで、発生する遅延を減少させることが可能となる。

【 0 0 4 8 】

〔 第 4 の実施形態 〕

以下に、図面を参照して、本発明の第 4 の実施形態について説明を行う。以下の説明において、上述してきた他の実施形態の説明に使用した符号と同じ符号が付されているものは、同様の構成・動作を有するものであるので、その詳細な説明に関しては省略する。

10

【 0 0 4 9 】

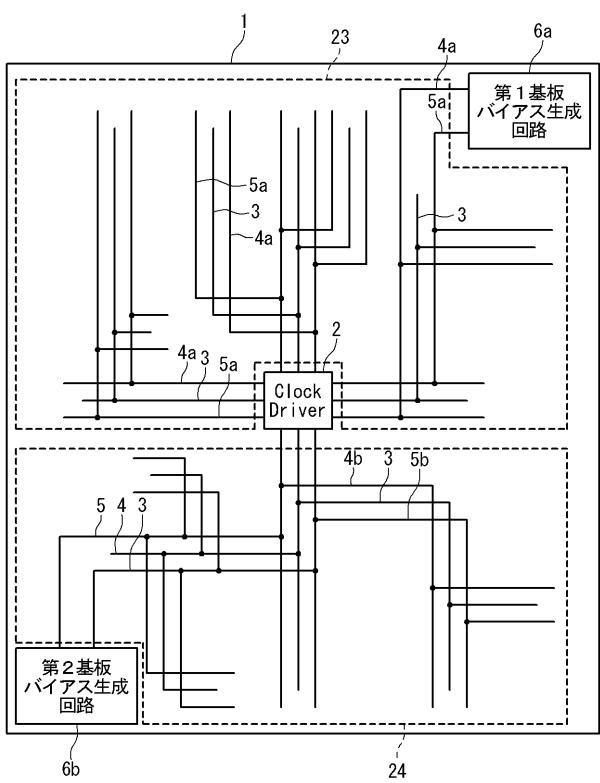

図 9 は、本発明の半導体デバイス 1 における第 4 の実施形態の構成を例示する平面図である。図 9 を参照すると、第 4 の実施形態における半導体デバイス 1 は、複数の基板バイアス生成回路 ( 6 a, 6 b ) を備えて構成されている。図 9 を参照すると、第 4 の実施形態の半導体デバイス 1 は、第 1 の領域 ( 例えば、図 9 に示されている第 1 領域 2 3 ) に第 1 基板バイアスが供給され、第 2 の領域 ( 例えば、図 9 に示されている第 2 領域 2 4 ) に第 2 基板バイアスが供給されている。

【 0 0 5 0 】

第 4 に実施形態における半導体デバイス 1 は、第 2 の実施形態と同様に、図 5 に示されているような構成であることが好ましい。つまり、複数の P ウェル 1 3 が形成される場合に、その P ウェル 1 3 が半導体基板 1 1 から電気的に絶縁されることで、各 P ウェル 1 3 に異なる電圧の基板バイアスを供給することが可能となる。また、半導体基板 1 1 に複数の N ウェル 1 2 が形成される場合には、それら複数の N ウェル 1 2 は互いに電気的に絶縁されることとなる。したがって、各 N ウェル 1 2 に対しても、異なる電圧の基板バイアスを供給することが可能である。

20

【 0 0 5 1 】

半導体デバイスの中には、一つのチップの中で複数の異なる基板バイアスによる閾値電圧の制御が実行されるものが存在する。そのような半導体デバイス 1 に対応するために、第 4 の実施形態における第 1 基板バイアス生成回路 6 a は、第 1 基板バイアスを生成し、その第 1 基板バイアスを第 1 N ウェル側基板バイアス供給ノード 4 a および第 1 P ウェル側基板バイアス供給ノード 5 a を介して第 1 領域 2 3 に対応する領域に形成されている M O S トランジスタに印加している。同様に、第 2 基板バイアス生成回路 6 b は、第 1 基板バイアスと異なる第 2 基板バイアスを生成している。そして、その第 2 基板バイアスを、第 2 N ウェル側基板バイアス供給ノード 4 b および第 2 P ウェル側基板バイアス供給ノード 5 b を介して第 2 領域 2 4 に対応する領域に形成されている M O S トランジスタに供給している。

30

【 0 0 5 2 】

上述したように、本願発明を適用する半導体デバイスは、P M O S トランジスタ 1 4 を有する N ウェルと、N M O S トランジスタ 1 5 を有する P ウェルとを含んで構成されている。その N ウェルが複数形成され、手いる場合、それらは、p 型半導体基板 1 1 によって互いに電気的に絶縁されている。また、その P ウェルが複数形成されている場合、それらは、N ウェル 1 6 とディープ N ウェル 1 7 とによって互いに電気的に絶縁されている。したがって、第 1 基板バイアス生成回路 6 a と第 2 基板バイアス生成回路 6 b とを備え、第 1 基板バイアス生成回路 6 a と第 2 基板バイアス生成回路 6 b とが異なる電圧の基板バイアスを供給することで、第 1 領域 2 3 と第 2 領域 2 4 とをそれぞれ独立して制御することが可能となる。なお、図 9 に示されているように、第 4 の実施形態の半導体デバイス 1 は、2 種類の基板バイアスに対応して構成されているが、これは本発明において、基板バイアスが 2 種類の場合にのみ適用可能であることを意味するものではない。

40

【 0 0 5 3 】

〔 第 5 の実施形態 〕

50

以下に、図面を参照して、本発明の第5の実施形態について説明を行う。以下の説明において、上述してきた他の実施形態の説明に使用した符号と同じ符号が付されているものは、同様の構成・動作を有するものであるので、その詳細な説明に関しては省略する。

#### 【0054】

図10は、本発明の第5の実施形態の構成を例示する断面図である。図5を参照すると、第5の実施形態の半導体デバイス1は、半導体基板11に形成されるサブウェル31を備えて構成されている。また、図10に示されているように、サブウェル31は、P+半導体領域32を含み、そのP+半導体領域32はコンタクト25を介してPウェル側基板バイアス供給ノード5に接続されている。

#### 【0055】

第5の実施形態の半導体デバイス1には、第1の実施形態の半導体デバイス1と同様に、基板バイアス生成回路6が備えられている。第5の実施形態における基板バイアス生成回路6は、Nウェル側基板バイアス供給ノード4およびPウェル側基板バイアス供給ノード5に接続され、半導体デバイス1の動作状態が通常モードであるのか待機モードであるのかを示す制御信号に応答して、Nウェル側基板バイアスVnwとPウェル側基板バイアスVpwとを生成している。基板バイアス生成回路6から出力されるNウェル側基板バイアスVnwは、Nウェル側基板バイアス供給ノード4伝わってN+半導体領域18に印加され、そのN+半導体領域18を介してNウェル12に供給される。半導体基板11に複数のNウェル12が形成される場合に、それら複数のNウェル12は互いに電気的に絶縁されることとなる。したがって、各Nウェル12に対して、異なる電圧の基板バイアスを供給することが可能である

ここで、第5の実施形態において、基板バイアス生成回路6から出力されるPウェル側基板バイアスVpwは、Pウェル側基板バイアス供給ノード5を伝わってサブウェル31のP+半導体領域32に印加される。P+半導体領域32に印加されたPウェル側基板バイアスVpwは、半導体基板11を経由してPウェル13に供給される。そのため、半導体基板11に複数のPウェル13が形成される場合に、半導体基板11を経由して、それら複数のPウェル13の基板電位をすべて同一にすることが可能となり、また、これによって、第5の実施形態の半導体デバイス1は、第1の実施形態の半導体デバイス1と同様の効果を得ることが可能となる。

#### 【0056】

上述してきた複数の実施形態において、Nウェル側基板バイアス供給ノード4またはPウェル側基板バイアス供給ノード5の一つの経路に一つの基板バイアス生成回路6が接続されている場合を例示して説明を行ってきた。本発明を構成するにあたり、Nウェル側基板バイアス供給ノード4またはPウェル側基板バイアス供給ノード5の一つの経路に複数の基板バイアス生成回路6が備えられている構成であっても、上述の実施形態で述べる効果を発生させることが可能である。また、上記の実施形態において、p型半導体基板に各回路が形成される半導体デバイスを例示して本発明を説明したが、これは、本発明の構成を制限するものではない。例えば、n型半導体基板上に、各回路を構成した半導体装置に本願発明を適用した場合においても、上記の実施形態と同様の効果を得ることができる。

#### 【0057】

また、上述してきた複数の実施形態において、Nウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5とは、クロック配線3に沿って配置されている。各基板バイアス供給ノード(4、5)をこのような構成にすることで、クロック配線3をシールドする効果と基板バイアスを供給する作用とをほぼ同時に実現することが可能となる。ここにおいて、基板バイアス生成回路6は、Nウェル側基板バイアス供給ノード4とPウェル側基板バイアス供給ノード5とのどちらか一方に基板バイアスを供給する構成であっても良い。

#### 【0058】

さらに、上述してきた複数の実施形態は、その構成・動作に矛盾が生じない場合において、組み合わせて実行することが可能である。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0059】

【図1】図1は、従来の基板バイアスノードを備える半導体デバイスの構成を示す平面図である。

【図2】図2は、従来の半導体デバイスのレイアウトを示す平面図である。

【図3】図3は、本発明の基板バイアスノードを備える半導体デバイスの、第1の実施形態における平面構成を例示する平面図である。

【図4】図4は、本発明の半導体デバイスのレイアウトの一部を例示する平面図である。

【図5】図5は、本発明の基板バイアスノードを備える半導体デバイスの、第1の実施形態における断面構成を例示する断面図である。

【図6】図6は、基板バイアスとリーク電流との関連、及び、基板バイアスとパフォーマンスとの関連を示すグラフである。

【図7】図7は、本発明の第2の実施形態における半導体デバイスの構成を例示する平面図である。

【図8】図8は、本発明の第3の実施形態における半導体デバイスの構成を例示する平面図である。

【図9】図9は、本発明の第4の実施形態における半導体デバイスの構成を例示する平面図である。

【図10】図10は、本発明の第5の実施形態における半導体デバイスの構成を例示する平面図である。

## 【符号の説明】

## 【0060】

Vn w ... Nウェル側基板バイアス

Vp w ... Pウェル側基板バイアス

Vn w 1 ... 第1順方向基板バイアス

Vn w 2 ... 第1逆方向基板バイアス

Vp w 1 ... 第2順方向基板バイアス

Vp w 2 ... 第2逆方向基板バイアス

1 ... 半導体デバイス

2 ... クロックドライバ

3 ... クロック配線

4 ... Nウェル側基板バイアス供給ノード

5 ... Pウェル側基板バイアス供給ノード

6 ... 基板バイアス生成回路

6 a ... 第1基板バイアス生成回路、6 b ... 第2基板バイアス生成回路

7 ... シールド配線

8 ... シールド配線

9 ... 領域

10 ... 基板バイアス印加領域

11 ... 半導体基板

12 ... Nウェル

13 ... Pウェル

14 ... PチャネルMOSトランジスタ (PMOSトランジスタ)

15 ... NチャネルMOSトランジスタ (NMOSトランジスタ)

16 ... Nウェル

17 ... ディープNウェル

18 ... N+半導体領域

19 ... P+半導体領域

21 ... メタル配線

22 ... ビア

10

20

30

40

50

- 2 3 ... 第 1 領域

2 4 ... 第 2 領域

2 5 ... コンタクト

2 6 ... P 拡散領域

2 7 ... N 拡散領域

2 8 ... ポリシリコン配線

3 1 ... サブウェル

3 2 ... P + 半導体領域

1 0 1 ... チップ

1 0 2 ... クロックドライバ

1 0 3 ... クロック配線

1 0 4 ... 基板バイアス供給ノード

1 0 5 ... 基板バイアス供給ノード

1 0 6 ... 基板バイアス生成回路

1 0 7 ... シールド配線

1 0 8 ... シールド配線

1 0 9 ... 領域

1 1 0 ... コンタクト

1 2 2 ... ピア

1 2 6 ... P 拡散領域

1 2 7 ... N 拡散領域

1 2 8 ... ポリシリコン配線

10

20

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 図 8 】

【図9】

【 図 1 0 】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 01 L 27/04

H