(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6507768号

(P6507768)

(45) 発行日 令和1年5月8日(2019.5.8)

(24) 登録日 平成31年4月12日(2019.4.12)

(51) Int.Cl.

F 1

G 1 O H 1/34 (2006.01)

G 1 O H 1/00 (2006.01)G 1 O H 1/34

G 1 O H 1/00

A

請求項の数 5 (全 18 頁)

(21) 出願番号 特願2015-60222 (P2015-60222)

(22) 出願日 平成27年3月23日 (2015.3.23)

(65) 公開番号 特開2016-180820 (P2016-180820A)

(43) 公開日 平成28年10月13日 (2016.10.13)

審査請求日 平成30年3月14日 (2018.3.14)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 春日 一貴

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

(72) 発明者 酒井 勝利

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

(72) 発明者 原田 栄一

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

最終頁に続く

(54) 【発明の名称】押弦位置検知装置、電子弦楽器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の押弦位置が定められた指板と、

前記押弦位置の夫々に対応付けて設けられ、導電性の複数の弦夫々との間の距離の変化に応じて共振周波数が変化するとともに、前記共振周波数が隣接する前記押弦位置間で夫々異なるように構成された複数の共振回路と、

前記共振周波数の変化を検知する複数のセンサと、

前記複数のセンサ夫々が検知した前記共振周波数の変化に基づいて、押弦位置を検知する押弦位置検知部と、

を備える押弦位置検知装置。

10

## 【請求項 2】

前記共振回路は、隣接する前記押弦位置間で当該各押弦位置に対応する各前記共振回路に含まれる各キャパシタの容量値が異なる請求項1に記載の押弦位置検知装置。

## 【請求項 3】

前記指板の位置に応じて、前記共振周波数の異なる共振回路の数を変化させる請求項1または2に記載の押弦位置検知装置。

## 【請求項 4】

複数の弦と、

請求項1乃至3のいずれかに記載の前記押弦位置検知装置と、

前記押弦位置検知装置により検知される押弦位置に応じた音高で楽音を発生する音源と

20

、を有する電子弦楽器。

【請求項 5】

複数の押圧位置が定められた誘導性の押圧板と、

前記押圧位置の夫々に対応付けて設けられ、夫々が前記押圧板との間の距離の変化に応じて共振周波数が変化し、前記共振周波数が隣接する前記押圧位置間で夫々異なるように構成された複数の共振回路と、

前記共振周波数の変化を検知する複数のセンサと、

前記複数のセンサ夫々が検知する前記共振周波数の変化に基づいて、押圧位置を検知する押圧位置検知部と、

を備える押圧位置検知装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、押弦位置検知装置、電子弦楽器に関する。

【背景技術】

【0002】

従来より、電子ギター等の電子弦楽器においては、電子式でない弦楽器と同様に、複数のフレットが設けられた指板上に、複数の弦が張設されている。このため、演奏者は、例えば、左手で弦を所定のフレットに押さえつつ右手で弦を弾く、といった弦楽器と同様の演奏をすることができる。

20

この場合、電子弦楽器は、弦の振動そのもので発音しているのではなく、音源と呼ばれる電子回路で電子音を生成することにより発音している。このため、電子弦楽器の発音を実現するためには、音高の情報が必要になる。弦楽器においては指で弦が押さえられたフレットの位置（以下、押弦位置）で音高が決定されるため、電子弦楽器においても、押弦位置に基づいて音高の情報が生成されることが好ましい。このため、従来より、電子弦楽器において押弦位置を検出する技術が研究開発されている（例えば特許文献1参照）。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭59-176783号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1を含む従来の技術においては、弦に対して電流を印加する必要があり、そのための構成が必要となる。この結果、構造の複雑化・コスト高を招いていた。このため、従来より押弦位置を検出する新たな技術の実現が要望されていた。

【0005】

そこで、本発明は、電子弦楽器における演奏時の押弦位置または電子楽器における演奏時の押圧位置を精度良く検知することを目的とする。

【課題を解決するための手段】

40

【0006】

態様の一例では、複数の押弦位置が定められた指板と、前記押弦位置の夫々に対応付けて設けられ、導電性の複数の弦夫々との間の距離の変化に応じて共振周波数が変化するとともに、前記共振周波数が隣接する前記押弦位置間で夫々異なるように構成された複数の共振回路と、前記共振周波数の変化を検知する複数のセンサと、前記複数のセンサ夫々が検知した前記共振周波数の変化に基づいて、押弦位置を検知する押弦位置検知部と、を備える。

【発明の効果】

【0007】

本発明によれば、電子弦楽器における演奏時の押弦位置または電子楽器における演奏時

50

の押圧位置を精度良く検知することが可能となる。

【図面の簡単な説明】

【0008】

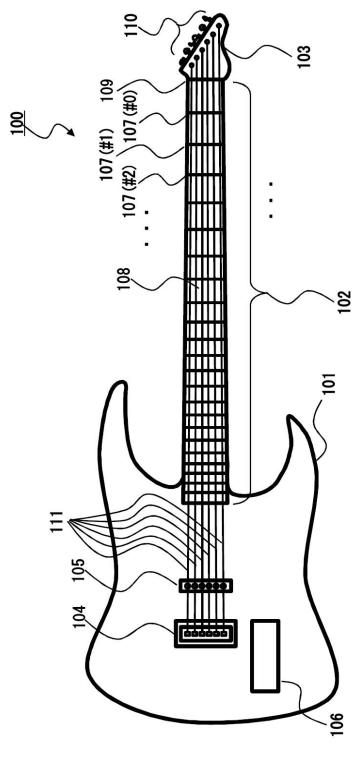

【図1】電子弦楽器の外観を示す正面図である。

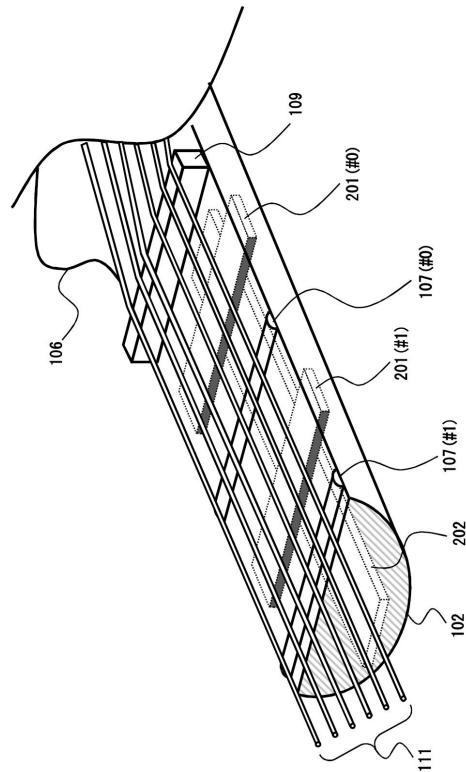

【図2】ネック部とその内部の機構の一例を示す透視図である。

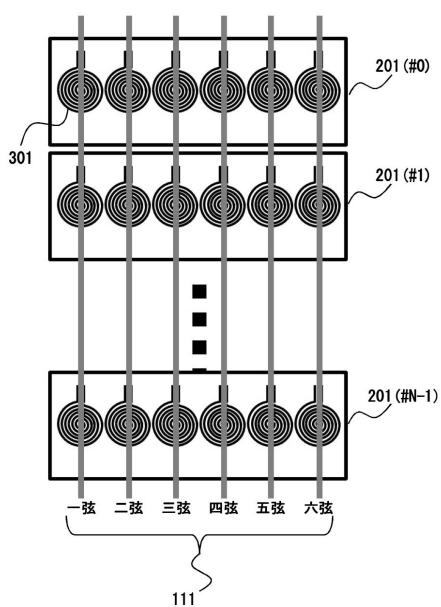

【図3】センサ基板の一例(全体)を示す図である。

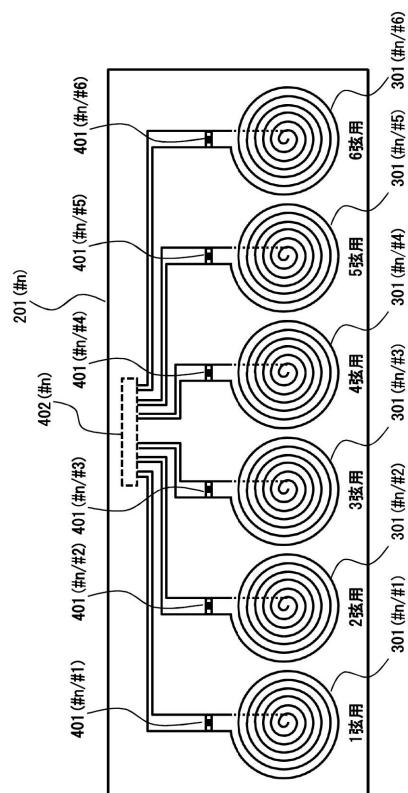

【図4】センサ基板の一例(1フレット)を示す図である。

【図5】センサ基板と制御回路との配線関係を示す図である。

【図6】隣接するコイル間の電磁誘導による発生する問題点を説明する図である。

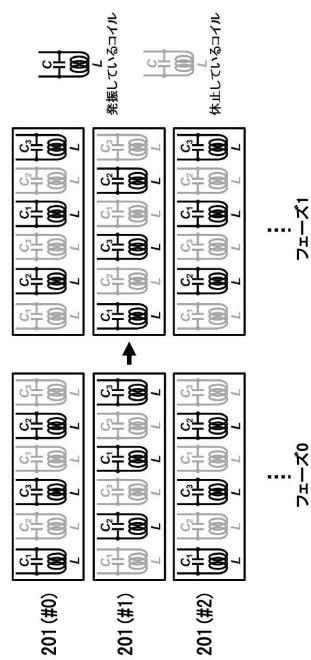

【図7】本実施形態によるコイルの時分割駆動動作の説明図である。 10

【図8】制御回路のハードウェア構成例を示す図である。

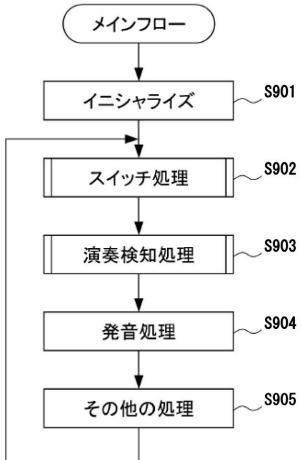

【図9】制御回路が実行する全体制御処理の例を示すフローチャートである。

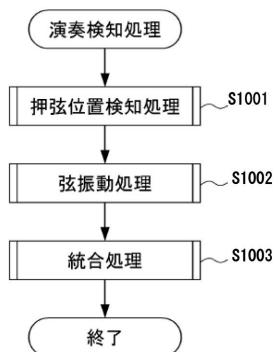

【図10】演奏検知処理の詳細例を示すフローチャートである。

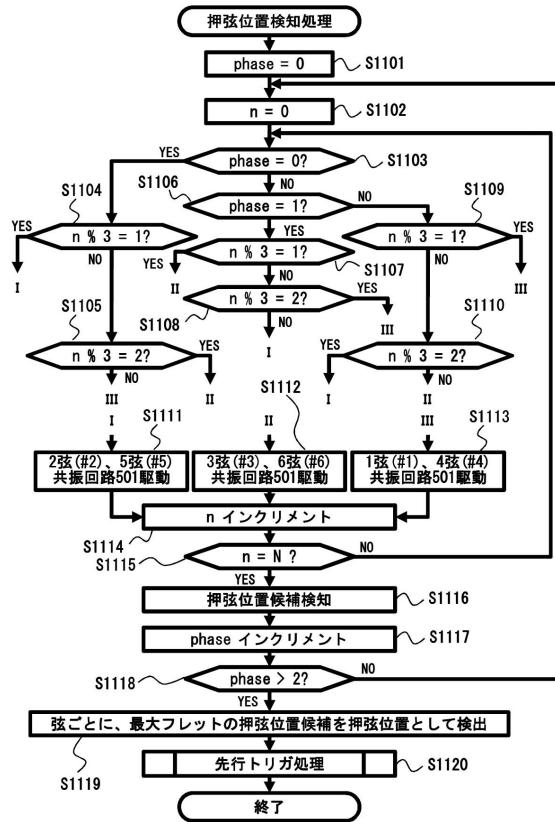

【図11】押弦位置検知処理の詳細例を示すフローチャートである。

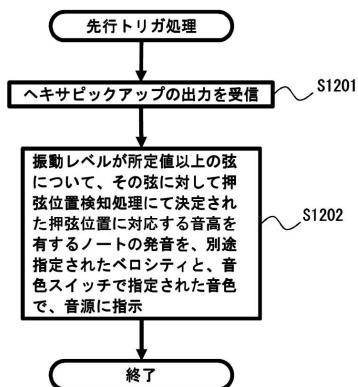

【図12】先行トリガ処理の詳細例を示すフローチャートである。

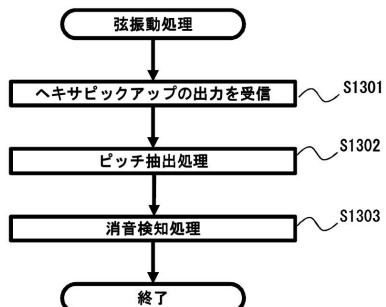

【図13】弦振動処理の詳細例を示すフローチャートである。

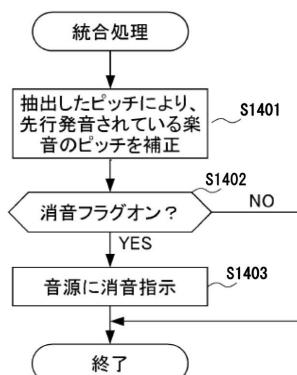

【図14】統合処理の詳細例を示すフローチャートである。

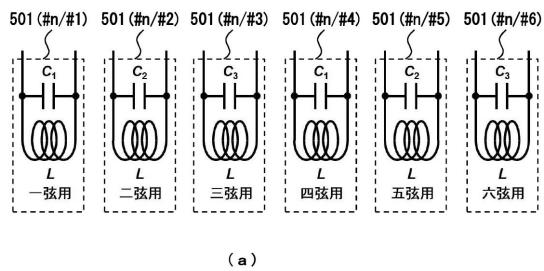

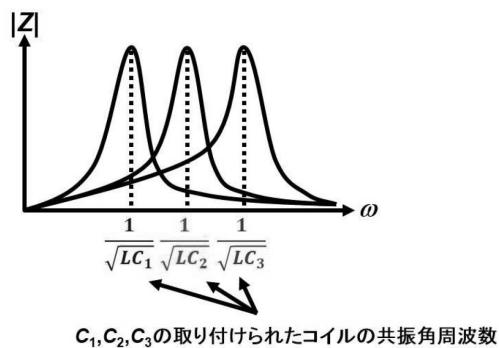

【図15】センサ基板上に配置される共振回路における、キャパシタとコイルの具体的な設計例を示す図である。 20

【図16】フェーズ分割による時分割処理に加えて周波数分割の概念を取り入れた押弦位置検知処理の制御動作の説明図である。

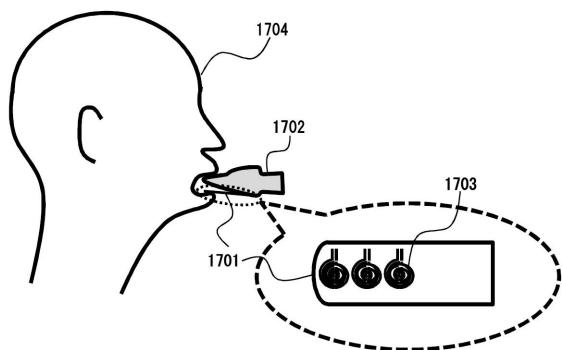

【図17】電子管楽器の実施形態の説明図である。

【発明を実施するための形態】

【0009】

以下、本発明を実施するための形態(以下「本実施形態」という)について図面を参照しながら詳細に説明する。本実施形態は、共振しているコイルに近づいた金属を検知する金属探知の技術を利用して、電子弦楽器のネックの中に埋め込まれたコイルと誘導型近接センサを用いて電子弦楽器の弦の位置を非接触で検知する電子弦楽器である。

【0010】

図1は電子弦楽器100の外観を示す正面図、図2はネック部とその内部の機構の一例を示す透視図である。図1に示す如く、電子弦楽器1は、胴部101と、ネック部102と、ヘッド部103とを備える。ヘッド部103には、6本の金属製の弦111の各一端が巻かれる6個のペグ(糸巻き)110が取り付けられている。各ペグ110に巻かれた各弦111はそれぞれ、ヘッド部103のナット(上駒)109(図2参照)で支持されながら、ネック部102から胴部101の上を通り、胴部101に取り付けられたブリッジ部104の6個の支持部との間に張られている。6本の弦111にはそれぞれ弦番号が対応付けられている。図1の図面上側の最も細い弦111が、「第1弦」であり、弦111の太さが太くなる順番で「第2弦」「第3弦」「第4弦」「第5弦」「第6弦」というように弦番号が大きくなる。 30

【0011】

ネック部102には、その表面に貼り付けられた指板108に、ヘッド部103から胴部101に向かって#0～#N-1(Nの個数は例えば「22」個)の複数のフレット107が、図2に示されるように、各弦111に直行するように埋め込まれている。N個のフレット107は、各々フレット番号と対応付けられている。ヘッド部103のナット109に最も近いフレット107が第1フレット(または#0フレット)であり、以下順次、第2フレット(#1フレット)、第3フレット(#2フレット)、・・・と番号付けされ、胴部101に最も近いフレット107が第Nフレット(#N-1フレット)である。

【0012】

図2に例示されるように、ネック部102の内部には、ナット109と#0のフレット107間、#0と#1のフレット107間、・・・、#N-2と#N-1のフレット10 50

7間の指板108下にそれぞれ、#0、#1、…#N-1の各センサ基板201が設置される。また、各センサ基板201と接続され、各センサ基板201の情報を胴部101内に設置されている制御回路106(図1参照)へ伝達する配線基板202が、ネック部102内の長手方向に設置される。

#### 【0013】

図3および図4は、センサ基板201の一例を示す図である。図3に示されるように、#0、#1、…#N-1の各センサ基板201には、各弦111の振動を検知するための6個のコイル301がプリントされている。また、図4に示されるように、例えば、任意の#n(0 n N-1)のセンサ基板201(#n)において、第1弦から第6弦までの各弦111に対応して配設されている#1から#6の各コイル301(#n/#1)～301(#n/#6)の各両端配線間に、コイル301が共振器として動作するための各キャパシタ401(#n/#1)～401(#n/#6)が接続される。各コイル301(#n/#1)～301(#n/#6)の各両端子の組は、コネクタ402(#n)を介して配線基板202(図2参照)へ接続され、配線基板202上の配線を介して胴部101内の制御回路106へ接続されている。

10

なお、コイルの中心位置に対応するセンサ基板201には穴があいており、コイルはその穴を通過し、センサ基板201の裏側を通り、コネクタ402(#n)を介して配線基板202(図2参照)へ接続されている。

#### 【0014】

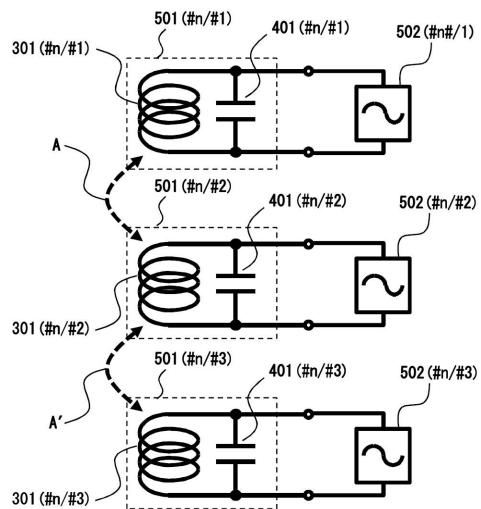

図5は、センサ基板201と制御回路106との配線関係を示す図である。各センサ基板201(#n)(0 n N-1)上の、各コイル301(#n/#i)と各キャパシタ401(#n/#i)(1 i 6)とからなる各共振回路501(#n/#i)は、制御回路106内の各センサ502(#n/#i)の中にある電圧源から供給される各信号によって共振させられる。センサ502(#n/#i)の中には電圧源、出力信号(周波数)を数えるカウンターが含まれている。コイル(#n/#i)に金属の弦111(#i)が近づくと、周波数が変化してカウント値が変化する。この結果、各共振回路501(#n/#i)は、各コイル301(#n/#i)のインダクタンス値と各キャパシタ401(#n/#i)の容量値とで決まる共振周波数で共振させられる。今、ある共振回路501(#n/#i)がそれに対応するセンサ502(#n/#i)の中にある電圧源によって共振させられている状態で、演奏者が指で共振回路501(#n/#i)に対応する金属の弦111(#i)をネック部102の#nフレットの手前(#n-1フレットと#nフレットの間、n=0の場合は図1または図2のナット109と#0フレットの間)の指板108上で押弦することにより、その金属の弦111(#i)が共振回路501(#n/#i)内のコイル301(#n/#i)に接近すると(弦111(#i)とコイル301(#n/#i)との距離が変化すると)、当該コイル301(#n/#i)とキャパシタ401(#n/#i)とで決定されるリアクタンスが変化する。この結果、当該コイル301(#n/#i)の両端の電圧が変化する。そこで、センサ502(#n/#i)内の出力信号(周波数)を数えるカウンターが周波数をカウントして、カウント値の変化から、電圧変化を検知することにより、弦111(#i)が#nフレットの手前で押弦されたことを検知することが可能となる。

20

30

40

#### 【0015】

なお、各信号供給回路501(#n/#i)(0 n N-1, 1 i 6)は、上述のように胴部101内の制御回路106内にまとめて配置されてもよいし、共振回路501(#n/#i)におけるアナログ信号の劣化を防ぐために、センサ基板201(#n)近傍の配線基板202上に配置されてもよい。

#### 【0016】

ここで、電子弦楽器100(図1)では、#0～#N-1の全フレット107の手前の指板108下で、金属の弦111の押弦状態(距離の変化)を検知し続けることが要求される。しかしそのためには、全ての共振回路501(#n/#i)(0 n N-1, 1 i 6)を共振状態にする必要がある。しかし、図6に例示されるように、隣接するコ

50

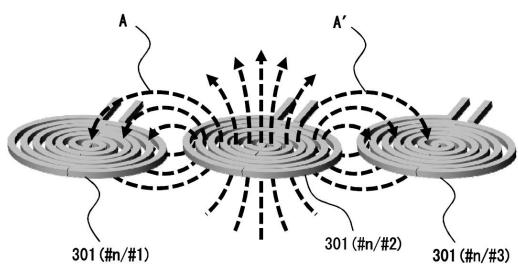

イル301(#n/#1)、301(#n/#2)、301(#n/#3)などが同時に共振すると、例えばコイル301(#n/#2)が発生した磁界AおよびA'がそれぞれ別のコイル301(#n/#1)および301(#n/#3)に入って電磁誘導を起こす。その逆もあり得る。この結果、各コイル301(#n/#1)、301(#n/#2)、301(#n/#3)同士が干渉して、各共振回路501(#n/#1)、501(#n/#2)、501(#n/#3)でそれぞれノイズが発生し、そのノイズの影響で各弦111(#1)、111(#2)、111(#3)の押弦位置の検知精度が劣化し、場合によっては検知が不可能となってしまう。

#### 【0017】

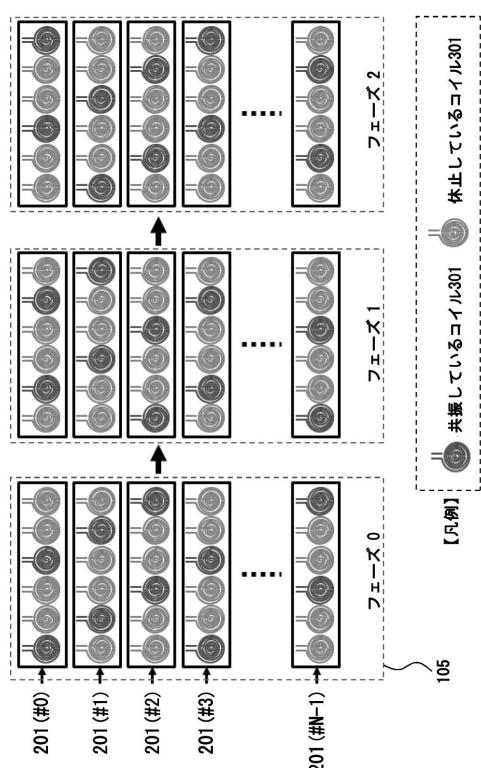

これを回避するために、本実施形態では、互いに近くにあるコイル301同士を同時に駆動せず、時分割で駆動する。図7は、本実施形態によるコイル301の時分割駆動動作の説明図である。図7に示されるように、例えば、各センサ基板201上の6個のコイル301のうち、互いに2つコイル301をはさんで離れたコイル301のみが1フェーズの間に同時駆動させられ、他のコイル301は共振を停止させられる。また、隣り合うセンサ基板201では、ネック部102の長手方向にも2つコイル301をはさんで離れたコイル301のみが駆動させられる。そして、図7に示されるフェーズ0、フェーズ1、およびフェーズ2の3つのフェーズが高速に切り替えながら時分割で各コイル301が共振させられることにより、コイル301間の電磁誘導による干渉を抑えつつ、各弦111の押弦位置の検知が行われる。

#### 【0018】

図1の説明に戻り、胴部101には、6本の弦111の各端が取り付けられるブリッジ104と、各弦111の振動を独立して検出するヘキサピックアップ105が備えられている。

#### 【0019】

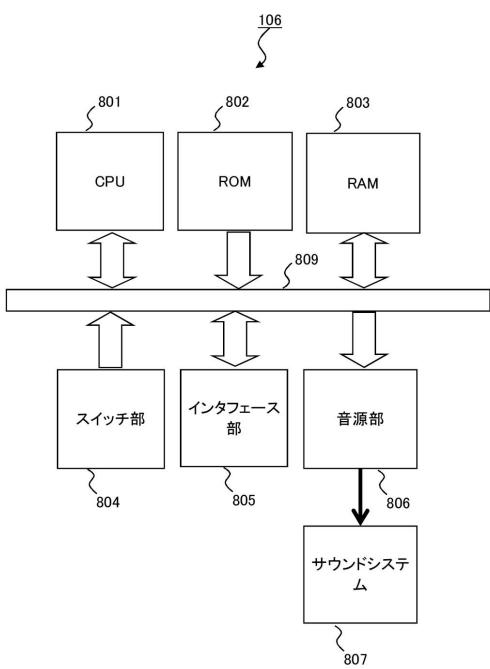

図8は、図1に示される胴部101内の制御回路106のハードウェア構成例を示す図である。図8に例示される制御回路106のハードウェア構成は、CPU(中央演算処理装置)801、ROM(リードオンリーメモリ)802、RAM(ランダムアクセスメモリ)803、スイッチ部804、インターフェース部805、および音源部806を備え、これらがシステムバス809によって相互に接続された構成を有する。また、音源部806の出力はサウンドシステム807に入力する。

#### 【0020】

CPU801は、RAM803をワークメモリとして使用しながらROM802に記憶された制御プログラムを実行することにより、図1の電子弦楽器100の制御動作を実行する。

#### 【0021】

スイッチ部804は、後述する音色スイッチまたはモードスイッチを備え、これらのスイッチの状態を入力して、CPU801に通知する。

#### 【0022】

インターフェース部805は、図2の配線基板202と接続され、図5に示されるセンサ502(#n/#i)(0 n N-1, 1 i 6)の機能に対応するハードウェア(信号共振器と電圧検出器)を実装する。

#### 【0023】

音源部806は、CPU801から入力する発音制御データに基づいて、デジタル楽音データを生成し、サウンドシステム807に出力する。サウンドシステム807は、音源部806から入力したデジタル楽音データをアナログ楽音信号に変換した後、そのアナログ楽音信号を内蔵又は外部のアンプで増幅して内蔵のスピーカから放音する。

#### 【0024】

図9は、制御回路106が実行する全体制御処理の例を示すフローチャートである。まず、CPU801は、電源の投入によりイニシャライズを実行する。その後、CPU801は、電源がオフされるまで、ステップS902からS905までの一連の処理を繰り返

10

20

30

40

50

し実行する。

#### 【0025】

上記繰返し処理においてまず、CPU801は、スイッチ処理を実行する（ステップS902）。CPU801は、演奏者によりスイッチ部804の特には図示しないいずれかの音色スイッチがオンされると、音色スイッチにより指定された音色に対応する音色番号を、RAM803内の変数TONEに格納する。そして、CPU801は、変数TONEに基づくイベントを、音源部806に供給する。これにより、音源部806に、発音されるべき音色が指定される。また、CPU801は、演奏者によりスイッチ部804の特には図示しないいずれかのモードスイッチがオンされると、各種動作モードを設定する。

#### 【0026】

次に、CPU801は、演奏検知処理を実行する（ステップS903）。ここでは、CPU801は、いずれのフレット位置のいずれの弦111が押弦されたか、ヘキサピックアップ105（図1参照）によりいずれの弦111が弾弦されたかを検知する。

#### 【0027】

続いて、CPU801は、発音処理を実行する（ステップS904）。ここでは、CPU801は、ステップS903の演奏検知処理の結果に基づいて、音源部806に発音制御データを供給する。この結果、音源部806が、デジタル楽音データを生成し、サウンドシステム807が、そのデジタル楽音データをアナログ楽音信号に変換することにより、楽音の発音を実行する。

#### 【0028】

最後に、CPU801は、その他の処理を実行する（ステップS905）。ここでは、CPU801は、ステップS902、S903、およびS904で実行しなかった、電子弦楽器100の制御に必要な各種処理を実行する。その後、CPU801は、ステップS902の処理に戻る。

#### 【0029】

図10は、図9のステップS903の演奏検知処理の詳細例を示すフローチャートである。

#### 【0030】

まず、CPU801は、演奏者がどのフレット位置のどの弦111の押弦を開始したかを検知する押弦位置検知処理（ステップS1001）を実行する。

#### 【0031】

次に、CPU801は、ヘキサピックアップ105（図1参照）によりいずれの弦111が弾弦されたかを検出する弦振動処理（ステップS1002）を実行する。

#### 【0032】

最後に、CPU801は、現在の押弦位置および弦振動の状態に、ステップS1001およびS1002で新たに検知された押弦位置および弦振動の状態を統合する統合処理（ステップS1003）を実行する。

#### 【0033】

図11は、図10のステップS1001の押弦位置検知処理の詳細例を示すフローチャートである。

#### 【0034】

押弦位置検知処理では、CPU801は、ステップS1101で現在のフェーズを示すRAM803上の変数phaseに初期値0をセットした後、ステップS1117で変数phaseの値を+1ずつインクリメントしながら、ステップS1118で変数phaseの値が2を超えたと判定するまで、変数phaseの値=0, 1, 2で示される3つのフェーズのそれぞれごとに、以下のステップS1102からS1116までの一連の処理を繰り返し実行する。この繰返し処理は、図7の説明で前述したフェーズ0、1、2の時分割処理に対応する。

#### 【0035】

ステップS1102からS1116の一連の処理において、CPU801は、ステップ

10

20

30

40

50

S 1 1 0 2 で現在のセンサ基板 2 0 1 の位置を示す R A M 8 0 3 上の変数 n に初期値 0 (図 2、図 7 等のセンサ基板 2 0 1 (# 0) の位置に対応する) をセットした後、ステップ S 1 1 1 4 で変数 n の値を + 1 ずつインクリメントしながら、ステップ S 1 1 1 5 で変数 n の値が値「N」に達したと判定するまで、変数 n の値で示されるセンサ基板 2 0 1 の位置 (図 2、図 7 等のセンサ基板 2 0 1 (# 0)、2 0 1 (# 1)、…、2 0 1 (# N - 1) の各位置に対応する) のそれぞれごとに、以下のステップ S 1 1 0 3 から S 1 1 1 3 までの一連の処理を繰り返し実行する。この繰返し処理は、図 7において、各フェーズごとに、センサ基板 2 0 1 (# 0 ~ # N - 1) に対して、駆動する共振回路 5 0 1 (# n / # 1 ~ # n / # 6 のいずれか) (図 5 参照) を決定する処理に対応する。

## 【0 0 3 6】

10

ステップ S 1 1 0 3 から S 1 1 1 3 までの一連の処理において、まず、C P U 8 0 1 は、変数 phase の値が「0」であるか否かを判定する (ステップ S 1 1 0 3)。

## 【0 0 3 7】

変数 phase の値が「0」(ステップ S 1 1 0 3 の判定が Y E S ) である場合、C P U 8 0 1 は、変数 n の値を「3」で割ったときの剰余「n % 3」が「1」であるか否かを判定する (ステップ S 1 1 0 4)。なお、「%」は剰余を算出する演算子を示す。

## 【0 0 3 8】

変数 n の値を「3」で割ったときの剰余「n % 3」が「1」(ステップ S 1 1 0 4 の判定が Y E S ) である場合、C P U 8 0 1 は、変数 n の値が示すセンサ基板 2 0 1 (# n) 上の 2 弦と 5 弦の共振回路 5 0 1 (# n / # 2) と 5 0 1 (# n / # 5) を駆動する (ステップ S 1 1 1 1)。これは例えば図 7において、フェーズ = 0 の時分割タイミングにおけるセンサ基板 2 0 1 (# 1) 上で共振させられる共振回路 5 0 1 の例である。

20

## 【0 0 3 9】

変数 n の値を「3」で割ったときの剰余「n % 3」が「1」ではない (ステップ S 1 1 0 4 の判定が N O である) 場合、C P U 8 0 1 は、変数 n の値を「3」で割ったときの剰余「n % 3」が「2」であるか否かを判定する (ステップ S 1 1 0 5)。

## 【0 0 4 0】

30

変数 n の値を「3」で割ったときの剰余「n % 3」が「2」(ステップ S 1 1 0 5 の判定が Y E S ) である場合、C P U 8 0 1 は、変数 n の値が示すセンサ基板 2 0 1 (# n) 上の 3 弦と 6 弦の共振回路 5 0 1 (# n / # 3) と 5 0 1 (# n / # 6) を駆動する (ステップ S 1 1 1 2)。これは例えば図 7において、フェーズ = 0 の時分割タイミングにおけるセンサ基板 2 0 1 (# 2) 上で共振させられる共振回路 5 0 1 の例である。

## 【0 0 4 1】

40

変数 n の値を「3」で割ったときの剰余「n % 3」が「2」ではない (ステップ S 1 1 0 5 の判定が N O である) 場合、すなわち、変数 n の値を「3」で割ったときの剰余「n % 3」が「0」である場合、C P U 8 0 1 は、変数 n の値が示すセンサ基板 2 0 1 (# n) 上の 1 弦と 4 弦の共振回路 5 0 1 (# n / # 1) と 5 0 1 (# n / # 4) を駆動する (ステップ S 1 1 1 3)。これは例えば図 7において、フェーズ = 0 の時分割タイミングにおけるセンサ基板 2 0 1 (# 0) または 2 0 1 (# 3) 上で共振させられる共振回路 5 0 1 の例である。

## 【0 0 4 2】

変数 phase の値が「0」でない (ステップ S 1 1 0 3 の判定が N O ) 場合、C P U 8 0 1 は、変数 phase の値が「1」であるか否かを判定する (ステップ S 1 1 0 6)。

## 【0 0 4 3】

変数 phase の値が「1」(ステップ S 1 1 0 6 の判定が Y E S ) である場合、C P U 8 0 1 は、変数 n の値を「3」で割ったときの剰余「n % 3」が「1」であるか否かを判定する (ステップ S 1 1 0 7)。

## 【0 0 4 4】

変数 n の値を「3」で割ったときの剰余「n % 3」が「1」(ステップ S 1 1 0 7 の判

50

定がYES)である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の3弦と6弦の共振回路501(#n/#3)と501(#n/#6)を駆動する(ステップS1112)。これは例えば図7において、フェーズ=1の時分割タイミングにおけるセンサ基板201(#1)上で共振させられる共振回路501の例である。

#### 【0045】

変数nの値を「3」で割ったときの剰余「n%3」が「1」ではない(ステップS1107の判定がNOである)場合、CPU801は、変数nの値を「3」で割ったときの剰余「n%3」が「2」であるか否かを判定する(ステップS1108)。

#### 【0046】

変数nの値を「3」で割ったときの剰余「n%3」が「2」(ステップS1108の判定がYES)である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の1弦と4弦の共振回路501(#n/#1)と501(#n/#4)を駆動する(ステップS1113)。これは例えば図7において、フェーズ=1の時分割タイミングにおけるセンサ基板201(#2)上で共振させられる共振回路501の例である。

10

#### 【0047】

変数nの値を「3」で割ったときの剰余「n%3」が「2」ではない(ステップS1108の判定がNOである)場合、すなわち、変数nの値を「3」で割ったときの剰余「n%3」が「0」である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の2弦と5弦の共振回路501(#n/#2)と501(#n/#5)を駆動する(ステップS1111)。これは例えば図7において、フェーズ=1の時分割タイミングにおけるセンサ基板201(#0)または201(#3)上で共振させられる共振回路501の例である。

20

#### 【0048】

変数phaseの値が「1」でない(ステップS1106の判定がNO)場合、すなわち、変数phaseの値が「2」である場合、CPU801は、変数nの値を「3」で割ったときの剰余「n%3」が「1」であるか否かを判定する(ステップS1109)。

#### 【0049】

変数nの値を「3」で割ったときの剰余「n%3」が「1」(ステップS1109の判定がYES)である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の1弦と4弦の共振回路501(#n/#1)と501(#n/#4)を駆動する(ステップS1113)。これは例えば図7において、フェーズ=2の時分割タイミングにおけるセンサ基板201(#1)上で共振させられる共振回路501の例である。

30

#### 【0050】

変数nの値を「3」で割ったときの剰余「n%3」が「1」ではない(ステップS1109の判定がNOである)場合、CPU801は、変数nの値を「3」で割ったときの剰余「n%3」が「2」であるか否かを判定する(ステップS1110)。

#### 【0051】

変数nの値を「3」で割ったときの剰余「n%3」が「2」(ステップS1110の判定がYES)である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の2弦と5弦の共振回路501(#n/#2)と501(#n/#5)を駆動する(ステップS1111)。これは例えば図7において、フェーズ=2の時分割タイミングにおけるセンサ基板201(#2)上で共振させられる共振回路501の例である。

40

#### 【0052】

変数nの値を「3」で割ったときの剰余「n%3」が「2」ではない(ステップS1110の判定がNOである)場合、すなわち、変数nの値を「3」で割ったときの剰余「n%3」が「0」である場合、CPU801は、変数nの値が示すセンサ基板201(#n)上の3弦と6弦の共振回路501(#n/#3)と501(#n/#6)を駆動する(ステップS1112)。これは例えば図7において、フェーズ=1の時分割タイミングにおけるセンサ基板201(#0)または201(#3)上で共振させられる共振回路501の例である。

50

**【0053】**

以上のステップS1103からS1110までの判定処理によって、図7の説明で前述したように、同一のセンサ基板201(#n)上では互いに2つコイル301をはさんで離れたコイル301のみが1フェーズの間に同時駆動させられ、隣り合うセンサ基板201(#n-1と#nまたは#nと#n+1)では、ネック部102の長手方向にも2つコイル301をはさんで離れたコイル301のみが駆動させられ、フェーズ0、1、2の3つのフェーズ全体で全てのコイル301が共振させられる。これにより、コイル301間の電磁誘導による干渉を抑えつつ、各弦111を精度良く検知することが可能となる。

**【0054】**

ステップS1111、S1112、またはS1113での共振回路501の駆動処理の後、CPU801は、変数nの値を+1インクリメントし(ステップS1114)、変数nの値が値「N」に達したか否かを判定する(ステップS1115)。変数nの値が値「N」に達していない場合(ステップS1115の判定がNOの場合)、CPU801は、ステップS1103の処理に戻り、次のセンサ基板201(#n)に対する制御処理を実行する。

**【0055】**

変数nの値が値「N」に達した場合(ステップS1115の判定がYESの場合)、CPU801は、変数phaseの値が示す現在のフェーズにおいて共振させられた共振回路501のうち、押弦を検知した共振回路501の位置情報(センサ基板201の番号とそのセンサ基板201内の弦111の番号に対応する共振回路501の番号)を、押弦位置候補としてRAM803内の所定の記憶領域に記憶する(ステップS1116)。

**【0056】**

その後、CPU801は、変数phaseの値を+1インクリメントし(ステップS1117)、変数phaseの値が値「2」を超えたか否かを判定する(ステップS1118)。変数phaseの値が値「2」を超えていない場合(ステップS1118の判定がNOの場合)、CPU801は、ステップS1102の処理に戻り、次のフェーズ(時分割タイミング)に対する制御処理を実行する。

**【0057】**

変数phaseの値が値「2」を超えた場合(ステップS1118の判定がYESの場合)、全てのセンサ基板201上の全ての共振回路501からの押弦検知処理が完了する。この場合、CPU801は、1弦から6弦までの弦111の番号ごとに、RAM803の所定の記憶領域に記憶されている当該番号で押弦が検知されている共振回路501のうち、最も大きな番号(最大フレット番号)のセンサ基板201の当該最大フレット番号を、その弦111の番号の押弦位置として検知する(ステップS1119)。

**【0058】**

その後、CPU801は、先行トリガ処理を実行する(ステップS1120)。

**【0059】**

図12は、ステップS1120の先行トリガ処理の詳細例を示すフローチャートである。

**【0060】**

まず、CPU801は、ヘキサピックアップ105(図1)の各弦111の出力を受信する(ステップS1201)。

**【0061】**

次に、CPU801は、ステップS1201で受信した出力のうち振動レベルが所定値以上である弦111の番号に対して図10のステップS1001(図11のフローチャートの処理)で決定された押弦位置に対応する音高を有するノートを、別途指定されたベロシティと、図9のステップS902のスイッチ処理において検出された音色スイッチの音色で発音指示する発音制御データを、音源部806に出力する(ステップS1202)。

**【0062】**

ステップS1202の処理の後、CPU801は、図12のフローチャートで示される図

10

20

30

40

50

11のステップS1120の先行トリガ処理を終了し、図11のフローチャートで示される図10のステップS1001の押弦位置検知処理を終了する。

#### 【0063】

図10において、ステップS1001の押弦位置検知処理の後、CPU801は、弦振動処理を実行する(ステップS1002)。ここでは、演奏者がヘキサピックアップ105(図1)付近のどの弦111を弾弦したかおよびどの弦111の弾弦を終了したかが検知される。図13は、図10のステップS1002の弦振動処理の詳細例を示すフローチャートである。

#### 【0064】

まず、CPU801は、ヘキサピックアップ105(図1)から各弦111の振動信号を受信する(ステップS1301)。

#### 【0065】

次に、CPU801は、各弦111の振動信号からその周期を取得し、この周期からピッチ(ピッチ周波数またはピッチ周期)を抽出するピッチ抽出処理を実行する(ステップS1302)。ここでは、例えば特開平01-177082号公報に記載の技術等に基づいて、弦111の振動のピッチが抽出される。

#### 【0066】

最後に、CPU801は、消音検知処理を実行する(ステップS1303)。この処理では、CPU801は、消音が指示されていない弦111について、当該弦111の振動レベルが所定の閾値より小さくなかったか否かを判定し、この判定がYESの場合に当該弦111に対応するRAM803上の変数である消音フラグをオンにする。

#### 【0067】

ステップS1303の処理の後、CPU801は、図13のフローチャートで示される図10のステップS1002の弦振動処理を終了する。

#### 【0068】

図10において、ステップS1002の弦振動処理の後、CPU801は、統合処理を実行する(ステップS1003)。ここでは、現在の押弦位置および弦振動の状態に、ステップS1001およびS1002で新たに検知された押弦位置および弦振動の状態が統合される。図14は、図10のステップS1003の統合処理の詳細例を示すフローチャートである。

#### 【0069】

まず、CPU801は、図13のステップS1302のピッチ抽出処理で抽出されたピッチのデータを、音源部806(図8参照)に供給する(ステップS1401)。この結果、音源部806は、図11のステップS1120(図12のステップS1202)の先行トリガ処理で先行して発音を開始している楽音の音高を、CPU801から新たに供給されたピッチのデータで補正する。これにより、弦111の実際の振動によって決定されるピッチが加味された音高で楽音を発音させることが可能となる。

#### 【0070】

次に、CPU801は、弦111ごとに、RAM803上の消音フラグがオンに設定されているか否かを判定する(ステップS1402)。CPU801は、消音フラグがオン(ステップS1402の判定がYES)である弦111について、音源部806に、消音指示信号を送信する(ステップS1403)。この結果、音源部806は、消音指示信号を受信した発音中のノートについて、消音を行う。

#### 【0071】

ステップS1403の処理の後、またはステップS1402の判定がNOの場合に、CPU801は、図14のフローチャートで示される図10のステップS1003の統合処理を終了する。

#### 【0072】

図10のステップS1003の統合処理の後、CPU801は、図9のステップS903の演奏検知処理を終了する。

10

20

30

40

50

## 【0073】

以上説明した実施形態において、弦楽器の高音側では一般に、指板のフレット間の間隔が短くなり、さらに指板から弦までの距離が遠くなる。このため、本実施形態でも、ネック部102の胴部101に近い側では、指板108下に設置されるセンサ基板201上のコイル301の間隔が狭くなり、さらに検知のためのコイルのインダクタンスも大きくする必要が生じる。この結果、高音側では電磁誘導の干渉が大きくなってしまう。そこで、これを解消するために、センサ基板201の位置（胴部101側かヘッド部103側か）に応じて、フェーズ数を変更する制御を行ってよい。例えば、ヘッド部103に近く、ネック部102の指板108の表面から弦111までの垂直距離が小さいセンサ基板201の位置では、1フェーズにセンサ基板201上で同時に駆動する共振回路501は3つとされて、2フェーズで6弦分が検知される。また、ネック部102の中央（ヘッド部103と胴部101の中間付近）では、ネック部102の指板108の表面から弦111までの垂直距離が大きくなるので、1フェーズにセンサ基板201上で同時に駆動する共振回路501は2つとされて、3フェーズで6弦分が検知される。さらに、胴部101に近いセンサ基板201の位置では、さらにネック部102の指板108の表面から弦111までの垂直距離が大きくなるので、1フェーズにセンサ基板201上で同時に駆動する共振回路501は1つとされて、6フェーズで6弦分が検知される。このようにして、ネック部102上でのセンサ基板201の位置に応じて、押弦位置の検知精度を一定に維持することが可能となる。

## 【0074】

図15は、センサ基板201(#n)(0 n N-1)上に配置される図5の共振回路501(#n/#1)~301(#n/#6)における、キャパシタ401(#n/#1)~401(#n/#6)とコイル301(#n/#1)~301(#n/#6)の設計例を示す図である。図15(a)の回路構成において、6個のLは、図5のコイル301(#n/#1)~301(#n/#6)の各インダクタンス値に対応し、C1、C2、C3はそれぞれ図5の、1弦と4弦のキャパシタ401(#n/#1)と401(#n/#4)、2弦と5弦のキャパシタ401(#n/#2)と401(#n/#5)、3弦と6弦のキャパシタ401(#n/#3)と401(#n/#6)の各容量値に対応する。C1、C2、C3の各値を変えることにより、図15(b)に示されるように、隣り合う共振回路501のインピーダンスZの絶対値が最大となる共振周(角)周波数がずれ(分割され)、隣接するコイル301間の電磁誘導による干渉を抑えることが可能となる。図15は、共振(角)周波数を3分割した例を示したが、ノイズの影響によっては、周波数の分割数を3に固定する必要は無い。例えば、一般的に弦楽器の高音側では指板の間隔が短くなり、さらに指板から弦までの距離が遠くなる。そこで、指板面と金属弦間の垂直距離が近い低音側では周波数分割数を小さくし、高音側では分割数を多くするといった構成が採用されてよい。

## 【0075】

図16は、図7等で前述したフェーズ分割による時分割処理に加えて、図15で説明した周波数分割の概念を取り入れた、押弦位置検知処理の制御動作の説明図である。各センサ基板201(#n)上の6個のコイル301のうち、互いに1つコイル301をはさんで離れたコイル301のみが1フェーズの間に同時に駆動させられ、他のコイル301は共振を停止させられる。また、隣り合うセンサ基板201では、ネック部102の長手方向にも1つコイル301をはさんで離れたコイル301のみが駆動させられる。2フェーズを高速で切り替えながら押弦位置検知を行うことによって、干渉を抑えつつ精度良く押弦位置を検知することができる。この駆動(周波数3分割以上)の仕方では、同一のセンサ基板201(#n)では、同一の共振周波数をもった共振回路501が同時に駆動しないので、共振によって高効率で伝わる干渉ノイズは伝わりにくい。従って、同時に駆動するコイル301を増やすことができる、すなわち、フェーズ数を少なくすることができる、高速なセンシングが可能となる。

## 【0076】

10

20

30

40

50

本実施例では、電子弦楽器の押弦検出に関して、密接に並んだ共振回路による押弦位置の検知手法を提案したが、この手法は、電子弦楽器に限って応用されるものではない。例えば図17に示されるように、電子管楽器のマウスピース部1702やリード部1701に共振回路1703を配置し、人間1704が電子管楽器のマウスピース部1702を吹奏するときの唇の位置や接触具合、リード1701の閉じ具合などを検知する手法としても応用することも可能である。

なお、本実施例では、隣接の位置を左右隣として説明したが、これに限られず、上下隣や対角線隣を含んでよい。

なお、センサ502(#n/#i)は周波数の変化(変化量)を検知しても良いし、周波数が変化する前後の周波数の値を検知しても良い。周波数の値を検知できれば、周波数の変化前と変化後の周波数の値により周波数の変化が分かるため、周波数の値を検知しても良い。

10

#### 【0077】

以上の実施形態に関して、更に以下の付記を開示する。

##### (付記1)

複数の押弦位置が定められた指板と、

前記押弦位置の夫々に対応付けて設けられ、導電性の複数の弦夫々との間の距離の変化に応じて共振周波数が変化するとともに、当該変化した共振周波数が隣接する前記押弦位置間で夫々異なるように構成された複数の共振回路と、

前記複数の共振回路夫々に対応して設けられ、当該対応する共振回路夫々の共振周波数の変化を検知する複数のセンサと、

20

前記複数のセンサ夫々が検知した前記共振周波数の変化に基づいて、押弦位置を検知する押弦位置検知部と、

を備える押弦位置検知装置。

##### (付記2)

前記共振回路は、隣接する前記押弦位置間で当該各押弦位置に対応する各前記共振回路に含まれる各キャパシタの容量値が異なる付記1に記載の押弦位置検知装置。

##### (付記3)

前記指板の位置に応じて、前記共振周波数の異なる共振回路の数を変化させる付記1または2に記載の押弦位置検知装置。

30

##### (付記4)

複数の弦と、

付記1乃至3のいずれかに記載の前記押弦位置検知装置と、

前記押弦位置検知装置により検知される押弦位置に応じた音高で楽音を発生する音源と、を有する電子弦楽器。

##### (付記5)

複数の押圧位置が定められた誘導性の押圧板と、

前記押圧位置の夫々に対応付けて設けられ、夫々が前記押圧板との間の距離の変化に応じて共振周波数が変化し、当該変化した共振周波数が隣接する前記押圧位置間で夫々異なるように構成された複数の共振回路と、

40

前記複数の共振回路夫々に設けられ、当該共振回路夫々の共振周波数の変化を検知する複数のセンサと、

前記複数のセンサ夫々が検知する前記共振周波数の変化に基づいて、押圧位置を検知する押圧位置検知部と、

を備える押圧位置検知装置。

#### 【符号の説明】

#### 【0078】

100 電子弦楽器

101 脳部

102 ネック部

|               |             |    |

|---------------|-------------|----|

| 1 0 3         | ヘッド部        |    |

| 1 0 4         | ブリッジ部       |    |

| 1 0 5         | ヘキサピックアップ   |    |

| 1 0 6         | 制御回路        |    |

| 1 0 7         | フレット        |    |

| 1 0 8         | 指板          |    |

| 1 0 9         | ナット(上駒)     |    |

| 1 1 0         | ペグ(糸巻き)     |    |

| 1 1 1         | 弦           |    |

| 2 0 1         | センサ基板 2 0 1 | 10 |

| 2 0 2         | 配線基板        |    |

| 3 0 1         | コイル         |    |

| 4 0 1         | キャパシタ       |    |

| 4 0 2         | コネクタ        |    |

| 5 0 1、1 7 0 3 | 共振回路        |    |

| 5 0 2         | センサ         |    |

| 8 0 1         | C P U       |    |

| 8 0 2         | R O M       |    |

| 8 0 3         | R A M       |    |

| 8 0 4         | スイッチ部       | 20 |

| 8 0 5         | インターフェース部   |    |

| 8 0 6         | 音源部         |    |

| 8 0 7         | サウンドシステム    |    |

| 1 7 0 1       | リード         |    |

| 1 7 0 2       | マウスピース      |    |

| 1 7 0 4       | 人間          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

(a)

(b)

【図16】

【図17】

---

フロントページの続き

審査官 菊池 智紀

(56)参考文献 特開2015-52642(JP, A)

米国特許第4580478(US, A)

実開平4-85394(JP, U)

特表2014-523004(JP, A)

特開2012-168747(JP, A)

特開2015-28712(JP, A)

(58)調査した分野(Int.Cl., DB名)

G10H 1/00 - 7/12

G06F 3/02 - 3/047

H01H 36/00 - 36/02