(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6220864号

(P6220864)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

H01S 5/02 (2006.01)

F 1

H01S 5/02

請求項の数 24 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-511630 (P2015-511630)  |

| (86) (22) 出願日 | 平成25年5月7日(2013.5.7)           |

| (65) 公表番号     | 特表2015-519008 (P2015-519008A) |

| (43) 公表日      | 平成27年7月6日(2015.7.6)           |

| (86) 國際出願番号   | PCT/US2013/039971             |

| (87) 國際公開番号   | W02013/169796                 |

| (87) 國際公開日    | 平成25年11月14日(2013.11.14)       |

| 審査請求日         | 平成28年5月9日(2016.5.9)           |

| (31) 優先権主張番号  | 61/644,270                    |

| (32) 優先日      | 平成24年5月8日(2012.5.8)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 516132747<br>マイコム テクノロジー ソリューションズ ホールディングス インコーポレイテッド<br>アメリカ合衆国 マサチューセッツ州 01851 ローウェル チェルムスフォード ストリート 100 |

| (74) 代理人  | 100086771<br>弁理士 西島 孝喜                                                                                     |

| (74) 代理人  | 10008694<br>弁理士 弟子丸 健                                                                                      |

| (74) 代理人  | 100094569<br>弁理士 田中 伸一郎                                                                                    |

| (74) 代理人  | 100095898<br>弁理士 松下 满                                                                                      |

最終頁に続く

(54) 【発明の名称】ビーム形状の改良を伴うレーザ

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

エッチファセットを有する、前記基板の表面上のエピタキシャルレーザと、を備え、前記基板は、前記エッチファセットから外側へ延びて、複数の段差が形成されたテラス部を形成し、前記レーザから放出される光が前記複数の段差の少なくとも1つで反射され、前記レーザの垂直方向の遠視野を変更するように、前記エッチファセットから外側へ順次に延びる各段差が更に前記基板内へ向かう前記基板の表面と略垂直な方向に延びている、半導体チップ。

## 【請求項 2】

前記エッチファセットから外側へ延びる少なくとも1つの反射性側壁をさらに備え、各側壁が前記テラス部の表面に対して略垂直な反射面を有する、請求項1に記載の半導体チップ。

## 【請求項 3】

前記エッチファセットから外側へ延びる前記テラス部と向かい合って配置された屋根部をさらに備え、前記屋根部は、前記テラス部の表面と向かい合う反射面を有する、請求項2に記載の半導体チップ。

## 【請求項 4】

前記テラス部に蒸着された反射コーティングをさらに備えた、請求項1に記載の半導体チップ。

10

20

**【請求項 5】**

基板と、

エッチファセットを有する、前記基板の表面上のエピタキシャルレーザと、

前記エッチファセットから外側へ延びると共に、反射面及び複数の段差が形成され、前記エッチファセットから外側へ順次に延びる各段差が更に前記基板内へ向かう前記基板の表面と略垂直な方向に延びている、テラス部と、

前記エッチファセットから外側へ延びると共に、前記テラス部の反射面と向かい合う反射面を有する屋根部と、

を備え、

前記レーザから放出される光が前記屋根部及び前記複数の段差の少なくとも1つで反射され、前記レーザの垂直方向の遠視野を変更する、半導体チップ。 10

**【請求項 6】**

前記エッチファセットから外側へ延びる少なくとも1つの反射性側壁をさらに備え、各側壁が前記テラス部の反射面に対して略垂直な反射面を有する、請求項5に記載の半導体チップ。

**【請求項 7】**

基板と、

エッチファセットを有する、前記基板の表面上のエピタキシャルレーザであって、前記エピタキシャルレーザにより生成されたレーザビームが前記エッチファセットの臨界角未満の角度で前記エッチファセットに衝突するように、前記エッチファセットが前記基板の表面に対して90°以外の角度を成す表面を有する、前記エピタキシャルレーザと、 20

前記エッチファセットから外側へ延びる少なくとも2つの向かい合った反射面を有する、前記エッチファセットに隣接する構造と、

を備えた、半導体チップ。

**【請求項 8】**

前記構造が、反射面を有する傾斜されたテラス部を備える、請求項7に記載の半導体チップ。

**【請求項 9】**

前記少なくとも2つの向かい合った反射面が、少なくとも2つの反射性側壁をさらに備え、各側壁が前記テラス部の反射面に対して略垂直な反射面を有する、請求項8に記載の半導体チップ。 30

**【請求項 10】**

各側壁がギャップを隔てて前記エッチファセットから分離している、請求項9に記載の半導体チップ。

**【請求項 11】**

前記構造が、反射面を有する複数の段差を含む階段を備え、前記エッチファセットから外側へ順次に延びる各段差が更に前記基板内へ向かう前記基板の表面と略垂直な方向に延びている、請求項7に記載の半導体チップ。

**【請求項 12】**

前記少なくとも2つの向かい合った反射面が、少なくとも2つの反射性側壁をさらに備え、各側壁が前記段差の反射面に対して略垂直な反射面を有する、請求項11に記載の半導体チップ。 40

**【請求項 13】**

各側壁がギャップを隔てて前記エッチファセットから分離している、請求項12に記載の半導体チップ。

**【請求項 14】**

基部であって、この基部に向かい下向きに進む複数の段差を有する階段を有するテラス部の反射面を備え、各段差が更に順次に前記基部内へ向かう前記基部の表面と略垂直な方向に延びている前記基部と、

活性層および少なくとも1つのファセットを備え、前記基部上に取り付けられたレーザ

50

と、

を備えており、

前記レーザから放出される光が前記複数の段差の少なくとも1つで反射され、前記レーザの垂直方向の遠視野を変更するように、前記少なくとも1つのファセットが、前記反射面に隣接して位置付けられている、ハイブリッドアセンブリ。

【請求項15】

前記少なくとも1つのファセットがエッチファセットであり、

前記複数の段差が、前記エッチファセットに隣接して配置された反射性構造である、請求項14に記載のハイブリッドアセンブリ。

【請求項16】

前記基部が、前記レーザが前記基部上で位置決めされるストッパーをさらに含む、請求項14に記載のハイブリッドアセンブリ。

10

【請求項17】

半導体チップを形成する方法であって、

表面を有する基板を準備するステップと、

前記基板の表面上にエピタキシャルレーザを形成するステップと、

前記エピタキシャルレーザをエッチングして、前記エピタキシャルレーザにエッチファセットを形成するステップと、を備え、

前記基板は、前記エッチファセットから外側へ延びて、露出された反射面と複数の段差が形成されたテラス部が形成され、前記レーザから放出される光が前記複数の段差の少なくとも1つで反射され、前記レーザの垂直方向の遠視野を変更する、方法。

20

【請求項18】

半導体チップを形成する方法であって、

基板を準備するステップと、

前記基板上にエピタキシャルレーザを形成するステップと、

前記エピタキシャルレーザをエッチングして、前記エピタキシャルレーザにエッチファセットを形成するステップと、

前記エッチファセットから外側へ延びる前記基板に、露出された反射面と複数の段差が形成されたテラス部を形成するステップと、

を備え、前記レーザから放出される光が前記複数の段差の少なくとも1つで反射され、前記レーザの垂直方向の遠視野を変更する、方法。

30

【請求項19】

半導体チップを形成する方法であって、

基板を準備するステップと、

前記基板の表面上にエピタキシャルレーザを形成するステップと、

前記エピタキシャルレーザをエッチングして、前記エピタキシャルレーザに前記基板の表面に対して90°以外の角度を成すエッチファセットを形成するステップと、

前記エッチファセットから外側へ延びる少なくとも2つの向かい合った反射面を有し、

前記エッチファセットに隣接する構造を形成するステップと、

を備え、前記少なくとも2つの向かい合った反射面が、前記レーザから放出される光が前記少なくとも2つの向かい合った反射面で反射され、前記レーザの垂直方向の遠視野を変更するように、前記エッチファセットに対して配置されている、方法。

40

【請求項20】

ハイブリッドアセンブリを形成する方法であって、

基部であって、この基部に向かい下向きに進む複数の段差を有する階段を有するテラス部の露出された反射面を備えた基部を形成するステップと、

活性層および少なくとも1つの劈開ファセットを有するレーザを前記基部に取り付けるステップと、を備え、

前記少なくとも1つの劈開ファセットは、前記レーザから放出される光が前記複数の段差の少なくとも1つの前記露出された反射面で反射され、前記レーザの垂直方向の遠視野

50

を変更するように、前記露出された反射面に隣接して配置される、方法。

**【請求項 2 1】**

表面を有する基板と、

エッチファセットを有する、前記基板の表面上のエピタキシャルレーザと、

前記基板及び前記エピタキシャルレーザを覆う金属カンパッケージと、

を備えたパッケージ化された半導体レーザ装置であって、

前記基板は、前記エッチファセットから外側へ延びて、露出された反射面及び複数の段差が形成されたテラス部を形成しており、前記レーザから放出される光が前記複数の段差の少なくとも 1 つで反射され、前記レーザの垂直方向の遠視野を変更する、半導体レーザ装置。

10

**【請求項 2 2】**

基板と、

エッチファセットを有する、前記基板上のエピタキシャルレーザと、

露出された反射面及び複数の段差が形成された、前記エッチファセットから外側へ延びるテラス部であって、前記レーザから放出される光が前記複数の段差の少なくとも 1 つで反射され、前記レーザの垂直方向の遠視野を変更する、前記テラス部と、

前記基板、前記エピタキシャルレーザ及び前記テラス部を覆う金属カンパッケージと、

を備えたパッケージ化された半導体レーザ装置。

**【請求項 2 3】**

基板と、

前記基板の表面に対して 90° 以外の角度を成す表面を有するエッチファセットを有する、前記基板の表面上のエピタキシャルレーザと、

前記エッチファセットから外側へ延びる少なくとも 2 つの向かい合った反射面を有し、

前記エッチファセットに隣接する構造と、

前記基板、前記エピタキシャルレーザ及び前記構造を覆う金属カンパッケージと、を備え、前記少なくとも 2 つの向かい合った反射面が、前記レーザから放出される光が前記少なくとも 2 つの向かい合った反射面で反射され、前記レーザの垂直方向の遠視野を変更するように、前記エッチファセットに対して配置されている、パッケージ化された半導体レーザ装置。

20

**【請求項 2 4】**

基部であって、この基部に向かい下向きに進む複数の段差を有する階段を有するテラス部の露出された反射面を備えた基部と、

活性層および少なくとも 1 つの劈開ファセットを有し、前記基部上に取り付けられているレーザと、

前記基板及び前記レーザを覆う金属カンパッケージと、

を備えたパッケージ化されたハイブリッドアセンブリであって、

前記少なくとも 1 つの劈開ファセットは、前記レーザから放出される光が前記複数の段差の少なくとも 1 つの前記露出された反射面で反射され、前記レーザの垂直方向の遠視野を変更するように、前記露出された反射面に隣接して配置されている、ハイブリッドアセンブリ。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

関連出願の相互参照

本特許出願は、米国仮特許出願第 61 / 644,270 号（2012 年 5 月 8 日出願）の優先権を主張するものであり、その主題はその全体が参照により本明細書に組み込まれる。

**【0 0 0 2】**

本開示は、一般的にフォトニックデバイスに関する、より詳細には、改善されたフォトニックデバイスおよびそれらのフォトニックデバイスを製造するための方法に関する。

40

50

**【背景技術】****【0003】**

半導体レーザは、一般に、有機金属化学気相成長法（MOCVD）または分子線エピタキシャル法（MBE）によって基板上に適切な層状半導体材料を成長させて、基板表面と平行な活性層を有するエピタキシャル構造を形成することによってウェハ上に製造される。次にウェハを、さまざまな半導体処理ツールを用いて処理して、活性層を組み込みかつ半導体材料に取り付けられた金属コンタクトを組み込んでいるレーザ光キャビティが生成される。レーザファセットは、一般に、レーザ光キャビティの縁部または端部を画定するように半導体材料をその結晶構造に沿って劈開することによってレーザキャビティの端部に形成される。その結果、バイアス電圧がコンタクトを横断して印加されると、その結果生じた活性層を通る電流の流れにより、電流の流れに垂直な方向に活性層のファセット縁部から光子が放出される。半導体材料はレーザファセットを形成するように劈開されるので、ファセットの位置および向きは制限される。さらに、ウェハは劈開された後、一般に小片となり、その結果従来のリソグラフィ技法をレーザのさらなる処理に容易には使用できない。

10

**【0004】**

劈開ファセットの使用に起因する前述のおよび他の問題が、エッチングによって半導体レーザのファセットを形成する過程の開発につながった。この過程はまた、その開示が参考により本明細書に組み込まれる米国特許第4,851,368号に記述されているように、レーザを同一の基板上の他のフォトニックデバイスと一緒に集積することも可能である。この研究はさらに継続され、エッチファセットに基づいたリッジレーザ過程が、IEEE Journal of Quantum Electronics、28巻、5号、1227-1231頁、1992年5月に開示されている。

20

**【0005】**

半導体レーザの使用における1つの重大な課題に、レーザからの出力ビームと、ビームが導かれるまたは結合する媒体とのミスマッチがある。例えば、スポットサイズ変換器（SSC）を用いた半導体レーザの形成は、レーザ光の光ファイバへのより効率的な結合を可能にし、または光学的配列における許容誤差を拡大できる。しかしながら、一般に、SSCの形成に伴う処理の複雑性およびレーザ特性の低下などのいくつかの不利点がある。レーザ特性の低下の例には、レーザ閾値電流の増大がある。以下の刊行物は、利用される様々なSSC手法を論じている。IEEE Journal of Selected Topics in Quantum Electronics、3巻、3号、968-974頁、「Spot-Size Converter Integrated Laser Diodes (SS-LD's)」と題する論文でItayaらによって、IEEE Journal of Selected Topics in Quantum Electronics、3巻、6号、1308-1320頁、「A Review on Fabrication Technologies for the Monolithic Integration of Tapers with III-V Semiconductor Devices」と題する論文でMoermanらによって、およびIEEE Journal of Selected Topics in Quantum Electronics、3巻、6号、1392-1398頁、「1.3- $\mu$ m Spot-Size-Converter Integrated Laser Diodes Fabricated by Narrow-Stripe Selective MOVPE」と題する論文でYamazakiらによって論じられている。

30

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

レーザ閾値などのレーザ特性に重大な影響を与えずにビーム変更を可能にする単純な過程によって形成されたレーザ構造が非常に望ましい。これは例えば、低費用のパッケージ

40

50

ングを備えた光ファイバへのレーザビームの非常に効率的な結合をもたらすことができる。

**【課題を解決するための手段】**

**【0007】**

本開示によれば、半導体レーザは、その出力ビームの変更が可能なように形成される。

**【0008】**

本開示の一実施形態では、レーザの垂直方向の遠視野の変更は、出力ファセットの前に位置する、傾斜した角または階段を有するパティオ又はテラス部を備えたエッチファセットトレーザを使用して行われる。本開示の別の実施形態では、傾斜した角度または階段を備えたパティオに加えて、側壁を使用してレーザの水平方向の遠視野を変更する。なおも別の実施形態では、レーザの垂直方向の遠視野を変更する屋根部が提供される。なおも別の実施形態では、劈開またはエッチファセットトレーザが、傾斜されたパティオまたは階段などの構造を有する、シリコンまたは窒化アルミニウム(AlN)などの基板または基部上に活性側を下側にして取り付けられる。10

**【0009】**

例として、本開示の一実施形態では、以下を備える半導体チップを開示する。すなわち、基板、基板上のエピタキシャルレーザ、エッチファセットすなわちエッチングされたファセット、およびエッチファセットに隣接する構造。構造は、下向きの斜面および少なくとも1つの段差を有する下向きの階段のいずれかを有するパティオである。半導体チップは、反射性側壁も備えることができる。半導体チップは、エッチファセットの前に位置する屋根部をさらに備えることができる。屋根部は、エッチファセットの最低点よりも最高点に近い下部反射面を有する。半導体チップは、構造上に蒸着された反射コーティングを追加的に備えることができる。半導体チップは、InP、GaAsおよびGaNを含む群から選択された基板をなおもさらに備えることができる。20

**【0010】**

本開示の別の実施形態では、以下を備える半導体チップを開示する。すなわち、基板、基板上のエピタキシャルレーザ、エッチファセットすなわちエッチングされたファセット、およびエッチファセットの前に位置する屋根部。屋根部は、エッチファセットの最低点よりも最高点に近い下部反射面を有する。半導体チップは、反射性側壁も備えることができる。半導体チップは、InP、GaAsおよびGaNを含む群から選択された基板をなおもさらに備えることができる。30

**【0011】**

本開示のなおも別の実施形態では、以下を備える半導体チップを開示する。すなわち、基板、基板上のエピタキシャルレーザ、基板の平面と90°以外の角度を成すエッチファセットすなわちエッチングされたファセット、臨界角未満の角度でエッチファセットに衝突するレーザビーム、およびエッチファセットに隣接する反射性構造。半導体チップは、傾斜されたパティオである構造も備えることができる。半導体チップは、反射性側壁をさらに備えることができる。側壁は、エッチファセットとギャップを隔てて分離できる。半導体チップは、少なくとも1つの段差を含有する階段である構造を追加的に備えることができる。半導体チップは、InP、GaAsおよびGaNを含む群から選択された基板をなおもさらに備えることができる。40

**【0012】**

本開示のなおも別の実施形態では、以下を備えるハイブリッドアセンブリを開示する。すなわち、下向きの斜面および少なくとも1つの段差を有する下向きの階段のいずれかを有するパティオの反射面を備えた基部、ならびに活性層および少なくとも1つのファセットを備え、基部上に活性側を下側にして配置されたレーザ。少なくとも1つのファセットは、反射面に隣接して位置付けられる。ハイブリッドアセンブリは、AlNまたはSiのいずれかである基部も備えることができる。ハイブリッドアセンブリは、エッチファセットすなわちエッチングされたファセットである少なくとも1つのファセットをさらに備え、これはエッチファセットに隣接する反射性構造をさらに備えることができる。ハイブリ50

ツドアセンブリは、InP、GaAs および GaN を含む群から選択された基板上にエピタキシャルに蒸着されたレーザ構造から形成されたレーザを追加的に備えることができる。ハイブリッドアセンブリは、ストッパーをさらに含む基部をなおもさらに備えることができる。

#### 【0013】

本開示の前述のおよび追加的な目的、特徴および利点は、以下に簡潔に記述する添付図面と併せて本開示の以下の詳細な説明から当業者に明らかになる。

#### 【図面の簡単な説明】

#### 【0014】

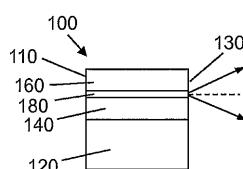

【図1】図1(a)は、劈開によって形成された前部および後部ファセットの両方を備えた半導体レーザの断面である。図1(b)は、RSoft 有限差分時間領域(FDTD)シミュレーションによって得られた、前部または後部ファセットいずれかにおける対応する垂直方向の遠視野(VFF)である。10

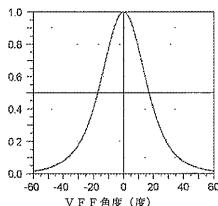

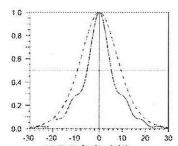

【図2】図2(a)は、前部ファセットに隣接する2μmの平坦なパティオを有する、エッチングによって形成された前部および後部ファセットの両方を備えた半導体レーザの断面である。図2(b)は、RSoft FDTDシミュレーションによって得られた実線であるこの構造に対応するVFF、および参考として破線である図1(b)のVFFを含有する。

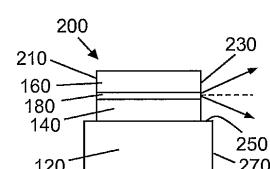

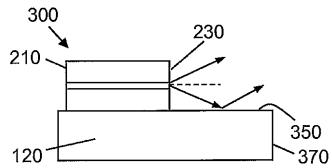

【図3】図3(a)は、前部ファセットに隣接する10μmの平坦なパティオを有する、エッチングによって形成された前部および後部ファセットの両方を備えた半導体レーザの断面である。図3(b)は、RSoft FDTDシミュレーションによって得られた実線であるこの構造に対応するVFF、および参考として破線である図1(b)のVFFを含有する。20

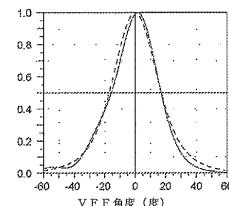

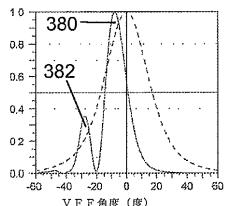

【図4】図4(a)は、前部ファセットに隣接する全長10μmの10°に傾斜したパティオを有する、エッチングによって形成された前部および後部ファセットの両方を備えた半導体レーザの断面である。図4(b)は、RSoft FDTDシミュレーションによって得られた実線であるこの構造に対応するVFF、および参考として破線である図1(b)のVFFを含有する。

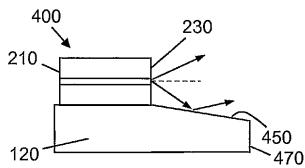

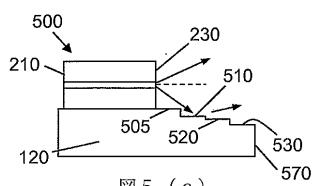

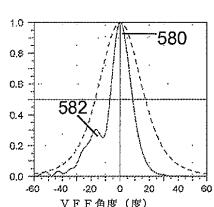

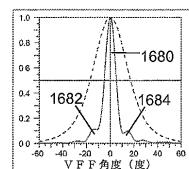

【図5】図5(a)は、エッチングによって形成された前部および後部ファセットの両方を備え、そして前部ファセットに隣接する階段を備えた半導体レーザの断面である。階段における各段差は、高さが0.6μm、幅が2.5μmである。図5(b)は、RSoft FDTDシミュレーションによって得られた実線であるこの構造に対応するVFF、および参考として破線である図1(b)のVFFを含有する。30

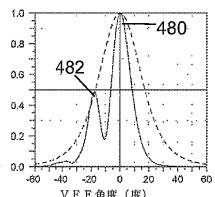

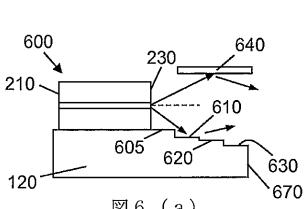

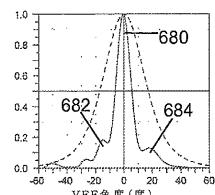

【図6】図6(a)は、エッチングによって形成された前部および後部ファセットの両方を備え、そして前部ファセットに隣接する階段を備えた半導体レーザの断面である。階段における各段差は、高さが0.6μm、幅が2.5μmである。階段の上方に位置する厚さが1μmの「屋根部」は、階段に面する屋根部の側面がレーザ光に対して反射性であり、全長が3.75μmである。これは、断面において屋根部の左下隅が第一の段差の縁部の上方4.75μmに位置付けられる。図6(b)は、RSoft FDTDシミュレーションによって得られた実線であるこの構造に対応するVFF、および参考として破線である図1(b)のVFFを含有する。40

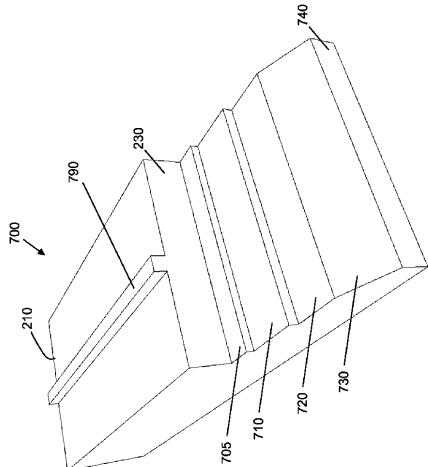

【図7】ビームの垂直方向を制御するのに使用される、前部ファセットに隣接する階段を有する、リッジレーザ前部ファセットを示す斜視図である。

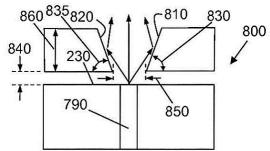

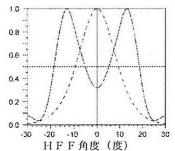

【図8】図8(a)は、前部ファセットの前方に配置された反射性の角度の付いた側壁を備えた半導体レーザの上面図である。図8(b)は、前部ファセットから出て、反射性側壁により変更された光に関する光強度のRSoft FDTDシミュレーションを示す。図8(c)は、反射性側壁により変更された水平方向の遠視野(HFF)を実線に示し、一方でいかなる反射性側壁も有さないレーザに対応するHFFを参考として破線に示す。

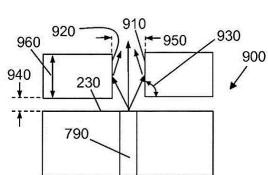

【図9】図9(a)は、前部ファセットの前方に配置された反射性の平行側壁を備えた半導体レーザの上面図である。図9(b)は、前部ファセットから出て、反射性側壁により50

変更された光に関する光強度の R S o f t F D T D シミュレーションを示す。図 9 ( c ) は、反射性側壁により変更された H F F を実線に示し、一方でいかなる反射性側壁も有さないレーザに対応する H F F を参考として破線に示す。

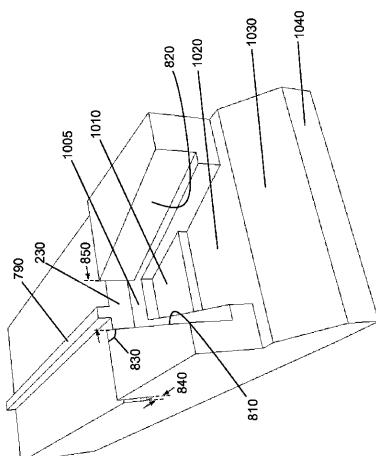

【図 10】前部ファセットに隣接する足部および 3 つの段差から成る階段を持つリッジレーザ前部ファセットを示す斜視図である。第一および第二の段差は平坦であり、第三の段差は平坦であるが、その上基板に向かい傾斜する。これは図 5 ( a ) の場合のようにビームの垂直方向を制御するのに使用されるが、ビームの水平方向を制御するのに使用される図 8 のものに類似する側壁も含む。

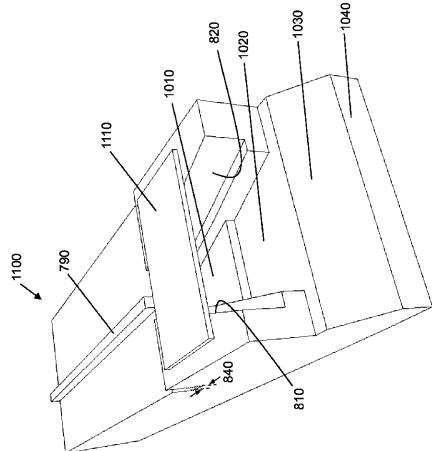

【図 11】階段および屋根部を備えたリッジレーザ前部ファセットを示す斜視図である。これは図 6 ( a ) の場合のようにビームの垂直方向を制御するのに使用されるが、ビームの水平方向を制御するのに使用される図 8 のものに類似する側壁も含む。10

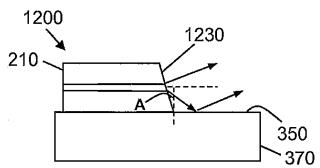

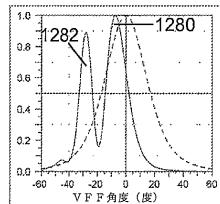

【図 12】図 12 ( a ) は、基板の垂直線から平面まで角度 A に傾斜する前部エッチファセット、および基板と垂直またはほぼ垂直な後部エッチファセットを備え、そして前部ファセットに隣接する 10 μm の平坦なパティオを備えた半導体レーザの断面である。図 12 ( b ) は、R S o f t F D T D シミュレーションによって得られた実線であるこの構造に対応する V F F 、および参考として破線である図 1 ( b ) の V F F を含有する。

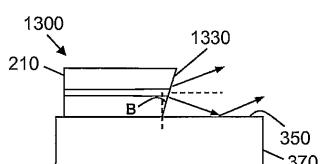

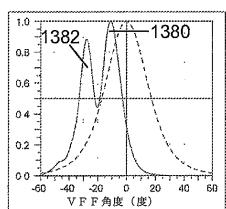

【図 13】図 13 ( a ) は、基板の垂直線から平面まで角度 B に傾斜する前部エッチファセット、および基板と垂直またはほぼ垂直な後部エッチファセットを備え、そして前部ファセットに隣接する 10 μm の平坦なパティオを備えた半導体レーザの断面である。図 13 ( b ) は、R S o f t F D T D シミュレーションによって得られた実線であるこの構造に対応する V F F 、および参考として破線である図 1 ( b ) の V F F を含有する。20

【図 14】図 14 ( a ) は、基板の垂直線から平面まで角度 A に傾斜する前部エッチファセット、および基板と垂直またはほぼ垂直な後部エッチファセットを備え、そして前部ファセットに隣接する階段を備えた半導体レーザの断面である。階段における各段差は、高さが 0.6 μm 、幅が 2.5 μm である。図 14 ( b ) は、R S o f t F D T D シミュレーションによって得られた実線であるこの構造に対応する V F F 、および参考として破線である図 1 ( b ) の V F F を含有する。

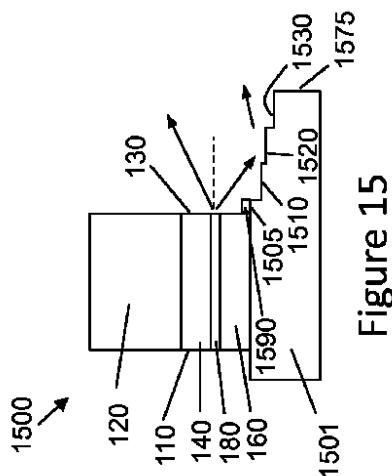

【図 15】シリコン基部に活性側を下側にして取り付けられた劈開ファセットレーザを示す断面図である。このシリコン基部は階段を含有し、ファセットがシリコン階段に隣接するようにレーザが位置付けられる。30

【図 16】図 16 ( a ) は、エッチングによって形成された前部および後部ファセットの両方を備え、そして前部ファセットに隣接する階段を備えた半導体レーザの断面である。シリコン基部は階段を含有し、レーザがシリコン基部に活性側を下側にして取り付けられ、その結果前部ファセットがシリコン階段に隣接するように位置付けられる。図 16 ( b ) は、R S o f t F D T D シミュレーションによって得られた実線であるこの構造に対応する V F F 、および参考として破線である図 1 ( b ) の V F F を含有する。

【図 17】図 17 ( a ) は、前部ファセットの前方に配置された反射性の湾曲側壁を備えた半導体レーザの上面図である。図 17 ( b ) は、前部ファセットから出て、反射性側壁により変更された光に関する光強度の R S o f t F D T D シミュレーションを示す。図 17 ( c ) は、反射性側壁により変更された H F F を実線に示し、一方でいかなる反射性側壁も有さないレーザに対応する H F F を参考として破線に示す。40

#### 【発明を実施するための形態】

##### 【0015】

図 1 ( a ) は、前部ファセット 130 および後部ファセット 110 の劈開によって形成された半導体レーザ 100 を示す。レーザ構造は、下部クラッド層 140 の形成を可能にするエピタキシャルに蒸着された層を有する基板 120 を備える。下部クラッド層 140 は、基板内に延長してもよいし、図 1 ( a ) に示すように完全にエピタキシャルに蒸着されてもよい。この層の厚さは 1.83 μm であり、活性領域 180 の厚さは 0.34 μm であり、上部クラッド層 160 の厚さは 1.83 μm である。レーザは、およそ 1310 nm のレーザ光を放出する。図 1 ( b ) は、R S o f t 有限差分時間領域 ( F D T D ) シ50

ミュレーションによって得られた、図1(a)の構造の前部または後部ファセットいずれかに関する垂直方向の遠視野(VFF)を示す。

#### 【0016】

図2(a)は、基板120の平面と垂直またはほぼ垂直な前部ファセット230および後部ファセット210のエッチングによって形成された半導体レーザ200の断面を示す。このエッチファセットすなわちエッチングされたファセットのすれば、通常、基板の平面の法線から最大3°である。エッチファセットレーザを形成する過程の例は、米国特許出願第11/356203号または米国特許第8,130,806号に記述されている。これらは共に、本願の譲受人に譲渡され、その開示はその全体が参照により本明細書に組み込まれる。エッチファセットは、通常、上部クラッド層、活性領域、および下部クラッド層の少なくとも一部を通じたエッチングにより形成される。レーザチップは、前部ファセット230に隣接するパティオ又はテラス部250の幅が2μmとなるように270でシンギュレートされる(2μmは、前部ファセットとシンギュレートされた平面270との間の水平距離である)。図2(b)は、前部ファセットからのRSoftFDTDシミュレーションによって得られたVFFを実線に示し、参考として図1(b)のVFFを破線に示す。2つのVFF曲線の間にはわずかな差異しかない。

#### 【0017】

図3(a)は、前部ファセット230および後部ファセット210のエッチングによって形成された半導体レーザ300の断面を示す。レーザチップは、前部ファセット230に隣接するパティオ又はテラス部350の幅が10μmとなるように370でシンギュレートされる。図3(b)は、前部ファセットからのRSoftFDTDシミュレーションによって得られたVFFを実線に示し、参考として図1(b)のVFFを破線に示す。2つのVFF曲線の間には相当な差異がある。実線のVFFは、破線と比較してその主ロープ380の半値全幅(FWHM)が顕著に狭いことを示す。さらに、実線のVFFは、中心からおよそ10°であるかなりの程度のビームポインティング、およびサイドロープ382の存在を示す。狭いFWHMは、例えば光ファイバへの結合効率を高くできるため非常に有用である。しかしながら、ビームポインティングが問題を招き、パッケージ化されたレーザの大抵の従来型の手法、および光ファイバとの結合に不適合である。

#### 【0018】

図4(a)は、前部ファセット230および後部ファセット210のエッチングによって形成された半導体レーザ400の断面を示す。レーザチップは、前部ファセット230に隣接するパティオ又はテラス部450の幅が10μmとなるように470でシンギュレートされる。ただし、パティオ450はまた、基板120の方に下向きに10°傾斜付けられる。図4(b)は、前部ファセットからのRSoftFDTDシミュレーションによって得られたVFFを実線に示し、参考として図1(b)のVFFを破線に示す。実線のVFFは、破線と比較してその主ロープ480のFWHMが顕著に狭いことを示す。しかしながら、図3(b)とは異なり、実線のVFFの主ロープ480は、中心に位置し、いかなる有意なビームポインティングも示さない。VFFにおける主ロープの狭いFWHM、およびビームポインティングの欠如は、例えば、光ファイバとの結合において半導体レーザチップの従来型のパッケージングを備えた光ファイバとの結合効率を高くできるため非常に有用である。一般に、サイドロープ482の出力は、例えば、主ロープと同程度に効率的には光ファイバに結合しない。したがって、例えば光ファイバとの最高効率の結合のために、サイドロープを最小化し、主ロープを最大化することが望ましい。

#### 【0019】

図5(a)は、前部ファセット230および後部ファセット210のエッチングによって形成された半導体レーザ500の断面を示す。レーザチップは、前部ファセットに隣接する階段の幅が10μmとなるように570でシンギュレートされる。階段は、足部505ならびに3つの平坦な段差510、520および530を有し、基板に向かい下向きに進む。段差510の面は、エッチングされた前部ファセット230における活性領域、および下部クラッド層の少なくとも一部よりも低い。段差520の面は段差510よりも低

10

20

40

50

く、段差 530 の面は段差 520 よりも低い。各段差は、幅が 2.5 μm であり、高さが 0.6 μm である。足部 505 は、段差 510 の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差 510 よりもわずかだけ高くできる。図 5 (b) は、前部ファセットからの RSoft FDTD シミュレーションによって得られた VFF を実線に示し、参考として図 1 (b) の VFF を破線に示す。実線の VFF は、破線と比較してその主ロープ 580 の FWHM が顕著に狭いことを示す。図 5 (b) と同様に、実線の VFF の主ロープ 580 は、中心に位置し、いかなる有意なビームポインティングも示さない。階段の単一の段差でさえ、ビームポインティングの除去に重大な影響を及ぼすことが示された。サイドロープ 582 は、サイドロープ 482 と比較して強度が減少する。

10

### 【0020】

図 6 (a) は、前部ファセット 230 および後部ファセット 210 のエッチングによって形成された半導体レーザ 600 の断面を示す。レーザチップは、前部ファセットに隣接する階段の幅が 10 μm となるように 670 でシンギュレートされる。階段は、足部 605 ならびに 3 つの平坦な段差 610、620 および 630 を有し、基板に向かい下向きに進む。段差 610 の面は、エッチングされた前部ファセット 230 における活性領域、および下部クラッド層の少なくとも一部よりも低い。段差 620 の面は段差 610 よりも低く、段差 630 の面は段差 620 よりも低い。各段差は、幅が 2.5 μm であり、高さが 0.6 μm である。さらに、厚さが 1 μm の屋根部 640 が階段の上方に位置し、階段に面する屋根部の面がレーザ光に対して反射性であり、屋根部の全長は 3.75 μm である。これは、断面において屋根部の左下隅が階段の第一の段差の縁部の上方 4.75 μm に位置付けられる。図 6 (b) は、前部ファセットからの RSoft FDTD シミュレーションによって得られた VFF を実線に示し、参考として図 1 (b) の VFF を破線に示す。実線の VFF は、破線と比較してその主ロープ 680 の FWHM が顕著に狭いことを示す。図 4 (b) および図 5 (b) と同様に、実線の VFF の主ロープ 680 は、中心に位置し、いかなる有意なビームポインティングも示さない。それにもかかわらず、より多くの出力が主ロープ 680 に集中し、別の小さいサイドロープ 684 が存在するが、サイドロープ 682 は、サイドロープ 482 および 582 と比較してさらに減少する。

20

### 【0021】

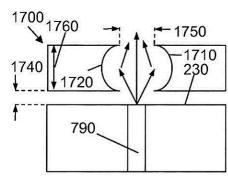

図 7 は、2 つの段差を持つ階段および足部に隣接する前部ファセット 230 を備えたりッジレーザ 700 の斜視図である。足部 705 が、その平面が前部エッチファセット 230 の最低点である第一の面に位置して示されている。第 1 の段差 710 および第 2 の段差 720 は、共に平坦な面を有する。傾斜面 730 が、基板に向かい下向きに角度付けられて存在する。チップは 740 でシンギュレートされている。リッジ 790 レーザを示したが、本明細書に記述する特徴を利用して他の種類のレーザを製造できることが理解される。例えば、レーザ構造は、埋め込みヘテロ構造 (BH) レーザでもよい。レーザの種類は、例えば、ファブリペロー (FP) レーザでもよいし、分布帰還型 (DFB) レーザでもよい。足部 705 の面は、段差 710 の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差 710 よりもわずかだけ高くできる。足部を図 7 に示すように平滑な反射面を備えて製造する場合には、それを階段の第 1 の段差として使用できる。

30

### 【0022】

実行した実験では、2 種類のリッジレーザが製造された。タイプ 1 は、図 2 (a) に示す類のものであり、タイプ 2 は、図 5 (a) に示すような 3 つの段差を持つ階段を備えたものであった。固体リッジレーザの従来の製造で従来型にあるように、基板は、例えば適切にドープできる III-V 族化合物またはそれらの合金から形成できる。基板は、有機金属化学気相成長法 (MOCVD) または分子線エピタキシャル法 (MBE) などのエピタキシャル蒸着により、連続層に蒸着される上面を含む。レーザ構造は、InP 基板上に以下の層を備えた 1310 nm 放出エピタキシャル構造であった。すなわち、n-InP 下部クラッド層、AlGaInAs 下部グレーディド領域、その各々が引張歪 AlGaI

40

50

n A s バリアに挟まれた、圧縮歪 AlGaInAs 量子井戸を含有する活性領域、AlGaInAs 上部グレーディド領域、p-InP 上部クラッド層、および高度に p-ドープされた InGaAs キャップ層。ウェハレベルの試験により、リッジレーザの閾値電流などの電子的特性が、タイプ1のレーザとタイプ2のレーザとで非常に類似すると確定された。タイプ1およびタイプ2のレーザは、反射防止膜を有さない屈折率 1.496 の 1.5 mm レンズを備えた TO-56 can にパッケージングした。パッケージ化したレーザは、最適位置において光ファイバと結合し、そのファイバにおけるスロープ効率（ファイバに結合したレーザ出力の量を、レーザダイオードに適用される閾値を超えた電流量で割った値）を確定した。タイプ1に関するファイバの平均 SE は、0.0737 W/A であった。一方で、タイプ2に関するファイバの平均 SE は、0.0970 W/A であった。

10 前部ファセットに隣接する階段に起因する結合効率の増大は、31% を上回った。

#### 【0023】

図8(a)は、幅が 2 μm のリッジ 790 を備えた半導体レーザ 800 の上面図を示す。このレーザは図8(c)に示す水平方向の遠視野(HFF)を有し、この図には図1(a)または図2(a)に示す事例のような前部ファセットの前方に位置する特徴がない場合の RSoftFDTD シミュレーションによって得られた破線を共に示す。反射性側壁 810 および 820 が、レーザと反射性側壁との間の電気的分離を許容するため 2 μm のギャップ 840 をあけて前部エッチファセット 230 の前方に配置される。側壁構造の全長 860 は 13 μm である。反射面 810 は、前部エッチファセットの平面に対して 75° の角度 830 を成す。反射面 820 は、前部エッチファセットの平面に対して 75° の角度 835 を成す。2つの反射性側壁間のギャップ 850 は、前部エッチファセット同士が最も近接した点において 6 μm である。図8(b)は、リッジレーザおよび反射性側壁の RSoftFDTD シミュレーションを示す。図8(c)は、反射性側壁が HFF に与える影響を実線に示し、この HFF は、反射性側壁のないレーザのそれよりも顕著に狭い。半導体レーザからのより狭い HFF は、光ファイバへのより優れた結合を含む多くの用途を有する。

20

#### 【0024】

図9(a)は、幅が 2 μm のリッジ 790 を備えた半導体レーザ 900 の上面図を示す。このレーザは図9(c)に示す水平方向の遠視野(HFF)を有し、この図には図1(a)または図2(a)に示す事例のような前部ファセットの前方に位置する特徴がない場合の RSoftFDTD シミュレーションによって得られた破線を共に示す。反射性側壁 910 および 920 が、レーザと反射性側壁との間の電気的分離を許容するため 2 μm のギャップ 940 をあけて前部エッチファセットの前方に配置される。側壁構造の全長 960 は 13 μm である。反射面 910 は、前部エッチファセットの平面に対して 90° の角度 930 を成す。反射面 920 は 910 と平行である。2つの反射性側壁間のギャップ 950 は、6 μm である。図9(b)は、リッジレーザおよび反射性側壁の RSoftFDTD シミュレーションを示す。図9(c)は、反射性側壁が HFF に与える影響を実線に示し、2つの区域のロープが側壁の結果として形成されたのを示す。レーザビームの 2 つ以上のロープへの分割は、それぞれの光を 2 つ以上の導波管に提供するなどの多くの用途を有する。

30

#### 【0025】

図10は、前部ファセット 230 を有するリッジレーザ 1000 の斜視図を示し、前部ファセット 230 に隣接する 2 つの段差を持つ階段および足部を備えている。第1の平坦な面は、前部エッチファセット 230 の最低点により画定された足部 1005 である。第1の段差 1010 および第2の段差 1020 は平坦な面を有する。傾斜面 1030 が基板に向かい下向きに角度付けられ、チップは 1040 でシンギュレートされる。構造は反射性側壁 810 および 820 を含む。階段構造により、より多くのレーザ光出力が前部エッチファセットから出て、リッジから延伸しかつリッジ 790 と平行の線に沿って維持され得る。したがって、反射性側壁 810 および 820 の影響が、例えば図3(a)の構造の事例にあり得るよりも顕著である。足部 1005 の面は、段差 1010 の面よりも低くて

40

10

20

30

40

50

もよいが、何らかの顕著な様式でビームに干渉しない限り、段差 1010 よりもわずかだけ高くできる。足部を図 10 に示すように平滑な反射面を有するものとして設計する場合には、それを階段の第 1 の段差として使用できる。

#### 【 0026 】

側壁 810 および 820 のための反射面を形成するために、反射性金属のスパッタリングがリフトオフ過程と共に用いられる。あるいは、蒸着金属をリフトオフ過程と共に用いる。ただしこの過程では、平坦な面 1010 および 1020 とともに側壁 810 および 820 にも良好なカバレッジを許容するために基板が蒸着中に揺らされる。他の種類の反射薄膜を側壁に蒸着できることが理解される。

#### 【 0027 】

図 11 は、レーザ 1100 の斜視図を示す。これは図 10 と同一であるが、図 6 ( a ) および図 6 ( b ) の記述において前述したように、主ロープにおけるレーザ光出力をさらに集中し、サイドロープを減少するための屋根部 1110 を含む。屋根部は、金属などの反射性材料を用いて蒸着され、これには、半導体における金属ブリッジの形成に使用される処理に類似する処理が使用される（例えば、<http://www.microchem.com/App1-IIIVs-Airbridges.htm> を参照されたい）。

#### 【 0028 】

図 12 ( a ) は、基板の平面の法線に対して 10° の角度 A を成す前部ファセット 1230 のエッチング、および基板の平面と垂直またはほぼ垂直な後部ファセット 210 のエッチングによって形成された半導体レーザ 1200 の断面を示す。レーザチップは、前部ファセット 1230 に隣接するパティオ 350 の幅が 10 μm となるように 370 でシンギュレートされる。図 12 ( b ) は、前部ファセットからの RSoft FDTD シミュレーションによって得られた VFF を実線に示し、参考として図 1 ( b ) の VFF を破線に示す。2 つの VFF 曲線の間には相当な差異がある。実線の VFF は、破線と比較してその主ロープ 1280 の FWHM が顕著に狭いことを示す。さらに、実線の VFF は、中心からおよそ 10° であるかなりの程度のビームポインティング、およびサイドロープ 1282 の存在を示す。サイドロープ 1282 は、サイドロープ 382 よりも大きい。

#### 【 0029 】

図 13 ( a ) は、基板の平面の法線に対して 10° の角度 B を成す前部ファセット 1330 のエッチング、および基板の平面と垂直またはほぼ垂直な後部ファセット 210 のエッチングによって形成された半導体レーザ 1300 の断面を示す。レーザチップは、前部ファセット 1330 に隣接するパティオ 350 の幅が 10 μm となるように 370 でシンギュレートされる。図 13 ( b ) は、前部ファセットからの RSoft FDTD シミュレーションによって得られた VFF を実線に示し、参考として図 1 ( b ) の VFF を破線に示す。2 つの VFF 曲線の間には相当な差異がある。実線の VFF は、破線と比較してその主ロープ 1380 の FWHM が顕著に狭いことを示す。さらに、実線の VFF は、中心からおよそ 10° であるかなりの程度のビームポインティング、およびサイドロープ 1382 の存在を示す。サイドロープ 1382 は、サイドロープ 382 よりも大きい。

#### 【 0030 】

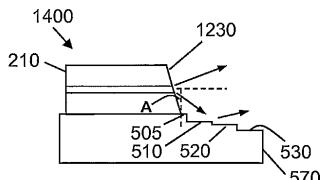

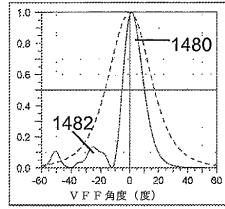

図 14 ( a ) は、基板の平面の法線に対して 10° の角度 A を成す前部ファセット 1230 のエッチング、および基板の平面と垂直またはほぼ垂直な後部ファセット 210 のエッチングによって形成された半導体レーザ 1400 の断面を示す。レーザチップは、前部ファセットに隣接する階段の幅が 10 μm となるように 570 でシンギュレートされる。階段は、足部 505 ならびに 3 つの平坦な段差 510、520 および 530 を有し、基板に向かい下向きに進む。段差 510 は、エッチングされた前部ファセット 1430 における活性領域、および下部クラッド層の少なくとも一部よりも低い。段差 520 の面は段差 510 よりも低く、段差 530 の面は段差 520 よりも低い。各段差は、幅が 2.5 μm であり、高さが 0.6 μm である。足部 505 は、段差 510 の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差 510 よりもわずかだけ高くできる。図 14 ( b ) は、前部ファセットからの RSoft FDTD シミュレーションによっ

10

20

30

40

50

て得られたVFFを実線に示し、参考として図1(b)のVFFを破線に示す。実線のVFFは、破線と比較してその主ロープ1480のFWHMが顕著に狭いことを示す。図14(b)に見られるように、実線のVFFの主ロープ1480は、中心に位置し、いかなる有意なビームポインティングも示さない。階段の単一の段差でさえ、ビームポインティングの除去に重大な影響を及ぼすことが示された。サイドロープ1482は、サイドロープ482と比較して強度が減少する。

### 【0031】

図15は、シリコン基板または基部上に、活性側を下側にして取り付けられた、図1(a)の劈開ファセットレーザのハイブリッドアセンブリ1500を示す断面図である。A1Nなどの他の種類の基板または基部材料をシリコン基部の代わりに用いることができる。シリコン基部は、1575で切断またはシンギュレートされる。シリコン基部は、下向きの階段構造を含有する。図15に示された階段構造は、足部1505ならびに3つの段差1510、1520および1530を示す。段差1510は段差1520よりも高く、段差1520は段差1530よりも高い。各段差は、幅が $2.5\mu m$ であり、高さが $0.6\mu m$ である。足部1505は、段差1510の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差1510よりもわずかだけ高くできる。劈開ファセットレーザは、ファセットがシリコン階段に隣接し、前部ファセットに隣接する階段の幅が $10\mu m$ となるように注意深く位置付けられる。図5(b)の実線のVFFに類似するVFFがRSoft FDTDシミュレーションによって得られた。シリコン基部は、ストッパー1590をさらに組み込み、これにより、劈開ファセットレーザをシリコン基部に高精度に位置決めることができる。

### 【0032】

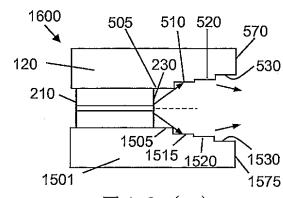

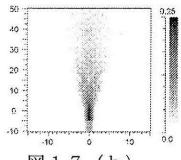

図16(a)は、シリコン基部上に活性側を下側にして取り付けられた、図5(a)のエッチファセットレーザのハイブリッドアセンブリ1600を示す断面図である。シリコン基部は、1575で切断またはシンギュレートされる。シリコン基部は、下向きの階段構造を含有する。図16(a)に示された階段構造は、足部1505ならびに3つの段差1510、1520および1530を示す。段差1510は段差1520よりも高く、段差1520は段差1530よりも高い。各段差は、幅が $2.5\mu m$ であり、高さが $0.6\mu m$ である。足部1505は、段差1510の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差1510よりもわずかだけ高くできる。レーザチップは、前部ファセットに隣接する階段の幅が $10\mu m$ となるように570でシンギュレートされる。階段は、足部505ならびに3つの平坦な段差510、520および530を有し、基板120に向かい下向きに進む。段差510の面は、エッチングされた前部ファセット230における活性領域、および下部クラッド層の少なくとも一部よりも低い。段差520の面は段差510よりも(基板120の方に)低くなり、段差530の面は520よりも(基板120の方に)低くなる。各段差は、幅が $2.5\mu m$ であり、高さが $0.6\mu m$ である。足部505は、段差510の面よりも低くてもよいが、何らかの顕著な様式でビームに干渉しない限り、段差510よりもわずかだけ高くできる。エッチファセットレーザは、ファセットがシリコン階段に隣接し、前部ファセットに隣接するシリコン階段の幅が約 $10\mu m$ となるように注意深く位置付けられる。図16(b)は、前部ファセットからのRSoft FDTDシミュレーションによって得られたVFFを実線に示し、参考として図1(b)のVFFを破線に示す。実線のVFFは、破線と比較してその主ロープ1680のFWHMが顕著に狭いことを示す。図16(b)に見られるように、実線のVFFの主ロープ1680は、中心に位置し、いかなる有意なビームポインティングも示さない。サイドロープ1682は、サイドロープ482と比較して強度が減少する。別の小さいサイドロープ1684が存在する。

### 【0033】

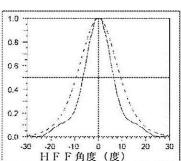

図17(a)は、幅が $2\mu m$ のリッジ790を備えた半導体レーザ1700の上面図を示す。このレーザは図17(c)に示す水平方向の遠視野(HFF)を有し、この図には図1(a)または図2(a)に示す事例のような前部ファセットの前方に位置する特徴が

10

20

30

40

50

ない場合の R S o f t F D T D シミュレーションによって得られた破線を共に示す。反射性の湾曲側壁 1710 および 1720 が、レーザと反射性側壁との間の電気的分離を許容するために 6  $\mu\text{m}$  のギャップ 1740 をあけて前部エッチファセットの前方に配置される。湾曲側壁構造の全長 1760 は 4  $\mu\text{m}$  であり、曲率半径は 3  $\mu\text{m}$  である。湾曲側壁構造間のギャップ 1750 は 7  $\mu\text{m}$  である。図 17 (b) は、リッジレーザおよび反射性側壁の R S o f t F D T D シミュレーションを示す。図 17 (c) は、反射性側壁が H F F に与える影響を実線に示し、この H F F は、反射性側壁のないレーザのそれよりも顕著に狭いのを示す。この例は、単純な直線以外にも多くの形状の側壁が可能であることを例証する。

## 【0034】

10

図 12 (a)、図 13 (a) および図 14 (a) に示された装置などの角度付けられてエッチングされた前部ファセットを備えた装置は、レーザビームが前部ファセットの臨界角未満の角度で前部ファセットに衝突するように角度付けられたファセットを有する。これにより、これらのファセットにおける少なくとも部分的な透過が可能になる。反射防止コーティングされ角度付けられた前部ファセットを備えた DFB レーザが、この手法を特によく実行する。

## 【0035】

スポットサイズ変換器 (SSC) を備えた半導体レーザを使用した先行技術の装置は、レーザから放出されたビームの形状を変更することを可能にした。しかしながら、SSC の組み込みにより、レーザ性能が損失した。例えば、SSC を備えたレーザは、SSC を備えない同じレーザよりも閾値電流が高いであろう。本開示の 1 つの有益な特性は、階段、屋根部または側壁をレーザに追加しても、レーザ閾値電流が何らかの顕著な様式により影響を受けないことである。ビーム形状の変更により、いくつかの利点がもたらされる。例えば、光ファイバもしくは光導波路へのより高い結合効率、または光学的配列における許容誤差の拡大がある。

20

## 【0036】

例えば、レーザ 200 をエッチングによって形成された後部ファセット 210 を有するように記述したが、後部ファセットを、代わりに劈開によって形成できることが理解される。

## 【0037】

30

面 730 または 1030 の角度が基板に向っておよそ 45° 以上である場合、これは何らかの顕著な様式においてレーザビームの制御または変更に寄与しない。しかしながら、シンギュレーション位置における許容誤差は顕著に増大できる。すなわち、平面 740 と前部エッチファセット 230 の平面との間の距離は、より大きい許容誤差を有し、シンギュレーション過程の実行がより容易になる。

## 【0038】

階段構造における段差の各平坦な面の種々の深度レベルは、エピタキシャル成長によって高精度に画定される。InP ベースのレーザの場合では、エピタキシャル物質の成長は、互いに対してもウェットエッチングの選択性を有する 2 つの物質を交互に配置することにより行われる。例えば、0.58  $\mu\text{m}$  の InP の層と、およそ 0.02  $\mu\text{m}$  の InGaAs または InGaAsP の薄層とを交互に配置する。階段構造に段差が所望される程度に、2 つの層が繰り返される。それらは、通常、n 型ドープされる。n 型下部クラッド層、非ドープの活性領域、p 型上部クラッド層、および高度に p 型の接触層が、これらの層の上面に続いて蒸着される。

40

## 【0039】

エッチファセットおよびリッジの製造後、レーザの前方に位置する階段構造の形成は、フォトレジストまたは誘電体を用いた一連のリソグラフィマスクの定義、それに続く層特異的な湿式化学エッチングにより行われる。これは例えば、InP エッチングには 1 : 4 の HCl - H<sub>3</sub>PO<sub>4</sub>、InGaAs または InGaAsP エッチングには 1 : 1 : 10 の H<sub>2</sub>SO<sub>4</sub> : H<sub>2</sub>O<sub>2</sub> : H<sub>2</sub>O を用いる。

50

## 【0040】

多くの用途では、単一縦モードレーザがマルチ縦モードレーザよりも望ましい。1つのそのような用途は、マルチ縦レーザと比較して単一縦モードレーザを用いることにより、データ伝達において伝達のより長い到達が得られることである。前述したように、階段、屋根部および反射性側壁の一以上を備えたD F B レーザは、レーザから出るビーム形状を変更できる。本願の譲受人に譲渡され、その開示がその全体において参照により本明細書に組み込まれる米国特許第7,835,415号は、レーザビーム制御のために本開示とともに使用できる代替的な単一縦レーザを教示している。

## 【0041】

例えは40°よりも大きい高いVFF値を有する半導体レーザを、望ましいように、より低い閾値電流を有するように設計できる。しかしながら、通常、これらのレーザは、光ファイバなどとの結合が弱い。本開示は、良好な結合効率をもたらしつつ、高いVFFによる低閾値電流の利点を可能にする。

## 【0042】

本開示を1310nm放出InPベースのレーザに関して記述したが、他の基板における他の波長のレーザに加えて、InPのレーザ構造における他の波長も、本開示から利益となり得ることが理解される。これらの波長は例えは、GaN基板のレーザ構造における紫色、青色および緑色、そしてGaN基板のレーザ構造における赤外線および赤色が挙げられる。

## 【0043】

本開示を好ましい実施形態について例証したが、以下の請求項に提示されるようなその真の本質および範囲から逸することなく、変化および変更を為せることが理解される。

10

20

【図1】

図1 (a)

図1 (b)

【図2】

図2 (a)

図2 (b)

【図3】

図3 (a)

図3 (b)

【図4】

図4 (a)

図4 (b)

【図5】

図5 (a)

図5 (b)

【図6】

図6 (a)

図6 (b)

【図7】

Figure 7

【図8】

図8 (a)

図8 (b)

図8 (c)

【図9】

図9 (a)

図9 (b)

図9 (c)

【図10】

Figure 10

【図 1 1】

Figure 11

【図 1 2】

図 1 2 (a)

図 1 2 (b)

【図 1 3】

図 1 3 (a)

図 1 3 (b)

【図 1 4】

図 1 4 (a)

図 1 4 (b)

【図 1 5】

Figure 15

【図 1 6】

図 1 6 (a)

図 1 6 (b)

【図 1 7】

図 1 7 (a)

図 1 7 (b)

図 1 7 (c)

---

フロントページの続き

(74)代理人 100098475

弁理士 倉澤 伊知郎

(74)代理人 100130937

弁理士 山本 泰史

(72)発明者 スタガレスク クリストゥイアン

アメリカ合衆国 ニューヨーク州 14850 イサカ ノース タイオガ ストリート 110

8 アパートメント 1

(72)発明者 ベーファー アレックス エイ

アメリカ合衆国 バージニア州 22947 ケスウィック シスル ダウン 1256

(72)発明者 クウォン ノーマン ジ - ケウン

アメリカ合衆国 カリフォルニア州 91108 サン マリノ マクファーレン ストリート

1853

審査官 小濱 健太

(56)参考文献 特開平09-214055(JP,A)

特開平05-136459(JP,A)

特開2006-047680(JP,A)

特開2000-114639(JP,A)

特開2004-327654(JP,A)

特開2000-277850(JP,A)

特表2009-506550(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50