(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6096072号

(P6096072)

(45) 発行日 平成29年3月15日(2017.3.15)

(24) 登録日 平成29年2月24日(2017.2.24)

(51) Int.Cl.

G 11 C 11/41 (2006.01)

G 11 C 11/405 (2006.01)

F 1

G 11 C 11/40

G 11 C 11/34Z

352 B

請求項の数 4 (全 31 頁)

(21) 出願番号 特願2013-138690 (P2013-138690)

(22) 出願日 平成25年7月2日 (2013.7.2)

(65) 公開番号 特開2014-149901 (P2014-149901A)

(43) 公開日 平成26年8月21日 (2014.8.21)

審査請求日 平成28年4月20日 (2016.4.20)

(31) 優先権主張番号 特願2012-152318 (P2012-152318)

(32) 優先日 平成24年7月6日 (2012.7.6)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2013-4143 (P2013-4143)

(32) 優先日 平成25年1月14日 (2013.1.14)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 王丸 拓郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小林 英智

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

演算部と、データ退避部と、を有し、

前記データ退避部は、第1のトランジスタと、第2のトランジスタと、第1のアナログスイッチと、第2のアナログスイッチと、インバータと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記演算部のノードと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第1のアナログスイッチは、前記ノードと、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記第2のアナログスイッチは、配線と、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記インバータは、前記第1のアナログスイッチと、前記第2のアナログスイッチとを反転動作させる機能を有し、

前記第1のトランジスタは、酸化物半導体に形成されたチャネル形成領域を有することを特徴とする半導体装置。

## 【請求項 2】

演算部と、データ退避部と、を有し、

前記データ退避部は、第1のトランジスタと、第2のトランジスタと、アナログスイッ

10

20

チと、第3のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記演算部のノードと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記アナログスイッチは、前記ノードと、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記第3のトランジスタは、配線と、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記第1のトランジスタは、酸化物半導体に形成されたチャネル形成領域を有することを特徴とする半導体装置。 10

### 【請求項3】

演算部と、データ退避部と、を有し、

前記データ退避部は、第1のトランジスタと、第2のトランジスタと、容量素子と、第1のアナログスイッチと、第2のアナログスイッチと、インバータと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記演算部のノードと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記容量素子の電極と電気的に接続され。 20

前記第1のアナログスイッチは、前記ノードと、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記第2のアナログスイッチは、配線と、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記インバータは、前記第1のアナログスイッチと、前記第2のアナログスイッチとを反転動作させる機能を有し、

前記第1のトランジスタは、酸化物半導体に形成されたチャネル形成領域を有することを特徴とする半導体装置。

### 【請求項4】

演算部と、データ退避部と、を有し、

前記データ退避部は、第1のトランジスタと、第2のトランジスタと、容量素子と、アナログスイッチと、第3のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記演算部のノードと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記容量素子の電極と電気的に接続され、

前記アナログスイッチは、前記ノードと、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、 40

前記第3のトランジスタは、配線と、前記第1のトランジスタのソース又はドレインの一方との電気的な接続を制御する機能を有し、

前記第1のトランジスタは、酸化物半導体に形成されたチャネル形成領域を有することを特徴とする半導体装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置に関する。特に、動作中に電力供給が適宜停止される半導体装置に関する。また、本発明は、当該半導体装置の駆動方法に関する。なお、本明細書中にお 50

いて、半導体装置とは、半導体特性を利用して機能することで機能する装置を指す。

【背景技術】

【0002】

中央演算処理装置（CPU：Central Processing Unit）などの半導体装置は、その用途によって多種多様な構成を有している。一般的には、データ又はプログラムを記憶するためのメインメモリに加えて、レジスタ、キャッシュメモリなど、各種の記憶装置が設けられていることが多い。レジスタは、演算処理又はプログラムの実行状態の保持などのために一時的にデータを保持する役割を担っている。また、キャッシュメモリは、演算回路とメインメモリの間に介在し、低速なメインメモリへのアクセスを減らして演算処理を高速化するために設けられている。

10

【0003】

レジスタ及びキャッシュメモリには、メインメモリと比較して、データの書き込み及び読み出しなどの動作が高速であることが求められる。よって、レジスタとしてはフリップフロップが、キャッシュメモリとしてはSRAM（Static Random Access Memory）が用いられることが多い。

【0004】

ところで、消費電力を抑えるため、適宜（例えば、データの入出力が行われない期間）半導体装置への電源電圧の供給を停止することが好ましい。ただし、フリップフロップ、及びSRAM等は、揮発性の記憶装置である。よって、半導体装置への電源電圧の供給を停止する場合には、電源電圧の供給再開後にレジスタ及びキャッシュメモリ等の揮発性の記憶装置において消失したデータを復元することが必要となる。例えば、外部に設けられている補助記憶装置から必要なデータを読み出し、読み出したデータを信号処理回路内の揮発性の記憶装置に改めて書き込むなどの動作が必要となる。これは、当該信号処理回路の動作遅延に直結する。

20

【0005】

これに対して、揮発性の記憶装置の周辺に不揮発性の記憶装置を配置する半導体装置が開発されている。例えば、特許文献1では、電源電圧の供給を停止する前にフリップフロップなどに保持されているデータを強誘電体メモリへと退避させ、電源電圧の供給を再開した後に強誘電体メモリに退避されているデータをフリップフロップなどに復元する技術が開示されている。

30

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10-078836号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一態様は、新規な半導体装置及びその駆動方法を提供することを目的のーとする。例えば、消費電力の低減及び動作遅延の抑制を図ることが可能な中央演算処理装置などの半導体装置を提供することを目的のーとする。

40

【課題を解決するための手段】

【0008】

本発明の一態様の半導体装置では、演算処理によって適宜書き換えられるデータを保持するノード（揮発性）と、当該データが退避されることになるノードとをチャネルが酸化物半導体層に形成されるトランジスタのソース及びドレインを介して電気的に接続させる。なお、当該トランジスタは、オフ電流値が極めて低い。そのため、後者のノードから当該トランジスタを介して電荷がリークすることがほとんどない。その結果、後者のノードでは、電源電圧の供給が停止される期間においてもデータを保持することが可能である。なお、本明細書において、電源電圧の供給を停止するとは、電源電圧（高電源電位及び低電源電位）を供給しない、又は電源電圧（高電源電位と低電源電位の電位差）をゼロ若し

50

くは実質的にゼロにすることを意味する。

**【0009】**

さらに、当該半導体装置では、後者のノードの電位を予め定められている電位とする手段が設けられている。具体的には、前者のノードから後者のノードへと退避されるデータである1又は0に対応する電位を後者のノードに供給する手段が設けられている。

**【0010】**

例えば、本発明の一態様は、電源電圧が供給されている期間において、1又は0に対応する電位をデータとして保持することが可能な第1のノードと、電源電圧が供給されているか否かに依存せずにデータを保持することが可能な第2のノードと、第1のノードと第2のノードを電気的に接続させるか否かを制御することが可能であり且つチャネルが酸化物半導体層に形成される第1のトランジスタと、第2のノードの電位に応じてスイッチングが制御される第2のトランジスタと、データに依存せずに1又は0に対応する電位を第2のノードに供給することが可能な手段と、を有する半導体装置である。10

**【0011】**

また、当該半導体装置の駆動方法であって、当該手段によって第2のノードに1又は0に対応する電位を供給する第1のステップと、第1のステップ後に第1のトランジスタをオンすることによって、データを第1のノードから第2のノードに退避させる第2のステップと、第2のステップ後に電源電圧の供給を停止する第3のステップと、第3のステップ後に電源電圧の供給を再開する第4のステップと、第4のステップ後に第2のトランジスタの導通状態に基づいて第2のステップ前に第1のノードに保持されていたデータが復元される第5のステップと、を有する半導体装置の駆動方法も本発明の一態様である。20

**【発明の効果】**

**【0012】**

本発明の一態様の半導体装置では、電源電圧の供給を適宜停止することによって消費電力の低減を図ることが可能である。また、電源電圧の供給を停止する前におけるデータの退避及び電源電圧の供給を再開した後におけるデータの復元によって動作遅延の抑制を図ることが可能である。

**【図面の簡単な説明】**

**【0013】**

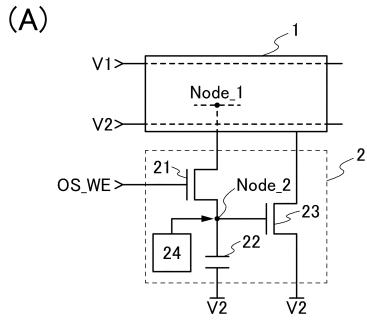

**【図1】**(A)半導体装置の構成例を示す図、(B)半導体装置の駆動方法の一例を示すフロー チャート。30

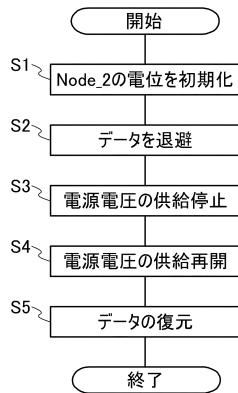

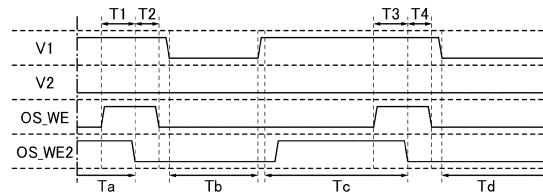

**【図2】**(A)半導体装置の構成例を示す図、(B)半導体装置に供給される電位及び信号の一例を示すタイミングチャート。

**【図3】**半導体装置の構成例を示す図。

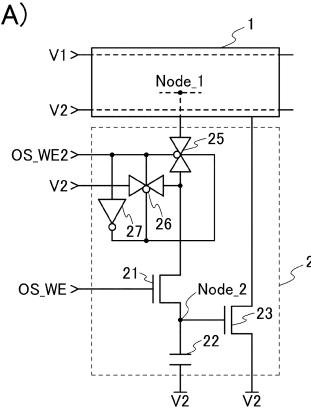

**【図4】**(A)半導体装置の構成例を示す図、(B)半導体装置に供給される電位及び信号の一例を示すタイミングチャート。

**【図5】**(A)演算部の構成例を示す図、(B)演算部に供給される電位及び信号の一例を示すタイミングチャート。

**【図6】**トランジスタの構造例を示す図。

**【図7】**半導体装置の構造例を示す図。

**【図8】**(A)～(F)電子機器の具体例を示す図。

**【図9】**半導体装置の構成例を示す図。

**【図10】**半導体装置の構成例を示す図。

**【図11】**データの書き込み時間の測定結果を示す図。

**【図12】**データの書き込み時間の測定結果を示す図。

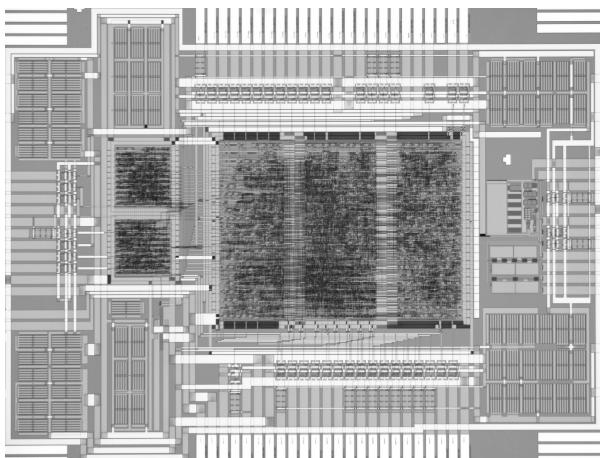

**【図13】**プロセッサのレイアウトを示す図。

**【発明を実施するための形態】**

**【0014】**

以下では、本発明の一態様について詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態を様々に変更し得50

る。したがって、本発明は以下に示す記載内容に限定して解釈されるものではない。

**【0015】**

<半導体装置の構成例及びその駆動方法例>

図1(A)は、本発明の一態様の半導体装置の構成例を示す図であり、図1(B)は、図1(A)に示す半導体装置におけるデータの退避及び復元の際の駆動方法の一例を示すフロー・チャートである。

**【0016】**

図1(A)に示す半導体装置は、演算処理を行う演算部1と、演算部1で保持されているデータが退避されるデータ退避部2とを有する。

**【0017】**

演算部1は、電源電位V1及び電源電位V2が供給され、両者の電位差を電源電圧として動作することが可能である。なお、ここでは、電源電位V1は、高電源電位VDDと低電源電位VSSのいずれかの電位をとり、電源電位V2は、低電源電位VSSをとることとする。また、演算部1には、電源電圧が供給されている期間において、1又は0に対応する電位をデータとして保持することが可能なノード(Node\_1)が設けられている。

**【0018】**

データ退避部2は、ゲートが信号OS\_WEを供給する配線に電気的に接続され、ソース及びドレインの一方が演算部1のノード(Node\_1)に電気的に接続され、ソース及びドレインの他方がノード(Node\_2)に電気的に接続されているトランジスタ21と、一方の電極がノード(Node\_2)に電気的に接続され、他方の電極が電源電位V2を供給する配線に電気的に接続されている容量素子22と、ゲートがノード(Node\_2)に電気的に接続され、ソース及びドレインの一方が電源電位V2を供給する配線に接続され、ソース及びドレインの他方が演算部1に電気的に接続されているトランジスタ23と、演算部1のノード(Node\_1)において保持されるデータである1又は0に対応する電位をノード(Node\_2)に供給することが可能な手段24とを有する。なお、図1(A)に示すデータ退避部2において、容量素子22を設けない構成とすることも可能である。

**【0019】**

ここでは、信号OS\_WEは、トランジスタ21のしきい値電圧と、高電源電位VDDとの和よりも高電位である電位、又は低電源電位VSSをとる信号である(前者の場合)こととする。なお、信号OS\_WEとして、高電源電位VDD又は低電源電位VSSをとる信号を適用する(後者の場合)ことも可能である。後者の場合には、前者の場合と比較して、半導体装置を駆動するのに必要な電源電位数を低減することが可能である。他方、前者の場合には、ノード(Node\_2)に高電源電位VDDを供給することが可能であり、後述するデータの退避を確実に行うことが可能である。

**【0020】**

なお、トランジスタ21は、チャネルが酸化物半導体層に形成されるトランジスタである。また、ノード(Node\_2)に対する電荷の供給経路は、チャネルが酸化物半導体層に形成されるトランジスタのソース及びドレインを介する経路のみである。ここで、当該トランジスタのオフ電流値は著しく低い。よって、当該トランジスタがオフする期間においては、ノード(Node\_2)の電位を概略一定に保持することが可能である。その結果、ノード(Node\_2)は、電源電圧が供給されるか否かに依存せずにデータを保持することが可能である。すなわち、ノード(Node\_2)には演算部1のノード(Node\_1)で保持されているデータを退避させることができる。

**【0021】**

また、トランジスタ23は、各種の半導体材料を用いて構成することが可能である。例えば、シリコン又はゲルマニウムなどの材料を用いることができる。また、化合物半導体又は酸化物半導体を用いることも可能である。なお、トランジスタ23としては、移動度が高いトランジスタ(例えば、チャネルが単結晶シリコンに形成されるトランジスタなど

10

20

30

40

50

)を適用することが好ましい。

**【0022】**

そして、演算部1では、電源電圧の供給を停止することによって消失した演算部1のノード(Node\_1)に保持されていたデータをトランジスタ23の導通状態に基づいて復元することが可能である。

**【0023】**

以下では、図1(A)に示す半導体装置の駆動方法の一例について図1(B)を参照して説明する。

**【0024】**

図1(A)に示す半導体装置においては、ノード(Node\_2)の電位を初期化することが可能である(S1)。具体的には、手段24によって、演算部1のノード(Node\_1)において保持されるデータである1又は0に対応する電位をノード(Node\_2)に供給することが可能である。10

**【0025】**

次いで、演算部1のノード(Node\_1)において保持されるデータをデータ退避部2のノード(Node\_2)に退避させることができ(S2)。具体的には、トランジスタ21をオンすることで、ノード(Node\_1)において保持されていたデータをノード(Node\_2)に書き込む。なお、ノード(Node\_2)には当該1又は0に対応する電位が供給されているため、当該退避によってノード(Node\_2)の電位が変化しないこともある。20

**【0026】**

次いで、半導体装置に対する電源電圧の供給を停止することが可能である(S3)。具体的には、電源電位V1を低電源電位VSSとする。

**【0027】**

次いで、半導体装置に対する電源電圧の供給を再開することが可能である(S4)。具体的には、電源電位V1を高電源電位VDDとする。

**【0028】**

次いで、演算部1のノード(Node\_1)のデータを復元することが可能である(S5)。具体的には、トランジスタ23の導通状態に基づいてノード(Node\_1)のデータを復元する。30

**【0029】**

上述したように図1(A)に示す半導体装置においては、電源電圧の供給を停止することによって、消費電力の低減を図ることが可能である。また、電源電圧の供給を再開した後にノード(Node\_1)に保持されていたデータを復元することによって、動作遅延を抑制することが可能である。

**【0030】**

さらに、図1(A)に示す半導体装置では、データの退避が行われる前にノード(Node\_2)の電位が初期化されている。この場合、当該初期化を行わない場合と比較して、データの退避に要する期間を短縮することが可能である。以下、この点について詳細に述べる。40

**【0031】**

図1(A)に示す半導体装置におけるデータの退避とは、ノード(Node\_2)の電位をノード(Node\_1)に保持されているデータに対応する電位とすることである。すなわち、ノード(Node\_2)の電位は、データの退避によって、1に対応する電位から0に対応する電位へ書き換えられる又は0に対応する電位から1に対応する電位へ書き換えられる可能性がある。

**【0032】**

ここで、図1(A)に示す半導体装置においては、0に対応する電位から1に対応する電位への書き換えに要する期間と、1に対応する電位から0に対応する電位への書き換えに要する期間とが同一であるとは限らない。具体的に述べると、図1(A)に示す半導体

装置においては、トランジスタ23の導通状態に基づいてノード(Node\_2)に保持されているデータを判別する。すなわち、ノード(Node\_2)の電位のみならずトランジスタ23のしきい値電圧にも依存して、ノード(Node\_2)に保持されているデータが判別されることになる。よって、双方の期間がトランジスタ23のしきい値電圧に依存して変化することになる。例えば、トランジスタ23のしきい値電圧が1に対応する電位よりも0に対応する電位に近い値である場合には、1に対応する電位から0に対応する電位への書き換えに要する期間が、0に対応する電位から1に対応する電位への書き換えに要する期間よりも長くなる。そして、データの退避の際に双方の書き換えが生じる可能性がある場合には、より長い方の期間(1に対応する電位から0に対応する電位への書き換えに要する期間)をデータの退避に要する期間として設定せざるを得ない。確実にデータを退避させるためである。

#### 【0033】

これに対して、図1(A)に示す半導体装置においては、ノード(Node\_2)の電位が予め1又は0に対応する電位となっている。すなわち、双方の期間を比較して、データの退避に必要な期間が長い方のデータを予めノード(Node\_2)に供給することが可能である。これにより、図1(A)に示す半導体装置においては、データの退避に必要な期間が短い方の期間をデータの退避に要する期間として設定することが可能である。すなわち、データの退避に要する期間を短縮することが可能である。その結果、図1(A)に示す半導体装置においては、動作遅延を抑制することが可能である。

#### 【0034】

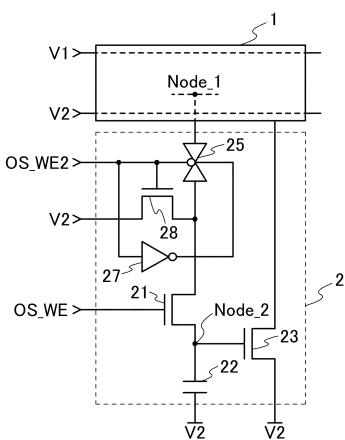

##### <手段24の具体例1>

図2(A)は、手段24を具体化した半導体装置の構成例を示す図であり、図2(B)は、図2(A)に示す半導体装置に供給される電源電位V1、V2及び信号OS\_WE、OS\_WE2のタイミングチャートの一例を示す図である。

#### 【0035】

図2(A)に示す半導体装置は、手段24として、演算部1のノード(Node\_1)とトランジスタ21のソース及びドレインの一方を電気的に接続させるか否かを制御するアナログスイッチ25と、電源電位V2を供給する配線とトランジスタ21のソース及びドレインの一方を電気的に接続させるか否かを制御するアナログスイッチ26とを有する。なお、アナログスイッチ25、26は、信号OS\_WE2及び信号OS\_WE2の反転信号(インバータ27の出力信号)によって、反転動作することになる。すなわち、図2(A)に示す半導体装置においては、アナログスイッチ25、26及びインバータ27によって切り替えスイッチが構成されている。また、ここでは、信号OS\_WE2は、高電源電位VDD又は低電源電位VSSをとる信号であることとする。

#### 【0036】

図2(A)に示す半導体装置においては、データの退避が行われる期間(図2(B)に示す期間T2、T4)の前の期間(図2(B)に示す期間T1、T3)にノード(Node\_2)の電位の初期化が行われている。具体的には、アナログスイッチ26及びトランジスタ21のソース及びドレインを介して、ノード(Node\_2)に電源電位V2(低電源電位VSS)が供給されている。なお、図2(A)に示す半導体装置においては、図2(B)に示す期間Ta、Tcが演算部1において演算処理が可能な期間であり、期間Tb、Tdが電源電圧の供給が停止される期間である。

#### 【0037】

ここで、ノード(Node\_2)の電位の初期化が行われる期間(図2(B)に示す期間T1、T3)をデータの退避が行われる期間(図2(B)に示す期間T2、T4)よりも長くすることが好ましい。これにより、1に対応する電位から0に対応する電位への書き換えに要する期間と、0に対応する電位から1に対応する電位への書き換えに要する期間とを比較して、データの退避に必要な期間が長い方のデータを予め(期間T1、T3において)ノード(Node\_2)に供給することが可能となるからである。

#### 【0038】

10

20

30

40

50

なお、図3に示すように、図2(A)に示す半導体装置が有するアナログスイッチ26をトランジスタ28に置換することも可能である。なお、トランジスタ28のスイッチングは、信号OS\_WE2によって制御される。

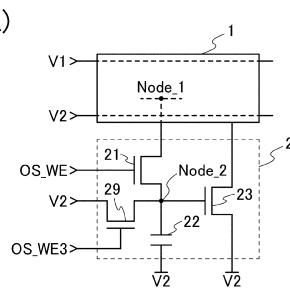

#### 【0039】

<手段24の具体例2>

図4(A)は、図2(A)に示す半導体装置とは異なる手段24を具体化した半導体装置の構成例を示す図であり、図4(B)は、図4(A)に示す半導体装置に供給される電源電位V1、V2及び信号OS\_WE、OS\_WE3のタイミングチャートの一例を示す図である。

#### 【0040】

図4(A)に示す半導体装置は、手段24として、電源電位V2を供給する配線とノード(Node\_2)を電気的に接続させるか否かを制御するトランジスタ29を有する。なお、トランジスタ29のスイッチングは、信号OS\_WE3によって制御される。また、トランジスタ29は、チャネルが酸化物半導体層に形成されるトランジスタである。また、ここでは、信号OS\_WE3は、高電源電位VDD又は低電源電位VSSをとる信号であることとする。

#### 【0041】

図4(A)に示す半導体装置においては、データの退避が行われる期間(図4(B)に示す期間t2、t4)の前の期間(図4(B)に示す期間t1、t3)にノード(Node\_2)の電位の初期化が行われている。具体的には、トランジスタ29がオンすることによって、ノード(Node\_2)に電源電位V2(低電源電位VSS)が供給されている。なお、図4(A)に示す半導体装置においては、図4(B)に示す期間ta、tcが演算部1において演算処理が可能な期間であり、期間tb、tdが電源電圧の供給が停止される期間である。

#### 【0042】

ここで、ノード(Node\_2)の電位の初期化が行われる期間(図4(B)に示す期間t1、t3)をデータの退避が行われる期間(図4(B)に示す期間t2、t4)よりも長くすることが好ましい。

#### 【0043】

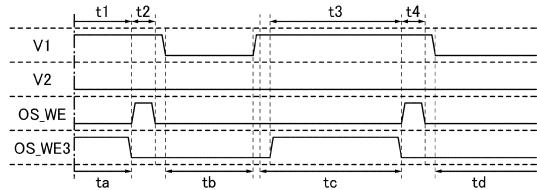

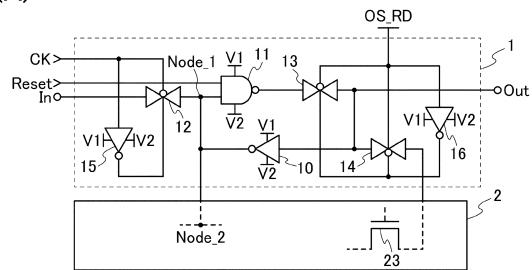

<演算部1におけるデータの復元の一例>

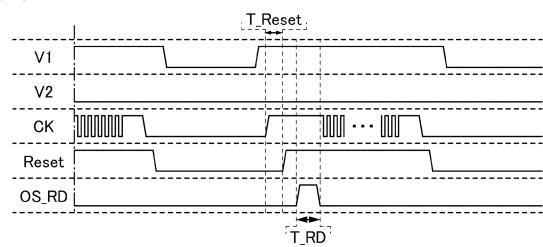

図5(A)は、図1～図4に示す半導体装置が有する演算部1の構成例を示す図であり、図5(B)は、図5(A)に示す半導体装置に供給される電源電位V1、V2、信号CK、信号Reset、及び信号OS\_RDのタイミングチャートの一例を示す図である。なお、ここでは、信号CK、信号Reset、及び信号OS\_RDは、高電源電位VDD又は低電源電位VSSとなる信号であることとする。

#### 【0044】

図5(A)に示す演算部1は、ノード(Node\_1)に信号を出力するインバータ10と、一方の入力として信号Resetが入力され、他方の入力としてノード(Node\_1)の電位が入力されるNANDゲート11と、演算部1の入力端子(In)とノード(Node\_1)を電気的に接続させるか否かを制御するアナログスイッチ12と、NANDゲート11の出力端子と、演算部1の出力端子(Out)及びインバータ10の入力端子とを電気的に接続させるか否かを制御するアナログスイッチ13と、演算部1の出力端子(Out)及びインバータ10の入力端子と、データ退避部2に含まれるトランジスタ23のソース又はドレインとを電気的に接続させるか否かを制御するアナログスイッチ14とを有する。

#### 【0045】

なお、アナログスイッチ12は、信号CK及び信号CKの反転信号(インバータ15の出力信号)によって、動作することになる。また、アナログスイッチ13、14は、信号OS\_RD及び信号OS\_RDの反転信号(インバータ16の出力信号)によって、反転動作することになる。すなわち、図5(A)に示す半導体装置においては、アナログスイ

10

20

30

40

50

ツチ 13、14 及びインバータ 16 によって切り替えスイッチが構成されている。

#### 【0046】

図 5 (A) に示す演算部 1においては、電源電圧の供給を再開した後であって、信号 C\_K を高電源電位 V\_DDD とし且つ信号 R es e t が低電源電位 V\_SS である期間 (図 5 (B)) に示す期間 T\_R es e t ) に、N AND ゲート 11 の出力が高電源電位 V\_DDD となる。なお、期間 T\_R es e t においては、信号 O S \_ R D が低電源電位 V\_SS となっているため、演算部 1 の出力端子 (O u t) から出力される信号は高電源電位 V\_DDD となり、ノード (Node\_1) の電位は低電源電位 V\_SS となる。そして、信号 R es e t を高電源電位 V\_DDD とした後に信号 O S \_ R D を高電源電位 V\_DDD とする期間 (図 5 (B)) に示す期間 T\_R D ) に、ノード (Node\_1) のデータを復元することが可能である。

10 具体的には、トランジスタ 23 がオンしている場合には、ノード (Node\_1) の電位を高電源電位 V\_DDD へと上昇させ、オフしている場合には、ノード (Node\_1) の電位を低電源電位 V\_SS のまま維持することで、ノード (Node\_1) のデータを復元することができる。

#### 【0047】

< チャネルが酸化物半導体層に形成されるトランジスタの一例 >

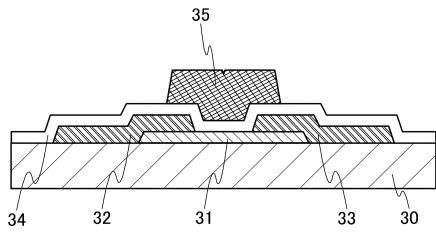

図 6 は、チャネルが酸化物半導体層に形成されるトランジスタの構造例を示す図である。

20 図 6 に示すトランジスタは、絶縁表面を有する層 30 上に設けられている酸化物半導体層 31 と、酸化物半導体層 31 の一端と接する導電層 32 と、酸化物半導体層 31 の他端と接する導電層 33 と、酸化物半導体層 31 及び導電層 32、33 上に設けられている絶縁層 34 と、絶縁層 34 上に設けられている導電層 35 とを有する。なお、図 6 に示すトランジスタにおいては、導電層 32、33 がソース及びドレインとして機能し、絶縁層 34 がゲート絶縁膜として機能し、導電層 35 がゲートとして機能する。

#### 【0048】

< 1. 酸化物半導体層 31 の具体例 >

< (1) 酸化物半導体材料について >

酸化物半導体層 31 として、少なくともインジウムを含む膜を適用することができる。

30 特に、インジウムと亜鉛を含む膜を適用することが好ましい。また、トランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウムを有する膜を適用することが好ましい。

#### 【0049】

また、酸化物半導体層 31 として、スズ、ハフニウム、アルミニウム、若しくはジルコニウム、又はランタノイドである、ラントン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、若しくはルテチウムのいずれか一種又は複数種をスタビライザーとして含む膜を適用することもできる。

#### 【0050】

例えば、酸化物半導体層 31 として、酸化インジウム膜、二元系金属の酸化物である In-Zn 系酸化物膜、In-Mg 系酸化物膜、In-Ga 系酸化物膜、三元系金属の酸化物である In-Ga-Zn 系酸化物膜、In-Al-Zn 系酸化物膜、In-Sn-Zn 系酸化物膜、In-Hf-Zn 系酸化物膜、In-La-Zn 系酸化物膜、In-Ce-Zn 系酸化物膜、In-Pr-Zn 系酸化物膜、In-Nd-Zn 系酸化物膜、In-Sm-Zn 系酸化物膜、In-Eu-Zn 系酸化物膜、In-Gd-Zn 系酸化物膜、In-Tb-Zn 系酸化物膜、In-Dy-Zn 系酸化物膜、In-Ho-Zn 系酸化物膜、In-Er-Zn 系酸化物膜、In-Tm-Zn 系酸化物膜、In-Yb-Zn 系酸化物膜、In-Lu-Zn 系酸化物膜、四元系金属の酸化物である In-Sn-Ga-Zn 系酸化物膜、In-Hf-Ga-Zn 系酸化物膜、In-Al-Ga-Zn 系酸化物膜、In-Sn-Al-Zn 系酸化物膜、In-Sn-Hf-Zn 系酸化物膜、In-Hf-Al-Zn 系酸化物膜を適用することができる。

40

#### 【0051】

50

ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0052】

なお、酸化物半導体層31を構成する酸素の一部は窒素で置換されてもよい。

#### 【0053】

<(2)酸化物半導体の結晶構造について>

酸化物半導体層31として、単結晶、多結晶(ポリクリスタルともいう)又は非晶質などの結晶構造を有する膜を適用することができます。また、酸化物半導体層31として、C AAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜を適用することができます。以下、AAC-OS膜について詳述する。

10

#### 【0054】

C AAC-OS膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

#### 【0055】

C AAC-OS膜を透過型電子顕微鏡(TEM:Transmission Electron Microscope)によって観察すると、明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、AAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

20

#### 【0056】

C AAC-OS膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、AAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、AAC-OS膜の被形成面または上面と平行に配列する。

#### 【0057】

一方、AAC-OS膜を、試料面と概略垂直な方向からTEMによって観察(平面TEM観察)すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

30

#### 【0058】

断面TEM観察および平面TEM観察より、AAC-OS膜の結晶部は配向性を有していることがわかる。

#### 【0059】

なお、AAC-OS膜に含まれるほとんどの結晶部は、一辺が100nm未満の立方体内に収まる大きさである。従って、AAC-OS膜に含まれる結晶部は、一辺が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの場合も含まれる。ただし、AAC-OS膜に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面TEM像において、 $2500\text{ nm}^2$ 以上、 $5\mu\text{m}^2$ 以上または $1000\mu\text{m}^2$ 以上となる結晶領域が観察される場合がある。

40

#### 【0060】

C AAC-OS膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えば $\text{InGaZnO}_4$ の結晶を有するAAC-OS膜のout-of-plane法による解析では、回折角( $2\theta$ )が $31^\circ$ 近傍にピークが現れる場合がある。このピークは、 $\text{InGaZnO}_4$ の結晶の(009)面に帰属されることから、AAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

#### 【0061】

一方、AAC-OS膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、 $2\theta$ が $56^\circ$ 近傍にピークが現れる場合がある。このピーク

50

は、 $InGaZnO_4$  の結晶の(110)面に帰属される。 $InGaZnO_4$  の単結晶酸化物半導体膜であれば、2 を 56° 近傍に固定し、試料面の法線ベクトルを軸(c 軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、 $CAC-O_S$  膜の場合は、2 を 56° 近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

#### 【0062】

以上のことから、 $CAC-O_S$  膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

10

#### 【0063】

なお、結晶部は、 $CAC-O_S$  膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、 $CAC-O_S$  膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、 $CAC-O_S$  膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が $CAC-O_S$  膜の被形成面または上面の法線ベクトルと平行にならないこともある。

#### 【0064】

また、 $CAC-O_S$  膜中において、c 軸配向した結晶部の分布が均一でなくてもよい。例えば、 $CAC-O_S$  膜の結晶部が、 $CAC-O_S$  膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも c 軸配向した結晶部の割合が高くなることがある。また、 $CAC-O_S$  膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的に c 軸配向した結晶部の割合の異なる領域が形成されることもある。

20

#### 【0065】

なお、 $InGaZnO_4$  の結晶を有する $CAC-O_S$  膜の out-of-plane 法による解析では、2 が 31° 近傍のピークの他に、2 が 36° 近傍にもピークが現れる場合がある。2 が 36° 近傍のピークは、 $CAC-O_S$  膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。 $CAC-O_S$  膜は、2 が 31° 近傍にピークを示し、2 が 36° 近傍にピークを示さないことが好ましい。

#### 【0066】

30

$CAC-O_S$  膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【0067】

40

また、 $CAC-O_S$  膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0068】

不純物濃度が低く、欠陥準位密度が低い(酸素欠損の少ない)ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる

50

。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

#### 【0069】

また、CAC-O<sub>x</sub>膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0070】

なお、酸化物半導体層31として、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAC-O<sub>x</sub>膜のうち、二種以上を有する積層膜であってもよい。

10

#### 【0071】

<(3)酸化物半導体の層構造について>

酸化物半導体層31として、単一層からなる酸化物半導体膜のみならず複数種の酸化物半導体膜の積層を適用することができる。例えば、非晶質酸化物半導体膜、多結晶酸化物半導体膜、及びCAC-O<sub>x</sub>膜の少なくとも2種を含む層を酸化物半導体層31として適用することができる。

20

#### 【0072】

また、組成の異なる酸化物半導体膜の積層からなる層を酸化物半導体層31として適用することもできる。具体的には、絶縁層34側に設けられる第1の酸化物半導体膜(以下、上層ともいう)と、絶縁表面を有する層30側に設けられ、且つ第1の酸化物半導体膜と組成が異なる第2の酸化物半導体膜(以下、下層ともいう)とを含む層を酸化物半導体層31として適用することもできる。

20

#### 【0073】

<2.導電層32、33の具体例>

導電層32、33として、アルミニウム、銅、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、これらの元素を成分とする合金、又はこれらの元素を含む窒化物からなる膜を適用することができる。また、これらの膜の積層を適用することもできる。

#### 【0074】

<3.絶縁層34の具体例>

30

絶縁層34として、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁材料膜を適用することができる。また、これらの材料の積層を適用することもできる。なお、絶縁層34として酸化アルミニウム膜を適用することが好ましい。酸化アルミニウム膜は、水素などの不純物、及び酸素の両方に対して膜を透過させない遮断(プロッキング)効果が高い。よって、絶縁層34として酸化アルミニウム膜を含む層を適用することで、酸化物半導体層31からの酸素の脱離を防止するとともに、酸化物半導体層31への水素などの不純物の混入を防止することができる。

#### 【0075】

また、絶縁層34として、酸化ハフニウム膜、酸化イットリウム膜、ハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0,y>0))膜、窒素が添加されたハフニウムシリケート膜、ハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>(x>0,y>0))膜、又は酸化ランタン膜など(いわゆるhig h-k材料からなる膜)を含む膜を適用することもできる。このような膜を用いることでゲートリーク電流の低減が可能である。

40

#### 【0076】

<4.導電層35の具体例>

導電層35として、アルミニウム、銅、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素又はこれらの元素を成分とする合金からなる膜を適用することができる。また、導電層35として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Ga-Zn-O膜、窒素を含むIn-Sn-O膜、窒素を

50

含むIn-Ga-O膜、窒素を含むIn-Zn-O膜、窒素を含むSn-O膜、窒素を含むIn-O膜、又は金属窒化膜(InN、SiNなど)を適用することもできる。これらの窒化膜は5eV(電子ボルト)以上、好ましくは5.5eV(電子ボルト)以上の仕事関数を有し、ゲートとして用いた場合、トランジスタのしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。また、これらの膜の積層を適用することもできる。

#### 【0077】

##### <5.付記>

図6に示すトランジスタにおいては、酸化物半導体層31への不純物の混入又は酸化物半導体層31を構成する元素の脱離を抑制することが好ましい。このような現象が生じると、トランジスタの電気的特性が変動するからである。当該現象を抑制する手段としては、トランジスタの上下(絶縁表面を有する層30及びトランジスタの間と、絶縁層34及び導電層35上)にブロッキング効果が高い絶縁層を設ける手段が挙げられる。例えば、当該絶縁層として、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁材料膜を適用することができる。また、これらの材料の積層を適用することもできる。

#### 【実施例1】

#### 【0078】

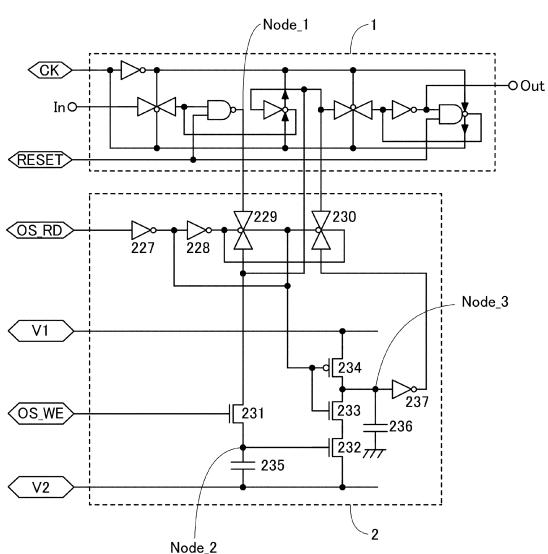

図9は、本発明の一態様の半導体装置の構成例を示す図である。

#### 【0079】

図9に示す半導体装置は、演算処理を行う演算部1と、演算部1で保持されているデータが退避されるデータ退避部2とを有する。データ退避部2は、インバータ227、インバータ228、アナログスイッチ229、アナログスイッチ230、トランジスタ231乃至トランジスタ234、容量素子235、容量素子236、及びインバータ237を有する。

#### 【0080】

インバータ227及びインバータ228により、信号OS\_RDと、信号OS\_RDの反転信号とが、アナログスイッチ229及びアナログスイッチ230に供給される。アナログスイッチ229及びアナログスイッチ230は、信号OS\_RDと、信号OS\_RDの反転信号とに従って、スイッチングが制御される。トランジスタ231は、そのゲートに入力される信号OS\_WEに従って、スイッチングが制御される。アナログスイッチ229及びトランジスタ231がオンであるとき、ノード(Node\_1)のデータである1又は0に対応する電位が、アナログスイッチ229及びトランジスタ231を介して容量素子235及びトランジスタ232のゲートに供給される。トランジスタ232のゲートをノード(Node\_2)とすると、トランジスタ232は、ノード(Node\_2)に与えられた1又は0に対応する電位により、スイッチングが制御される。

#### 【0081】

トランジスタ231がオフであるとき、1又は0に対応する電位が、ノード(Node\_2)において保持される。トランジスタ231のオフ電流は、著しく小さいことが望ましい。トランジスタ231のオフ電流が小さいことで、ノード(Node\_2)から、トランジスタ231を介して電荷がリークするのを防ぐことができる。

#### 【0082】

トランジスタ232は、ソース及びドレインの一方が、電源電位V2の与えられているノードに接続されている。トランジスタ233は、トランジスタ232のソース及びドレインの他方と、インバータ237の入力端子との、接続を制御する機能を有する。トランジスタ234は、電源電位V1の与えられているノードと、インバータ237の入力端子との、接続を制御する機能を有する。

#### 【0083】

また、容量素子236は、トランジスタ233のソース及びドレインの一方と、トラン

10

20

30

40

50

ジスタ 234 のソース及びドレインの一方とを接続するノード (Node\_3) の電位を保持する機能を有する。

**【0084】**

データ退避部 2 では、トランジスタ 233 をオフ、トランジスタ 234 をオンとし、ノード (Node\_3) に電源電位 V1 を供給することで、ノード (Node\_3) の電位をリセットすることができる。

**【0085】**

また、データ退避部 2 では、トランジスタ 233 をオン、トランジスタ 234 をオフとすることで、ノード (Node\_2) に保持されているデータをノード (Node\_3) の電位に反映させることができる。具体的には、トランジスタ 232 がオンであるとき、電源電位 V2 がトランジスタ 232 を介してノード (Node\_3) に与えられ、トランジスタ 232 がオフであるとき、ノード (Node\_3) において電源電位 V1 が保持される。よって、ノード (Node\_3) の電位は、ノード (Node\_2) に保持されているデータ（演算部 1 から入力されたデータ）が反映されることになる。10

**【0086】**

インバータ 237 の出力信号は、アナログスイッチ 230 を介して、演算部 1 に供給される。

**【0087】**

上記構成により、本発明の一態様では、半導体装置においてデータ退避部 2 の動作を制御することで、演算部 1 からデータ退避部 2 へのデータの退避と、データ退避部 2 から演算部 1 へのデータの復帰とを、行うことができる。20

**【実施例 2】**

**【0088】**

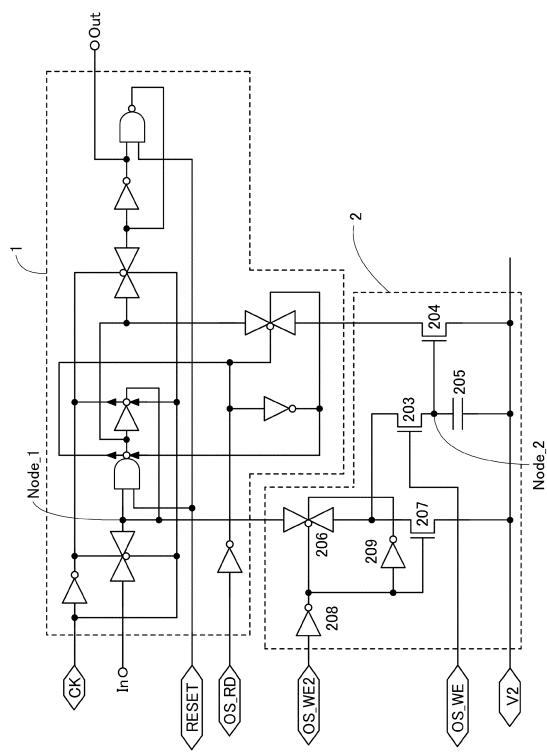

図 10 は、本発明の一態様の半導体装置の構成例を示す図である。

**【0089】**

図 10 に示す半導体装置は、演算処理を行う演算部 1 と、演算部 1 で保持されているデータが退避されるデータ退避部 2 とを有する。データ退避部 2 は、トランジスタ 203、トランジスタ 204、容量素子 205、アナログスイッチ 206、トランジスタ 207、インバータ 208、及びインバータ 209 を有する。

**【0090】**

トランジスタ 203 は、信号 OS\_WE に従って、スイッチングが制御される。また、アナログスイッチ 206 は、信号 OS\_WE2 に従って、スイッチングが制御される。具体的に、図 10 では、アナログスイッチ 206 は、インバータ 208 の出力信号（信号 OS\_WE2 の反転信号）と、インバータ 209 の出力信号（インバータ 208 の出力信号の反転信号）とにより、スイッチングが制御される。トランジスタ 207 は、インバータ 208 の出力信号（信号 OS\_WE2 の反転信号）に従って、スイッチングが制御される。30

**【0091】**

アナログスイッチ 206 及びトランジスタ 203 がオンであるとき、ノード (Node\_1) のデータである 1 又は 0 に対応する電位が、ノード (Node\_2) に供給される。また、トランジスタ 203 及びトランジスタ 207 がオンであるとき、電源電位 V2 が、ノード (Node\_2) に供給される。40

**【0092】**

トランジスタ 204 は、ノード (Node\_2) の電位に従って、スイッチングが制御される。トランジスタ 204 がオンのとき、電源電位 V2 がトランジスタ 204 を介して演算部 1 に与えられる。容量素子 205 は、トランジスタ 203 がオフにあるとき、ノード (Node\_2) の電位を保持する機能を有する。

**【0093】**

トランジスタ 203 のオフ電流は、著しく小さいことが望ましい。トランジスタ 203 のオフ電流が小さいことで、ノード (Node\_2) からリークする電荷の量を小さく抑50

えることができるので、データ退避部2においてデータが保持される期間を長く確保することができる。

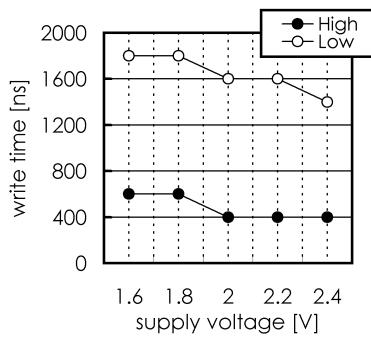

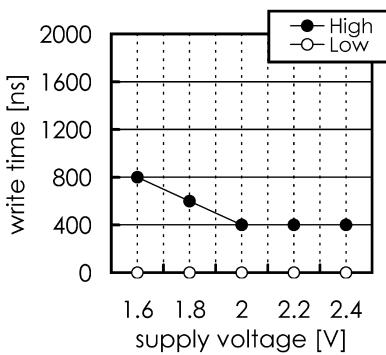

【実施例3】

【0094】

図9に示した半導体装置における、データ退避部2へのデータの書き込み時間を測定し、図11にその結果を示す。また、図10に示した半導体装置における、データ退避部2へのデータの書き込み時間を測定し、図12にその結果を示す。図11では、図9に示すアナログスイッチ229及びトランジスタ231をオンにしている時間Tを、200ns(ナノ秒)乃至2000nsの範囲内で、200nsごとに定め、書き込まれたデータと読み出されたデータとが一致する時間Tのうち、最も短い時間Tをデータの書き込み時間とした。図12でも、図11の場合と同様に、図10に示すアナログスイッチ206及びトランジスタ203をオンにしている時間Tを、200ns(ナノ秒)乃至2000nsの範囲内で、200nsごとに定め、書き込まれたデータと読み出されたデータとが一致する時間Tのうち、最も短い時間Tをデータの書き込み時間とした。10

【0095】

また、書き込み時間の測定は、ノード(Node\_2)にハイレベルの電位(High)を書き込む場合と、ノード(Node\_2)にローレベルの電位(Low)の電位を書き込む場合とで行った。そして、上記測定では、電源電位V1と電源電位V2の電位差である電源電圧を、1.6V、1.8V、2.0V、2.2V、2.4Vとした。

【0096】

図11に示すように、図9に示した半導体装置では、電源電圧が2.0Vのときに、データの書き込み時間が1600nsであった。また、図12に示すように、図10に示した半導体装置では、電源電圧が2.0Vのときに、データの書き込み時間が400nsであった。そして、電源電圧が2.0Vのとき、図10に示した半導体装置では、図9に示した半導体装置に対し、データの書き込み時間が4分の1であることが分かった。20

【0097】

そして、図10に示す半導体装置では、室温において、データの書き換え回数が10<sup>11</sup>回でも、上記書き込み時間に変化は見られなかった。

【実施例4】

【0098】

図13に、図10に示す半導体装置が255段接続された記憶装置を有する、プロセッサのレイアウトを示す。上記プロセッサは、本発明の一態様に係る半導体装置の一形態に相当する。30

【0099】

図13に示すプロセッサは、電源電圧の遮断時間が数十μ秒以上のアプリケーションを実行する際に、オーバーヘッドと電源電圧の遮断により削減される電力とが等しくなる電源電圧の遮断時間、すなわち損益分岐時間(BET: Break Even Time)が、電源電圧が2.0V、CPUの駆動周波数を25MHzとしたとき、25.3μ秒であった。よって、上記プロセッサは、電源電圧の遮断時間が数十μ秒以上のアプリケーションを実行する際に、電力削減の効果が見込めることが分かった。40

【実施例5】

【0100】

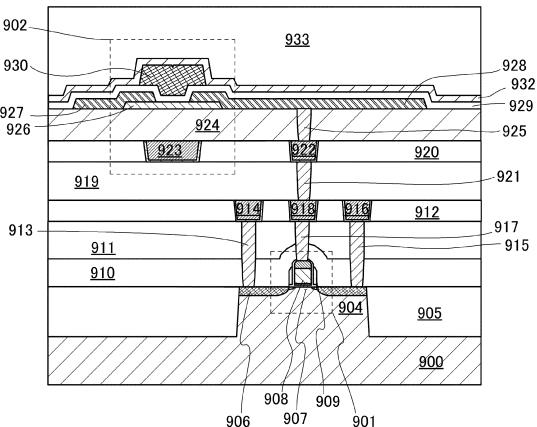

本実施例では、チャネルが酸化物半導体層に形成されるトランジスタ902と、チャネルが単結晶シリコンウェハに形成されるトランジスタ901とを含んで構成される半導体装置の構造例及びその作製方法例について図7を参照して説明する。なお、トランジスタ902は、図1～図4に示すトランジスタ21などとして適用することが可能であり、トランジスタ901は、図1～図4に示すトランジスタ23などとして適用することが可能である。

【0101】

ただし、トランジスタ901は、シリコンの他、ゲルマニウム、シリコンゲルマニウム50

、単結晶炭化シリコンなどの半導体材料を用いていても良い。また、例えば、シリコンを用いたトランジスタは、S O I 法により作製されたシリコン薄膜、気相成長法により作製されたシリコン薄膜などを用いて形成することができる。この場合、基板にはフュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730以上の中を用いると良い。

#### 【0102】

図7に示す半導体装置においては、単結晶シリコンウェハを用いて形成されたトランジスタ901と、その上階層に酸化物半導体を用いて形成されたトランジスタ902とが形成されている。すなわち、本実施例で示す半導体装置は、シリコンウェハを基板として、その上層にトランジスタ層が設けられた三次元の積層構造を有する半導体装置であり、また、シリコンをチャネル形成領域に用いたトランジスタと酸化物半導体をチャネル形成領域に用いたトランジスタとを有するハイブリッド型の半導体装置である。10

#### 【0103】

半導体材料を含む基板900を用いて作製されたトランジスタ901は、nチャネル型トランジスタ(NMOSFET)、pチャネル型トランジスタ(PMOSFET)のいずれも用いることができる。図7に示す例においては、トランジスタ901は、STI(Shallow Trench Isolation)905によって他の素子と絶縁分離されている。STI905を用いることにより、LOCOSによる素子分離法で発生した素子分離部のバースピークを抑制することができ、素子分離部の縮小等が可能となる。一方で、構造の微細化小型化が要求されない半導体装置においてはSTI905の形成は必ずしも必要ではなく、LOCOS等の素子分離手段を用いることもできる。トランジスタ901が形成される基板900には、ボロンやリン、ヒ素等の導電性を付与する不純物が添加されたウェル904が形成されている。20

#### 【0104】

図7におけるトランジスタ901は、基板900中に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域906(ソース領域及びドレイン領域ともいう)と、チャネル形成領域上に設けられたゲート絶縁膜907と、ゲート絶縁膜907上にチャネル形成領域と重畠するように設けられたゲート電極層908とを有する。ゲート電極層908は、加工精度を高めるための第1の材料からなるゲート電極層と、配線として低抵抗化を目的とした第2の材料からなるゲート電極層を積層した構造とすることができます。例えば、導電性を付与するリン等の不純物を添加した結晶性シリコンとニッケルシリサイドとの積層構造などが挙げられる。しかし、この構造に限らず、適宜要求される仕様に応じて材料、積層数、形状等を調整することができる。30

#### 【0105】

なお、図7に示すトランジスタ901を、フィン型構造のトランジスタとしてもよい。フィン型構造とは、半導体基板の一部を板状の突起形状に加工し、突起形状の長尺方向を交差するようにゲート電極層を設けた構造である。ゲート電極層は、ゲート絶縁膜を介して突起構造の上面及び側面を覆う。第2のトランジスタをフィン型構造のトランジスタとすることで、チャネル幅を縮小してトランジスタの集積化を図ることができる。また、電流を多く流すことができ、加えて制御効率を向上させることができるために、トランジスタのオフ時の電流及び閾値電圧を低減することができる。40

#### 【0106】

また、基板900中に設けられた不純物領域906には、コンタクトプラグ913、915が接続されている。ここでコンタクトプラグ913、915は、接続するトランジスタ901のソース電極やドレイン電極としても機能する。また、不純物領域906とチャネル形成領域の間には、不純物領域906と異なる不純物領域が設けられている。該不純物領域は、導入された不純物の濃度によって、LDD領域やエクステンション領域としてチャネル形成領域近傍の電界分布を制御する機能を果たす。ゲート電極層908の側壁には絶縁膜を介してサイドウォール絶縁膜909を有する。この絶縁膜やサイドウォール絶50

縁膜 909 を用いることで、LDD 領域やエクステンション領域を形成することができる。

#### 【0107】

また、トランジスタ 901 は、絶縁膜 910 により被覆されている。絶縁膜 910 には保護膜としての機能を持たせることができ、外部からチャネル形成領域への不純物の侵入を防止することができる。また、絶縁膜 910 を CVD 法による窒化シリコン等の材料とすることで、チャネル形成領域に単結晶シリコンを用いた場合には加熱処理によって水素化を行うことができる。また、絶縁膜 910 に引張応力又は圧縮応力を有する絶縁膜を用いることで、チャネル形成領域を構成する半導体材料に歪みを与えることができる。<sup>10</sup> n チャネル型のトランジスタの場合にはチャネル形成領域となるシリコン材料に引張応力を、p チャネル型のトランジスタの場合にはチャネル形成領域となるシリコン材料に圧縮応力を付加することで、各トランジスタの電界効果移動度を向上させることができる。

#### 【0108】

さらに、絶縁膜 910 上に絶縁膜 911 が設けられ、その表面は CMP による平坦化処理が施されている。これにより、トランジスタ 901 を含む階層よりも上の階層に高い精度で素子層を積層していくことができる。

#### 【0109】

トランジスタ 901 を含む階層よりも上層に、チャネルが酸化物半導体層に形成されるトランジスタ 902 を含む階層を形成する。トランジスタ 902 はトップゲート構造のトランジスタであり、酸化物半導体膜 926 の側面及び上面に接してソース電極層 927 及びドレイン電極層 928 を有し、これらの上のゲート絶縁膜 929 上にゲート電極層 930 を有している。また、トランジスタ 902 を覆うように絶縁膜 932、933 が形成されている。ここでトランジスタ 902 の作製方法について、以下に説明する。<sup>20</sup>

#### 【0110】

絶縁膜 924 上に酸化物半導体膜 926 を形成する。絶縁膜 924 は、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。特に、誘電率の低い (low-k) 材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁膜 924 に上記材料を用いた多孔性の絶縁膜を適用しても良い。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。本実施例では、膜厚 50 nm の酸化アルミニウム膜上に膜厚 300 nm 程度の酸化珪素膜を積層させて、絶縁膜 924 として用いる。<sup>30</sup>

#### 【0111】

酸化物半導体膜 926 は、絶縁膜 924 上に形成した酸化物半導体膜を所望の形状に加工することで、形成することができる。上記酸化物半導体膜の膜厚は、2 nm 以上 200 nm 以下、好ましくは 3 nm 以上 50 nm 以下、更に好ましくは 3 nm 以上 20 nm 以下とする。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス（例えばアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（例えばアルゴン）及び酸素混合雰囲気下においてスパッタ法により形成することができる。<sup>40</sup>

#### 【0112】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁膜 924 の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

#### 【0113】

10

20

30

40

50

本実施例では、In（インジウム）、Ga（ガリウム）、及びZn（亜鉛）を含むターゲットを用いたスパッタ法により得られる膜厚30nmのIn-Ga-Zn系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、好ましくは、原子数比がIn : Ga : Zn = 1 : 1 : 1、4 : 2 : 3、3 : 1 : 2、1 : 1 : 2、2 : 1 : 3、または3 : 1 : 4で示されるターゲットを用いる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

#### 【0114】

なお、酸化物半導体膜としてIn-Zn系の材料を用いる場合、用いるターゲットの組成は、原子数比で、In : Zn = 50 : 1 ~ 1 : 2（モル数比に換算すると $In_2O_3 : ZnO = 25 : 1 \sim 1 : 4$ ）、好ましくはIn : Zn = 20 : 1 ~ 1 : 1（モル数比に換算すると $In_2O_3 : ZnO = 10 : 1 \sim 1 : 2$ ）、さらに好ましくはIn : Zn = 15 : 1 ~ 1.5 : 1（モル数比に換算すると $In_2O_3 : ZnO = 15 : 2 \sim 3 : 4$ ）とする。例えば、In-Zn系酸化物半導体の形成に用いるターゲットは、原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとする。Znの比率を上記範囲に収めることで、移動度の向上を実現することができる。

#### 【0115】

また、酸化物半導体膜としてIn-Sn-Zn系酸化物半導体膜をスパッタリング法で成膜する場合、好ましくは、原子数比がIn : Sn : Zn = 1 : 1 : 1、2 : 1 : 3、1 : 2 : 2、または20 : 45 : 35で示されるIn-Sn-Zn-Oターゲットを用いる。

#### 【0116】

本実施例では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0117】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

#### 【0118】

また、スパッタリング装置の処理室のリーケートを $1 \times 10^{-10} Pa \cdot m^3 / 秒$ 以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として上述した吸着型の真空ポンプを用いることで、排気系からのアルカリ金属、水素原子、水素分子、水、または水素化物等の不純物の逆流を低減することができる。

#### 【0119】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

10

20

30

40

50

## 【0120】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜924までが形成された基板900を予備加熱し、基板900に吸着した水分又は水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400以下、好ましくは150以上300以下である。また、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

## 【0121】

なお、酸化物半導体膜926を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、三塩化硼素（BCl<sub>3</sub>）、四塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（CF<sub>4</sub>）、六弗化硫黄（SF<sub>6</sub>）、三弗化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）など）、臭化水素（HBr）、酸素（O<sub>2</sub>）、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。

10

## 【0122】

ドライエッチング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いることができる。所望の形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

20

## 【0123】

酸化物半導体膜926を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0124】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体膜926及び絶縁膜924の表面に付着しているレジスト残渣などを除去することが好ましい。

## 【0125】

30

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分又は水素（水酸基を含む）が多量に含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとって不純物である。そこで、本実施例では、酸化物半導体膜中の水分又は水素などの不純物を低減（脱水化または脱水素化）するために、酸化物半導体膜926に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア（CRDS（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20ppm（露点換算で-55）以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）雰囲気下で、酸化物半導体膜926に加熱処理を施す。

## 【0126】

40

酸化物半導体膜926に加熱処理を施すことで、酸化物半導体膜926中の水分又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化又は脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

## 【0127】

本実施例では、加熱処理装置の一つである電気炉を用いる。

## 【0128】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas

50

Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等のRTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

#### 【0129】

加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

10

#### 【0130】

以上の工程により、酸化物半導体膜926中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、オフ電流の著しく低いトランジスタを作製することができる。上記加熱処理は、酸化物半導体膜の成膜以降であれば、いつでも行うことができる。

20

#### 【0131】

次いで、フォトリソグラフィ工程を用いて、ソース電極層927及びドレイン電極層928を形成する。具体的には、ソース電極層927及びドレイン電極層928は、スパッタ法や真空蒸着法で絶縁膜924上に導電膜を形成した後、当該導電膜を所定の形状に加工(パターニング)することで、形成することができる。

#### 【0132】

本実施例では、ソース電極層927及びドレイン電極層928として、膜厚100nmのタンゲステン膜を用いる。

#### 【0133】

なお、導電膜のエッチングの際に、酸化物半導体膜926がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、酸化物半導体膜926の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

30

#### 【0134】

本実施例では、ソース電極層927及びドレイン電極層928となる導電膜に、タンゲステン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(アンモニア過水)を用いて、選択的に上記導電膜をウェットエッチングすることができる。具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と、水とを、体積比5:2:2で混合したアンモニア過水を用いる。あるいは、四弗化炭素(CF<sub>4</sub>)、塩素(Cl<sub>2</sub>)、酸素を含むガスを用いて、上記導電膜をドライエッチングしても良い。

40

#### 【0135】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、アッシングを行うことで更に形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。すなわち、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

#### 【0136】

50

また、酸化物半導体膜926と、ソース電極層927及びドレイン電極層928との間に、ソース領域及びドレイン領域として機能する酸化物導電膜を設けるようにしても良い。酸化物導電膜の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを適用することができる。

#### 【0137】

例えば、酸化物導電膜を形成する場合、酸化物導電膜を形成するためのパターニングと、ソース電極層927及びドレイン電極層928を形成するためのパターニングとを一括で行うようにしても良い。

10

#### 【0138】

ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、酸化物半導体膜926とソース電極層927及びドレイン電極層928との間の抵抗を下げることができるので、トランジスタの高速動作を実現させることができる。また、ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、トランジスタの耐圧を高めることができる。

#### 【0139】

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行うようにしても良い。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

20

#### 【0140】

なお、プラズマ処理を行った後、ソース電極層927及びドレイン電極層928と、酸化物半導体膜926とを覆うように、ゲート絶縁膜929を形成する。そして、ゲート絶縁膜929上において、酸化物半導体膜926と重なる位置にゲート電極層930を形成する。

#### 【0141】

本実施例では、スパッタ法で形成された膜厚20nmの酸化窒化珪素膜をゲート絶縁膜929として用いる。成膜時の基板温度は、室温以上400以下とすればよく、本実施例では300とする。

#### 【0142】

30

なお、ゲート絶縁膜929を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、又は希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。本実施例では、例えば、窒素雰囲気下で250、1時間の加熱処理を行う。あるいは、ソース電極層927及びドレイン電極層928を形成する前に、水分又は水素を低減させるための酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含むゲート絶縁膜929が設けられた後に、加熱処理が施されることによって、酸化物半導体膜926に対して行った先の加熱処理により、酸化物半導体膜926に酸素欠損が発生していたとしても、ゲート絶縁膜929から酸化物半導体膜926に酸素が供与される。そして、酸化物半導体膜926に酸素が供与されることで、酸化物半導体膜926において、ドナーとなる酸素欠損を低減し、化学量論的組成を満たすことが可能である。その結果、酸化物半導体膜926をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性的向上を実現することができる。この加熱処理を行うタイミングは、ゲート絶縁膜929の形成後であれば特に限定されず、他の工程と兼ねることで、工程数を増やすことなく酸化物半導体膜926をi型に近づけることができる。

40

#### 【0143】

また、酸素雰囲気下で酸化物半導体膜926に加熱処理を施することで、酸化物半導体に酸素を添加し、酸化物半導体膜926中においてドナーとなる酸素欠損を低減させても良

50

い。加熱処理の温度は、例えば 100 以上 350 未満、好ましくは 150 以上 250 未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガスの純度を、6 N (99.9999%) 以上、好ましくは 7 N (99.99999%) 以上、(即ち酸素中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下) とすることが好ましい。

#### 【0144】

あるいは、イオン注入法又はイオンドーピング法などを用いて、酸化物半導体膜 926 に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45 GHz のマイクロ波でプラズマ化した酸素を酸化物半導体膜 926 に添加すれば良い。

#### 【0145】

ゲート電極層 930 は、ゲート絶縁膜 929 上に導電膜を形成した後、該導電膜をパターニングすることで形成することができる。

#### 【0146】

ゲート電極層 930 は、10 nm ~ 400 nm、好ましくは 100 nm ~ 300 nm とする。本実施例では、スパッタ法により膜厚 30 nm の窒化タンタル上に膜厚 135 nm のタンクステンを積層させてゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極層 930 を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0147】

以上の工程により、トランジスタ 902 が形成される。

#### 【0148】

なお、トランジスタ 902 はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

#### 【0149】

また、上記作製方法では、ソース電極層 927 及びドレイン電極層 928 が、酸化物半導体膜 926 の後に形成されている。よって、図 7 に示すように、上記作製方法によって得られるトランジスタ 902 は、ソース電極層 927 及びドレイン電極層 928 が、酸化物半導体膜 926 の上に形成されている。しかし、トランジスタ 902 は、ソース電極層及びドレイン電極層が、酸化物半導体膜 926 の下、すなわち、酸化物半導体膜 926 と絶縁膜 924 の間に設けられていても良い。

#### 【0150】

また、酸化物半導体膜 926 に接する絶縁膜は、第 13 族元素及び酸素を含む絶縁材料を用いるようにしても良い。酸化物半導体材料には第 13 族元素を含むものが多く、第 13 族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体膜に接する絶縁膜に用いることで、酸化物半導体膜との界面の状態を良好に保つことができる。

#### 【0151】

第 13 族元素を含む絶縁材料とは、絶縁材料に一又は複数の第 13 族元素を含むことを意味する。第 13 族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上のものを示す。

#### 【0152】

例えば、ガリウムを含有する酸化物半導体膜に接して絶縁膜を形成する場合に、絶縁膜に酸化ガリウムを含む材料を用いることで酸化物半導体膜と絶縁膜の界面特性を良好に保つことができる。例えば、酸化物半導体膜と酸化ガリウムを含む絶縁膜とを接して設けることにより、酸化物半導体膜と絶縁膜の界面における水素のパイアップを低減することができる。なお、絶縁膜に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同

10

20

30

40

50

様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁膜を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体膜への水の侵入防止という点においても好ましい。

#### 【0153】

また、酸化物半導体膜926に接する絶縁膜は、酸素雰囲気下による熱処理や、酸素ドープなどにより、絶縁材料を化学量論的組成より酸素が多い状態とすることが好ましい。酸素ドープとは、酸素をバルクに添加することをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。

また、酸素ドープは、イオン注入法又はイオンドーピング法を用いて行ってもよい。

10

#### 【0154】

酸素ドープ処理を行うことにより、化学量論的組成より酸素が多い領域を有する絶縁膜を形成することができる。このような領域を備える絶縁膜と酸化物半導体膜が接することにより、絶縁膜中の過剰な酸素が酸化物半導体膜に供給され、酸化物半導体膜中、又は酸化物半導体膜と絶縁膜の界面における酸素欠陥を低減し、酸化物半導体膜をi型化又はi型に限りなく近くすることができる。

#### 【0155】

なお、化学量論的組成より酸素が多い領域を有する絶縁膜は、酸化物半導体膜926に接する絶縁膜のうち、上層に位置する絶縁膜又は下層に位置する絶縁膜のうち、どちらか一方のみに用いても良いが、両方の絶縁膜に用いる方が好ましい。化学量論的組成より酸素が多い領域を有する絶縁膜を、酸化物半導体膜926に接する絶縁膜の、上層及び下層に位置する絶縁膜に用い、酸化物半導体膜926を挟む構成とすることで、上記効果をより高めることができる。

20

#### 【0156】

また、酸化物半導体膜926の上層又は下層に用いる絶縁膜は、上層と下層で同じ構成元素を有する絶縁膜としても良いし、異なる構成元素を有する絶縁膜としても良い。また、酸化物半導体膜926に接する絶縁膜は、化学量論的組成より酸素が多い領域を有する絶縁膜の積層としても良い。

#### 【0157】

30

なお、本実施例においては、トランジスタ902はトップゲート構造としている。また、トランジスタ902にはバックゲート電極層923が設けられている。バックゲート電極層を設けた場合、さらにトランジスタ902のノーマリーオフ化を実現することができる。例えば、バックゲート電極層923の電位をGNDや固定電位とすることでトランジスタ902の閾値電圧をよりプラスとし、さらにノーマリーオフのトランジスタとすることができます。

#### 【0158】

このような、トランジスタ901及びトランジスタ902を電気的に接続して電気回路を形成するために、各階層間及び上層に接続のための配線層を単層又は多層積層する。

#### 【0159】

40

図7においては、トランジスタ901のソース及びドレインの一方は、コンタクトプラグ913を介して配線層914と電気的に接続している。一方、トランジスタ901のソース及びドレインの他方は、コンタクトプラグ915を介して配線層916と電気的に接続している。また、トランジスタ901のゲートは、コンタクトプラグ917、配線層918、コンタクトプラグ921、配線層922、及びコンタクトプラグ925を介してトランジスタ902のドレイン電極層928と電気的に接続している。

#### 【0160】

配線層914、918、916、922及びバックゲート電極層923は、絶縁膜中に埋め込まれている。これらの配線層等は、例えば銅、アルミニウム等の低抵抗な導電性材料を用いることが好ましい。また、CVD法により形成したグラフェンを導電性材料とし

50

て用いて配線層を形成することもできる。グラフェンとは、 $s p^2$ 結合を有する1原子層の炭素分子のシートのこと、または2乃至100層の炭素分子のシートが積み重なっているものをいう。このようなグラフェンを作製する方法として、金属触媒の上にグラフェンを形成する熱CVD法や、紫外光を照射して局所的にプラズマを発生させることで触媒を用いずにメタンからグラフェンを形成するプラズマCVD法などがある。

#### 【0161】

このような低抵抗な導電性材料を用いることで、配線層を伝播する信号のRC遅延を低減することができる。配線層に銅を用いる場合には、銅のチャネル形成領域への拡散を防止するため、バリア膜を形成する。バリア膜として、例えば窒化タンタル、窒化タンタルとタンタルとの積層、窒化チタン、窒化チタンとチタンとの積層等による膜を用いることができるが、配線材料の拡散防止機能、及び配線材料や下地膜等との密着性が確保される程度においてこれらの材料からなる膜に限られない。バリア膜は配線層とは別個の層として形成してもよく、バリア膜となる材料を配線材料中に含有させ、加熱処理によって絶縁膜に設けられた開口の内壁に析出させて形成しても良い。

#### 【0162】

絶縁膜911、912、919、920、933には、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、BPSG(Boron Phosphorus Silicate Glass)、PSG(Phosphorus Silicate Glass)、炭素を添加した酸化シリコン(SiOC)、フッ素を添加した酸化シリコン(SiOF)、 $Si(OCH_3)_4$ を原料とした酸化シリコンであるTEOS(Tetraethyl orthosilicate)、HSQ(Hydrogen Silsesquioxane)、MSQ(Methyl Silsesquioxane)、OSG(Organic Silicate Glass)、有機ポリマー系の材料等の絶縁体を用いることができる。特に半導体装置の微細化を進める場合には、配線間の寄生容量が顕著になり信号遅延が増大するため酸化シリコンの比誘電率( $k = 4.0 \sim 4.5$ )では高く、 $k$ が3.0以下の材料を用いることが好ましい。また該絶縁膜に配線を埋め込んだ後にCMP処理を行うため、絶縁膜には機械的強度が要求される。この機械的強度が確保できる限りにおいて、これらを多孔質(ポーラス)化させて低誘電率化することができる。絶縁膜は、スパッタリング法、CVD法、スピンドルコート法(Spin On Glass:SOGともいう)を含む塗布法等により形成する。

#### 【0163】

絶縁膜911、912、919、920、933には、配線材料をこれら絶縁膜中に埋め込んだ後、CMP等による平坦化処理を行う際のエッチングストップとして機能させるための絶縁膜を別途設けてもよい。

#### 【0164】

コントラクトプラグ913、915、917、921、925は、絶縁膜に高アスペクト比の開口(ピアホール)を形成し、タンゲステン等の導電材料で埋め込むことで作製する。開口は、異方性の高いドライエッ칭を行なうことが好ましい。特に、反応性イオンエッチング法(RIE法)を用いることが好ましい。開口の内壁にはチタン膜、窒化チタン膜又はこれらの積層膜等からなるバリア膜(拡散防止膜)が設けられ、バリア膜の内部にタンゲステンやリン等をドープしたポリシリコン等の材料が充填される。例えばプランケットCVD法により、ピアホール内にタンゲステンを埋め込むことができ、CMPによりコントラクトプラグの上面は平坦化されている。

#### 【実施例6】

#### 【0165】

本発明の一態様に係る半導体装置は、デジタル信号処理、ソフトウェア無線、アビオニクス(通信機器、航法システム、自動操縦装置、飛行管理システム等の航空に関する電子機器)、ASICのプロトタイピング、医療用画像処理、音声認識、暗号、バイオインフォマティクス(生物情報科学)、機械装置のエミュレータ、電波天文学における電波望遠鏡等、幅広い分野の電子機器に用いることができる。

10

20

30

40

50

## 【0166】

このような電子機器の例として、例えば民生機器としては、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（DVD等の記録媒体を再生し、その画像を表示するディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーラジオ、デジタルオーディオプレーヤ等）、複写機、ファクシミリ、プリンタ、プリンタ複合機等が挙げられる。これら電子機器の具体例を図8に示す。

## 【0167】

10

図8(A)は、携帯型ゲーム機を示す図である。図8(A)に示す携帯型ゲーム機は、筐体5001、筐体5002、表示部5003、表示部5004、マイクロホン5005、スピーカ5006、操作キー5007、スタイルス5008等を有する。なお、図8(A)に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

## 【0168】

図8(B)は、携帯情報端末を示す図である。図8(B)に示す携帯情報端末は、第1の筐体5601、第2の筐体5602、第1の表示部5603、第2の表示部5604、接続部5605、操作キー5606等を有する。第1の表示部5603は第1の筐体5601に設けられており、第2の表示部5604は第2の筐体5602に設けられている。そして、第1の筐体5601と第2の筐体5602とは、接続部5605により接続されており、第1の筐体5601と第2の筐体5602との間の角度は、接続部5605により変更が可能となっている。第1の表示部5603における映像の切り替えを、接続部5605における第1の筐体5601と第2の筐体5602との間の角度に従って、切り替える構成としても良い。また、第1の表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。あるいは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

20

## 【0169】

30

図8(C)は、ノート型パーソナルコンピュータを示す図である。図8(C)に示すノート型パーソナルコンピュータは、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。

## 【0170】

図8(D)は、電気冷凍冷蔵庫を示す図である。図8(D)に示す電気冷凍冷蔵庫は、筐体5301、冷蔵室用扉5302、冷凍室用扉5303等を有する。

## 【0171】

図8(E)は、ビデオカメラを示す図である。図8(E)に示すビデオカメラは、第1の筐体5801、第2の筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。操作キー5804及びレンズ5805は第1の筐体5801に設けられており、表示部5803は第2の筐体5802に設けられている。そして、第1の筐体5801と第2筐体5802とは、接続部5806により接続されており、第1の筐体5801と第2筐体5802との間の角度は、接続部5806により可動となっている。表示部5803における映像の切り替えを、接続部5806における第1の筐体5801と第2の筐体5802との間の角度に従って行う構成としても良い。

40

## 【0172】

図8(F)は、普通自動車を示す図である。図8(F)に示す普通自動車は、車体5101、車輪5102、ダッシュボード5103、ライト5104等を有する。

## 【符号の説明】

## 【0173】

50

|       |            |    |

|-------|------------|----|

| 1     | 演算部        |    |

| 2     | データ退避部     |    |

| 1 0   | インバータ      |    |

| 1 1   | NANDゲート    |    |

| 1 2   | アナログスイッチ   |    |

| 1 3   | アナログスイッチ   |    |

| 1 4   | アナログスイッチ   |    |

| 1 5   | インバータ      |    |

| 1 6   | インバータ      |    |

| 2 1   | トランジスタ     | 10 |

| 2 2   | 容量素子       |    |

| 2 3   | トランジスタ     |    |

| 2 4   | 手段         |    |

| 2 5   | アナログスイッチ   |    |

| 2 6   | アナログスイッチ   |    |

| 2 7   | インバータ      |    |

| 2 8   | トランジスタ     |    |

| 2 9   | トランジスタ     |    |

| 3 0   | 絶縁表面を有する層  |    |

| 3 1   | 酸化物半導体層    | 20 |

| 3 2   | 導電層        |    |

| 3 3   | 導電層        |    |

| 3 4   | 絶縁層        |    |

| 3 5   | 導電層        |    |

| 9 0 0 | 基板         |    |

| 9 0 1 | トランジスタ     |    |

| 9 0 2 | トランジスタ     |    |

| 9 0 4 | ウェル        |    |

| 9 0 6 | 不純物領域      |    |

| 9 0 7 | ゲート絶縁膜     | 30 |

| 9 0 8 | ゲート電極層     |    |

| 9 0 9 | サイドウォール絶縁膜 |    |

| 9 1 0 | 絶縁膜        |    |

| 9 1 1 | 絶縁膜        |    |

| 9 1 2 | 絶縁膜        |    |

| 9 1 3 | コントラクトプラグ  |    |

| 9 1 4 | 配線層        |    |

| 9 1 5 | コントラクトプラグ  |    |

| 9 1 6 | 配線層        |    |

| 9 1 7 | コントラクトプラグ  | 40 |

| 9 1 8 | 配線層        |    |

| 9 1 9 | 絶縁膜        |    |

| 9 2 0 | 絶縁膜        |    |

| 9 2 1 | コントラクトプラグ  |    |

| 9 2 2 | 配線層        |    |

| 9 2 3 | バックゲート電極層  |    |

| 9 2 4 | 絶縁膜        |    |

| 9 2 5 | コントラクトプラグ  |    |

| 9 2 6 | 酸化物半導体膜    |    |

| 9 2 7 | ソース電極層     | 50 |

|         |             |    |

|---------|-------------|----|

| 9 2 8   | ドレイン電極層     |    |

| 9 2 9   | ゲート絶縁膜      |    |

| 9 3 0   | ゲート電極層      |    |

| 9 3 2   | 絶縁膜         |    |

| 9 3 3   | 絶縁膜         |    |

| 5 0 0 1 | 筐体          |    |

| 5 0 0 2 | 筐体          |    |

| 5 0 0 3 | 表示部         |    |

| 5 0 0 4 | 表示部         |    |

| 5 0 0 5 | マイクロホン      | 10 |

| 5 0 0 6 | スピーカ        |    |

| 5 0 0 7 | 操作キー        |    |

| 5 0 0 8 | スタイラス       |    |

| 5 1 0 1 | 車体          |    |

| 5 1 0 2 | 車輪          |    |

| 5 1 0 3 | ダッシュボード     |    |

| 5 1 0 4 | ライト         |    |

| 5 3 0 1 | 筐体          |    |

| 5 3 0 2 | 冷蔵室用扉       |    |

| 5 3 0 3 | 冷凍室用扉       | 20 |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キーボード       |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          |    |

| 5 6 0 2 | 筐体          |    |

| 5 6 0 3 | 表示部         |    |

| 5 6 0 4 | 表示部         |    |

| 5 6 0 5 | 接続部         |    |

| 5 6 0 6 | 操作キー        | 30 |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 筐体          |    |

| 5 8 0 3 | 表示部         |    |

| 5 8 0 4 | 操作キー        |    |

| 5 8 0 5 | レンズ         |    |

| 5 8 0 6 | 接続部         |    |

【図1】

(B)

【図2】

(B)

【図3】

【図4】

(B)

【図5】

(A)

【図6】

【図7】

(B)

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開2011-171723(JP,A)

特開2011-238334(JP,A)

米国特許第04510584(US,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 41

G 11 C 11 / 405