### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2016/025478 A1

(43) International Publication Date 18 February 2016 (18.02.2016)

(51) International Patent Classification: *H01L 23/538* (2006.01)

(21) International Application Number:

PCT/US2015/044651

(22) International Filing Date:

11 August 2015 (11.08.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data: 62/035,713

3 11 August 2014 (11.08.2014)

US

- (71) Applicant: MASSACHUSETTS INSTITUTE OF TECHNOLOGY [US/US]; 77 Massachusetts Avenue, Cambridge, Massachusetts 02139 (US).

- (72) Inventors: DAS, Rabindra, N.; 4134 Lexington Ridge Drive, Lexington, Massachusetts 02421 (US). YOST, Donna-Ruth, W.; 15 Putnam Road, Acton, Massachusetts 01720 (US). CHEN, Chenson; 39 Rokeby Road, Waban, Massachusetts 02468 (US). WARNER, Keith; 823 Hill Street, Whitinsville, Massachusetts 01588 (US). VITALE, Steven, A.; 124 Bishops Forest Drive, Waltham, Massachusetts 02452 (US). GOUKER, Mark, A.; 54 Cary Avenue, Lexington, Massachusetts 02421 (US). KEAST, Craig, L.; 65 Duck Pond Drive, Groton, Massachusetts 01450 (US).

- (74) Agents: CROOKER, Albert, C. et al.; Daly, Crowley, Mofford & Durkee, LLP, 354A Turnpike Street, Suite 301A, Canton, Massachusetts 02021 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

- of inventorship (Rule 4.17(iv))

#### Published:

with international search report (Art. 21(3))

(54) Title: INTERCONNECT STRUCTURES FOR ASSEMBLY OF SEMICONDUCTOR STRUCTURES INCLUDING AT LEAST ONE INTEGRATED CIRCUIT STRUCTURE

(57) Abstract: A semiconductor structure includes at least two substrate layers, each of the at least two substrate layers having first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. The semiconductor structure also includes a substrate joining layer disposed between and coupled to the second surface of a first one of the at least two substrate layers and the first surface of a second one of the at least two substrate layers. The substrate joining layer includes at least one integrated circuit (IC) structure disposed between the first and second surfaces of said substrate joining layer. A corresponding method for fabricating a semiconductor structure is also provided.

# INTERCONNECT STRUCTURES FOR ASSEMBLY OF SEMICONDUCTOR STRUCTURES INCLUDING AT LEAST ONE INTEGRATED CIRCUIT STRUCTURE

## CROSS REFERENCE TO RELATED APPLICATION

[001] This application claims the benefit of U.S. Provisional Application No. 62/035,713 filed August 11, 2014 under 35 U.S.C. §119(e) which application is hereby incorporated herein by reference in its entirety.

#### **GOVERNMENT RIGHTS**

[002] This invention was made with government support under Contract No. FA8721-05-C-0002 awarded by the U.S. Air Force. The government has certain rights in the invention.

#### **FIELD**

[003] This disclosure relates generally to semiconductor structures, and more particularly, to semiconductor interconnect structures which enable assembly of semiconductor structures including at least one integrated circuit structure.

#### **BACKGROUND**

[004] As is known in the art, there is trend toward miniaturization of electronic products such as mobile phones, tablets, digital cameras, and the like. Consequently, there has been a trend in semiconductor device manufacturing towards smaller and more densely packed semiconductor structures. This has resulted in a demand for semiconductor packages which are relatively low loss, lightweight structures and which support increased electronic capabilities (e.g., increased density, mobility and extended operational life) in miniaturized electronic products demanded by both military and commercial customers alike.

[005] The foregoing trend and demand, for example, drives a need for multi-layer integrated semiconductor (IC) structures (e.g., three dimensional (3D) integrated circuits (ICs)), semiconductor structures in which a number of individual semiconductor structures are both mechanically and electrically

coupled. The foregoing trend and demand also drives a need for interconnect structures which enable assembly of semiconductor structures including at least one integrated circuit structure (e.g., multi-layer IC structure).

## SUMMARY

[006] Described herein are concepts, systems, circuits and techniques related to a semiconductor interconnect structure (i.e., a substrate joining layer) suitable for electrically and mechanically coupling at least two semiconductor structures (e.g., substrate layers) together to form a semiconductor structure including the at least two semiconductor structures. The present disclosure further describes circuits and techniques for fabricating semiconductor structures including at least one integrated circuit structure (e.g., 2D, 2.5D, and 3D IC structures), the at least one integrated circuit structure disposed (e.g., embedded) between surfaces of the semiconductor structures. A first integrated circuit structure (e.g., a 2D IC structure) in the semiconductor structures can be replaced by a second integrated circuit structure (e.g., a 3D IC structure) without substantially changing a distance between first and second surfaces of the semiconductor structures.

[007] As one example, the process and materials developed for embedding the first IC structure (e.g., having a thickness of about seventy hundred fifty micron) can be used for embedding the second IC structure (e.g., having a thickness of about seven hundred sixty two micron) because thickness differences between the first IC structure and the second IC structure are within spacing tolerance limits of the first IC structure (e.g., about twenty micron) and/or tolerance limits of a pressed/laminated dielectric used to embed the first IC structure (e.g., to prevent the first IC structure from cracking during lamination).

[008] In one aspect of the concepts described herein, a semiconductor structure includes at least two substrate layers, each of the at least two substrate layers having first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. Each

of the at least two substrate layers include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads of a first one of the at least two substrate layers is disposed over or beneath select portions of the second surface of the first one of the substrate layers and is electrically coupled to select ones of the electrical connections in the first one of the substrate layers. Additionally, the first surface of at least a first select one of the interconnect pads of a second one of the at least two substrate layers is disposed over or beneath select portions of the first surface of the second one of the substrate layers and is electrically coupled to select ones of the electrical connections in the second one of the substrate layers.

[009] The semiconductor structure also includes a substrate joining layer disposed between and coupled to the second surface of the first one of the substrate layers and the first surface of the second one of the substrate layers. The substrate joining layer has first and second opposing surfaces and a plurality of electrical connections extending between select portions of the first and second surfaces, and includes at least one integrated circuit (IC) structure disposed between the first and second surfaces of the substrate joining layer. The at least one IC structure has first and second opposing surfaces and includes one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the at least one IC structure and is electrically coupled to select ones of the electrical connections in the substrate joining layer.

[0010] The semiconductor structure may also include one or more of the following features individually or in combination with other features. The at least one IC structure of the substrate joining layer may include a two-dimensional (2D) IC structure and a three-dimensional (3D) IC structure. The substrate joining layer may include a first substrate joining layer portion having first and second opposing surfaces and a first plurality of electrical connections

extending between select portions of the first and second surfaces. The first surface of the first substrate joining layer portion corresponds to the first surface of the substrate joining layer, and the 3D IC structure is disposed between the first and second surfaces of the first substrate joining layer. The 3D IC structure includes at least a first select interconnect pad disposed over or beneath select portions of the first surface of the 3D IC structure, the first select interconnect pad electrically coupled to first select ones of the first plurality of electrical connections in the first substrate joining layer portion.

[0011] The semiconductor structure may additionally include one or more of the following features individually or in combination with other features. The substrate joining layer may include a second substrate joining layer portion having first and second opposing surfaces and a second plurality of electrical connections extending between select portions of the first and second surfaces. The first surface of the second substrate joining layer portion corresponds to the second surface of said substrate joining layer, and the 2D IC structure is disposed between the first and second surfaces of the second substrate joining layer. The 2D IC structure includes at least a first select interconnect pad disposed over or beneath select portions of the first surface of the 2D IC structure, the first select interconnect pad electrically coupled to first select ones of the second plurality of electrical connections in the second substrate joining layer portion. The substrate joining layer may include an insulating layer having first and second opposing surfaces. The first surface of the insulating layer is coupled to the second surface of the first substrate joining layer portion, and the second surface of the insulating layer is coupled to the second surface of the second substrate joining layer portion.

[0012] The semiconductor structure may further include one or more of the following features individually or in combination with other features. The substrate joining layer may include openings formed in select portions of the insulating layer, the openings shaped to receive the 3D IC structure and the 2D IC structure. The first substrate joining layer portion may include a first

substrate layer having first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. The first surface of the first substrate layer corresponds to the first surface of the first substrate joining layer portion and the plurality of electrical connections in the first substrate layer correspond to the first plurality of electrical connections in the first substrate joining layer portion. The substrate joining layer may include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of each one of the interconnect pads is disposed over or beneath select portions of the second surface of the first substrate layer and is electrically coupled to select ones of the electrical connections in the first substrate layer. The substrate joining layer may include one or more alignment marks disposed over or beneath the second surface of the first substrate layer and an adhesive layer having first and second opposing surfaces. The first surface of the adhesive layer is disposed over at least the second surface of the first substrate layer and the second surfaces and one or more sides of the interconnect pads, and the first surface of the 3D IC structure is disposed over or beneath select portions of the second surface of the adhesive layer and is aligned relative to at least one of the alignment marks.

[0013] The semiconductor structure may further include one or more of the following features individually or in combination with other features. The substrate joining layer may include one or more pad interconnects having at least one pad portion and at least one interconnect portion, the pad interconnects electrically coupled to at least the first select interconnect pad of the 3D IC structure. The pad portion of each one of the pad interconnects has a surface disposed over select portions of the first surface of the first substrate layer and the interconnect portion of each one of the pad interconnects extends from the pad portion to the second surface of at least the first select interconnect pad of the 3D IC structure. The first substrate joining layer portion may include a second substrate layer having first and second opposing surfaces and a plurality of electrical connections extending between the first

and second surfaces. The first surface of the second substrate layer corresponds to the first surface of the second substrate joining layer portion and the plurality of electrical connections in the second substrate layer correspond to the second plurality of electrical connections in the second substrate joining layer portion.

[0014] The semiconductor structure may also include one or more of the following features individually or in combination with other features. The first substrate joining layer portion may include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of each one of the interconnect pads is disposed over or beneath select portions of the second surface of the second substrate layer and is electrically coupled to select ones of the electrical connections in the second substrate layer. The first substrate joining layer portion may include one or more alignment marks disposed over or beneath the second surface of the second substrate layer, and an adhesive layer having first and second opposing surfaces. The first surface of the adhesive layer is disposed over at least the second surface of the second substrate layer and the second surfaces and one or more sides of the interconnect pads, and the first surface of the 2D IC structure is disposed over or beneath select portions of the second surface of the adhesive layer and is aligned relative to at least one of the alignment marks.

[0015] The semiconductor structure may additionally include one or more of the following features individually or in combination with other features. The first substrate joining layer portion may include one or more pad interconnects having at least one pad portion and at least one interconnect portion, the pad interconnects electrically coupled to at least the first select interconnect pad of the 2D IC structure. The pad portion of each one of the pad interconnects has a surface disposed over select portions of the first surface of the second substrate layer and the interconnect portion of each one of the pad interconnects extends from the pad portion to the second surface of at least the

first select interconnect pad of the 2D IC structure. The first surface of said substrate joining layer may be electrically coupled to the second surface of the first select one of the interconnect pads of the first one of the substrate layers, and the second surface of said substrate joining layer may be electrically coupled to the second surface of the second select one of the interconnect pads of the second one of the substrate layers to form one or more electrical connections between the first one of the substrate layers and the second one of the substrate layers.

[0016] The semiconductor structure may further include one or more of the following features individually or in combination with other features. A 2D IC structure disposed over and coupled to the first surface of said first substrate layer or the second surface of the second substrate layer, the 2D IC structure having first and second opposing surfaces and one or more interconnect pads, and the interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads of the 2D IC structure is disposed over or beneath select portions of the first surface of the 2D IC structure. A 3D IC structure disposed over and coupled to the first surface of the first substrate layer or the second surface of said second substrate layer, the 3D IC structure having first and second opposing surfaces and one or more interconnect pads, and the interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads of the 3D IC structure is disposed over or beneath select portions of the first surface of the 3D IC structure.

[0017] The semiconductor structure may also include one or more of the following features individually or in combination with other features. One or more fusible coupling structures disposed between and electrically coupled to the second surface of at least the first select one of the interconnect pads of the 2D IC structure and the second surface of a second select one of the interconnect pads of the second one of the substrate layers. The first surface

of the second select one of the interconnect pads is disposed over or beneath select portions of the second surface of the second one of the substrate layers and is electrically coupled to second select ones of the electrical connections in the second one of the substrate layers. One or more fusible coupling structures disposed between and electrically coupled to the second surface of at least the first select one of the interconnect pads of the 3D IC structure and the second surface of a third select one of the interconnect pads of the second one of the substrate layers. The first surface of the third select one of the interconnect pads is disposed over or beneath select portions of the second surface of the second one of the substrate layers and is electrically coupled to third select ones of the electrical connections in the second one of the substrate layers.

[0018] The semiconductor structure may additionally include one or more of the following features individually or in combination with other features. A heat dissipation structure having first and second opposing surfaces, with a first surface of the heat dissipation structure disposed over and coupled to at least one of the second surface of the 2D IC structure and the second surface of the 3D IC structure. A thermal interface structure disposed between the first surface of the heat dissipation structure and the second surface of the 2D IC structure and/or the first surface of the heat dissipation structure and the second surface of the 3D IC structure. The first surface of the heat dissipation structure may be further disposed over and coupled to the second surface of at least a fourth select one of the interconnect pads of the second one of the substrate layers. The first surface of the fourth select one of the interconnect pads is disposed over or beneath select portions of the second surface of the second one of the substrate layers and is electrically coupled to fourth select ones of the electrical connections in the second one of the substrate layers.

[0019] The semiconductor structure may further include one or more of the following features individually or in combination with other features. One or more fusible coupling structures disposed between the first and second

surfaces of the substrate joining layer and electrically coupled to the second surface of at least the first select one of the interconnect pads of the first one of the substrate layers and to the second surface of at least the first select one of the interconnect pads of the second one of the substrate layers to form an interconnect for electrically and mechanically coupling the first one of the substrate layers to the second one of the substrate layers. The fusible coupling structures may be provided as at least one of a solder ball and a self-aligned contact pad. At least one of the first one of the substrate layers and the second one of the substrate layers may be a multi-layer substrate. The semiconductor structure may be integrated into a communications device.

[0020] In one aspect of the concepts described herein, a method for fabricating a semiconductor structure includes providing at least two substrate layers, each of the at least two substrate layers has first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. Each of the at least two substrate layers includes one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads of a first one of the at least two substrate layers is disposed over or beneath select portions of the second surface of the first one of the substrate layers and is electrically coupled to select ones of the electrical connections in the first one of the substrate layers. Additionally, the first surface of at least a first select one of the interconnect pads of a second one of the at least two substrate layers is disposed over or beneath select portions of the first surface of the second one of the substrate layers and is electrically coupled to select ones of the second one of the substrate layers.

[0021] The method additionally includes providing a substrate joining layer having first and second opposing surfaces and a plurality of electrical connections extending between select portions of the first and second surfaces. The substrate joining layer includes at least one integrated circuit (IC) structure disposed between the first and second surfaces of the substrate joining layer.

The at least one IC structure has first and second opposing surfaces and includes one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the at least one IC structure and is electrically coupled to select ones of the electrical connections in the substrate joining layer.

[0022] The method also includes coupling the first surface of the substrate joining layer to the second surface of the first one of the substrate layers to form one or more electrical connections between the substrate joining layer and the first one of the substrate layers. The method further includes coupling the second surface of the substrate joining layer to the first surface of the second one of the substrate layers to form one or more electrical connections between the substrate joining layer and the second one of the substrate layers.

[0023] The method may include one or more of the following features either individually or in combination with other features. Providing a substrate joining layer having first and second opposing surfaces and a plurality of electrical connections extending between select portions of the first and second surfaces may include providing a first substrate joining layer portion having first and second opposing surfaces and a first plurality of electrical connections extending between select portions of the first and second surfaces. The first substrate joining layer portion may include one or more three-dimensional (3D) integrated circuit (IC) structures disposed between the first and second surfaces of the first substrate joining layer. Each of the 3D IC structures may include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the 3D IC structures and is electrically coupled to first select ones of the first plurality of electrical connections in the first substrate joining layer portion.

[0024] The method may also include one or more of the following features either individually or in combination with other features. Providing a substrate joining layer may include providing a second substrate joining layer portion having first and second opposing surfaces and a second plurality of electrical connections extending between select portions of the first and second surfaces. The second substrate joining layer portion may include one or more two-dimensional (2D) IC structures disposed between the first and second surfaces of the first substrate joining layer. Each of the 2D IC structures may include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the 2D IC structures and is electrically coupled to first select ones of the second plurality of electrical connections in the second substrate joining layer portion.

[0025] Providing a substrate joining layer may include providing an insulating layer having first and second opposing surfaces. Providing a substrate joining layer may include coupling the first surface of the insulating layer to the second surface of the first substrate joining layer portion and the second surface of the insulating layer to the second surface of the second substrate joining layer portion to form a substrate joining layer having first and second opposing surfaces and a plurality of electrical connections extending between select portions of the first and second surfaces. The first surface of the first substrate joining layer portion corresponds to the first surface of said substrate joining layer and the first surface of the second substrate joining layer.

[0026] The method may additionally include one or more of the following features either individually or in combination with other features. Providing an insulating layer having first and second opposing surfaces may include disposing an insulating material over the second surface of the first substrate joining layer portion, and forming an insulating layer having first and second

opposing surfaces from the insulating material. The first surface of the insulating layer is disposed over the second surface of the first substrate joining layer portion. Providing an insulating layer having first and second opposing surfaces may include providing an insulating layer having first and second opposing surfaces and openings formed in select portions of the insulating layer. The openings may be shaped to receive the 3D IC structures and the 2D IC structures. The first surface of the insulating layer is disposed over and coupled to the second surface of the first substrate joining layer portion and the second surface of the insulating layer is disposed over and coupled to the first surface of the second substrate joining layer portion.

[0027] The method may further include one or more of the following features either individually or in combination with other features. Providing a first substrate joining layer portion having first and second opposing surfaces and a first plurality of electrical connections extending between select portions of the first and second surfaces may include providing a first substrate layer having first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. The first surface of the first substrate layer corresponds to the first surface of the first substrate joining layer portion and the plurality of electrical connections in the first substrate layer correspond to the first plurality of electrical connections in the first substrate layer portion.

[0028] Providing a first substrate joining layer portion may include providing one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of each one of the interconnect pads is disposed over or beneath select portions of the second surface of the first substrate layer and is electrically coupled to select ones of the electrical connections in the first substrate layer. Providing a first substrate joining layer portion may include providing one or more alignment marks on the second surface of the first substrate layer. Providing a first substrate joining layer portion may include applying an adhesive layer having first and second

opposing surfaces. The first surface of the adhesive layer is disposed over at least the second surface of the first substrate layer and the second surfaces and one or more sides of the interconnect pads.

[0029] The method may also include one or more of the following features either individually or in combination with other features. Providing a first substrate joining layer portion may include providing one or more three-dimensional (3D) IC structures having first and second opposing surfaces. The first surface of each one of the 3D IC structures is disposed over or beneath select portions of the second surface of the adhesive layer and each of the 3D IC structures is aligned relative to at least one of the alignment marks. Each of the 3D IC structures include one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the 3D IC structures.

[0030] Providing a first substrate joining layer portion may include forming openings having a predetermined shape in select portions of the first substrate layer and the adhesive layer. The openings extend between the first surface of the first substrate layer and the second surface of at least the first select one of the interconnect pads of the 3D IC structures. Providing a first substrate joining layer portion may include providing one or more pad interconnects having at least one pad portion and at least one interconnect portion, the pad interconnects electrically coupled to at least the first select one of the interconnect pads, wherein the pad portion of each one of the pad interconnects has a surface disposed over select portions of the first surface of the first substrate layer and the interconnect portion of each one of the pad interconnects extends from the pad portion to the second surface of at least the first select one of the interconnect pads and has a surface disposed over select edges of the openings formed in the first substrate layer and the adhesive layer.

[0031] The method may also include one or more of the following features either individually or in combination with other features. Providing a second substrate joining layer portion having first and second opposing surfaces and a second plurality of electrical connections extending between select portions of the first and second surfaces may include providing a second substrate layer having first and second opposing surfaces and a plurality of electrical connections extending between the first and second surfaces. The first surface of the second substrate layer corresponds to the first surface of the second substrate joining layer portion and the plurality of electrical connections in the second substrate layer correspond to the second plurality of electrical connections in the second substrate joining layer portion.

Providing a second substrate joining layer portion may include providing one or more interconnect pads having first and second opposing surfaces and one or more sides. The first surface of each one of the interconnect pads is disposed over or beneath select portions of the second surface of the second substrate layer and is electrically coupled to the plurality of electrical connections in the second substrate layer.

[0032] The method may additionally include one or more of the following features either individually or in combination with other features. Providing a second substrate joining layer portion may include providing one or more alignment marks on the second surface of the second substrate layer. Providing a second substrate joining layer portion may include applying an adhesive layer having first and second opposing surfaces. The first surface of the adhesive layer is disposed over at least the second surface of the second substrate layer and the second surfaces and one or more sides of the interconnect pads. Providing a second substrate joining layer portion may include providing one or more two-dimensional (2D) IC structures having first and second opposing surfaces. The first surface of each one of the 2D IC structures is disposed over or beneath select portions of the second surface of the adhesive layer and each of the 2D IC structures is aligned relative to at least one of the alignment marks

[0033] Each of the 2D IC structures may include one or more interconnect pads having first and second opposing surfaces and one or more sides, wherein the first surface of at least a first select one of the interconnect pads is disposed over or beneath select portions of the first surface of the 2D IC structures. Providing a second substrate joining layer portion may include forming openings having a predetermined shape in select portions of the second substrate layer and the adhesive layer. The openings may extend between the first surface of the second substrate layer and the second surface of at least the first select one of the interconnect pads of the 2D IC structures. Providing a second substrate joining layer portion may include providing one or more pad interconnects having at least one pad portion and at least one interconnect portion, the pad interconnects electrically coupled to at least the first select one of the interconnect pads. The pad portion of each one of the pad interconnects has a surface disposed over select portions of the first surface of the second substrate layer and the interconnect portion of each one of the pad interconnects extends from the pad portion to the second surface of at least the first select one of the interconnect pads and has a surface disposed over select edges of the openings formed in the second substrate layer and the adhesive layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0034] Features and advantages of the concepts, systems, circuits and techniques disclosed herein will be apparent from the following description of the embodiments taken in conjunction with the accompanying drawings in which:

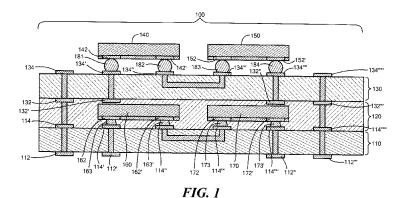

[0035] Fig. 1 is a block diagram of an example semiconductor structure;

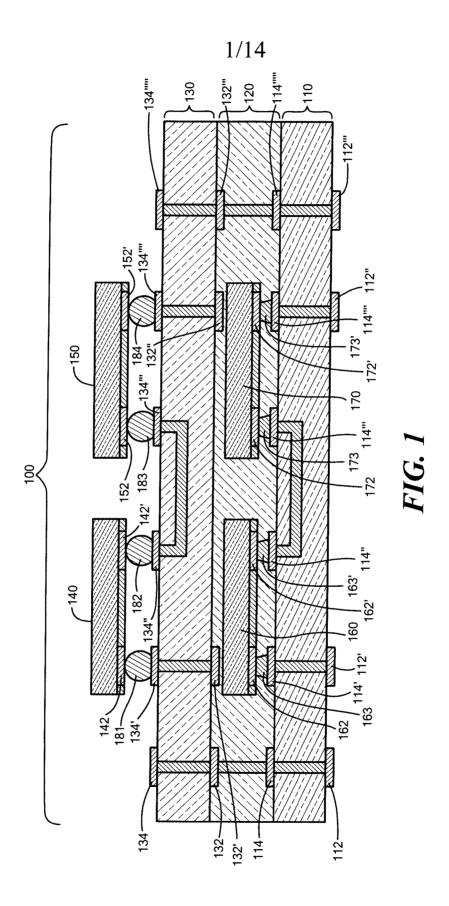

[0036] Fig. 2 is a block diagram of an example semiconductor structure similar to the semiconductor structure of Fig. 1, for example;

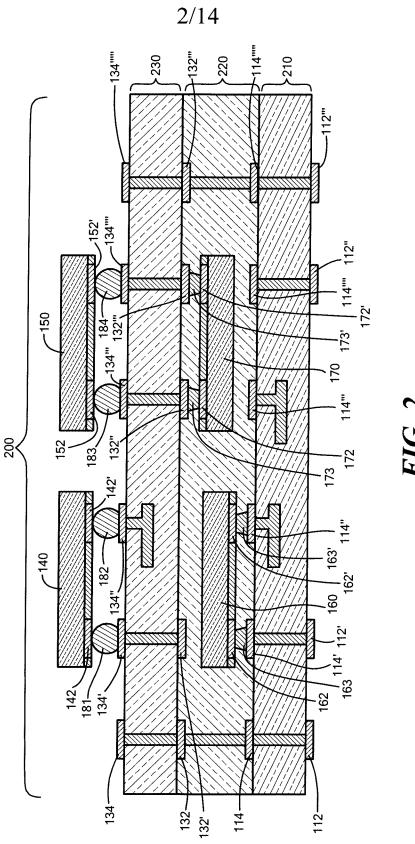

[0037] Fig. 3 is a block diagram of another example semiconductor structure;

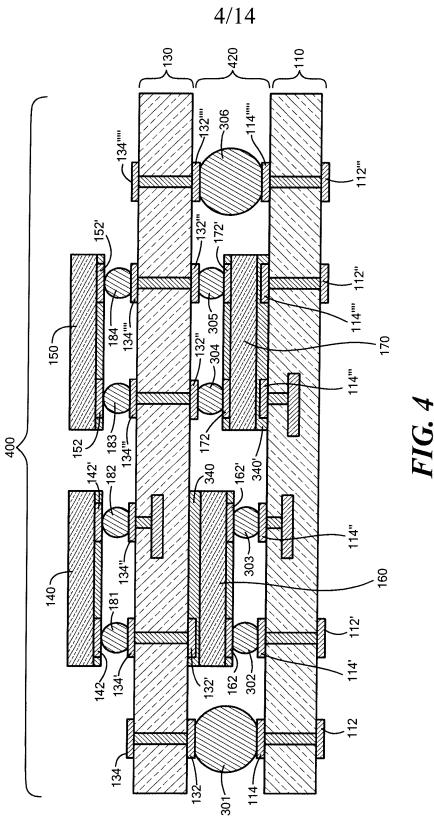

[0038] Fig. 4 is a block diagram of another example semiconductor structure;

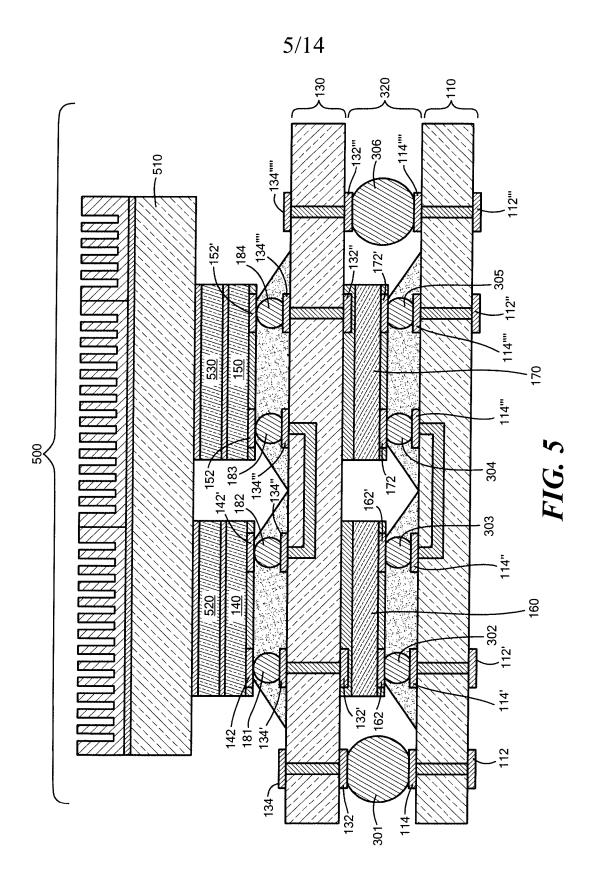

[0039] Fig. 5 is a block diagram of another example semiconductor structure similar to the semiconductor structure of Fig. 4, for example;

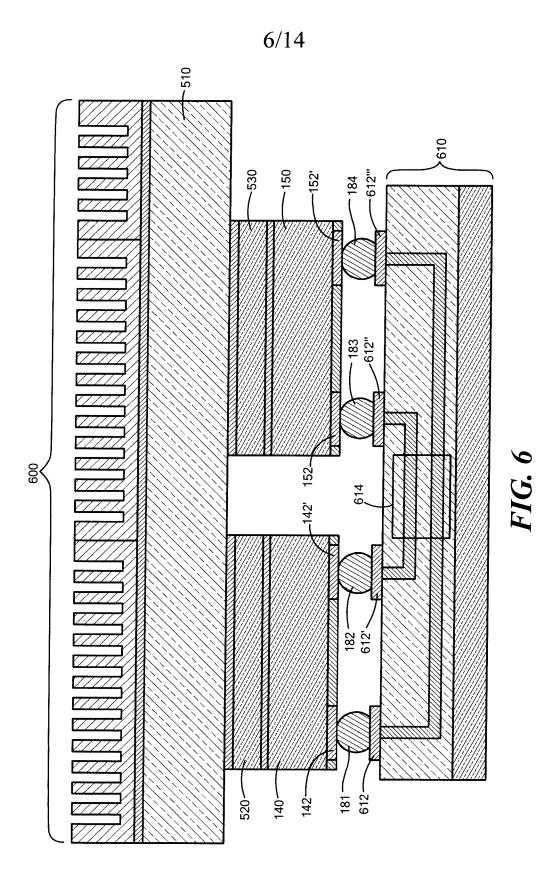

[0040] Fig. 6 is a block diagram of another example semiconductor structure;

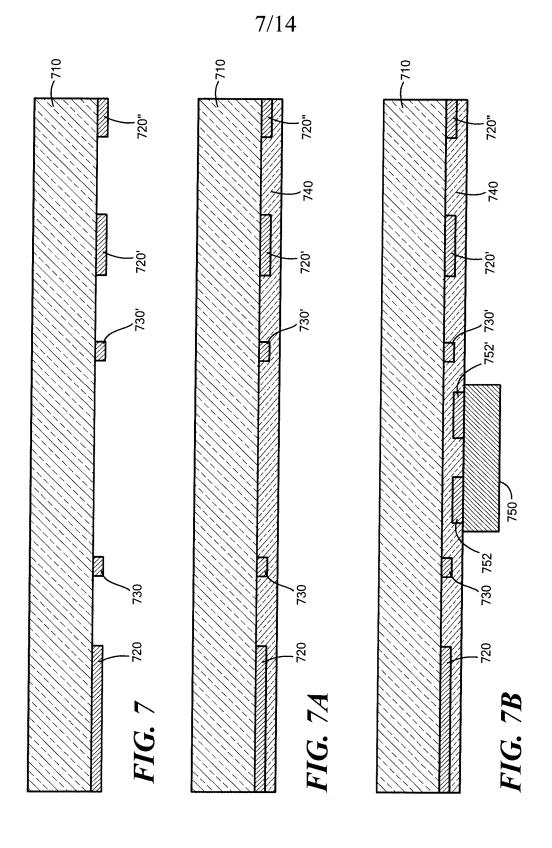

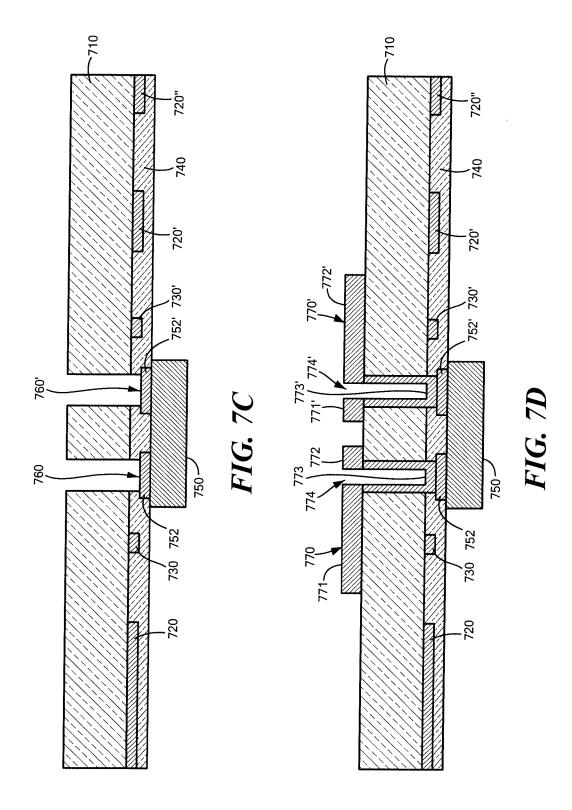

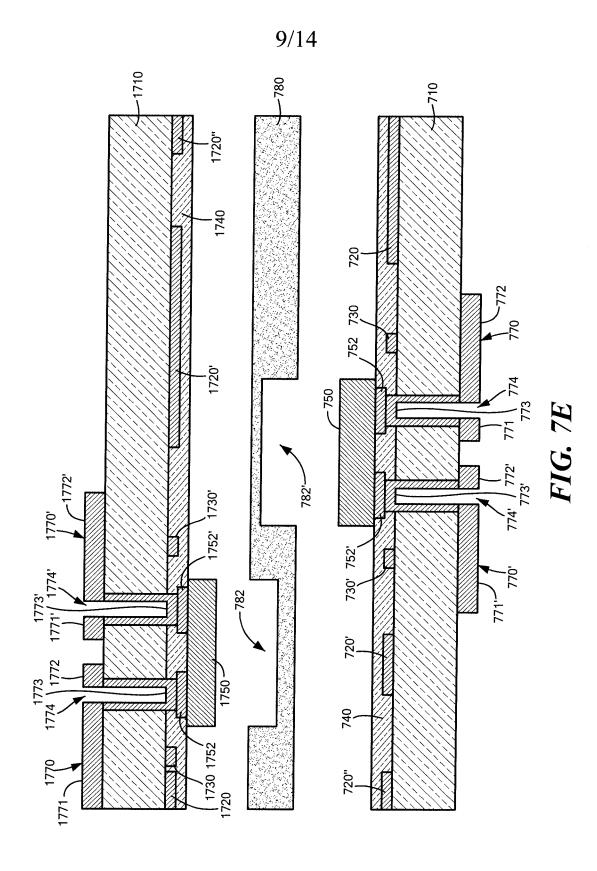

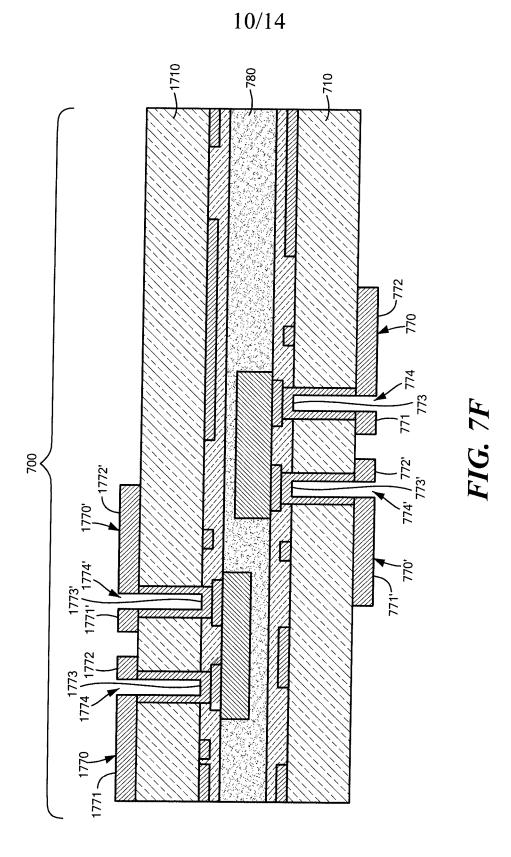

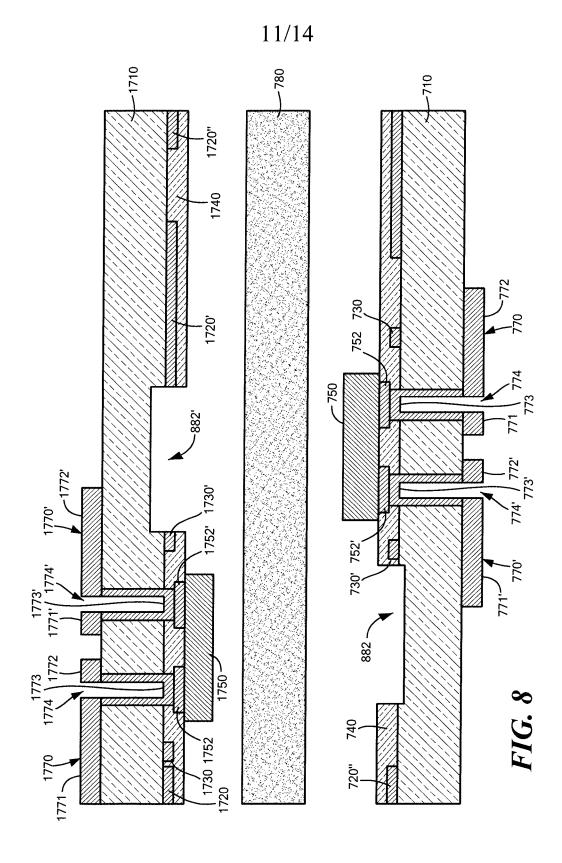

[0041] Figs. 7-7F are example semiconductor structures as may be provided in an example method for fabricating a substrate joining layer in accordance with an embodiment;

[0042] Fig. 8 is a block diagram of example semiconductor structures;

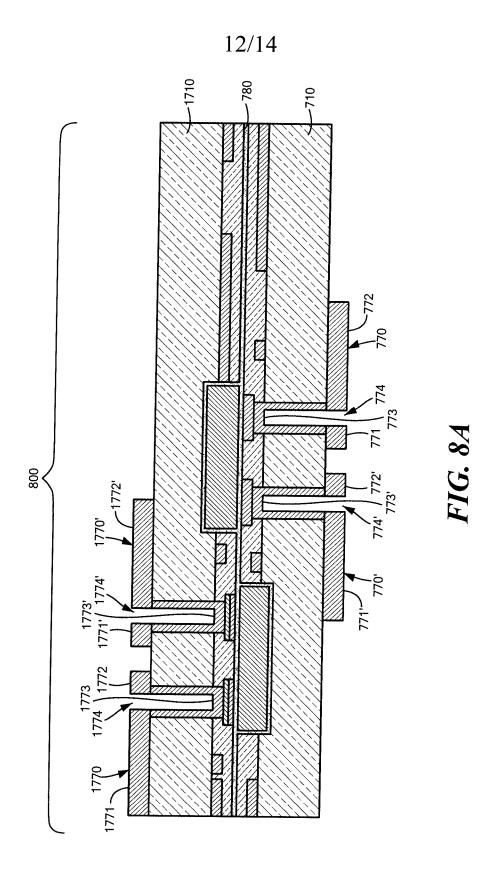

[0043] Fig. 8A is a block diagram of an example substrate joining layer including the semiconductor structures of Fig. 8, for example;

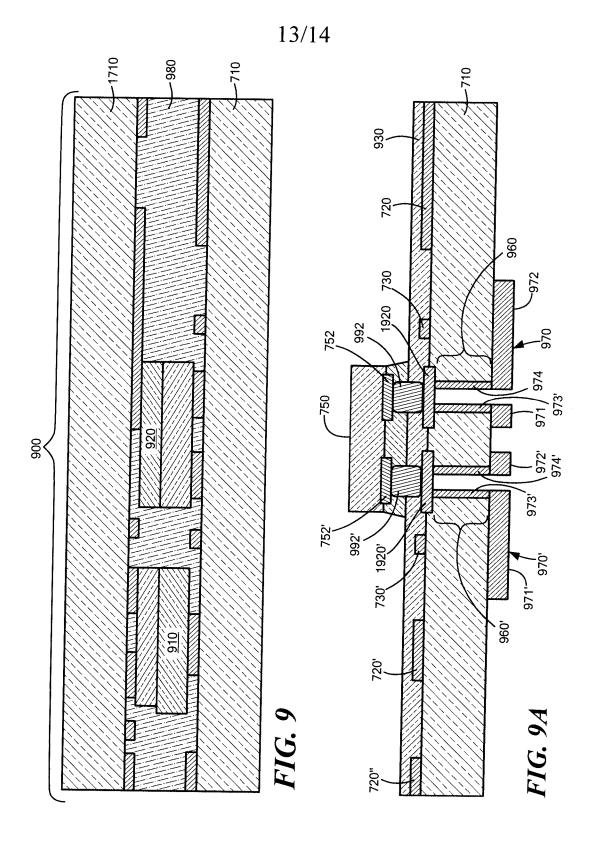

[0044] Fig. 9 is a block diagram of an example substrate joining layer;

[0045] Fig. 9A is a block diagram of an example semiconductor structure as may be provided in an example method for fabricating a substrate joining layer in accordance with an embodiment; and

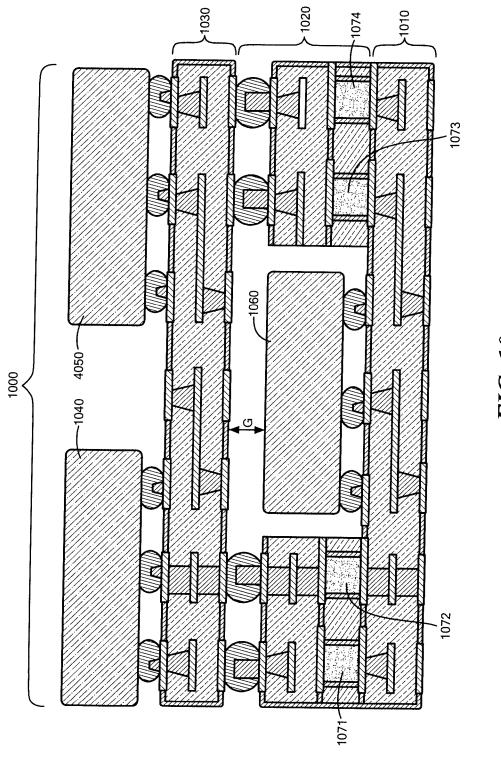

[0046] Fig. 10 is a block diagram of an example semiconductor structure.

#### **DETAILED DESCRIPTION**

[0047] The features and other details of the concepts, systems, and techniques sought to be protected herein will now be more particularly described. It will be understood that any specific embodiments described herein are shown by way of illustration and not as limitations of the disclosure and the concepts described herein. Features of the subject matter described herein can be

employed in various embodiments without departing from the scope of the concepts sought to be protected. Embodiments of the present disclosure and associated advantages may be best understood by referring to the drawings, where like numerals are used for like and corresponding parts throughout the various views.

#### **Definitions**

[0048] For convenience, certain introductory concepts and terms used in the specification are collected here.

[0049] As used herein, the term "circuitized substrate" is used to describe a semiconductor structure including at least one dielectric layer, the at least one dielectric layer having at least one surface on which at least one circuit is disposed. Examples of dielectric materials suitable for the at least one dielectric layer include low temperature co-fired ceramic (LTCC), ceramic (alumina), fiberglass-reinforced or non-reinforced epoxy resins (sometimes referred to simply as FR4 material, meaning its Flame Retardant rating), polytetrafluoroethylene (Teflon), polyimides, polyamides, cyanate resins, photoimagable materials, and other like materials, or combinations thereof. Examples of electrically conductive materials suitable for the at least one circuit include copper and copper alloy. If the dielectric layer is provided from a photoimagable material, it is photoimaged or photopatterned, and developed to reveal the desired circuit pattern, including the desired opening(s) as defined herein, if required. The dielectric layer may be curtain coated or screen applied, or it may be supplied as a dry film or in other sheet form.

[0050] As used herein, the term "conductive fusible metal" is used to describe a metal including one or more of tin-lead, bismuth-tin, bismuth-tin-iron, tin, indium, tin-indium, indium-gold, tin-indium-gold, tin-silver, tin-gold, indium, tin-silver-zinc, tin-silver-zinc-copper, tin-bismuth-silver, tin-copper, tin-copper-silver, tin-indium-silver, tin-antimony, tin-zinc, tin-zinc-indium, copper-based

solders, and alloys thereof. The metals may change forms (e.g., from a solid to a liquid) during a bonding or a reflow process.

[0051] As used herein, the term "conductive structure" is used to describe an interconnect structure for electrically coupling one or more interconnect pads, electrical connections, components, devices, modules, and semiconductor structures and devices. Printed circuit boards (PCBs), laminate chip carriers (LCCs), and like organic products and structures, which may include one or more conductive structures, permit the formation of multiple circuits using minimum volume or space. Such typically comprise a stack of electrically conductive layers of signal, ground and/or power planes separated from each other by at least one layer including an organic dielectric material (i.e., a dielectric layer). The planes may be in electrical contact with each other by plated holes passing through the dielectric layer(s). The plated holes are often referred to as vias if internally located, blind vias if extending a predetermined depth within the product or structure (e.g., PCB, LCC) from an external surface, or plated thru-holes (PTHs) if extending substantially through the product's or structure's full thickness. The term thru-hole as used herein is used to describe and meant to include vias, blind vias, and PTHs.

[0052] As used herein, the term "electronic device" is used to describe an integrated circuit (IC) device (e.g., a semiconductor chip).

[0053] As used herein, the term "interposer" is used to describe an interconnect structure capable of electrically coupling two or more semiconductor structures together.

[0054] As used herein, the term "module" is used to describe an electrical component having a substrate (e.g., a silicon substrate or printed circuit board (PCB)) on which at least one semiconductor device is disposed. The module may include a plurality of conductive leads adapted for coupling the module to electrical circuitry and/or electrical components located externally of the

module. One known example of such a module is a Multi-Chip Module (MCM), such modules coming in a variety of shapes and forms. These can range from pre-packaged chips on a PCB (to mimic the package footprint of an existing chip package) to fully custom chip packages integrating many chips on a High Density Interconnection (HDI) substrate.

[0055] As used herein, the term "processor" is used to describe an electronic circuit that performs a function, an operation, or a sequence of operations. The function, operation, or sequence of operations can be hard coded into the electronic circuit or soft coded by way of instructions held in a memory device. A "processor" can perform the function, operation, or sequence of operations using digital values or using analog signals.

[0056] In some embodiments, the "processor" can be embodied, for example, in a specially programmed microprocessor, a digital signal processor (DSP), or an application specific integrated circuit (ASIC), which can be an analog ASIC or a digital ASIC. Additionally, in some embodiments the "processor" can be embodied in configurable hardware such as field programmable gate arrays (FPGAs) or programmable logic arrays (PLAs). In some embodiments, the "processor" can also be embodied in a microprocessor with associated program memory. Furthermore, in some embodiments the "processor" can be embodied in a discrete electronic circuit, which can be an analog circuit or digital circuit.

[0057] As used herein, the term "substrate" is used to describe any structure upon which an integrated circuit or semiconductor device can be disposed or upon which semiconductor materials can be deposited and/or into which semiconductor materials can be implanted and diffused to form a semiconductor structure or device, for example. In some embodiments, the substrate may be provided as a P-type substrate (i.e., a substrate) having a particular range of concentrations of P-type atoms (i.e., ions). In other

embodiments an N-type substrate may be used (i.e., a substrate having a particular range of concentration of N-type atoms).

[0058] The substrate may, for example, be provided from a semiconductor material, an insulator material or even a conductor material. For example, the substrate may be provided from silicon, alumina, glass or any other semiconductor material. Further, the substrate can include a number of metal-oxide-silicon (MOS) devices, complementary-MOS (CMOS) devices, or a number of active or passive integrated circuit semiconductor devices.

[0059] Additionally, while semiconductor structures including first and second substrate layers which are the same as or similar to each other are described in several examples below, such are discussed to promote simplicity, clarity and understanding in the drawings as well as in the written description of the broad concepts, systems, circuits and techniques sought to be protected herein and is not intended to be, and should not be construed, as limiting. The concepts, systems, circuits and techniques disclosed herein may, of course, be implemented using first and second substrate layers which are different from each other.

[0060] Moreover, it should, of course, be appreciated that elements shown in the figures are not necessarily drawn to scale. For example, the dimensions of some elements may be exaggerated relative to other elements for clarity.

[0061] Referring now to Fig. 1, an example semiconductor structure 100 in accordance with the concepts, systems, circuits, and techniques sought to be protected herein is shown. The semiconductor structure 100 includes a first substrate layer 110, a second substrate layer 130 and a substrate joining layer 120. Each of the first and second substrate layers 110, 130 (e.g. single or multilayer substrates) has first and second opposing surfaces and a plurality of electrical connections (e.g., micro vias and/or sub-micron vias) extending between the first and second surfaces. Additionally, each of the first and second

substrate layers 110, 130 includes one or more interconnect pads (e.g., 112) having first and second opposing surfaces and one or more sides.

[0062] First substrate layer 110 includes a first plurality of interconnect pads (here, interconnect pads 112, 112', 112") and a second plurality of interconnect pads (here, interconnect pads 114, 114', 114", 114", 114", 114"") in the illustrated embodiment. Each of interconnect pads 112, 112', 112", 112" (e.g., solderable metal pads) has a first surface which is disposed over or beneath select portions of the first surface of the first substrate layer 110, and each of interconnect pads 114, 114', 114", 114", 114"", 114"" has a first surface which is disposed over or beneath select portions of the second surface of the first substrate layer 110.

[0063] Interconnect pads 112, 114 are electrically coupled to first select ones of the electrical connections in the first substrate layer 110, interconnect pads 112', 114' are electrically coupled to second select ones of the electrical connections in the first substrate layer 110, and interconnect pads 114", 114" are electrically coupled to third select ones of the electrical connections in the first substrate layer 110. Additionally, interconnect pads 112", 114" are electrically coupled to fourth select ones of the electrical connections in the first substrate layer 110, and interconnect pads 112", 114" are electrically coupled to fifth select ones of the electrical connections in the first substrate layer 110.

[0064] Second substrate layer 130 also includes a first plurality of interconnect pads (here, interconnect pads 132, 132', 132", 132"') and a second plurality of interconnect pads (here, interconnect pads 134, 134', 134"', 134"'', 134"''') in the illustrated embodiment. Each of interconnect pads 132, 132', 132", 132"' has a first surface which is disposed over or beneath select portions of the first surface of the second substrate layer 130, and each of interconnect pads 134, 134'', 134''', 134'''', 134'''' has a first surface which is disposed over or beneath select portions of the second substrate layer 130.

[0065] Interconnect pads 132, 134 are electrically coupled to first select ones of the electrical connections in the second substrate layer 130, interconnect pads 132', 134' are electrically coupled to second select ones of the electrical connections in the second substrate layer 130, and interconnect pads 134", 134" are electrically coupled to third select ones of the electrical connections in the second substrate layer 130. Additionally, interconnect pads 132", 134" are electrically coupled to fourth select ones of the electrical connections in the second substrate layer 130, and interconnect pads 112", 114" are electrically coupled to fifth select ones of the electrical connections in the second substrate layer 130. In some embodiments, one or more the select ones (e.g., first select ones) of the electrical connections in the first and second substrate layers 110, 130 are the same as one or more of the other select ones (e.g., second select ones) of the electrical connections in the first and second layers 110, 130, respectively.

[0066] Substrate joining layer 120, which may be provided from a circuitized substrate, for example, has first and second opposing surfaces and a plurality of electrical connections extending between select portions of the first and second surfaces. The substrate joining layer 120 is disposed between and coupled to the second surface of the first substrate layer 110 and the first surface of the second substrate layer 130.

[0067] The substrate joining layer 120 includes a two-dimensional (2D) integrated circuit (IC) structure 160 and a three-dimensional (3D) IC structure 170 in the illustrated embodiment, each disposed (e.g., embedded) between the first and second surfaces of the substrate joining layer 120. In one embodiment, the substrate joining layer 120 is provided from a dielectric material (e.g., cured or uncured), the dielectric material having openings to accommodate each of the 2D IC structure 160 and 3D IC structure 170. Additionally, in one embodiment, the substrate joining layer 120 includes a plurality of dielectric layers (e.g., as may be provided from one or more dielectric materials). A first one of the dielectric layers may be a cured or

uncured dielectric layer with an opening, a second one of the dielectric layers may be a cured or partially cured dielectric layer disposed over a first select surface (e.g., a first surface) of each of the 2D IC structure 160 and 3D IC structure 170, and a third one of the dielectric layers may be a cured or partially cured dielectric layer disposed over a second select surface (e.g., a second surface) of each of the 2D IC structure IC and 3D IC structure 170. Further, in one embodiment, the process and materials used to embed a 3D IC structure (e.g., 170) in a substrate joining layer (e.g., 120) are substantially the same as the process and materials used to embed a 2D IC structure (e.g., 160) in the substrate joining layer, as will be discussed further below in conjunction with Figs. 7-7F, for example.

[0068] The 2D IC structure 160 has first and second opposing surfaces and includes a plurality of interconnect pads (here, interconnect pads 162, 162'). A first surface of interconnect pad 162 is disposed over or beneath the first surface of the 2D IC structure 160 and a second opposing surface of interconnect pad 162 is electrically coupled to select ones (here, second select ones) of the electrical connections in the substrate joining layer 120. Additionally, a first surface of interconnect pad 162' is disposed over or beneath the first surface of the 2D IC structure 160 and a second opposing surface of interconnect pad 162' is electrically coupled to select ones (here, third select ones) of the electrical connections in the substrate joining layer 120.

[0069] The 2D IC structure 160 also includes a plurality of interconnects (here, interconnects 163, 163'), each of which may be provided as a pad interconnect (e.g., 770, as will be discussed). Interconnect 163 has a first portion which is electrically coupled to the second surface of interconnect pad 162 of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114' of the first substrate layer 110. Additionally, interconnect 163' has a first portion which is electrically coupled to the second surface of interconnect pad 162' of 2D IC structure 160 and a

second opposing portion which is electrically coupled to the second surface of interconnect pad 114" of the first substrate layer 110.

[0070] The 3D IC structure 170 has first and second opposing surfaces and includes a plurality of interconnect pads (here, interconnect pads 172, 172'). A first surface of interconnect pad 172 is disposed over or beneath the first surface of the 3D IC structure 170 and a second opposing surface of interconnect pad 172 is electrically coupled to select ones (here, fourth select ones) of the electrical connections in the substrate joining layer 120. Additionally, a first surface of interconnect pad 172' is disposed over or beneath the first surface of the 3D IC structure 170 and a second opposing surface of interconnect pad 172' is electrically coupled to select ones (here, fifth select ones) of the electrical connections in the substrate joining layer 120.

[0071] Similar to 2D IC structure 160, the 3D IC structure 170 also includes a plurality of interconnects (here, interconnects 173, 173'), each of which may be provided as a pad interconnect (e.g., 770, as will be discussed). Interconnect 173 has a first portion which is electrically coupled to the second surface of interconnect pad 172 of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114''' of the first substrate layer 110. Additionally, interconnect 173' has a first portion which is electrically coupled to the second surface of interconnect pad 172' of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114'''' of the first substrate layer 110.

[0072] In one embodiment, a predetermined distance between about one hundred micron and about five hundred micron exists between the first and second surfaces of the substrate joining layer 120, with the predetermined distance corresponding to a height (i.e., thickness) of the substrate joining layer 120. Additionally, in one embodiment the 2D IC structure 160 (e.g., a 2D IC structure including one device layer and an interconnect) can be replaced by a 3D IC structure (e.g., 170) without substantially changing the height of the

substrate joining layer 120. As one example, the 2D IC structure 160 may have a height of about one hundred fifty micron and may require a substrate joining layer 120 having a height of between about one hundred seventy five micron and about two hundred micron. A substrate joining layer (e.g., 120) having the same height can be used to embed an about one hundred sixty two micron 3D IC structure, for example, which has two extra device layers. One example 3D IC structure suitable for the 3D IC structure is described in in co-pending U.S. Patent Application No. 14/694,540 entitled "Interconnect Structures For Fine Pitch Assembly Of Semiconductor Structures," which is assigned to the assignee of the present disclosure and incorporated herein by reference in its entirety. Another example 3D IC structure suitable for the 3D IC structure is described in co-pending International Application No. PCT/US2015/044608 entitled "Interconnect Structures For Assembly of Multi-layer Semiconductor Devices," which is assigned to the assignee of the present disclosure and incorporated herein by reference in its entirety.

[0073] In the illustrated embodiment, a first predetermined distance (e.g., one hundred micron) exists between the second surface of 2D IC structure 160 and the second surface of substrate joining layer 120. Additionally, a second predetermined distance (e.g., five hundred micron) exists between the second surface of 3D IC structure 170 and the second surface of substrate joining layer 120. The first and second predetermined distances may, for example, be selected to accommodate for height (i.e., thickness) differences between 2D IC structure 160 and 3D IC structure 170. In some embodiments, the first and second predetermined distances are substantially the same.

[0074] The semiconductor structure 100 additionally includes a 2D IC structure 140 and a 3D IC structure 150 disposed over the second surface of the second substrate layer 130 in the illustrated embodiment. The 2D IC structure 140, which may be the same as or similar to 2D IC structure 160 in some embodiments, has first and second opposing surfaces and a plurality of interconnect pads (here, interconnect pads 142, 142'). A first surface of

interconnect pad 142 is disposed over or beneath the first surface of the 2D IC structure 140 and a second opposing surface of interconnect pad 142 is electrically coupled to the second surface of interconnect pad 134' of the second substrate layer 130. Additionally, a first surface of interconnect pad 142' is disposed over or beneath the first surface of the 2D IC structure 140 and a second opposing surface of interconnect pad 142' is electrically coupled to the second surface of interconnect pad 134" of the second substrate layer 130.

[0075] The 3D IC structure 150, which may be the same as or similar to 3D IC structure 170 in some embodiments, has first and second opposing surfaces and a plurality of interconnect pads (here, interconnect pads 152, 152'). A first surface of interconnect pad 152 is disposed over or beneath the first surface of the 3D IC structure 150 and a second opposing surface of interconnect pad 152 is electrically coupled to the second surface of interconnect pad 134''' of the second substrate layer 130. Additionally, a first surface of interconnect pad 152' is disposed over or beneath the first surface of the 3D IC structure 150 and a second opposing surface of interconnect pad 152' is electrically coupled to the second surface of interconnect pad 134''' of the second substrate layer 130.

[0076] In the example embodiment shown, interconnect pads 142, 142' of the 2D IC structure 140 and interconnect pads 152, 152' of the 3D IC structure 150 are electrically coupled to the interconnect pads 132, 132', 132", 132"' of the second substrate layer 130 through fusible coupling structures 181, 182, 183, 184 (e.g., solder balls, self-aligned contact pads) which are disposed between the second surfaces of interconnect pads 142, 142', 152, 152' and interconnect pads 132, 132', 132'', respectively. The fusible coupling structures 181, 182, 183, 184 may, for example, form a ball grid array (BGA) type package on the second surface of the second substrate layer 130.

Those of ordinary skill in the art will understand how to select the size, shape and electrically conductive materials of fusible coupling structures 181, 182,

183, 184 for a particular application (e.g., based on pitch and assembly risk sites). Example electrically conductive materials for fusible coupling structures 181, 182, 183, 184 include, but are not limited to: copper, aluminum, gold/nickel/Cu, gold/platinum/Titanium/Al, conductive fusible metals, and/or other suitable electrically conductive materials.

[0077] In some embodiments, substrate joining layer 120 electrically couples the second substrate layer 130 to the first substrate layer 110 such that one or more electrical connections are formed between the first substrate layer 110 and the second substrate layer 130 (e.g., as illustrated by the electrical connection formed between interconnect pad 112 of the first substrate layer 110 and interconnect pad 134 of the second substrate layer 130, and by the electrical connection formed between interconnect pad 112" of the first substrate layer 110 and interconnect pad 134"" of the second substrate layer 130).

[0078] Additionally, in some embodiments, substrate joining layer 120 is formed on the second surface of the first substrate layer 110. Additionally, in some embodiments, substrate joining layer 120 is formed on the first surface of the second substrate layer 130.

[0079] Further, in some embodiments, the semiconductor structure 100 discussed above and one or more of the semiconductor structures of Figs. 2-10 discussed below may include or be provided as part of a system such as a telecommunication system (e.g., in a handset or base station) or an information technology system or a circuit such as a filter circuit (e.g., a tunable radio-frequency (RF) filter circuit). The filter circuit may be integrated into a communications device.

[0080] Additional aspects of the concepts, systems, circuits and techniques sought to be protected herein, with particular emphasis on semiconductor

interconnect structures (e.g., substrate joining layers) are described in conjunction with the figures below.

[0081] Referring now to Fig. 2, an example semiconductor structure 200 similar to semiconductor structure 100 of Fig. 1 is shown. The semiconductor structure 200 includes a first substrate layer 210, a second substrate layer 230 and a substrate joining layer 220. The semiconductor structure 200 also includes a 2D IC structure 140 and a 3D IC structure 150.

[0082] The first substrate layer 210 includes a first plurality of interconnect pads (here, interconnect pads 112, 112', 112", 112"') and a second plurality of interconnect pads (here, interconnect pads 114, 114', 114", 114"', 114"'', 114"'''). Interconnect pads 112, 114 are electrically coupled to first select ones of the electrical connections in the first substrate layer 210, interconnect pads 112', 114' are electrically coupled to second select ones of the electrical connections in the first substrate layer 210, and interconnect pad 114" is electrically coupled to third select ones of the electrical connections in the first substrate layer 210. Additionally, interconnect pads 112", 114" are electrically coupled to fourth select ones of the electrical connections in the first substrate layer 210, interconnect pads 112", 114"" are electrically coupled to fifth select ones of the electrical connections in the first substrate layer 210, and interconnect pads 112"", 114"" are electrically coupled to sixth select ones of the electrical connections in the first substrate layer 210.

[0083] The second substrate layer 230 includes a first plurality of interconnect pads (here, interconnect pads 132, 132', 132'', 132''', 132'''') and a second plurality of interconnect pads (here, interconnect pads 134, 134', 134''', 134''''). Interconnect pads 132, 134 are electrically coupled to first select ones of the electrical connections in the second substrate layer 230, interconnect pads 132', 134' are electrically coupled to second select ones of the electrical connections in the second substrate layer 230, and interconnect pad 134'' is electrically coupled to third select ones of the electrical connections in the

second substrate layer 230. Additionally, interconnect pads 132", 114" are electrically coupled to fourth select ones of the electrical connections in the second substrate layer 230, interconnect pads 132", 114" are electrically coupled to fifth select ones of the electrical connections in the second substrate layer 230, and interconnect pads 132", 134" are electrically coupled to sixth select ones of the electrical connections in the second substrate layer 230.

[0084] The substrate joining layer 220 includes the 2D IC structure 160 and the 3D IC structure 170, each disposed (e.g., embedded) between the first and second surfaces of the substrate joining layer 120. The 2D IC structure 160 includes a plurality of interconnects (here, interconnects 163, 163'). Interconnect 163 has a first portion which is electrically coupled to the second surface of interconnect pad 162 of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114' of the first substrate layer 210. Additionally, interconnect 163' has a first portion which is electrically coupled to the second surface of interconnect pad 162' of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 162' of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114" of the first substrate layer 210.

[0085] The 3D IC structure 170, which is shown oriented in a different manner (i.e., rotated about one-hundred eighty degrees about the origin of substrate joining layer 230) than the 3D IC structure 170 shown in Fig. 1, for example, includes a plurality of interconnects (here, interconnects 173, 173'). Interconnect 173 has a first portion which is electrically coupled to the second surface of interconnect pad 172 of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 132" of the second substrate layer 230. Additionally, interconnect 173' has a first portion which is electrically coupled to the second surface of interconnect pad 172' of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 132" of the second substrate layer 230. It should, of course, be appreciated that 2D IC

structure 160 and the 3D IC structure 170 can be oriented and electrically coupled in any number of manners, as will be apparent by those of ordinary skill in the art.

[0086] In one embodiment, first substrate layer 210 and second substrate layer 230 can be prepared differently. As one example, one substrate layer (e.g., 210) can have a 2D IC structure, one substrate layer (e.g., 230) can have a 3D IC structure, and the two substrate layers (e.g., 210, 230) can be attached with substrate joining layer 220 using one or more approaches. In one embodiment, first and second substrate layers 210, 230 have Plated thorough holes (PTH) with external pads for attachment to the substrate joining layer 220 (and for forming an electrical connection between first and second substrate layers 210, 230). Additionally, in one embodiment, substrate joining layer 220 can have an uncured or partially cured conducting metal and/or alloy filled via which cured during bonding to create an electrical connection between first and second substrate layers 210, 230. Further, in one embodiment, substrate joining layer 220 and first and second substrate layers 210, 230 are coupled together, and then PTHs are created to form an electrical connection between first and second substrate layers 210, 230.

[0087] Additionally, it is further possible to use one or more pins (e.g., male/female connections or pins/sockets) to create the electrical connection. For example, second substrate layer 230 can have pins and first substrate layer 210 can have openings for the pins. In such embodiment, substrate joining layer 220 can have openings shaped according to the pins and/or openings of the second substrate layer 230 and the first substrate layer 210, for example. Alternatively, the substrate joining layer 220 can have pins for substrate 210 openings and openings for substrate 230 pins. In some instances, the pins and openings of substrate joining layer 220 can be connected such that an electrical connection is formed between substrate 210 and substrate 230.

[0088] Further according to one aspect of the concepts, systems, circuits and techniques sought to be protected herein, there is provided a method of making a circuitized substrate assembly (e.g., as shown in Figs. 1 and 2, and further described below). In such method, at least three circuitized substrate subassemblies (e.g., 110, 120, 130) are provided, each subassembly including at least one dielectric layer and at least one conductive layer including a plurality of metallic conductor pads (e.g., interconnect pads) as part thereof. At least some of these pads are attached to a 2D IC structure (e.g., 160) and/or a 3D IC structure (e.g., 170) using photolithographic plating processing and/or solder reflow and/or conductive paste curing or a combination thereof. Two or more such subassemblies are then aligned and laminated, using an interim organic so-called "pre-preg" layer to form a final multilayered assembly (e.g., 100). The circuitized substrate subassemblies are aligned relative to one another such that each of the metallic conductor pads of the first circuitized substrate subassembly (e.g., 110) are aligned with a corresponding metallic conductor pad of the second circuitized substrate subassembly (e.g., 120) in a facing manner, and such that each of the metallic conductor pads of the third circuitized substrate subassembly (e.g., 130) are aligned with a corresponding metallic conductor pad of the second circuitized substrate subassembly (e.g., 120), for example.

[0089] A flowable dielectric layer is positioned between each of the circuitized substrate subassemblies (e.g., 110, 120, 130), this flowable dielectric layer including a plurality of openings therein, each opening aligning with a respective pair of aligned and facing metallic conductor pads (e.g., interconnect pads) as well as the 2DIC (e.g., 160) and/or 3DIC (e.g., 170). A predetermined amount of a multilayer fusible metal paste and/or fusible metal coated single/multiple micro pillar is deposited on at least one of the metallic conductor pads of each of the pairs of aligned and facing metallic conductor pads. The circuitized substrate subassemblies are bonded together using heat and pressure so the metallurgies of the various layers of the fusible metal paste and metallic conductor pads are combined to form an electrical connection there

between and the material of the flowable dielectric layer flows into the openings to substantially fill the openings and surround the 2D IC structure and/or 3D IC structure and electrical connections.

[0090] The electrical connection of fusible metal as used herein is used to describe and meant to include a bondable (e.g., capable of lamination) conductive material which, when laminated, results in a new composition at the bonding interface and/or at the joining interface of interconnects. The fusible metal can include Cu, tin, and/or lead particles and other pastes containing tin and silver particles which can form high melting tin-silver-Cu (SAC) or tin-lead or a tin-copper solid solution at the interface during lamination. Tin and silver particles can form tin-silver-Cu (SAC) or tin-copper solid solution with a Cu or micro pillar pad during lamination. Dielectric materials, thickness and processing require to embed a 2D IC structure can be used to embed a 3D IC structure. Thus, it is possible to maintain a same or similar embedding layer thickness as well as overall package thickness for an embedded 3D IC structure and an embedded 2D IC structure. Circuitized substrates with at least one 2D IC structure may be replaced by a 3D IC structure without changing total substrate thickness. Additionally, circuitized substrates with at least two 2D IC structures and at least one 2D IC structure may be replaced by a 3D IC structure without changing total embedding layer as well total substrate thickness.

[0091] Referring now to Fig. 3, another example semiconductor structure 300 includes the first substrate layer 110, the second substrate layer 130 and a substrate joining layer 320. Semiconductor structure 300 also includes the 2D IC structure 140 and a 3D IC structure 150.

[0092] The substrate joining layer 320 includes the 2D IC structure 160, the 3D IC structure 170, and a plurality of interconnect structures (here, interconnect structures 301, 302, 303, 304, 305, 306), each disposed between the first and second surfaces of the substrate joining layer 320. Interconnect structures 301,

302, 303, 304, 305, 306 may be provided as fusible coupling structures (as shown), pad interconnects (e.g., 770, as will be discussed), or a combination thereof, for example. Similar to fusible coupling structures 181, 182, 183, 184 of Fig. 1, the size, shape and electrically conductive materials of interconnect structures 301, 302, 303, 304, 305, 306 may be selected to achieve a desired pitch, for example. As one example, a pitch of between about one hundred twenty five micron and about one hundred fifty micron may be achieved in semiconductor structure 300 when a distance between first and second opposing surfaces of the substrate joining layer 320 is about one hundred fifty micron, and a distance between first and second opposing surfaces of the 2D IC structure 160 and/or 3D IC structure 170 is about seventy micron (e.g., an about one-tothree ratio between the distance of the 2D IC structure 160 and/or 3D IC structure 170 and the distance of the substrate joining layer 120). The size, shape and electrically conductive materials of interconnect structures 301, 302. 303, 304, 305, 306 may, for example, be selected based on the distance between the first and second surfaces of the substrate joining layer 320 to achieve the desired pitch. Thus, a thinner 2D IC structure 160 and/or 3D IC structure 170 may result in a decreased distance between the first and second surfaces of the substrate joining layer 320, and favor a finer pitch semiconductor structure 300.

[0093] Interconnect structure 301 has a first portion which is electrically coupled to the second surface of interconnect pad 114 of first substrate layer 110 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 132 of second substrate layer 130. Additionally, interconnect structure 306 has a first portion which is electrically coupled to the second surface of interconnect pad 134" of first substrate layer 110 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 132" of second substrate layer 130.

[0094] In the illustrated embodiment, interconnect structure 301 and interconnect structure 306 each electrically couple the second substrate layer

130 to the first substrate layer 110 such that one or more electrical connections are formed between the first substrate layer 110 and the second substrate layer 130. A first electrical connection is formed between interconnect pad 112 of first substrate layer 110 and interconnect pad 134 of second substrate layer 130. Additionally, a second electrical connection is formed between interconnect pad 112" of first substrate layer 110 and interconnect pad" 134 of second substrate layer 130.

[0095] Interconnect structure 302, which may be the same as or similar to interconnect 163 of Fig. 1 in some embodiments, has a first portion which is electrically coupled to the second surface of interconnect pad 162 of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114' of the first substrate layer 110. Additionally, interconnect structure 303, which may be the same as or similar to interconnect 163' of Fig. 1 in some embodiments, has a first portion which is electrically coupled to the second surface of interconnect pad 162' of 2D IC structure 160 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114" of the first substrate layer 110.

[0096] Interconnect structure 304, which may be the same as or similar to interconnect 173 of Fig. 1 in some embodiments, has a first portion which is electrically coupled to the second surface of interconnect pad 172 of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114" of the first substrate layer 110. Additionally, interconnect structure 305, which may be the same as or similar to interconnect 173 of Fig. 1 in some embodiments, has a first portion which is electrically coupled to the second surface of interconnect pad 172 of 3D IC structure 170 and a second opposing portion which is electrically coupled to the second surface of interconnect pad 114" of the first substrate layer 110.

[0097] In the illustrated embodiment, a spacer material (e.g., a dielectric material) 390 exists between the second surface of 2D IC structure 160 and the

second surface of substrate joining layer 320. Additionally, a spacer material 390' exists between the second surface of 3D IC structure 170 and the second surface of substrate joining layer 320. The spacer materials 390, 390' may, for example, be selected to accommodate for height differences between 2D IC structure 160 and 3D IC structure 170. In one embodiment, instead of spacer materials 390, 390', a gap (i.e., a cavity) exists between second surfaces of 2D IC structure 160 and 3D IC structure 170.

[0098] Referring now to Fig. 4, another example semiconductor structure 400 includes the first substrate layer 210, the second substrate layer 230 and a substrate joining layer 320. Semiconductor structure 400 also includes the 2D IC structure 140 and a 3D IC structure 150.

[0099] The substrate joining layer 420 includes the 2D IC structure 160, the 3D IC structure 170, and a plurality of interconnect structures (here, interconnect structures 301, 302, 303, 304, 305, 306), each disposed between the first and second surfaces of the substrate joining layer 420. Interconnect structure 301 electrically couples the second surface of interconnect pad 214 of first substrate layer 210 to the second surface of interconnect pad 132 of second substrate layer 230. Additionally, interconnect structure 306 electrically couples the second surface of interconnect pad 214"" of first substrate layer 210 to the second surface of interconnect pad 214" of second substrate layer 230.

[00100] Interconnect structures 302, 303, which are disposed between the second surfaces of interconnect pads 162, 162' of 2D IC structure 160 and the second surfaces of interconnect pads 134', 134" of first substrate layer 210, respectively, electrically couple the second surfaces of interconnect pads 162, 162' to the second surfaces of interconnect pads 134', 134". Additionally, interconnect structures 304, 305, which are disposed between the second surfaces of interconnect pads 172, 172' of 3D IC structure 170 and the second surfaces of interconnect pads 232", 232" of second substrate layer 230,

respectively, electrically couple the second surfaces of interconnect pads 172, 172' to the second surfaces of interconnect pads 232", 232".