(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4646608号

(P4646608)

(45) 発行日 平成23年3月9日(2011.3.9)

(24) 登録日 平成22年12月17日(2010.12.17)

(51) Int.Cl.

F 1

G 11 C 17/00 (2006.01)

G 11 C 17/14 (2006.01)G 11 C 17/00

G 11 C 17/06C

B

請求項の数 6 (全 15 頁)

(21) 出願番号 特願2004-341880 (P2004-341880)

(22) 出願日 平成16年11月26日 (2004.11.26)

(65) 公開番号 特開2006-155710 (P2006-155710A)

(43) 公開日 平成18年6月15日 (2006.6.15)

審査請求日 平成19年11月8日 (2007.11.8)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

1回だけデータを書き込むことが可能な複数のデータ記憶セルと、

1回だけデータを書き込むことが可能な選択用記憶セルを有し、その選択用記憶セルに

書き込まれた内容に応じて、上記複数のデータ記憶セルのうちの何れかを選択して、選択

されたデータ記憶セルに書き込まれた内容に応じてデータを出力する読み出し選択回路と

、

1回だけデータを書き込むことが可能な選択用記憶セルを有し、上記選択用記憶セルに

書き込まれた内容に応じて、上記複数のデータ記憶セルのうちの何れかを選択してデータ

を書き込む書き込み選択回路と、を備え、

上記読み出し選択回路と上記書き込み選択回路とが同一の上記選択用記憶セルを兼用す

るように構成され、

上記兼用される読み出し選択回路および書き込み選択回路は、読み出しが行われるデータ記憶セルとは異なるデータ記憶セルを書き込み用に選択するように構成されていることを特徴とする半導体記憶装置。

## 【請求項 2】

請求項1の半導体記憶装置であって、

上記読み出し選択回路は、上記複数のデータ記憶セルから出力される信号のうちの何れかを選択して出力するように構成されていることを特徴とする半導体記憶装置。

## 【請求項 3】

10

20

請求項 1 の半導体記憶装置であって、

上記読み出し選択回路は、上記複数のデータ記憶セルのうちの何れかを選択して読み出し信号を与えるように構成されていることを特徴とする半導体記憶装置。

**【請求項 4】**

請求項 1 の半導体記憶装置であって、

上記書き込み選択回路の選択用記憶セルは複数設けられ、上記書き込み選択回路は、上記選択用記憶セルに書き込まれた内容に応じて、書き込みの行われるデータ記憶セルと共に、書き込み選択回路の選択用記憶セルを選択するように構成されていることを特徴とする半導体記憶装置。

**【請求項 5】**

請求項 1 の半導体記憶装置であって、

上記複数のデータ記憶セルを複数組備え、所定ビット長のデータを出力し得るように構成されていることを特徴とする半導体記憶装置。

**【請求項 6】**

請求項 5 の半導体記憶装置であって、

上記所定ビット長分のデータ記憶セルをさらに複数ワード分備え、上記読み出し選択回路は、アドレス信号に応じたワードのデータを出力するように構成されていることを特徴とする半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、FUSE 素子を用いて 1 回だけ記憶情報の書き換えが可能な OTP (One Time Program) 素子等と称される記憶素子を用いた不揮発メモリに関するものである。

**【背景技術】**

**【0002】**

近年、半導体の技術としては製造プロセスの微細化が進むとともに、ゲート酸化膜の薄膜化やゲート電極材料等の改変が進み、また、FLASH、EEPROM 等の書き換え用途デバイス等も大規模化、高集積化を遂げて技術的な進展をみている。この種のいわゆる不揮発メモリは、通常、長期間に亘る保持データの信頼性に対する要求が高く、また、フローティングゲートの形成などに、標準 CMOS プロセス以外の特殊な専用プロセスを必要とするため、製造コストも高くなりがちである。

**【0003】**

一方、半導体デバイスを使用するシステム分野でも、必要とするデバイスの用途が変わりつつある分野もあり、セキュリティー用途製品や IC-TAG 等のように不揮発メモリ素子または OTP 素子を内部に混載するケースも増加している。また、既存のシステムで言えば、システム LSI に混載するメモリ、アナログデバイス等においても冗長性付与またはアナログ回路のキャリブレーションなどのように、ウエハ工程での FUSE 素子での冗長救済や調整自体を組立工程以後に再調整することが必要とされる場合がある。特に素子の周波数におけるパフォーマンスが高い場合には、ウエハでのプローブ工程における低周波数テストから組立て後の実周波数テストでのミスマッチから後工程での調整を余儀なくされる場合が存在する。すなわち、プローブを当てること自体の影響による調整精度の低下を補うために、パッケージング後に微調整を行うことが有効な場合もある。

**【0004】**

上記のような用途に用いられる最近の OTP 用 FUSE 素子としては、書き込み回数が 1 回に限定される一方で、標準 CMOS プロセスでの製造が可能であるとともに、書き込みデータに対する信頼性が高いという利点などから、既存のメタルまたはポリシリコンをレーザーリペア装置で切断するレーザー FUSE や、FUSE 素子部分に電流を流して切断する電気 FUSE 等が用いられつつある（例えば、特許文献 1 参照。）。

**【0005】**

10

20

30

40

50

また、上記のようなOTP素子の利点を活かしつつ複数回の書き込みを可能にする技術として、複数のOTP素子の排他的論理和(XOR)演算を行うことにより、一旦書き込んだ状態を反転させることができるようにしたものも知られている(例えば、特許文献2参照。)。

【特許文献1】米国特許第6384664号明細書

【特許文献2】米国特許第5966339号明細書

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0006】

しかしながら、上記のように複数回の書き込みを可能にするためにXOR演算を行う構成では、書き込み可能な回数やビット数に応じた数のXOR回路を必要とするため、回路規模が大きくなるという問題点を有している。10

##### 【課題を解決するための手段】

##### 【0007】

上記の点に鑑み、本発明は、回路規模の大幅な増加を招くことなく、複数回の書き込みを可能にすることを目的とする。

##### 【0008】

上記の課題を解決するため、半導体記憶装置であって、

1回だけデータを書き込むことが可能な複数のデータ記憶セルと、

1回だけデータを書き込むことが可能な選択用記憶セルを有し、その選択用記憶セルに書き込まれた内容に応じて、上記複数のデータ記憶セルのうちの何れかを選択して、選択されたデータ記憶セルに書き込まれた内容に応じてデータを出力する読み出し選択回路と20

、

1回だけデータを書き込むことが可能な選択用記憶セルを有し、上記選択用記憶セルに書き込まれた内容に応じて、上記複数のデータ記憶セルのうちの何れかを選択してデータを書き込む書き込み選択回路と、を備え、

上記読み出し選択回路と上記書き込み選択回路とが同一の上記選択用記憶セルを兼用するように構成され、

上記兼用される読み出し選択回路および書き込み選択回路は、読み出しが行われるデータ記憶セルとは異なるデータ記憶セルを書き込み用に選択するように構成されていることを特徴とする。30

##### 【0009】

これにより、次に書き込まれるデータ記憶セルが選択されることによって、データの読み出されるデータ記憶セルへの書き込みができなくなるので、不用意に記憶内容が書き換わることが確実に防止される。

#### 【発明の効果】

##### 【0010】

本発明によれば、いわゆるOTPセルを有する半導体記憶装置において、回路規模の大幅な増加を招くことなく、複数回の書換を実施することができ、全ビット書換、個別ビット追記、アレイ型の書換を行うことができる。40

#### 【発明を実施するための最良の形態】

##### 【0011】

以下、本発明の実施形態を図面に基づいて詳細に説明する。なお、以下の各実施形態および各参考例において、他の実施形態および参考例と同様の機能を有する構成要素については同一の符号を付して説明を省略する。

##### 【0012】

#### 《発明の実施形態1》

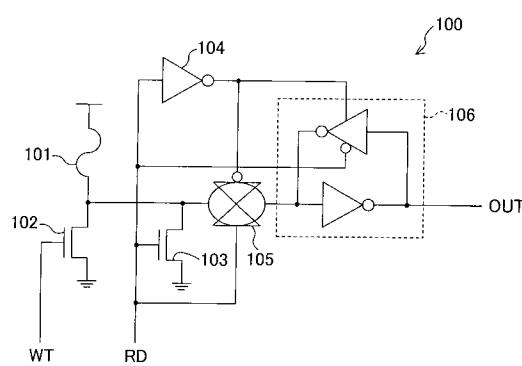

まず、図1に基づいて、本実施形態1の半導体記憶装置に用いられるビットセル100の例について説明する。同図において、

101は、所定の大きさの電流を流すことによって切断が可能なFUSE素子である。

50

## 【0013】

102は、書き込み信号(WT信号)がHigh(ハイレベル)になったときに、FUSE素子101に所定の大きさの電流を流して同素子を切斷するNchの書き込みトランジスタである。

## 【0014】

103は、読み出し信号(RD信号)がHighになったときに、FUSE素子101の切斷の有無に応じた電位をドレイン端子に生じさせるための読み出しトランジスタである。

## 【0015】

104は、上記RD信号の反転信号を出力するNOT回路である。 10

## 【0016】

105は、RD信号がHighである場合にON(導通状態)になる一方、Low(ローレベル)である場合にOFF(遮断状態)になるトランスマニアゲート回路である。

## 【0017】

106は、RD信号がHighになったときに書き込みトランジスタ102のドレイン端子に生じる電位に応じた信号レベル、すなわちFUSE素子101の切斷の有無に応じた信号レベル(書き込みデータ)を上記RD信号がLowの間ラッチし、OUT信号として出力するラッチ回路である。なお、このラッチ回路106は必ずしも設けなくてよく、その場合でもRD信号をHighにしている間は書き込みデータを読み出せるが、ラッチ回路106を設け、初期化動作として書き込みデータをラッチさせることによって、読み出しごとにFUSE素子101に電流を流す必要がなくなるので、消費電力の低減が容易になる。 20

## 【0018】

上記のように構成されたビットセル100では、WT信号がHighにされることによって、FUSE素子101が切斷される。

## 【0019】

また、RD信号が一旦Highにされた後にLowにされると(初期化動作)、FUSE素子101が切斷されていない場合には、読み出しトランジスタ103のドレイン端子がHighでOUT信号がLowになる一方、FUSE素子101が切斷されている場合には、読み出しトランジスタ103のドレイン端子がLowになってOUT信号がHighになる。 30

## 【0020】

すなわち、上記のようなビットセル100によって、1回だけ書き込み(書き換え)が可能な1ビットの不揮発メモリセルが構成される。

## 【0021】

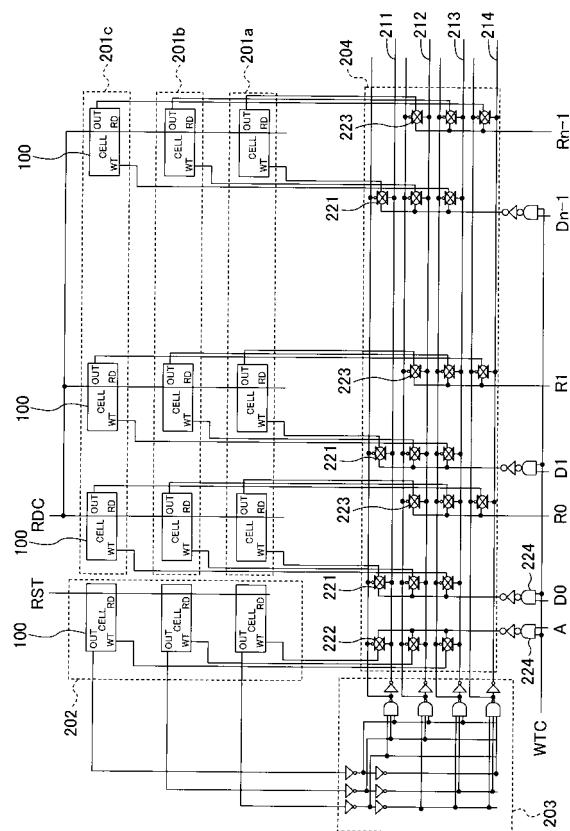

図2は、上記ビットセル100(CELL)を $3 \times (n + 1)$ 個用いて、nビットのデータを3回書き込むことができるよう構成された半導体記憶装置の例を示す回路図である。同図において、

201a～201cは、それぞれ、n個のビットセル100を含むデータビットセル群である。各ビットセル100のRD信号としては、外部から供給されるRDC信号が共通に入力されるようになっている。 40

## 【0022】

202は、3つのビットセル100を含み、上記データビットセル群201a～201cのうち、書き込みが有効なもの、および読み出しが有効なものを指定するセル群指定回路である。上記セル群指定回路202に含まれる各ビットセル100のRD信号としては、外部から供給されるRST信号が共通に入力されるようになっている。

## 【0023】

203は、セル群指定回路202の出力をデコードして、選択信号211～214、およびこれらの反転信号を出力するデコード回路である(なお、以下、反転信号についての説明は適宜省略する。)。 50

## 【0024】

204は、デコード回路203から出力される選択信号211～214に応じてトランスマゲート221～223がON/OFFすることによって、データを書き込むビットセル100、および読み出すビットセル100を選択するセレクタ回路である。

## 【0025】

上記のように構成された半導体記憶装置では、まず、各ビットセル100に入力されるRST信号およびRDC信号がHighにされることによって初期化動作が行われ、各ビットセル100からFUSE素子101の状態に応じたOUT信号が出力される。

## 【0026】

これによって、セル群指定回路202では、例えば何れのビットセル100もFUSE素子101が切断されていなかったとすると、各ビットセル100からLowのOUT信号が出力されるので、これらのOUT信号がデコード回路203でデコードされて、選択信号211がHighになる。

## 【0027】

上記選択信号211がHighの状態で、書き込み制御信号WTCがHighになるとともに、書き込みデータ信号D0～Dn-1（のうちの少なくとも一部）がHighになると、AND回路224およびセレクタ回路204のトランスマゲート221からデータビットセル群201aに入力されるWT信号のうち、Highになった書き込みデータ信号D0～Dn-1に対応するWT信号がHighになる。そこで、データビットセル群201aに含まれるビットセル100のFUSE素子101が切断されることによって、データの書き込みが行われる。

## 【0028】

また、同様に、上記データビットセル群201aへの書き込みと同時に、または別途、書き込み制御信号WTCがHighになるとともに書き込み完了信号AがHighになると、AND回路224およびセレクタ回路204のトランスマゲート222から、セル群指定回路202における図2の一番下側のビットセル100に入力されるWT信号がHighになる。そこで、上記ビットセル100のFUSE素子101が切断され、その後RST信号による初期化が行われると、OUT信号がHighになり、デコード回路203から出力される選択信号212がHighになる。これによって、データビットセル群201aの各ビットセル100から出力されるOUT信号が、セレクタ回路204のトランスマゲート223を介して、読み出しデータ信号R0～Rn-1として出力される。

## 【0029】

また、上記のように選択信号212がHighになった状態では、書き込み制御信号WTCがHighになると、書き込みデータ信号D0～Dn-1に応じたデータが、データビットセル群201bに書き込まれる。

## 【0030】

以下、同様に、セル群指定回路202における各ビットセル100のFUSE素子101の切断に応じて、データビットセル群201bからの書き込みデータの読み出し、データビットセル群201cへの書き込み等が行われ、合計で3回のデータの書き込みをすることができる。

## 【0031】

## 《発明の実施形態2》

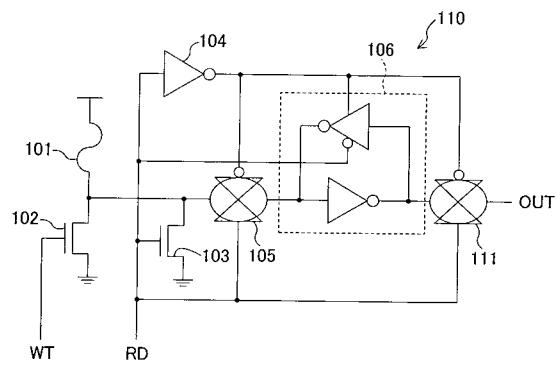

本実施形態2の半導体記憶装置で記憶データの保持に用いられるビットセル110は、図3に示すように、OUT信号として、前記実施形態1のビットセル100と同様の回路にトランスマゲート111が接続され、RD信号がHighレベルの場合にだけ、ラッチ回路106に保持されている信号が出力されるようになっている。

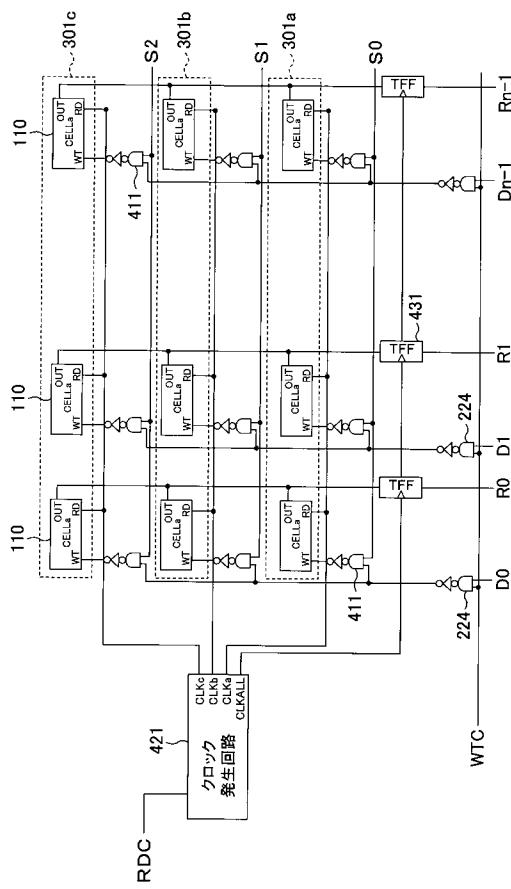

## 【0032】

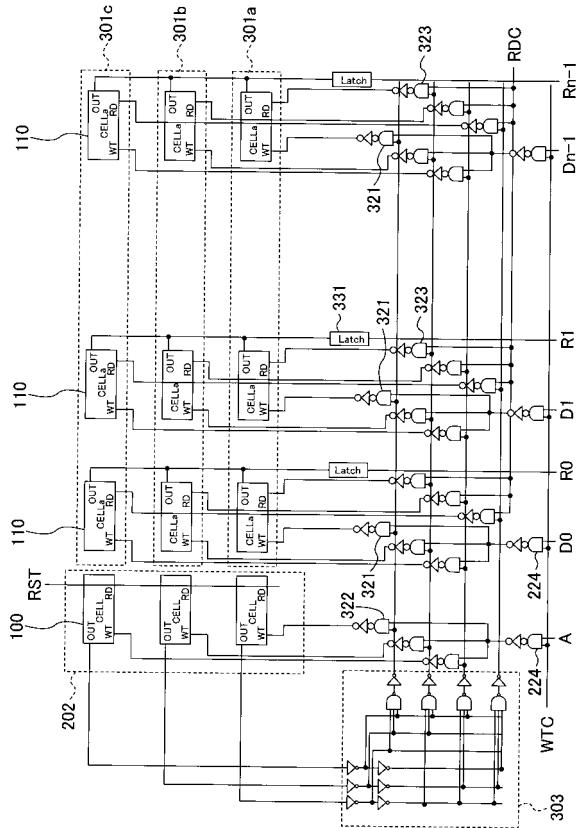

半導体記憶装置には、図4に示すように、上記ビットセル110（CELLa）を3×n個有するデータビットセル群301a～301cが設けられている。これらに対して書き込みおよび読み出しが有効なものを指定するセル群指定回路202は、前記実施形態1

10

20

30

40

50

と同じものである。

**【0033】**

デコード回路303は、実施形態1のデコード回路203と同様の構成を有しているが、反転信号は出力されない点が異なる。

**【0034】**

上記デコード回路303からの出力に応じたデータビットセル群301a～301cの書き込みや読み出し、およびセル群指定回路202の書き込みの制御は、AND回路321～323から出力されるWT信号およびRD信号によって行われるようになっている。

**【0035】**

また、データビットセル群301a～301cのうちの何れかのビットセル110から出力されるOUT信号は、ラッチ回路331によって保持されるようになっている。

**【0036】**

上記のように構成された半導体記憶装置では、セル群指定回路202の初期化時の動作、および各ビットセル100・110にデータが書き込まれるときの動作は、実施形態1の半導体記憶装置とほぼ同様である。すなわち、セル群指定回路202の各ビットセル100は、RD信号として入力されるRST信号がHighになると初期化されて記憶データを出力し、これに基づいて、デコード回路303から出力される何れかの選択信号がHighになる。そこで、書き込み制御信号WTCがHighになるとともに、書き込みデータ信号D0～Dn-1または書き込み完了信号AがHighになると、AND回路321・322からデータビットセル群301a～301cまたはセル群指定回路202のビットセル110・100に入力されるWT信号がHighになる。そこで、上記ビットセル110・100のFUSE素子101が切断されることによって、データの書き込みが行われる。

**【0037】**

一方、記憶データの読み出しのための初期化動作が行われるときには、RDC信号がHighにされると、デコード回路303から出力される選択信号のうちHighになる選択信号が入力されるAND回路323から出力されるRD信号がHighになる。すなわち、データビットセル群301a～301cのうちの何れかに含まれるビットセル110だけに入力されるRD信号がHighになる。そこで、そのビットセル110におけるFUSE素子101の切断の有無に応じたOUT信号が出力され、図示しないラッチ信号に応じてラッチ回路331にラッチされることにより、読み出しデータ信号R0～Rn-1として半導体記憶装置から出力される。

**【0038】**

上記のように、記憶データ読み出しのための初期化動作時に、全てのビットセル110に入力されるRD信号がHighにされるのではなく、デコード回路303による選択に応じたデータビットセル群201a～201cの何れかのビットセル110に入力されるRD信号だけがHighにされることによって、初期化動作時に流れる電流を小さく抑えることができる。

**【0039】**

**《参考例1》**

図5は、参考例1の半導体記憶装置の構成を示す回路図である。この半導体記憶装置は、各ビットごとに、3つのビットセル110のうちで何本のFUSE素子101が切断されているかによって、データが記憶されるようになっている。

**【0040】**

具体的には、この半導体記憶装置には、実施形態2の半導体記憶装置と同じく $3 \times n$ 個のビットセル110が設けられ、図5で上下方向に並べて示す3個ずつのビットセル110から出力されるOUT信号がTフリップフロップ431に入力されるようになっている。上記各ビットセル110には、RD信号として、クロック発生回路421から出力されるクロック信号CLKa～CLKcが入力される一方、Tフリップフロップ431には、上記クロック信号CLKa～CLKcが合成されたクロック信号CLKALLが入力され

10

20

30

30

40

50

るようになっている。

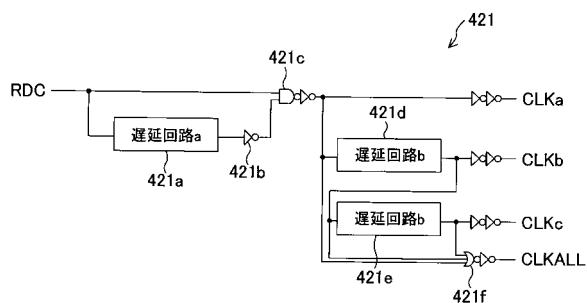

#### 【0041】

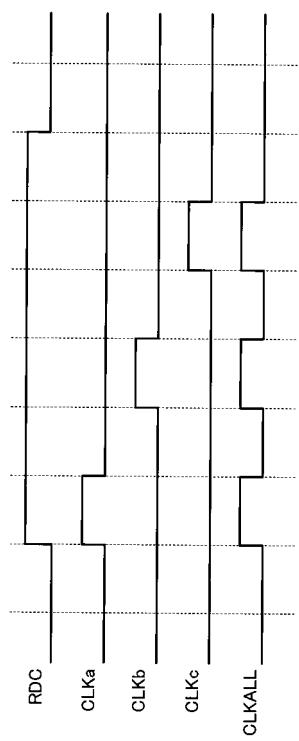

上記クロック発生回路421は、詳しくは、例えば図6に示すように、遅延回路421a、NOT回路421b、AND回路421c、遅延回路421d・421e、およびOR回路421fを備えて構成され、図7に示すように、所定の期間HighになるRDC信号に基づいて、1ショットパルスの生成、遅延、およびこれらの合成によって、各クロック信号を出力するようになっている。

#### 【0042】

また、各ビットセル110のWT信号としては、AND回路411の出力が用いられている。上記AND回路411には、WTC信号と書き込みデータ信号D0～Dn-1との論理積、および選択信号S0～S2が入力されるようになっている。10

#### 【0043】

上記のように構成された半導体記憶装置の動作について、まず、読み出し動作を説明する。遅延回路421aに入力されるRDC信号がHighになると、クロック信号CLKa～CLKcが順次Highになり、データビットセル群301a～301cに含まれるビットセル110が順に出力状態となる。すなわち、各ビットセル110からは、FUSE素子101が切斷されている場合に、HighのOUT信号が出力される。Tフリップフロップ431は、クロック信号CLKALLが立ち上がる際に上記OUT信号がHighであるごとに、反転された信号を出力する。そこで、各3個のビットセル110のうちのFUSE素子101が切斷されている数に応じたレベルの読み出しデータ信号R0～Rn-1が出力される。20

#### 【0044】

一方、この半導体記憶装置への書き込みは、出力される信号のレベルを反転させようとするビットの書き込みデータ信号D0～Dn-1、およびWTC信号をHighにするとともに、各ビット用の3つのビットセル110のうち、未だFUSE素子101が切斷されていないビットセル110に対応する選択信号S0～S2をHighにして、AND回路411から出力されるWT信号をHighにすることによって行われる。すなわち、前記のように、読み出しデータ信号R0～Rn-1のレベルは各3個のビットセル110のうちの何本のFUSE素子101が切斷されているかによって定まり、何れのFUSE素子101が切斷されているかには直接関係ないので、各ビットごとに3回まで、出力される信号が反転されるように書き換えることができる。30

#### 【0045】

上記のように、各ビットごとに切斷したFUSE素子101の数によってデータを記憶させることにより、書き換え回数がより柔軟になる。また、各ビットごとの書き換え回数に応じた数のビットセル110と、その数だけの相数のクロック信号が生成されるようなクロック発生回路とを設ければよいので、回路規模、および半導体基板の面積を小さく抑えられることが容易にできる。

#### 【0046】

##### 《参考例2》

上記参考例1の半導体記憶装置のように、切斷したFUSE素子の数によってデータを記憶させる場合、書き込みの前後で出力信号が反転するビットについてのFUSE素子が切斷されればよい。そこで、書き込み前に出力される信号レベルと、書き込み後に出力されるべき信号レベルとを比較して、両者が相違する場合にだけWT信号がHighになるようすれば、書き込み後に出力されるべき信号レベルを指定するだけで（書き込み前の状態をユーザが考慮することなく）、適切な書き込みを行わせることができる。また、出力信号を反転させる場合には、未切斷のFUSEのうちの何れかが切斷されればよいので、各ビットセルのFUSE切斷の有無に応じて、自動的に、次に切斷するビットセルに入力されるWT信号がHighになるようにすることにより、選択信号S0～S2を入力することなく、すなわち、何れのビットセルのFUSEを切斷するかをユーザが意識することなく、書き込みを行えるようにすることができる。4050

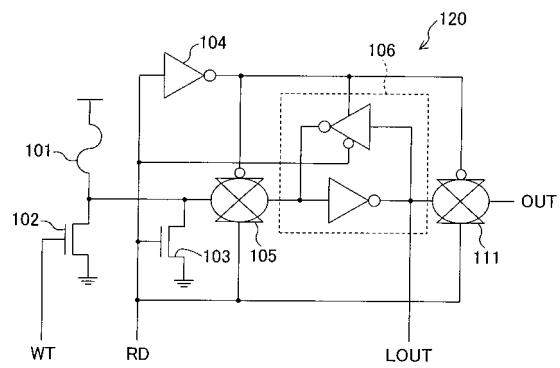

## 【0047】

具体的には、本参考例2の半導体記憶装置で記憶データの保持に用いられるビットセル120は、図8に示すように、実施形態2(図3)のビットセル110におけるラッチ回路106の出力が(トランスマルチエレメント111を介さずに)LOUT信号として出力されるようにしたものである。

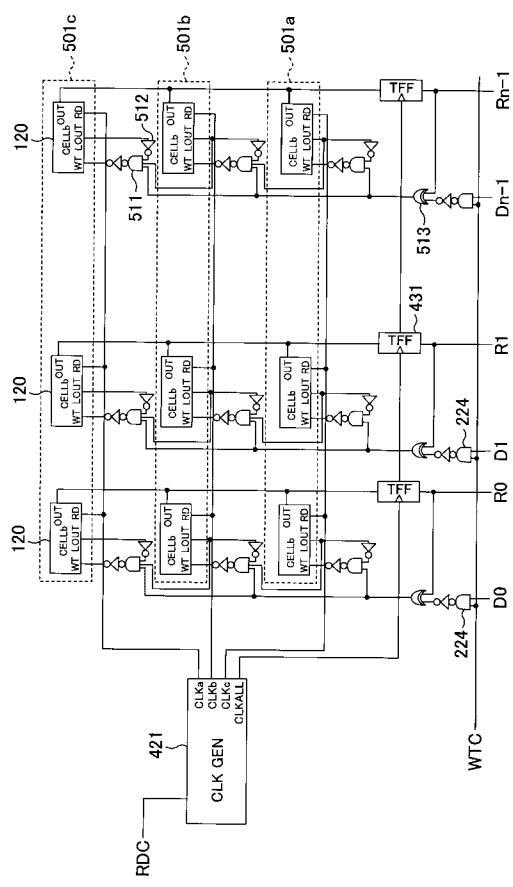

## 【0048】

上記ビットセル120(CELLb)が用いられる半導体記憶装置は、図9に示すように、各ビットごとに、AND回路224の出力とTフリップフロップ431の出力とがXOR回路513に入力され、両者が相違する場合にHighになる信号が生成されるようになっている。

10

## 【0049】

また、上記XOR回路513の出力と、各ビットセル120のLOUT信号がNOT回路512で反転された信号と、前段の(図9で各1つ下側に示す)ビットセル120のLOUT信号とが、AND回路511に入力されて、WT信号が生成されるようになっている。

## 【0050】

上記のように構成されることによって、各ビットごとに、現時点の読み出しデータと書き込みデータとが異なる場合に、FUSE素子101の切断が行われる。また、各ビット用のビットセル120のうち、切断が行われるビットセル120としては、FUSE素子101が未切断のビットセル120であって、前段のビットセル120のFUSE素子101が既に切断されているものが選択される。したがって、書き込むべきデータが入力されるだけで、自動的に適切なビットセル120のFUSE素子101が切断されて、追加書き込みが完了する。

20

## 【0051】

上記のようにしてデータが書き込まれた場合の各ビットセル120の状態は、前記参考例1の半導体記憶装置の場合と同様であり、読み出し動作は、やはり同様にRDC信号がHighになることによって行われる。

## 【0052】

## 《発明の実施形態3》

前記各実施形態および前記各参考例では、nビットのデータが記憶、読み出しされる半導体記憶装置の例を示したが、同様のデータビットセル群を複数組設け、アドレス信号に応じて複数ワードのデータが選択的に記憶、読み出しされるようにしてもよい。

30

## 【0053】

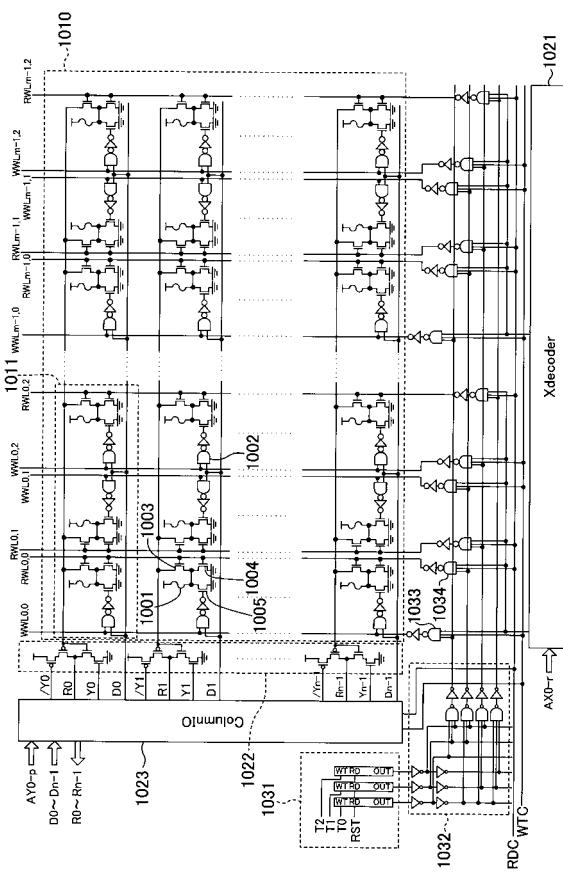

具体的には例えば図10に示すように、実施形態3の半導体記憶装置のメモリセルアレイ1010には、3回書き込み可能なデータビットセル群1011がn個(nビット)×m組設けられている。各データビットセル群1011は、それぞれ3つずつのFUSE素子1001、AND回路1002、読み出しへトランジスタ1003・1004、および書き込みトランジスタ1005を備えて構成されている。

## 【0054】

上記n個×m組のデータビットセル群1011のうちの何れの組のデータビットセル群1011が選択されるかは、デコード回路1021によるアドレス信号AX0-rのデコード結果に基づいて行われるようになっている。また、各データビットセル群1011内で何れのビットセルが用いられるかの選択は、実施形態1、2と同様に、セル群指定回路1031およびデコード回路1032によって生成される選択信号により行われるようになっている。すなわち、上記デコード回路1032から出力される選択信号とデコード回路1021から出力されるデコード信号とがAND回路1033・1034に入力されて、書き込み信号WWL0,0または読み出し信号RWL0,0等が生成されるようになっている。ここで、同図の例では、セル群指定回路1031内のビットセルのWT信号としては、外部から入力される書き込み信号T0-T2が用いられる例を示しているが、これに限らず、実施形態1、2と同様にデコード回路1032のデコード結果に応じて自動的

40

50

に選択されるようにしてもよい。

**【0055】**

記憶データの読み出し時に、上記読み出し信号 R W L 0 , 0 等により選択されたビットセルから、読み出しトランジスタ 1003 を介してビット線に出力された電圧は、例えば Y 信号線により駆動される（活性・非活性が決められる）センスアンプ列 1022 によって所定の電位に増幅され、コラム I/O 回路 1023 を介してデコードやバッファリングされて、読み出しデータ信号 R 0 ~ R n - 1 として出力されるようになっている。

**【0056】**

また、データの書き込み時に上記書き込み信号 W W L 0 , 0 等により選択されたビットセルの F U S E 素子 1001 は、コラム I/O 回路 1023 を介して入力された書き込みデータ信号 D 0 ~ D n - 1 に基づき書き込みトランジスタ 1005 を介して流れる電流により切斷されるようになっている。

10

**【0057】**

上記のように、ビットセルをアレイ化することによって、実施形態 1、2 と同様にデータを 3 回書き込むことができるとともに、アドレス信号に応じて、m 組の n ビットデータのうちの何れかを選択的に読み出すことができる。

**【0058】**

なお、前記各実施形態および前記各参考例や下記の変形例で説明する構成要素は、論理的に可能な範囲で種々組み合わせてもよい。具体的には、例えば参考例 1, 2 で説明したような F U S E 素子 101 の切斷本数に応じたデータを出力するビットセル 120 をアレイ化して、実施形態 5 のようにアドレス信号に応じてデータを読み出せるようにしてもよい。

20

**【0059】**

また、実施形態 1 において、実施形態 2 と同様に、データビットセル群 201a ~ 201c のうち選択信号 211 ~ 214 に応じたものだけに、初期化のための R D C 信号が入力されるようにしてもよい。

**【0060】**

また、実施形態 1、2 においては、ビットセル 100 · 110 に入力される W T 信号を生成する素子として、実施形態 1 ではトランスマルチプレクタ 221 等が用いられ、実施形態 2 では A N D 回路 321 等が用いられる例を示したが、実施形態 1 に A N D 回路が用いられるようにしたり、実施形態 2 にトランスマルチプレクタが用いられるようにしたりしてもよい。

30

**【0061】**

また、セル群指定回路 202 内の F U S E 素子 101 は、書き込み完了信号 A を H i g h にしたときに切斷されるようにした例を示したが、書き込み完了信号 A を H i g h に固定して、または W T C 信号（もしくは書き込み完了信号 A ）がトランスマルチプレクタ 222 に直接入力されるようにして、W T C 信号等を H i g h にするだけで切斷できるようにしてもよい。また、書き込みデータ信号 D 0 ~ D n - 1 についても、直接トランスマルチプレクタ 221 等に入力されるようにして、これらの書き込みデータ信号 D 0 ~ D n - 1 が H i g h にされるだけで書き込みが行われるようにもよい。

40

**【0062】**

また、読み出しデータ信号 R 0 ~ R n - 1 と書き込みデータ信号 D 0 ~ D n - 1 とが別個に設けられる例を示したが、これに限らず、W T C 信号などに応じて、書き込みデータ信号線または読み出しデータ信号線に切り換わる兼用のデータ線を用いるなどしてもよい。

**【0063】**

また、上記のようにデータビットセル群 201a ~ 201c のうち、データが書き込まれるものと読み出されるものとが異なるように構成する場合には、一旦、読み出される状態にすれば、不用意に記憶内容が書き換わることは確実に防止されるが、これに限らず、同じデータビットセル群に対して書き込みおよび読み出しがなされるようにもよい。

50

その場合には、切断される FUSE 素子 101 を増加させるような書き換えの場合には、新たなデータビットセル群 201a ~ 201c に切り換えることなく（書き換え可能な回数に関係なく）書き換えることができる。また、上記の例のように書き換え回数が 3 回であれば、セル群指定回路 202 には 2 つのビットセル 100 を設けるだけでもよい。さらに、必ずしも読み出しと書き込みとで同じセル群指定回路 202 が用いられなくてもよい。

#### 【0064】

また、デコード回路 203 の構成は図 2 等に示すものに限るものではない。特に、セル群指定回路 202 の各ビットセル 100 から出力される信号は、FUSE 素子 101 の切断に伴って 1 回反転するだけで、デコード回路 203 に入力される信号のパターンは 4 通りしかないので、実際には、より簡略化することもできる。10

#### 【0065】

また、実施形態 2 のように各ビットセル 110 の出力に接続されるラッチ回路 331 が設けられる場合には、ビットセル 110 内にラッチ回路 106 を設けずに、インバータやバッファなどを設けるだけでもよい。

#### 【0066】

また、参考例 1では、ビットセル 110 が用いられ、それらの出力が互いに接続されて T フリップフロップ 431 に（データとして）入力される例を示したが、例えばビットセル 100 を用い、これらの出力が OR 回路で合成されて入力されるようにしてもよい。また、FUSE 素子 101 が切断されているビットセル 100 等の数をカウントするためには、上記のような合成された信号が T フリップフロップ 431 のクロック信号として入力されるようにしたりしてもよい。20

#### 【0067】

また、クロック発生回路 421 は図 6 に示すようなものに限らず、例えば RDC 信号に代えて、AND 回路 421c から出力されるのと同じようなワンショットパルスが入力されるようにしたり、また、シフトレジスタを用いるなどしてもよく、さらに、クロック発生回路を設けずに、CLKa ~ CLKc 等がそれぞれ入力されるようにしてもよい。

#### 【0068】

また、参考例 2では、XOR 回路 513 による FUSE 素子 101 切断要否の判定、および AND 回路 511 による切断されるビットセル 120 の選択がともに行われる例を示したが、何れか一方が、参考例 1と同じように外部から与えられる信号によって決定されるようにしてもよい。30

#### 【0069】

また、実施形態 3 では、n 個 × m 組のデータビットセル群 1011 を設けて、n ビットのデータが出力される例を示したが、n ビットより小さく分割されたビット数のデータが、例えばアドレス信号 AX0 - r の他に入力されるアドレス信号 AY0 - p によって選択されるようにしたりしてもよい。

#### 【0070】

また、例えば実施形態 1 のセル群指定回路 202 等に含まれるビットセル 100 の出力が半導体記憶装置の外部から参照できるようにして、書き込みが何回行われたかなどを容易に判別できるようにしてもよい。40

#### 【0071】

また、米国特許 5966339 号明細書に記載されているように、FUSE 素子の切断数に応じたデータを出力させるために複数のビットセル等の出力が XOR 回路に入力されるようにするのに代えて、一方の入力信号が反転される AND 回路に入力されるようにするなどしてもよい。すなわち、例えば 2 つのビットセルにおける FUSE 素子の切断される順序が決まっていれば、一方だけが切断された状態と他方だけが切断された状態とを両方とも考慮する必要はないので、XOR 回路よりも論理を簡素化することができる。

#### 【産業上の利用可能性】

#### 【0072】

本発明にかかる半導体記憶装置は、いわゆるOTPセルを有する半導体記憶装置において、回路規模の大幅な増加を招くことなく、複数回の書換を実施することができ、全ビット書換、個別ビット追記、アレイ型の書換を行うことができる効果を有し、FUSE素子を用いて1回だけ記憶情報の書き換えが可能なOTP素子等と称される記憶素子を用いた不揮発メモリ等として有用である。

【図面の簡単な説明】

【0073】

【図1】実施形態1の半導体記憶装置等に用いられるビットセル100の構成を示す回路図である。

【図2】実施形態1の半導体記憶装置の構成を示す回路図である。

10

【図3】実施形態2の半導体記憶装置に用いられるビットセル110の構成を示す回路図である。

【図4】実施形態2の半導体記憶装置の構成を示す回路図である。

【図5】参考例1の半導体記憶装置の構成を示す回路図である。

【図6】参考例1の半導体記憶装置のクロック発生回路421の構成を示す回路図である。

【図7】参考例1の半導体記憶装置のクロック発生回路421の動作を示すタイミングチャートである。

【図8】参考例2の半導体記憶装置に用いられるビットセル120の構成を示す回路図である。

20

【図9】参考例2の半導体記憶装置の構成を示す回路図である。

【図10】実施形態3の半導体記憶装置の構成を示す回路図である。

【符号の説明】

【0074】

S0～S2 選択信号

T0～T2 書き込み信号

100 ビットセル

101 FUSE素子

102 書き込みトランジスタ

103 読み出しトランジスタ

104 NOT回路

105 トランスファゲート回路

106 ラッチ回路

110 ビットセル

111 トランスファゲート

120 ビットセル

201a～201c データビットセル群

30

202 セル群指定回路

203 デコード回路

204 セレクタ回路

40

211～214 選択信号

221～223 トランスファゲート

224 AND回路

301a～301c データビットセル群

303 デコード回路

321～323 AND回路

331 ラッチ回路

411 AND回路

421 クロック発生回路

421a 遅延回路

50

|                   |            |    |

|-------------------|------------|----|

| 4 2 1 b           | NOT回路      |    |

| 4 2 1 c           | AND回路      |    |

| 4 2 1 d • 4 2 1 e | 遅延回路       |    |

| 4 2 1 f           | OR回路       |    |

| 4 3 1             | Tフリップフロップ  |    |

| 5 1 1             | AND回路      |    |

| 5 1 2             | NOT回路      |    |

| 5 1 3             | XOR回路      |    |

| 1 0 0 1           | FUSE素子     |    |

| 1 0 0 2           | AND回路      | 10 |

| 1 0 0 3 • 1 0 0 4 | 読み出しトランジスタ |    |

| 1 0 0 5           | 書き込みトランジスタ |    |

| 1 0 1 0           | メモリセルアレイ   |    |

| 1 0 1 1           | データビットセル群  |    |

| 1 0 2 1           | デコード回路     |    |

| 1 0 2 2           | センスアンプ列    |    |

| 1 0 2 3           | コラムI/O回路   |    |

| 1 0 3 1           | セル群指定回路    |    |

| 1 0 3 2           | デコード回路     |    |

| 1 0 3 3 • 1 0 3 4 | AND回路      | 20 |

| 1 0 3 3 • 1 0 3 4 | AND回路      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(72)発明者 白濱 政則

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 西原 竜二

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 川崎 利昭

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 縣 政志

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 外山 賀

(56)参考文献 特開昭63-187498(JP,A)

特開2006-120244(JP,A)

米国特許第05966339(US,A)

特開平03-214498(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 17/00

G 11 C 17/14

G 11 C 16/00 - 16/34