(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5893020号

(P5893020)

(45) 発行日 平成28年3月23日(2016.3.23)

(24) 登録日 平成28年3月4日(2016.3.4)

(51) Int.Cl.

G06F 13/38 (2006.01)

F 1

G 06 F 13/38 3 2 O Z

請求項の数 19 (全 16 頁)

(21) 出願番号 特願2013-519835 (P2013-519835)

(86) (22) 出願日 平成23年7月14日 (2011.7.14)

(65) 公表番号 特表2013-534680 (P2013-534680A)

(43) 公表日 平成25年9月5日 (2013.9.5)

(86) 國際出願番号 PCT/US2011/044048

(87) 國際公開番号 WO2012/009559

(87) 國際公開日 平成24年1月19日 (2012.1.19)

審査請求日 平成26年7月14日 (2014.7.14)

(31) 優先権主張番号 12/836,731

(32) 優先日 平成22年7月15日 (2010.7.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

最終頁に続く

(54) 【発明の名称】 PCI エクスプレス適合デバイスの資源にアクセスするためのシステム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ソースデバイスから発生したメッセージを用いて宛先の機能メモリ空間にアクセスするための方法であって、

宛先がベンダ定義メッセージの資源アクセス要求をサポートしているかどうかを判断すること、

前記宛先がサポートしていると判断した場合に、

前記ソースデバイスに実装されたメッセージ標準プロトコルで定義された特定ベンダ向けタイプフィールド内の値に基づく前記ベンダ定義メッセージである前記メッセージであって、前記機能メモリ空間のアクセスのタイプを特定するアクセスタイプ値と、前記機能メモリ空間に関連付けられる宛先オフセット値とを含む前記メッセージを、前記ソースデバイスで形成すること、

前記メッセージを前記宛先へ送ることと、を備える方法。

## 【請求項 2】

前記メッセージ標準プロトコルは PCI エクスプレスマッセージプロトコルである、請求項 1 に記載の方法。

## 【請求項 3】

前記機能メモリ空間のアクセスのタイプは、メモリ読み出し動作、メモリ書き込み動作、構成レジスタ読み出し動作、構成レジスタ書き込み動作及び完了動作のうち 1 つである、請求項 1 に記載の方法。

**【請求項 4】**

前記メッセージはデータ値を更に含み、前記機能メモリ空間のアクセスのタイプは、メモリ書き込み動作、構成レジスタ書き込み動作及び完了動作のうち1つである、請求項1に記載の方法。

**【請求項 5】**

前記機能メモリ空間は、メモリロケーション及びレジスタロケーションのうち1つである、請求項1に記載の方法。

**【請求項 6】**

前記形成すること及び前記送ることは、前記ソースデバイスに関連付けられる有効化フィールドがメッセージング有効化を示す値にセットされるときに行われる、請求項1に記載の方法。 10

**【請求項 7】**

前記ソースデバイスに関連付けられる状態フィールドが予め定められた値に設定されることによって、前記メッセージが成功裏に送られたことを示すことを更に備える、請求項1に記載の方法。

**【請求項 8】**

前記メッセージが成功裏に送られたこと及び前記データ値の読み出しが可能であることを示すことを更に備える、請求項4に記載の方法。

**【請求項 9】**

前記形成すること及び前記送ることは、前記ソースデバイスで先のベンダ定義メッセージによる先のアクセスがクリアされたことを検証した後に行われる、請求項1に記載の方法。 20

**【請求項 10】**

前記メッセージを形成することは、単一ステップ伝搬に関連付けられる予め定められたルーティング値にルート値が設定されることを更に含む、請求項1に記載の方法。

**【請求項 11】**

前記メッセージを形成することは、多重ステップ伝搬に関連付けられる予め定められたルーティング値にルート値が設定されることを更に含む、請求項1に記載の方法。

**【請求項 12】**

ソースデバイスから発生したメッセージを用いて宛先の機能メモリ空間にアクセスするための方法であって、 30

宛先がベンダ定義メッセージの資源アクセス要求をサポートしていることを、前記宛先が前記ソースデバイスに示すことと、

前記ソースデバイスに実装されたメッセージ標準プロトコルで定義された特定ベンダ向けタイプフィールド内の値に基づくベンダ定義メッセージである前記メッセージであって、前記機能メモリ空間のアクセスのタイプを特定するアクセスタイル値と、前記機能メモリ空間に関連付けられる宛先オフセット値とを含む前記メッセージを、前記宛先で受け取ることと、

前記宛先オフセット値及び前記アクセスタイル値に基づき前記機能メモリ空間での前記アクセスを行うことと、を備える方法。 40

**【請求項 13】**

前記メッセージ標準プロトコルはPCIエクスプレスマッセージプロトコルである、請求項12に記載の方法。

**【請求項 14】**

前記機能メモリ空間のアクセスのタイプは、メモリ読み出し動作、メモリ書き込み動作、構成レジスタ読み出し動作、構成レジスタ書き込み動作及び完了動作のうち1つである、請求項12に記載の方法。

**【請求項 15】**

前記メッセージはデータ値を更に含み、前記機能メモリ空間のアクセスのタイプは、メモリ書き込み動作、構成書き込み動作及び完了動作のうち1つである、請求項12に記載 50

の方法。

【請求項 1 6】

前記機能メモリ空間は、メモリロケーション及びレジスタロケーションのうち 1 つである、請求項 1 2 に記載の方法。

【請求項 1 7】

前記機能メモリ空間にアクセスすることは、前記宛先でのレジスタ値がメッセージ有効化を示す予め定められた値にセットされるときに生じる、請求項 1 2 に記載の方法。

【請求項 1 8】

ソースデバイスから発生したメッセージを用いて宛先デバイスの機能メモリ空間にアクセスするための装置であって、

10

宛先がベンダ定義メッセージの資源アクセス要求をサポートしているかどうかを判断するように構成されたデジタルソースデバイスであって、前記宛先がサポートしていると判断した場合に前記メッセージを形成するように構成されたデジタルソースデバイスを備え、

前記メッセージは、前記ソースデバイスに実装されたメッセージ標準プロトコルで定義された特定ベンダ向けタイプフィールド内の値に基づくベンダ定義メッセージであって、前記機能メモリ空間のアクセスのタイプを特定するアクセスタイプ値と、前記宛先デバイスの前記機能メモリ空間に関連付けられる宛先オフセット値とを含む、装置。

【請求項 1 9】

ソースデバイスから発生したメッセージを用いて宛先デバイスの機能メモリ空間にアクセスするための装置であって、

20

ベンダ定義メッセージの資源アクセス要求をサポートしていることを前記ソースデバイスに示すように構成されたデジタル宛先デバイスであって、前記メッセージを受け取るように構成されたデジタル宛先デバイスを備え、

前記メッセージは、前記ソースデバイスに実装されたメッセージ標準プロトコルで定義された特定ベンダ向けタイプフィールド内の値に基づくベンダ定義メッセージであって、前記機能メモリ空間のアクセスのタイプを特定するアクセスタイプ値と、前記宛先デバイスの前記機能メモリ空間に関連付けられる宛先オフセット値とを含み、

前記デジタル宛先デバイスは前記宛先オフセット値及び前記アクセスタイプ値に基づき前記機能メモリ空間にアクセスするように更に構成される、装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は概してデータ通信に関し、特にシリアル点対点データ通信に関する。

【背景技術】

【0002】

近年、コンピュータの速度は劇的に増大してきている。その増大の大部分は C P U 速度の増大に起因している。一方、コンピュータ速度は、データ通信の速度、即ち C P U が周辺デバイスとの間でデータを通信する能力にも依存する。暫くの間は、周辺部品相互接続 (peripheral component interconnect) ( P C I ) バスが適切な周辺接続性を提供していた。しかし、C P U 速度の増大及びより大きなデータ転送要求に伴い、P C I はすぐに C P U と周辺機器の間での最も低速なリンクになってしまった。特に、P C I バスは、データ転送要求の増大を満たすためには、ピン、電力及びクロッキングに関する相当な不利益をもたらしていた。

40

【0003】

これらの不利益に対応するために、P C I エクスプレス業界規格 (PCI Express industry standard) が開発された。低電圧差動信号を用いるシリアルプロトコルが採用される P C I エクスプレス業界規格は、上述のようなクロッキングの不利益をもたらすことはなく、またより広帯域をより少ないピン数で伝達する。P C I エクスプレスは、「ルート (root)」デバイスと「エンドポイント (endpoint)」デバイスの間でのシリアル点対点接続性 (s

50

erial point-to-point connectivity)をもたらす最大で32データチャネル(レーン(lanes)として知られる)を提供する。

#### 【0004】

PCIエクスプレスプロトコルは、トランザクションレイヤ、データリンクレイヤ及び物理レイヤを含む複数のレイヤを伴うレイヤードプロトコルである。PCIエクスプレス適合デバイスの間での通信の基本構築プロトコルは、トランザクションレイヤパケット(TLP)である。TLPは、ヘッダとデータペイロードと誤り訂正セグメント(ダイジェストと称される)とを含む。1つ以上のTLPが、PCIエクスプレス適合デバイスにおける動作を有効にするトランザクションを作り出す。例えばTLPトランザクションは、メモリの読み出し及び書き込みの動作を容易にする。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

上述したように、PCIエクスプレスプロトコルは、最新のデータ通信デバイス対デバイス課題への柔軟な高速アプローチを提供するために開発された。それでもなお、高性能コンピュータ設計をサービスするために効率的なデータ転送の要求が増大してきており、データ転送の効率はいまだに最優先である。従って、PCIエクスプレスプロトコルを強化する必要性が継続している。PCIエクスプレスプロトコルに対するどのような改善も、標準的なPCIエクスプレス仕様と後方互換(backwards compatible)である必要がある。

20

#### 【0006】

結果として、PCIエクスプレスプロトコル強化からの追加的な機能が実現されるのを可能にするために、デバイス修正が必要である。PCIエクスプレスプロトコルに対する強化は、通信リンクのいずれかの端におけるデバイスに関連するソフトウェアドライバのアップグレードにより実現され得る。そのようなアップグレードされたソフトウェアドライバは、関連デバイスがPCIエクスプレスプロトコル強化を十分に利用することができるよう、メモリマップされた空間(memory-mapped space)をプログラムする。デバイスソフトウェアドライバのアップグレードは望ましい解決法ではあるが、多くの場合にそのようなアップグレードは、タイミング良く利用可能であるわけではない。また、PCIエクスプレス機能は、その機能により所有されていない資源(例えば構成空間(configuration space))にアクセスすることを許可されていない。PCIエクスプレス環境における外部資源の幾つかの限定されたアクセスがピアツーピア(peer-to-peer)アプローチを用いて可能であることがあるが、多くのプラットフォームはピアツーピアアクセスをサポートしておらず、またピアツーピアアプローチを用いる「読み出しアクセス」をサポートしているプラットフォームは殆どない。加えて、下流のPCIエクスプレスポートは、構成空間へのアクセスを受け入れない。更に、幾つかのシステムは、「アクセス制御サービス(ACCESS Control Service)」を介したピアツーピアアクセスを全てブロックする。

30

#### 【0007】

そこで、関連デバイスソフトウェアドライバのアップグレードがない場合にPCIエクスプレスプロトコル強化を実装する方法及びシステムに対する必要性がある。

40

#### 【課題を解決するための手段】

#### 【0008】

本発明のある実施形態においては、ベンダ定義のメッセージ(vendor defined messages)を用いてメモリ空間及びレジスタ空間が構成される。

#### 【0009】

本発明の更なる実施形態においては、資源アクセスアプローチは、タイプ1ベンダ定義のPCIエクスプレスマッセージを用いて適用される。メモリ読み出し、メモリ書き込み、構成読み出し(configuration read)、構成書き込み及び完了のためのタイプ1ベンダ定義のPCIエクスプレスマッセージの例示的な実施形態が説明される。

#### 【0010】

50

資源アクセスへのメッセージングアプローチを用いる使用モデルの例もまた説明される。

。

【0011】

本発明の更なる実施形態、特徴及び利点並びに本発明の種々の実施形態の構成及び動作は、添付図面を参照して以下に詳細に説明される。

【図面の簡単な説明】

【0012】

ここに組み込まれ且つ出願書類の一部をなす添付の図面は、本発明を示し、そして明細書と共に、本発明の原理を説明すること及び関連分野を含めた当業者が本発明を作りそして使用するのを可能にすることに更に役立つ。

10

【0013】

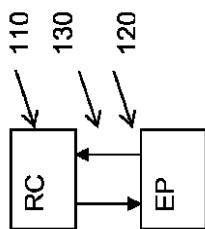

【図1】図1はPCIエクスプレスアプローチを用いるデータ通信システムを示す図である。

【0014】

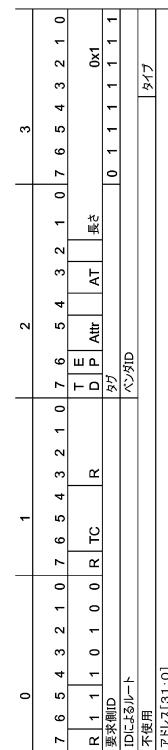

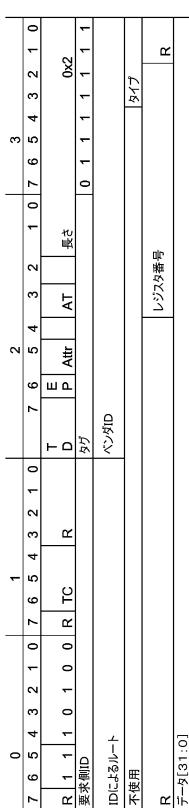

【図2】図2は本発明の実施形態に従う例示的なベンダ定義のメモリ読み出しメッセージ定義を示す図である。

【0015】

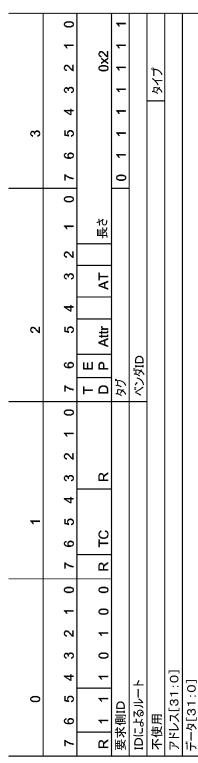

【図3】図3は本発明の実施形態に従う例示的なベンダ定義のメモリ書き込みメッセージ定義を示す図である。

【0016】

20

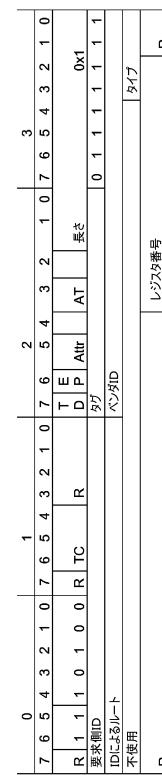

【図4】図4は本発明の実施形態に従う例示的なベンダ定義の構成読み出しメッセージ定義を示す図である。

【0017】

【図5】図5は本発明の実施形態に従う例示的なベンダ定義の構成書き込みメッセージ定義を示す図である。

【0018】

【図6】図6は本発明の実施形態に従う例示的なベンダ定義の完了メッセージ定義を示す図である。

【0019】

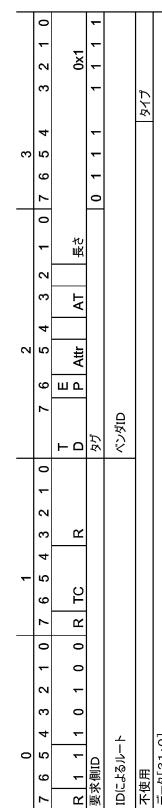

【図7A】図7Aは本発明の実施形態に従う資源アクセスへのベンダメッセージングアプローチのための例示的なレジスタ定義を示す図（その1）である。

30

【図7B】図7Bは本発明の実施形態に従う資源アクセスへのベンダメッセージングアプローチのための例示的なレジスタ定義を示す図（その1の2）である。

【図8】図8は本発明の実施形態に従う資源アクセスへのベンダメッセージングアプローチのための例示的なレジスタ定義を示す図（その2）である。

【図9】図9は本発明の実施形態に従う資源アクセスへのベンダメッセージングアプローチのための例示的なレジスタ定義を示す図（その3）である。

【0020】

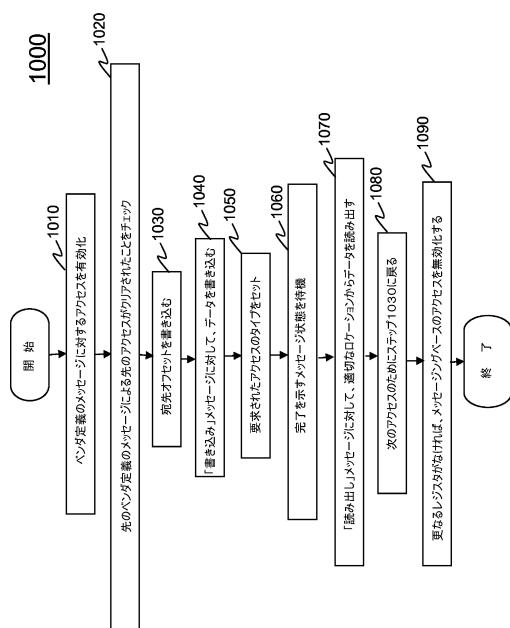

【図10】図10は本発明の実施形態に従いメッセージングを用いる資源アクセスの例示的な方法のフローチャートである。

40

【0021】

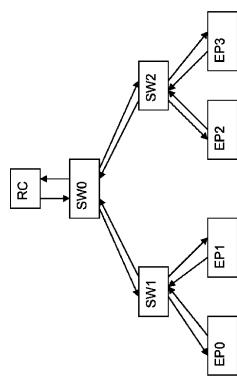

【図11】図11は4つのエンドポイント、1つのルートコンプレックス及び3つのスイッチを伴うPCIエクスプレストポロジを示す図である。

【0022】

次に、添付図面を参照して本発明を説明する。図面において同様の参照番号は同一の又は機能的に類似の要素を示すことがある。また、参照番号の最も左の単一又は複数の数字は、その参照番号が初めて現れる図面を指定することがある。

【発明を実施するための形態】

【0023】

図1はデバイス110及び120の間での通信のためのPCIエクスプレスシステムを

50

用いるデータ通信システムを示している。PCIエクスプレス規格における通信の基本ユニットは、トランザクションレイヤパケット(TLP)である。1つ以上のTLPがPCIエクスプレストランザクションを確立し、そしてデバイス110及び120の間でリンク130を介して伝送される。デバイス110及び120は、典型的にはPCIエクスプレストランザクションを制御し且つ管理する制御器を含む。

#### 【0024】

一般的なTLPパケットは、ヘッダとデータペイロードと誤り照合部分(ダイジェストとしても知られる)とを含む。全てのTLPパケットがデータペイロード及びダイジェストを必要とするわけではないので、データペイロード及びダイジェストは随意的である。TLPヘッダはダブルワード(DWordとしても知られる)として調整され、DWordは4バイト即ち32ビットに等しい。具体的なPCIエクスプレストランザクションに応じて、TLPヘッダの長さは変化し得る(例えば3DWor d長又は4DWor d長)。

#### 【0025】

上述したように、PCIエクスプレスプロトコル強化からの追加的な機能が実現されるのを可能にするためには、デバイス修正が必要である。PCIエクスプレスプロトコルに対する強化は、典型的には通信リンクのいずれかの端におけるデバイスに関連するソフトウェアドライバのアップグレードにより実装され得る。そのようなアップグレードされたソフトウェアドライバは、デバイスに関連するメモリマップされた空間(memory-mapped space)をプログラムすることにより、PCIエクスプレスプロトコル強化を用いることができる。影響を受ける各PCIエクスプレスデバイス(エンドポイント、スイッチ及びルートコンプレックスを含む)のためにアップデートされたソフトウェアドライバは、PCIエクスプレスプロトコル強化を組み込むために必要な望ましい解決法である。デバイスソフトウェアドライバのアップグレードは望ましい解決法ではあるが、多くの場合にそのようなアップグレードは、タイミング良く利用可能であるわけではない。

#### 【0026】

以下に説明されるアプローチにおいては、関連デバイスのメモリマップされた空間(又は構成空間)に対して読み出し及び書き込みするためにベンダ定義のPCIエクスプレスマッセージが用いられる包括的方法が提案される。これらのベンダ定義のPCIエクスプレスマッセージは、PCIエクスプレスプロトコルにおけるベンダ定義タイプ1メッセージである。ベンダ定義のタイプ1メッセージアプローチを用いることによって、PCIエクスプレスリンクの他端にあるPCIエクスプレス適合デバイスがそのようなタイプのメッセージをサポートしていない場合に、メッセージは受け取り側により静かに廃棄され、エラーは報告されない。以下に説明するアプローチにおいては、どの時点においても1つの未処理要求のみがサポートされる。

#### 【0027】

このメッセージングアプローチを用いて4タイプのレジスタアクセスが定義される。4タイプのレジスタアクセスは、メモリ読み出し、メモリ書き込み、構成読み出し及び構成書き込みである。所望のレジスタアクセスのタイプは、ベンダ定義のメッセージのヘッダにおける特定ベンダ向けタイプフィールド(vendor-specific type field)内の適切な値によって定義される。この方法の例として、メモリ読み出し要求は以下のようにして動作する。このアプローチを用いてメモリ読み出し要求が送られると、通信リンクの反対側は、タイプ完了を示す特定ベンダ向けメッセージと32ビットデータペイロードとに応答する。特定ベンダ向けメッセージの受け取り側は次いでこのメッセージを処理し、そしてデータは関連レジスタ内に記憶され、関連レジスタはソフトウェアによって後で読まれ得る。

#### 【0028】

[メモリ読み出しのための例示的なベンダ定義のメッセージ]

図2～図6は本発明の実施形態に従いレジスタアクセスのために用いられるベンダ定義のタイプ1メッセージのためのトランザクションレイヤパケット定義を示している。図2はベンダ定義のメッセージにおけるメモリ読み出しのための例示的なTLP定義を示して

10

20

30

40

50

いる。図2に示されるように、ベンダ定義のメモリ読み出しメッセージのヘッダは、4つのDWo rdと1つのDWo rdペイロードとから構成される。ヘッダの第1のワードは予備フィールドである第1のフィールドからなり、1ビット長であり、「R」で示されている。第2のフィールドは7ビットフィールドであり、TLPがベンダ定義のメッセージであることを示す値「1110100」を含む。

#### 【0029】

第1のDWo rdにおける次のフィールドもまた予備フィールドであり、1ビット長であり、「R」で示されている。トライッククラス(TC)フィールドは3ビットフィールドであり、トライッククラスの最大で8つの異なるタイプを識別する。そのような情報は、異なる品質のサービスを提供するための基礎を形成し得る。次のフィールドもまた予備フィールドであり、4ビット長であり、「R」で示されている。TDフィールドは1ビットフィールドであり、TLPパケットの最後にダイジェストがあるかどうかを示す。従ってTDフィールド値の「1」はダイジェストの存在を示し、「0」の値はダイジェストの不在を示す。EPフィールドは1ビットであり、TLPパケットが「悪い」データを含んでいるとみなされるかどうかを示す。従ってEPフィールド値の「1」は悪いデータの存在を示し、「0」の値は悪いデータの不在を示す。「Att r」は2ビットフィールドであり、TLPパケットのための属性情報を提供し、属性情報は、キャッシュコヒーレンシ及び緩和された順序(relaxed ordering)に関する情報を含む。「AT」は2ビットフィールドであり、PCIエクスプレスアドレストランスレーションサービスが用いられる場合にパケット内のアドレスがトランスレートされているかどうかを示す。

10

20

#### 【0030】

最後に「長さ」フィールドは10ビットフィールドであり、TLP内のペイロードの長さを示す。ペイロード長はDWo rdで表現される。このフィールドの値が「1」の値にセットされていると、これはペイロード長が1DWo rdの長さであることを示す。

#### 【0031】

ベンダ定義のメモリ読み出しメッセージの第2のDWo rdは、「要求側ID」フィールド、「タグ」フィールド及び固定値フィールドを含む。「要求側ID」フィールドは16ビットフィールドであり、要求側のバス番号、デバイス番号及び機能番号を含む。「要求側ID」フィールドの内容は、構成フェーズの間に割り当てられ、そしてPCIエクスプレストポロジにおける要求側を一意的に識別することが意図されている。

30

#### 【0032】

「タグ」フィールドは8ビットフィールドであり、要求を一意的に識別するために用いられる。特に、要求側は、完了を必要とするその要求側によって作られる要求の各々に対して固有の「タグ」フィールドを作成することができる。従って、関連完了ヘッダは、その関連完了ヘッダを要求側が速やかに識別し得るように、関連「要求側ID」及び「タグ」を含む。

#### 【0033】

ベンダ定義のメモリ読み出しメッセージの第2のDWo rd内の最後のフィールドは8ビットフィールドであり、その値は「01111111」に固定されている。

#### 【0034】

ベンダ定義のメモリ読み出しメッセージの第3のDWo rdは、「IDによるルート」フィールド及び「ベンダID」フィールドを含む。「IDによるルート」フィールドは16ビットフィールドであり、メッセージの所定の受け取り側であるデバイスを示すルーティング情報を含む。「ベンダID」フィールドは16ビットフィールドであり、メッセージを送っているデバイスのベンダの識別を含む。「ベンダID」はPCIスペシャルインタレストグループ(PCI Special Interest Group)(PCI-SIG)によって割り当てられる。

40

#### 【0035】

ベンダ定義のメモリ読み出しメッセージの第4のDWo rdは、28ビットの不使用フィールドと4ビットのタイプフィールドとを含む。4ビットのタイプフィールドは所望の

50

アクセスのタイプを示す。「タイプ」フィールドのための例示的な値のセットは図7Bに示されている。

【0036】

最後に、ベンダ定義のメモリ読み出しメッセージの第5のDWordは、32ビットフィールドを含むペイロードであり、メモリ読み出しメッセージによってアドレスされている最中の関連メモリ空間のアドレスを示す。

【0037】

〔メモリ書き込みのための例示的なベンダ定義のメッセージ〕

図3はベンダ定義のメッセージにおけるメモリ書き込みのための例示的なTLP定義を示している。図3に示されるように、ベンダ定義のメモリ書き込みメッセージのヘッダは、4つのDWordと2つのDWordペイロードとから構成される。ヘッダの第1のDWordは、メモリ読み出しメッセージに対して図2に示されるのと同じフィールド及び値を含む。唯一の違いは、長さフィールドが「2」の値にセットされていることであり、これはペイロード長が2DWordの長さであることを示している。次の3つのDWordは、タイプフィールドがメモリ書き込みタイプメッセージに関連付けられる値にセットされている点を除き、メモリ読み出しメッセージに対して図2に示されるのと同じである。メッセージのペイロードは2つのDWordを含み、第1のDWordは32ビットのアドレスフィールドを含み、第2のDWordは32ビットのデータフィールドを含む。代替的な実施形態においては、TLPパケットは、可変長データのアドレシングをサポートするアドレシング情報を含むことができる。そのような実施形態においては、ペイロード長は、2(又はメモリ読み出しの場合には1)等のセットされた値でハードウェア組み込みされていない代わりに、データブロックに1を加えた長さにセットされる。この代替的な実施形態は、メモリ書き込み、メモリ読み出し及び完了のメッセージに適用され得る。

【0038】

〔構成読み出しのための例示的なベンダ定義のメッセージ〕

図4はベンダ定義のメッセージにおける構成読み出しのための例示的なTLP定義を示している。図4に示されるように、ベンダ定義の構成読み出しメッセージのヘッダは、4つのDWordとそれに続く1つのDWordペイロードとから構成される。ヘッダの第1のDWordは、メモリ読み出しメッセージに対して図2に示されるのと同じフィールド及び値を含む。メモリ読み出しメッセージと同様に、長さフィールドは「1」の値にセットされており、これはペイロード長が1DWordの長さであることを示している。次の3つのDWordは、タイプフィールドが構成読み出しタイプメッセージに関連付けられる値にセットされている点を除き、メモリ読み出しメッセージに対して図2に示されるのと同じである。メッセージのペイロードは1つのDWordを含み、このDWordは20ビットの予備フィールドを含み、それに続き、読み出し中のレジスタの数を示す10ビットの「レジスタ数」フィールドがある。最後に、残りの2ビットは、2ビット予備フィールドを構成する。

【0039】

〔構成書き込みのための例示的なベンダ定義のメッセージ〕

図5はベンダ定義のメッセージにおける構成書き込みのための例示的なTLP定義を示している。図5に示されるように、ベンダ定義の構成書き込みメッセージのヘッダは、4つのDWordとそれに続く2つのDWordペイロードとから構成される。ヘッダの第1のDWordは、ペイロード長が2DWordの長さであることを示す「2」の値に長さフィールドがセットされている点を除き、メモリ読み出しメッセージに対して図2に示されるのと同じフィールド及び値を含む。次の3つのDWordは、タイプフィールドが構成書き込みタイプメッセージに関連付けられる値にセットされている点を除き、メモリ読み出しメッセージに対して図2に示されるのと同じである。メッセージのペイロードは2つのDWordを含み、第1のDWordは20ビットの予備フィールドを含み、それに続き、書き込み中のレジスタの数を示す10ビットの「レジスタ数」フィールドがある。

10

20

30

40

50

。ペイロードの第1のDW o r dの残りの2ビットは、2ビット予備フィールドを構成する。最後にペイロードの第2のDW o r dは、構成書き込みメッセージの32ビットのデータを含む。

#### 【0040】

〔完了のための例示的なベンダ定義のメッセージ〕

図6はベンダ定義のメッセージにおける完了のための例示的なT L P定義を示している。図6に示されるように、ベンダ定義の完了読み出しメッセージのヘッダは、4つのDW o r dとそれに続く1つのDW o r dペイロードとから構成される。ヘッダの第1のDW o r dは、メモリ読み出しメッセージに対して図2に示されるのと同じフィールド及び値を含む。メモリ読み出しメッセージと同様に、長さフィールドは「1」の値にセットされており、これはペイロード長が1DW o r dの長さであることを示している。次の3つのDW o r dは、タイプフィールドが完了メッセージに関連付けられる値にセットされている点を除き、メモリ読み出しメッセージに対して図2に示されるのと同じである。メッセージのペイロードは1つのDW o r dを含み、このDW o r dは32ビットのデータを含む。

#### 【0041】

〔ベンダ定義のメッセージングアプローチのための例示的なレジストリ定義〕

図7A～図9はベンダ定義のメッセージングアプローチのサポートにおける例示的なレジストリ定義を示している。図7Aは5つのフィールドの例示的な定義を示しており、これらのフィールドは、ここで説明される能力をサポートするデバイスを指定するリードオンリ2ビットフィールド( REG\_ACCESS\_CAPABILITY )と、ベンダ定義のメッセージを介してレジスタアクセスの発生を有効にする1ビットフィールド( REG\_ACCESS\_GEN\_EN )と、セットされたときに、受け取ったベンダ定義のメッセージを介してレジスタアクセスを無効にすることができる1ビットフィールド( REG\_ACCESS\_RCV\_DIS )と、先のメッセージが既に送られていること(書き込みの場合)及びデータがアクセスされ得ること(読み出しの場合)を、「0」の値を用いて示す1ビットフィールド( REG\_ACCESS\_DONE )と、図7Bに示される例示的な定義を用いてアクセスのタイプを示す4ビットフィールド( REG\_ACCESS\_TYPE )と、である。図8はベンダ定義のメッセージを介してレジスタアクセスのためのメモリマップされた空間におけるオフセットを提供する32ビットフィールド( REG\_ACCESS\_ADDRESS )の例示的な定義を示している。構成読み出し及び構成書き込みの動作の場合に対しては、レジスタオフセットを提供するために、32ビットフィールドのうちのビット9:0のみが用いられる。図9は、ベンダ定義のメッセージを介したレジスタアクセスを用いて、メモリマップされた書き込み又は構成書き込みのためのデータを提供する32ビットフィールド( REG\_ACCESS\_WRITE\_DATA )の例示的な定義を示している。読み出しデータレジスタはまた、読み出し動作の完了に際して受け取ったデータを記憶する必要がある。例示的な実施形態においては、読み出しデータレジスタは、単純に読み出し動作のために再使用される書き込みデータレジスタであってよい。代替的には、読み出しデータレジスタは、全く別のレジスタ、例えば32ビットフィールド( REG\_ACCESS\_READ\_DATA )であってよい。既に述べたように、本発明の実施形態は、柔軟な長さのデータブロックへのアクセスを提供することを含む。加えて、データブロックは、レジスタロケーション又はメモリロケーションの範囲内にあってよい。

#### 【0042】

〔ベンダ定義のメッセージアプローチを用いる方法〕

図10は本発明の実施形態に従うベンダ定義のP C Iエクスプレスマッセージアプローチの使用のための例示的な方法のフローチャート1000を示す。図1の動作環境への参照を続けて図10を説明する。しかし、方法1000はその実施形態には限定されない。方法1000はステップ1010で始まる。

#### 【0043】

10

20

30

40

50

ステップ1010では、ベンダ定義のメッセージに対してソースでの資源アクセスを有効にする。例示的な実施形態においては、PCI\_E\_REG\_ACCESS\_CNTLレジスタのREG\_ACCESS\_GEN\_ENフィールドを「1」の値にセットすることにより、アクセスが有効にされ得る。

【0044】

ステップ1020では、先のベンダ定義のメッセージによる先のアクセスが確実にクリアされたことをチェックする。例示的な実施形態においては、そのようなチェックは、PCI\_E\_REG\_ACCESS\_CNTLのREG\_ACCESS\_DONEフィールドが「0」にセットされているかを調べてチェックすることにより行うことができる。

【0045】

ステップ1030では、ソースに関連付けられる適切なロケーションに宛先資源オフセットが書き込まれる。例示的な実施形態においては、宛先資源オフセットは、PCI\_E\_REG\_ACCESS\_ADDRレジスタ内に書き込まれる。

【0046】

ステップ1040では、メモリ書き込みベンダメッセージ又は構成書き込みベンダメッセージに対して、ソースに関連付けられる適切なロケーションにデータを書き込む。例示的な実施形態においては、PCI\_E\_REG\_ACCESS\_DATAレジスタ内のREG\_ACCESS\_WRITE\_DATAロケーション内にデータが書き込まれる。

【0047】

ステップ1050では、所望の宛先アクセスのタイプをセットする。例示的な実施形態では、PCI\_E\_REG\_ACCESS\_CNTL内のREG\_ACCESS\_TYPEフィールドを所望の宛先アクセスにセットする。タイプフィールドが書き込まれると、ベンダ定義のメッセージが送られる。

【0048】

ステップ1060では、ベンダ定義のメッセージを送ることの完了を示すメッセージ状態を待機する。例示的な実施形態では、PCI\_E\_REG\_ACCESS\_CNTLレジスタのREG\_ACCESS\_DONE値が「0」の値にセットされるまで待機することができる。

【0049】

ステップ1070では、ベンダメッセージを介したメモリ読み出し又は構成読み出しの動作であった場合に、適切なロケーションからデータを読み出す。例示的な実施形態では、ロケーションPCI\_E\_REG\_ACCESS\_DATAからデータが読み出され得る。

【0050】

ステップ1080では、ステップ1030に戻って次の宛先資源アクセスを続ける。

【0051】

ステップ1090では、更なる資源要求アクセスがない場合に、ベンダ定義のメッセージを介して資源アクセスを無効にする。例示的な実施形態では、PCI\_E\_REG\_ACCESS\_CNTL内のREG\_ACCESS\_GEN\_ENを「0」の値にセットすることにより、資源アクセスが無効にされ得る。

【0052】

ベンダ定義のメッセージの方法を介してこの資源アクセス要求をソフトウェアが用いる前に、ソフトウェアは、通信リンクの反対側がこの特徴をサポートしていることを決定する必要がある。このことは、ソフトウェアがこの方法を用いて構成空間アドレス0（ベンダ/デバイスID）の読み出しを行うことによりなされてよい。これにより、オフセット0をレジスタするタイプ0×2（即ち構成読み出し）のベンダ定義のメッセージが反対側へと送られることになる。この要求が成功し且つソフトウェアがPCI\_E\_REG\_ACCESS\_DATA内のベンダ/デバイスIDを読み出すことができる場合には、この方法はサポートされ、次いでソフトウェアはこの方法を用いることができる。ソフトウェアにおいてセットされるタイムアウト値の後にもPCI\_E\_REG\_ACCESS\_CNT

10

20

30

40

50

L . R E G \_ A C C E S S \_ D O N E = 1 である場合には、この方法はサポートされず、この方法を用いることはできない。例示的な実施形態では、このステップはステップ 10 10 に続いて行われ得る。

#### 【 0 0 5 3 】

前述したように、PCIエクスプレス仕様のように、通信リンクの反対側がこのメカニズムをサポートしておらず且つベンダ定義のメッセージを理解しない場合には、メッセージは受け取り側で静かに廃棄される必要がある。上述の方法は、例えば図 11 に示されるような多重エンドデバイスを含むより複雑なトポロジに容易に拡張され得る。例えば、図 11 におけるルート制御器、全てのスイッチ及びエンドポイントが、メモリアクセスに対するメッセージベースのアプローチをサポートする。

10

#### 【 0 0 5 4 】

尚、これらのベンダ定義のメッセージは受け取り側で終端し、スイッチによって転送されない（即ちルーティング [ 2 : 0 ] = 1 0 0 b ）。例えば図 11 において、EP0 が SW0 のレジスタにアクセスする必要がある場合には、EP0 は多重ステッププロセスでこれを行う必要がある。例えば EP0 が SW0 へのメモリ書き込みを行うためには、ベンダ定義のメッセージを介してメモリ書き込みを SW1 の上流へ送るように EP0 をプログラムする。EP0 からのこの書き込みは、SW1 の PCI\_E\_R E G \_ A C C E S S \* レジスタをプログラムし、これらレジスタは次いで、ベンダ定義のメッセージを介してメモリ書き込みを SW0 の上流へ送るように SW1 をトリガーすることになる。そのような単一ステップの伝搬モードは効率的でない。代替的でより効率的な多重ステップの実施形態においては、メッセージは ID によりルートされ得る（即ちルーティング [ 2 : 0 ] = 0 1 0 b ）。そのようなルーティングを用いることにより、メッセージはそれらの最終的な宛先へとスイッチを介して伝搬することができる。これら 2 つのベンダ伝搬方法のどちらが用いられるべきかは、追加的なレジスタロケーション（例えば REG \_ A C C E S S \_ R O U T E \_ A P P R O A C H ）が示す必要がある。

20

#### 【 0 0 5 5 】

関連分野を含めた当業者であれば、本発明の実施形態の範囲はこの説明において提供される特定の例示的なエンコーディングに限定されないことを認識するはずである。特に、本発明の実施形態は、PCIエクスプレストポロジにおいて低減されたヘッダアプローチを実装する代替的なエンコーディングと共に用いられ得る。また、本発明の実施形態は、PCIエクスプレス規格の将来のバージョンを含むバージョンと共に用いられ得る。加えて、本発明の実施形態は、現在及び将来の他のデータトランザクション規格にも適用可能である。

30

#### 【 0 0 5 6 】

本発明は、ここに説明される以外のソフトウェア、ハードウェア及びオペレーティングシステムの実装と共に実施され得る。ここに説明される機能を行うのに適する任意のソフトウェア、ハードウェア及びオペレーティングシステムの実装が用いられ得る。

#### 【 0 0 5 7 】

特定の機能の実装及びそれらの関係性を示す機能構築ブロックを補助として、本発明が上述のように説明されてきた。これらの機能構築ブロックの境界は、説明の便宜上ここでは適宜画定されてきた。特定の機能及びそれらの関係性が適切に実行される限りにおいて、代替的な境界が画定され得る。

40

#### 【 0 0 5 8 】

特定の実施形態の上述した説明は、本発明の一般的性質を十分に明らかにするであろうから、他者は、当業者における知識を適用することによって、過度の実験なしに、本発明の一般的概念から逸脱することなく、そのような特定の実施形態を容易に修正し且つ/又は種々の応用に適応させることができる。従って、そのような適応及び修正は、ここに提示されている教示及び指針に基いて、開示されている実施形態と均等なものの意味及び範囲の範疇にあることが意図されている。ここでの用語等は、説明を目的としたものであって限定を目的としていないことが理解されるべきであり、本出願書類の用語等は教示及び

50

指針の下で当業者によって解釈されるべきである。

【 0 0 5 9 】

〔 結論 〕

本発明の例示的な実施形態が提示されてきた。本発明はこれらの例に限定されない。これらの例は例示の目的でここに提示されており、限定の目的ではない。ここに含まれる教示に基く代替案（ここに説明されるものに対する均等なもの、拡張、変形、改変等を含む）が関連分野を含む当業者には明らかに明確である。そのような代替案は本発明の範囲及び精神に包含される。

【 0 0 6 0 】

本発明の広さ及び範囲は、上述したいかなる例示的な実施形態によっても限定されるべきではなく、以下の特許請求の範囲及びそれらと均等なものに従ってのみ画定されるべきである。

10

【 図 1 】

FIG. 1

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図 7 A】

| ポート名                  | PCIE_REG_ACCESS_CNTL [RW] | 説明                                                                                                                                                                                                  |

|-----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG_ACCESS_CAPABILITY | 1:0                       | 当該デバイスによりリポートされるバタ定義のメッセージ能力                                                                                                                                                                        |

| アクセス: R               | 0x0                       | を介してシステムアクセスを指定。                                                                                                                                                                                    |

| REG_ACCESS_GEN_EN     | 2                         | バタ定義のメッセージを介してシステムアクセスの発生を有効化。                                                                                                                                                                      |

| REG_ACCESS_RCV_DIS    | 3                         | 受信したバタ定義メッセージが介してシステムアクセスを無効化。他のバタ定義のメッセージを介してシステムアクセスを有効化するには、受け取ったメッセージを介してバタ定義のメッセージを介してシステムアクセスを無効化する。既述のと同様に、受け取ったメッセージを介してバタ定義のメッセージを介してシステムアクセスを無効化する。この操作は、データバスのデータを読み取る操作が有効化される場合に必要である。 |

| REG_ACCESS_DONE       | 4                         | 書込み済みに対しては、先にメモリアクセスが済んでから、読み出しが行われる。他の読み出しが可否であることを示す。REG_ACCESS_DONEが0の場合は、データバスのデータを読み取る操作が有効化される。                                                                                               |

| REG_ACCESS_TYPE       | 8:5                       | システムアクセスのタイプ。REG_ACCESS_TYPEのバタ定義のメッセージが、レジストラポート、REG_ACCESS_TYPEのバタ定義のメッセージが、レジストラポート、REG_ACCESS_TYPEのバタ定義のメッセージが、レジストラポートと共に送られる。                                                                 |

【図7B】

【圖 8】

【図9】

| PCIe REG ACCESS DATA (RW) |

|---------------------------|

| REG_ACCESS_WRITE_DATA     |

【図10】

【図11】

FIG. 11

---

フロントページの続き

(73)特許権者 508301087

エーティーアイ・テクノロジーズ・ユーエルシー

A T I T E C H N O L O G I E S U L C

カナダ、オンタリオ エル3ティー 7エックス6、マーカム、コマース バリー ドライブ

イースト 1

One Commerce Valley Drive East, Markham, Ontario, L3T 7X6 Canada

(74)代理人 100108833

弁理士 早川 裕司

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ベティー ラック

アメリカ合衆国 94107 カリフォルニア州、サン フランシスコ、キング ストリート 2

50、アパートメント 500

(72)発明者 ゴードン エフ. チャルク

カナダ国 エル6ティー 1ピー5 オンタリオ州、ブランプトン、アルダーベリー クレセント

29

審査官 小林 義晴

(56)参考文献 特開平09-128347 (JP, A)

特開平09-026853 (JP, A)

特開2010-044750 (JP, A)

特表2007-535006 (JP, A)

特開2009-205334 (JP, A)

特開2008-287573 (JP, A)

特開2010-026592 (JP, A)

米国特許出願公開第2006/0288098 (US, A1)

国際公開第2007/004525 (WO, A1)

PCI Express Base Specification Revision 1.1, PCI-SIG, 2005年 3月28日, Revision

1.1, pp.30-35,44-47,73-75

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 38