(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7179657号**

**(P7179657)**

(45)発行日 令和4年11月29日(2022.11.29)

(24)登録日 令和4年11月18日(2022.11.18)

(51)国際特許分類

H 02 M 3/155(2006.01)

F I

H 02 M

3/155

C

H 02 M

3/155

H

請求項の数 9 (全15頁)

(21)出願番号 特願2019-50973(P2019-50973)

(22)出願日 平成31年3月19日(2019.3.19)

(65)公開番号 特開2020-156170(P2020-156170)

A)

(43)公開日 令和2年9月24日(2020.9.24)

審査請求日 令和3年9月2日(2021.9.2)

(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73)特許権者 317011920

東芝デバイス＆ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74)代理人 100091982

弁理士 永井 浩之

(74)代理人 100091487

弁理士 中村 行孝

(74)代理人 100105153

弁理士 朝倉 悟

(74)代理人 100107582

弁理士 関根 賀

(74)代理人 100118843

最終頁に続く

(54)【発明の名称】 電源回路、及び電源回路の制御方法

**(57)【特許請求の範囲】****【請求項1】**

負荷に出力端子から電圧もしくは電流を供給する電源回路において、

一端が第1ノードに接続され、他端が前記出力端子側に接続される第1スイッチング素子と、

一端が前記第1ノードに接続され、他端が低電圧側端子に接続される第2スイッチング素子と、

前記第1スイッチング素子に並列に接続され、前記負荷側の方向に電流を流すダイオードとを有する第1回路と、

一端が前記低電圧側端子よりも高電位の電源と接続され、他端が第2ノードに接続される第3スイッチング素子と、一端が前記第2ノードに接続され、他端が前記低電圧側端子に接続される第4スイッチング素子とを有する第2回路と、

前記第1ノードと前記第2ノードとの間に接続されるインダクタと、

前記第1スイッチング素子の他端と前記出力端子との間に接続される第5スイッチング素子と、

前記出力端子を介して接続される前記負荷への出力に応じて、前記第1乃至第4スイッチング素子の内の少なくとも2つのスイッチング素子におけるスイッチング制御を行う際、

前記第5スイッチング素子を導通し、

前記第1乃至第4スイッチング素子のすべてを非導通にする際、前記第1乃至第4スイッチング素子を非導通にした時点から所定の遅延時間が経過した後に、前記第5スイッチング素子を非導通にする制御回路と、

を備える、電源回路。

10

20

**【請求項 2】**

前記制御回路は、前記第1、第2スイッチング素子を交互にスイッチングすることによる昇圧制御を行う場合に、前記第3、第5スイッチング素子を導通にし、且つ前記第4スイッチング素子を非導通にし、

前記第1乃至第3スイッチング素子を非導通にする場合に、前記第1乃至第3スイッチング素子を非導通にした時点から前記所定の遅延時間が経過した後に、前記第5スイッチング素子を非導通にする、請求項1に記載の電源回路。

**【請求項 3】**

前記制御回路は、前記第3、第4スイッチング素子を交互にスイッチングすることによる降圧制御を行う場合に、前記第1、第5スイッチング素子を導通にし、且つ前記第2スイッチング素子を非導通にし、

前記第1、第3、第4スイッチング素子を非導通にする場合に、前記第1、第3、第4スイッチング素子を非導通にした時点から所定の遅延時間が経過した後に、前記第5スイッチング素子を非導通にする、請求項1に記載の電源回路。

**【請求項 4】**

前記制御回路は、前記第1乃至第4スイッチング素子をスイッチングすることによる昇降圧制御を行う場合に、前記第5スイッチング素子を導通にし、

前記第1乃至第4スイッチング素子を非導通にする場合に、前記前記第1乃至第4スイッチング素子を非導通にした時点から所定の遅延時間が経過した後に、前記第3スイッチング素子を非導通にする、請求項1に記載の電源回路。

10

**【請求項 5】**

前記第5スイッチング素子に並列に接続され、負荷側の向きと反対方向に電流を流すダイオードを更に備える、請求項1に記載の電源回路。

**【請求項 6】**

前記制御回路は、前記所定の遅延時間を、前記第5スイッチング素子を介した放電により、前記インダクタに蓄積されるエネルギーが所定レベル以下になる時間に設定する、請求項1に記載の電源回路。

**【請求項 7】**

前記制御回路は、前記所定の遅延時間を前記インダクタに流れる電流の定数倍に比例する時間に設定する、請求項1に記載の電源回路。

30

**【請求項 8】**

前記制御回路は、前記負荷に供給される電圧が所定の範囲を超えた場合に、前記第1乃至第4スイッチング素子を非導通にする、請求項1に記載の電源回路。

**【請求項 9】**

負荷に出力端子から電圧もしくは電流を供給する電源回路において、

一端が第1ノードに接続される第1スイッチング素子と、一端が前記第1ノードに接続され、他端が低電圧側端子に接続される第2スイッチング素子と、前記第1スイッチング素子に並列に接続され、負荷側の方向に電流を流すダイオードとを有する第1回路と、

前記低電圧側端子よりも高電位の電源と前記第1ノードの間に接続されるインダクタと、

前記第1スイッチング素子の他端と出力端子との間に接続される第5スイッチング素子と、

40

前記出力端子を介して接続される前記負荷への出力に応じて、前記第1、第2スイッチング素子を交互にスイッチングすることによる昇圧制御を行う際、前記第5スイッチング素子を導通にし、

前記第1、第2スイッチング素子を非導通にする際、前記第1、第2スイッチング素子を非導通にした時点から所定の遅延時間が経過した後に、前記第5スイッチング素子を非導通にする、電源回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

50

本発明の実施形態は、電源回路、及び電源回路の制御方法に関する。

**【背景技術】**

**【0002】**

車載製品は自動運転実現のため、満たすべき機能安全要求が従来の製品に対してより厳しくなっている。このため、DCDCコンバータなどの電源回路は、異常状態を検出した際に、電源回路に接続される負荷を保護するために、その出力電圧を遮断することが行われる。しかしながら、このような突然の出力電圧の遮断によって、場合によっては電源回路自体が損傷してしまう可能性がある。

**【先行技術文献】**

**【特許文献】**

10

**【0003】**

**【文献】特開平11-146635号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

本発明が解決しようとする課題は、突然に出力電圧を遮断するような場合であっても、損傷を生じさせない電源回路、及び電源回路の制御方法を提供することである。

**【課題を解決するための手段】**

**【0005】**

本実施形態によれば、負荷に出力端子から電圧もしくは電流を供給する電源回路は、第1回路と、第2回路と、インダクタと、第5スイッチング素子と、制御回路と、を備える。第1回路は、一端が第1ノードに接続される第1スイッチング素子と、一端が第1ノードに接続され、他端が低電圧側端子に接続される第2スイッチング素子と、第1スイッチング素子に並列に接続され、負荷側の方向に電流を流すダイオードとを有する。第2回路は、一端が低電圧側端子よりも高電位の電源と接続され、他端が第2ノードに接続される第3スイッチング素子と、一端が第2ノードに接続され、他端が低電圧側端子に接続される第4スイッチング素子とを有する。インダクタは、第1ノードと第2ノードとの間に接続される。第5スイッチング素子は、第1スイッチング素子の他端と出力端子との間に接続される。制御回路は、出力端子を介して接続される負荷への出力に応じて、第1乃至第4スイッチング素子の内の少なくとも2つのスイッチング素子におけるスイッチング制御を行う際、第5スイッチング素子を導通し、第1乃至第4スイッチング素子を非導通にする際、第1乃至第4スイッチング素子を非導通にした時点から遅延時間が経過した後に、第5スイッチング素子を非導通にする。

20

**【図面の簡単な説明】**

**【0006】**

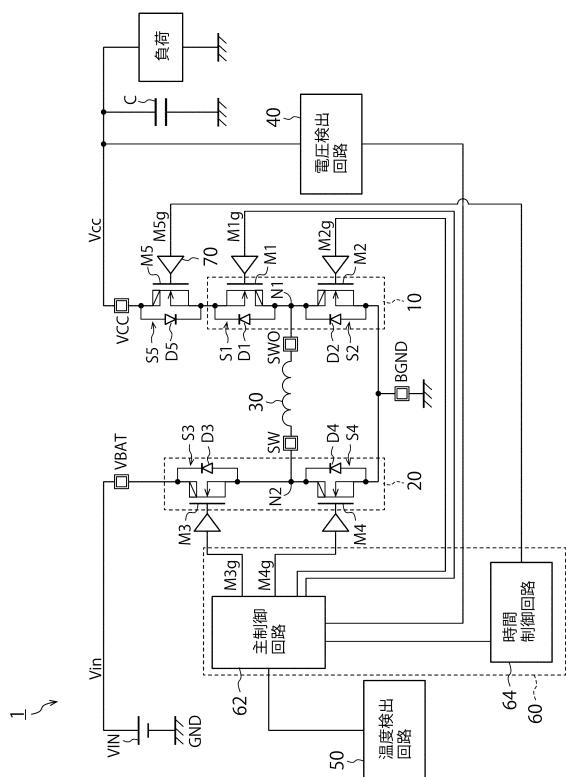

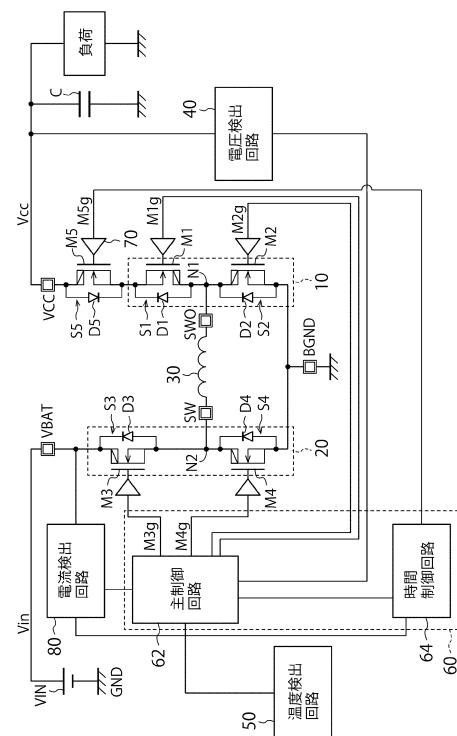

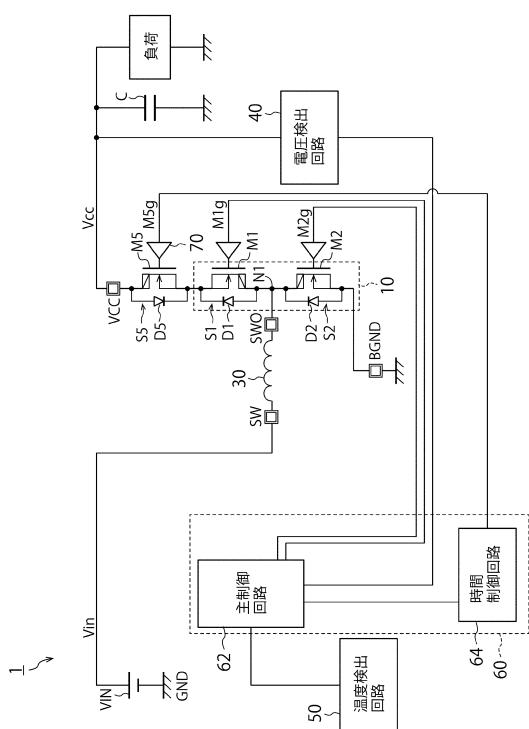

**【図1】第1実施形態による電源回路の構成を示すブロック図。**

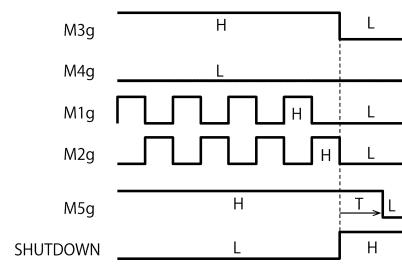

**【図2A】昇圧モードにおけるタイミングチャート。**

30

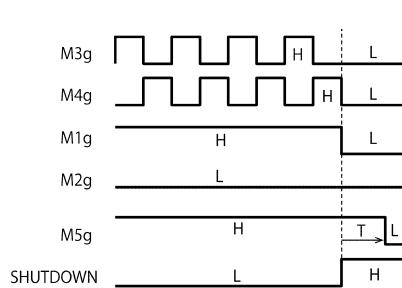

**【図2B】降圧モードにおけるタイミングチャート。**

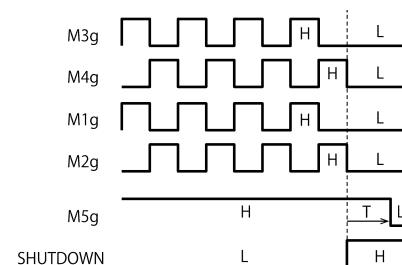

**【図2C】昇降圧モードにおけるタイミングチャート。**

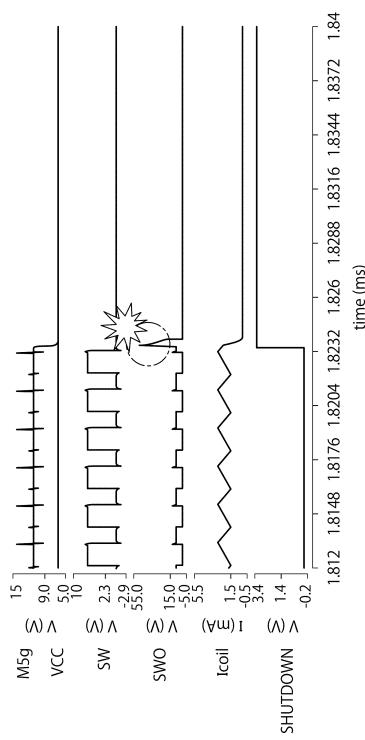

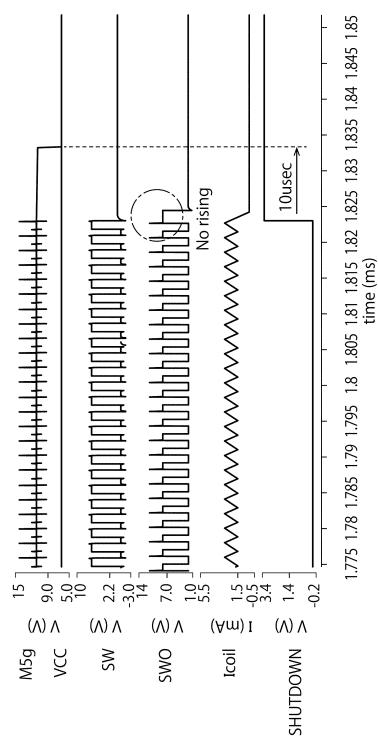

**【図3A】遅延時間T = 0として遮断処理を行った場合のタイミングチャート。**

40

**【図3B】遅延時間T ((1)式)として遮断処理を行った場合のタイミングチャート。**

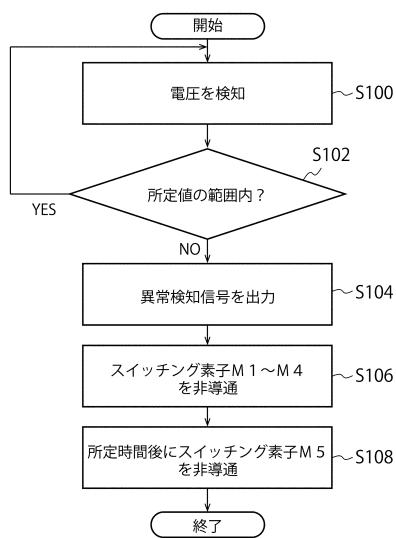

**【図4】電源回路の制御方法例を示すフローチャート。**

**【図5】第2実施形態による電源回路の構成を示すブロック図。**

**【図6】第3実施形態による電源回路の構成を示すブロック図。**

**【図7】第3実施形態に係る第1回路のタイミングチャート。**

**【発明を実施するための形態】**

**【0007】**

以下、本発明の実施形態に係る電源回路、及び電源回路の制御方法について、図面を参照しながら詳細に説明する。なお、以下に示す実施形態は、本発明の実施形態の一例であって、本発明はこれらの実施形態に限定して解釈されるものではない。また、本実施形態

50

で参照する図面において、同一部分又は同様な機能を有する部分には同一の符号又は類似の符号を付し、その繰り返しの説明は省略する場合がある。また、図面の寸法比率は説明の都合上、実時の比率とは異なる場合や、構成の一部が図面から省略される場合がある。

#### (第1実施形態)

##### 【0008】

図1は、第1実施形態による電源回路1の構成を示すブロック図である。

電源回路1は、高電位側電源VINから供給される入力電圧Vinを制御して、電源電圧出力端子VCCに接続された負荷に対し、電源電圧出力端子VCCから出力電圧Vccを供給する回路である。

##### 【0009】

電源回路1は、第1回路10、第2回路20、インダクタ30、電圧検出回路40、温度検出回路50、制御回路60、複数のドライバ70、第5スイッチング部S5、及び、コンデンサCを備える。電源回路1の上記の各構成については後述する。

10

##### 【0010】

また、図1には、電源回路1の入力側に相当する高電位側電源VINと、電源回路1の出力側に相当し、負荷に接続される電源電圧出力端子VCCが図示されている。尚、ここで高電位側電源VINの電位はVin、電源電圧出力端子VCCの電位はVccとする。

##### 【0011】

さらに、図1には、第1回路10、第2回路20、及び第5スイッチング部S5を制御するためのゲート信号M1g～M5g、グランドGND、電源端子VBAT、低電圧側端子BGND、スイッチ端子SW、SWO、負荷、ノードN1、N2等が図示されている。

20

##### 【0012】

第1回路10は、昇圧回路であり、ノードN1を介して直列に接続される第1スイッチング部S1と、第2スイッチング部S2とを有する。第1スイッチング部S1のノードN1と反対側の端部は、第5スイッチング部S5を介して電源電圧出力端子VCCに接続される。

##### 【0013】

第1スイッチング部S1は、第1スイッチング素子M1と、第1スイッチング素子M1と並列に接続され、負荷側の方向に電流を流すダイオードD1を有する。この第1スイッチング部S1は、例えばnチャネル型MOSFETであり、第1スイッチング素子M1は、ゲート信号M1gがハイレベル信号(H信号)である場合に、導通となり、ロウレベル信号(L信号)である場合に、非導通となるように制御される。

30

##### 【0014】

第2スイッチング部S2も、第1スイッチング部S1と同等の構造である。すなわち、第2スイッチング部S2は、一端が第1ノードN1に接続され、第1ノードの反対側の他端は低電圧側端子BGNDに接続される第2スイッチング素子M2と、第2スイッチング素子M2と並列に接続され、負荷側の方向に電流を流すダイオードD2と、を有する。第2スイッチング素子M2は、第1スイッチング素子M1と同様に、ゲート信号M2gの「H」、「L」信号により、導通、非導通が制御される。

##### 【0015】

第2回路20は、降圧回路であり、ノードN2を介して直列に接続される第3スイッチング部S3と、第4スイッチング部S4とを有する。第3スイッチング部S3、及び、第4スイッチング部S4も、第1スイッチング部S1、第2スイッチング部S2と同等の構造である。すなわち、第2回路20は、一端が高電位側電源VINと接続され、他端が第2ノードN2に接続される第3スイッチング素子M3と、一端が第2ノードN2に接続され、他端が低電圧側端子BGNDに接続される第4スイッチング素子M4を備える。さらに、第3スイッチング素子M3と第4スイッチング素子M4は、それぞれ第3スイッチング素子M3と並列に接続され、高電位側電源VIN側の向きに電流が流れるダイオードD3と、第4スイッチング素子M4と並列に接続され、高電位側電源VIN側の向きに電流が流れるダイオードD4とが対になっている。また、第3スイッチング素子M3及び第4

40

50

スイッチング素子M 4 の導通、非導通は、それぞれ、ゲート信号M 3 g 及びM 4 g によって制御される。

【0016】

インダクタ30は、第1ノードN1に接続されるスイッチ端子SW0と第2ノードN2に接続されるスイッチ端子SWとの間に接続される。

【0017】

第5スイッチング部S5は、第1スイッチング部10の第1スイッチング素子M1の他端（ノードN1の反対側のノード）と電源電圧出力端子VCCとの間に接続される。第5スイッチング部S5も第1スイッチング部S1と同等の構造である。すなわち、第5スイッチング素子M5は、一端が第1スイッチング素子M1の他端（ノードN1の反対側のノード）に接続され、他端が電源電圧出力端子VCCに接続される。さらに、ダイオードD5は、第5スイッチング素子M5に並列に接続され、負荷側の方向と反対の方向に電流を流す。第5スイッチング素子M5は、第1スイッチング素子M1と同様に、ゲート信号M5gの「H」、「L」信号により、導通、非導通が制御される。なお、本実施形態に係る第1～第5スイッチング部S1～S5は、nチャネルMOSFETで構成されるが、これに限定されず、例えばpチャネル型MOSFETなどで構成してもよい。

10

【0018】

電圧検出回路（出力短絡保護回路）40は、電源電圧出力端子VCCと、制御回路60とに接続される。電圧検出回路40は、電源電圧出力端子VCCから負荷に供給されるべき出力電圧Vccを検知し、制御回路60にその電圧情報を含む電圧信号を出力する。もし、電圧検出回路40が検知した出力電圧Vccの電圧値が予め定めた所定範囲を超えた場合に、異常検知信号を制御回路60に出力する。

20

【0019】

尚、この実施形態の説明では、電圧検出回路40は、出力電圧Vccを検知したが、電源電圧出力端子VCCからの出力電流を検知するようにしてもよい。その場合、電源電圧出力端子VCCからの出力電流が予め定めた所定範囲を超えた場合に、異常検知信号を制御回路60に出力する。

【0020】

温度検出回路（過熱保護回路）50は、制御回路60に接続される。温度検出回路50は、電源回路1内、例えばインダクタ30が配置される半導体チップの温度を検知し、温度の情報を含む温度信号を制御回路60に出力する。また、温度検出回路50は、温度が予め定めた所定範囲を超える場合に、異常検知信号を制御回路60に出力する。

30

【0021】

高電位側電源VINは、電源端子VBATに接続され、直流電圧を出力する直流電源である。コンデンサCは、電源電圧出力端子VCCと低電圧側端子BGNDとの間に接続される。

【0022】

制御回路60は、第1～第5スイッチング素子M1～M5それぞれのゲートに対応する複数のドライバ70を介して接続される。制御回路60は、主制御回路62（例えばCPUを含む）と時間制御回路64とを含んで構成され、負荷に供給される出力電圧Vccの値に応じて、第1～第5スイッチング素子M1～M5を制御するゲート信号M1g～M5gを出力する。

40

【0023】

より具体的には、主制御回路62は、出力電圧Vccに応じて、第1～第4スイッチング素子M1～M4に対し、昇圧制御を行う昇圧モード、降圧制御を行う降圧モード、及び、昇降圧制御を行う昇降圧モードを切り替えるスイッチング制御を可能とする。このスイッチング制御は、第1～第4スイッチング素子M1～M4の内の少なくとも2つのスイッチング素子におけるスイッチング制御を行う。

【0024】

また、主制御回路62は、電圧検出回路40、及び温度検出回路50のいずれかからの

50

異常検知信号に応じて、第1～第4スイッチング素子M1～M4を全て非導通にする。つまり、異常を検出したとき、主制御回路62は、第1～第4スイッチング素子M1～M4に対するゲート信号M1g～M4gをすべてロウレベル(L)信号にする。このとき、第5スイッチング素子M5のゲート信号M5gは、まだハイレベル(H)信号のままである。

#### 【0025】

時間制御回路64は、第5スイッチング素子M5を導通、または非導通にするタイミングを遮断信号SHUTDOWNにより制御する。例えば、異常検知信号に応じて、第5スイッチング素子M5を非導通にする場合に、第1～第4スイッチング素子M1～M4を非導通にした時点から第5スイッチング素子M5を非導通にするまでの遅延時間Tを制御する。具体的には、時間制御回路64は、遅延時間Tをインダクタに蓄積されるエネルギーが所定レベル以下になる時間に設定し、そのタイミングで第5スイッチング素子M5のゲート信号M5gをハイレベル信号からロウレベル信号に切り替え、第5スイッチング素子M5を非導通にする。

10

#### 【0026】

遅延時間Tは、例えば(1)式を用いて設定することができる。ここでLは、インダクタ30のインダクタンスを示し、Cは、コンデンサCの出力容量を示し、WOUTは、負荷の負荷電力を示し、Iはインダクタ30に流れるコイル電流を示す。なお、コイル電流Iは、コイル電流Icoilとして示される場合がある。

#### 【数1】

$$T = \frac{1}{2} \sqrt{L \times C} \frac{1}{W_{\text{OUT}}} I \quad (1)$$

20

#### 【0027】

このように、制御回路60は、電源電圧出力端子VCCを介して接続される負荷への出力電圧Vccに応じて、第1～第4スイッチング素子M1～M4の内の少なくとも2つのスイッチング素子におけるスイッチング制御を行う場合に、第5スイッチング素子M5を導通にし、第1～第4スイッチング素子M1～M4を非導通にする場合に、第1～第4スイッチング素子M1～M4を全て非導通にした時点から遅延時間Tが経過した後に、第5スイッチング素子M5を非導通にする。

30

#### 【0028】

複数のドライバ70のそれぞれは、対応する第1～第5スイッチング素子M1～M5と、制御回路60に接続される。複数のドライバ70のそれぞれは、対応する第1～第5スイッチング素子M1～M5を制御するゲート信号M1g～M5gを増幅する。

#### 【0029】

以上が第1実施形態に係る電源回路1の構成の説明であるが、以下に動作例について説明する。

#### 【0030】

図2Aは、昇圧モードにおける第1～第5スイッチング素子M1～M5のゲート信号M1g～M5gと遮断信号SHUTDOWNの関係を示すタイミングチャートである。図2Bは、降圧モードにおけるスイッチング素子M1～M5のタイミングチャートである。図2Cは、昇降圧モードにおけるスイッチング素子M1～M5のタイミングチャートである。上から順にゲート信号M3g、M4g、M2g、M1g、M5g、遮断信号SHUTDOWNを示している。縦軸は各信号の値であり、横軸は時間を示している。遅延時間Tは(1)式で示される時間である。この実施形態では、第1～第5スイッチング素子M1～M5は、H信号で導通にされ、L信号で非導通にされるものとする。

40

#### 【0031】

図2Aに示すように、第3、第5スイッチング素子M3、M5を導通にし、且つ第4スイッチング素子M4を非導通にすると電源回路1は、Vin < Vccの関係を有する昇圧型のDCDCコンバータとして動作する。この場合の出力電圧Vccは、(2)式で示す

50

ように、第2スイッチング素子M2の導通時間の割合D<sub>t g 2</sub>により決定される。すなわち、制御回路60は、第1、第2スイッチング素子M1、M2を交互にスイッチングすることによる昇圧制御を行う場合に、第3、第5スイッチング素子M3、M5を導通にし、且つ第4スイッチング素子M4を非導通にする。ここで、D<sub>t g 2</sub>は、第2スイッチング素子M2の導通時間を第1スイッチング素子M1の導通時間と第2スイッチング素子M2の導通時間との加算値で除算した値である。なお、D<sub>t g 2</sub>は1未満の値である。

#### 【数2】

$$V_{CC} = \frac{1}{1-D_{t g 2}} \times V_{IN} \quad (2)$$

10

#### 【0032】

主制御回路62は、通常の昇圧動作時には、ゲート信号M1g及びゲート信号M2gのハイレベル信号(H信号)とロウレベル信号(L信号)を交互に発生する。これにより、ゲート信号M1gがハイレベル信号である場合にスイッチング素子M1は導通となり、スイッチング素子M2は非導通になる。逆に、ゲート信号M1gがロウレベル信号である場合にスイッチング素子M1は非導通となり、スイッチング素子M2は導通となる。

#### 【0033】

一方で、前述したように電圧検出回路40或いは温度検出回路50から異常検知信号が入力されると、主制御回路62は、スイッチング素子M3、M4、M1、及びM2にゲート信号M3g、M4g、M1g、及び、M2gとしてロウレベル信号(L信号)を与える。同時に、主制御回路62は、異常検知信号の入力によって、時間制御回路62に遮断信号SHUTDOWNとしてハイレベル信号(H信号)を与える。この時間制御回路62により、所定の遅延時間T((1)式)が経過した後に、第5スイッチング素子M5へのゲート信号M5gがロウレベル信号に切り替わり、第5スイッチング素子M5は非導通となる。

20

#### 【0034】

このように、制御回路60は、昇圧制御を行っている時に異常検知信号が入力されると、第1～第3スイッチング素子M1、M2、M3を非導通とする。その時点から、所定の遅延時間Tが経過した後に、第5スイッチング素子M5を非導通にする。これにより、遅延時間T中に、インダクタ30のコイルエネルギーが電源電圧出力端子VCCを介して放電することができるため、第5スイッチング素子M5を非導通にした後のSWO端子における過電圧の発生を抑制可能となる。

30

#### 【0035】

図2Bに示すように、第1、第5スイッチング素子M1、M5を導通にし、且つ第2スイッチング素子M2を非導通にすると電源回路1は、V<sub>IN</sub> > V<sub>CC</sub>の関係を有する降圧型のDCDCコンバータとして動作する。この場合の出力電圧V<sub>CC</sub>は、(3)式で示すように、第3スイッチング素子M3の導通時間の割合D<sub>t g 3</sub>により決定される。すなわち、制御回路60は、第3、第4スイッチング素子M3、M4を交互にスイッチングすることによる降圧制御を行う場合に、第1、第5スイッチング素子M1、M5を導通にし、且つ第2スイッチング素子M4を非導通にする。ここで、D<sub>t g 3</sub>は、第3スイッチング素子M3の導通時間を第3スイッチング素子M3の導通時間と第4スイッチング素子M4の導通時間との加算値で除算した値である。なお、D<sub>t g 3</sub>は1未満の値である。

40

#### 【数3】

$$V_{CC} = D_{t g 3} \times V_{IN} \quad (3)$$

#### 【0036】

主制御回路62は、通常の降圧動作時には、ゲート信号M3gとゲート信号M4gのハイレベル信号(H信号)とロウレベル信号(L信号)を交互に発生する。これにより、ゲート信号M3gがハイレベル信号である場合にスイッチング素子M3が導通となり、スイ

50

ツチング素子M 4 は非導通になる。逆に、ゲート信号M 3 g がロウレベル信号である場合にスイッチング素子M 3 が非導通となり、スイッチング素子M 4 は導通になる。

#### 【 0 0 3 7 】

一方で、前述したように電圧検出回路4 0 或いは温度検出回路5 0 から異常検知信号が入力されると、主制御回路6 2 は、スイッチング素子M 3 、M 4 、M 1 、及びM 2 にゲート信号M 3 g 、M 4 g 、M 1 g 、及び、M 2 g としてロウレベル信号（L 信号）を与える。同時に、主制御回路6 2 は、異常検知信号の入力によって、時間制御回路6 2 に遮断信号S H U T D O W N としてハイレベル信号（H 信号）を与える。この時間制御回路6 2 により、所定の遅延時間T ((1)式) が経過した後に、第5スイッチング素子M 5 へのゲート信号M 5 g がロウレベル信号に切り替わり、第5スイッチング素子M 5 は非導通となる。

10

#### 【 0 0 3 8 】

このように、制御回路6 0 は、降圧制御を行っている時に異常検知信号が入力されると、スイッチング素子M 1 、M 3 、M 4 を非導通とする。その時点から、所定の遅延時間T が経過した後に、第5スイッチング素子M 5 を非導通にする。これにより、遅延時間T 中に、インダクタ3 0 のコイルエネルギーが電源電圧出力端子V C C を介して放電することができるため、第5スイッチング素子M 5 を非導通にした後のS W O 端子における過電圧の発生を抑制可能となる。

#### 【 0 0 3 9 】

図2 C に示すように、制御回路6 0 は、第1 ~ 第4スイッチング素子M 1 ~ M 4 をスイッチングすることによる昇降圧制御を行う場合に、第5スイッチング素子M 5 を導通にする。

20

#### 【 0 0 4 0 】

主制御回路6 2 は、通常の昇降圧動作時には、ゲート信号M 1 g とゲート信号M 3 g を同期させ、ゲート信号M 2 g とゲート信号M 4 g を同期させる。これにより、ゲート信号M 1 g 、M 3 g がハイレベル信号である場合にスイッチング素子M 1 、M 3 が導通となり、スイッチング素子M 2 、M 4 は非導通になる。逆に、ゲート信号M 1 g 、M 3 g がロウレベル信号である場合にスイッチング素子M 1 、M 3 が非導通となり、スイッチング素子M 2 、M 4 は導通になる。

30

#### 【 0 0 4 1 】

一方で、前述したように電圧検出回路4 0 或いは温度検出回路5 0 から異常検知信号が入力されると、主制御回路6 2 は、スイッチング素子M 3 、M 4 、M 1 、及びM 2 にゲート信号M 3 g 、M 4 g 、M 1 g 、及び、M 2 g としてロウレベル信号（L 信号）を与える。同時に、主制御回路6 2 は、異常検知信号の入力によって、時間制御回路6 2 に遮断信号S H U T D O W N としてハイレベル信号（H 信号）を与える。この時間制御回路6 2 により、所定の遅延時間T ((1)式) が経過した後に、第5スイッチング素子M 5 へのゲート信号M 5 g がロウレベル信号に切り替わり、第5スイッチング素子M 5 は非導通となる。

#### 【 0 0 4 2 】

このように、制御回路6 0 は、昇降圧制御を行っている時に異常検知信号が入力されると、第1 ~ 第4スイッチング素子M 1 ~ M 4 を非導通とする。その時点から、所定の遅延時間T が経過した後に、第5スイッチング素子M 5 を非導通にする。これにより、遅延時間T 中に、インダクタ3 0 のコイルエネルギーが電源電圧出力端子V C C を介して放電することができるため、第5スイッチング素子M 5 を非導通にした後のS W O 端子における過電圧の発生を抑制可能となる。

40

#### 【 0 0 4 3 】

図3 A は、昇降圧モード時に遅延時間T = 0 として遮断処理を行った場合のタイミングチャートである。図3 B は、昇降圧モード時に遅延時間T を(1)式に従い設定した場合に遮断処理を行った場合のタイミングチャートである。上から第5スイッチング素子M 5 、電源電圧出力端子V C C 、S W 端子、S W O 端子の電圧、コンダクタ3 0 のコイル電流

50

I c o i l、遮断信号 S H U T D O W N を示している。

【 0 0 4 4 】

図 3 A に示すように、第 5 スイッチング素子 M 5 が非導通にされた場合に、コンダクタ 3 0 のコイル電流 I c o i l の流れる経路がなくなるため SWO 端子の過電圧は ( 4 ) 式で示す電圧まで上昇してしまう。この過電圧 V が第 2 スイッチング素子 M 2 の耐圧を超える場合、第 2 スイッチング素子 M 2 が破壊されてしまう。ここで C p a r a は端子 SWO における寄生容量である。

【 数 4 】

$$V = \sqrt{\frac{L}{C_{para}}} \cdot I \quad (4)$$

10

【 0 0 4 5 】

一方で、図 3 B に示すように、昇降圧モード時に遅延時間 T を ( 1 ) 式に従い設定した場合には、遮断処理を行ってもインダクタ 3 0 による過電圧 V の発生は抑制される。

【 0 0 4 6 】

図 4 は、電源回路 1 の制御方法例を示すフローチャートである。ここでは、昇降圧モードにおける電圧異常の検知時の動作例を説明する。

【 0 0 4 7 】

電圧検出回路 4 0 は、電源電圧出力端子 V C C の電圧 V c c を検知し ( ステップ S 1 0 0 )、電圧が所定範囲内か否かを判定する ( ステップ S 1 0 2 )。電圧検出回路 4 0 は、電圧が所定範囲内である場合 ( ステップ S 1 0 2 の Y E S )、電圧信号を制御回路 6 0 に出力し、ステップ S 1 0 0 からの処理を繰り返す。

20

【 0 0 4 8 】

一方で、電圧検出回路 4 0 は、電圧 V c c が所定範囲内でない場合 ( ステップ S 1 0 2 の N O )、異常検知信号を制御回路 6 0 に出力する ( ステップ S 1 0 4 )。続けて、主制御回路 6 2 は、ゲート信号 M 3 g、M 4 g、M 1 g、及び、M 2 g としてロウレベル信号 ( L 信号 ) を与える。同時に、主制御回路 6 2 は、異常検知信号の入力によって、時間制御回路 6 2 に遮断信号 S H U T D O W N としてハイレベル信号 ( H 信号 ) を与える ( ステップ S 1 0 6 )。

30

【 0 0 4 9 】

続けて時間制御回路 6 2 は、所定の遅延時間 T ( ( 1 ) 式 ) が経過した後に、第 5 スイッチング素子 M 5 へのゲート信号 M 5 g をロウレベル信号に切り替え、第 5 スイッチング素子 M 5 を非導通にし ( ステップ S 1 0 8 )、全体処理を終了する。

【 0 0 5 0 】

以上のように、本実施形態によれば、第 1 ~ 第 4 スイッチング素子 M 1 ~ M 4 を非導通にする場合に、第 1 ~ 第 4 スイッチング素子 M 1 ~ M 4 を全て非導通にした時点から遅延時間 T が経過した後に、第 5 スイッチング素子 M 5 を非導通にすることとした。これにより、遅延時間 T 中に、インダクタ 3 0 のコイルエネルギーが電源電圧出力端子 V C C を介して出力容量 C、および負荷に放電されるため、第 5 スイッチング素子 M 5 を非導通にした後のインダクタ 3 0 による過電圧の発生を抑制可能となる。

40

【 0 0 5 1 】

( 第 2 実施形態 )

第 1 実施形態に係る時間制御回路 6 4 が設定する遅延時間 T は、固定値であるのに対し、第 2 実施形態に係る時間制御回路 6 4 は、遅延時間 T が変動値であることで相違する。以下では第 1 実施形態に係る電源回路 1 と相違する点に関して説明する。

【 0 0 5 2 】

図 5 は、第 2 実施形態による電源回路 1 の構成を示すブロック図である。図 5 に示すように、電流検出回路 8 0 を更に備える点で第 1 実施形態に係る電源回路 1 と相違する。

【 0 0 5 3 】

50

電流検出回路 8 0 は、電源端子 V B A T と制御回路 6 0 とに接続される。電流検出回路 8 0 は、インダクタ 3 0 を流れるコイル電流 I を検出し、コイル電流 I の情報を含む電流信号を制御回路 6 0 に出力する。

#### 【 0 0 5 4 】

時間制御回路 6 4 は、コイル電流 I に基づき、遅延時間 T (( 5 )式) を演算する。すなわち、時間制御回路 6 4 はコイル電流 I の定数 A 倍に比例した遅延時間 T を設定する。W<sub>min</sub> は、設計値などで定められている電源回路 1 の負荷における最小負荷電力である。

#### 【 数 5 】

$$T = \frac{1}{2} \sqrt{LC_{VCC}} \quad \frac{1}{W_{min}} I \propto AI$$

10

(5)

#### 【 0 0 5 5 】

以上のように、本実施形態によれば、時間制御回路 6 4 はコイル電流 I の定数 A 倍に比例した遅延時間 T を設定することとした。これにより、遅延時間 T を固定値とするよりも、過電圧の発生を抑制しつつ、より短い時間で第 5 スイッチング素子 M 5 を非導通にすることが可能となる。

#### 【 0 0 5 6 】

( 第 3 実施形態 )

第 1 実施形態に係る電源回路 1 が降圧用の第 2 回路 2 0 を有していたのに対し、第 3 実施形態に係る電源回路 1 は、第 2 回路 2 0 を有していないことで相違する。以下では第 1 実施形態に係る電源回路 1 と相違する点に関して説明する。

20

#### 【 0 0 5 7 】

図 6 は、第 3 実施形態による電源回路 1 の構成を示すブロック図である。図 6 に示すように、第 2 回路 2 0 を有していない点で第 1 実施形態に係る電源回路 1 と相違する。

#### 【 0 0 5 8 】

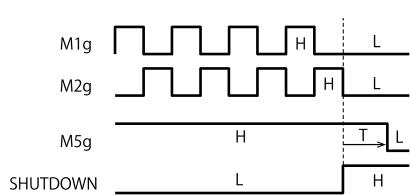

図 7 は、第 3 実施形態に係る第 1 、第 2 、第 5 スイッチング素子 M 1 、 M 2 、 M 5 のゲート信号 M 1 g 、 M 2 g 、 M 5 g と遮断信号 S H U T D O W N の関係を示すタイミングチャートである。上から順にゲート信号 M 1 g 、 M 2 g 、 M 5 g 、遮断信号 S H U T D O W N を示している。縦軸は各信号の値であり、横軸は時間を示している。この実施形態では、第 1 、第 2 、第 5 スイッチング素子 M 1 、 M 2 、 M 5 は、 H 信号で導通にされ、 L 信号で非導通にされるものとする。

30

#### 【 0 0 5 9 】

図 7 に示すように、第 5 スイッチング素子 M 5 を導通にし、第 1 、第 2 スイッチング素子 M 1 、 M 2 を交互にスイッチングする。これにより、電源回路 1 は、 V i n < V c c の関係を有する昇圧型の D C D C コンバータとして動作する。この場合の出力電圧 V c c は、( 2 ) 式で示すように、第 1 スイッチング素子 M 1 の導通時間の割合 D t g 1 により決定される。

#### 【 0 0 6 0 】

主制御回路 6 2 は、通常の昇圧動作時には、ゲート信号 M 1 g とゲート信号 M 2 g のハイレベル信号 ( H 信号 ) とロウレベル信号 ( L 信号 ) を交互に発生する。これにより、ゲート信号 M 1 g がハイレベル信号である場合にスイッチング素子 M 1 が導通となり、スイッチング素子 M 2 は非導通になる。逆に、ゲート信号 M 1 g がロウレベル信号である場合にスイッチング素子 M 1 が非導通となり、スイッチング素子 M 2 は導通となる。

40

#### 【 0 0 6 1 】

一方で、前述したように電圧検出回路 4 0 或いは温度検出回路 5 0 から異常検知信号が入力されると、主制御回路 6 2 は、スイッチング素子 M 1 、及び M 2 にゲート信号 M 1 g 、及び、 M 2 g としてロウレベル信号 ( L 信号 ) を与える。同時に、主制御回路 6 2 は、異常検知信号の入力によって、時間制御回路 6 2 に遮断信号 S H U T D O W N としてハイレベル信号 ( H 信号 ) を与える。この時間制御回路 6 2 により、所定の遅延時間 T (( 1

50

)式)が経過した後に、第5スイッチング素子M5へのゲート信号M5gがロウレベル信号に切り替わり、第5スイッチング素子M5は非導通となる。

#### 【0062】

以上のように、本実施形態によれば、制御回路60は、第1、第2スイッチング素子M1、M2を非導通にする場合に、第1、第2スイッチング素子M1、M2を非導通にした時点から遅延時間Tが経過した後に、第5スイッチング素子M5を非導通にする。この遅延時間T中に、インダクタ30のコイルエネルギーが電源電圧出力端子VCCを介して出力容量C、および負荷に放電されるため、第5スイッチング素子M5を非導通にした後のSWO端子の電圧の上昇を防ぐことが可能となる。

#### 【0063】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。

例えば、電源回路として電源電圧出力回路の例について説明したが、電流源としての電源回路に対しても同様に適用可能である。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0064】

1：電源回路、10：第1回路、20：第2回路、30：インダクタ、60：制御回路

、M1～M5：第1～第5スイッチング素子、D1：第1ダイオード、D5：第5ダイオード、N1：第1ノード、N2：第2ノード、BGND：低電圧側端子、VIN：高電位側電源、VCC：電源電圧出力端子、T：遅延時間。

10

20

30

40

50

## 【図面】

【図 1】

【図 2 A】

10

20

【図 2 B】

【図 2 C】

30

40

50

【図 3 A】

【図 3 B】

10

20

30

40

【図 4】

【図 5】

50

【図 6】

【図 7】

10

20

30

40

50

---

フロントページの続き

弁理士 赤岡 明

(74)代理人 100125151

弁理士 新畠 弘之

(72)発明者 大塚 正臣

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

(72)発明者 山中 祐司

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

審査官 土井 悠生

(56)参考文献 特開2016-131446 (JP, A)

特開2017-184301 (JP, A)

特開2014-116996 (JP, A)

特開2014-204625 (JP, A)

特開2015-088238 (JP, A)

米国特許出願公開第2015/0280486 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H02M 1/00 - 7/98

B60L 1/00 - 3/12

B60L 7/00 - 13/00

B60L 15/00 - 58/40

G05F 1/00 - 1/44

G05F 1/45 - 7/00

H02H 7/00

H02H 7/10 - 7/20