(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6340079号

(P6340079)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月18日(2018.5.18)

(51) Int.Cl.

F 1

G02F 1/15 (2006.01)

G09F 9/30 (2006.01)G02F 1/15

G09F 9/30505

380

請求項の数 12 (全 23 頁)

(21) 出願番号 特願2016-534714 (P2016-534714)

(86) (22) 出願日 平成26年12月3日 (2014.12.3)

(65) 公表番号 特表2016-540248 (P2016-540248A)

(43) 公表日 平成28年12月22日 (2016.12.22)

(86) 國際出願番号 PCT/US2014/068357

(87) 國際公開番号 WO2015/084952

(87) 國際公開日 平成27年6月11日 (2015.6.11)

審査請求日 平成28年11月7日 (2016.11.7)

(31) 優先権主張番号 14/095,308

(32) 優先日 平成25年12月3日 (2013.12.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 504416080

セイジ・エレクトロクロミクス、インコーポレイテッド

アメリカ合衆国ミネソタ州55021, フィアボルト, ワン・セイジ・ウェイ

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

最終頁に続く

(54) 【発明の名称】電気活性素子および電気活性素子の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

エレクトロクロミック素子であって、

第1の導電層および第2の導電層と、前記第1の導電層および前記第2の導電層の間に挟まれる1つまたは複数の電気活性層とを含み、

前記第1の導電層は、第1のバスバーに連結された第1の部分と、第2のバスバーに結合された第2の部分とを含み、

前記エレクトロクロミック素子の1つまたは複数の隣接層は、該複数の電気活性層の第1の部分および第2の部分の間に物理的な分離を含み、前記第1および第2のバスバーを互いに電気的に分離し、前記物理的な分離は、前記第1の部分および前記第2の部分のそれぞれの各テーパー状側壁を規定し、前記1つまたは複数の隣接層は前記第1の導電層および前記第2の導電層の一方を含み、

前記エレクトロクロミック素子の残りの層は、前記物理的な分離を覆って前記1つまたは複数の隣接層上に形成され、前記残りの層は前記第1の導電層および前記第2の導電層の他方を含む、エレクトロクロミック素子。

## 【請求項2】

エレクトロクロミック素子の作製方法であって、

基板を設置することと、

前記基板の表面上に前記エレクトロクロミック素子の1つまたは複数の隣接層を形成することと、

10

20

上に形成される前記 1 つまたは複数の隣接層を有する前記基板の側に向けてスクリービング手段を位置決めすることと、

前記スクリービング手段を用いて前記基板から前記エレクトロクロミック素子の前記 1 つまたは複数の隣接層の一部を除去することによって、前記 1 つまたは複数の隣接層の第 1 の部分および第 2 の部分の間に物理的な分離を形成して、前記物理的な分離は前記第 1 の部分および前記第 2 の部分のそれぞれの各テーパー状側壁を規定することと、

前記 1 つまたは複数の隣接層の前記物理的な分離を覆う前記エレクトロクロミック素子の 1 つまたは複数の残りの層を形成することと

を含み、

前記第 1 の部分は第 1 のバスバーに連結され、前記第 2 の部分は第 2 のバスバーに結合され、前記第 1 および第 2 の部分の間の前記物理的な分離は前記第 1 および第 2 のバスバーを互いに電気的に分離する、方法。 10

【請求項 3】

前記各テーパー状側壁は、実質的に直線の輪郭または実質的にガウシアンの輪郭を有する、請求項 1 記載のエレクトロクロミック素子。

【請求項 4】

前記各テーパー状側壁は前記基板の面に対して約 45 度以下の傾斜を有して、各側壁はシャドウイングを示さない、請求項 1 記載のエレクトロクロミック素子。

【請求項 5】

前記 1 つまたは複数の隣接層は、少なくとも 1 つのエレクトロクロミック層をさらに含む、請求項 1、3 および 4 のいずれか 1 項に記載のエレクトロクロミック素子。 20

【請求項 6】

前記残りの層は、前記エレクトロクロミック素子の前記エレクトロクロミック層のそれを含む、請求項 1、3、4 および 5 のいずれか 1 項に記載のエレクトロクロミック素子。

【請求項 7】

前記 1 つまたは複数のエレクトロクロミック層は、

エレクトロクロミック電極層および対極電極層の一方を含む第 1 の電極と、

前記エレクトロクロミック電極層および前記対極電極層の他方を含む第 2 の電極と、

前記第 1 の電極および前記第 2 の電極の間でイオンを伝導するイオン伝導体層とを含む、

請求項 1、3、4、5 および 6 のいずれか 1 項に記載のエレクトロクロミック素子。 30

【請求項 8】

前記 1 つまたは複数の隣接層は、前記エレクトロクロミック素子の前記 1 つまたは複数の残りの層の前記エレクトロクロミック層の少なくとも約 2 倍または約 3 倍の厚さである、請求項 1、3、4 ないし 7 のいずれか 1 項に記載のエレクトロクロミック素子。

【請求項 9】

前記物理的な分離は、前記各テーパー状側壁に沿ってメルトスポットを有さない、請求項 1、3 ないし 8 のいずれか 1 項に記載のエレクトロクロミック素子。

【請求項 10】

前記導電層は、前記物理的な分離を含み、前記各テーパー状側壁に沿って剥離なしに基板と直接接触する、請求項 1、3 ないし 9 のいずれか 1 項に記載のエレクトロクロミック素子。 40

【請求項 11】

前記第 2 の部分と、複数のエレクトロクロミック層の第 3 の部分との間の物理的な分離をさらに含み、前記第 2 の部分および前記第 3 の部分の間の前記物理的な分離は、前記第 2 の部分および前記第 3 の部分のそれぞれの各テーパー状側壁を規定する、請求項 1、3 ないし 10 のいずれか 1 項に記載のエレクトロクロミック素子。

【請求項 12】

前記第 2 の導電層は、前記第 2 の導電層の、第 1 の部分および第 2 の部分の間の物理的な分離を含む、請求項 1、3 ないし 11 のいずれか 1 項に記載のエレクトロクロミック素 50

子。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、電気活性素子における改良に関し、より詳細には、固体の無機薄膜素子における改良に関する。

【0002】

本開示に関する電気活性素子の一例は、エレクトロクロミック素子（「EC素子」）である。エレクトロクロミック材料および素子は、ビルおよび車両の窓における光および熱を管理する不動態皮膜材料の代替として開発されている。不動態皮膜材料とは対照的に、電気活性素子は、引加される電位に応じた電気化学的な酸化還元を伴う、それらの光学的な性質を可逆的に変化させることができ材料を用いる。光変調は、電気化学材料の格子内でイオンを補償する電子および電荷が同時に挿入および脱離することにより生じる。

【0003】

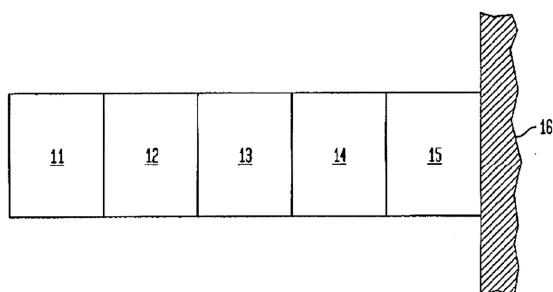

EC素子は、透過する光の透過率を変調可能である複合構造を有する。図1は、以下の5つの層、酸化または還元により吸光または反射の変化を生み出すエレクトロクロミック電極層（「EC」）14と、機能的に電解質と置き換わって電子電流を遮断しつつイオンの通過を可能にするイオン伝導体層（「IC」）13と、素子が白色または透明状態にあるときにイオンの貯蔵層として機能する対極電極層（「CE」）12と、エレクトロクロミック素子に電位を加えるよう機能する2つの透明導電層（「TCL」）11および15とを重ね合わせた典型的な5層の固体エレクトロクロミック素子を断面図で示している。上述の各層は、一般に、基板16上に順次塗布される。こうした素子は、一般に、電子の漏洩（積層したエレクトロクロミック層間で）および電子的な絶縁をもたらす内因的な欠陥がある。

【0004】

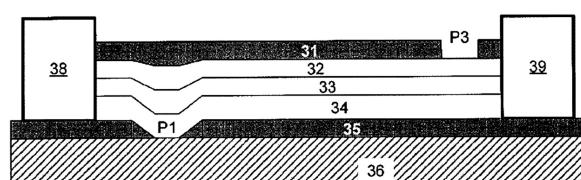

一般に、電力は、バスバーを通してエレクトロクロミック素子に分布する。図2は、図1のエレクトロクロミック素子を断面図で示しており、例えばバスバー18および19である2つの導電素子から供給される電力を有する。バスバーが同時に短絡することを防ぐために、バスバーは、互いに電気的に分離されている。従来は、これをTCL11および15のスクライビングにより行っている。図2に示すように、第1の（下方の）TCL15は、点P1においてスクライブされており、下方のTCL15を断続した（すなわち、物理的に分離している）層とし、それによりバスバーが下方のTCL15で短絡することを防いでいる。点P1におけるスクライブ幅は、一般に、25ミクロン以上のオーダーであるが、長さは形成される特定の素子の幅に基づいて変更される。同様に、第2の（上方の）TCL11は、点P3においてスクライブされて、上方のTCL11もまた断続してなされており、それによりバスバーが上方のTCL11で同時に短絡することを防いでいる。P1のスクライブ寸法と同様に、一般に、P3のスクライブは25ミクロン以上のオーダーであるが、長さは形成される特定の素子の幅に基づいて変更される。

【0005】

固体エレクトロクロミック素子が正確に機能するためには、所望のエレクトロクロミック機構を通る以外の、エレクトロクロミック素子のバスバー間を電流が直接通過することを阻止する必要がある。電気活性層を介して漏洩または通過するいかなる電子電流も、エレクトロクロミック素子を通るイオンの流れの短絡および阻害となりうる。そのように、内因性のまたは電子の漏洩をもたらす欠陥に起因するリーク電流は、ダイナミックレンジの低下、不均一な発色、イオン透過性の減少、切り替え速度低下および電力消費量増加を含む素子性能の妥協に至る。

【0006】

単にイオン伝導体層の厚さを増すことで、リーク電流の減少につながりうるが、光学的な性質の低下、層の成膜時間およびコストの増加、および切り替え速度の低下という犠牲を伴う。同様に、積層に誘電体層を加えることで、リーク電流が減少しうるが、同様の欠陥

10

20

30

40

50

という犠牲および収量減少の可能性を伴う。一般に、収量は、基板または他のワークが成膜チャンバーと雰囲気との間を相互に循環する度に減少するものと考えられる。これは、成膜の際に必ず存在するものである被膜処理よりのほこりおよび残骸が、ページ、排出および／またはポンプダウン中に「吹き」散らされ、活性層へ至る途中で見つかりうるものであって、膜構造の欠陥を導くことによる。理想としては、すべての層を单一の連続処理工程で、すなわち1つの被膜装置で成膜するのがよい。しかしながら、追加の誘電体層を成膜することは、追加の層を成膜するためのコーナー間でのワークの移動と、その後上記したE C積層の作製を再開するためにワークを戻すための移動とを必要としうる。ワークが成膜システム内に出入りすることおよび／または追加でワークを操作することにつながりうるそうした移動は、製造時間を有意に増加させ、素子に対する粒子や他の混入物への暴露を増し、かつ、素子のダメージを受けるリスク（例えば、傷、誤操作など）を大いに増加させる。従って、イオン伝導体層を厚くすることや誘電体層を追加することなく、これらの性能上の妥協を回避するように、エレクトロクロミック素子での電子の漏洩量を低減することが望ましい。

#### 【0007】

上記した問題は、エレクトロクロミック素子だけに限定されるものではない。トップおよびボトムの導電層間に挟まれる1つまたは複数の機能的な電気活性層を有するいかなる電気活性素子においても、導電層をスクライプしてその導電層での短絡を防ぐ場合に同様の問題が存在しうる。例えば、電気活性素子（例えば、導電体／絶縁体／蛍光体／絶縁体／導電体の構造を有するエレクトロルミネッセンス素子、導電体／電子輸送層／発光層／正孔輸送層／導電体の構造を有する有機発光ダイオード（OLED）、または導電体／電子供与体／P-N接合／電子受容体／導電体の構造を有する光起電力素子など）において下方の導電体層および任意の1つまたは複数の電気活性層へのスクライビングは、スクライブエッジ（例えば、P1スクライブの上方エッジの5ミクロンの範囲内）に沿った隆起、ひび、剥離、メルトスポットおよび／または他の欠陥のリスクまたは可能性を作り出すことになる。つまり、電気活性素子のそれらの層に組み込まれているものに關係なく、上記した問題は、スクライブした導電体層および電気活性層の融解および剥離の特性の產物である。

#### 【0008】

このように、できるだけ高い収量を維持しながら（例えば、カッティング処理中のスクライビング工程はできるだけ少なくして行う）、エレクトロクロミック素子の透明導電層の部分間の電子の漏洩量を低減することが望まれる。より一般的には、素子の製造中に行われるスクライビングにより、スクライブした層の剥離または融解からの電子の漏洩に至りうる任意の電気活性素子において、上方および下方の（すなわち、対向している）導電層間の電子の漏洩量を低減することと、製造中にできるだけ高い収量をなお維持することが要望されている。

#### 【発明の概要】

#### 【0009】

開示の一態様は、第1の導電層と、第2の導電層と、上記第1の導電層および上記第2の導電層の間に挟まれる1つまたは複数の電気活性層とを含む電気活性素子を提供する。例えば、上記素子は、エレクトロクロミック電極層および対極電極層の一方である第1の電極と、上記エレクトロクロミック電極層および上記対極電極層の他方である第2の電極とを含みうる。電気活性（例えば、エレクトロクロミック素子、エレクトロルミネッセンス素子、バッテリー、フォトクロミック素子、サーモクロミック素子、懸濁粒子素子、液晶ディスプレイデバイス、光起電力素子、発光ダイオード等）素子は、上記第1および第2の電極間でイオンを伝導するイオン伝導体層と、第1および第2の導電層とをさらに含みうるものであり、上記第1および第2の電極と上記イオン伝導体層とは上記第1および第2の導電層間に挟まれる。

#### 【0010】

上記素子の1つまたは複数の隣接層は、その導電層の第1の部分と第2の部分との間に

10

20

30

40

50

物理的な分離を含みうる。上記物理的な分離は、上記第1および第2の部分のそれぞれの各テーパー状側壁を規定しうる。上記電気活性素子の残りの層は、上記物理的な分離を覆って上記1つまたは複数の隣接層上に形成されうる。この開示のいくつかの例では、上記1つまたは複数の隣接層は、上記第1および第2の導電層の一方を含みうるものであり、上記電気活性素子の上記残りの層は、上記第1および第2の導電層の他方を含みうる。いくつかの例では、上記1つまたは複数の隣接層は、上記電気活性層の少なくともひとつを含みうる。いくつかの例では、上記残りの層は、上記電気活性層のすべてを含みうるものであり、上記電気活性層のそれぞれが上記物理的な分離より上に形成される。

#### 【0011】

この開示によるエレクトロクロミック素子のいくつかの例では、上記1つまたは複数の隣接層は、上記第1および第2の電極層の一方をさらに含みうるものであり、上記電気活性素子の上記残りの層は上記第1および第2の電極層の他方と上記イオン伝導体層とをさらに含みうる。いくつかのさらなる例では、上記1つまたは複数の隣接層は、上記第1および第2の電極層の一方と、上記イオン伝導体層とをさらに含みうるものであり、上記電気活性素子の上記残りの層は上記第1および第2の電極層の他方を含みうる。またさらなる例では、上記電気活性素子の上記残りの層は、上記イオン伝導体層と、上記第1および第2の電極層の両方とを含みうる。

#### 【0012】

いくつかの例では、上記1つまたは複数の隣接層は、スクライブした隣接層と上記第1および第2の導電層の他方（すなわち、以下に規定するように、P1においてスクライブされていない導電層）との間にあるものである電気活性（例えば、エレクトロクロミックなど）素子の上記残りの層の少なくとも約2倍の厚さでありうるものである。さらなる例では、上記1つまたは複数の隣接層は、スクライブした隣接層と上記第1および第2の導電層の他方（すなわち、以下に規定するように、P1においてスクライブされていない導電層）との間にあるものである電気活性（例えば、エレクトロクロミックなど）素子の上記残りの層の少なくとも約3倍の厚さでありうるものである。

#### 【0013】

いくつかの例では、上記第1および第2の電極の一方は、上記物理的な分離を有する上記導電層の上に直接形成されうる。上記第1および第2の部分の間の上記物理的な分離は、その上の電極によって少なくとも一部分が満たされうる。

#### 【0014】

いくつかの例では、上記物理的な分離を有する上記導電層は、上記テーパー状側壁に沿ってメルトスポットを有さない。いくつかのさらなる例では、上記電気活性（例えば、エレクトロクロミックなど）素子は、基板を含みうるものであり、上記物理的な分離を有する上記導電層は、各テーパー状側壁に沿って剥離を有することなく上記基板に直接接触しうる。

#### 【0015】

いくつかの例では、上記テーパー状側壁のそれぞれは、実質的に直線の輪郭を有しうる。他の例では、上記テーパー状側壁のそれぞれは、実質的にガウシアンの輪郭を有しうる。さらなる例では、上記テーパー状側壁のそれぞれの傾斜（すなわち、上記基板に関するまたは対する）は、各側壁がシャドウイングを示さないように、上記基板の面に対して約45度以下でありうる。いくつかのさらなる例では、上記電気活性素子は、上記第2の部分と複数の電気活性層の第3の部分との間に物理的な分離をさらに含みうる。その物理的な分離は、上記第2および第3の部分のそれぞれの各テーパー状側壁を規定しうる。

#### 【0016】

この開示の他の態様は、電気活性（例えば、エレクトロクロミックなど）素子の作製方法を提供する。上記方法は、基板を設置することと、上記基板表面上に前記電気活性（例えば、エレクトロクロミックなど）素子の1つまたは複数の隣接層を形成することとを含みうる。上記方法は、レーザまたは他のスクライビング手段を上記基板に向けて位置決めすることをさらに含む。いくつかの例では、上記レーザまたは他のスクライビング手段は

10

20

30

40

50

、上に形成される上記 1 つまたは複数の隣接層を有する上記基板の側（すなわち、膜側）に向けて位置決めされうる。いくつかの例では、上記レーザは、約 100 ピコ秒以下のパルス幅を有しうる。上記方法は、上記 1 つまたは複数の隣接層の一部を除去することと、上記 1 つまたは複数の隣接層の上記物理的な分離を覆う上記素子の上記残りの層の 1 つまたは複数を形成することとをさらに含みうる。

【0017】

いくつかの例では、上記レーザまたは他のスクライビング手段を用いて上記基板から上記 1 つまたは複数の隣接層の一部を除去することは、上記 1 つまたは複数の隣接層の第 1 の部分と第 2 の部分との間の物理的な分離を形成することをさらに伴うものであり、上記物理的な分離は、上記第 1 および第 2 の部分のそれぞれの各テーパー状側壁を規定する。

10

【0018】

いくつかの例では、上記レーザのパルス幅は、100 ピコ秒よりも短いものありうる。例えば、上記パルス幅は、約 10 ピコ秒以下ありうる。さらに例えば、上記レーザのパルス幅は約 6 ピコ秒でありうる。

【0019】

いくつかの例では、上記レーザの波長は、約 340 nm および約 1070 nm の間でありうる。さらなる例では、上記波長は、約 515 nm および約 532 nm の間でありうる。

【0020】

20

またこの開示のさらなる態様では、電気活性（例えば、エレクトロクロミックなど）素子を作製するシステムを提供する。上記システムは、上に上記素子が形成される基板を含有する筐体と、上記基板上にエレクトロクロミック素子の 1 つまたは複数の層を成膜するための成膜システムと、上記筐体内に搭載されるレーザまたは他のスクライビング手段と、上記基板に対してレーザビームまたは他のスクライビング手段を移動する位置決めデバイスと、上記基板表面上での上記ビームの集束によって発生する粒状物質または蒸気を収集する収集システムとを含みうる。いくつかの例では、上記レーザまたは他のスクライビング手段は、上記基板の膜側に向けて搭載および位置決めされうる。いくつかの例では、該搭載および位置決めされるレーザは、100 ピコ秒以下のパルス幅を有しうる。

【0021】

30

この開示のいくつかの例では、エレクトロクロミック素子の 1 つまたは複数の隣接層は、上記基板上に形成されうるものあり、それらの層の一部が除去されうるものあり、上記素子の 1 つまたは複数の上記残りの層は、上記 1 つまたは複数の隣接層を覆って形成されうるものあり、すべてにおいて上記筐体から上記基板を取り除くことはない。さらなる例では、作製の第 1 段階の間に形成される上記電気活性（例えば、エレクトロクロミックなど）素子のすべての層は、上記筐体から上記基板を取り除くことなく形成されうる。いくつかのさらなる例では、スクライビング工程を含む上記した工程はそれぞれ、上記筐体内での単一の連続する真空工程において行われうる。

【図面の簡単な説明】

【0022】

40

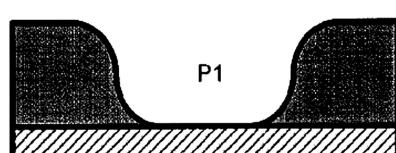

【図 1】図 1 は、典型的なエレクトロクロミック素子の概略断面図である。

【図 2】図 2 は、典型的なエレクトロクロミック素子の別の概略断面図である。

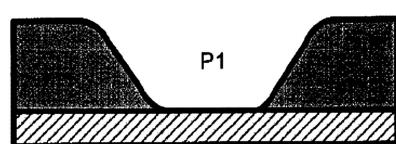

【図 3】図 3 は、本開示の実施形態によるエレクトロクロミック素子の概略断面図である。

【図 4 A】図 4 A は、本開示の実施形態によるエレクトロクロミック素子の一部拡大を示す概略断面図である。

【図 4 B】図 4 B は、本開示の実施形態によるエレクトロクロミック素子の一部拡大を示す概略断面図である。

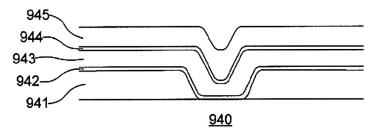

【図 4 C】図 4 C は、本開示の実施形態によるエレクトロクロミック素子の一部拡大を示す概略断面図である。

50

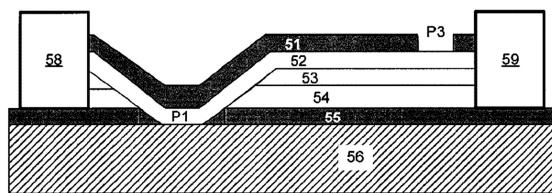

【図5】図5は、本開示の実施形態によるエレクトロクロミック素子の別の概略断面図である。

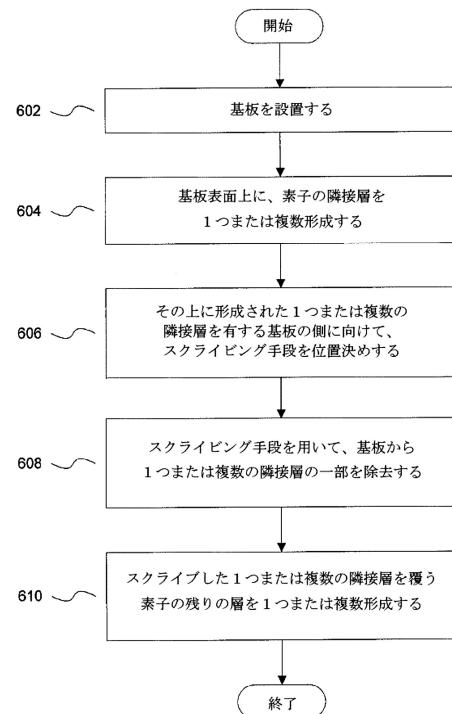

【図6】図6は、ある実施形態によるエレクトロクロミック素子を形成する処理を示すフロー チャートである。

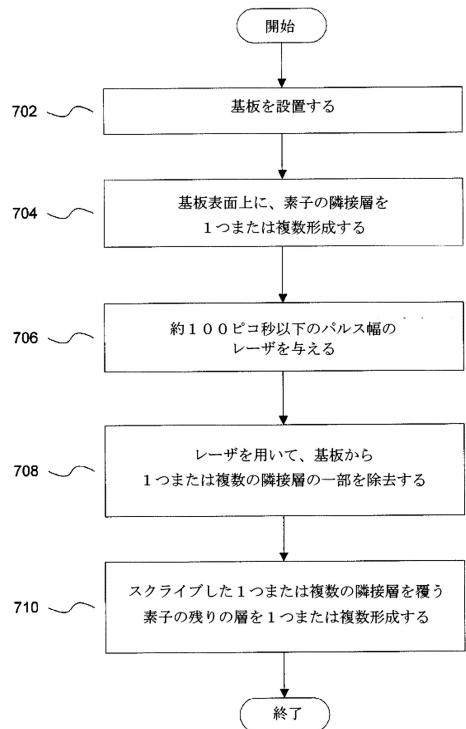

【図7】図7は、ある実施形態によるエレクトロクロミック素子を形成する処理を示す別のフロー チャートである。

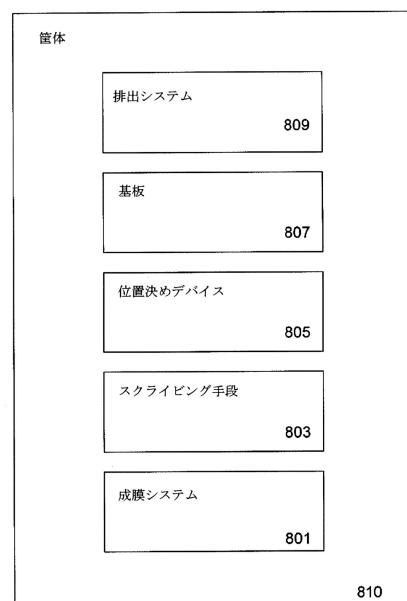

【図8】図8は、ある実施形態によるエレクトロクロミック素子を形成するシステムのブロック図である。

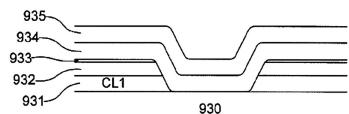

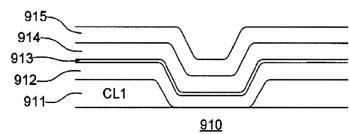

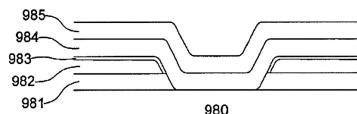

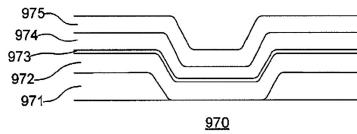

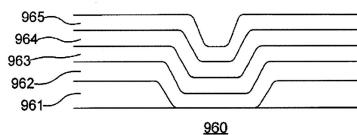

【図9A】図9Aは、ある実施形態による電気活性素子の概略断面図である。

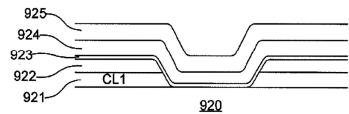

【図9B】図9Bは、ある実施形態による電気活性素子の概略断面図である。

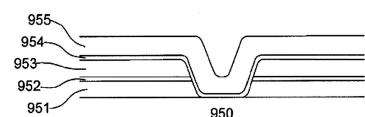

10

【図9C】図9Cは、ある実施形態による電気活性素子の概略断面図である。

【発明を実施するための形態】

【0023】

本開示は、上方および下方の導電層の間の電子の漏洩量が低減された電気活性層の構造を提供する。この構造は、できるだけ高い収量を維持する製造方法によって取得可能である。これらの目的は、約100ピコ秒以下のオーダーのパルス幅を有する適切に調節されたレーザを与えることによって実行される。いくつかの実施形態では、パルス幅は約50ピコ秒以下でありうる。他の実施形態では、パルス幅は約10ピコ秒以下でありうる。さらに他の実施形態では、パルス幅は約6ピコ秒でありうる。

【0024】

20

驚いたことに、予想外に、約100ピコ秒以下のオーダーのパルス幅のレーザを用いての電気活性構造の下方の層または複数の層のスクライピングは、スクライピング処理中に層構造で広がる熱の量を最適化することが発見された。約100ピコ秒以下のパルス幅は、基板から下方の層（例えば、下方の導電層、エレクトロクロミック層およびイオン伝導層のエレクトロクロミック素子の場合において）の一部を除去または切除するには十分長く、またスクライピング中に発生する熱の過剰な拡散に起因するスクライプエッジに沿う基板からの下方の層の剥離を回避するには十分短いことがわかっている。スクライプエッジに沿う剥離を回避することにより、上記構造はひび割れが発生しにくく、そうしたひび割れの結果としての上記構造の下方の導電層の上方の導電層への暴露を発生しにくくさせる。上方および下方の導電層の間の電子の漏洩は、上方の導電層と下方の導電層の暴露された部分との間の結合によってしばしば発生するため、下方の導電層の暴露を回避することはまた、それにより2つの導電層間の電子の漏洩の量または可能性を低減する。

30

【0025】

さらにまた、約100ピコ秒以下のオーダーのパルス幅によれば、スクライピング処理中に電気活性構造から除去されないものである、加熱された材料の平らでない凸条または穴であるメルトスポットの生成を回避することが発見されている。これらのメルトスポットは、スクライピング中に発生した熱の過剰な拡散に起因して、スクライプエッジに沿って形成される（例えば、スクライプエッジの上方エッジの5ミクロン以下の範囲内に位置するメルトスポットの少なくとも一部）。短いパルス幅のレーザを用いることによって、不要の熱が上記構造で広がりにくくなるため、スクライプエッジに沿うメルトスポットの生成が回避される。結果として、スクライプした下方の層は、相対的になめらかな輪郭（メルトスポットのある層と比較して）を保持する。このことは、他の層が、同様に相対的になめらかな輪郭を備えるそれらの下方の層の上部に成膜されることを可能とし、下方の導電層のよりよい被覆性を可能とし、それにより上記スクライプされたエッジに沿う、上方および下方の導電層の間におけるピンホール接触または電気的な短絡の可能性を最小限にする。

40

【0026】

本開示の目的は、電気活性構造が形成される基板の膜または積層側（以下、簡潔に「膜」側と称する。）に向けて、基板側（すなわち、電気活性構造とは反対の基板の側）に向けるのとは反対であるように、レーザを位置決めすることによってさらに実施される。基

50

板の膜側とは反対に位置決めされるレーザから発光されるレーザビームは、膜側上に形成された材料のスクライプのために、基板および他の介在する層を貫通しなければならない。こうした状況において、ビームは、例えばビルの窓に一般に用いられるものである普通の品質のフロート板ガラス内によくある泡または固体の含有物によって遮断、散乱、または焦点ぼけされやすい。ビームの遮断は、材料の一部がスクライプされないという結果を招きうるものであり、下方の導電層の場合においては、層の隔離された部分間で導電性ブリッジ（すなわち、短絡）を導きうる。対照的に、基板の膜側に向けて位置決めされたレーザから発光されるレーザビームは、こうした遮断が発生しやすいものではなく、従って、下方の導電層において導電性ブリッジを残したままとなりにくくなる。

【0027】

10

さらに、多様なエネルギー断面を有するレーザを基板の膜側に向けて位置決めすることは、上方および下方の導電層間の膜層の良好な段差被覆性を可能とすることが発見されている。基板の膜側とは反対に発光されるレーザビームは、スクライプエッジに沿う絶壁のような輪郭を有するスクライプ側壁を形成し、追加の膜層による不良な段差被覆性に起因して下方の導電層は暴露が発生しやすいまとなることが発見された。下方の導電層の暴露によって、上方および下方の導電層間において結果として短絡が生じうる。対照的に、膜側に向けて発光されるレーザビームはテーパー状の輪郭を有するスクライプ側壁を形成することが驚くことに発見されている。テーパー状のスクライプエッジは良好な段差被覆性を可能とするため、下方においての上方および下方の導電層間での短絡しやすさを意味する下方の導電層の暴露部分を残すことがなくなる。

【0028】

20

これにより、約100ピコ秒以下のパルス幅を有するレーザを用いることおよび/または基板の膜側に向けてレーザを位置決めすることは、破損、ピンホール接触または上方および下方の導電層間の暴露の他の原因を有意に減少させる結果となる。組み合わせて、約100ピコ秒以下のパルス幅を有するレーザを基板の膜側に向けて位置決めすることは、こうした欠陥をより一層劇的に減少させる結果を可能とし、導電層全体の短絡を事実上除去して、1nsパルス幅を有する基板の膜側とは反対に位置決めされたレーザによってスクライプした導電層を有する素子と比較して、よりよい動作（すなわち、エレクトロクロミック素子における発色）および改良されたエネルギー効率を結果としてもたらすことが示されている。

【0029】

30

上記した改良は、各導電および電気活性層の相対的な厚さに関係なく、多くのスクライプした薄膜の電気活性積層（例えば、エレクトロクロミック素子、バッテリー、フォトクロミック素子、サーモクロミック素子、懸濁粒子素子、液晶ディスプレイデバイス、光起電力素子、発光ダイオード等）に広く適用されうるものであるが、本開示に記載した実施は、相対的に厚いスクライプした層の上部に相対的に薄い層を成膜する場合に特に有益である。例えば、例示としてエレクトロクロミック素子の電気活性層を用いて、素子のスクライプした下方の透明導電層が、素子の電極層およびイオン伝導層よりも厚い場合、下方の透明導電層または複数の層のスクライピング中にその後生成される不良（例えば、剥離、隆起、ひび、メルトスポットなど）が、上部に形成される他の層によって完全にまたは均一に被覆されないおそれがあり、それにより下方の透明導電層が上方の透明導電層に暴露されたままとなり素子内での電子の漏洩に至る。この漏洩は、素子のある点まで許容または補償可能であるが、この漏洩は、スクライプした層または複数の層が、上部に形成されるスクライプしていない層よりも約2倍以上の厚さである場合にかなり大きな問題となり、スクライプした層または複数の層が、上部に形成されるスクライプしていない層よりも約3倍厚い場合により大きな問題となる。このように、本開示における改良は、限定するものではないが、スクライプした層の上部に形成されるスクライプしていない層（上方の導電体層は含まない）の約2倍の厚さ、3倍の厚さ、または3倍以上の厚さであるスクライプした層を1つまたは複数有する電気活性層の構造に特に有益である。

【0030】

40

50

エレクトロクロミック層構造の場合、エレクトロクロミック層構造内で短絡が生じるリスクを低減することで、さらに、下方の導電層より上に追加の誘電体層を形成する必要性がなくなる。層構造からこれら追加の誘電体層を省略することの利点は、上記構造の加工が、最初のコーチャーを通しての上記基板（または「ワーク」）の単一パスのみで実施可能なことである。一般に、段差被覆性を改良するように追加の誘電体層を形成するためには、ワークは、下方の導電層が形成されてスクライブされるところである最初のコーチャーから出て、誘電体層が形成されるところである異なるコーチャーへ移動させられ、その後残りの初期層（例えば、エレクトロクロミック電極層、イオン伝導層等）が形成されるところである最初のコーチャーへ戻されなければならない。追加の誘電体層をなくすことで、ワークの外部環境への暴露を低減し（通常は移動中に生じる）、それにより収量が改良され、加工中の素子に対する欠陥のリスク（例えば、傷、エッジ屑、ワーク表面上に蓄積した粒子、他の機械的な損失）が最小限となる。追加の誘電体層が同じコーチャー内で成膜されたとしても、追加の誘電体層をなくすことで、ワークごとの加工時間が低減されるはずである。

### 【0031】

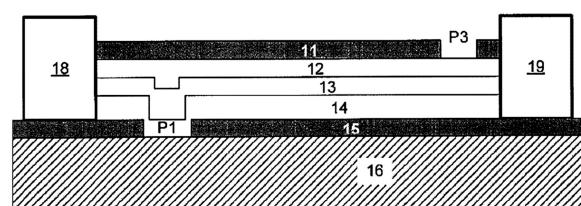

図3は、改良された膜構造を有する固体電気活性素子30の一部を断面図で示している。明確に示すことを目的として、図3に示す電気活性素子30は、図1および2に示す素子と同様のエレクトロクロミック素子とする。しかしながら、本明細書における教示は、異なる積層または膜の構造（例えば、追加の層）を備えた他のエレクトロクロミック素子ならびに、スクライブした他のタイプの電気活性素子にも同様に適用可能であることは認識されるであろう。図3のエレクトロクロミック素子30に関しては、上述の層11から15がそれぞれ図3の素子内に存在する（層31から35として）部分に限り、その素子は図1および2の素子と同様である。図3の素子は、位置P1におけるスクライブの側壁の輪郭が違うように形作られ、かつ、異なる性質または特徴を有する部分について図1および2に示す素子と異なる。例えば、図1および2ではスクライブの側壁の輪郭は実質的に垂直または絶壁のようであるが、図3では輪郭はテーパー状である。さらに例えば、図には示されていないが、図1および2の素子の下方の導電層は、スクライブエッジに沿って剥離およびメルトスポットが生じやすいが、図3の改良された素子は、剥離の欠陥またはメルトスポットを有さない。

### 【0032】

図3において、下方の導電層35は、基板36上に形成され、第1のバスバー38に結合される第1の部分および第2のバスバー39に結合される第2の部分を含む。第1の部分および第2の部分は、スクライブによって位置P1において互いに物理的に分離している。物理的な分離は、その上に直接形成される電極層34（エレクトロクロミック電極層または対極電極層のいずれかであります）と、イオン伝導体層33と、他の電極層32（エレクトロクロミック電極層と対極電極層との他方であります）と、上方の導電層31とを含むエレクトロクロミック素子の残りの層によって、完全にまたは部分的にいずれかで被覆され満たされる。図1および2における素子のスクライブ側壁と比べて相対的にならかな、スクライブ側壁のテーパー状の輪郭であることから、電極層34は、下方の導電層を覆うスクライブエッジに沿う改良された段差被覆性を備える。図2に示すイオン伝導層13は、下方の導電層15の側壁にほぼ到達しそうであるが、図3に示す電極層34は、イオン伝導層33および下方の導電層35の間ににおいて改良された分離を維持している。さらに、電極層32および34と、それらの間に挟まれるイオン伝導体層33とは、下方の導電層31のスクライブエッジに沿う改良された段差被覆性を全体として提供するため、各導電層31および35において電流の漏洩または短絡がない。

### 【0033】

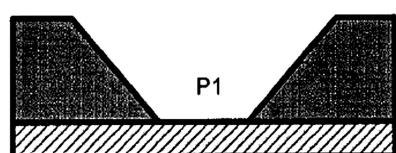

図3の例において、位置P1のスクライブ側壁は、直線的なテーパー状の輪郭を有する。しかしながら、レーザの空間的なビームエネルギー断面を調節することによって、他の輪郭（例えば、ガウシアンまたは通常の分布曲線形状、実質的にガウシアンまたは別の曲線形状など）が実現されうる。いくつかの例では、テーパー状側壁はそれぞれ、スクライ

10

20

30

40

50

ブした層表面と基板表面との間においてなめらかな移行を備えうる。例えば、テーパー状側壁はそれぞれ、角がとれた上方エッジを有しうる。さらに例えば、各テーパー状側壁の全体的な傾斜は、基板の面に対して約45度でありうる。いくつかの例では、シャドウイングのリスクを低減するために、テーパー状側壁はそれぞれ、基板の面に対して45度よりも急な傾斜を有する側壁の部位を有しないように形成されうる。

#### 【0034】

図4Aから4Cに、実現されうるいくつかの可能な側壁の輪郭を示す。例えば、図4Aは、図3の直線の輪郭の拡大を示す。さらに、例えば、図4Bに、曲げられた側壁のエッジを備える実質的にガウシンアン(曲線状)の輪郭を示す。またさらに、例えば、図4Cに、直線および曲線状の両方の特徴を有する輪郭を示す。いくつかの例では、ビームのエネルギー断面はなめらかに変更されうる。

10

#### 【0035】

本開示は、下方の導電層のみならず、複数の層がスクライブされる電気活性素子に対して同様に適用可能である。例えば、図5は、改良された別の膜構造を有する他の固体エレクトロクロミック素子50の一部を断面図で示している。図5の素子50は、前述の層31から35がそれぞれ図5の素子内に再び存在している(層51から55として)部分に限り、図3に示す固体素子と同様である。図5の素子は、下方の導電層に直接隣接する電極層と、イオン伝導層とが下方の導電層に加えてスクライブされている部分について図3に示す素子と異なる。図3と比べて、位置P1におけるスクライブの側壁の輪郭はテーパー状である。また、図3のように、図5の素子のスクライブした層はそれぞれ、剥離の欠陥またはメルトスポットを有していない。

20

#### 【0036】

図5において、下方の導電層55、第1の電極層54およびイオン伝導層53はそれぞれ、基板56上に形成され、第1のバスバー58に結合される第1の部分と、第2のバスバー59に結合される第2の部分とを含む。各層の第1の部分および第2の部分は、スクライブによって位置P1において互いに物理的に分離されている。物理的な分離は、電極層52(エレクトロクロミック電極層または対極電極層のいずれかでありうる)と、上方の導電層51とを含む残りの層によって、完全にまたは部分的にいずれかで被覆され満たされている。図1および2における素子のスクライブ側壁と比べて相対的になめらかな、スクライブ側壁のテーパー状の輪郭であることから、電極層52は、下方の導電層55を覆うスクライブエッジに沿う改良された段差被覆性を備えるため、各導電層51および55の間において電流の漏洩または短絡がない。

30

#### 【0037】

図5の例では、下方の導電層、エレクトロクロミック電極層およびイオン伝導体層は、対極の電極層の約2倍以上の厚さである。他の開示の例では、下方の導電層、エレクトロクロミック電極層およびイオン伝導体層は、対極の電極層の約3倍以上の厚さでありうる。また他の例では、下方の導電層および1つまたは複数のスクライブした他の隣接層は、スクライブした層の上で、かつ、上方の導電層の下に成膜される層よりも約2倍またはそれ以上の厚さでありうる。さらなる例では、下方の導電層および1つまたは複数のスクライブした他の隣接層は、スクライブした層の上で、かつ、上方の導電層の下に成膜される層の約3倍またはそれ以上の厚さでありうる。上の例のいずれにおいても、100ピコ秒のパルス幅を有するレーザ、基板の膜側に向けたレーザ(または他のスクライビング手段)、またはその両方を用いて素子をスクライブすることが特に有益でありうる。

40

#### 【0038】

本開示においてはまた、上記した改良を有する電気活性素子の作製方法が提供される。成膜される層の構成またはタイプは、本明細書における教示から逸脱することなく、所望の結果を達成するために変更されてよい。

#### 【0039】

図6は、それにより素子30が形成されうる処理を示すフロー図600を提供する。ブロック602において、上に素子が形成または作製されていく基板またはワークが設置さ

50

れる。基板は、ビルの窓に通常用いられるような普通のフロート板ガラス片、ホウケイ酸ガラス、または例えれば車両や航空機の用途の他の窓用ガラスでありうる。基板は、熱処理、熱強化、熱的に強化、または化学的に強化されうる。基板は、作製される素子のタイプに好適な、ダイヤモンド、酸化アルミニウム、またはサファイアおよび堅いまたはフレキシブルなポリマーなどの多くの透明材料含む、他の材料をさらに含みうる。さらに、鏡面反射するのに十分なめらかな表面を備えた不透明材料が用いられるものであり、電気活性膜に反射性のバックグラウンドを形成するように研磨または被覆される場合に反射性の電気活性素子を結果として生じる。これは、研磨される表面を備える金属と、炭素、ケイ素、炭化ケイ素、ガリウムヒ素、酸化ホウ素などの半導体または誘電体上の反射性の金属または誘電性被覆とを含みうる。

10

#### 【0040】

ブロック604において、電気活性素子の1つまたは複数の隣接層は、インジウムスズ酸化物などの伝導性材料の層を含み、基板表面上に形成される。該層は、各層が素子の第1のバスバーから第2のバスバーへ連続的に延びるように成膜されうる。いくつかの実施形態では、該層は導電層のみとしうる。他の実施形態では、該層は導電層上に直接、かつ、隣接して形成される電極層をさらに含みうる。またさらなる実施形態では、該層は電極層上に形成されたイオン伝導層を含みうる。好ましい実施形態では、導電層を構成する材料は、スパッタリングにより透明基板上に成膜されて透明導電層を形成する。

#### 【0041】

ブロック606において、スクライビング手段は、上に形成される1つまたは複数の隣接層を有する基板の側に向けて位置決めされる。スクライビング手段は、レーザスクライビング、例えはダイヤモンド、ルピー、またはステンレススチールの先端の使用を伴う機械的な研磨、放電加工、または化学エッチングやこの分野（「カッティング」）で公知の他の好適な除去処理を含む様々な異なる方法のうちのひとつを用いて層のスクライビングが可能でありうる。スクライビング手段は、成膜（例えは、被覆）チャンバ内に搭載されうる。スクライビング手段がレーザの場合、レーザの位置決めは基板の位置P1にレーザのレーザビームを集束させることを伴う。

20

#### 【0042】

ブロック608において、1つまたは複数の隣接層の一部は、スクライビング手段を用いて除去される。いくつかの実施形態では、層は位置P1でスクライプまたはカットされうる。このスクライプは、基板の全長、すなわち基板の一方の端部から反対の端部まであって通常図3の断面図に示す位置P1まで延びうる。スクライプの線幅は、約25ミクロン以上でありうる。いくつかの実施形態では、その開示がここに本明細書の全体に組み込まれる同時係属出願の米国出願シリアル番号第13/950,791号の技術に基づき、より大きな線幅を有するスクライプまたは1つ以上のスクライプは、位置P1周辺で行われうる。例えは、複数の同一のスクライプは、互いに隣接して（例えは、互いに平行に）スクライプする層に形成されうる。こうしたスクライビングは、漏洩（例えは局所的な欠陥に起因）を導く可能性がありうるレーザ線の断絶リスクを軽減しうる。いくつかの例では、各スクライプは、スクライプした層内のスクライプされない材料によって分離されうる。他の例では、複数のスクライプは、各スクライプ間のすべての材料を除去しうるものであり、それにより個別的なスクライプそれぞれと比較して相対的に大きな線幅を有する単一のスクライプが効果的にもたらされる。

30

#### 【0043】

ブロック610において、電気活性素子の1つまたは複数の残りの層が、1つまたは複数のスクライプした隣接層を覆って形成される。例えは、図3のエレクトロクロミック素子において、該残りの層は、エレクトロクロミック電極層、対極電極層、2つの電極層の間に挟まれるイオン伝導層および他の層より上に形成される上方の導電層を含みうる。これらの層の成膜は、スパッタリング、化学蒸着、または同時係属出願の米国出願シリアル番号第13/950,791号に記載される方法のような本分野で公知の他の薄膜作製方法により行われうる。いくつかの実施形態では、米国特許第5,724,177号に記載

40

50

される層のような反射防止膜層、光チューニング層や、米国特許第8,004,744号に記載される層のようなイオン輸送層などの追加の層を層構造に形成してよく、その開示はここに本明細書の全体に組み込まれる。これらの層の形成は、例えば、米国特許第5,699,192号、5,321,544号、5,659,417号、5,370,775号および5,404,244号にさらに記載されており、その開示は本明細書の全体に参照によりここに組み込まれる。

#### 【0044】

いくつかの実施形態では、すべてのスクライプした隣接層および少なくとも1つの残りの層は、素子作製の製造能が増すように、同じ真空処理チャンバ内でマグネットロンスパッタ成膜により成膜されるものであって、素子の製造プロセスにおいて初期層の被覆の際に基板は1段階のみを経ること、減少した手順の結果として収量は向上される可能性が高いこと、およびさらにより少ない加工工程の結果として処理量もまた増す可能性が高いことを意味する。さらに、基板を除去することなく同じチャンバ内で初期層のすべてを成膜することは、短絡数の減少をもたらす。

#### 【0045】

図7は、それにより素子30が形成されうる他の処理を示す別のフロー図700を提供する。ブロック702、704、708および710に記載されるステップは、フロー図600に関して記載されるステップ602、604、608および610にそれぞれ相当するため、ここでは繰り返さない。フロー図700は、追加のステップのブロック706を含み、フロー図600のステップ606の代わりに、または追加して実施されうる。ブロック706において、約100ピコ秒以下のパルス幅を備えたレーザが与えられる。図7のフロー図700において、レーザは、基板の膜側に向けてまたは対向して位置決めされうる。100ピコ秒以下のパルス幅を有するレーザを基板の膜側に向けて位置決めすることによって、フロー図600および700の両方が同時に実施されうる。

#### 【0046】

普通、レーザのパルス幅は、下方の導電層内に剥離またはメルトスポットを引き起こさうる不要な熱の拡散を防止するように、加工中の素子内の熱の放散を最適化するように選択されうる。こうしたパルス幅は、普通約100ピコ秒以下であるが、スクライプ対象の材料に応じて変更してよい。普通、1nm以上続くパルス幅が不要な熱の拡散を引き起こすことがわかっているが、より短いパルス幅を有するレーザの使用が有益でありうる。いくつかの例では、レーザのパルス幅は約50ピコ秒以下でありうる。さらなる例では、パルス幅は約10ピコ秒以下でありうる。またさらなる例では、パルス幅は約6ピコ秒でありうる。

#### 【0047】

レーザの波長は、約340nmから約1070nmまでにわたりうる。より詳しくは、レーザの波長は、基板によるビームエネルギーの吸収が低減するように、より詳しくは、下方の導電層と基板との間の吸収率を最適化するように選択されうる。最適な波長は、基板の材料および他の層の材料に応じて変更しうる。いくつかの実施形態では、下方の導電層は、レーザからのエネルギーを高い割合で吸収するであろうし、基板はエネルギーを低い割合で吸収するであろう。例えば、同時係属出願の米国出願シリアル番号第13/950,791号に記載されるエレクトロクロミック素子において、エレクトロクロミック素子のガラス基板は、緑色光に対して相対的に低い吸収を有し、ガラス基板上のインジウムスズ酸化物はより高い吸収率を示すことがわかっている。さらに、こうした素子内では、約515nmおよび約532nm間の波長を有する光が好ましいことがわかっている。異なる材料を用いた他の素子内では、異なる波長を有する光を発光するレーザが好ましいものでありうる。

#### 【0048】

図8は、本開示の電気活性素子を形成するためのシステム800の簡略図を提供する。システム800は、素子作製のための筐体またはチャンバ810を含む。チャンバ810は、電気活性素子の作製に用いられる本分野で公知の任意の標準の蒸着チャンバまたはコ

10

20

30

40

50

ーターでありうる。例えば、チャンバ 810 は、基板上に導電層および / または電気活性層を被覆する初期段階を実施するためなどのコーティングでありうる。チャンバ 810 は、真空または他の圧力条件下 ( 例えば、大気圧 ) のいずれかで動作されうる。成膜システム 801、レーザ 803、基板に対してレーザのビーム位置を位置決めまたは調節するための位置決めデバイス 805、基板 807 および収集システム 809 がチャンバ 810 内に収納されうる。

【 0049 】

成膜システム 801 は、マグнетロンスパッタ、DC スパッタまたは RF スパッタもしくは真空条件下で基板上に導電および / または絶縁の材料の薄膜を成膜する他の手段でありうる。上記したように、いくつかの例では、レーザ 803 は約 100 ピコ秒未満のパルス幅を有しうる。いくつかの実施形態では、位置決めデバイス 805 は、所定位置にレーザを保持および / またはチャンバ内にレーザを搭載しうるものであり、レーザは基板 807 表面にレーザビームを発光するように配向される。いくつかの例では、位置決めデバイス 805 は、レーザビームが基板 807 の膜側に向けられるように構成されうる。位置決めデバイス 805 は、集束ビームが基板 807 表面上のスクライプエッジに沿って移動しうるようにレーザを置き換えるまたは再配向するようにさらに構成されうる。

【 0050 】

収集システム 809 は、排出口、静電板、チルド表面、パイプまたは基板表面上におけるビームの集束によって発生する粒状物質または蒸気を収集するための他の構造でありうる。収集システム 809 はさらに、それら粒状物質または蒸気を分離し、および / またはそれらを筐体 810 の外に出すように構成されうる。粒状物質または蒸気の収集および / または排出は、これにより基板および / または膜構造の傷または別のダメージとなりうる筐体のページ、排出および / またはポンプダウン中に材料に「吹き」散らされることを防ぐために有益でありうる。

【 0051 】

本開示の一例では、筐体から基板を除去することなく電気活性素子が形成されうる。例えば、図 3 のエレクトロクロミック素子の形成では、基板は筐体内に配置されうるものであり、導電材料の層は、基板表面上に形成されうるものであり、導電材料の層の一部がレーザを用いて除去されうるものであり、エレクトロクロミック電極層および対極電極層のうちの少なくともひとつは、導電材料の層上に形成されうるものであり、すべてにおいて筐体から基板を取り除くことはない。いくつかの例では、これらの工程は、単一の連続する真空工程で実施されうる。

【 0052 】

上記各実施形態は、位置 P1 において、下方の導電層のみを貫通する切れ目を例示しているが、短パルス幅レーザおよび / または基板の膜側に向けて位置決めされたレーザを用いることによる利益は、例えば下方の導電層および隣接する電極層の両方を通り、またさらには下方の導電層、隣接する電極層を通って、そして電極層に隣接するイオン伝導体層をさらに通るように、素子の複数の層を貫通するスクライプにおいて実現されうることが理解されるであろう。こうしたスクライプは、例えば、その開示がここに本明細書の全体に組み込まれる同時係属出願の米国出願シリアル番号第 13 / 786,934 号に記載されている。

【 0053 】

上記したように、スクライプしたエレクトロクロミック素子の場合、上記した利益は、電極層およびイオン伝導体層 912 ~ 914 が上方および下方の導電層 915 および 911 をそれぞれに分離するように導電層 911 のみを通るスクライプにおいて ( 910 ) 、または発光層 923 および他の輸送層 924 が上方および下方の導電層 925 および 921 をそれぞれに分離するように導電層 921 および 1 つの電極層 922 を通るスクライプにおいて ( 920 ) 、または他の電極層 934 のみが上方および下方の導電層 935 および 931 をそれぞれに分離するように導電層 931 、 1 つの電極層 932 およびイオン伝導体層 933 を通るスクライプにおいて ( 930 ) 、実現されうる。同様に、スクライプ

10

20

30

40

50

したエレクトロルミネッセンス素子の場合、上記した利益は、絶縁層および蛍光体層 942～944 が、上方および下方の導電層 945 および 941 をそれぞれに分離するように導電層 941 のみを通るスクライプにおいて (940)、または導電層 951、1 つの絶縁層 952 および蛍光体層 953 を通るスクライプにおいて (例えば、絶縁層 954 のみが上方および下方の導電層 955 および 951 をそれぞれに分離するように) (950)、実現されうる。スクライプした OLED の場合、上記した利益は、輸送層および発光層 962～964 が、上方および下方の導電層 965 および 961 をそれぞれに分離するように導電層 961 のみを通るスクライプにおいて (960)、または発光層および他の輸送層が上方および下方の導電層 (図示せず) を分離するように導電層および 1 つの輸送層を通るスクライプにおいて、または他の輸送層のみが上方および下方の導電層 (こちらも図示せず) を分離するように導電層、1 つの輸送層および発光層を通るスクライプにおいて、実現されうる。さらに、スクライプした光起電力素子の場合、上記した利益は、受容体 / 供与体層および p-n 接合層 972～974 が上方および下方の導電層 975 および 971 をそれぞれに分離するように導電層 971 のみを通るスクライプにおいて (970)、または他の受容体 / 供与体層 984 のみが上方および下方の導電層 985 および 981 をそれぞれに分離するような導電層 981 と受容体 / 供与体層 982 のうちのひとつと p-n 接合層 983 とを通るスクライプにおいて (980)、実現されうる。これらの各実施形態は、図 9A～C の図に明確な説明のために示している。

#### 【0054】

また、基板の膜側に向けてスクライビングが行われる上記した各実施形態において、こうしたスクライビングはレーザで行われるように記載している。しかしながら、少なくともテーパー状側壁エッジによる利益は、エッティング、機械的な研磨、またはこの分野 (「カッティング」) で公知のその他の好適な除去処理などの他のカッティングまたはアブレーションのツール / 技術を用いて達成されることは理解されるであろう。さらに、上記実施形態はレーザを収納するチャンバに関して記載されているが、チャンバには、本開示のテーパー状側壁を達成するためのこれらの他のカッティングまたはアブレーションのツールをどれでも備えてよい。

#### 【0055】

さらに、上記各実施形態は、2 つのみのバスバー間での素子構造を示しているが、上記開示は同様に 2 つ以上のバスバーをさらに有する素子に適用されることが理解されるであろう。こうした素子では、各バスバーは、上記したような構造を形成することによって互いに電気的に分離されうる。各構造の形成は、同時にまたは順次行われてよく、各対のバスバー間に形成される層は、上記した任意の手法でスクライプされうる。

#### 【0056】

最後に、上記し、かつ、図面において説明した実施形態は、長方形形状の素子に限定されない。むしろ該記載および図面は素子の断面図を表すことのみを意味しており、いかなる手法においてもこうした素子の形状を限定することを意味していない。例えば、素子は長方形以外の形状 (例えば、三角形、円形、弧状構造など) に形成されうる。さらなる例としては、素子は三次元 (例えば、凸状、凹状など) に形作られうる。

#### 【0057】

多くの異なる態様および実施形態が可能である。それらの態様および実施形態のいくつかを以下に記載する。この明細書に目を通せば、当業者はそれらの態様および実施形態が例示にすぎず、本発明の範囲を限定しないことを十分理解するであろう。実施形態は、以下に列挙するような 1 つまたは複数の項のいずれにも基づいてよい。

#### 【0058】

項 1. 電気活性素子であって、

第 1 の導電層および第 2 の導電層と、上記第 1 の導電層および上記第 2 の導電層の間に挟まれる 1 つまたは複数の電気活性層とを含み、

上記電気活性素子の 1 つまたは複数の隣接層は、該複数の電気活性層の第 1 の部分および第 2 の部分の間に物理的な分離を含み、上記物理的な分離は、上記第 1 の部分および上

10

20

30

40

50

記第2の部分のそれぞれの各テーパー状側壁を規定し、上記1つまたは複数の隣接層は上記第1の導電層および上記第2の導電層の一方を含み、

上記電気活性素子の残りの層は、上記物理的な分離を覆って上記1つまたは複数の隣接層上に形成され、上記残りの層は上記第1の導電層および上記第2の導電層の他方を含む。

【0059】

項2. 電気活性素子の作製方法であって、上記方法は、

基板を設置することと、

上記基板表面上に上記電気活性素子の1つまたは複数の隣接層を形成することと、

上に形成される上記1つまたは複数の隣接層を有する上記基板の側に向けてスクライビング手段を位置決めすることと、

上記スクライビング手段を用いて上記基板から上記電気活性素子の上記1つまたは複数の隣接層の一部を除去することによって、上記1つまたは複数の隣接層の第1の部分および第2の部分の間に物理的な分離を形成して、上記物理的な分離は上記第1の部分および上記第2の部分のそれぞれの各テーパー状側壁を規定することと、

上記1つまたは複数の隣接層の上記物理的な分離を覆う上記電気活性素子の1つまたは複数の残りの層を形成することとを含む。

【0060】

項3. 項1の電気活性素子または項2の方法であって、上記各テーパー状側壁は、実質的に直線の輪郭または実質的にガウシアンの輪郭を有する。

【0061】

項4. 項1の電気活性素子または項2の方法であって、上記各テーパー状側壁は上記基板の面に対して約45度以下の傾斜を有して、各側壁はシャドウイングを示さない。

【0062】

項5. 第1の導電層と、第2の導電層と、上記第1の導電層および上記第2の導電層の間に挟まれる1つまたは複数の電気活性層とを含む電気活性素子の作製方法であって、上記方法は、

基板を設置することと、

上記基板表面上に上記電気活性素子の1つまたは複数の隣接層を形成し、上記1つまたは複数の隣接層は上記第1の導電層および上記第2の導電層の一方を含むことと、

約100ピコ秒以下のパルス幅のレーザを与えることと、

上記レーザを用いて上記基板から上記1つまたは複数の隣接層の一部を除去することと、

上記1つまたは複数の隣接層を覆う上記電気活性素子の残りの層を形成し、上記残りの層は、上記第1の導電層および上記第2の導電層の他方を含む。

【0063】

項6. 項5の方法であって、上記レーザは、上に形成される上記1つまたは複数の隣接層を有する上記基板の側に向けて位置決めされる。

【0064】

項7. 項1から6のいずれか1つの電気活性素子または方法であって、上記1つまたは複数の隣接層は、少なくとも1つの電気活性層をさらに含む。

【0065】

項8. 項1から7のいずれか1つの電気活性素子または方法であって、上記残りの層は、上記電気活性素子の上記電気活性層のそれぞれを含む。

【0066】

項9. 項1から8のいずれか1つの電気活性素子または方法であって、上記電気活性素子は、エレクトロクロミック素子である。

【0067】

項10. 項9の電気活性素子または方法であって、上記1つまたは複数の電気活性層は、

10

20

30

40

50

エレクトロクロミック電極層および対極電極層の一方を含む第1の電極と、

上記エレクトロクロミック電極層および上記対極電極層の他方を含む第2の電極と、

上記第1の電極および上記第2の電極の間でイオンを伝導するイオン伝導体層とを含む

。

【0068】

項11. 項1から10のいずれか1つの電気活性素子または方法であって、上記1つまたは複数の隣接層は、上記電気活性素子の上記1つまたは複数の残りの層の上記電気活性層の少なくとも約2倍または約3倍の厚さである。

【0069】

項12. 項1から4および7から11のいずれか1つの電気活性素子または方法であって、上記物理的な分離は、上記各テーパー状側壁に沿ってメルトスポットを有さない。

10

【0070】

項13. 項1から4および7から12のいずれか1つの電気活性素子または方法であって、上記導電層は、上記物理的な分離を含み、上記各テーパー状側壁に沿って剥離なしに基板と直接接触する。

【0071】

項14. 項1から4および7から13のいずれか1つの電気活性素子または方法であって、上記第2の部分と、複数の電気活性層の第3の部分との間の物理的な分離をさらに含み、上記第2の部分および上記第3の部分の間の上記物理的な分離は、上記第2の部分および上記第3の部分のそれぞれの各テーパー状側壁を規定する。

20

【0072】

項15. エレクトロクロミック素子を作製するシステムであって、上記システムは、上に上記エレクトロクロミック素子が形成される基板を包含する筐体と、

上記基板上に上記エレクトロクロミック素子の1つまたは複数の層を成膜するように構成された成膜システムと、

上記筐体に搭載されるレーザであり、

上記レーザは、100ピコ秒以下のパルス幅を有し、上記基板上にビームを生じるよう位置決めされ、または

上記層は、上に上記エレクトロクロミック素子が形成される上記基板の側に向けられるものであって、

30

上記基板表面上にビームを生じるように位置決めされる上記レーザと、

上記基板に対して上記ビームを移動する位置決めデバイスと、

上記基板表面上における上記ビームの集束によって発生する粒状物質または蒸気を収集する収集システムとを含む。

【0073】

項16. 電気活性素子であって、

第1の導電層および第2の導電層と、上記第1の導電層および上記第2の導電層の間に挟まる1つまたは複数の電気活性層とを含み、

上記電気活性素子の1つまたは複数の隣接層は、該複数の電気活性層の第1の部分および第2の部分の間に物理的な分離を含み、上記物理的な分離は、上記第1の部分および上記第2の部分のそれぞれの各テーパー状側壁を規定し、上記1つまたは複数の隣接層は上記第1の導電層および上記第2の導電層の一方を含み、

40

上記電気活性素子の残りの層は、上記物理的な分離を覆って上記1つまたは複数の隣接層上に形成され、上記残りの層は上記第1の導電層および上記第2の導電層の他方を含む。

【0074】

項17. 項16の電気活性素子であって、上記1つまたは複数の隣接層は、少なくとも1つの電気活性層をさらに含む。

【0075】

項18. 項16の電気活性素子であって、上記残りの層は、上記電気活性素子の上記電

50

気活性層のそれを含む。

【0076】

項19.項16の電気活性素子であって、上記電気活性素子は、エレクトロクロミック素子、エレクトロルミネッセンス素子、バッテリー、フォトクロミック素子、サーモクロミック素子、懸濁粒子素子、液晶ディスプレイデバイス、光起電力素子および発光ダイオードのうちのひとつである。

【0077】

項20.項16の電気活性素子であって、上記電気活性素子はエレクトロクロミック素子であり、上記1つまたは複数の電気活性層は、

エレクトロクロミック電極層および対極電極層の一方を含む第1の電極と、

上記エレクトロクロミック電極層および上記対極電極層の他方を含む第2の電極と、

上記第1の電極および上記第2の電極の間でイオンを伝導するイオン伝導体層とを含む。

。

【0078】

項21.項20の電気活性素子であって、上記1つまたは複数の隣接層は、上記第1の電極および上記第2の電極の一方をさらに含み、上記残りの層は、上記イオン伝導体層と、上記第1の電極および上記第2の電極の他方とをさらに含む。

【0079】

項22.項20の電気活性素子であって、上記1つまたは複数の隣接層は、上記イオン伝導体層と、上記第1の電極および上記第2の電極の一方と、上記イオン伝導体層とをさらに含み、上記残りの層は、上記第1の電極および上記第2の電極の他方をさらに含む。

【0080】

項23.項20の電気活性素子であって、上記残りの層は、上記イオン伝導体層および上記第1の電極および上記第2の電極のそれをさらに含む。

【0081】

項24.項16の電気活性素子であって、上記1つまたは複数の隣接層は、上記電気活性素子の上記1つまたは複数の残りの層の上記電気活性層の少なくとも約2倍の厚さである。

【0082】

項25.項16の電気活性素子であって、上記1つまたは複数の隣接層は、上記電気活性素子の上記1つまたは複数の残りの層の上記電気活性層の少なくとも約3倍の厚さである。

【0083】

項26.項16の電気活性素子であって、上記物理的な分離は、上記テーパー状側壁に沿ってメルトスポットを有さない。

【0084】

項27.項16の電気活性素子であって、基板をさらに含み、上記導電層は、上記物理的な分離を含み、上記テーパー状側壁に沿って剥離なしに上記基板と直接接触する。

【0085】

項28.項16の電気活性素子であって、上記テーパー状側壁のそれぞれの傾斜は上記基板の面に対して約45度以下であり、各側壁はシャドウイングを示さない。

【0086】

項29.項16の電気活性素子であって、上記第2の部分と、複数の電気活性層の第3の部分との間の物理的な分離をさらに含み、上記第2の部分および上記第3の部分の間の上記物理的な分離は、上記第2の部分および上記第3の部分のそれぞれの各テーパー状側壁を規定する。

【0087】

項30.電気活性素子の作製方法であって、上記方法は、

基板を設置することと、

上記基板表面上に上記電気活性素子の1つまたは複数の隣接層を形成することと、

10

20

30

40

50

上に形成される上記 1 つまたは複数の隣接層を有する上記基板の側に向けてスクライビング手段を位置決めすることと、

上記スクライビング手段を用いて上記基板から上記電気活性素子の上記 1 つまたは複数の隣接層の一部を除去することによって、上記 1 つまたは複数の隣接層の第 1 の部分および第 2 の部分の間に物理的な分離を形成して、上記物理的な分離は上記第 1 の部分および上記第 2 の部分のそれぞれの各テーパー状側壁を規定することと、

上記 1 つまたは複数の隣接層の上記物理的な分離を覆う上記電気活性素子の 1 つまたは複数の残りの層を形成することとを含む。

【 0 0 8 8 】

項 3 1 . 項 3 0 の方法であって、それらの間の上記物理的な分離によって規定される上記各テーパー状側壁は、実質的に直線の輪郭で形成される。 10

【 0 0 8 9 】

項 3 2 . 項 3 0 の方法であって、それらの間の上記物理的な分離によって規定される上記各テーパー状側壁は、実質的にガウシアンの輪郭で形成される。

【 0 0 9 0 】

項 3 3 . 項 3 0 の方法であって、それらの間の上記物理的な分離によって規定される上記各テーパー状側壁は、上記基板の面に対して約 45 度以下の傾斜で形成されて、各側壁はシャドウイングを示さない。

【 0 0 9 1 】

項 3 4 . 項 3 0 の方法であって、上記方法によって形成される上記電気活性素子は、エレクトロクロミック素子である。 20

【 0 0 9 2 】

項 3 5 . 第 1 の導電層と、第 2 の導電層と、上記第 1 の導電層および上記第 2 の導電層の間に挟まれる 1 つまたは複数の電気活性層を含む電気活性素子の作製方法であって、上記方法は、

基板を設置することと、

上記基板表面上に上記電気活性素子の 1 つまたは複数の隣接層を形成し、上記 1 つまたは複数の隣接層は上記第 1 および第 2 の導電層の一方を含むことと、

約 100 ピコ秒以下のパルス幅のレーザを与えることと、

上記レーザを用いて上記基板から上記 1 つまたは複数の隣接層の一部を除去することと 30

、

上記 1 つまたは複数の隣接層を覆う上記電気活性素子の残りの層を形成し、上記残りの層は、上記第 1 の導電層および上記第 2 の導電層の他方を含む。

【 0 0 9 3 】

項 3 6 . 項 3 5 の方法であって、上記 1 つまたは複数の隣接層は、少なくとも 1 つの電気活性層をさらに含む。

【 0 0 9 4 】

項 3 7 . 項 3 5 の方法であって、上記残りの層は、上記第 1 の導電層および上記第 2 の導電層の間に挟まれる上記 1 つまたは複数の電気活性層のすべてをさらに含む。

【 0 0 9 5 】

項 3 8 . 項 3 5 の方法であって、上記レーザのパルス幅は、約 10 ピコ秒以下である。 40

【 0 0 9 6 】

項 3 9 . 項 3 8 の方法であって、上記レーザのパルス幅は、約 6 ピコ秒である。

【 0 0 9 7 】

項 4 0 . 項 3 5 の方法であって、上記レーザは、約 515 nm および約 532 nm の間の動作波長を有する。

【 0 0 9 8 】

項 4 1 . 項 3 5 の方法であって、上記方法によって形成される上記電気活性素子は、エレクトロクロミック素子である。

【 0 0 9 9 】

項42. 項41の方法であって、レーザは、上に形成される上記1つまたは複数の隣接層を有する上記基板の側に向けて位置決めされる。

【0100】

項43. エレクトロクロミック素子を作製するシステムであって、上記システムは、上に上記エレクトロクロミック素子が形成される基板を包含する筐体と、

上記基板上に上記エレクトロクロミック素子の1つまたは複数の層を成膜するように構成された成膜システムと、

上記筐体に搭載され、上に上記エレクトロクロミック素子が形成される上記基板の側に向けてられるレーザであって、上記基板表面上にビームを生じるように位置決めされる上記レーザと、

上記基板に対して上記ビームを移動する位置決めデバイスと、

上記基板表面上における上記ビームの集束によって発生する粒状物質または蒸気を収集する収集システムとを含む。

【0101】

項44. 項43のシステムにおけるエレクトロクロミック素子の作製方法であって、上記方法は、

上記筐体内に基板を設置すること、および上記筐体から上記基板を除去することがないこと、

上記基板表面上に上記エレクトロクロミック素子の1つまたは複数の隣接層を形成することと、

上記レーザを用いて上記1つまたは複数の隣接層の一部を除去することと、

上記1つまたは複数の隣接層を覆う上記エレクトロクロミック素子の1つまたは複数の残りの層を形成することとを含む。

【0102】

項45. エレクトロクロミック素子を作製するシステムであって、上記システムは、上に上記エレクトロクロミック素子が形成される基板を包含する筐体と、

上記基板上に上記エレクトロクロミック素子の1つまたは複数の層を成膜するように構成された成膜システムと、

上記筐体に搭載されたレーザであり、100ピコ秒以下のパルス幅を有し、上記基板上にビームを生じるように位置決めされる上記レーザと、

上記基板に対して上記ビームを移動する位置決めデバイスと、

上記基板表面上における上記ビームの集束によって発生する粒状物質または蒸気を収集する収集システムとを含む。

【0103】

項46. 項45のシステムにおけるエレクトロクロミック素子の作製方法であって、上記方法は、

上記筐体内に基板を設置すること、および上記筐体から上記基板を除去することがないこと、

上記基板表面上に上記エレクトロクロミック素子の1つまたは複数の隣接層を形成することと、

上記レーザを用いて上記1つまたは複数の隣接層の一部を除去することと、

上記1つまたは複数の隣接層を覆う上記エレクトロクロミック素子の1つまたは複数の残りの層を形成することとを含む。

【0104】

一般的な記載または例で上に記載した動作のすべてを必要とするわけではないこと、特別な動作の一部を必要としなくてもよいこと、記載した動作に加えて、さらなる動作が1つまたは複数実施されうることに注意されたい。さらにまた、列挙した動作の順序は、必ずしもそれらが実施される順序ではない。

【0105】

利益、他の利点および課題の解決方法は、特定の実施形態に関して上に記載している。

10

20

30

40

50

しかしながら、利益、利点、課題の解決方法および任意の利益、利点または解決方法を引き起こして著しく生じるまたはより顕著になりうるいかなる特徴も、いずれかの請求項またはすべての請求項の重要な、必須な、または本質的な特徴として解釈されてはならない。

【 0 1 0 6 】

ここでは概念を、特定の実施形態を参照しながら記載しているが、これらの実施形態は単に原理の例示であって、本発明を限定するものではないことが理解される。従って、多くの変形が例示の実施形態になされうること、添付の特許請求の範囲によって規定されるような本発明の範囲を逸脱することなく、他の構成が考えられうることが理解される。

【 図 1 】

図 1

【 図 3 】

図 3 30

【 図 2 】

図 2

10

【 図 4 A 】

【 図 4 B 】

【 図 4 C 】

【図5】

図5

50

【図6】

図6

600

【図7】

図7

700

【図8】

図8

【図 9 A】

図 9 A

【図 9 B】

図 9 B

【図 9 C】

図 9 C

---

フロントページの続き

(74)代理人 100134175

弁理士 永川 行光

(74)代理人 100188857

弁理士 木下 智文

(72)発明者 ハーヴェー・カルヴァイト

アメリカ合衆国 ミネソタ州 55021 バーンズビル ウエスト・ハンドレッドサーティーナ

インス・ストリート 1513

(72)発明者 サティヤ・アッジャラブ

アメリカ合衆国 ミネソタ州 55124 アップル・ヴァレー フローリスト・サークル 15

231

(72)発明者 リー・ヤ・イエー

ドイツ連邦共和国 ガイレンキルヒエン 52511 アン・デア・フォーゲルシュタング 6

(72)発明者 ジャン-クリストフ・ギロン

アメリカ合衆国 ミネソタ州 55436 イーダイナ ワーデン・アベニュー 5525

審査官 廣田 かおり

(56)参考文献 特開2002-076390 (JP, A)

特開2011-009307 (JP, A)

特表2012-517089 (JP, A)

特表2012-523018 (JP, A)

特表2013-536996 (JP, A)

米国特許第05724175 (US, A)

(58)調査した分野(Int.Cl., DB名)

|        |        |

|--------|--------|

| G 02 F | 1 / 15 |

| G 09 F | 9 / 00 |

| G 09 F | 9 / 30 |