(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-180077

(P2007-180077A)

(43) 公開日 平成19年7月12日(2007.7.12)

(51) Int.CI.

H01L 23/50

(2006.01)

F 1

H01L 23/50

H01L 23/50

テーマコード(参考)

U

5 F O 6 7

S

審査請求 未請求 請求項の数 18 O L (全 25 頁)

(21) 出願番号

特願2005-373734 (P2005-373734)

(22) 出願日

平成17年12月27日 (2005.12.27)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人

100080001

弁理士 筒井 大和

(72) 発明者

佐々木 敏夫

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者

石橋 孝一郎

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者

伊藤 富士夫

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】半導体装置における端子数の低減化を図る。

【解決手段】マイコンチップ2と、メモリチップ3と、マイコンチップ2及びメモリチップ3と接続するタブ5cと、タブ5cを支持する吊りリード5gと、複数のインナリード5aと、封止体4とを有し、タブ5cの2つのチップ間の領域に第1スリット7が形成され、さらに吊りリード5gの一端部は、各辺の複数のインナリード5aの外側に配置され、かつ封止体4の側面に露出しているものである。さらにマイコンチップ2の第1電源/第1GND用の電極とタブ5cの第1バーリード5dとが第1ワイヤ9aで接続され、かつメモリチップ3の第1電源/第1GND用の電極と第1バーリード5dとが第2ワイヤ9bで接続されており、両チップのGND/電源の電極をバーリードによって共通化してQFP(半導体装置)1の端子数の低減化を図る。

【選択図】図1

|                      |                     |

|----------------------|---------------------|

| 1: QFP(半導体装置)        | 6: 第2バーリード(第2共通リード) |

| 2: マイコンチップ(第1半導体チップ) | 6a: 支持リード(第2吊りリード)  |

| 3: メモリチップ(第2半導体チップ)  | 7: 第1スリット           |

| 4: 封止体               | 8: 第2スリット           |

| 5a: インナーリード          | 9a: 第1ワイヤ           |

| 5c: タブ               | 9b: 第2ワイヤ           |

| 5d: 第1バーリード(第1共通リード) | 9c: 第3ワイヤ           |

| 5e: 突出部              | 9d: 第4ワイヤ           |

| 5g: 吊りリード(第1吊りリード)   | 9e: 第5ワイヤ           |

**【特許請求の範囲】****【請求項 1】**

主面に半導体素子及び複数の電極が形成され、かつ演算処理機能を有する第1半導体チップと、

主面に半導体素子及び複数の電極が形成され、かつメモリ回路を有する第2半導体チップと、

前記第1及び第2半導体チップと接続するタブと、

前記タブを支持する吊りリードと、

前記第1半導体チップの周囲に配置された複数のリードと、

前記第1半導体チップの第1電源／第1GND用の電極と前記タブとを電気的に接続する第1ワイヤと、10

前記第2半導体チップの第1電源／第1GND用の電極と前記タブとを電気的に接続する第2ワイヤと、

前記第1半導体チップの電極とこれに対応する前記リードとを電気的に接続する第3ワイヤと、

前記第2半導体チップの電極とこれに対応する前記リードとを電気的に接続する第4ワイヤと、

前記第1及び第2半導体チップを封止する封止体とを有し、

前記タブの前記第1半導体チップと前記第2半導体チップの間の領域に第1スリットが形成され、さらに前記吊りリードの一端部は、各辺の前記複数のリードの外側に配置され、かつ前記封止体の側面に露出していることを特徴とする半導体装置。20

**【請求項 2】**

請求項1記載の半導体装置において、前記タブの前記第1ワイヤの接続点と前記第1半導体チップとの間の領域に第2スリットが形成されていることを特徴とする半導体装置。

**【請求項 3】**

請求項1記載の半導体装置において、前記タブ及び前記吊りリードに連結し、かつ前記タブの外周部に配置された第1共通リードと、前記第1共通リードの外側に配置され、かつ前記封止体の側面に露出する支持リードを両端に備え、さらに前記第1半導体チップの第2電源／第2GND用の電極と電気的に接続する第5ワイヤが接続された第2共通リードとを有することを特徴とする半導体装置。30

**【請求項 4】**

請求項3記載の半導体装置において、前記第1共通リードと前記第2共通リードの間にチップ部品が配置されていることを特徴とする半導体装置。

**【請求項 5】**

請求項3記載の半導体装置において、前記第2共通リードの支持リードは、信号用リードの外側に配置されていることを特徴とする半導体装置。

**【請求項 6】**

請求項5記載の半導体装置において、前記第2共通リードの長手方向の側部に、前記第2共通リードに連結する他の支持リードが設けられていることを特徴とする半導体装置。

**【請求項 7】**

請求項1記載の半導体装置において、前記封止体の裏面側から表面側に向かって、前記第1半導体チップと接続するタブ、前記第2半導体チップと接続する前記タブの突出部、前記リードの順の高さでそれぞれが配置されていることを特徴とする半導体装置。40

**【請求項 8】**

請求項3記載の半導体装置において、前記第1共通リードと前記第2共通リードの間にチップ部品が配置されており、前記封止体の裏面側から表面側に向かって、前記第1半導体チップと接続するタブ、前記第2半導体チップと接続する前記タブの突出部、前記リードの順の高さでそれぞれが配置され、さらに、前記チップ部品を支持する前記第2共通リードは、前記第1半導体チップと接続する前記タブと同じ高さに配置されていることを特徴とする半導体装置。50

**【請求項 9】**

請求項 1 記載の半導体装置において、前記封止体の裏面側から表面側に向かって、前記第2半導体チップと接続する前記タブの突出部、前記第1半導体チップと接続する前記タブ、前記リードの順の高さでそれぞれが配置されていることを特徴とする半導体装置。

**【請求項 10】**

請求項 1 記載の半導体装置において、前記吊りリードの両側に、隣接する前記リード間の隙間より幅広の隙間を有していることを特徴とする半導体装置。

**【請求項 11】**

請求項 3 記載の半導体装置において、前記支持リードの両側に、隣接する前記リード間の隙間より幅広の隙間を有していることを特徴とする半導体装置。 10

**【請求項 12】**

主面に半導体素子及び複数の電極が形成された半導体チップと、

前記半導体チップの周囲に配置された複数のリードと、

前記半導体チップと接続し、かつ外周部に配置された第1共通リードを有するタブと、

前記第1共通リードの外側に配置され、かつ両端に支持リードを備えた第2共通リードと、

前記半導体チップの第1電源 / 第1GND用の電極と前記第1共通リードとを電気的に接続する第7ワイヤと、

前記半導体チップの第2電源 / 第2GND用の電極と前記第2共通リードとを電気的に接続する第8ワイヤと、 20

前記半導体チップの電極とこれに対応する前記リードとを電気的に接続する第9ワイヤと、

前記タブを支持する吊りリードと、

前記半導体チップを封止する封止体とを有し、

前記吊りリードの少なくとも一部と前記第2共通リードの支持リードが、前記封止体の側面に露出していることを特徴とする半導体装置。

**【請求項 13】**

請求項 12 記載の半導体装置において、前記第1共通リードと前記第2共通リードの間にチップ部品が配置されていることを特徴とする半導体装置。

**【請求項 14】**

請求項 12 記載の半導体装置において、前記第2共通リードの支持リードは、信号用リードの外側に配置されていることを特徴とする半導体装置。 30

**【請求項 15】**

請求項 14 記載の半導体装置において、前記第2共通リードの長手方向の側部に前記第2共通リードに連結する他の支持リードが設けられていることを特徴とする半導体装置。

**【請求項 16】**

請求項 12 記載の半導体装置において、前記吊りリードの一端部は、各辺の前記複数のリードの外側に配置され、かつ前記封止体の側面に露出していることを特徴とする半導体装置。

**【請求項 17】**

請求項 12 記載の半導体装置において、前記第2共通リードの支持リードは、前記リードの内側に配置されていることを特徴とする半導体装置。 40

**【請求項 18】**

請求項 12 記載の半導体装置において、前記吊りリードの先端は、二股に分離していることを特徴とする半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関し、特に、半導体装置の端子数の低減化に適用して有効な技術に関する。 50

**【背景技術】****【0002】**

マイコンチップと、マイコンチップの横に並べて配置され、かつマイコンチップより薄いSDRAMと、タブと、マイコンチップのパッドとSDRAMのパッドとを接続する第1のワイヤと、SDRAMを飛び越えて配置され、かつ第1のワイヤのループより高い位置にループが形成された第2のワイヤとからなり、多ピン化とコスト低減化を図る技術がある（例えば、特許文献1参照）。

**【0003】**

また、半導体チップと、複数のインナリード及びアウタリードと、インナリードの端部と絶縁性の接着剤を介して接続し、かつ半導体チップと接着剤を介して接続するシート部材と、半導体チップとインナリードを接続する複数のワイヤと、半導体チップと複数のインナリードの間の領域において複数のインナリードのリード列に沿って配置されたバーリードとを有し、QFPの小型化を図る技術がある（例えば、特許文献2参照）。

【特許文献1】特開2005-303222号公報（図2）

【特許文献2】特開2005-347369号公報（図1）

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

複数の半導体チップを有する半導体装置の一例として、演算処理機能を有する半導体チップ（以降、マイコンチップともいう）と、メモリ回路を有する半導体チップ（以降、メモリチップともいう）とが組み込まれた半導体装置が知られている。

**【0005】**

前記半導体装置において、マイコンチップには信号（IO）用の電源とコア用の電源があるが、メモリチップの処理動作（例えば、ON/OFFのタイミング等）がマイコンチップに比べて非常に速いため、メモリチップから発生するノイズ量も大きい（出力ドライバの遷移速度が速く、 $d_i/dt$ が大でノイズ発生量大）。このメモリチップからのノイズがマイコンチップのGNDを伝わってマイコンチップの特にコア用の配線に伝わると誤動作につながることが問題となる。

**【0006】**

また、前記半導体装置において、マイコンチップには信号（IO）用の電源とコア用の電源があるため、電源やGNDの安定化を図ろうとすると、電源/GNDの端子数が多く必要となるが、単に電源/GNDの端子数を増やすと半導体装置の外形サイズが大きくなってしまう。すなわち、電源/GNDの種類が多い半導体装置において、電源/GNDの安定化を図ろうとすると、端子数が増えることが問題である。

**【0007】**

なお、前記特許文献1（特開2005-303222号公報）に記載の半導体装置では、電源がIO用とコア用の2種類あり、IO用とコア用それぞれの電源/GND用の端子が必要となるため、端子数が増えることが問題である。

**【0008】**

また、前記特許文献2（特開2005-347369号公報）に記載の半導体装置では、シート部材の上にバーリードを固定する構造であるため、シート部材を用いることでコストが高くなることが問題であり、さらに組み立ても複雑になることが問題である。

**【0009】**

本発明の目的は、半導体装置の端子数の低減化を図ることができる技術を提供することにある。

**【0010】**

本発明の他の目的は、半導体装置のコストの低減化を図ることができる技術を提供することにある。

**【0011】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面か

10

20

30

40

50

ら明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0013】

すなわち、本発明は、演算処理機能を有する第1半導体チップと、メモリ回路を有する第2半導体チップと、第1及び第2半導体チップと接続するタブと、タブを支持する吊りリードと、複数のリードと、第1及び第2半導体チップを封止する封止体とを有し、タブの2つのチップ間の領域に第1スリットが形成され、さらに吊りリードの一端部は、各辺の複数のリードの外側に配置され、かつ封止体の側面に露出しているものである。さらに第1半導体チップの第1電源／第1GND用の電極とタブとがワイヤで電気的に接続され、かつ第2半導体チップの第1電源／第1GND用の電極とタブとがワイヤで電気的に接続されている。

【0014】

また、本発明は、半導体チップと、この半導体チップの周囲に配置された複数のリードと、半導体チップと接続し、かつ外周部に配置された第1共通リードを有するタブと、タブを支持する吊りリードと、第1共通リードの外側に配置され、かつ両端に支持リードを備えた第2共通リードと、半導体チップを封止する封止体とを有し、吊りリードの少なくとも一部と第2共通リードの支持リードが、封止体の側面に露出しているものである。さらに半導体チップの第1電源／第1GND用の電極と第1共通リードとがワイヤで電気的に接続され、かつ半導体チップの第2電源／第2GND用の電極と第2共通リードとがワイヤで電気的に接続されている。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0016】

第1半導体チップの電源／GND用の電極とタブとがワイヤで接続され、かつ第2半導体チップの電源／GND用の電極とタブとがワイヤで接続されることにより、第1半導体チップ及び第2半導体チップそれぞれの電源／GND用の端子をタブによって共通化することができる。その結果、電源／GND用の端子数を低減することができ、半導体装置の端子数の低減化を図ることができる。

【0017】

また、第1共通リードがタブの外周部に配置されており、かつタブを支持する吊りリードの一端部が封止体の側面に露出していることにより、第1共通リードをシート部材を使わずに固定することができる。その結果、第1共通リードを有する半導体装置のコストの低減化を図ることができる。

【0018】

また、第2共通リードを第1共通リードの外側に配置して共通リードを2重構造にすることにより、電源／GNDを信号用とコア用とに分けて接続することが可能になるとともに、接続時にそれを容易に接続することができる。

【0019】

さらに、共通リードを2重構造にすることにより、電源／GNDの端子を更に共通化することができ、半導体装置の端子数の低減化を更に図ることができる。

【0020】

さらに、第1半導体チップ及び第2半導体チップそれぞれの電源／GNDの電極を第1共通リード及び第2共通リードを介して半導体装置の外部に引き出しているため、半導体チップの周囲に配置された複数のリードにワイヤボンディングを介して電気的に接続するよりも、ワイヤ長を低減することができる。すなわち、ワイヤ抵抗に比べて共通リードの

10

20

30

40

50

方が低抵抗であり、電源電圧マージンの拡張が見込まれる。

【0021】

また、タブの第1半導体チップと第2半導体チップの間の領域にスリットが形成されていることにより、第1半導体チップと第2半導体チップのそれぞれのGND電流が回り込んで相互の半導体チップに影響を与えることを抑制することができ、半導体チップの誤動作を防止することができる。

【発明を実施するための最良の形態】

【0022】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0023】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

【0024】

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0025】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0026】

（実施の形態1）

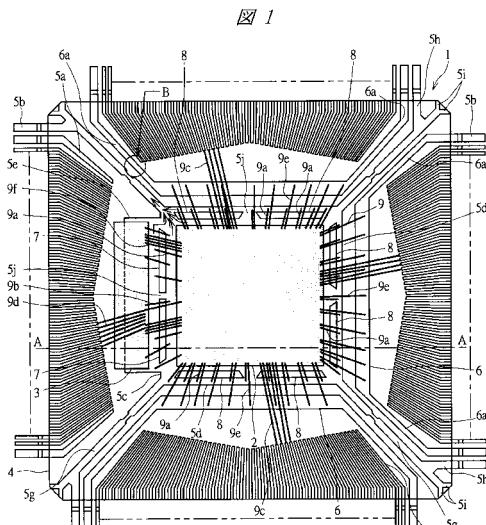

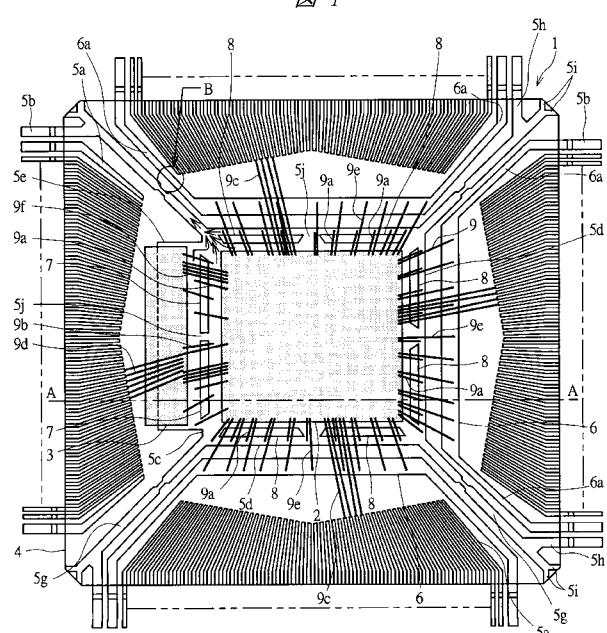

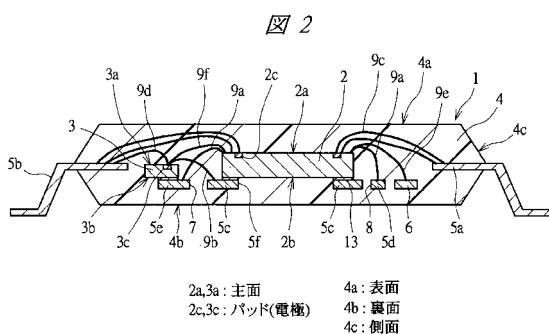

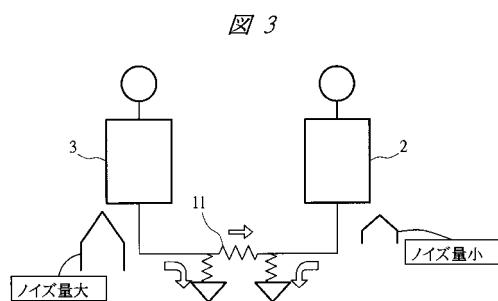

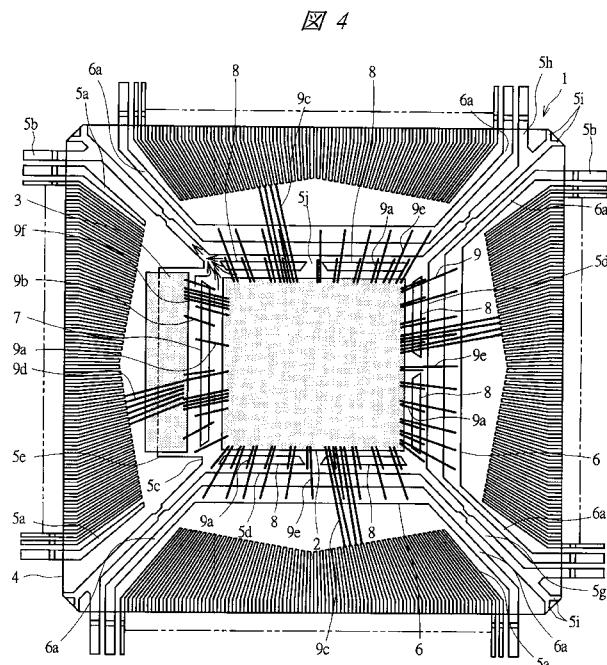

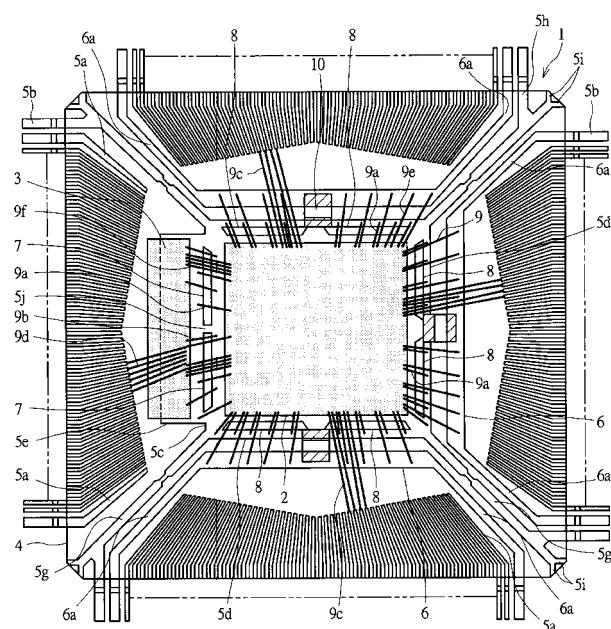

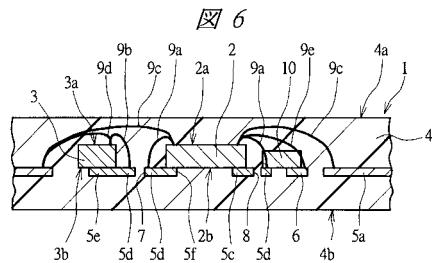

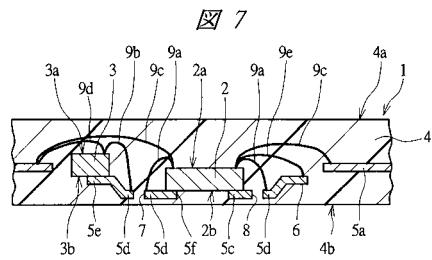

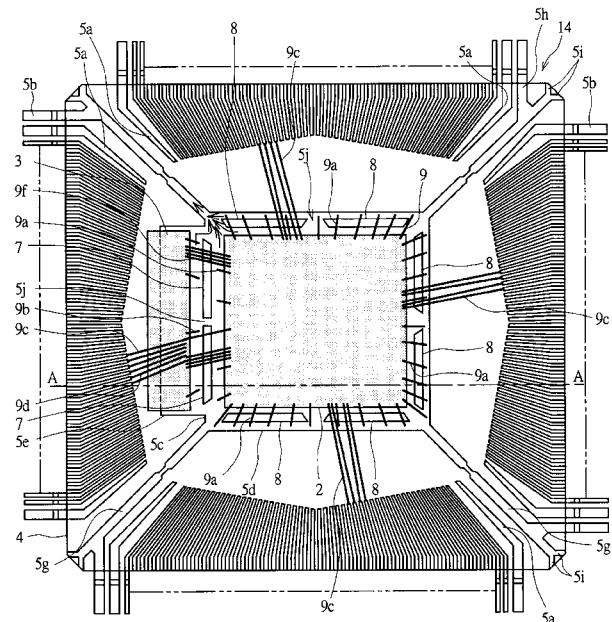

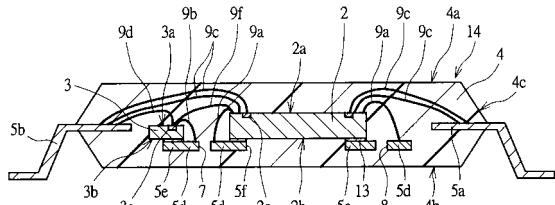

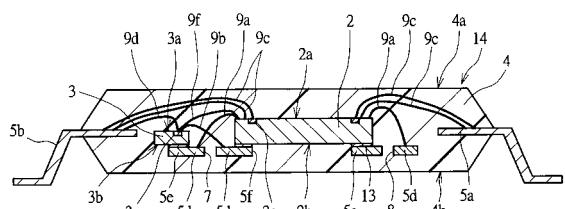

図1は本発明の実施の形態1の半導体装置の内部構造の一例を示す平面図、図2は図1に示すA-A線に沿って切断した構造の一例を示す断面図、図3は図1に示す半導体装置における第1スリットの作用効果の一例を示す概念図、図4及び図5はそれぞれ本発明の実施の形態1の変形例の半導体装置の内部構造を示す平面図、図6～図13はそれぞれ本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【0027】

図1、図2に示す本実施の形態1の半導体装置は、複数の半導体チップが樹脂製の封止体4の内部に埋め込まれた半導体パッケージであり、ここでは、封止体4から突出する外部端子である複数のアウタリード5bがガルウィング状に形成されたQFP(Quad Flat Package)1を一例として取り上げて説明する。

【0028】

QFP1の構成について説明すると、正面2aに半導体素子及び複数のパッド（電極）2cが形成され、かつ演算処理機能を有するマイコンチップ（第1半導体チップ）2と、正面3aに半導体素子及び複数のパッド（電極）3cが形成され、かつメモリ回路を有するメモリチップ（第2半導体チップ）3と、マイコンチップ2及びメモリチップ3を封止する封止体4とを有している。さらに、マイコンチップ2及びメモリチップ3と接続するタブ5cと、タブ5cを支持する吊りリード（第1吊りリード）5gと、マイコンチップ2の周囲に配置されたリードである複数のインナリード5aと、これらインナリード5aそれぞれに繋がり、かつ封止体4の側面4cから突出する複数のアウタリード5bとを有している。

【0029】

また、QFP1では、タブ5cのマイコンチップ2とメモリチップ3の間の領域に第1スリット7が形成されている。また、吊りリード5gの一端部は、各辺において複数のインナリード5aの外側に配置され、かつ封止体4の側面4cの端部において電源/GND

10

20

30

40

50

用の端子部 5 h として側面 4 c に露出している。さらに、吊りリード 5 g の先端は、分割部 5 i として二股に分かれた形状になっている。

#### 【0030】

また、QFP 1 には、各半導体チップとこれらに対応するインナリード 5 a あるいはタブ 5 c とを電気的に接続する複数のワイヤ（例えば、金線）9 が設けられている。ワイヤ 9 には、マイコンチップ 2 の第 1 電源 / 第 1 GND 用のパッド 2 c とタブ 5 c を電気的に接続する第 1 ワイヤ 9 a と、メモリチップ 3 の第 1 電源 / 第 1 GND 用のパッド 3 c とタブ 5 c を電気的に接続する第 2 ワイヤ 9 b と、マイコンチップ 2 の信号用のパッド 2 c とこれに対応するインナリード 5 a を電気的に接続する第 3 ワイヤ 9 c と、メモリチップ 3 の第 1 電源 / 第 1 GND 用のパッド 3 c とこれに対応するインナリード 5 a を電気的に接続する第 4 ワイヤ 9 d がある。10

#### 【0031】

更に説明すると、マイコンチップ 2 のパッド 2 c の内、第 1 ワイヤ 9 a を介してタブ（共通リード）5 c と電気的に接続されるのは第 1 電源用のパッド 2 c か、あるいは第 1 GND 用のパッド 2 c である。マイコンチップ 2 のパッド 2 c の内、第 1 ワイヤ 9 a を介してタブ 5 c と電気的に接続されているのが第 1 GND 用パッドの場合は、マイコンチップ 2 の第 1 電源用のパッド 2 c は、第 3 ワイヤ 9 c を介してインナリード 5 a と電気的に接続される。また、メモリチップ 3 に関しても、マイコンチップ 2 と同様であり、メモリチップ 3 のパッド 3 c の内、第 2 ワイヤ 9 b を介してタブ（共通リード）5 c と電気的に接続されているのが第 1 GND 用パッドの場合は、メモリチップ 3 の第 1 電源用のパッド 3 c は、第 4 ワイヤ 9 d を介してインナリード 5 a と電気的に接続される。これらは、電源と GND が共通のタブ（共通リード）5 c にワイヤボンディングすることで生じるショート不良を防ぐためである。ここで、電源用のパッドよりも GND 用のパッドの数が多い場合は、GND 用のパッドとタブ 5 c をワイヤを介して電気的に接続することで、タブ 5 c の外周に配置されるインナリード 5 a の数を低減することが可能である。20

#### 【0032】

ここで、第 1 半導体チップであるマイコンチップ 2 は、演算処理機能を有した半導体チップであり、例えば、マイクロプロセッサやチップセット等の機能が 1 チップに集積されたものである。

#### 【0033】

一方、第 2 半導体チップであるメモリチップ 3 は、メモリ回路を有した半導体チップであり、例えば、DRAM (Dynamic Random Access Memory) 等である。メモリチップ 3 は、マイコンチップ 2 の制御によって動作するものであり、したがって、図 1 に示すように、マイコンチップ 2 とメモリチップ 3 とでは、マイコンチップ 2 の方が端子数（パッド数）は多い。30

#### 【0034】

例えば、マイコンチップ 2 は、一辺が 5 ~ 10 mm の四角形のものであり、その厚さが、例えば、0.28 mm または 0.42 mm である。一方、メモリチップ 3 は、例えば、5 × 2 mm の大きさであり、厚さは、0.2 mm 程度である。

#### 【0035】

また、マイコンチップ 2 は、図 2 に示すようにタブ 5 c 上に Ag ペースト 13 等のダイボンド材を介して固着（実装）されており、一方、メモリチップ 3 は、タブ 5 c の一辺の側方に突出して形成された突出部 5 e 上に、同様に Ag ペースト 13 等のダイボンド材を介して固着（実装）されている。すなわち、タブ 5 c とマイコンチップ 2 の裏面 2 b とが Ag ペースト 13 によって接続されており、一方、タブ 5 c の突出部 5 e とメモリチップ 3 の裏面 3 b とが同様に Ag ペースト 13 によって接続されている。タブ 5 c には、その中央部付近に開口部 5 f が形成されており、これにより、マイコンチップ 2 の裏面 2 b と封止体 4 の樹脂とが広い面積で密着している。その結果、QFP 1 におけるリフロークラックの発生を防ぐことができる。また、本実施の形態 1 ではこれに限定されるものではなく、接着層を有する DAF (Die Attach Film) を介してマイコンチップ 2 4050

をタブ 5 c 上、かつメモリチップ 3 を突出部 5 e 上に実装してもよい。マイコンチップ 2 の裏面 2 b には接着層を有する D A F が配置されているため、マイコンチップ 2 の裏面 2 b に樹脂が接触する場合に比べ、D A F に樹脂が接触する方が接着強度を向上することができる。これにより、Q F P 1 におけるリフロークラックの発生を更に防ぐことが可能である。また、メモリチップ 3 の裏面 3 b の一部も突出部 5 e から露出していることから、上記マイコンチップ 2 と同等の効果が期待できる。

#### 【 0 0 3 6 】

さらに、本実施の形態 1 の Q F P 1 には、タブ 5 c 及び吊りリード 5 g に連結し、かつタブ 5 c の外周部に配置された第 1 バーリード（第 1 共通リード）5 d と、第 1 バーリード 5 d の外側に配置され、かつ封止体 4 の側面 4 c に露出する支持リード（第 2 吊りリード）6 a を両端に備えるとともにマイコンチップ 2 の第 2 電源 / 第 2 G N D 用のパッド 2 c と電気的に接続する第 5 ワイヤ 9 e が接続された第 2 バーリード（第 2 共通リード）6 とが形成されている。詳細には、第 1 バーリード 5 d は、タブ 5 c の周囲に 4 つ（隣り合う吊りリード 5 g 間に 1 つずつ）形成されているが、そのうち 1 つは他の 3 つの第 1 バーリード 5 d に比べて、その幅を広く形成している。これにより、上記した突出部 5 e を形成している。また、マイコンチップ 2 の第 2 電源 / 第 2 G N D 用のパッド 2 c についても、上記したように、マイコンチップ 2 の第 2 G N D 用のパッド 2 c が第 5 ワイヤ 9 e を介して第 2 バーリード（共通リード）6 と電気的に接続されている場合は、マイコンチップ 2 の第 2 電源用のパッド 2 c は第 3 ワイヤ 9 c を介してインナリード 5 a と電気的に接続されている。

#### 【 0 0 3 7 】

すなわち、第 1 バーリード 5 d の外側に配置された第 2 バーリード 6 は、その両端に設けられた支持リード 6 a によって支持されており、さらに、支持リード 6 a の端部は、封止体 4 の側面 4 c に露出して端子となっている。

#### 【 0 0 3 8 】

その際、第 2 バーリード 6 の両端から延在する支持リード 6 a は、複数の信号用リード（信号用のインナリード 5 a）の外側、言い換えると、封止体 4 の一辺に沿って配置された複数の信号用リードの外側であり、吊りリード 5 g の電源 / G N D 用の端子部 5 h または吊りリード 5 g の先端を二股に分割した分割部 5 i の内側に配置されている。

#### 【 0 0 3 9 】

また、Q F P 1 では、図 1 に示すように、タブ 5 c の外周部に配置された第 1 バーリード 5 d と連結する 4 本の吊りリード 5 g がタブ 5 c の角部に対角線上に配置されており、したがって、第 2 バーリード 6 とこれを支持する支持リード 6 a は、複数の吊りリード 5 g の内、隣り合う 2 本の吊りリード 5 g と第 1 バーリード 5 d とによって囲まれた領域に配置されている。

#### 【 0 0 4 0 】

そのうち、第 2 バーリード 6 は、複数のインナリード 5 a の先端部と第 1 バーリード 5 d の間の領域にインナリード列に沿って配置されており、さらに、第 2 バーリード 6 の支持リード 6 a は、インナリード列に並んでタブ 5 c の吊りリード 5 g に隣接して配置されている。

#### 【 0 0 4 1 】

なお、Q F P 1 においては、マイコンチップ 2 の第 1 電源 / 第 1 G N D 用のパッド 2 c に接続された第 1 ワイヤ 9 a が、タブ 5 c の第 1 バーリード 5 d に接続されているとともに、同じくメモリチップ 3 の第 1 電源 / 第 1 G N D 用のパッド 3 c に接続された第 2 ワイヤ 9 b が、タブ 5 c の第 1 バーリード 5 d に接続されている。

#### 【 0 0 4 2 】

さらに、マイコンチップ 2 の第 2 電源 / 第 2 G N D 用のパッド 2 c に接続された第 5 ワイヤ 9 e が、第 1 バーリード 5 d の外側に配置された第 2 バーリード 6 に接続されている。

#### 【 0 0 4 3 】

10

20

30

40

50

ここで、第1ワイヤ9aによって第1バーリード5dと電気的に接続されるマイコンチップ2の第1電源／第1GND、及び第2ワイヤ9bによって第1バーリード5dと電気的に接続されるメモリチップ3の第1電源／第1GNDは、例えば、コア用の電源／GND(Vss)である。

#### 【0044】

一方、第5ワイヤ9eによって第2バーリード6と電気的に接続されるマイコンチップ2の第2電源／第2GNDは、例えば、信号(I/O)用の電源／GND(Vss)である。

#### 【0045】

すなわち、本実施の形態1のQFP1では、電源／GNDの共通化のために、電源／GND用のバーリードとして、第1バーリード5dと第2バーリード6の2種類を設けており、マイコンチップ2のコア用の電源／GNDと信号用の電源／GNDを、それぞれ別々のバーリードに分けて接続している。

#### 【0046】

また、QFP1では、マイコンチップ2とメモリチップ3とがチップ間ワイヤ(第6ワイヤ)9fで直接電気的に接続されている。メモリチップ3はマイコンチップ2を介して外部との信号処理を行う、すなわち、マイコンチップ2がメモリチップ3を制御している。そのため、メモリチップ3における信号用のパッドとマイコンチップ2におけるメモリインターフェース用のパッドとが第6ワイヤ9fを介して電気的に接続されている。

#### 【0047】

また、タブ5cの第1バーリード5dの領域において、第1ワイヤ9aの接続点とマイコンチップ2との間の領域に第2スリット8が形成されている。すなわち、マイコンチップ2と第1バーリード5dとを第1ワイヤ9aで接続する際には、第2スリット8を飛び越えて第1バーリード5dの第2スリット8の外側の領域に接続することが好ましい。

#### 【0048】

また、図1のB部に示すように、吊りリード5gの両側(吊りリード5gと支持リード6aとの間)と、第2バーリード6の支持リード6aの両側(支持リード6aと吊りリード5gとの間、および支持リード6aと信号用リード(インナリード5a)との間)には、複数の信号用リードの内、隣接するインナリード5a間の間隔より幅広の間隔が形成されている。

#### 【0049】

なお、インナリード5a、アウタリード5b、タブ5c、吊りリード5g、第1バーリード5d、第2バーリード6及びその支持リード6a等は、銅合金または鉄-Ni合金等からなる薄板状の部材である。さらに、封止体4は、エポキシ系の熱硬化性樹脂等から形成されている。

#### 【0050】

本実施の形態1のQFP1では、マイコンチップ2のコア用電源の複数のパッド2cと第1バーリード5dとがそれぞれ複数の第1ワイヤ9aで接続され、かつメモリチップ3のコア用電源の複数のパッド3cと第1バーリード5dとがそれぞれ複数の第2ワイヤ9bで接続されることにより、マイコンチップ2及びメモリチップ3それぞれのコア用の電源のパッド2c, 3cをタブ5cによって共通化することができる。

#### 【0051】

その結果、QFP1のコア用電源の端子数を低減することができ、QFP1の端子数の低減化を図ることができる。

#### 【0052】

さらに、第1バーリード5dの外側に第2バーリード6を配置してバーリードを2重構造にすることにより、電源／GNDをコア用の第1電源／第1GNDと、信号用の第2電源／第2GNDとに分けて接続することが可能になる。これにより、それぞれの電源／GNDに対してワイヤ9を接続する際に、各ワイヤを容易に接続することができる。

#### 【0053】

10

20

30

40

50

なお、バーリードを2重構造にすることにより、電源/GNDの端子を更に共通化することができ、QFP1の端子数の低減化を更に図ることができる。

#### 【0054】

例えば、図1に示すQFP1の場合、1本のバーリードに10本程度のGND/電源用のワイヤ9を接続可能であるため、吊りリード5gや支持リード6aの配置により、それらの両側に所定の隙間が必要であったとしても、1辺あたり7本程度の端子(リード)を削減することができ、QFP1の端子数の低減化を図ることができる。

#### 【0055】

また、第1バーリード5dはタブ5cの外周部に配置されており、かつタブ5cを支持する吊りリード5gの一端部が封止体4の側面4cに露出しており、さらに、第2バーリード6は、その両端で第2バーリード6を支持する支持リード6aが封止体4の側面4cに露出しており、これにより、第2バーリード6は2点支持となるため、第1バーリード5d及び第2バーリード6をシート部材を使わずに固定することができる。10

#### 【0056】

その結果、シート部材を介してバーリードを固定する半導体装置に比較して、第1バーリード5d及び第2バーリード6を有するQFP1のコストの低減化を図ることができる。。

#### 【0057】

また、タブ5cのマイコンチップ2とメモリチップ3の間の領域に第1スリット7が形成されていることにより、マイコンチップ2とメモリチップ3のそれぞれのGND電流が回り込んで相互の半導体チップに影響を与えることを抑制できる。上記したように、メモリチップ3のGND電流から発生するノイズ量は大きく、マイコンチップ2の特にコア用の配線に伝わると誤動作の原因となる。そのため、第1スリット7が形成されていないと、メモリチップ3の第1GND用のパッド3cと電気的に接続される第2ワイヤ9bからマイコンチップ2の第1GND用のパッド2cと電気的に接続される第1ワイヤ9aを介してノイズが伝わってしまう。しかしながら、本実施の形態1では、第1ワイヤ9aと第2ワイヤ9bのそれぞれの接続点(ワイヤ接合部)の間に第1スリット7が形成されているため、第2ワイヤ9bからのノイズを第1ワイヤ9aに伝わり難くすることが可能である。20

#### 【0058】

すなわち、両チップ間にスリットを形成することで、図3に示すように、チップ間GNDのL成分(抵抗11)を大きくすることができ、お互いのGND電流(ノイズ)の回り込みを抑制できる。30

#### 【0059】

その結果、マイコンチップ2やメモリチップ3の誤動作を防止することができる。

#### 【0060】

なお、2つの第1スリット7間にブリッジ部5jが設けられてスリットが2つに分割されていることにより、タブ5cのチップ間の領域の反りを防止することができる。これは、メモリチップ3が実装されている突出部5eの幅は、他の第1バーリード5dの幅よりも太いため、突出部5eに応力が集中し易い。ここで、第1スリット7間にブリッジ部5jが設けられていない場合は、突出部5eはタブ5cと2箇所のみで支持されることになる。このとき、支持している箇所が、互いに対向する位置で支持されていれば、突出部5eを支える強度は確保できるが、図1に示すように、2箇所の支持部が同一方向に形成されている場合は、上下方向(封止体4の厚さ方向)における応力に対して弱くなる。そこで、図1に示すように、突出部5eを支持する箇所が同一方向に形成されている場合は、第1スリット7にブリッジ部5jを形成することで、突出部5eを支持する強度を向上することができるため、第1ワイヤ9aや第2ワイヤ9bの接続不良の発生を低減できる。40

#### 【0061】

また、タブ5cの第1バーリード5dの領域において、第1ワイヤ9aの接続点とマイ

コンチップ2との間の領域に第2スリット8が形成されていることにより、高温時のA gペースト13による熱応力の進展を防止してリフロークラックの発生や、第1ワイヤ9aの剥がれを防止することができる。

#### 【0062】

したがって、マイコンチップ2と第1バーリード5dとを第1ワイヤ9aで接続する際には、第2スリット8を飛び越えて第1バーリード5dの第2スリット8の外側の領域に接続することが好ましい。ただし、例えば、タブ5cの角部のようにワイヤリングを斜めに行わなければならぬような領域やブリッジ部5j近傍については、必ずしも第2スリット8を飛び越えた領域に接続しなくてもよい。

#### 【0063】

なお、第2スリット8についてもスリット間にブリッジ部5jが設けられている。上記したように、第1バーリード5dを支持する箇所が、互いに対向する位置にあるので、応力による反りには強い構造である。しかしながら、単に第2スリット8を相対的に大きく形成すると、第1バーリード5dの幅が相対的に細くなるため、第1バーリード5dの強度（機械的強度）が低下してしまう。そこで、図1に示すように、第2スリット8についてもスリットにブリッジ部5jを設けることにより、第1バーリード5dの領域の反りを防止することができ、第1ワイヤ9aの接続不良の発生を低減できる。

#### 【0064】

また、図1のB部に示すように、吊りリード5gの両側と、第2バーリード6の支持リード6aの両側に、隣接するインナリード5a間の隙間より幅広の隙間が形成されていることにより、インナリード5aの先端切断時にプレス金型を配置することができ、各インナリード5aの先端カットを容易に行うことができる。

#### 【0065】

すなわち、各リードのパターン形成は、エッチングまたはプレス加工で行うが、各インナリード5aの先端を限界まで細くし、その後の先端のカッティングでインナリード5aの先端成形を行う。その際、吊りリード5gの両側を含む支持リード6aの両側に、十分な隙間（クリアランス）が確保されていることにより、プレス金型を配置してプレス加工を容易に行うことができる。

#### 【0066】

なお、第2バーリード6の両端から延在する支持リード6aが、信号用リード（信号用のインナリード5a）の外側、すなわち、吊りリード5gの隣に配置されていることにより、インナリード5aの先端カッティング用のクリアランス確保によるインナリード配置不可の領域をできるだけ少なくしてインナリード5aの本数を可能な限り確保することができる。

#### 【0067】

また、タブ5cを支持する吊りリード5gの先端が、分割部5iとして二股に分かれた形状になっていることにより、QFP1の組み立てにおけるフレームの安定性（二股に分かれているので折り曲げる際の折れ易さ）を向上でき、QFP1の組み立て性の向上を図ることができる。ここで、分割部5iはQFP1が完成するまで、リードフレームの枠体に保持されていれば問題ないので、その幅は端子部5hより狭いことが好ましい。これにより、封止体4の一辺におけるリードの数を増加して配置することができる。

#### 【0068】

次に、本実施の形態1のQFP1の変形例について説明する。

#### 【0069】

図4に示す変形例のQFP1は、タブ5cのチップ間に形成される第1スリット7を、図1に示すようなブリッジ部5jを設げずに1つの長いスリットとしたものであり、これにより、チップ間でお互いのGND電流（ノイズ）の回り込みをさらに抑制することが可能になる。特にメモリチップ3からマイコンチップ2に流れ込むGND電流の抑制に有用である。

#### 【0070】

10

20

30

40

50

また、図5に示す変形例のQFP1は、第1バーリード5dと第2バーリード6の間にチップコンデンサ10等のチップ部品を搭載したものである。すなわち、第1バーリード5dと第2バーリード6の両バーリード上に橋渡すように、チップ部品の一端を第1バーリード5dと電気的に接続し、チップ部品の他端を第2バーリード6と電気的に接続して、半田付けしてチップコンデンサ10を搭載したものである。ここで、本実施の形態1では、例えば第1バーリード5dはマイコンチップ2の第1GND用のパッド2cと第1ワイヤ9aを介して電気的に接続されており、第2バーリード6はマイコンチップ2の第1電源用のパッド2cと第5ワイヤ9eを介して電気的に接続されている。これにより、電源ノイズをさらに除去してQFP1の回路性能を向上させることができる。また、本実施の形態1ではこれに限定されるものではなく、例えば第1バーリード5dはマイコンチップ2の第1電源用のパッド2cと第1ワイヤ9aを介して電気的に接続されており、第2バーリード6はマイコンチップ2の第1GND用のパッド2cと第5ワイヤ9eを介して電気的に接続されてもよい。更には、第2電源用のパッドおよび第2GND用のパッドと接続されていても良い。

10

## 【0071】

なお、チップコンデンサ10の大きさは、例えば、0.6mm×0.3mm、あるいは0.4mm×0.2mm等である。また、チップ部品は、チップコンデンサ10に限らず、他のチップ部品であってもよい。

## 【0072】

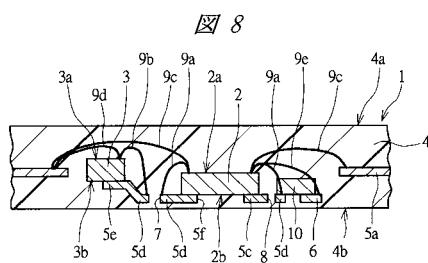

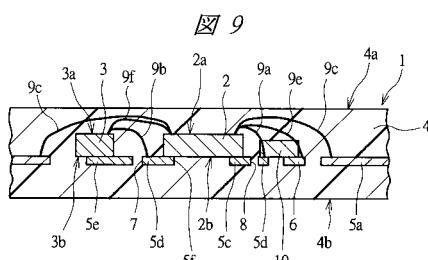

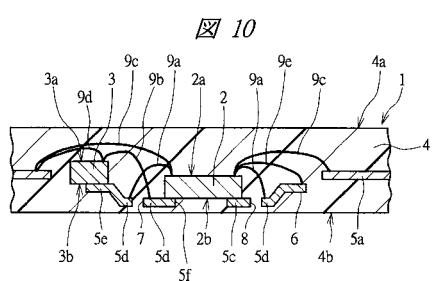

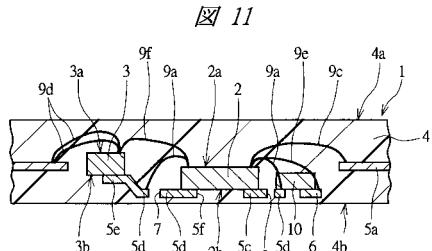

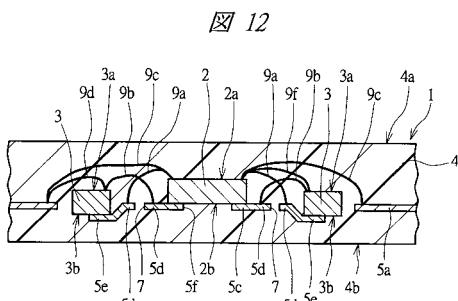

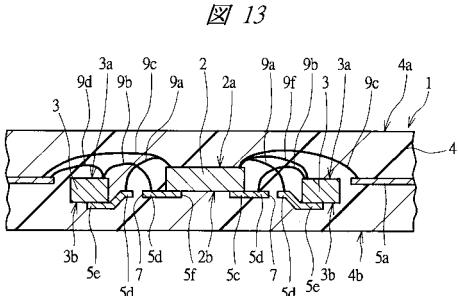

次に、図6～図13は、QFP1におけるインナリード5aと、タブ5cと、タブ5cの突出部5eのそれぞれの高さの関係とワイヤリング状態を表した種々の変形例であり、これらの構造について説明する。

## 【0073】

図6は、マイコンチップ2とメモリチップ3とチップコンデンサ10が搭載されているQFP1において、インナリード5aと、マイコンチップ2を支持するタブ5cと、メモリチップ3を支持するタブ5cの突出部5eと、チップコンデンサ10を支持する第2バーリード6の高さが全て同じ高さに形成されたQFP1である。この場合、リードフレームの曲げ加工が少ないためQFP1の組み立て性を向上させることができる。

## 【0074】

図7は、マイコンチップ2とメモリチップ3が搭載されているQFP1において、インナリード5aと、マイコンチップ2を支持するタブ5cと、メモリチップ3を支持するタブ5cの突出部5eが、封止体4の裏面4b側から表面4a側に向かって順に、マイコンチップ2と接続するタブ5c、メモリチップ3と接続するタブ5cの突出部5e、インナリード5aの順の高さでそれぞれが配置されている。

## 【0075】

すなわち、下から順に、タブ5c、タブ5cの突出部5e、インナリード5aとなっており、マイコンチップ2の高さをメモリチップ3より低くすることにより、インナリード5aとマイコンチップ2の間のワイヤ接続や、チップ間のワイヤ接続を容易に行うことができる。

## 【0076】

また、図8は、図7の構造に対してチップコンデンサ10を搭載する際に、突出部5eと反対側の第2バーリード6上(又は、突出部5e以外の他の第2バーリード6上)にチップコンデンサ10を接続するものである。その際、第2バーリード6をタブ5cと同じ高さに配置する。すなわち、封止体4の裏面4b側から表面4a側に向かって、タブ5c、タブ5cの突出部5e、インナリード5aの高さ順でそれぞれが配置され、かつチップコンデンサ10を支持する第2バーリード6が、タブ5cと同じ高さに配置されている。

## 【0077】

これにより、図7の構造と同様に、マイコンチップ2の高さをメモリチップ3より低くすることにより、インナリード5aとマイコンチップ2の間のワイヤ接続や、チップ間のワイヤ接続を容易に行うことができ、さらに第2バーリード6上のチップコンデンサ10

40

50

上でインナリード 5 a とマイコンチップ 2 のワイヤ接続を容易に行うことができる。

【0078】

また、図 9 は、図 6 に示す構造において、マイコンチップ 2 の GND を直接第 1 バーリード 5 d に接続することができない場合に、一度メモリチップ 3 にワイヤ接続し、そこから第 1 バーリード 5 d に接続することにより、マイコンチップ 2 の GND 配線を確保するものである。

【0079】

図 10 は、図 7 に示す構造において、マイコンチップ 2 及びメモリチップ 3 それぞれの GND をチップ間の第 1 バーリード 5 d に接続する際に、それぞれの半導体チップのすぐ脇の直下は、キャピラリーサイズの制限により、ワイヤボンディングできない。この場合に第 1 スリット 7 を飛び越して第 1 バーリード 5 d のできる限り遠い箇所にワイヤ接続を行うことにより、GND 配線を確保することができる。詳細に説明すると、マイコンチップ 2 の GND 用のパッド 2 c と第 1 ワイヤ 9 a が電気的に接続される第 1 バーリード 5 d との間に第 1 スリット 7 が配置され、メモリチップ 3 の GND 用のパッド 2 c と第 2 ワイヤ 9 b が電気的に接続される第 1 バーリード 5 d との間に第 1 スリット 7 が配置されている。これにより、チップ間の間隔を詰めることができる。

【0080】

また、図 11 は、図 8 に示す構造において、メモリチップ 3 の GND を直接第 1 バーリード 5 d に接続できない場合に、一度マイコンチップ 2 にワイヤ接続し、そこから第 1 バーリード 5 d に接続するものであり、これにより、メモリチップ 3 の GND 配線を確保することができる。

【0081】

また、図 12 は、マイコンチップ 2 とその両側にメモリチップ 3 が搭載されている QFP 1 において、インナリード 5 a とタブ 5 c の高さを同じにし、タブ 5 c の両側に配置された突出部 5 e をタブ 5 c より低くするものである。これにより、メモリチップ 3 がマイコンチップ 2 より低くなるため、メモリチップ 3 の上部でのワイヤリングを容易にすることができます。すなわち、インナリード 5 a とマイコンチップ 2 間のワイヤリングを容易に行うことができる。さらに、それぞれの半導体チップと第 1 バーリード 5 d のワイヤ接続を容易に行うことができる。また、メモリチップ 3 が低く配置されたことにより、メモリチップ超えのワイヤのワイヤ長を短くすることができる。これにより、金線のコストの低減化を図ることができる。

【0082】

また、図 13 は、図 12 に示す構造において、インナリード 5 a の高さをタブ 5 c より高く配置したものであり、封止体 4 の裏面 4 b 側から表面 4 a 側に向かって、タブ 5 c の突出部 5 e、タブ 5 c、インナリード 5 a の順の高さでそれぞれが配置されているものである。これにより、インナリード 5 a の位置がタブ 5 c よりも高くなつたため、メモリチップ 3 を飛び越えてマイコンチップ 2 とインナリード 5 a とを接続するワイヤリングを図 12 に示す場合よりも容易に行うことができる。但し、図 12 に示す場合よりも、リードフレーム加工数が多くなる。

【0083】

次に本実施の形態 1 の図 1 及び図 2 に示す QFP 1 の組み立てについて説明する。

【0084】

まず、第 1 バーリード 5 d 及び突出部 5 e が形成されたタブ 5 c と、タブ 5 c の外側に形成された第 2 バーリード 6 と、タブ 5 c の周囲に形成された複数のインナリード 5 a を有するリードフレームを準備する。

【0085】

その後、Ag ペースト 13 を介してタブ 5 c 上にマイコンチップ 2 を搭載し、さらにタブ 5 c の突出部 5 e 上にメモリチップ 3 を搭載する。

【0086】

その後、ワイヤボンディングを行う。すなわち、マイコンチップ 2 のパッド 2 c と第 1

10

20

30

40

50

バーリード 5 d とを第 1 ワイヤ 9 a で電気的に接続し、メモリチップ 3 のパッド 3 c と第 1 バーリード 5 d とを第 2 ワイヤ 9 b で電気的に接続し、マイコンチップ 2 のパッド 2 c と第 2 バーリード 6 とを第 5 ワイヤ 9 e で電気的に接続し、マイコンチップ 2 のパッド 2 c とメモリチップ 3 のパッド 3 c とをチップ間ワイヤ（第 6 ワイヤ）9 f で電気的に接続する。さらに、メモリチップ 3 のパッド 3 c とインナリード 5 a とを第 4 ワイヤ 9 d で電気的に接続し、マイコンチップ 2 のパッド 2 c とインナリード 5 a とを第 3 ワイヤ 9 c で電気的に接続する。

## 【0087】

その後、樹脂モールディングを行って封止体 4 を形成し、マイコンチップ 2、メモリチップ 3 及び複数のワイヤ 9 等を封止体 4 で樹脂封止する。

10

## 【0088】

その後、アウタリード 5 b の切断・成形を行ってアウタリード 5 b をガルウィング状に曲げ成形する。

## 【0089】

これにより、QFP 1 の組み立て完了となる。

## 【0090】

## (実施の形態 2)

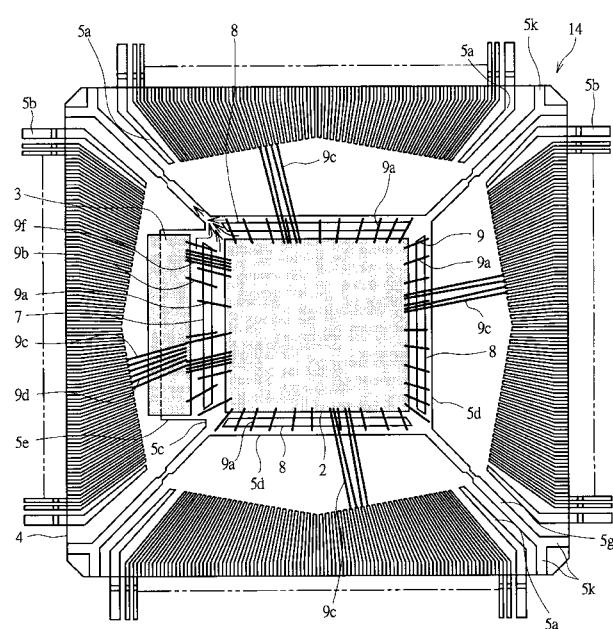

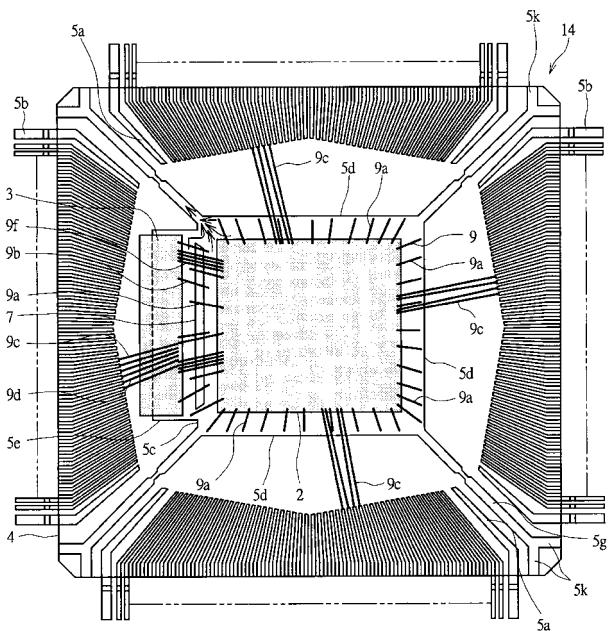

図 14 は本発明の実施の形態 2 の半導体装置の内部構造の一例を示す平面図、図 15 は図 14 に示す A - A 線に沿って切断した構造の一例を示す断面図、図 16 は本発明の実施の形態 2 の変形例の半導体装置の内部構造を示す平面図、図 17 は図 16 に示す A - A 線に沿って切断した構造の一例を示す断面図、図 18 及び図 19 はそれぞれ本発明の実施の形態 2 の変形例の半導体装置の内部構造を示す平面図である。

20

## 【0091】

図 14 及び図 15 に示す本実施の形態 2 の半導体装置は、共通リードとして第 1 バーリード 5 d のみを有したバーリード 1 重構造の QFP 14 である。なお、実施の形態 1 の図 1 に示す QFP 1 と同様に、タブ 5 c にはその外周部に第 1 バーリード 5 d が形成されており、さらに側方に突出した突出部 5 e も設けられている。したがって、タブ 5 c 上に第 1 半導体チップであるマイコンチップ 2 が搭載され、突出部 5 e 上に第 2 半導体チップであるメモリチップ 3 が搭載されている。

## 【0092】

本実施の形態 2 の QFP 14 では、マイコンチップ 2 のコア用電源のパッド 2 c と第 1 バーリード 5 d とを第 1 ワイヤ 9 a で接続し、かつメモリチップ 3 のコア用電源のパッド 3 c と第 1 バーリード 5 d とを第 2 ワイヤ 9 b で接続することにより、マイコンチップ 2 及びメモリチップ 3 それぞれのコア用の電源のパッド 2 c, 3 c をタブ 5 c によって共通化することができる。

30

## 【0093】

その結果、QFP 14 のコア用電源の端子数を低減することができ、QFP 14 の端子数の低減化を図ることができる。

## 【0094】

なお、本実施の形態 2 の QFP 14 では、第 1 バーリード 5 d の外側の第 2 バーリード 6 (図 1 参照) が設けられていないため、これを支持する支持リード 6 a も設けられていない。したがって、実施の形態 1 の図 1 に示す QFP 1 に比較して支持リード 6 a を配置しない分、QFP 14 の外観サイズを変えずに端子数を増加させることも可能である。

40

## 【0095】

QFP 14 における他の構造とその構造によって得られる作用効果については、実施の形態 1 の QFP 1 と同様であるため、その重複説明は省略する。

## 【0096】

次に、図 16 及び図 17 に示す変形例の QFP 14 は、タブ 5 c のチップ間に形成される第 1 スリット 7 を、1 つの長いスリットとしたものであり、これにより、チップ間でお互いの GND 電流 (ノイズ) の回り込みをさらに抑制することが可能になる。

50

## 【0097】

また、図18に示す変形例のQFP14は、タブ5cの第1バーリード5dに形成された第2スリット8を、1つの長いスリットとしたものである。これにより、高温時のAgペースト13による熱応力の進展をさらに防止してリフロークラックや、第1ワイヤ9aの剥がれの発生をさらに防止することができる。

## 【0098】

また、タブ5cを支持する吊りリード5gの先端が、二股に分離した分離端子部5kとなっており、封止体4の側面4cに端子として露出している。これにより、QFP14の組み立てにおけるフレームの安定性を向上でき、QFP14の組み立て性の向上を図ることができる。

10

## 【0099】

また、図19に示す変形例のQFP14は、第1バーリード5dの第2スリット8を削除したものであり、チップ間の第1スリット7のみ第1バーリード5dに形成されている。これにより、各第1バーリード5dにおけるボンディング領域を広げることができ、ボンディング性の向上を図ることができる。

## 【0100】

## (実施の形態3)

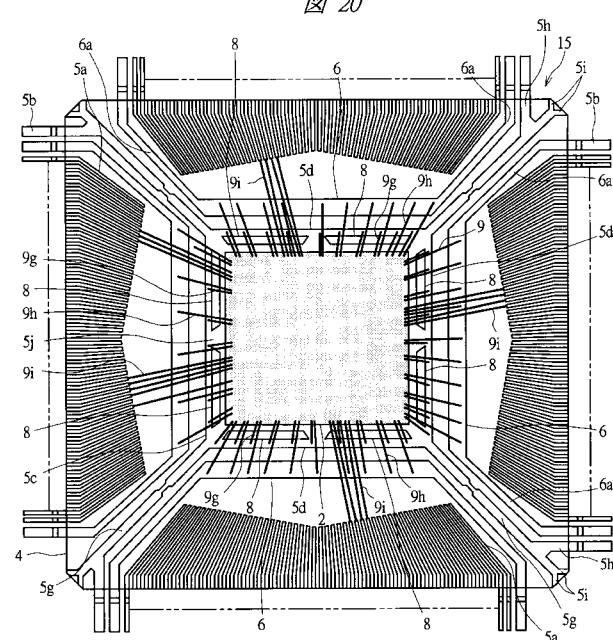

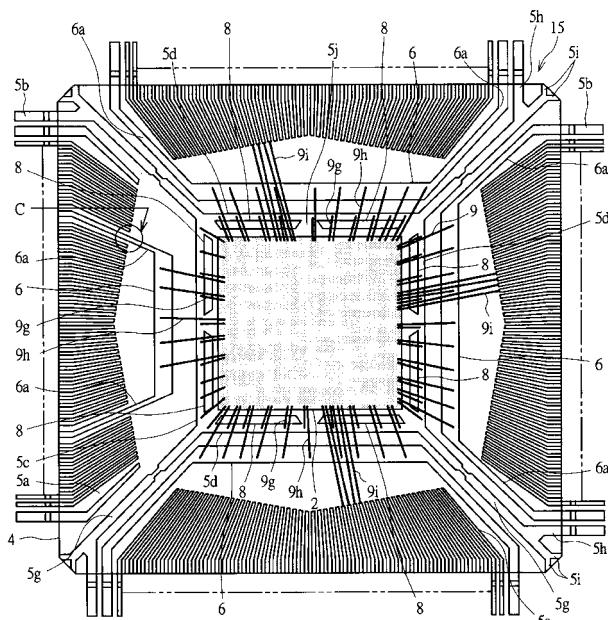

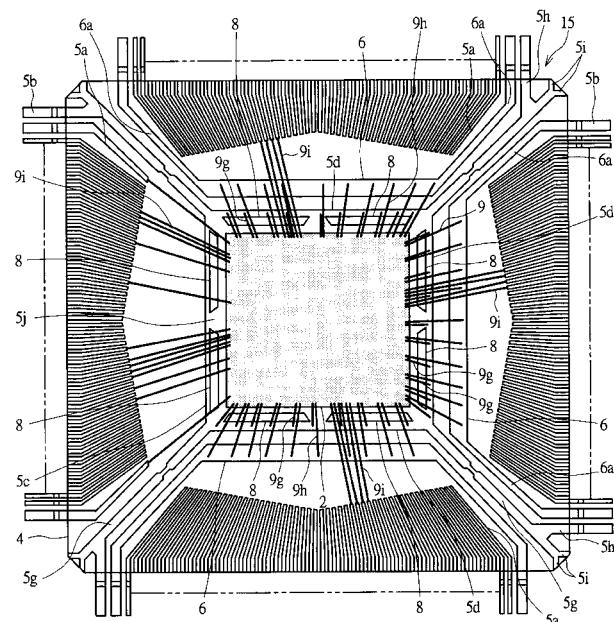

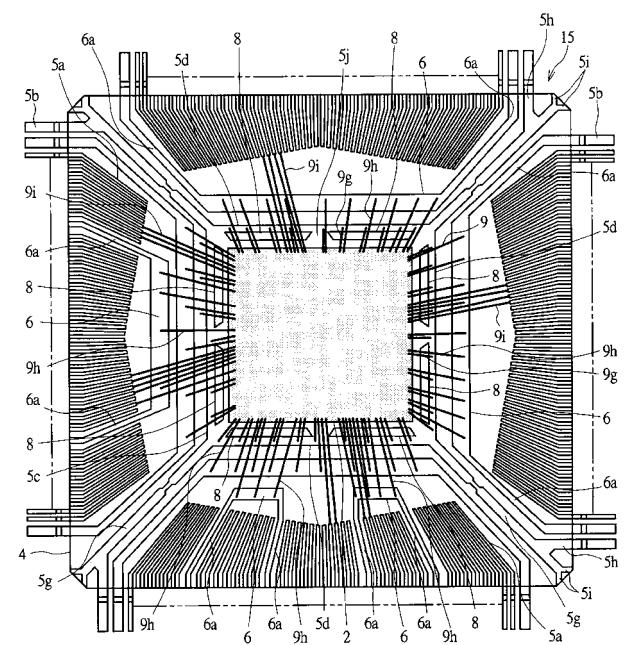

図20は本発明の実施の形態3の半導体装置の内部構造の一例を示す平面図、図21～図25はそれぞれ本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図、図26は図25に示す半導体装置におけるチップ部品の実装構造の一例を示す断面図、図27は図25に示す半導体装置におけるチップ部品を介したワイヤ接続状態の変形例を示す部分断面図である。

20

## 【0101】

図20に示す本実施の形態3の半導体装置は、第1半導体チップであるマイコンチップ2のみを有するQFP15である。なお、タブ5cの外周部には第1共通リードである第1バーリード5dが形成されており、第1バーリード5dの外側には第2共通リードである第2バーリード6が形成されている。第2バーリード6は、その両端が支持リード6aによって支持されている。マイコンチップ2は、タブ5c上に搭載されている。

## 【0102】

本実施の形態3のQFP15では、第1バーリード5dの外側に第2バーリード6を配置してバーリードを2重構造にすることにより、電源/GNDをコア用の第1電源/第1GNDと、信号用の第2電源/第2GNDとに分けて接続することができる。これにより、それぞれの電源/GNDに対してワイヤ接続を行う際に、各ワイヤを容易に接続することができる。

30

## 【0103】

また、バーリードを2重構造にすることにより、電源/GNDの端子を更に共通化することができ、QFP15の端子数の低減化を更に図ることができる。

## 【0104】

なお、QFP15では、マイコンチップ2のコア用の第1電源/第1GNDのパッド2cと第1バーリード5dとが第7ワイヤ9gで電気的に接続されており、一方、マイコンチップ2の信号用の第2電源/第2GNDのパッド2cと第2バーリード6とが第8ワイヤ9hで電気的に接続されており、さらに、マイコンチップ2の信号用のパッド2cとこれに対応するインナリード5aとが第9ワイヤ9iで電気的に接続されている。

40

## 【0105】

QFP15における他の構造とその構造によって得られる作用効果については、実施の形態1のQFP1と同様であるため、その重複説明は省略する。

## 【0106】

次に、図21に示す変形例のQFP15は、4辺の第1バーリード5dそれぞれの外側に設けられた4本の第2バーリード6のうちの1本が他の3本より短く、したがって、この短い第2バーリード6をその両端で支持する支持リード6aがインナリード列の端部で

50

はなく、インナリード列の内側（中央寄り）に配置されているものである。

【0107】

すなわち、電源端子は、必ずしも端部に配置されていなくてもよく、電源端子の位置に応じてより複数のワイヤ9を接続し易くすることも重要である。

【0108】

なお、支持リード6aがインナリード列の内側に配置されている場合においても、図21のC部に示すように、支持リード6aの両側に、隣接するインナリード5a間の隙間より幅広の隙間が形成されており、インナリード5aの先端切断時にプレス金型を配置して各インナリード5aの先端カットを容易に行うことができる。

【0109】

また、図22に示す変形例のQFP15は、4辺の第1バーリード5dのうち3辺の第1バーリード5dそれぞれの外側に第2バーリード6が設けられており、残りの1辺の第1バーリード5dの外側には第2バーリード6が設けられていない構造のものである。すなわち、第2バーリード6は、電源端子の配列や本数等に応じて設けられるものであり、第1バーリード5dの外側に必ずしも設けられていなくても良い。

10

【0110】

また、図23に示す変形例のQFP15は、4辺の第1バーリード5dそれぞれの外側に設けられた第2バーリード6の長さや本数が種々混在している構造のものである。すなわち、第2バーリード6は、その長さや、1辺あるいは4辺全体の本数においても電源端子の配列や本数等に応じて設けられるものであり、それぞれの第2バーリード6を支持する支持リード6aもインナリード列の端部に配置されていても、または内側に配置されていてもよい。

20

【0111】

さらに、図24に示す変形例のQFP15は、第2バーリード6に、その両端に連結された支持リード6aと、長手方向の側部6bに連結された他の支持リード6cとが設けられているものである。すなわち、第2バーリード6が、その両端の支持リード6aと、支持リード6aより内側に連結された1本または複数の他の支持リード6cとによって支持されており、さらに支持リード6a及び他の支持リード6cは、インナリード5aと一緒に並んで端子として配列されている。

30

【0112】

なお、第2バーリード6が支持リード6a及び他の支持リード6cによって支持されていることにより、第2バーリード6の補強を図ることができるとともに、低抵抗化を図ることができる。

【0113】

また、図25に示す変形例のQFP15は、4辺それぞれの第1バーリード5dと第2バーリード6の間にチップコンデンサ10等のチップ部品を搭載したものである。すなわち、4辺それぞれの第1バーリード5dと第2バーリード6の両バーリード上に橋渡すようにチップコンデンサ10を搭載したものであり、これにより、電源ノイズを除去してQFP15の回路性能をさらに向上させることができる。

40

【0114】

その際、図26に示すように、チップコンデンサ10の両端の外部端子10aを半田付けによってそれぞれのバーリードに電気的に接続してもよいし、あるいは、図27に示すように、バーリードに半田付けされた外部端子10aとマイコンチップ2、あるいはインナリード5aとをワイヤ9を介して電気的に接続してもよい。

【0115】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0116】

例えば、前記実施の形態1～3では、半導体装置の一例としてQFP1,14,15を

50

取り上げて説明したが、前記半導体装置は、Q F N (Quad Flat Non-leaded Package) 等であってもよい。

**【産業上の利用可能性】**

**【0 1 1 7】**

本発明は、バーリードを有する半導体装置に好適である。

**【図面の簡単な説明】**

**【0 1 1 8】**

【図1】本発明の実施の形態1の半導体装置の内部構造の一例を示す平面図である。

【図2】図1に示すA - A線に沿って切断した構造の一例を示す断面図である。

【図3】図1に示す半導体装置における第1スリットの作用効果の一例を示す概念図である。 10

【図4】本発明の実施の形態1の変形例の半導体装置の内部構造を示す平面図である。

【図5】本発明の実施の形態1の変形例の半導体装置の内部構造を示す平面図である。

【図6】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図7】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図8】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図9】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図10】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図11】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図12】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。 20

【図13】本発明の実施の形態1の変形例の半導体装置の構造を示す部分断面図である。

【図14】本発明の実施の形態2の半導体装置の内部構造の一例を示す平面図である。

【図15】図14に示すA - A線に沿って切断した構造の一例を示す断面図である。

【図16】本発明の実施の形態2の変形例の半導体装置の内部構造を示す平面図である。

【図17】図16に示すA - A線に沿って切断した構造の一例を示す断面図である。

【図18】本発明の実施の形態2の変形例の半導体装置の内部構造を示す平面図である。

【図19】本発明の実施の形態2の変形例の半導体装置の内部構造を示す平面図である。

【図20】本発明の実施の形態3の半導体装置の内部構造の一例を示す平面図である。

【図21】本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図である。

【図22】本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図である。 30

【図23】本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図である。

【図24】本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図である。

【図25】本発明の実施の形態3の変形例の半導体装置の内部構造を示す平面図である。

【図26】図25に示す半導体装置におけるチップ部品の実装構造の一例を示す断面図である。

【図27】図25に示す半導体装置におけるチップ部品を介したワイヤ接続状態の変形例を示す部分断面図である。

**【符号の説明】**

**【0 1 1 9】**

1 Q F P (半導体装置)

40

2 マイコンチップ (第1半導体チップ)

2 a 主面

2 b 裏面

2 c パッド (電極)

3 メモリチップ (第2半導体チップ)

3 a 主面

3 b 裏面

3 c パッド (電極)

4 封止体

4 a 表面

50

- 4 b 裏面

4 c 側面

5 a インナリード

5 b アウタリード

5 c タブ

5 d 第1バーリード(第1共通リード)

5 e 突出部

5 f 開口部

5 g 吊りリード(第1吊りリード)

5 h 端子部 10

5 i 分割部

5 j ブリッジ部

5 k 分離端子部

6 第2バーリード(第2共通リード)

6 a 支持リード(第2吊りリード)

6 b 側部

6 c 他の支持リード

7 第1スリット

8 第2スリット

9 ワイヤ 20

9 a 第1ワイヤ

9 b 第2ワイヤ

9 c 第3ワイヤ

9 d 第4ワイヤ

9 e 第5ワイヤ

9 f チップ間ワイヤ(第6ワイヤ)

9 g 第7ワイヤ

9 h 第8ワイヤ

9 i 第9ワイヤ

10 チップコンデンサ(チップ部品) 30

10 a 外部端子

11 抵抗

13 A g ペースト

14 , 15 Q F P (半導体装置)

【図1】

1:QFP(半導体装置)

2:マイコンチップ(第1半導体チップ)

3:メモリチップ(第2半導体チップ)

4:封止体

5a:インナーリード

5c:タブ

5d:第1バーリード(第1共通リード)

5e:突出部

5g:吊りリード(第1吊りリード)

6a:支持リード(第2吊りリード)

7:第1スリット

8:第2スリット

9a:第1ワイヤ

9b:第2ワイヤ

9c:第3ワイヤ

9d:第4ワイヤ

9e:第5ワイヤ

図1

【図2】

2a,3a:正面

2c,3c:パッド(電極)

4a:表面

4b:裏面

4c:側面

【図3】

図3

【図4】

図4

【図5】

10:チップコンデンサ(チップ部品)

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

【 図 1 5 】

☒ 14

14 : QFP(半導体装置)

図 15

【 図 1 6 】

【 図 17 】

☒ 16

☒ 17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

9g:第7ワイヤ

9i:第9ワイヤ

9h:第8ワイヤ

15:QFP(半導体装置)

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図25

6b:側部

6c:他の支持リード

【図26】

図26

【図27】

図27

---

フロントページの続き

(72)発明者 安 義彦

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F067 AA01 AA10 AB03 BA04 BB11 CB02 CD03 DE01 DF01