등록특허 10-2441106

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년09월07일

(11) 등록번호 10-2441106

(24) 등록일자 2022년09월02일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/20* (2006.01) *G02F 1/1362* (2006.01)

*H01L 27/32* (2006.01)

- (52) CPC특허분류

*G09G 3/20* (2013.01)

*G02F 1/136213* (2013.01)

- (21) 출원번호 10-2016-0056203

(22) 출원일자 2016년05월09일

심사청구일자 2021년05월07일

- (65) 공개번호 10-2016-0140377

(43) 공개일자 2016년12월07일

- (30) 우선권주장

14/725,472 2015년05월29일 미국(US)

- (56) 선행기술조사문헌

JP60193384 A\*

WO2012121372 A1\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

팔로 알토 리서치 센터 인코포레이티드

미국 캘리포니아주 94304 팔로 알토 코요테 힐 로드 3333

- (72) 발명자

루 쟁평

미합중국 94539 캘리포니아주 프리몬트 온디나 플레이스 40747

비겔슨 데이비드 케이.

미합중국 94028 캘리포니아주 포틀라 벨리 미모사 웨이 200

마에다 패트릭 앤스오

미합중국 95124 캘리포니아주 산 호세 찰메란 에비뉴 15075

- (74) 대리인

장훈

전체 청구항 수 : 총 11 항

심사관 : 신영교

(54) 발명의 명칭 박막 광결합기들을 이용하여 형성된 능동 매트릭스 백플레인

## (57) 요약

기기는 백플레인(backplane)의 출력 표면상에 어레이로 배열되는 다중 출력 단자들을 갖는 상기 백플레인을 포함한다. 상기 기기는 상기 백플레인의 입력 단자 및 상기 출력 단자들 사이에 각각 결합되는 박막 고체 상태(solid state) 광 스위치들을 포함하는 능동 매트릭스 어레이를 더 포함한다. 스토리지 커페시터들이 상기 출력 단자들과 각각 결합될 수 있다. 광셀화된 광원이 상기 광 스위치들을 제어하는 광셀화된 광을 제공한다.

## 대표도 - 도2

(52) CPC특허분류

**H01L 27/3244** (2013.01)

G09G 2300/0842 (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

기기(device)에 있어서,

백플레인(backplane)으로서,

상기 백플레인의 출력 표면 상에 배치되는 복수의 출력 단자와,

광결합기 능동 매트릭스 어레이로서,

상기 백플레인의 복수의 입력 단자 중 어느 하나와 복수의 상기 출력 단자 중 어느 하나의 사이에 각각 결합되는 박막 고체 상태(solid state) 광 스위치로서, 복수의 상기 입력 단자는, 열 방향을 따라 각각 연장되고, 또한, 행 방향으로 배열된 복수의 입력선 중 어느 하나 또는 하나의 입력선에 서로 전기적으로 연결된 상태로 연결되어 있고, 상기 광 스위치 및 상기 출력 단자는 어레이형으로 배치되고, 상기 광 스위치는 광의 존재 또는 부재에 의해 개별적으로 온 또는 오프되는, 상기 고체 상태 광 스위치, 및

각각 상기 출력 단자에 결합되는 스토리지 커패시터를 구비하는, 상기 광결합기 능동 매트릭스 어레이를 구비하는, 상기 백플레인과,

상기 광 스위치를 제어하는 광셀화된 광을 제공하도록 구성되는 광원을 구비하는, 기기.

#### 청구항 2

제 1 항에 있어서,

상기 광셀화된 광원은,

광 빔을 제공하도록 구성되는 적어도 하나의 광 생성 기기와,

적어도 하나의 미러와,

적어도 2개의 차원(dimension)을 따라 상기 미러의 운동을 가능하게 하도록 구성되는 운동 메커니즘을 구비하는, 기기.

#### 청구항 3

제 1 항에 있어서,

상기 광셀화된 광원은 복수의 광 생성 기기를 포함하고, 상기 복수의 광 생성 기기의 각각은 상기 광 스위치 중 적어도 하나를 제어하도록 배치되는, 기기.

#### 청구항 4

제 1 항에 있어서,

상기 광셀화된 광원은,

적어도 하나의 광 생성 기기와,

복수의 회전 가능한 소형 미러(micro mirror)를 구비하는 소형 미러 어레이를 구비하는, 기기.

#### 청구항 5

제 1 항에 있어서,

상기 광셀화된 광원은 평판(flat panel) 디스플레이를 포함하고,

상기 평판 디스플레이의 각 광셀은 상기 능동 매트릭스 어레이의 광셀에 대응하는, 기기.

**청구항 6**

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 광 스위치는 픽셀 그룹 내에 배치되고, 각각의 픽셀 그룹은 적어도 제 1 입력에 결합된 제 1 광 스위치 및 제 2 입력에 결합된 제 2 광 스위치로서, 상기 제 1 광 스위치 및 상기 제 2 광 스위치는 공통 출력 단자에 연결되는, 기기.

**청구항 7**

제 6 항에 있어서,

상기 픽셀화된 광원과 상기 제 1 광 스위치의 사이에 배치되는, 제 1 통과 대역 컬러를 가지는 제 1 광 필터와, 상기 픽셀화된 광원과 상기 제 2 광 스위치의 사이에 배치되는, 제 2 통과 대역 컬러를 가지는 제 2 광 필터를 더 포함하는, 기기.

**청구항 8**

제 7 항에 있어서,

상기 픽셀화된 광원은 상기 제 1 통과 대역 컬러를 방출함으로써 상기 제 1 광 스위치를 활성화하고 상기 제 2 통과 대역 컬러를 방출함으로써 상기 제 2 광 스위치를 활성화하도록 구성되는, 기기.

**청구항 9**

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

전압원을 더 구비하고,

상기 전압원은 상기 입력 단자에 결합되고, 또한 상기 입력 단자에서 시간적으로 변화하는 입력 전압을 제공하도록 구성되고,

상기 능동 매트릭스 어레이에는 상기 시간적으로 변화하는 입력 전압에 기초하여 상기 출력에 복수의 전압 레벨을 제공하도록 구성되는, 기기.

**청구항 10**

제 9 항에 있어서,

상기 광 스위치는,

측면으로 확장되는 감광성 물질의 층과,

상기 감광성 물질의 층을 따라 상호간에 측면에서 이격되어 있는 제 1 전극 및 제 2 전극으로서, 상기 제 1 전극 및 제 2 전극은 각각 제 1 접합부 및 제 2 접합부에서 상기 감광성 물질과 접촉하는, 상기 제 1 전극 및 제 2 전극과,

적어도 하나의 절연체 영역에 의해 상기 감광성 물질로부터 분리되고, 상기 감광성 물질의 층을 따라 측면에서, 상기 제 1 접합부 또는 상기 제 2 접합부를 넘어서 확장되는 적어도 하나의 필드 판으로서, 상기 적어도 하나의 필드 판은 상기 제 1 전극 또는 상기 제 2 전극에 전기적으로 연결되는, 상기 적어도 하나의 필드 판을 구비하는, 기기.

**청구항 11**

제 10 항에 있어서,

상기 광 스위치는 픽셀 그룹 내에 배치되고, 각 픽셀 그룹은 디지털 입력 신호를 아날로그 출력 신호로 변환하도록 배치되는, 기기.

**청구항 12**

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명은 일반적으로 능동 매트릭스 어레이들 및 이러한 어레이들과 관련된 기기들 및 방법들에 관한 것이다.

### 배경 기술

[0002] 능동 매트릭스 어레이들은 다수의 전자 소자들을 액세스하기 위한 방법을 제공한다. 이러한 어레이들은 액정 디스플레이(LCD) 또는 유기발광 다이오드(OLED) 디스플레이와 같은 고밀도 발광 소자들을 어드레싱하는 것으로 전형적으로 사용되어왔다. 상기 LCD 또는 OLED 디스플레이 소자들을 액세스하는데 사용되는 상기 능동 매트릭스 어레이 백플레이인들은 평판 디스플레이들을 용이하게 하기 위해 얇게 만들어져 왔다. 능동 매트릭스 어드레싱은 고전압들에 의해 액추에이트되는 전자 소자들을 제어하는데 또한 유용할 수 있다. 고전압 응용들은 제어 및 출력 회로들 사이에 일부 유형의 전기적 격리도의 이용과 종종 관련된다. 고전압 응용들에 유용한 고밀도 능동 매트릭스 어레이들에 대한 필요가 있다.

### 발명의 내용

[0003] 일부 실시예들은 상기 백플레이인의 출력 표면 상에 어레이로 배열되는 다중 출력 단자들을 갖는 백플레이인을 포함하는 기기와 관련된다. 상기 기기는 상기 백플레이인의 입력 단자 및 상기 출력 단자들 사이에 각각 결합되는 박막 고체 상태 스위치들을 포함하는 액티브 매트릭스 행렬을 포함한다. 스토리지 커퍼시터들은 상기 출력 단자들에 각각 결합될 수 있다. 픽셀화된 광원은 상기 광 스위치들을 제어하는 픽셀화된 광을 제공한다.

[0004] 일부 실시예들은 백플레이인에 관한 것으로, 상기 백플레이인의 출력 표면 상에 배열되는 다중 출력 단자들 및 상기 백플레이인의 적어도 하나의 입력 단자 및 어레이로 배열되는 상기 출력 단자들 사이에 각각 결합되는 박막 고체 광 스위치들을 포함하는 능동 매트릭스 어레이를 포함한다. 각각의 광 스위치는 측면으로 확장되는 감광성 물질 층; 상기 감광성 물질 층을 따라 상호 간에 측면에서 이격되어 배치되는 제1 및 제2 전극들을 포함하고, 상기 제1 및 제2 전극들은 제1 및 제2 접합부에서 상기 감광성 물질과 접촉하고; 적어도 하나의 필드 판은 상기 감광성 물질로부터 전기적으로 절연되고 상기 감광성 물질 층을 따라 측면에서 그리고 상기 제1 및 제2 접합부를 넘어서 확장되고, 상기 적어도 하나의 필드 판은 상기 제1 전극 또는 상기 제2 전극에 전기적으로 연결된다.

[0005] 다양한 실시예들의 상기 및 다른 특징들 및 양상은 다음의 상세한 논의 및 이에 수반되는 도면들의 관점에서 이해될 수 있다.

### 도면의 간단한 설명

[0006] 아래의 논의는 다음의 도면들에 참조를 생성하고, 복수의 도면들에서 동일한 참조 부호는 유사한/동일한 컴포넌

트를 식별하는데 사용될 수 있다.

도 1은 본 발명에서 논의되는 실시예들에 따른 광결합기 능동 매트릭스(옵토캠: optocam) 백플레인을 이용하는 시스템의 블록도이다.

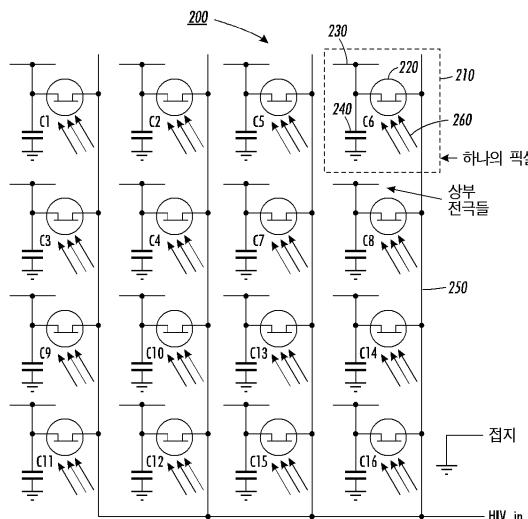

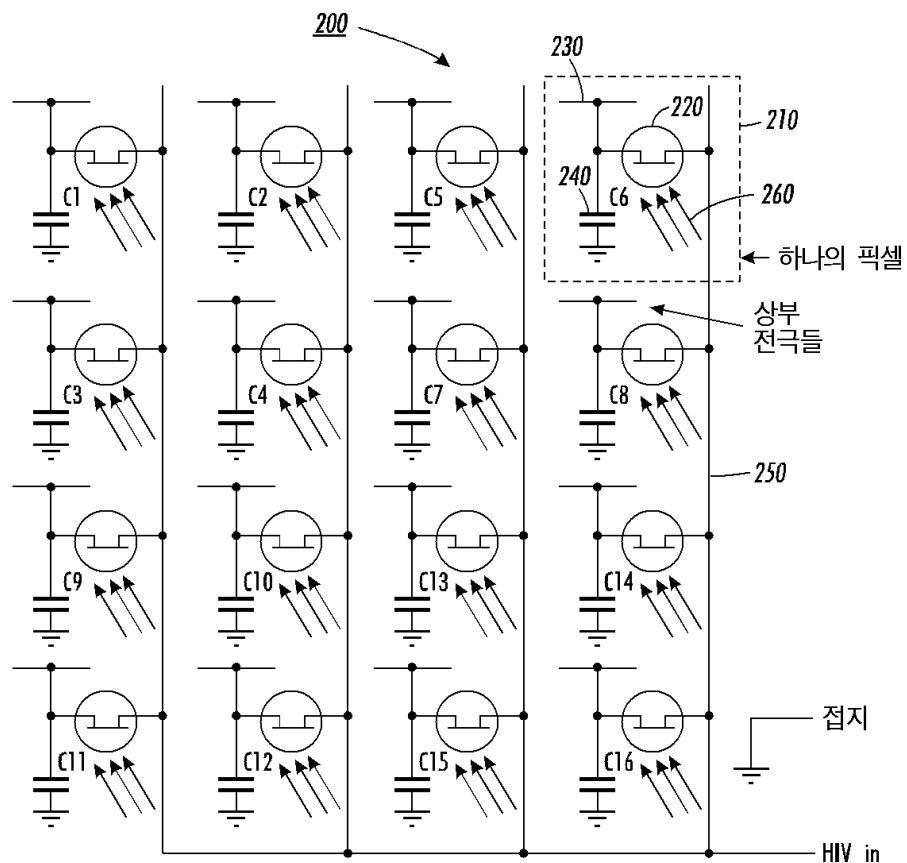

도 2는 일부 실시예들에 따른 옵토캠 백플레인의 회로도이다.

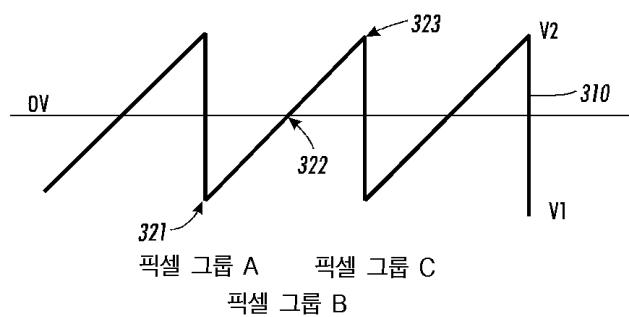

도 3은 상기 옵토캠 백플레인에 대한 예시의 입력 파형을 도시한다.

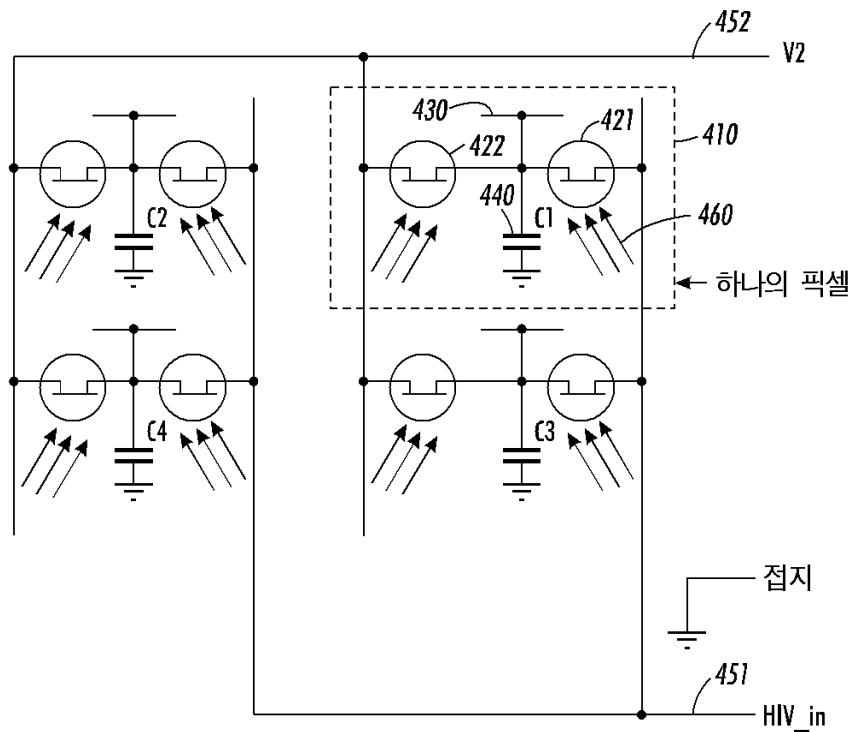

도 4는 일부 실시예들에 따른 입력 라인들의 두 세트들 및 픽셀 당 두 개의 광 스위치들을 이용하는 옵토캠 백플레인의 회로도이다.

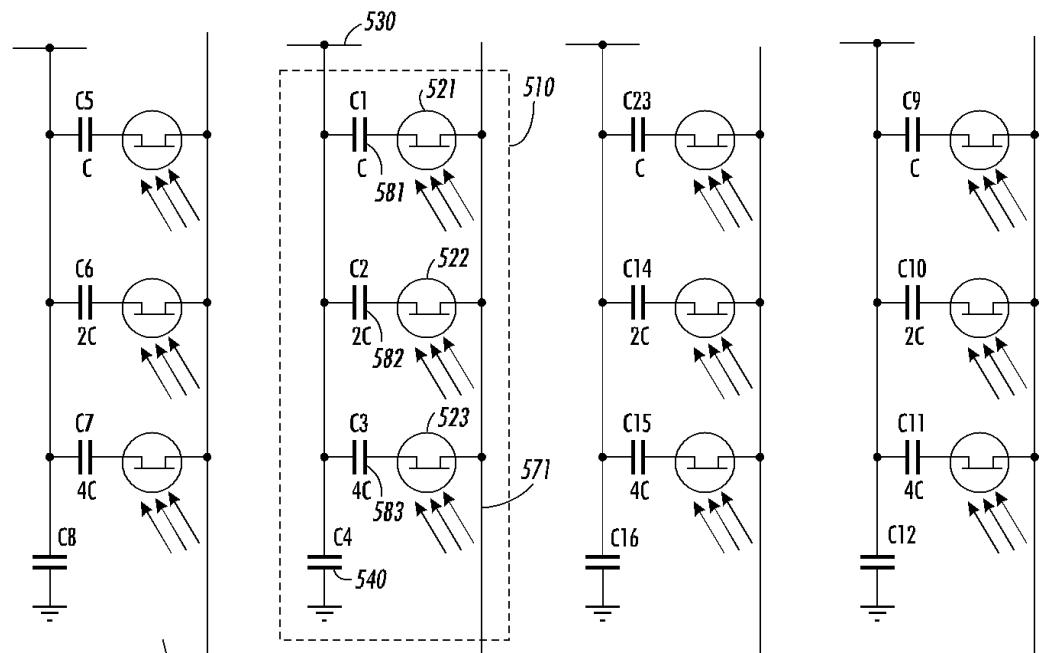

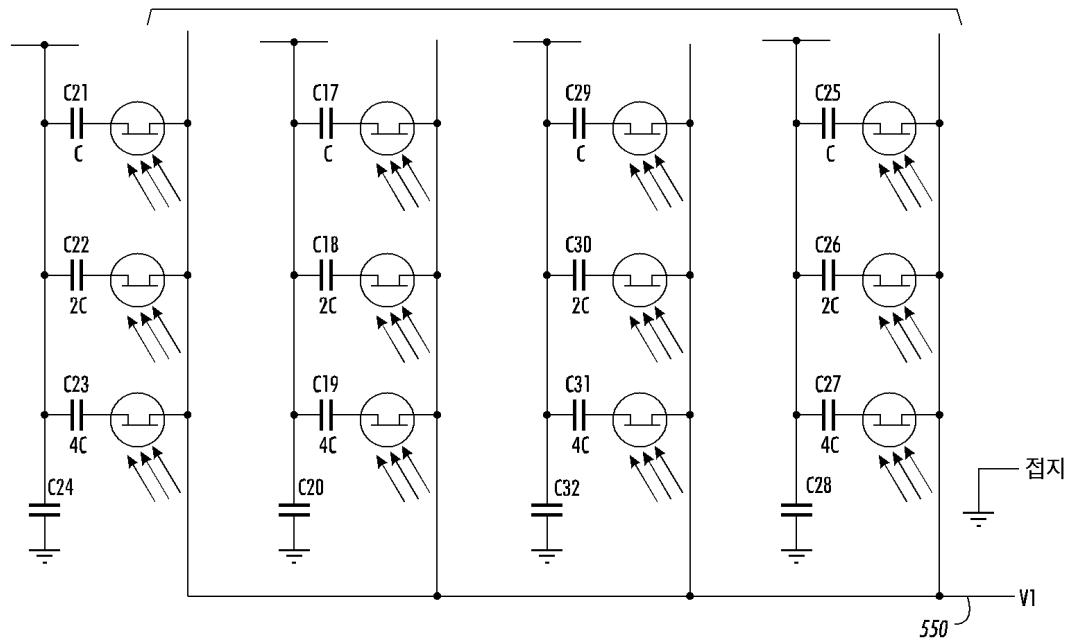

도 5A1 및 5A2는 일부 실시예들에 따른 각 픽셀에서 디지털 대 아날로그 변환기를 포함하는 옵토캠 백플레인의 회로도이다.

도 5B는 도 5A의 상기 옵토캠 백플레인에 대한 디지털 입력 파형을 도시한다.

도 6은 일부 실시예들에 따른 다중 색 필터들을 포함하는 옵토캠 백플레인의 회로도이다.

도 7은 일부 실시예들에 따른 광 제어 소스로서 평판 디스플레이를 이용하는 옵토캠 백플레인의 측면 뷰이다.

도 8은 일부 실시예들에 따른 상기 옵토캠 백플레인 및 상기 평판 디스플레이 사이에 배치되는 광 소자들을 포함하고 상기 광 제어 소스로서 평판 디스플레이를 이용하는 옵토캠 백플레인의 측면 뷰이다.

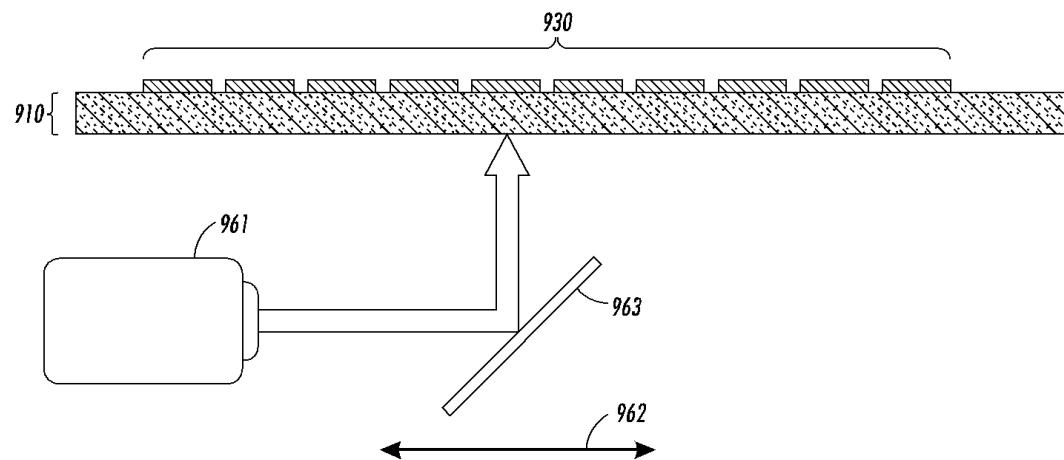

도 9은 일부 실시예들에 따른 상기 제어 광원으로서 이용되는 옵토캠 플레인 및 프로젝터를 도시한다.

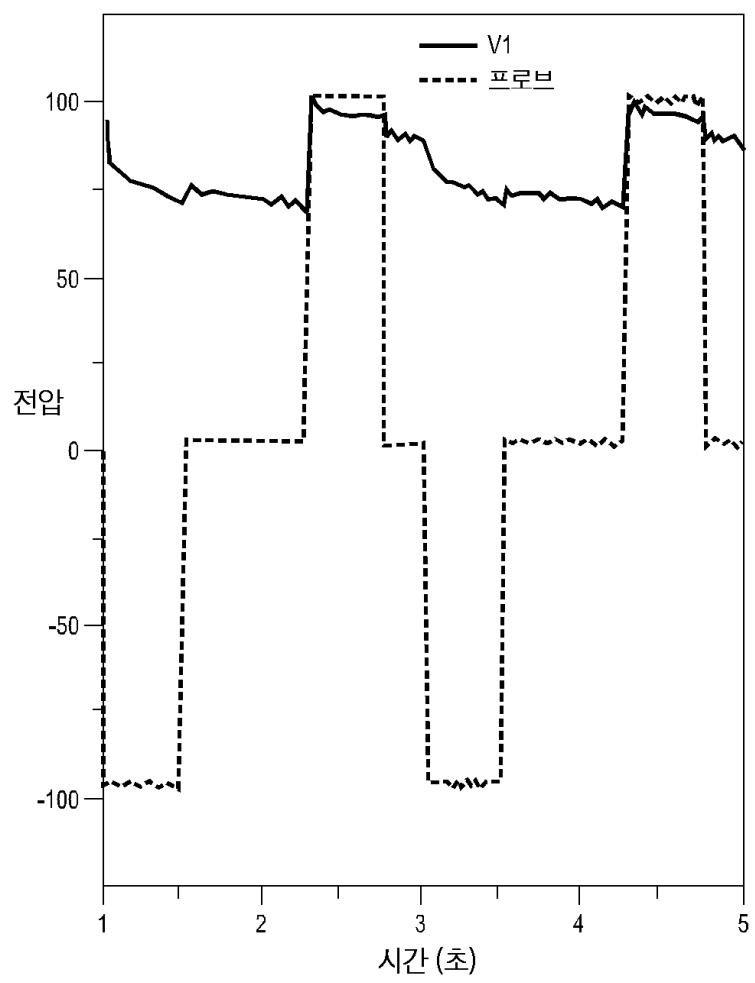

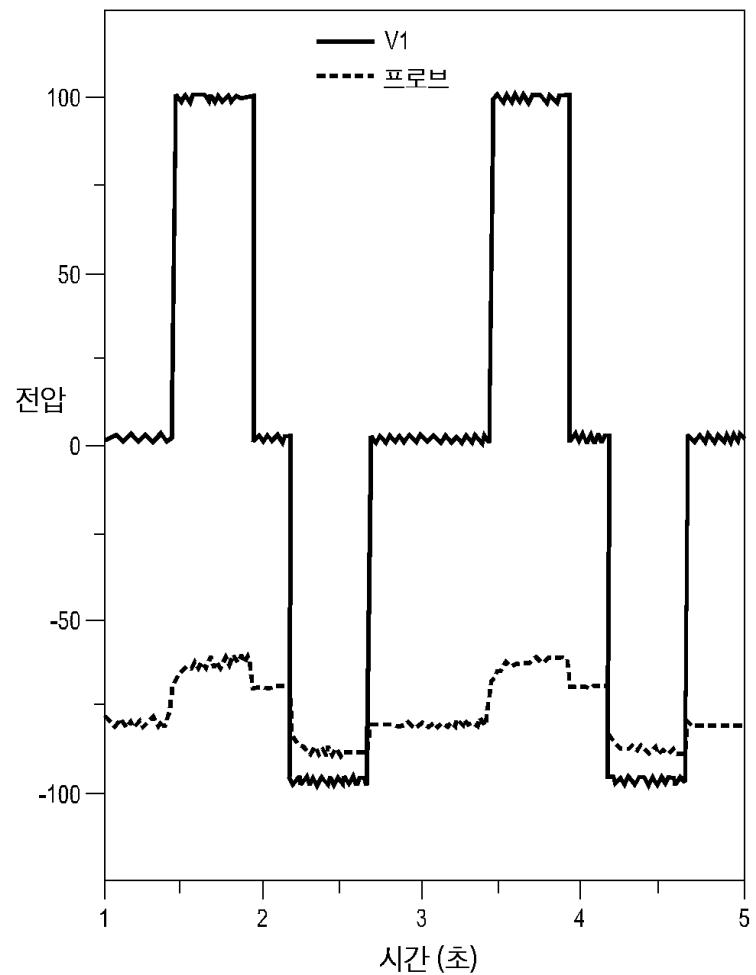

도 10 및 11은 일부 실시예들에 따른 옵토캠 백플레인의 측정된 파형들이다.

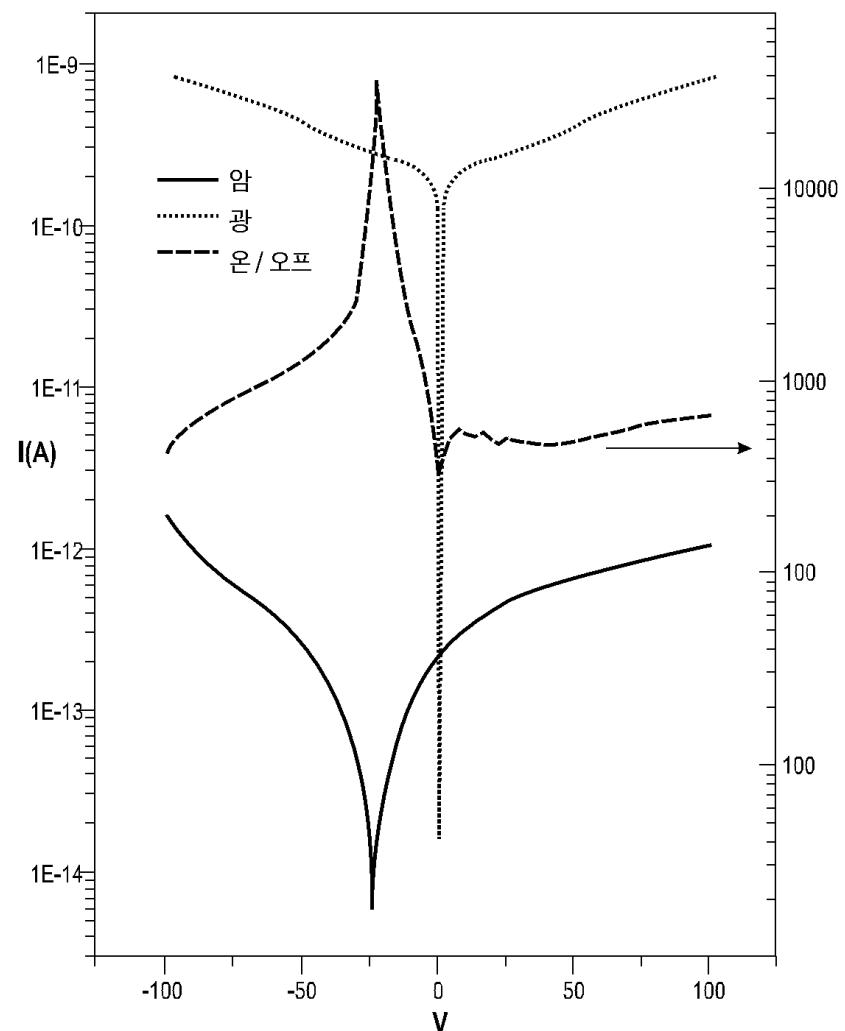

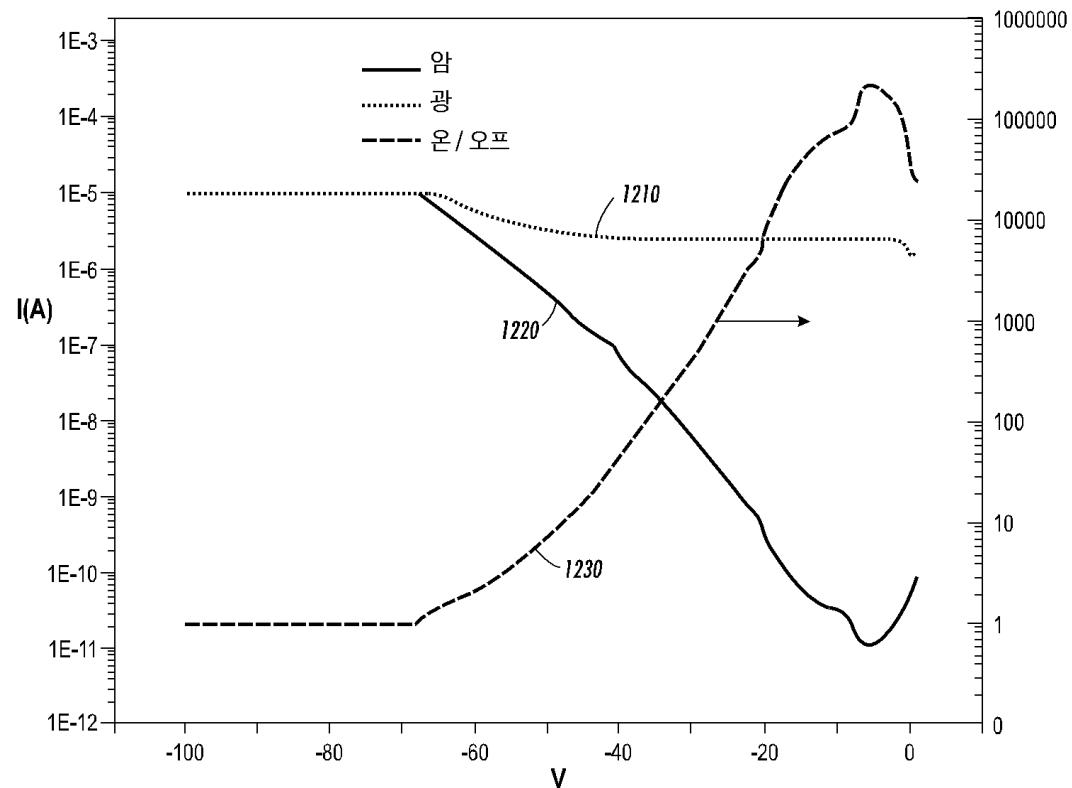

도 12는 표준 PIN 포토센서에 대한 암원 및 광원의 그래프들을 도시한다.

도 13A 및 13B는 일부 실시예들에 따른 박막 광 스위치의 단면 및 상부 뷰를 도시한다.

도 14는 일부 실시예들에 따른 두개의 필드 플레이트들을 포함하는 박막 광 스위치의 상부 뷰이다.

도 15는 도 13A 및 13B에서 도시되는 상기 광 스위치에 대한 암 및 광 IV 특성들을 제공한다.

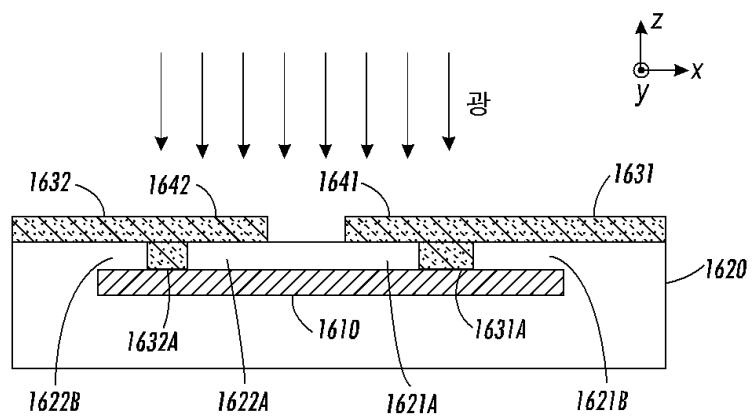

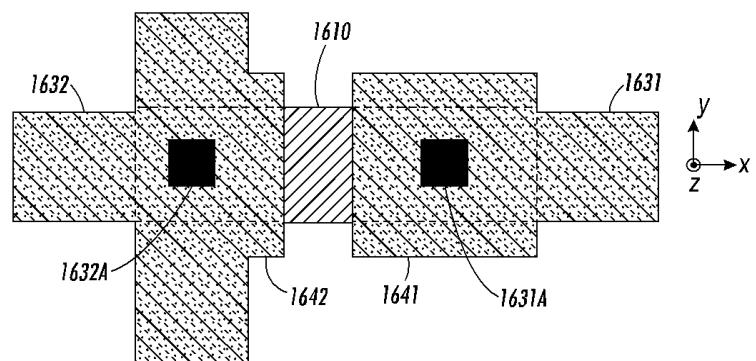

도 16A 및 16B는 일부 실시예들에 따른 p+/i/p+ 구조를 갖는 광 스위치의 단면 및 상부 뷰들을 도시한다.

도 17은 도 16A 및 16B에서 도시된 상기 광 스위치에 대한 암 및 광 IV 특성들을 도시한다.

본 도면들은 반드시 스케일된 것은 아니다. 본 도면에서 사용되는 동일한 부호들은 동일한 컴포넌트들을 지칭한다. 그러나, 주어진 도면에서 컴포넌트를 지칭하기 위한 부호의 사용은 동일한 부호로 레이블링된 다른 도면에서의 상기 컴포넌트를 한정하는 것으로 의도되는 것은 아니다.

### 발명을 실시하기 위한 구체적인 내용

**[0007]** 본 발명에서 기술되는 실시예들은 광결합된, 고전압 출력들을 제공하는 고밀도 백플레인을 지시한다. 광결합은 저전압 제어 시스템으로부터의 고전압 노드들을 격리시키기 위하여 제공된다. 대면적 광결합 백플레인들은 멤브레인 디스플레이들 및 광 미러 어레이들과 같은 소형전자기계(MEMS) 기기들을 포함하는 광범위한 응용들에 대하여 기회들을 제시하고 고전압 출력들의 어레이들을 제공할 수 있다. 논의되는 일부 실시예들은 예컨대, 약 100  $\mu\text{m}$ 보다 작은 어레이 피치를 갖는, 500 x 500, 1000 x 1000 또는 이상의 다수의 픽셀들을 포함할 수 있는, 광결합 능동 매트릭스 (옵토캠: optocam) 백플레인들로 지향된다. 다양한 실시예들에서, 상기 옵토캠 백플레인의 상기 광 스위치들은 평판 디스플레이 또는 프로젝터에 의해 생성되는 픽셀화된 광에 의해 제어될 수 있다. 본 발명에서 논의되는 일부 실시예들은 상기 옵토캠에 대하여 상기 광커플링을 제공하기 위하여 사용될 수 있는 새로운 박막 광 스위치들과 관련된다.

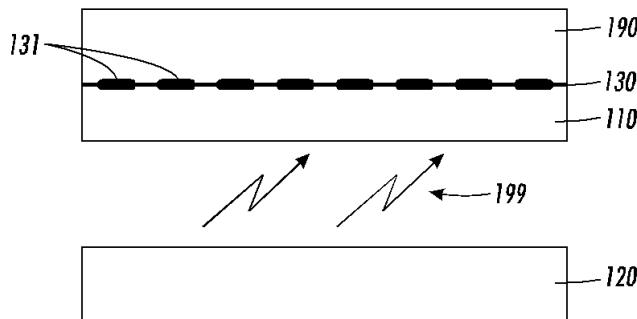

**[0008]** 도 1은 본 발명에서 논의되는 다양한 실시예들에 따른 옵토캠 백플레인(110)을 통합하는 예시의 시스템의 단면도이다. 상기 옵토캠 백플레인(110)은 예컨대, 출력 단자들(131)의, 다-차원 어레이, 2차원 또는 xy 어레이와 같은 어레이를 포함하는 출력 표면(130)을 갖는다. 상기 출력 단자들(131)은 예컨대, MEMs 어레이 등과 같은 기기(190)를 구동하도록 결합될 수 있다.

**[0009]** 도 1에 도시되지 않지만, 상기 백플레인(110) 내에, 예컨대, 고전압 입력과 같은 입력 전압을 상기 출력 단자들(131)에 결합하는 박막 광 스위치들이 있다. 고전압 출력들을 제공할 수 있고 상기 옵토캠 백플레인에 적합한

박막 스위치들의 구조가 아래에서 보다 상세하게 논의된다. 상기 백플레인(110)의 상기 광 스위치들은 상기 백플레인(110)의 상기 광 스위치들을 활성화시키기 위하여 광셀화된 광(199)를 생성하는 광원(120)에 의해 제어된다.

[0010] 도 2는 2차원 어레이로 배열되는 다수의 광셀들(210)을 도시하는 옵토캠 백플레인(200)의 개요도이다. 각 광셀(210)은 예컨대, 광(260)의 존재 또는 부재에 의해 턴 온되거나 턴 오프될 수 있는 광 스위치들(220)과 같은 광 스위치를 포함한다. 광 스위치(220)가 턴 온되는 경우, 고전압 입력과 같은 입력(250)이 낮은 임피던스를 통해 상기 광셀 출력 단자(230)에 결합되고, 상기 광 스위치(220)가 턴 오프되는 경우, 상기 입력(250) 및 출력 단자(230) 사이의 높은 임피던스에 의해 상기 광셀 출력 단자(230)로부터 결합해제된다. 각각의 광셀은 상기 광셀 출력 단자(230)과 결합되는 출력 스토리지 커뮤니케이터(240)를 포함할 수 있다. 광셀들(240)의 각 열이 개별적으로 어드레싱되는 것 대신에, 능동 매트릭스 스위치되는 LCD 디스플레이 백플레인들을 행 스캔하기위하여 전형적인 것처럼, 상기 광셀들(210)의 일부 또는 전부 중 상기 입력("데이터") 라인들(250)이 연결되어, 단순화된 2 포트 전기 인터페이스를 제공한다. 개별적인 광셀 어드레싱은 상기 광 스위치들(220)로 광 결합되는 (도 2에 도시되지 않은) 광원에 의해 생성되는 상기 광셀화된 광의 개별적인 광셀들의 온/오프 제어에 의해 달성된다.

[0011] 일부 실시예들에서, 백플레인(200)의 상기 각 광셀(120)은 상기 출력 단자(230)에 다중 전압 레벨들을 제공하는 능력을 갖는다. 상기 제어 광 소스는 상기 출력 단자 어레이의 상기 출력 단자들(230) 상에 다중-레벨 고전압 출력들을 달성하기 위하여 다중 그레이 레벨들을 생성할 필요가 있는 것은 아니다. 도 3은 광셀들의 그룹들 A, B, C에 대하여 턴 온 타이밍(321, 322, 323)을 제공하는 과정의 부분들 및 전압을 구동하는 상기 입력(250)의 예시적인 과정(310)을 도시한다. 이러한 특정 예시에서, V1은 광셀 그룹 A의 상기 스토리지 커뮤니케이터 내에 저장될 것이고, 0은 광셀 그룹 B에 대한 상기 스토리지 커뮤니케이터 내에 저장될 것이고 그리고 V2는 광셀 그룹 C에 대한 상기 스토리지 커뮤니케이터 내에 저장될 것이다. V1 및 V2는 본 출원에 의해 요구되는 바와 같이 동일한 극성을 가지거나 또는 도시된 바와 같이 반대 극성을 가질 수 있다. 임의의 수의 출력 전압 레벨들이 감소된 리프레쉬 레이트를 대가로 가능하게 되는 더 많은 그레이 레벨들을 갖는, 이러한 처리에 의해 제공될 수 있다.

[0012] 도 4는 다중-레벨 출력 전압들을 제공하는 옵토캠 백플레인의 도식도를 도시한다. 도 4의 상기 옵토캠 백플레인은 다중 전압 레벨들을 달성하기 위하여 하나의 광셀(410) 내에 복수의 입력 라인들(451, 452) 및 복수의 광 스위치들(421, 422)을 포함한다. 각각의 광셀(410)은 상기 광 스위치들(421, 422) 및 상기 출력 단자(430)에 결합되는 스토리지 커뮤니케이터(440)를 포함할 수 있다. 상기 광 스위치들(421, 422)들을 제어하는 광을 펄스 폭 변조 방식으로 변조함으로써, 상기 상부 출력 단자(430)에서의 출력 전압은 V1 및 V2 사이의 임의의 레벨로 튜닝될 수 있다.

[0013] 대안적으로, OLED 또는 LCD 디스플레이들과 같은, 일부 2차원(2D) 광원들이 각각의 개별 광셀에 대하여 그레이 레벨 광 출력들을 생성할 수 있다. 이러한 타입의 광원들을 통합하는 실시예에서, V1 및 V2 사이의 임의의 전압이 광 스위치들(421 및 422)를 제어하는 광원의 상대적인 광 레벨에 의해 생성될 수 있다.

[0014] 일부 구현들에 따르면, V1 및 V2는 DC 이거나 또는 (상기 광원-온 사이클들 중 하나 동안에 변화 없는) 준-DC가 될 필요는 없다. 대신에, V1 및 V2 중 하나 또는 모두는 고 주파수 전압 생성기에 의해 유도될 수 있다. 일 예에서, V1은 1 MHz 정현파 함수 생성기에 연결될 수 있고 V2는 접지에 연결될 수 있다. 상기 광원 광셀을 갖는 광셀 그룹들

[0015] 턴 온된 출력 스위치(421)를 에너지를 제공(energize)하는 상기 광원 광셀을 갖는 광셀 그룹들은 상기 상부 전극을 통해 1 MHz 전압을 출력할 것일 반면에, 광 스위치(422)를 에너지를 제공하는 턴 온된 상기 광원 광셀을 갖는 광셀 그룹들은 OV를 출력할 것이다.

[0016] 이러한 구성은 고 주파수 구동을 요구하는 어플리케이션들 또는 기기들을 인에이블시킬 수 있다. 예를 들어, 상기 옵토캠 백플레인의 임의의 소형-입자 엑츄에이터를 위하여 이용되는 경우, 이러한 접근은 전기 이동(dielectrophoretic) 시동(actuation)을 가능하게 한다. 도 2에 도시되는 상기 단순한 옵토캠 백플레인은 상기 상부 전극에 고 주파수 전위들을 또한 선택적으로 출력시킬 수 있다. 그러나, 선택적인 "접지" 전극을 제공하지 않지만, 오히려, 조향되어 어드레스되지 않은 임의의 백플레인 광셀들은 상기 스토리지 커뮤니케이터를 통해 접지와 연결될 것이다.

[0017] 도 5A (5A1 및 5A2) 및 5B는 상기 광원의 개별 광원 광셀들의 온/오프 제어만을 이용하여 다중-레벨 고 주파수 출력들을 생성하는 또 다른 실시예를 도시한다. 상기 옵토캠 백플레인의 각각의 광셀(510)은 광 디지털 입력을 갖는 소형 디지털 대 아날로그 변환기(DAC)를 포함한다. 예를 들어, 도 5A는 3 비트 디지털 입력을 갖는 백플레

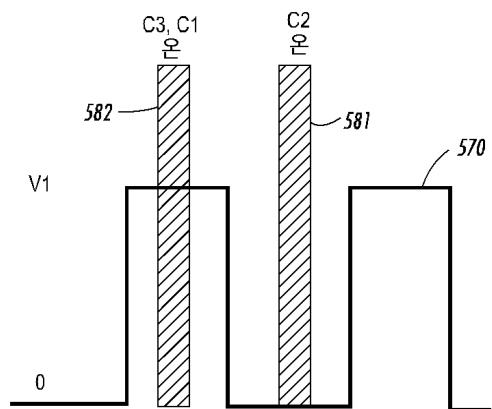

인 픽셀 구성을 도시하고, 각각은 광 스위치(521, 522, 523)에 의해 제어되고 가중치된 커패시터(581, 582, 583)에 연결된다. 스토리지 커패시터(540)는 상기 백플레인 픽셀 출력 단자(530) 및 상기 가중치된 커패시터들(581, 582, 583)의 각각에 전기적으로 연결된다. 광 스위치들(521, 522, 523)은 입력 전압 파형과 부합되는 패턴으로 턴 온된다. 도 5B는 상기 입력 파형(570)이 도 5A의 입력 단자(571)에 인가됨을 도시한다. 도 5A 및 5B에 도시되는 상기 예에서, 상기 입력 파형(570)이 V1 이고 상기 입력 전압 파형이 0인 경우 시간 구간(581) 동안에 상기 출력 스위치(522)가 턴 온되는 경우 광 스위치들(523 및 521)은 시간 구간(582) 동안에 턴 온된다. 도 5B에 도시된 상기 타이밍 패턴(581, 582) 및 상기 입력 파형(570)을 이용하여, 상기 픽셀(510)의 상기 출력 단자(530)에서 전압은  $(5/7) * V1$ 이다. 상기 독자는 사용되는 상기 타이밍 패턴 및 상기 입력 전압 파형에 의존하여 다양한 다른 아날로그 전압 레벨들이 달성될 수 있다는 것이 이해될 것이다.

[0018]

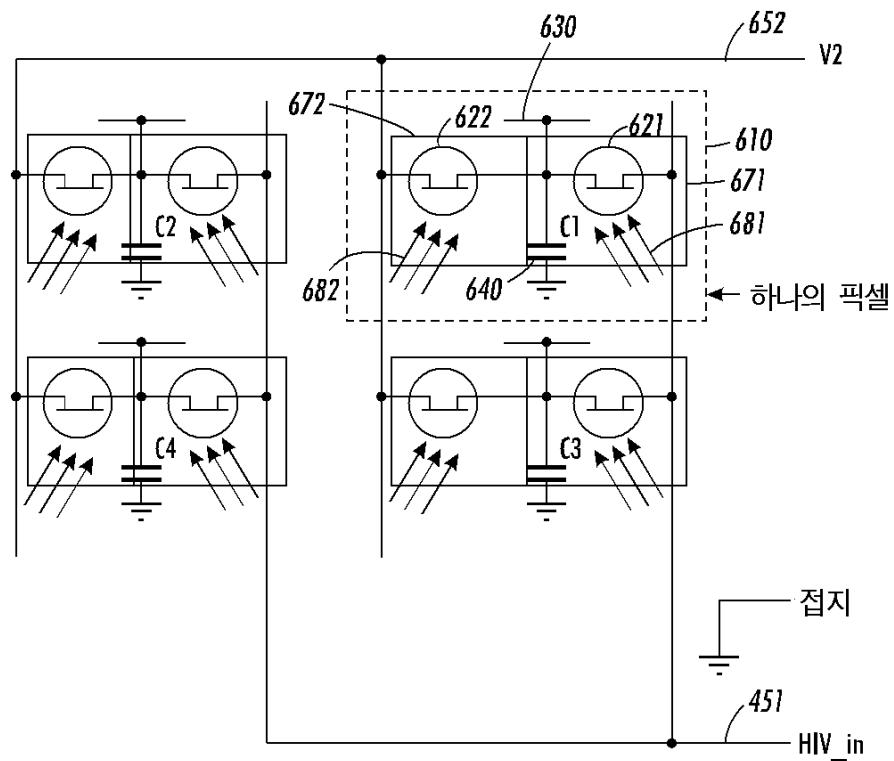

도 6은 상기 광원의 분해능 요구사항을 2배로 하여 이용될 수 있는 구성을 갖는 옵토캠 백플레인의 도식도이다. 이러한 실시예에서, 상기 광원은 컬러 디스플레이와 같은 2D 광원이다. 각 픽셀(610)은 두 개의 광 스위치들(621, 622)을 포함한다. 상기 광 스위치(621)에 에너지를 제공하는 상기 광 픽셀 및 광 스위치(621) 사이에 컬러 필터(671)가 배치된다. 상기 광 스위치(622)에 에너지를 제공하는 상기 광 픽셀 및 광 스위치(621) 사이에 컬러 필터(672)가 배치되고, 상기 컬러 필터(671)의 광 통과대역은 상기 컬러 필터(672)의 광 통과대역이 상이하다. 상기 컬러 필터(671)의 통과대역 내에 광장을 갖는 광(681)이 상기 백플레인 픽셀(610)로 향하는 경우 광 스위치(621)는 온 되고 광 스위치(622)는 오프된다. 반대로, 상기 컬러 필터(672)의 통과대역 내에 광장을 갖는 광(682)이 상기 백플레인 픽셀(610)로 향하는 경우 광 스위치(622)는 온 되고 광 스위치(621)는 오프된다. 따라서, 상기 픽셀(610)의 각각의 광 스위치(621, 622)를 개별 제어하기 위한 컬러 디스플레이를 이용하는 것이 가능하다. 상기 컬러 디스플레이에는 상기 컬러 필터(672)의 통과 대역에서 광을 실질적으로 방출하지 않고 상기 컬러 필터(671)의 통과대역에서 실질적으로 광량을 방출할 수 있고 상기 컬러 필터(671)의 통과대역 내에서 실질적으로 발광하지 않고 상기 컬러 필터(672)의 통과 대역에서 실질적인 광량을 방출할 수 있다. 상기 2D 광원으로서 컬러 디스플레이를 이용하여 도 2의 분해능 요구사항으로 복귀하는 도 4에 도시된 상기 옵토캠 백플레인을 제어하는데 요구되는 상기 2D 광원의 상기 분해능을 완화(relax)하는 것이 가능하다.

[0019]

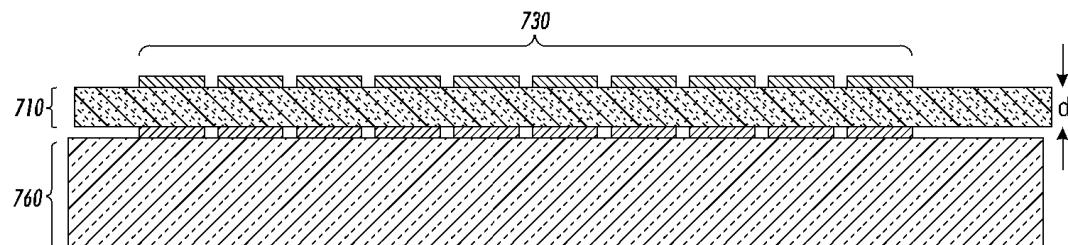

도 7은 상기 백플레인 2D 출력 단자 어레이(730)의 단면을 도시하는 옵토캠 백플레인(710)의 측면 뷰를 도시한다. 상기 옵토캠 백플레인(710)의 상기 광 스위치들은 예컨대, 평판 디스플레이(760)와 같은 2D 광원에 의해 제어된다. 도 7에서, 상기 백플레인(710)의 상기 픽셀 피치는 상기 2D 광원(760)의 픽셀 피치와 실질적으로 동일하고 상기 백플레인의 상기 기판 두께, d는 상기 광원 픽셀들로부터 광의 분산(dispersion)에 기인하는 크로스 토크가 크지 않도록 충분히 작다. 이러한 시나리오에서, 상기 광원(760)은 광학 간 간섭 없이 상기 옵토캠 백플레인(710)으로 직접 결합될 수 있다.

[0020]

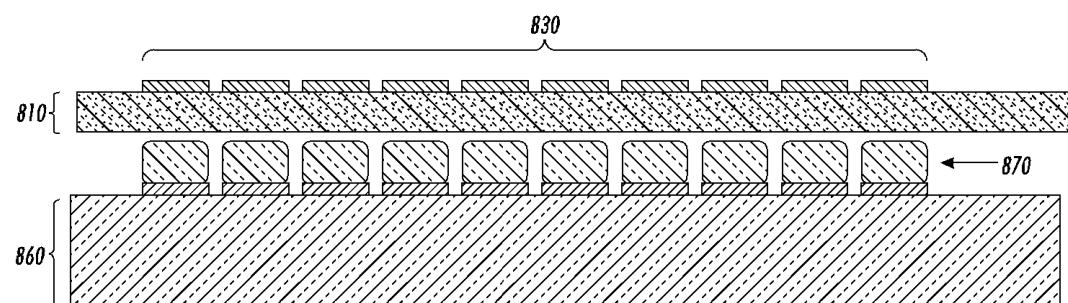

도 7은 예컨대, 유기 발광 다이오드(OLED) 디스플레이 또는 액정 디스플레이(LCD)와 같은 평판 디스플레이(760)가 옵토캠 백플레인(710)의 후면과 직접 광 결합된, 실시예를 도시한다. 상기 옵토캠 백플레인의 상기 기판 두께, d가 상기 백플레인 광 스위치 어레이의 상기 픽셀 피치보다 훨씬 작기만 하면, 이러한 접근은 충분할 수 있다. 현재의 디스플레이 산업에서 개발된 얇은 투과 기판들로의 현재 경향들을 이점을 취하면, 이러한 접근은 유용할 수 있다. 요구되는 어레이 피치가 상기 기판 두께보다 작다면, 도 8에 도시된, 적절한 릴레이 광학(870)이 이용될 수 있다. 예를 들어, 상기 릴레이 광학(870)은 상기 디스플레이(860)로부터의 광을 상기 옵토캠 백플레인(810)의 상기 광 스위치들 상에 집중(focus)시키도록 구성되는, 예컨대, 셀록(selfoc) 렌즈 어레이와 같은 소형 렌즈 어레이 및/또는 분산된 광을 차단하기 위한 펀홀 마스크를 포함할 수 있다.

[0021]

도 9는 상기 광 생성 기기, 경사진(tilted) 미러(963), 및 스캐닝 메커니즘(962)이 하나 이상의 축들을 따라 상기 경사진 미러를 전환(translate)하도록 구성되는 것으로 이용되는 프로젝터(961)를 포함하는 프로젝터 시스템을 이용하는 구성을 도시한다. 상기 프로젝터(961), 미러(963), 및 스캐닝 장치(962)는 상기 옵토캠 백플레인의 상기 출력 어레이(930)에서 원하는 패턴 출력을 제공하기 위하여 상기 옵토캠 백플레인(910)의 상기 광 스위치를 제어하기 위한 상기 픽셀화된 2D 광원을 제공할 수 있다. 도 7에서 도시된 상기 구조와 비교하여, 예를 들어, 프로젝터 시스템은 종종 더 부피가 큰 광학을 요구한다. 상기 프로젝터 시스템은 몇몇 유용한 특징을 제공한다. 예를 들어, 도 2와 같은 단일 광 스위치 픽셀을 갖는 옵토캠 백플레인이 이용된다면, 용이하게 스케일되고, 상기 기-설계된 어레이 피치와 독립적일 수 있는 가능한 맵 패턴들을 생성하기 위하여 상기 프로젝터의 광 줌이 이용될 수 있다. 상기 미러 및 상기 프로젝터는 대형 패턴 필드가 제공될 수 있도록 1D 또는 2D로 실시간으로 스캔되도록 또한 엔지니어링될 수 있다.

[0022]

도 9의 상기 프로젝터, 미터, 및 스캐닝 장치에 대안으로서, 많은 픽셀 크기의 회전 가능한 소형-미러들을 프로젝터에 의해 생성되는 광 빔을 향하는 또는 광 빔으로부터 벗어나는 상기 미러들을 경사지게 하는 스캐닝 메커-

니즘으로 통합하는, 디지털 광 프로젝터(DLP) 시스템을 이용하는 것이 가능하며, 상기 광 스위치들은 턴 온되거나 또는 턴 오프된다.

[0023] 도 10 및 11은 도 2에서 도시된 바와 같은 상기 픽셀 회로 및 연결 및 도 9에서 도시된 바와 같은 상기 2D 광원을 갖는 옵토캠 백플레인의 동작을 도시하는 그래프이다. 상기 측정들은 오실로스코프(TDS2014B) 및 고 임피던스 전압 프로브(Trek 800 고 임피던스 전압계)를 이용하여 수행된다. 도 10은 V1의 양의 상승 에지를 이용하여 동기되는, 0.1초에서 턴 온되는 광 면(light square) 상부를 호버링하는 프로브에 의해 검출된 신호를 도시한다. 도 11은 유사한 측정을 도시하지만, 상기 프로브가 음의 V1 사이클의 하강 에지를 이용하여 동기되는, 0.1초에서 턴 온되는 광 면 상부를 호버링한다. 도 10 및 11은 모두 상기 광학 광원이 턴 오프되는 경우 상기 픽셀들이 상기 지정된 전압으로 급격하게 충전되고 그리고 (V1의 전압에 후속하여) 천천히 감쇠(decay)됨을 도시하고, 이는 상기 옵토캠 백플레인 동작에 대하여 예상된 것이다. 이러한 측정의 리프레쉬 레이트는 2초이지만, 실용적인 어플리케이션들을 위하여, 훨씬 높은 리프레쉬 레이트가 전압 출력들의 리플 발생을 최소화하기 위하여 사용될 수 있다.

[0024] 전술된 상기 옵토캠 백플레인의 어플리케이션들은 MEMs 기기들과 같은 기기들을 제어하기 위한 고 전압 스위칭을 포함한다. 고 전압 스위칭은 종종 표준 VLSI 프로세스들과 호환되지 않는다. 고 전압을 저 전압 회로들로부터 격리하기 위한 일 기법은 광결합기의 사용과 관련된다. 하지만, 도 12에 도시된 바와 같이, 표준 PIN 포토센서들이 높은 역 바이어스 전압에서 높은 누출 전류 때문에 고 전압 어플리케이션들에 부적합하다. 도 12는  $1 \text{ mm}^2$  의 면적 및  $1 \mu\text{m}$ 의 두께를 갖는 표준 PIN (i-a-Si:H) 포토센서의 암 및 광 IV 특성의 그래프이다. 도 12에 도시된 바와 같이, 상기 온/오프 비율은  $|V| > 20\text{V}$ 으로 빠르게 하강하고  $50\text{V}$  이후에는 10 이하로 하강한다.

[0025] 본 발명에서 기술되는 실시예들은 전술된 상기 옵토캠 백플레인을 포함하여, 다양한 어플리케이션들에서 사용될 수 있는 박막 반도체 광 스위치를 포함한다. 여기에서 기술되는 상기 박막 광 스위치들은 일부 관점들에서는 박막 트랜지스터들(TFT들)의 구조와 유사할 수 있다. 박막 트랜지스터(TFT)는 능동 반도체 층들, 유전체 층들 및 기판을 지지하는 비-금속을 통한 금속 접촉들의 (예컨대, 약  $1 \text{ nm}$  내지  $1 \mu\text{m}$ 의 범위 내의 두께를 갖는) 박막들을 증착함으로써 생성되는 3단자 기기이다.

[0026] 그러나, 상기 다양한 실시예들에 따른 상기 박막 광 스위치들은 고 전압 광결합기들을 위한 고 전압 광전도 기기들을 생성하기 위한 조향 하에서 박막 반도체들로 측면 전도에 의존하고, 매우 낮은 누출 전류( $100\text{V}$ 에서 약  $1\text{pA}$ )을 요구하는 어플리케이션들을 타겟하여, 2단자 기기들로서 동작하도록 구성된다는 점에서 박막 트랜지스터들과 상이하다. 이하에서 기술될 일부 실시예들은 박막 구조들과 관련되고 일부는 측면 p+/i/p+ 구조에 기반한다.

[0027] 여기에서 기술되는 상기 박막 광 스위치들은 감광성 물질 및 제1 및 제2 측면에서 배치되는 전극들 중 적어도 하나 사이에 접합부를 보호(shield)하는 하나 이상의 필드 판들을 포함한다. 상기 필드 판은 상기 전극들의 바이어스 또는 확장을 통해서 상기 전극과 전기적으로 연결될 수 있다. 여기에서 기술되는 상기 박막 광 스위치들은 박막 광결합기 백플레인들로 이용될 수 있는 단순하고 효과적인 해결방법을 제공한다. 기술되는 상기 설계들은 측면 전도를 제어하기 위한 조향에 의존한다. 이러한 구성들은 단락(short)들을 잠재적으로 생성할 수 있는 고 전압 크로스오버들을 유도할 수 있는, 트랜지스터 게이트들을 제어하기 위한 임의의 여분의 전압원에 대한 필요를 없앤다.

[0028] 여기에서 기술되는 상기 박막 광 스위치 구성들은  $500 \text{ cd/m}^2$  의 조향 레벨들에서  $-100$  내지  $+100$ 의 전압 범위에 걸쳐 약 500보다 큰, 약 750보다 큰, 또는 약 1000보다도 큰 유사한 온/오프 비율들을 갖는다. 상기 박막 광 스위치들은 약  $7 \times 10^{13}$  광자들/초의 전형적인 조향 조건들을 제공하는 현미경 광을 이용하여 시험되었다. 상기 조향 레벨은 도 12, 15, 및 17의 측정에 대하여 동일하다. 상기 광 스위치의 상기 암 상태 누출 전류는 상기 제1 및 제2 전극들 사이에  $+/- 100 \text{ V}$ 에서 약  $1 \times 10^{-12}$  암페어보다 적을 수 있다.

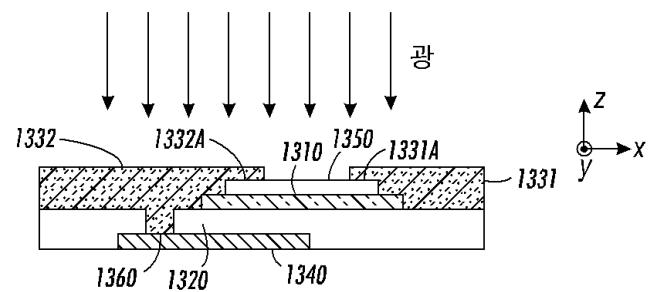

[0029] 도 13A 및 13B는 박막 호환 프로세스를 이용하여 제작될 수 있는 상기 박막 광 스위치의, 단면 및 측면 기기 구조를 각각 도시한다. 상기 광 스위치는 예컨대, a-Si:H와 같은 감광성 층(1310) 상부에 배치되는 예컨대, 질화물과 같은 절연 층(1320)을 포함한다. (예컨대, 금속, 금속 합금, 투명 도체, 또는 도핑된 n+ 물질과 같은) 제1 및 제2 전극들(1331, 1332)이 상기 감광성 층(1310)에 관하여 측면에서 오프셋된다. 상기 전극들(1331, 1332)은 접합부 영역(1331a, 1332a)에서 상기 감광성 층(1310)과 접촉한다. 절연층 예컨대, 질화물 층(1350)이 상기 감광성 층(1310)에 걸쳐 배치될 수 있다.

- [0030] 필드 판(1340)은 상기 감광성 층(1310)을 따라 x 및 y 축들로 확장된다. 상기 필드 판(1340)은 상기 절연층(1320)에 의해 상기 감광성 층(1310)으로부터 전기적으로 절연되고 연결(1360)에서 전극(1332)에 전기적으로 연결된다. 상기 필드 판(1340)은 도 13A에서 상기 접합부 영역(1332a) 내의 상기 필드 판 및 상기 감광성 반도체(1310) 사이에 z축에 따른 분리보다 큰 너비만큼 적어도 x 및/또는 y 방향들로 측면으로 확장된다. 필드 판(1340) 및 감광성 반도체(1310) 사이의 이러한 분리는 약 100 nm 내지 1 μm의 범위일 수 있다. x 및/또는 y 방향들로의 상기 접합부 영역(1332a)를 넘는 상기 확장은 상기 접합부 영역(1332a)에서의 상기 절연체(1320)의 (z축을 따르는) 두께의 약 2배보다 클 수 있다. 상기 감광성 반도체(1310)의 상기 감광성 반도체의 상기 z축에 따른 두께는 약 50nm 내지 약 1 μm의 범위 내 일 수 있다. 상기 접합부 영역(1332a)에서의 절연체(1320)의 상기 z축을 따른 두께는 약 100nm 내지 약 1 μm일 수 있다. 상기 z축에 따른 상기 필드 판의 두께는 약 100 nm 내지 수 마이크론 사이일 수 있다.

- [0031] 이러한 구성을 갖는 상기 필드 판(1340)은 Poole Frenkel 누출 전류를 완화(mitigate)한다. 상기 필드 판(1340)은 두 개의 전극들(1331, 1332)로부터 높은 전압 강하를 초래할 수 있는 높은 전기장으로부터 상기 접합부 영역(1332a)을 보호하도록 구성된다. 상기 필드 판(1340)은 금속을 포함할 수 있거나 또는 도 13A에서 지향되는 바와 같은 상기 기기의 하부로부터 광이 비추어지는 경우 광 응답을 향상시키기 위해 인듐 주석 산화물(ITO)와 같은 투명 전도 물질을 포함할 수 있다. 도 13A에서의 상기 조향(LIGHT)은 도 13A에서 지향되는 바와 같이 상기 상부로부터 비추어지도록 그려지지만, 일부 구성들에서는, 상기 조향은 상기 하부로부터 비추어질 수 있거나 또는 상기 기기의 상부 및 하부로부터 비추어질 수 있다. 상기 전극들(1331, 1332)은 일부 실시예들에서 투명 전도 물질을 포함할 수 있다.

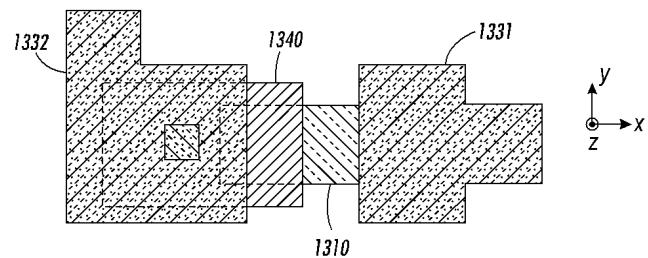

- [0032] 도 13A 및 13B은 하나의 바이어스 방향으로 고 전압 보호를 제공하기 위하여 설계된 하나의 필드 판을 갖는 기기를 도시한다. 도 14는 두 개의 필드 판들(1441, 1442)을 갖는 기기의 측면 구조를 도시한다. 도 14의 상기 기기는 모든 바이어스 방향들로 고 전압 보호를 제공하도록 설계된다. 상기 필드 판들(1441, 1442)은 상기 두 개의 전극들(1431, 1432) 사이에 높은 전압 강하로부터 초래될 수 있는 높은 전기장들로부터 상기 접합부 영역들(1431a, 1432a)을 보호하도록 구성된다.

- [0033] 도 14의 상기 기기는 접합부들(1431a 및 1432a)에서 감광성 층(140)과 접촉하는 전극들(1431 및 1432)을 갖는 상기 감광성 층(140)을 포함한다. 필드 판들(1441, 1442)은 상기 감광성 층(1410)을 따라 x 및 y 방향들로 확장된다. 필드 판들(1441, 1442)은 연결들(1461, 1462)에서 전극들(1431, 1432)에 전기적으로 연결되고 절연 층에 의해 상기 감광성 층(140)에 의해 상기 감광성 층(140)으로부터 전기적으로 절연된다. 상기 필드 판들(1441, 1442)은 상기 각각의 접합부 영역들(1431a, 1432a)을 넘어서 확장된다. 예를 들어, 상기 필드 판들(1441, 1442)의 각각은 도 14의 상기 접합부 영역(1431a, 1432a)에서 감광성 층(140) 및 상기 필드 판(1441, 1442)의 분리보다 큰 폭만큼 적어도 x 및/또는 y 방향들로 측면에서 확장될 수 있다. 필드 판(1441, 1442) 및 상기 감광성 반도체(1410) 간의 상기 분리는 전형적으로 약 100 nm 내지 1 μm의 범위에 있다. x 및 y 방향으로 상기 접합부 영역을 넘는 상기 확장은 종종 상기 절연 층의 두께의 약 2배보다 크다. 상기 감광성 반도체 층(1410)의 두께는 약 50nm 내지 약 1 μm의 범위에 있다. 상기 절연체의 두께는 전형적으로 약 100 nm 내지 약 1 μm의 범위에 있다. 상기 필드 판(1441, 1442)의 두께는 전형적으로 약 100 nm 내지 수 마이크론 사이에 있다.

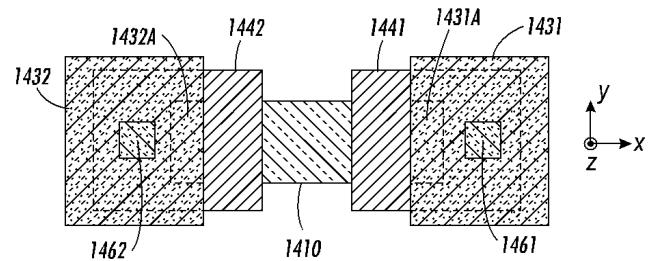

- [0034] 도 15는 도 13A 및 13B의 상기 구성을 갖는 기기의 상기 온/오프 비율 및 상기 암 및 광 IV 특성들을 도시한다. 상기 테스트된 기기는 상기 전극 금속으로서 MoCr을 이용하고, 이는 일부 광을 차단하지만 확산된 광이 상기 기기를 턴 온 하는데 충분하다.

- [0035] 도 16A 및 16B는 상기 소스 및 드레인 전극들로 통합되는 필드 판들을 포함하는 p+/i/p+ 구조에 기반하여 광 스 위치의 상기 단면 및 측면 기기 구조를 각각 도시한다. 비록 측면 p+/i/p+ 구조가 이러한 예로 제시되었음에도 불구하고, 당해 기술분야에서 통상의 지식을 가진 자는 측면으로 배치되는 전극들을 갖는 다른 구조들이 사용될 수 있고, 예를 들어, 일부 실시예들에서, 상기 기기가 측면의 p+/n-/p 또는 측면의 n+/p-/n+ 구조를 가질 수 있었다. 상기 기기는 절연 층(1620) 예컨대, 질화물 층 상에 배치되는 감광성 층(1610), 예컨대, a-Si:H을 포함한다. 상기 p+/i/p+ 층들은 측면에서 이격되어 배치된다. 제1 및 제2 전극들(1631, 1632) (예컨대, 소스 및 드레인 전극들)이 상기 감광성 층(1610)에 관하여 측면으로 이격되어 배치되고 제1 및 제2 접합부 영역들(1631a, 1632a)에서 상기 감광성 층(1610)이 각각 접촉한다. 다양한 실시예들에서, 상기 전극들(1631, 1632)은 금속, 금 속 합금, 예컨대, MoCr, p+ 도핑된 물질, 또는 ITO와 같은 투명 전도체를 포함할 수 있다.

- [0036] 필드 판들(1641, 1642)은 상기 접합부 영역들(1631a, 1632a)을 넘어 측면에서 확장되고, 전극들(1631, 1632)에 각각 전기적으로 연결된다. 상기 필드 판들(1641, 1642)은 절연체 영역들(1621a,b, 1622a,b)에 의해 상기 감광

성 층(1610)으로부터 전기적으로 절연된다. 상기 필드 판들(1641, 1642)은 상기 필드 판 및 감광성 반도체 사이에 상기 절연체 층(1621a,b, 1622a,b)의 상기 두께의 2배보다 큰 두께를 위한 하나 이상의 상기 절연체 영역들을 통해 상기 접합부 영역들을 넘어 확장될 수 있다. 상기 절연체 층(1621a,b, 1622a,b)은, 상기 접합부 영역들(1631a, 1632a) 근처에서 예를 들어, 약 100nm 내지 1μm 사이의 값을 가질 수 있다. 상기 감광성 반도체 층(1610)의 두께는 약 50nm 내지 1μm 사이일 수 있다. 상기 필드 판(1641, 1642)은 약 100nm 내지 1μm 두께일 수 있다.

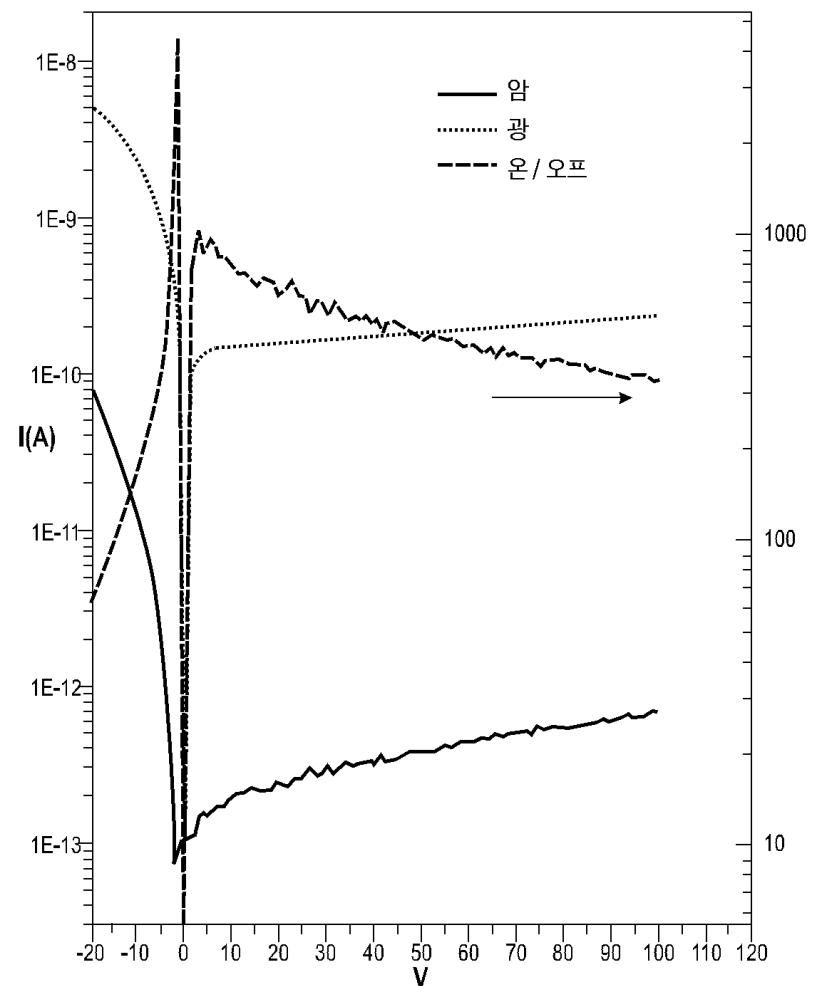

[0037] 도 17은 도 16A 및 16B의 상기 구조를 갖는 기기의 온/오프 비율 및 상기 암 및 광 IV 특성들을 도시한다. 대략적인 3차원의 크기는 -100 내지 +100 V 바이어스를 통해 관측된다. 상기 암 IV 특성들의 제로 교차(crossing)는 상대적인 높은 스윕 레이트 때문에 -25V로 천이되었다.

[0038] 본 발명에서 기술되는 광 스위치들은 높은 전기장으로부터 상기 반도체 접합부를 보호하기 위하여 측면의 광전 전도 플러스 하나 이상의 필드 판들을 이용하도록 설계된다. 상기 기술된 구조들은 고 전압 어플리케이션들과 호환되는 광 스위치들을 제공한다. 이러한 광 스위치들은 예를 들어, i-a-Si:H와 같은 감광성의 도핑되지 않은 반도체들을 포함할 수 있고 대면적 프로세스들과 호환된다. 상기 두 개의 전극들(예컨대, 소스 및 드레인)은 상기 반도체 층에 관하여 측면으로 오프셋된다. 상기 감광성 반도체 층은 평면형일 수 있거나, 또는, 일부 실시예들에서, 상기 감광성 반도체 층은 메사 서브-구조(mesa sub-structure)와 같은, 하나 이상의 비-평면형 서브-구조들에 걸쳐 곡면형으로 증착될 수 있다.

[0039] 상기 감광성 반도체 층 및 상기 전극들 중 하나 또는 전부 사이의 상기 접합부는 상기 전극과 동일한 전위에 있는 필드 판에 의해 커버되고, 반도체 접합부로의 상기 전극을 보호한다. 다양한 실시예들에서, 상기 제어 광은 상기 광 스위치의 상부, 하부 또는 상기 상부 및 하부로부터 공급(feed)된다.

## 도면

### 도면1

## 도면2

## 도면3

도면4

도면5aa

【도 5a2】로 및 【도 5a2】로부터

## 도면5ab

【도 5a1】으로 및 【도 5a1】으로부터

## 도면5b

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13a

도면13b

도면14

도면15

도면 16a

도면 16b

도면17