(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4401874号

(P4401874)

(45) 発行日 平成22年1月20日(2010.1.20)

(24) 登録日 平成21年11月6日(2009.11.6)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| H01L 21/3205 | (2006.01) |

| H01L 23/52   | (2006.01) |

| H01L 21/768  | (2006.01) |

| H01L 23/522  | (2006.01) |

|            |

|------------|

| H01L 21/88 |

| H01L 21/90 |

|   |

|---|

| S |

| B |

請求項の数 8 (全 24 頁)

(21) 出願番号

特願2004-182366 (P2004-182366)

(22) 出願日

平成16年6月21日 (2004.6.21)

(65) 公開番号

特開2006-5288 (P2006-5288A)

(43) 公開日

平成18年1月5日 (2006.1.5)

審査請求日

平成19年6月12日 (2007.6.12)

(73) 特許権者

503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人

100088672

弁理士 吉竹 英俊

(74) 代理人

100088845

弁理士 有田 貴弘

(72) 発明者

富田 和朗

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 長谷山 健

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

比誘電率が3以下の第1層間絶縁膜と、

前記第1層間絶縁膜上に形成され比誘電率が3以下の第2層間絶縁膜と、

半導体チップの回路形成領域を囲むように前記第1及び第2層間絶縁膜内に形成されたシールリングと、

前記半導体チップのダイシング領域に形成された複数のダミーパターンとを備え、

前記複数のダミーパターンのそれぞれは、

前記第1層間絶縁膜内に形成された第1ダミーメタルと、

前記第2層間絶縁膜内に形成された第2ダミーメタルと、

前記第2層間絶縁膜内に形成され、前記第1ダミーメタルと前記第2ダミーメタルとを接続する複数のダミーピアとを含み、

前記シールリングは、前記半導体チップのエッジ部近傍に配設され、

前記ダイシング領域は、前記シールリングの外側に配置されていることを特徴とする半導体装置。

## 【請求項 2】

前記ダミーピアは、平面視で複数の列に沿って配置され、隣り合う列に配置された前記ダミーピアは、交互に配置されることにより千鳥配置となっていることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

10

20

前記シールリングを囲むように前記第1及び第2層間絶縁膜内に形成されたダミースリットビアを更に有する

ことを特徴とする請求項2に記載の半導体装置。

**【請求項4】**

前記ダミースリットビアの線幅が最小寸法の5倍から20倍であることを特徴とする請求項3に記載の半導体装置。

**【請求項5】**

前記ダミービアの径は最小寸法の1~100倍であることを特徴とする請求項1から請求項4の何れかに記載の半導体装置。

**【請求項6】**

半導体基板上に形成され比誘電率が3以下の第1層間絶縁膜と、

半導体チップの回路形成領域を囲むように前記第1層間絶縁膜内に形成されたシールリングと、

前記第1層間絶縁膜内に形成され、前記シールリングを囲むように形成された複数の第1金属ダミーパターンと、

前記第1層間絶縁膜内に形成され、前記シールリング及び前記複数の第1金属ダミーパターンを囲むように形成されたスリット状金属パターンと、

前記第1層間絶縁膜内に形成され、前記シールリング、前記複数の第1金属ダミーパターン、及び前記スリット状金属パターンを囲むように形成された複数の第2金属ダミーパターンとを有し、

前記シールリングは、前記半導体チップのエッジ部近傍に形成され、

前記複数の第1金属ダミーパターン、前記スリット状金属パターン、及び前記複数の第2金属ダミーパターンは、前記シールリングの外側のダイシング領域に配置されていることを特徴とする半導体装置。

**【請求項7】**

前記複数の第1金属ダミーパターンは、平面視で複数の列に沿って配置され、隣り合う列に配置された前記第1金属ダミーパターンは、交互に配置されることにより千鳥配置となつてあり、

前記複数の第2金属ダミーパターンは、平面視で複数の列に沿って配置され、隣り合う列に配置された前記第2金属ダミーパターンは、交互に配置されることにより千鳥配置となつてている

ことを特徴とする請求項6に記載の半導体装置。

**【請求項8】**

前記第1層間絶縁膜の下側に形成され比誘電率が3以下の第2層間絶縁膜と、

前記第1層間絶縁膜内に形成された複数の第1ダミー配線パターンと、

前記第2層間絶縁膜内に形成された複数の第2ダミー配線パターンとを更に備え、

前記複数の第2金属ダミーパターンは、前記第1ダミー配線パターンと前記第2ダミー配線パターンとを接続している

ことを特徴とする請求項6に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置の保護構造であるシールリングに関するものである。

**【背景技術】**

**【0002】**

半導体装置の回路形成領域を外界の雰囲気からの水分やイオンの影響から保護するためには、ダイシングラインの内側、即ちチップ(ダイ)のエッジ部近傍に、シールリングあるいはダイエッジシール(Die Edge Seal)、ガードリングと呼ばれる保護構造が設けられる。シールリングは、回路形成領域と同様の配線層及びコンタクトによって形成され、半導体装置の回路形成領域を囲むように形成される。

10

20

30

40

50

**【0003】**

シールリングの存在により、半導体装置の回路形成領域は外界の雰囲気からの水分やイオンの影響から保護され、長期間に渡って当該半導体装置の特性を安定させることができる。

**【0004】**

また、シールリングは、ダイシング領域をダイシングする際に回路形成領域にクラックが発生するのを抑える作用も有している。ダイシングの際にはダイシング領域にクラックが発生することがあるが、ダイシング領域と回路形成領域との間にシールリングが存在するため、そのクラックが回路形成領域にまで達することが防止されるからである。

**【0005】**

10

例えば特許文献1には、シールリングを形成し、回路形成領域に複数ダミーパターンを設けている。そして、CMP (Chemical Mechanical Polishing) 法による平坦化プロセスにおいて、チップエッジ部の平坦性向上を可能とする発明が開示されている。

**【0006】**

【特許文献1】特開2002-208676号公報

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

20

ところで、近年、半導体装置における構造の微細化並びに高集積化、動作の高速化が進むにつれ、配線の低抵抗化の重要性が高まっている。それに伴い、比較的抵抗の小さいCu(銅)が、配線材料として多く用いられるようになっている。即ち、上記のシールリング構造にも銅が使用されるケースが増加しつつある。また、層間絶縁膜として比誘電率kの低い、いわゆるLow-k膜( $k < 3.0$ )が多く用いられるようになってきている。

**【0008】**

このようなLow-k膜を層間絶縁膜として用いた場合、ダイシング時に発生するクラックが、シールリングを越えて回路形成領域に達し易く、回路形成領域に悪影響を及ぼす問題があった。また、クラックが回路形成領域には至らなくても、シールリングにまで達した場合、半導体装置の吸湿耐性を劣化させる問題を生じる。

**【0009】**

30

そこで本発明は、Low-k膜を層間絶縁膜として用いた場合であっても、ダイシング時に発生するクラックがシールリングに達するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

**【課題を解決するための手段】****【0010】**

この発明の第1の局面に係る半導体装置は、比誘電率が3以下の第1層間絶縁膜と、前記第1層間絶縁膜上に形成され比誘電率が3以下の第2層間絶縁膜と、半導体チップの回路形成領域を囲むように前記第1及び第2層間絶縁膜内に形成されたシールリングと、前記半導体チップのダイシング領域に形成されたダミーパターンとを備え、前記ダミーパターンは、前記第1層間絶縁膜内に形成された第1ダミーメタルと、前記第2層間絶縁膜内に形成された第2ダミーメタルと、前記第2層間絶縁膜内に形成され、前記第1ダミーメタルと前記第2ダミーメタルとを接続する複数のダミービアとを含み、前記シールリングは、前記半導体チップのエッジ部近傍に配設され、前記ダイシング領域は、前記シールリングの外側に配置されていることを特徴とする。

40

また、この発明の第2の局面に係る半導体装置は、半導体基板上に形成され比誘電率が3以下の第1層間絶縁膜と、半導体チップの回路形成領域を囲むように前記第1層間絶縁膜内に形成されたシールリングと、前記第1層間絶縁膜内に形成され、前記シールリングを囲むように形成された複数の第1金属ダミーパターンと、前記第1層間絶縁膜内に形成され、前記シールリング及び前記複数の第1金属ダミーパターンを囲むように形成されたスリット状金属パターンと、前記第1層間絶縁膜内に形成され、前記シールリング、前記

50

複数の第1金属ダミーパターン、及び前記スリット状金属パターンを囲むように形成された複数の第2金属ダミーパターンとを有し、前記シールリングは、前記半導体チップのエッジ部近傍に形成され、前記複数の第1金属ダミーパターン、前記スリット状金属パターン、及び前記複数の第2金属ダミーパターンは、前記シールリングの外側のダイシング領域に配置されていることを特徴とする。

【発明の効果】

【0011】

本発明は、半導体チップのダイシング領域側において、シールリング部を囲うようにダミーパターンを形成している。そのため、ダイシング時にクラックが発生しても、ダミーパターンによってクラックの進行が阻まれ、クラックがシールリング部に到達するのを抑制することができる。

10

【発明を実施するための最良の形態】

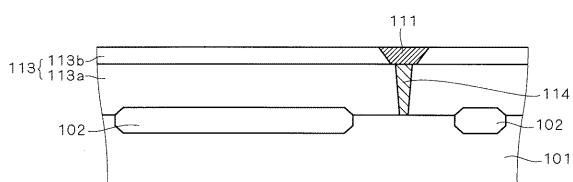

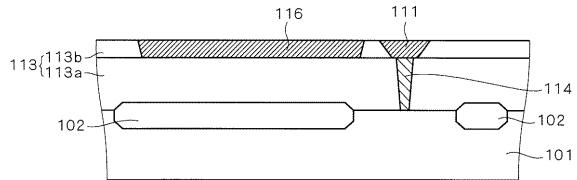

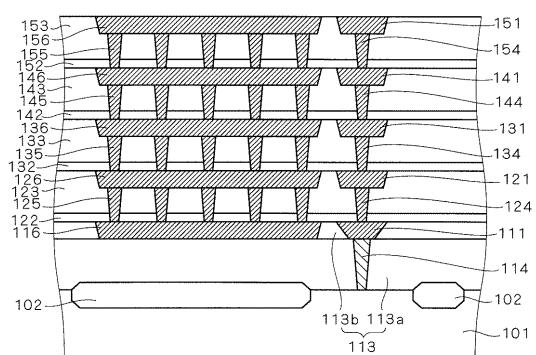

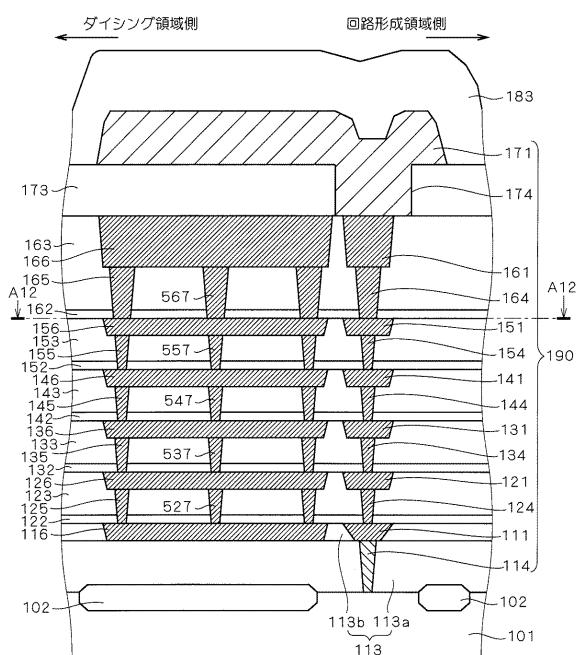

【0012】

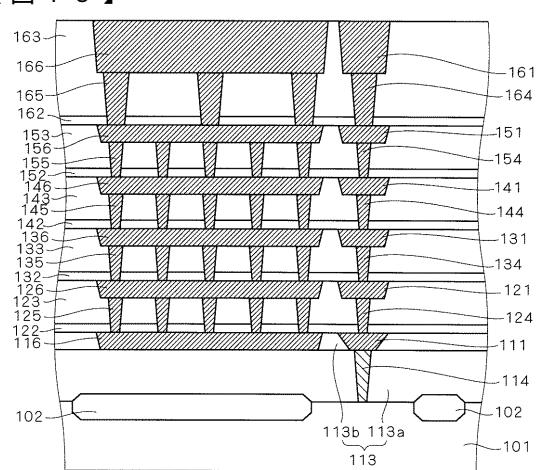

<実施の形態1>

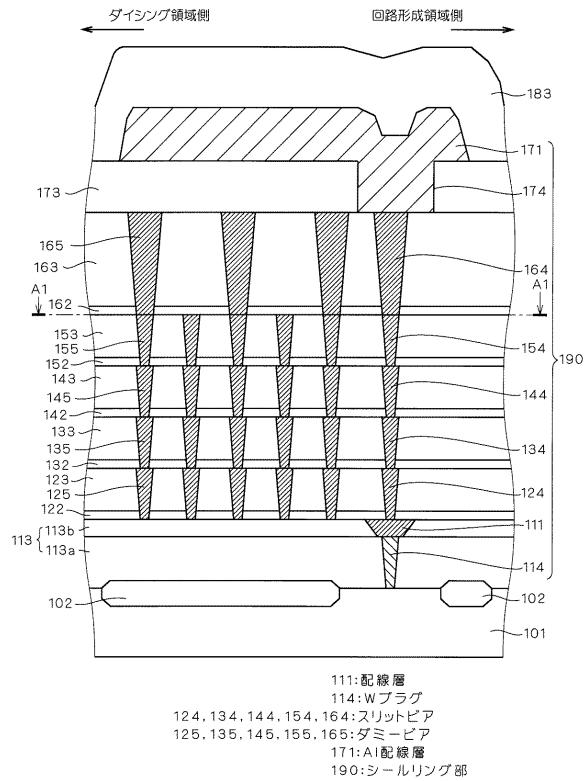

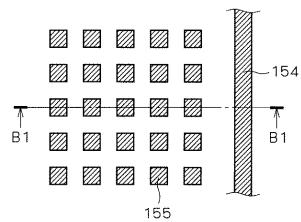

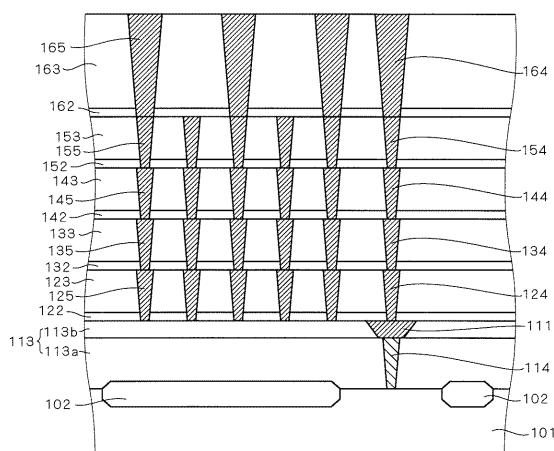

図1は、実施の形態1に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図2は、図1のA1-A1線での上面図に対応している。また、図1は、図2のB1-B1線断面図に対応している。図1に示した領域の右側に回路形成領域、左側にダイシング領域がそれぞれ存在する。

【0013】

ここで、半導体ウェハ上には半導体チップが縦横に配置され、夫々の半導体チップはダイシング領域によって区分けされている。半導体チップには、回路形成領域が形成され、回路形成領域の周りにシールリングが配置されている。すなわち回路形成領域を囲むようにシールリングが形成されている。図1は、その半導体チップの端面図に対応し、かつ半導体チップのエッジ部近傍(シールリングが形成された領域)に対応した図を示している。

20

【0014】

なお、同図において半導体装置の回路部分の図示は省略している。また図1は、6層のCu配線と1層のAl配線構造を備える半導体装置の場合を示している。

【0015】

トレンチ分離102が形成されたシリコン基板101上に層間絶縁膜113が形成されている。トレンチ分離(素子分離膜)102は、例えば酸化膜300nmで形成されている。層間絶縁膜113は、層間絶縁膜113a及び第1配線層間絶縁膜113bにより構成されている。そして層間絶縁膜113aは、例えばUSG(Undoped Siliccon Glass)膜500nmで形成され、第1配線層間絶縁膜113bは例えばプラズマTEOS(Tetraethyl orthosilicate)膜300nmで形成されている。

30

【0016】

層間絶縁膜113aには、スリット状のW(タンゲステン)プラグ114が形成されている。そしてWプラグ114内には、TiN(窒化チタン)/Ti(チタン)構造のバリアメタルが形成され、Wが埋め込まれている。Wプラグ114上には配線層111が形成されている。配線層111は、Ta(タンタル)/TaN(窒化タンタル)構造のバリアメタルにCuが埋め込まれている。

40

【0017】

層間絶縁膜113上にCu拡散防止絶縁膜(エッチングストッパー膜若しくはライナー膜と呼ばれることもある。以下、単に拡散防止膜と称する)122が形成されている。拡散防止膜122上に、層間絶縁膜123が形成されている。そして層間絶縁膜123には、複数のダミービア125及びスリット状のスリットビア124が形成されている。スリットビア124は、配線層111上に形成されている。そしてダミービア125は、ダイシング領域側に形成されている。

【0018】

10

20

30

40

50

層間絶縁膜123上に拡散防止膜132が形成されている。拡散防止膜132上に、複数のダミービア135及びスリット状のスリットビア134が形成された層間絶縁膜133が形成されている。スリットビア134はスリットビア124上に形成されている。そしてダミービア135は、ダミービア125上に形成されている。

## 【0019】

層間絶縁膜133上に拡散防止膜142が形成されている。拡散防止膜142上に、複数のダミービア145及びスリット状のスリットビア144が形成された層間絶縁膜143が形成されている。スリットビア144は、スリットビア134上に形成されている。そしてダミービア145は、ダミービア135上に形成されている。

## 【0020】

層間絶縁膜143上に拡散防止膜152が形成されている。拡散防止膜152上に、複数のダミービア155及びスリット状のスリットビア154が形成された層間絶縁膜153が形成されている。スリットビア154は、スリットビア144上に形成されている。そしてダミービア155は、ダミービア145上に形成されている。

## 【0021】

層間絶縁膜153上に拡散防止膜162が形成されている。拡散防止膜162上に、複数のダミービア165及びスリット状のスリットビア164が形成された層間絶縁膜163が形成されている。スリットビア164はスリットビア154に接して形成されている。さらに、ダミービア165は、ダミービア155に接して形成されている。

## 【0022】

図2に示すように、第5層目のダミービア155の径は、例えば0.14μmであり、例えば1μmピッチで縦横に等間隔に配列されている。第2層から第4層に形成されたダミービアについても、同様に形成されている。また、ダミービア165の径は0.28μmであり、例えば2μmピッチで縦横に等間隔に配列されている。

## 【0023】

拡散防止膜122, 132, 142, 152, 162は、例えばSiC(炭化シリコン)膜(k~4.8)50nmで形成されている。そして、層間絶縁膜123, 133, 143, 153は、Low-k膜であるSiOC(炭素含有シリコン酸化膜)膜(k~2.8)が用いられ膜厚500nmで形成されている。層間絶縁膜163は、USG膜(k~4.1)で約1000nmで形成されている。

## 【0024】

スリットビア124, 134, 144, 154, 164及びダミービア125, 135, 145, 155, 165は、Ta(タンタル)/TaN(窒化タンタル)構造のバリアメタルにCuが埋め込まれている。

## 【0025】

層間絶縁膜163上には、パッシベーション膜173が形成されている。パッシベーション膜173は、例えばプラズマSiN(窒化シリコン)膜(k~7)500nmで形成されている。そして第1パッシベーション膜173内にはホール174が形成されている。そして、第1パッシベーション膜173上にはA1(アルミニウム)配線層171が形成されている。

## 【0026】

A1配線層171は、バリアメタルTiN/Ti膜を含むAL(アルミニウム)積層膜によって形成されている。そしてA1配線層171の膜厚は、1000nmに形成されている。A1配線層171を覆うように、第2パッシベーション膜183が形成されている。第2パッシベーション膜183は、例えばプラズマSiN膜を材料として、1000nmの厚みで形成されている。

## 【0027】

なお、Wプラグ114、配線層111、スリットビア124, 134, 144, 154, 164、及びA1配線層171で、シールリング部190を形成している。

## 【0028】

10

20

30

40

50

そして、ダミービア 125, 135, 145, 155, 165 は、シールリング部 190 の周りに配置されている。すなわちダミービア 125, 135, 145, 155, 165 (ダミーパターン) は、シールリング部 190 を囲うように形成されている。

#### 【0029】

図 3 ~ 9 は、図 1 に示した半導体装置の製造工程を示す図である。以下、これらの図に基いて本実施の形態に係る半導体装置の製造方法について説明する。

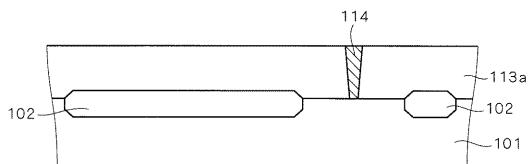

#### 【0030】

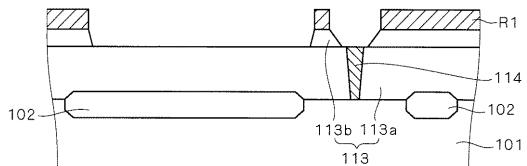

図 3 に示す工程においては、シリコン基板 101 に STI (Shallow Trench Isolation) 法で例えば厚さ 300 nm のトレンチ分離 102 を形成する。次に、例えば高密度プラズマ (HDP : High Density Plasma) 酸化膜を 800 nm 堆積して、CMP (Chemical Mechanical Polishing) 法により 300 nm 研磨することによって、層間絶縁膜 113a を形成する。そして層間絶縁膜 113a に、例えば 0.10 μm 幅のレジストマスクを用いたドライエッティングにより、シールリング部 190 に対応する位置にスリット状の開口部を形成する。このとき、シリコン基板 101 と、層間絶縁膜 113a とは充分エッティング選択比のある条件でエッティングしている。

#### 【0031】

続いて、CVD (Chemical Vapor Deposition) 法により、例えば TiN 及び Ti をそれぞれ 20 nm ずつ堆積させたバリアメタル (図示せず) を形成した後、同じく CVD 法によりタンゲステンを 200 nm 堆積させる。その後、CMP 法を用いて、層間絶縁膜 113a 上のタンゲステン及びバリアメタルを除去することで、スリット状の W プラグ 114 が形成される。

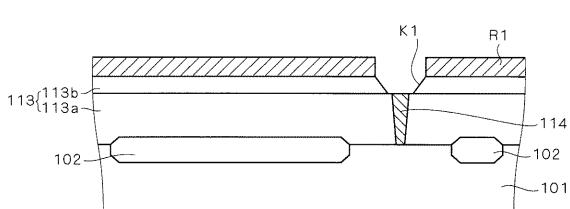

#### 【0032】

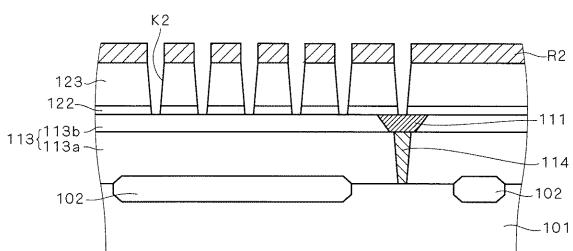

次に、層間絶縁膜 113a 上にプラズマ TEOS 膜を 300 nm 堆積して第 1 配線層間絶縁膜 113b を形成する。第 1 配線層間絶縁膜 113b 上にレジストマスク R1 を形成し、レジストマスク R1 を用いてプラズマ TEOS 膜をエッティングすることで、配線層 111 を形成するための開口部 K1 を W プラグ 114 上に形成する (図 4)。

#### 【0033】

次に、レジストマスク R1 を除去した後、TaN 及び Ta をそれぞれ 10 nm ずつスパッタ法により成膜することでバリアメタル (図示せず) を形成し、続いて Cu をスパッタ法で 100 nm 堆積させてシード (図示せず) を形成する。そして配線層 111 の材料となる Cu をメッキ法で 1000 nm 堆積させる。その後 CMP 法を用いて層間絶縁膜 113 上の Cu 及びバリアメタルを除去することで、配線層 111 が形成される (図 5)。

#### 【0034】

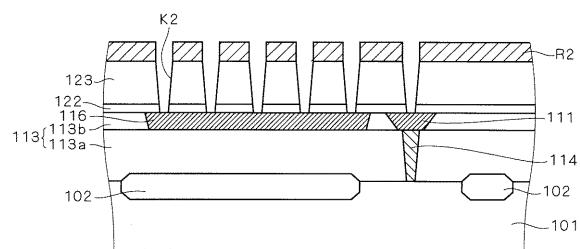

次に、プラズマ SiC 膜を 50 nm 堆積させることで、拡散防止膜 122 を形成する。続いて例えばプラズマ SiOC 膜を 600 nm 堆積させ、CMP 法を用いて 200 nm 研磨することにより層間絶縁膜 123 を形成する。その後、層間絶縁膜 123 を、レジストマスク R2 を用いたドライエッティングにより、ダミービア 125 及びシールリング部 190 を構成するスリットビア 124 を形成するための開口部 K2 を形成する (図 6)。

#### 【0035】

なお、このとき図示しない回路形成領域には、第 2 ビアを形成するための開口部 (図示せず) がダミービア 125 及びスリットビア 124 の開口部 K2 と同時に形成されている。

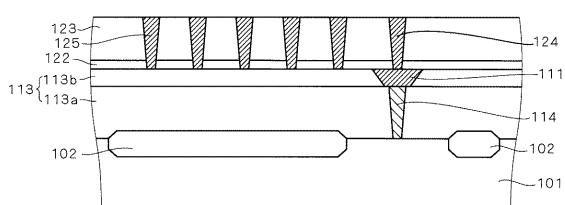

#### 【0036】

次に回路形成領域に第 2 配線層を形成するための開口部 (図示せず) を形成後、Ta 及び TaN をそれぞれ 10 nm ずつスパッタ法により堆積する。そしてスパッタ法により、Cu を 100 nm 堆積することでシードを形成する (図示せず)。その後メッキ法で Cu を 1000 nm 堆積し、CMP 法で層間絶縁膜 123 上の Cu 及びバリアメタルを除去する。そして、ダミービア 125 及びスリットビア 124 を形成する (図 7)。また回路形成領域には、第 2 ビア及び第 2 配線層が同時に形成されている。

10

20

30

40

50

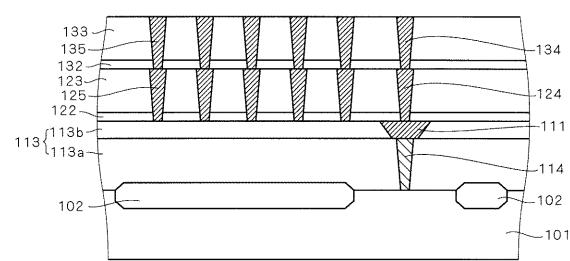

## 【0037】

次に、プラズマSiC膜を50nm堆積させることで、拡散防止膜132を形成する。続いて例えばプラズマSiOC膜を600nm堆積させ、CMP法を用いて200nm研磨することにより層間絶縁膜133を形成する。その後、層間絶縁膜133を、レジストマスクを用いたドライエッチングにより、ダミーピア135及びシールリング部190を構成するスリットピア134を形成するための開口部を形成する。

## 【0038】

なお、このとき図示しない回路形成領域には、第3ピアを形成するための開口部(図示せず)がダミーピア135及びスリットピア134の開口部と同時に形成されている。

## 【0039】

次に回路形成領域には、第3配線層を形成するための開口部を形成する。その後Ta及びTaNをそれぞれ10nmずつスパッタ法により堆積する。

10

## 【0040】

次にスパッタ法により、Cuを100nm堆積することでシードを形成する。その後メッキ法でCuを1000nm堆積し、CMP法で層間絶縁膜133上のCu及びバリアメタルを除去する。そして、ダミーピア135及びスリットピア134を形成する(図8)。また回路形成領域には、第3ピア及び第3配線層が同時に形成されている。

## 【0041】

同様の手順にしたがって第4層目及び第5層目のダミーピア145, 155及びスリットピア144, 154を形成する。また回路形成領域には、同時に第4, 5ピア、第4, 5配線層が形成される。形成方法は、第2層目及び第3層目と同様なので説明は省略する。

20

## 【0042】

次に図9に示す工程においては、例えば、プラズマSiC膜を50nm堆積させることで、拡散防止膜162を形成する。続いて例えばプラズマTEOS膜を1200nm堆積させ、CMP法を用いて200nm研磨することにより層間絶縁膜163を形成する。その後、層間絶縁膜163、ダミーピア165及びシールリング部190を構成するスリットピア164を形成する。同時に回路形成領域には第6ピア及び第6配線層を形成している。

## 【0043】

30

ここで、第6層目は、セミグローバル配線が形成される層に対応している。そして、セミグローバル配線を形成するセミグローバル工程は、第1～5層目のローカル配線を形成する工程(ファイン工程)に比べて例えば倍の寸法でレイアウトされている。そのためダミーピア165は、図9に示すように、0.28μmの径で形成され、例えば2μmピッチ縦横に整列されてレイアウトされている。

## 【0044】

次に層間絶縁膜163上にプラズマSiN膜500nmを堆積して第1パッシベーション膜173を形成する。その後、ホール174を第1パッシベーション膜173に形成する。さらに、TiN/Tiのバリアメタルを含むAL積層膜を堆積後、パターニングしてA1配線層171を形成する。さらに、プラズマSiN膜500nm堆積後に第2パッシベーション膜183を形成する。そして、図1に示した構造を形成することができる。

40

## 【0045】

以上説明したように、本実施の形態に係る半導体装置は、ダイシング領域側において、ダミーピアが形成されている。そのため、ダイシング時にクラックが発生しても、ダミーピアによってクラックの進行が阻まれ、クラックがシールリング部190に到達するのを抑制することができる。クラックが、シールリング部190、さらにはシールリング部190を越えて回路形成領域に到達することを抑制できるので、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

## 【0046】

また、シールリングが形成される領域のようなCuパターン率の低い箇所にLow-k

50

膜を用いた場合、Low-k膜の占有面積が大きくなる。Low-k膜と拡散防止膜との密着性は高くないのでデラミネーション（膜剥がれ）が生じ易くなる問題がある。

#### 【0047】

本実施の形態では、ダミービアを形成することにより、Low-k膜の占有面積を減少することができる。そのため、Low-k膜を用いた場合であっても、膜剥がれを抑制することができる。

#### 【0048】

なお、本実施の形態では、層間絶縁膜としてLow-k膜であるプラズマSiOC膜を用いた場合について述べたが、ULK( Ultra Low-k )膜又はそれらの積層膜でも同様の効果を有する。10

#### 【0049】

また、拡散防止膜122, 132, 142, 152, 162がプラズマSiC膜の場合について述べたが、より誘電率の低いプラズマSiC膜(k: 3~4)やプラズマSiN膜又はそれらの積層膜であってもよい。また、拡散防止膜を形成しない場合でも同様の効果を有する。

#### 【0050】

さらにダミービア、スリットビアがCuから構成されている場合について説明したが、W, TaN, TiN, Ta, Ti又はこれらの積層膜であってもよい。

#### 【0051】

本実施の形態では、ダミービアが1μmのピッチで、0.14μm径のビアの場合について説明したが、ビアの径は、最小寸法の1~100倍程度までなら同様のことが言える。またビアのピッチについても、占有率が0.01~20%の範囲であればよい。20

#### 【0052】

ここで最小寸法とは、各層に形成されるビア若しくは配線の設計上のビア径、配線幅で定義される寸法を指している。

#### 【0053】

また、ダミービアの形状は、正方形の形状について示したが、同程度の開口率であれば長方形でもかまわない。

#### 【0054】

本実施の形態では、ダミービアを回路形成領域のビアと同時に形成する工程を示したが、回路形成領域のビアより先に形成しても、後に形成してもよい。さらに、シールリング部190のスリットビアと別に形成してもよい。また、各層が同じレイアウトで積層されている場合について述べたが、上層のレイアウトが下層のレイアウトに比べて半ピッチずらした場合でも同様のことが言える。そして、各層でビア径やピッチのレイアウトが異なっていてもよい。30

#### 【0055】

<実施の形態2>

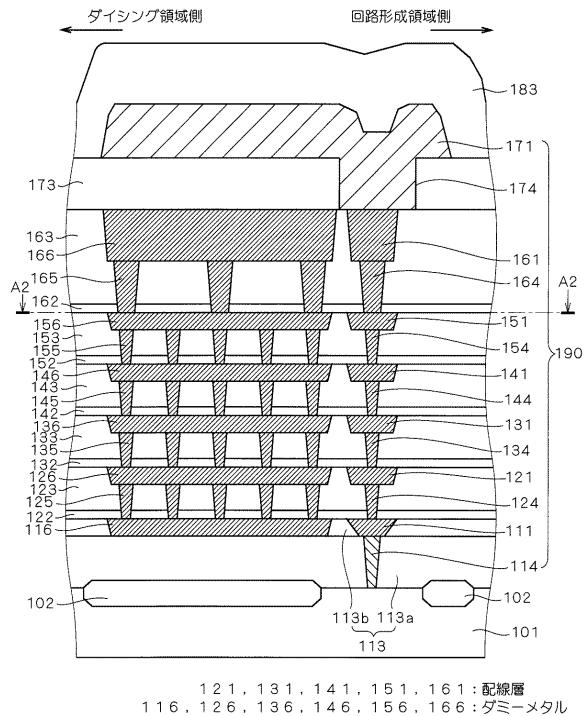

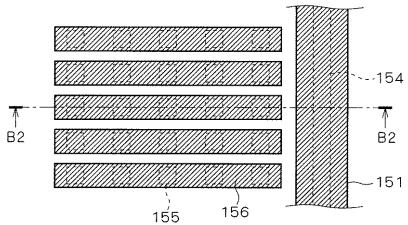

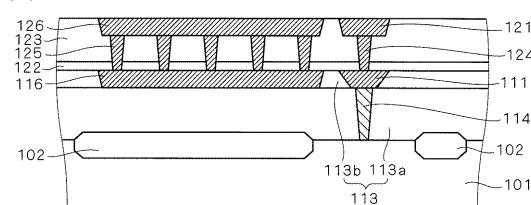

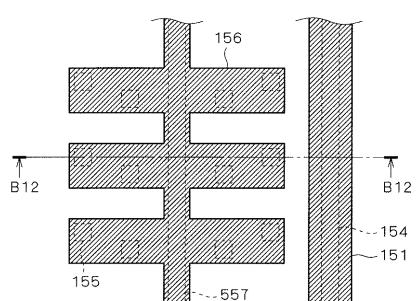

図10は、本実施の形態2に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図11は、図10のA2-A2線での上面図に対応している。また、図10は図11のB2-B2線断面図に対応している。本実施の形態では、各層にダミーメタル及び配線層がさらに形成されている。以下の説明では、実施の形態1と同一の構成には同一の符号を付し、重複する説明は省略する。40

#### 【0056】

ダミーメタル116が配線層111と同一平面上に形成されている。そして、ダミーメタル116上にダミービア125が形成されている。ダミービア125上にはダミーメタル126が形成されている。ダミービア135, 145, 155, 165上には、ダミーメタル136, 146, 156, 166がそれぞれ形成されている。また、スリットビア124, 134, 144, 154, 164上には、配線層121, 131, 141, 151, 161がそれぞれ形成されている。

#### 【0057】

50

また図11に示すように、複数のダミーメタル156は、ダミービア155の上端を覆うようにそれぞれ平行に配置されている。他の層に形成されたダミーメタルも同様に配置されている。ここでダミーメタルの線幅は、Cu堆積後のCMP工程で発生するディッシングを抑制するために10μm以上の幅を用いず、例えば2μm幅で形成されている。また、スリットビア154上には配線層151が形成されている。

#### 【0058】

ダミーメタル116, 126, 136, 146, 156, 166及び配線層111, 121, 131, 141, 151は、Ta/TaN構造のバリアメタルにCuが埋め込まれている。

#### 【0059】

なお、Wプラグ114、配線層111, 121, 131, 141, 151, 161及びスリットビア124, 134, 144, 154, 164、及びAl配線層171でシールリング部190を形成している。

#### 【0060】

以下図12～18を用いて、本実施の形態に係る半導体装置の製造方法について説明する。まず実施の形態1(図3)において説明したように、シリコン基板101上にトレンチ分離102、層間絶縁膜113及びWプラグ114を形成する。

#### 【0061】

次に図12に示す工程においては、プラズマTEOS膜を300nm堆積する。そしてレジストマスクR1を用いてプラズマTEOS膜をエッチングし、ダミーメタル116及び配線層111に対応する開口部を形成する。

#### 【0062】

続いて図13に示す工程においては、レジストマスクR1を除去した後、TaN及びTaをそれぞれ10nmずつスパッタ法により成膜することでバリアメタル(図示せず)を形成し、続いてCuをスパッタ法で100nm堆積させてシード(図示せず)を形成する。そして配線層111の材料となるCuをメッキ法で1000nm堆積させる。そして、CMP法を用いて層間絶縁膜103上のCu及びバリアメタルを除去することで、配線層111及びダミーメタル116が形成される。

#### 【0063】

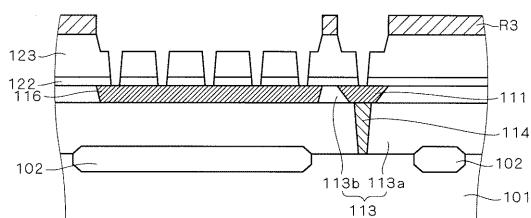

次にプラズマSiC膜を50nm堆積させることで、拡散防止膜122を形成する。続いて例えばプラズマSiOC膜を600nm堆積させ、CMP法を用いて200nm研磨することにより層間絶縁膜123を形成する。その後、レジストマスクR2を用いたドライエッチングにより、ダミービア125及びスリットビア124を形成するための開口部K2を層間絶縁膜123に形成する(図14)。

#### 【0064】

なお、このとき図示しない回路形成領域には、第2ビアを形成するための開口部(図示せず)がダミービア125及びスリットビア124の開口部K2と同時に形成されている。

#### 【0065】

続いて図15に示す工程においては、レジストマスクR3を用いて、層間絶縁膜123をエッチングすることで、ダミーメタル126及び配線層121を形成する領域を開口する。このとき、図示しない回路形成領域にも、第2配線層を形成するための開口部(図示せず)が形成されている。

#### 【0066】

次に図16に示す工程においては、レジストマスクR3を除去後、Ta及びTaNをそれぞれ10nmずつスパッタ法により堆積する。そしてスパッタ法によりCuを100nm堆積することでシードを形成する(図示せず)。その後メッキ法でCuを1000nm堆積し、CMP法で層間絶縁膜123上のCu及びバリアメタルを除去する。そして、ダミービア125、スリットビア124、ダミーメタル125及び配線層121を同時に成する。また、回路形成領域にも図示しない第2ビア及び第2配線層が同時に形成される

10

20

30

40

50

。

### 【 0 0 6 7 】

同様の手順にしたがって第3層目から第5層目のダミービア135, 145, 155、スリットビア134, 144, 154、ダミーメタル136, 146, 156及び配線層131, 141, 151を形成する(図17)。回路形成領域にも、第3ビア～第5ビア及び第3配線層～第5配線層を同時に形成する。形成方法は第2層目と同様なので説明は省略する。

### 【 0 0 6 8 】

次に図18に示す工程においては、例えば、プラズマSiC膜を50nm堆積させることで、拡散防止膜162を形成する。続いて例えばプラズマTEOS膜を1200nm堆積させ、CMP法を用いて200nm研磨することにより層間絶縁膜163を形成する。

10

### 【 0 0 6 9 】

そして、図14, 図15の説明と同様の手順にしたがって、層間絶縁膜163に、スリットビア164、ダミービア165、ダミーメタル166及び配線層161を形成する。同時に回路形成領域には第6ビア及び第6配線層を形成している。

### 【 0 0 7 0 】

ここで、第6層目は、セミグローバル配線が形成される層に対応している。そして、セミグローバル配線を形成するセミグローバル工程は、第1～5層目のローカル配線を形成する工程(ファイン工程)に比べて例えば倍の寸法でレイアウトされている。従って、ダミービア165は、図18に示すように、0.28μmの径で形成され、例えば2μmピッチ縦横に整列されてレイアウトされている。

20

### 【 0 0 7 1 】

次に層間絶縁膜163上にプラズマSiN膜500nmを堆積して第1パッシベーション膜173を形成する。その後、ホール174を第1パッシベーション膜173に形成する。さらに、TiN/Tiのバリアメタルを含むAL積層膜を堆積後、パターニングしてAL配線層171を形成する。さらに、プラズマSiN膜500nm堆積後に第2パッシベーション膜183を形成する。そして、図10に示した構造を形成することができる。

。

### 【 0 0 7 2 】

本実施の形態では、各層にダミーメタルを形成している。そのためダイシング時に発生するクラック等の伝播をさらに抑制することができる。シールリング部190がクラック等で露出することが防げるため、回路形成領域の吸湿性を向上できる。

30

### 【 0 0 7 3 】

また、Low-k膜と拡散防止膜は熱膨張率等に差がある。そのためLow-k膜と拡散防止膜間にストレスが生じる。本実施の形態では、ダミーメタルを設けることにより、Low-k膜と拡散防止膜に接する面積が減少する。その結果、Low-k膜と拡散防止膜間のストレスを緩和できる。

### 【 0 0 7 4 】

さらに、ダミーメタルを設けることで、ダミーメタルと上層に設けられた拡散防止膜との接触面積が大きくなる。ダミーメタルと拡散防止膜との密着性は、Low-k膜と拡散防止膜との密着性に比べて高いため、ダミーメタルの面積を大きくすることで、各層間の密着性を高めることができる。

40

### 【 0 0 7 5 】

また、ダミーメタルや配線層に太幅配線を用いた場合、Cu埋め込み後のCMP工程においてディッキングによりダミーメタルや配線層が断線する問題があった。

### 【 0 0 7 6 】

さらに、太幅配線を用いた場合、上層のダミービアと下層のダミーメタルの接合部(例えば、ダミービア125とダミーメタル116の接合部)に、高温保存(SM試験: Stress Migration試験)後にボイド(SIV: Stress Induced Void)が生じ、信頼性が低下するという問題もあった。本実施の形態では、ダミ

50

一メタルや配線層に太幅配線を用いないようにレイアウトしているので、これらの問題を防止することができる。

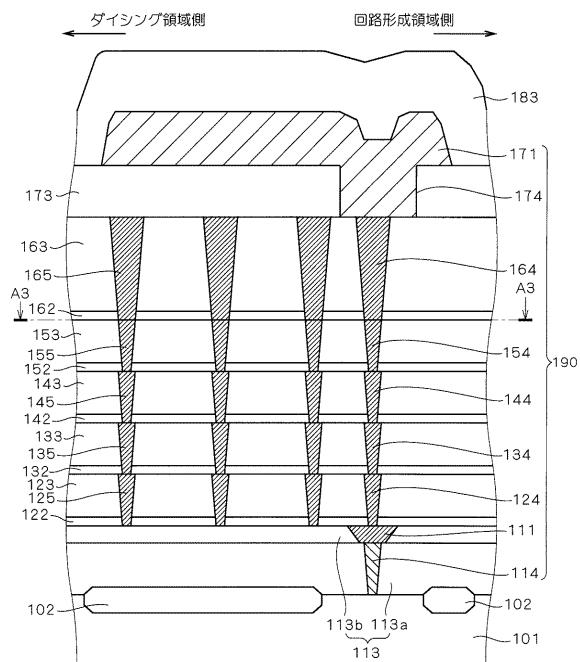

#### 【0077】

##### <実施の形態3>

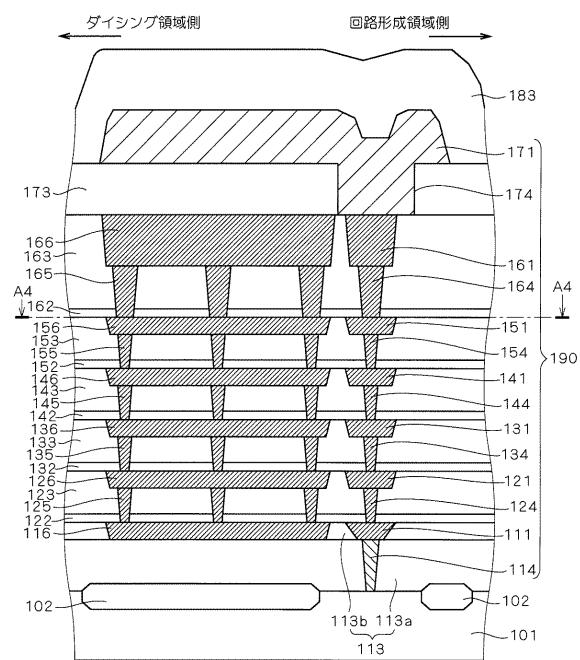

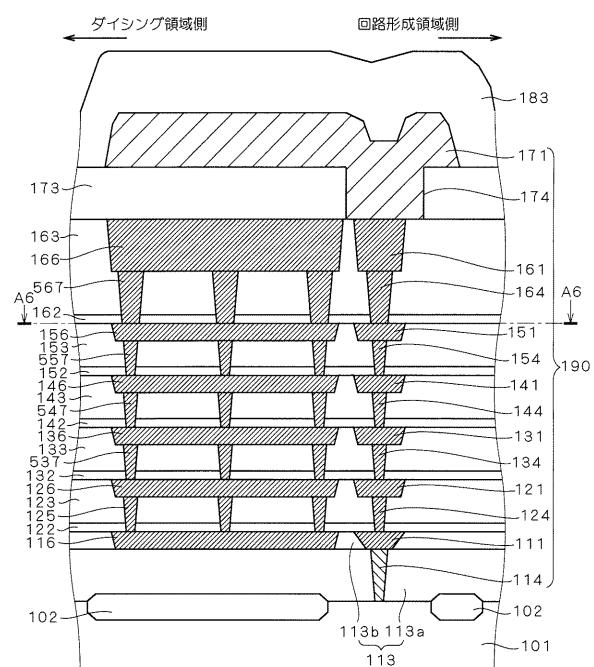

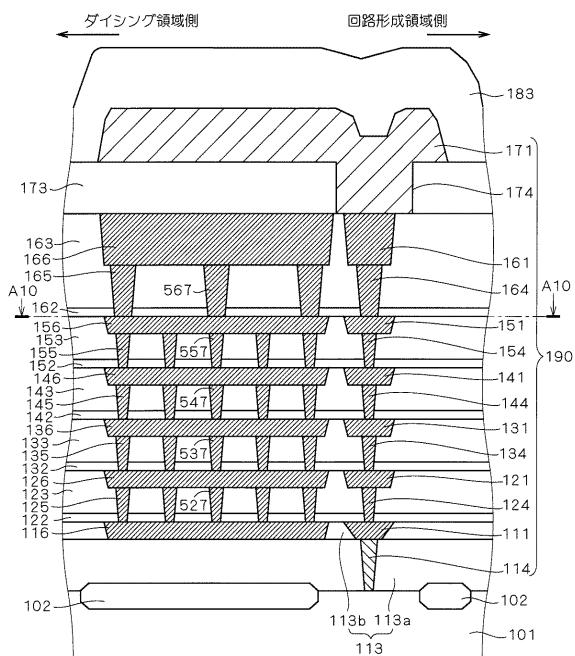

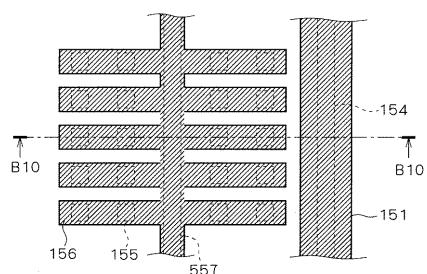

図19は、本実施の形態3に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図20は、図19のA3-A3線上面図に対応している。また図19は、図20のB3-B3線断面図に対応している。実施の形態1と同一の構成には同一の符号を付し、重複する説明は省略する。

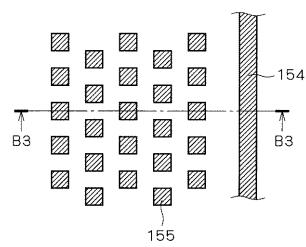

#### 【0078】

本実施の形態に係る半導体装置は、図20の上面図に示すように、ダミービア155の配列パターンが千鳥配置になっている。即ち、隣り合う列に形成されたダミービアが互いに半ピッチずれて形成されている。言い換えるとダミービア155は、平面視で複数の列に沿って配置され、隣り合う列に配置されたダミービア155は、交互に配置されることにより千鳥配置となっている。その他の層に形成されたダミービアも同様の配列になっている。製造方法は実施の形態1と同様であるので省略する。

10

#### 【0079】

以上のような構成を備えているので、実施の形態1と同様の効果を有する。また、実施の形態1においては、ダミービアが縦横に等間隔で並んでいたので、クラックがダミービア間を伝わり、シールリングに到達する可能性があった。本実施の形態では、ダミービアが上面からみて、千鳥配置されているので、クラックがダミービア間を伝わる可能性が低くなる。その結果、ダイシング時に発生するクラックの伝播をより抑制することができる。

20

#### 【0080】

##### <実施の形態4>

図21は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。実施の形態4は、実施の形態2と実施の形態3との組み合わせであって、実施の形態2又は実施の形態3と同一の構成には同一の符号を付し、重複する説明は省略する。

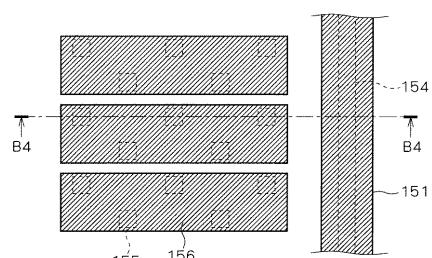

#### 【0081】

図22は、図21のA4-A4線での上面図に対応し、図21は、図22のB4-B4線断面図に対応している。図22に示すように、ダミービア155の配列パターンが千鳥配置になっている。即ち、隣り合う列に形成されたダミービア155が互いに半ピッチずれて形成されている。さらにダミービア155上には、ダミーメタル156が形成されている。その他の層も同様の構成となっている。また、製造方法は実施の形態2と同様であるので省略する。

30

#### 【0082】

以上説明したように、本実施の形態では、ダミービアが千鳥配置され、各層にダミーメタルが形成されている。そしてダミーメタルはダミービアを覆うように配置されている。その結果、ダイシング時に発生するクラックの伝播をさらに抑制することができる。また、ダミーメタルが形成されることでLow-k膜と拡散防止膜のストレスを緩和し、密着性を高めることができる。

40

#### 【0083】

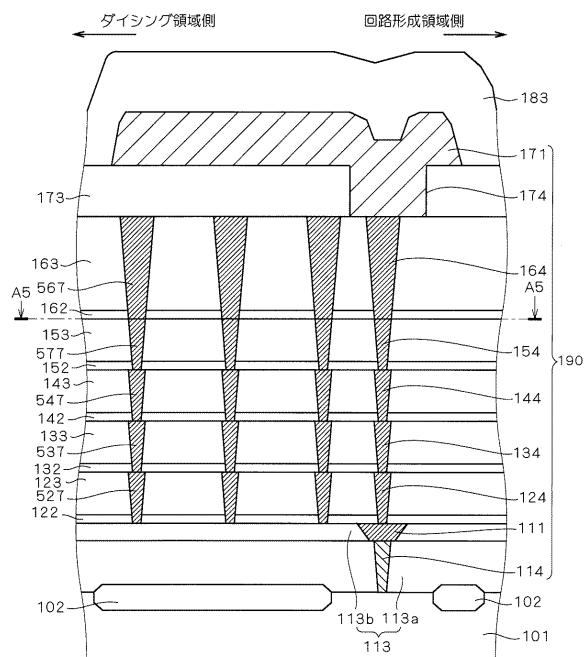

##### <実施の形態5>

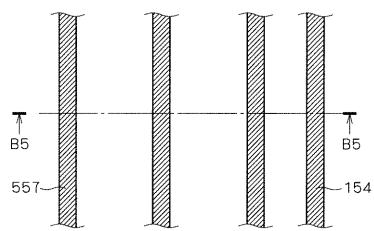

図23は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図24は、図23のA5-A5線の上面図に対応し、図23は、図24のB5-B5線断面図に対応している。

#### 【0084】

本実施の形態は、図24に示すように、ダミービア155に代えて、ダミースリットビア557が形成されている。ダミースリットビア557のスリット幅は、最小寸法で例えば0.14μmで形成されている。第2層から第4層の各層も同様の構成となっており、

50

ダミースリットビア 527, 537, 547 が形成されている。第6層目のダミースリットビア 567 は、0.28 μm のスリット幅で形成されている。

#### 【0085】

その他の構成は、実施の形態1と同様であり、同一の構成には同一の符号を付し、重複する説明は省略する。製造方法についても、ダミービアに代えてダミースリットビアを形成することを除いては実施の形態1と同様であるので省略する。

#### 【0086】

以上説明したように、本実施の形態では、ダイシング領域側にダミービアに代えてダミースリットビアが形成されている。ダイシング領域側にダミースリットビアを形成することで、ダミービアを形成したものに比べてダイシング時に発生するクラックの伝播を抑制することができる。ダミースリットを配置することにより、シールリング部 190 にクラックが伝播するのを防止できるので、回路形成領域の吸湿耐性を向上できる。

10

#### 【0087】

さらに、ダミースリットビアのようにスリット状の構造にすることで、ダミービアに比べて Low-k 膜の占有面積を減少することができる。そのため、Low-k 膜と拡散防止膜のストレスを緩和することができる。

#### 【0088】

また、ダミースリットビアを設けることにより、Low-k 膜と拡散防止膜との接触面積が小さくなるので、密着性を向上することができる。

#### 【0089】

20

##### <実施の形態6>

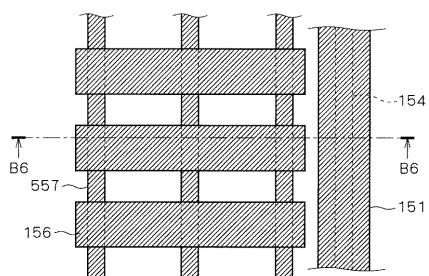

図25は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図26は、図25の A6-A6 線での上面図に対応し、図25は、図26の B6-B6 線断面図に対応している。

#### 【0090】

本実施の形態6は、実施の形態2と実施の形態5との組み合わせであって、実施の形態2又は実施の形態5と同一の構成には同一の符号を付し、重複する説明は省略する。

#### 【0091】

本実施の形態では、ダミースリットビアに加えて第1~6層の各層にダミーメタルがさらに形成されている。

30

#### 【0092】

図26に示すように、例えば第5層目に形成されたダミーメタル 156 は、ダミースリットビア 557 上に直交するように等間隔に形成されている。第2~4層、及び第6層も同様に、ダミースリットビア 527, 537, 547, 567 及びダミーメタル 126, 136, 146, 156, 166 が形成されている。第1層目については、ダミーメタル 116 のみが形成されている。

#### 【0093】

なお製造方法は、実施の形態2に示した製造方法と同様であるので詳細な説明は省略する。

#### 【0094】

40

ダミースリット上にダミーメタルを形成することで、ダイシング時に発生するクラックの伝播をダミースリットビアのみの構成に比べて抑制することができる。

#### 【0095】

また、ダミースリットビアにダミーメタルがさらに形成されることで Low-k 膜の占有面積が減少し、Low-k 膜と拡散防止膜のストレスを緩和し、密着性を高めることができる。

#### 【0096】

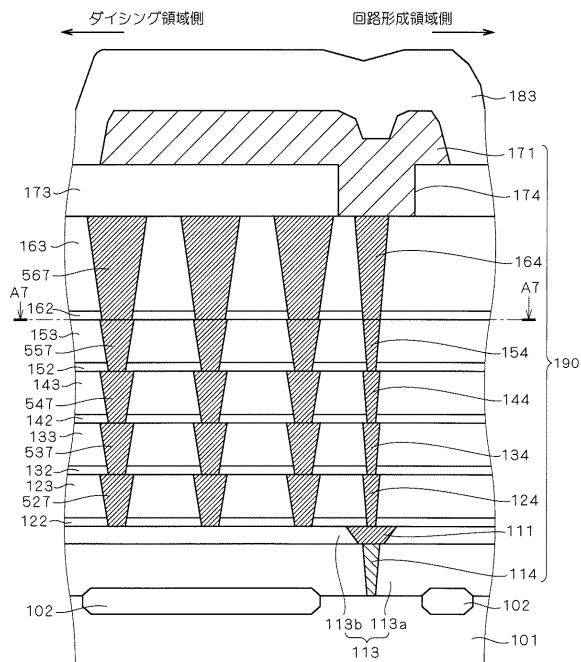

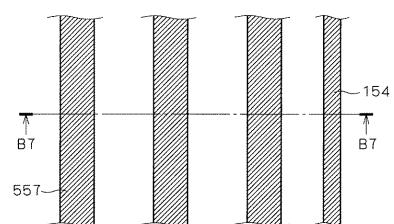

##### <実施の形態7>

図27は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図28は、図27の A7-A7 線の上面図に対応し、図

50

27は、図28のB7-B7線断面図に対応している。

**【0097】**

本実施の形態は、図28に示すようにダミースリットビア557の線幅を太く形成している。その他の構成は、実施の形態5と同様であり、同一の構成には同一の符号を付し、重複する説明は省略する。

**【0098】**

ダミースリットビアの線幅は、例えば $1\text{ }\mu\text{m}$ で形成されている。第2層目～第4層目も同様に線幅を太くしたダミースリットビア527, 537, 547が形成されている。第6層目には、例えば $2\text{ }\mu\text{m}$ の線幅のダミースリットビア567が形成されている。

**【0099】**

なお、製造方法は、ダミービアに代えてダミースリットビアを形成することを除いて、実施の形態1に示した製造方法と同様であるので省略する。

**【0100】**

以上のように、線幅が太く形成された太幅ダミースリットビア構造を用いることで、線幅が細い場合に比べてダイシング時に発生するクラックの伝播をより抑制することができる。

**【0101】**

また、太幅ダミースリットビアを形成することでLow-k膜の占有面積が減少する。そのため、Low-k膜と拡散防止膜のストレスを緩和することができる。

**【0102】**

さらに、ダミースリットビアと上層に形成された拡散防止膜との接触面積が、細幅のダミースリットビアを用いた場合に比べて大きくなるので、密着性を向上することができる。

**【0103】**

なお、ダミースリットビアの線幅は、 $1\text{ }\mu\text{m}$ に限らず、 $0.8\text{ }\mu\text{m} \sim 2\text{ }\mu\text{m}$ であれば同様の効果が得られる。より一般的には、各層に形成されるビア若しくは配線の設計上のビア径、配線幅で定義される最小寸法の5倍～20倍で形成されれば同様の効果を有する。但し、線幅に応じてエッティング条件や、ダミースリットビアを埋め込むためのCuメッキの膜厚等、製造工程の条件を最適化する必要がある。

**【0104】**

<実施の形態8>

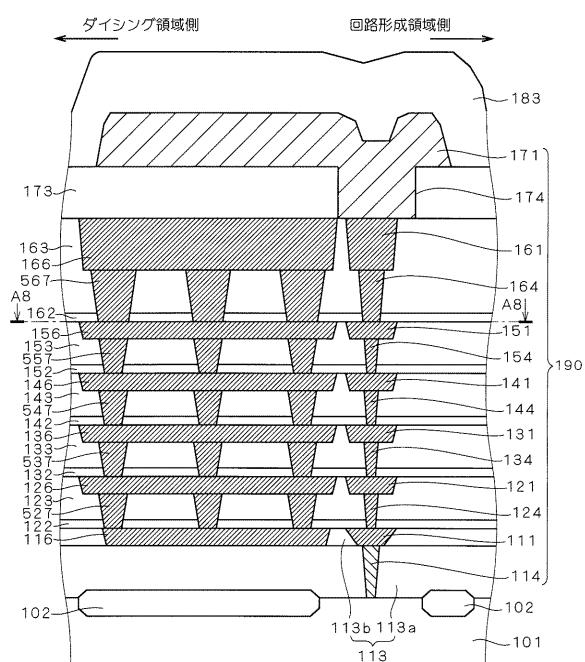

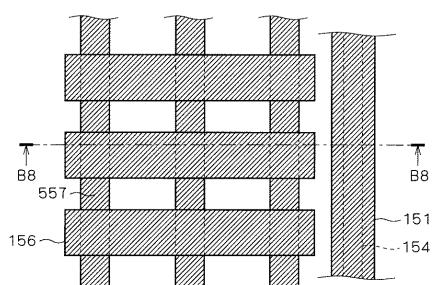

図29は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図30は、図29のA8-A8線の上面図に対応し、図30は、図29のB8-B8線断面図に対応している。

**【0105】**

本実施の形態は、実施の形態6においてダミースリットビアの線幅を太く形成したものである。ダミースリットビアの線幅は、例えば $1\text{ }\mu\text{m}$ で形成されている。その他の構成は、実施の形態6と同様であり、同一の構成には同一の符号を付し、重複する説明は省略する。

**【0106】**

以上のように、各層にダミーメタルを形成し、さらに線幅が太く形成された太幅ダミースリットビア構造を用いることで、線幅が細い場合に比べてダイシング時に発生するクラックの伝播をより抑制することができる。

**【0107】**

また、Low-k膜の占有面積が減少するので、Low-k膜と拡散防止膜のストレスを緩和することができる。

**【0108】**

さらに、Low-k膜と拡散防止膜との接触面積が、細い線幅のダミースリットビアを形成した場合に比べて小さくなるので、密着性を向上することができる。

**【0109】**

10

20

30

40

50

なお、ダミースリットビアの線幅は、 $1 \mu m$ に限らず、 $0.8 \mu m \sim 2 \mu m$ であれば同様の効果が得られる。より一般的には、各層に形成されるビア若しくは配線の設計上のビア径、配線幅で定義される最小寸法の5倍～20倍で形成されれば同様の効果を有する。但し、線幅に応じてエッティング条件や、ダミースリットビアを埋め込むためのCuメッキの膜厚等、製造工程の条件を最適化する必要がある。

#### 【0110】

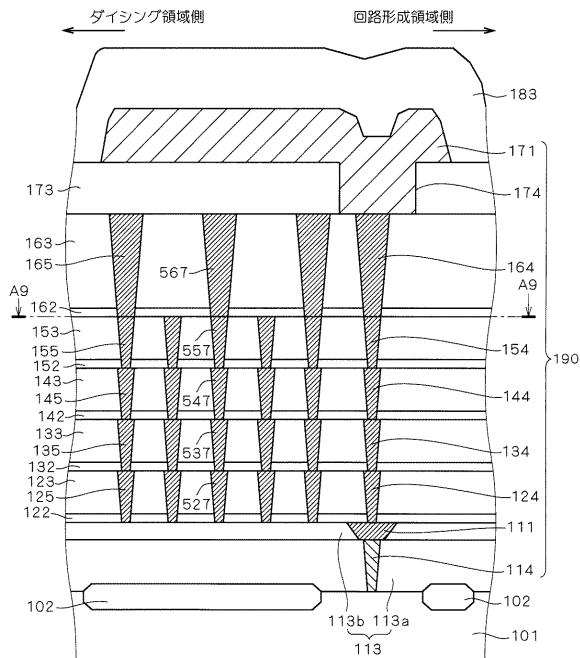

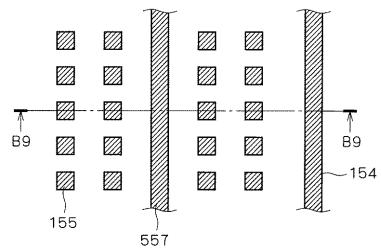

<実施の形態9>

図31は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図32は、図31のA9-A9線断面図に対応し、図31は図32のB9-B9線断面図に対応している。

10

#### 【0111】

本実施の形態9は、実施の形態1と実施の形態5との組み合わせであって、実施の形態1又は実施の形態5と同一の構成には同一の符号を付し、重複する説明は省略する。

#### 【0112】

本実施の形態では、ダイシング領域側の第2層から第6層の各層にダミービアとダミースリットビアが形成されている。

#### 【0113】

図32に示すように、ダミースリットビア557を挟んで両側にダミービア155が縦横に等間隔に形成されている。その他の層も同様の構造を備えている。

20

#### 【0114】

以上のような構造を備えているので、ダイシング時に発生するクラックがダミービア間を伝播しても、ダミースリットビアによりクラックの伝播を妨げることができる。そのため、実施の形態1に示した構造に比べてクラックの伝播を低減することができる。

#### 【0115】

また、ダミービアとダミースリットビアを組み合わせた構造を備えているので、ダミービアのみを備える実施の形態1の構造に比べてLow-k膜の占有面積を減少することができる。そのため、Low-k膜と拡散防止膜間のストレスを緩和することができる。

#### 【0116】

さらに、Low-k膜と拡散防止膜の接触面積が小さくなるので、密着性を向上することができる。

30

#### 【0117】

<実施の形態10>

図33は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図34は、図33のA10-A10線での上面図に対応し、図33は、図34のB10-B10線断面図に対応している。

#### 【0118】

本実施の形態10は、実施の形態2と実施の形態9との組み合わせであって、実施の形態2又は実施の形態9と同一の構成には同一の符号を付し、重複する説明は省略する。

#### 【0119】

図33に示すように、ダイシング領域側にダミースリットビア及びダミービアが形成され、第1層から第6層の各層にダミーメタルが形成されている。また図34に示すように、ダミースリットビア557の両側にダミービア155が縦横に等間隔に形成されている。そしてダミースリットビア557及びダミービア155を覆うようにダミーメタル156が形成されている。第2～4層、第6層の各層についても同様に構成されている。

40

#### 【0120】

なお、製造方法は、実施の形態2とほぼ同様であるので省略する。

#### 【0121】

ダミースリットビア及びダミービアを覆うように各層にダミーメタルを形成することで、実施の形態9の構造に比べてダイシング時に発生するクラックの伝播をさらに抑制することができる。

50

**【0122】**

また、ダミーメタルを設けることにより、Low-k膜が拡散防止膜に接する面積が減少する。その結果、Low-k膜と拡散防止膜間のストレスを緩和できる。さらに各層間の密着性を高めることができる。

**【0123】**

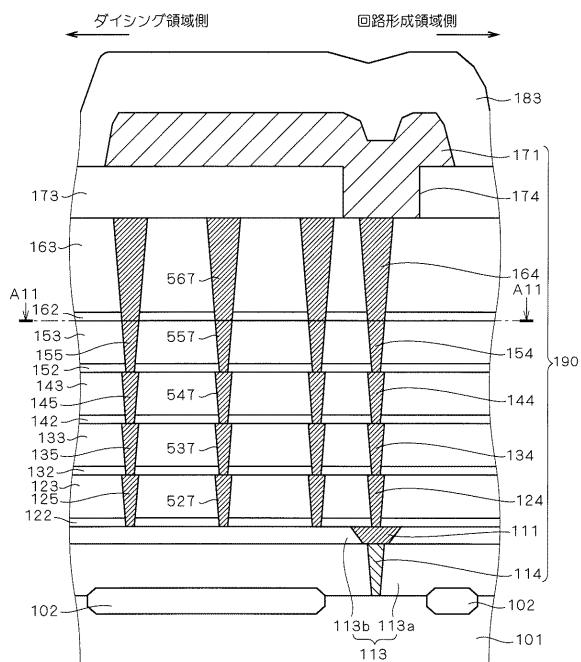

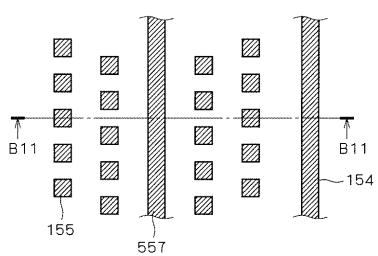

<実施の形態11>

図35は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。図36は、図35のA11-A11線上面図に対応する。また図35は、図36のB11-B11線断面図に対応している。

**【0124】**

本実施の形態では図36に示すように、ダミースリットビア557を挟んでダミービア155が形成されている。またダミービア155は千鳥配置されている。その他の各層についても同様の構成となっている。

**【0125】**

その他の構成は実施の形態9と同様であり、同一の構成には同一の符号を付し、重複する説明は省略する。また製造方法は、実施の形態1において説明した製造方法と同様のため省略する。

**【0126】**

本実施の形態では、ダミービアが千鳥配置されているので、ダミースリットビアに到達するクラックを減少することができる。そしてダミースリットビアを越えてクラックが進行した場合であっても、千鳥配置されたダミービアがダミースリットとシールリング部190の間にさらに形成されているので、クラックがシールリング部190に到達するのを、実施の形態9の構成に比べて低減することができる。

**【0127】**

<実施の形態12>

図37は、本実施の形態に係る半導体装置の構成を示す図であり、シールリングが形成された領域の拡大断面図である。本実施の形態12は、実施の形態2と実施の形態11との組み合わせであって、実施の形態2又は実施の形態11と同一の構成には同一の符号を付し、重複する説明は省略する。

**【0128】**

なお製造方法は、実施の形態2において説明した製造方法と同様であるので、説明は省略する。

**【0129】**

図38は、第5層目の上面図に対応している。図38に示すように、ダミースリットビア557及びダミービア155を覆うようにダミーメタル156が形成されている。また第2~4層、第6層の各層についても同様に構成されている。第1層目にはダミーメタル116のみが形成されている。

**【0130】**

本実施の形態は、ダミースリットビア及びダミービアを覆うようにダミーメタルを形成している。そのため、実施の形態11の構造に比べてダイシング時に発生するクラックの伝播をさらに抑制することができる。

**【0131】**

さらに、ダミーメタルを設けることにより、Low-k膜が拡散防止膜に接する面積が減少する。その結果、Low-k膜と拡散防止膜間のストレスを緩和できる。そして各層間の密着性も高めることができる。

**【図面の簡単な説明】****【0132】**

【図1】実施の形態1に係る半導体装置の構成を示す断面図である。

【図2】実施の形態1に係る半導体装置の構成を示す上面図である。

【図3】実施の形態1に係る半導体装置の製造工程を説明するための図である。

10

20

30

40

50

- 【図4】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図5】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図6】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図7】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図8】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図9】実施の形態1に係る半導体装置の製造工程を説明するための図である。

- 【図10】実施の形態2に係る半導体装置の構成を示す断面図である。

- 【図11】実施の形態2に係る半導体装置の構成を示す上面図である。

- 【図12】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図13】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図14】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図15】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図16】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図17】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図18】実施の形態2に係る半導体装置の製造工程を説明するための図である。

- 【図19】実施の形態3に係る半導体装置の構成を示す断面図である。

- 【図20】実施の形態3に係る半導体装置の構成を示す上面図である。

- 【図21】実施の形態4に係る半導体装置の構成を示す断面図である。

- 【図22】実施の形態4に係る半導体装置の構成を示す上面図である。

- 【図23】実施の形態5に係る半導体装置の構成を示す断面図である。

- 【図24】実施の形態5に係る半導体装置の構成を示す上面図である。

- 【図25】実施の形態6に係る半導体装置の構成を示す断面図である。

- 【図26】実施の形態6に係る半導体装置の構成を示す上面図である。

- 【図27】実施の形態7に係る半導体装置の構成を示す断面図である。

- 【図28】実施の形態7に係る半導体装置の構成を示す上面図である。

- 【図29】実施の形態8に係る半導体装置の構成を示す断面図である。

- 【図30】実施の形態8に係る半導体装置の構成を示す上面図である。

- 【図31】実施の形態9に係る半導体装置の構成を示す断面図である。

- 【図32】実施の形態9に係る半導体装置の構成を示す上面図である。

- 【図33】実施の形態10に係る半導体装置の構成を示す断面図である。

- 【図34】実施の形態10に係る半導体装置の構成を示す上面図である。

- 【図35】実施の形態11に係る半導体装置の構成を示す断面図である。

- 【図36】実施の形態11に係る半導体装置の構成を示す上面図である。

- 【図37】実施の形態12に係る半導体装置の構成を示す断面図である。

- 【図38】実施の形態12に係る半導体装置の構成を示す上面図である。

- 【符号の説明】

- 【0133】

111 配線層、114 Wプラグ、124, 134, 144, 154, 164 スリットビア、125, 135, 145, 155, 165 ダミービア、171 A1配線層、190 シールリング部。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図17】

【図15】

【図18】

【図16】

【図19】

【図20】

【図21】

【図22】

【図23】

527, 537, 547, 557, 567: ダモースリットビア

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

---

フロントページの続き

(56)参考文献 特開2004-153015(JP,A)

特開2000-150521(JP,A)

特開2003-045876(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 21/768

H01L 23/52

H01L 23/522