(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5948025号

(P5948025)

(45) 発行日 平成28年7月6日(2016.7.6)

(24) 登録日 平成28年6月10日(2016.6.10)

(51) Int.Cl.

F 1

G02F 1/13357 (2006.01)

G02F 1/13357

G02F 1/1368 (2006.01)

G02F 1/1368

請求項の数 5 (全 40 頁)

(21) 出願番号 特願2011-169937 (P2011-169937)

(22) 出願日 平成23年8月3日 (2011.8.3)

(65) 公開番号 特開2012-53463 (P2012-53463A)

(43) 公開日 平成24年3月15日 (2012.3.15)

審査請求日 平成26年7月11日 (2014.7.11)

(31) 優先権主張番号 特願2010-177025 (P2010-177025)

(32) 優先日 平成22年8月6日 (2010.8.6)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 烏海 聰志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 伊佐 敏行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 小林 俊久

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

透光性を有する一対の基板と、

前記一対の基板の間に少なくとも液晶素子を含む画素部と、

前記一対の基板の外側に照明部と、

前記一対の基板と前記照明部の間に第1の偏光部材と、

前記照明部の外側に反射部材と、

前記一対の基板を介して前記第1の偏光部材と反対側に第2の偏光部材と、

前記画素部の外側に設けられた第1の光センサと、

前記第2の偏光部材を介して前記一対の基板と対向して設けられた第2の光センサと、 10

を有し、

前記第1の光センサは外光の照度を検知する機能を有し、

前記第2の光センサは、前記外光及び前記照明部から前記画素部へ入射され前記画素部

から射出される偏光の色調を検知する機能を有し、

前記照明部は第1乃至第3の波長を有する光を射出することができる光源を有し、

前記第2の光センサで検知する前記画素部の色調によって前記照明部は前記第1乃至第

3の波長を有する光のいずれか一または複数を射出し、前記画素部の色調を補正する機能

を有し、

前記画素部の前記第2の光センサと重なる領域には、単色の静止画を表示することを特

徴とする液晶表示装置。

**【請求項 2】**

請求項 1において、

前記画素部はトランジスタを有し、

前記トランジスタは結晶領域を有する半導体を含むことを特徴とする液晶表示装置。

**【請求項 3】**

請求項 1または請求項 2において、

前記画素部はトランジスタを有し、

前記トランジスタは酸化物半導体を含むことを特徴とする液晶表示装置。

**【請求項 4】**

請求項 1乃至請求項 3のいずれか一において、

10

前記第 1 の光センサで検知する外光の照度によって用いる表示形式を反射型または透過型の一方とすることができる機能を有することを特徴とする液晶表示装置。

**【請求項 5】**

請求項 1乃至請求項 4のいずれか一において、

前記第 1 の光センサで検知する外光の照度によって用いる表示形式を反射型および透過型の両方とすることができる機能を有することを特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

液晶表示装置およびその作製方法に関する。

20

**【背景技術】****【0002】**

デジタルサイネージ等、屋外で使用するための液晶表示装置の開発が進められている。

**【0003】**

屋外での使用に好適な液晶表示装置として、外光を利用して画像を表示する反射型の液晶表示装置があり、さらに反射型の液晶表示装置にサイドライトを付加して、外光が不足した状況下でも画像を表示できるようにした液晶表示装置などもある（特許文献 1 参照）。

。

**【0004】**

さらに、外光がある場合には反射型として機能し、外光が不足している場合には透過型として機能する半透過型の液晶表示装置も提案されている（特許文献 2 参照）。

30

**【先行技術文献】****【特許文献】****【0005】**

【特許文献 1】特開 2000 - 98371 号公報

【特許文献 2】特開 2002 - 133907 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、従来の半透過型液晶表示装置では、各画素に透過型用の透光性画素電極と、反射型用の反射性画素電極とを設ける必要があり、各画素の開口率が低いという問題がある。

40

**【0007】**

さらに、屋外に設置された液晶表示装置は、晴天の時には直射日光が照射され、液晶表示装置自体が高温となる。特にアクティブマトリクス型の液晶表示装置に汎用されているアモルファスシリコン TFT (Thin Film Transistor) は、高温下で電気特性が変動してしまい、高温下での信頼性が低いという問題がある。

**【0008】**

そして、液晶材料も高温下や低温下などの厳しい環境下では、屈折率が低下するため、特定の波長の透過率が低減し、液晶表示装置の表示画像の色調が変化してしまうという問

50

題もある。

【0009】

そこで、本発明は、屋外でも使用可能であり、高精細で且つ色調変化の少ない液晶表示装置を提供することを課題とする。

【課題を解決するための手段】

【0010】

本発明の一態様は、外部が明るい場合には、外光を利用する反射型の液晶表示装置として機能し、外部からの光がない場合には、少なくとも光源および導光部材を有している照明部の射出光を利用する透過型の液晶表示装置として機能し、外部が薄暗いまたは暗い場合には、外光および照明部の射出光の両方を利用して画像を表示する液晶表示装置である。また、これらの切り替えは、該液晶表示装置に設けられた第1の光センサによって行われる。

【0011】

また、上記液晶表示装置は、液晶表示装置に設けられた第2の光センサによって表示画像の色調変化を検知し、該色調変化を補正するための光を照明部の光源から射出することができる。

【0012】

そして、上記液晶表示装置は、各画素に透過型用の透光性画素電極と、反射型用の反射性画素電極とを設ける必要がないために開口率を高めることができる。

【0013】

そこで、本発明の一態様は、透光性を有する一对の基板と、一对の基板の間に少なくとも液晶素子を含む画素部と、一对の基板の外側に設けられ少なくとも画素部に光を入射させる照明部と、一对の基板と照明部の間に設けられる第1の偏光部材と、照明部の外側に設けられる反射部材と、一对の基板を介して第1の偏光部材と反対側に設けられる第2の偏光部材と、画素部の外側に設けられる第1の光センサと、第2の偏光部材を介して一对の基板と対向して設けられる第2の光センサとを有し、第1の光センサは外光の照度を検知する機能を有し、第2の光センサは画素部から射出される偏光の色調を検知する機能を有する液晶表示装置である。

【0014】

また、上記液晶表示装置の画素部は、パッシブマトリクス型、またはアクティブマトリクス型であることを特徴とする液晶表示装置である。

【0015】

さらに、アクティブマトリクス型とする場合、画素電極の電位を制御するスイッチング素子は、複数の結晶領域を有する半導体または酸化物半導体を用いたトランジスタである。なお、酸化物半導体を用いる場合、該酸化物半導体は、非晶質な酸化物半導体でも複数の結晶領域を有する酸化物半導体膜でもよい。

【0016】

また、上記液晶表示装置において、液晶素子を含む画素部への光の入射効率や、画素部に表示される表示画像の輝度等を向上させるため、一对の基板と照明部を構成する導光部材との間に光学部材を有してもよい。

【発明の効果】

【0017】

本発明の一態様によれば、高精細且つ色調変化を補正することができ、温度特性が良好な液晶表示装置を提供することができる。また、温度特性が良好であることから屋外での使用に好適な液晶表示装置を提供できる。

【図面の簡単な説明】

【0018】

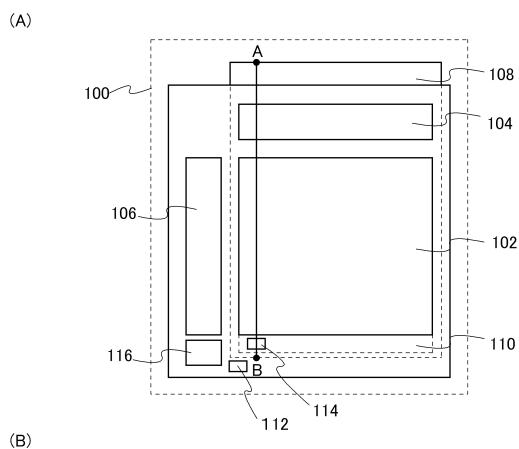

【図1】液晶表示装置の構成を説明するブロック図。

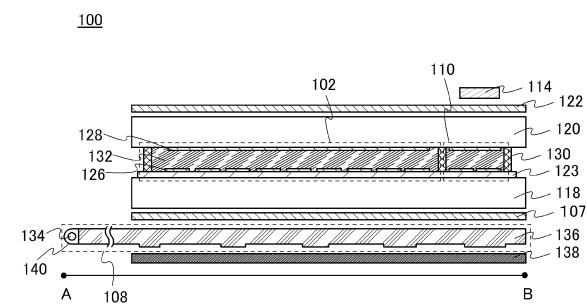

【図2】液晶表示装置の構成を説明する断面図。

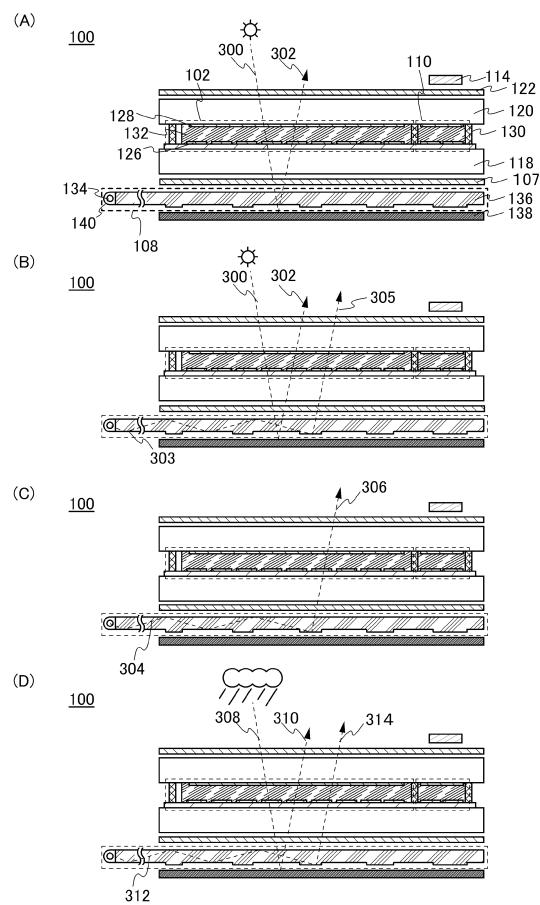

【図3】液晶表示装置における表示形式の違いを説明する断面図。

10

20

30

40

50

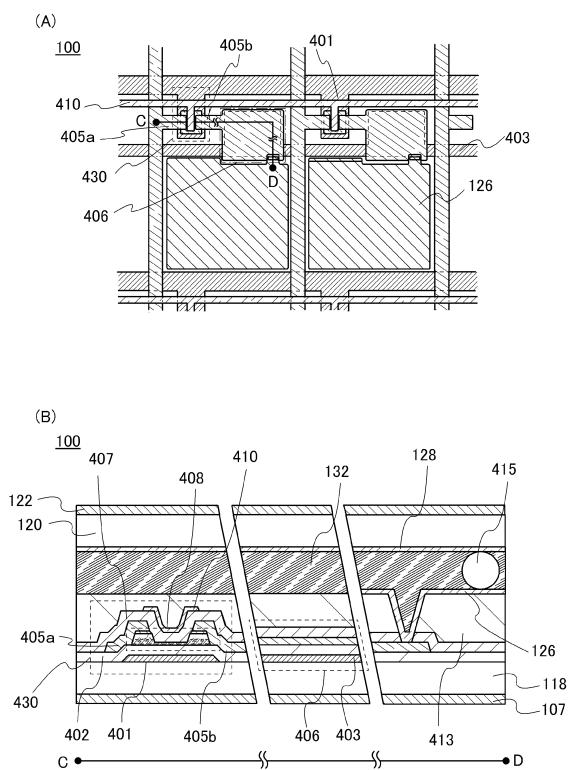

- 【図4】液晶表示装置の構成を説明する上面図および断面図。

- 【図5】液晶表示装置の構成を説明する上面図および断面図。

- 【図6】液晶表示装置を構成する薄膜トランジスタの作製方法を説明する断面図。

- 【図7】液晶表示装置を構成する薄膜トランジスタの作製方法を説明する断面図。

- 【図8】液晶表示装置を構成する薄膜トランジスタの作製方法を説明する断面図。

- 【図9】液晶表示装置を構成する薄膜トランジスタの作製方法を説明する上面図。

- 【図10】液晶表示装置を構成する薄膜トランジスタの作製方法を説明する断面図。

- 【図11】デジタルサイネージおよび電子書籍の一例を説明する図。

- 【図12】テレビジョン装置およびデジタルフォトフレームの一例を説明する図。

- 【図13】携帯型のコンピュータおよび携帯電話の一例を説明する図。

10

- 【図14】液晶表示装置を構成するトランジスタの電気特性結果を説明する図。

**【発明を実施するための形態】**

**【0019】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。また、便宜上、絶縁層は上面図には表さない場合がある。なお、各図面において示す各構成の、大きさ、層の厚さ、または領域は、明瞭化のために誇張されて表記している場合がある。従って、必ずしもそのスケールに限定されない。

20

**【0020】**

AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

**【0021】**

「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

30

**【0022】**

また、オン電流とは、薄膜トランジスタがオン状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、n型の薄膜トランジスタの場合には、ゲート電圧がトランジスタのしきい値電圧よりも高いときにソース電極とドレイン電極との間に流れる電流である。

**【0023】**

また、オフ電流とは、薄膜トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、n型の薄膜トランジスタの場合には、ゲート電圧が薄膜トランジスタのしきい値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

40

**【0024】**

**(実施の形態1)**

本実施の形態では、本発明の一態様である液晶表示装置100について、図1乃至図5を参照して説明する。

**【0025】**

本発明の一態様である液晶表示装置（主に画素部）は、パッシブマトリクス型およびアクティブラジオマトリクス型のどちらにおいても実施可能である。図1（A）は、アクティブラジオマトリクス型の構成を示すプロック図であり、図1（B）は、パッシブマトリクス型の構成を示すプロック図である。

**【0026】**

50

図1(A)において、アクティブマトリクス型の液晶表示装置100は、基板上に画素部102と、信号線駆動回路104と、走査線駆動回路106と、画素部102に光を入射させる照明部108と、モニタリング用画素部110と、外光の照度を検知する第1の光センサ112と、モニタリング用画素部110に設けられる表示画像の色調変化を検知する第2の光センサ114と、照明部108を制御する照明制御部(図示せず)に第1の光センサ112および第2の光センサ114からの信号をフィードバックさせるセンサ制御部116を有している。

#### 【0027】

モニタリング用画素部110は、画素部102と同様の構成とすればよく、センサ制御部116と信号のやりとりを行えるように配線や回路(駆動回路など)を適宜設ければよい。そこで、モニタリング用画素部110は、画素部102を作製する工程で作製することができる。また、モニタリング用画素部110には画素部102と同じ表示画像を表示する必要はなく、色調変化を検知できる画像を表示できればよいことから、例えば単色のみの静止画などを表示させればよい。

#### 【0028】

画素部102は、液晶素子を備えた複数の画素から構成されており、信号線駆動回路104は選択された各画素へのビデオ信号の入力を制御する回路である。また、走査線駆動回路106は、各画素のゲート電極に接続された走査線を制御する回路である。また、図1には図示していないが、1つの画素にスイッチング素子としてトランジスタ(主にTFT)が配置されている。本明細書中において、液晶素子とは、液晶の光学的変調作用によって光の透過または非透過を制御する素子であり、一対の電極、および液晶により構成される。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界または斜め方向の電界を含む)によって制御される。

#### 【0029】

なお、駆動回路は、論理回路部と、スイッチ部またはバッファ部とに大別されるが、駆動回路の構成については詳細を省略する。また、図1(A)では信号線駆動回路104および走査線駆動回路106を、画素部102が設けられる基板に作製する形態を示しているが、信号線駆動回路104および走査線駆動回路106の一部をIC等の半導体装置で実装してもよい。

#### 【0030】

図1(B)において、パッシブマトリクス型の液晶表示装置100は、基板上に画素部102と、セグメントドライバ103と、コマンドライバ105と、画素部102に光を入射させる照明部108と、モニタリング用画素部110と、外光の照度を検知する第1の光センサ112と、モニタリング用画素部110に設けられる表示画像の色調変化を検知する第2の光センサ114と、照明部108を制御する照明制御部(図示せず)に第1の光センサ112および第2の光センサ114からの信号をフィードバックさせるセンサ制御部116を有している。

#### 【0031】

モニタリング用画素部110は、画素部102と同様の構成とすればよく、センサ制御部116と信号のやりとりを行えるように配線や回路(駆動回路など)を適宜設ければよい。そこで、モニタリング用画素部110は、画素部102を作製する工程で作製することができる。また、モニタリング用画素部110には画素部102と同じ表示画像を表示する必要はなく、色調変化を検知できる画像を表示できればよいことから、例えば単色のみの静止画などを表示させればよい。

#### 【0032】

なお、セグメントドライバ103は表示データの出力を行う回路であり、コマンドライバ105はラインの選択を行っている回路である。これらドライバ回路は、スイッチ部またはバッファ部に大別されるが、ドライバ回路の構成については詳細を省略する。また、図1(B)ではセグメントドライバ103およびコマンドライバ105を、液晶表示装置100に作製する形態を示しているが、セグメントドライバ103およびコマンドライバ

10

20

30

40

50

105の一部をIC等の半導体装置で実装してもよい。

**【0033】**

図2は、図1(A)におけるA-B間ににおける断面図である。なお、信号線駆動回路104の断面は省略する。

**【0034】**

図2に示すように、液晶表示装置100のA-B間に、基板118と、対向基板120との間に、画素部102と、モニタリング用画素部110とが設けられており、基板118の下には、第1の偏光部材107と、第1の偏光部材107の下には照明部108と、照明部108の下には反射部材138とが設けられており、対向基板120の上には第2の偏光部材122と、モニタリング用画素部110と重畠して第2の光センサ114とが設けられている。

10

**【0035】**

画素部102およびモニタリング用画素部110は、基板118上に形成されたスイッチング素子を含むトランジスタ素子層123と、トランジスタ素子層123上に形成された画素電極126と、対向基板に接して形成された共通画素電極128と、シール材料130と、入射する光を透過または遮断する液晶132とで構成されている。また、図2には図示していないが、画素電極126と共通画素電極128との間の距離(セルギャップ)を一定に制御するためにスペーサが設けられている。スペーサとしては、ビーズスペーサや、絶縁層を選択的にエッティングすることで得られるスペーサ(ポストスペーサ)を用いることができる。

20

**【0036】**

照明部108には、少なくとも特定の波長を有する光を射出できる光源134と、光源134から射出される光を均一な面光源に変換させる導光部材136とが設けられている。

。

**【0037】**

また、照明部108の下には外光を反射させて画素部に入射させる反射部材138が設けられている。

**【0038】**

図2には図示していないが、液晶素子を含む画素部102への光の入射効率や、画素部102に表示される表示画像の輝度等を向上させるため、基板118と照明部108との間に、反射部材、拡散部材、プリズム、またはその他偏光部材など他の光学部材を適宜設けてもよい。さらに、これら光学部材は、板状またはフィルム状のものを用いることができるが、フィルム状のものを用いることで、液晶表示装置100を薄型化することができるため好ましい。また、本実施の形態では、光源134の照射効率を向上させるために反射シート140を設けるものとする。

30

**【0039】**

基板118および対向基板120は、透光性を有するものが好ましく、バリウムホウケイ酸ガラスやアルミニオホウケイ酸ガラスなどのガラス基板、石英基板、本液晶表示装置100の作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板などを用いることができる。また、基板118および対向基板120として、第3世代(550mm×650mm)、第3.5世代(600mm×720mm、または620mm×750mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1100mm×1300mm)、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)、第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)等のガラス基板を用いることができる。

40

**【0040】**

トランジスタ素子層123についての詳細は後述するが、トランジスタ素子層123に含まれるスイッチング素子(主にTFT)は、高温下でも、低温下でも動作する温度特性のよい半導体を用いることが好ましい。該半導体を用いたスイッチング素子は、100

50

近くの高温でもしきい値電圧の変動が少なく、信頼性が高いため、温度変化の大きな環境下においても高性能に動作する。温度特性のよい半導体の代表例としては、複数の結晶領域を持つ微結晶シリコンや、ポリシリコン等が好ましい。また、酸化物半導体も用いることができ、酸化物半導体としては、In-Ga-Zn系金属酸化物、およびIn-Sn-Zn系金属酸化物等がある。

#### 【0041】

画素電極126および共通画素電極128は酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、または酸化シリコンを含むインジウム錫酸化物等の透光性を有する導電性材料を用いて形成することができる。10

#### 【0042】

また、画素電極126および共通画素電極128は、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いる場合、シート抵抗が10000 /sq以下、波長550nmにおける透光率が70%以上の導電性組成物を用いることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

#### 【0043】

導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンもしくはその誘導体、ポリピロールもしくはその誘導体、ポリチオフェンもしくはその誘導体、またはアニリン、ピロールおよびチオフェンの2種以上の共重合体若しくはその誘導体などである。20

#### 【0044】

上記したように、液晶素子に含まれる液晶132の光学的変調作用は、液晶132にかかる電界（横方向の電界、縦方向の電界または斜め方向の電界を含む）によって制御される。液晶132の種類としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶（ライオトロピック液晶ともいう）、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶（PALC）、バナナ型液晶などがある。また、液晶素子の駆動モードとしては、TN（Twisted Nematic）モード、STN（Super Twisted Nematic）モード、IPS（In-Plane-Switching）モード、FFS（Fringe Field Switching）モード、MVA（Multi-domain Vertical Alignment）モード、PVA（Patterned Vertical Alignment）、TBA（Transverse Bend Alignment）モード、ASV（Advanced Super View）モード、ASM（Axially Symmetric aligned Micro-cell）モード、OCB（Optical Compensated Birefringence）モード、ECB（Electrically Controlled Birefringence）モード、FLC（Ferroelectric Liquid Crystal）モード、AFLC（Anti-Ferroelectric Liquid Crystal）モード、PDLC（Polymer Dispersed Liquid Crystal）モード、ゲストホストモード等を用いることができる。ただし、これに限定されず、液晶素子として様々なものを用いることができる。30

#### 【0045】

液晶132は、配向膜が不要なブルー相を示す液晶を用いて形成してもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は、狭い温度範囲でしか発現しないため、温度範囲を改善するために、カイラル剤を混合させた液晶組成物を用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が10μs～100μsと短く4050

、光学的に等方性であるため配向処理が不要であり、視野角依存性が小さい。

**【0046】**

液晶132を基板118と対向基板120の間で封止するためにシール材料130が設けられている。

**【0047】**

上記した照明部108における光源134には、冷陰極蛍光ランプ(CCFL)、LED(Light Emitting Diode)、EL(Electro Luminescence)素子などを用いることができる。また、画素部102の表示画像の色調変化を補正するために、白色の他にR(赤)、G(緑)、B(青)の光源も同時に設けておくことが好ましい。また、白色の光源のみを設けておく場合は、特定の波長を有する光のみを射出できるように光学フィルターを光源134と導光部材136の間に設ければよい。10

**【0048】**

光源134から射出される光を均一な面光源に変換するための導光部材136には、特殊加工されたアクリル板などを用いることができる。施される特殊加工には様々あるが、例えば、光源から遠ざかるにつれて凸部の長さが変化している凹凸加工がある。

**【0049】**

そして、上記したように照明部108の下には外光を反射させて画素部に入射させる反射部材138が設けられており、反射部材138には、鏡、反射性の高い金属層、光の散乱が可能な白色部材などを用いることができる。さらに、反射部材138の形状は画素部102の形状に合わせて適宜決めることができ、例えば、四角形状やドット状でもよい。またこれら反射部材138は、板状のものでも構わないがフィルム状のものを用いることで、液晶表示装置100を薄型化することができる。20

**【0050】**

基板118と照明部108の間に設けられる第1の偏光部材107および対向基板120上に設けられる第2の偏光部材122は、画素部102に入射する光および画素部102から射出される光を偏光できれば、特に制限はなく、例えば、ポリビニルアルコールなどの高分子で構成されている偏光板や偏光フィルムを用いることができる。また、本実施の形態では、第2の偏光部材122を対向基板120の外側(液晶132と反対側)に設けているが、対向基板の内側(液晶132側)に設けてもよい。30

**【0051】**

また、本発明の一態様である液晶表示装置は、白黒表示のみではなく、カラーフィルタを設けることで、カラー表示が可能となる。さらに、対向基板120には、ブラックマトリクスとして機能する遮蔽層を設けてもよい。

**【0052】**

外光の照度を検知する第1の光センサ112および、画素部に表示される画像の色調変化を検知する第2の光センサ114は、フォトダイオードを用いればよく、例えば、当該フォトダイオードはSi、CdS、またはInGaAsなどを用いたフォトダイオードを用いればよい。また、屋外での使用や温度特性を考慮すると、単結晶Siを使ったフォトダイオードが好ましい。40

**【0053】**

図3を用い、本発明の一態様である液晶表示装置100の表示形式について説明する。

**【0054】**

液晶表示装置100は、第1の光センサ112(図1参照)によって、外部からの光(外光)の照度を検知し、表示形式を切り替えることができる。例えば、図3(A)に示したように屋外が晴れて照度が高いときは、画像表示のために外光を利用する反射型として機能する。

**【0055】**

つまり、入射光300は、第2の偏光部材122、対向基板120、画素部102、基板118、第1の偏光部材107、照明部108を通り、反射部材138において反射さ50

れる。その反射光は上記と逆順で通り、第2の偏光部材122から射出される偏光302を観測者は視認する。この際、カラーフィルタを用いればカラー表示となり、用いなければ白黒（モノクロ）表示になる。

#### 【0056】

このような反射型の画像表示をすることで、液晶表示装置100（特に照明部108）を動作させる電力を省くことができ、消費電力を低減することができる。

#### 【0057】

さらに、晴れた屋外のような外光が強い環境下で液晶表示装置100を動作させると100 近い高温下で動作させることになる。そのため、液晶132が高温となり、液晶132の屈折率が室温での屈折率と異なってしまうことで、液晶表示装置100の表示画像に色調変化が生じてしまう。

10

#### 【0058】

色調変化が生じた場合、モニタリング用画素部110と重畳して設けられる第2のセンサ114は該色調変化を検知し、センサ制御部116は該色調変化を補正する信号を照明制御部（図示せず）に送る。具体的に、カラーフィルタを用いてカラー表示させる場合、100 近い高温下での動作について説明する。外光からの入射光300が反射部材138で反射され、画素部102から射出される光（偏光302）において、「青色が強い」という色調変化を第2のセンサ114が検知すると、センサ制御部116は、該色調変化を補正する光を射出する信号を照明制御部に送る。該信号を受けて、光源134は、該色調変化を補正する赤および緑の光（入射光303）を射出する。入射光303は、第2の偏光部材122から偏光305として射出され、液晶表示装置100の表示画像の色調のずれを補正する（図3（B）参照）。

20

#### 【0059】

夜間や暗い屋内など、反射型で表示するには照度が非常に低いことを第1の光センサ112が検知した場合、液晶表示装置100は、照明部108から射出される光を利用する透過型として機能する（図3（C）参照）。

#### 【0060】

光源134からの入射光304は、導光部材136で面光源に変換され、第1の偏光部材107、基板118を通り、画素部102に入射され、さらに対向基板120、第2の偏光部材122を通り、第2の偏光部材122から射出される偏光306を観測者は視認する。この際、カラーフィルタを用いればカラー表示となり、用いなければ白黒（モノクロ）表示になる。

30

#### 【0061】

さらに、曇りもしくは雨が降っている屋外、または薄暗い屋内など、外光の光量が少なく照度が低いことを第1の光センサ112が検知した場合、液晶表示装置100は、画像表示するために外光および光源134を利用する（図3（D）参照）。

#### 【0062】

つまり、観測者が視認する偏光は、偏光310および偏光314である。偏光310は、入射光308が、第2の偏光部材122、対向基板120、画素部102、基板118、第1の偏光部材107、および照明部108を通り、反射部材138において反射され、第2の偏光部材122から射出される偏光である。また、偏光314は、光源134からの入射光312が、導光部材136で面光源に変換され、第1の偏光部材107、基板118、画素部102、対向基板120、および第2の偏光部材122を通り、第2の偏光部材122から射出される偏光である。この際、カラーフィルタを用いればカラー表示となり、用いなければ白黒（モノクロ）表示となる。

40

#### 【0063】

また、表示画像の色調変化は、高温屋外環境下だけで起きるわけではなく、低温環境下でも生じる可能性がある。つまり、第2の光センサ114は、使用する場所、温度、または表示形式に関係なく、表示画像の色調変化を検知する。センサ制御部116は、該色調変化を補正する光を射出する信号を照明制御部に送る。該信号を受けて、光源134は、

50

該色調変化を補正するための光を射出する。したがって、光源 134 は白色の光を照射する光源と、補正のための光を照射する光源の 2 種類を備えておくとよい。さらに、補正するための光を照射する光源は、赤色、緑色および青色であるとさらによい。また、白色の光を照射する光源だけであっても、色調変化に合わせた最適な波長の光を光学フィルター(図示せず)で取り出し、照射する構成としてもよい。

#### 【0064】

ここで、液晶表示装置 100 をアクティブマトリクス型とした場合について、図 4 を用いて説明する。

#### 【0065】

図 4 (A) は、液晶表示装置 100 の上面図であり、2 画素分の画素を示している。

10

#### 【0066】

図 2 で説明したように、液晶表示装置 100 は、トランジスタ素子層 123 が設けられている基板 118 と、共通画素電極 128 が設けられた対向基板 120 との間に、トランジスタ素子層 123 が設けられている基板 118 と対向基板 120 とを固定するシール材料 130 によって、液晶が封止されている。また、図 4 (A) には、液晶 132、対向基板 120、第 1 の偏光部材 107 および第 2 の偏光部材 122 などは省略され図示されていないが、それぞれ、図 4 (B) で示すように設けられている。

#### 【0067】

図 4 (A)において、複数のソース配線(ソース電極 405a を含む)が互いに平行(図中上下方向に延伸)且つ互いに離間した状態で配置されている。複数のゲート配線(ゲート電極 401 を含む)は、ソース配線に略直交する方向(図中左右方向)に延伸し、且つ互いに離間するように配置されている。複数のソース配線は、信号線駆動回路 104(図 1 (A) 参照)に繋がっており、複数のゲート配線は走査線駆動回路 106(図 1 (A) 参照)に繋がっている。

20

#### 【0068】

また、容量配線 403 は、複数のゲート配線それぞれに隣接する位置に配置されており、ゲート配線に平行な方向、つまり、ソース配線に略直交する方向(図中左右方向)に延伸している。保持容量素子 406 は、図 4 (A) の 1 点鎖線で囲まれた箇所であり、ゲート絶縁膜を誘電体として、容量配線 403 とドレイン配線とで構成されている。また、保持容量素子 406 は、画素電極 126 とドレイン電極 405b に電気的に接続されている。また、容量配線 403 は走査線駆動回路 106(図 1 (A) 参照)に繋がっている。

30

#### 【0069】

画素電極 126 を駆動するトランジスタ 430 は、各画素の左上角に配置されている。画素電極 126 およびトランジスタ 430 は、マトリクス状に複数配置されている。

#### 【0070】

また、図 4 に示す画素構成に限定されず、容量配線を設けず、画素電極を、ゲート絶縁膜および他の絶縁膜を介して隣り合う画素のゲート配線と重畠させ、保持容量素子を形成してもよい。この場合、容量配線を省略することができ、画素における開口率を高めることができる。

#### 【0071】

アクティブマトリクス型液晶表示装置では、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

40

#### 【0072】

液晶表示装置の動画表示において、液晶分子自体の応答が遅いため、残像が生じる、または動画のぼけが生じるという問題がある。液晶表示装置の動画特性を改善するため、全面黒表示を 1 フレームおきに行う、所謂、黒挿入と呼ばれる駆動技術がある。

#### 【0073】

50

また、垂直同期周期数を1.5倍、好ましくは2倍以上にすることで応答速度を改善するとともに各フレーム内の分割された複数フィールド毎に書き込む階調を選択する、所謂、倍速駆動と呼ばれる駆動技術もある。

#### 【0074】

これらの駆動技術を組み合わせることによって、液晶表示装置の動画特性などの表示特性を従来よりも改善することができる。

#### 【0075】

図4(B)は、図4(A)のC-D間ににおける断面図である。また、図4(A)のC-D間に記してある波線箇所は、図4(B)において省略されている箇所である。

#### 【0076】

ここでは、トランジスタ430の構成について記述し、作製工程は後述する。トランジスタ430は逆スタガ型の薄膜トランジスタであり、基板118上に形成され、ゲート電極401と、ゲート絶縁膜402と、半導体層408と、ソース電極405aおよびドレイン電極405bを含む。

#### 【0077】

本明細書に開示する液晶表示装置に適用できるトランジスタの構造は特に限定されず、例えば、トップゲート構造、およびボトムゲート構造のスタガ型またはブレーナ型などを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、2つ形成されるダブルゲート構造もしくは3つ形成されるトリプルゲート構造であってもよい。また、チャネル領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有する、デュアルゲート型でもよい。なお、本実施の形態ではデュアルゲート型とする。

#### 【0078】

トランジスタ430を覆い、半導体層408に接する絶縁膜407、絶縁膜407に接するバックゲート電極410が設けられ、バックゲート電極410上に層間絶縁膜413が積層され設けられている。

#### 【0079】

また、保持容量素子406は、上記したように容量配線403とドレイン電極405bの間に誘電体としてゲート絶縁膜402が積層されている。容量配線403は、ゲート配線(ゲート電極401を含む)と同じ条件で形成することができるため、容量配線403は、ゲート電極401の作製時に形成される。つまり、トランジスタ430とは別に保持容量素子406を作製する必要がなく、トランジスタ430の作製工程で保持容量素子406も作製することができる。

#### 【0080】

トランジスタ430および保持容量素子406の上には層間絶縁膜413が設けられている。層間絶縁膜413を形成する方法は、特に限定されず、その材料に応じて、CVD法、スパッタリング法、スピニコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ロールコート、カーテンコート、ナイフコート等を用いることができる。

#### 【0081】

層間絶縁膜413をエッチング工程で開口し、画素電極126を設けてドレイン電極405bと電気的に接続させる。また、対向基板120には、共通画素電極128を設ける。画素電極126および共通画素電極128は、上記列挙した導電材料を用いてスパッタリング法などにより形成することができる。

#### 【0082】

液晶表示装置100はモノクロ表示またはカラー表示とすることができますが、フルカラー表示とする場合、カラーフィルタは、赤色(R)、緑色(G)、青色(B)を呈する材料から形成すればよく、モノクロ以外のモノカラー表示とする場合、少なくとも一つの色を呈する材料からカラーフィルタを形成すればよい。

#### 【0083】

10

20

30

40

50

カラーフィルタは、液晶132を挟持して固着される基板118と対向基板120の内側（液晶132側）に設けてもよいし、対向基板120の外側（液晶132と反対側）に設けてもよい。

#### 【0084】

カラーフィルタは別途独立して設けてもよいし、アクティブマトリクス型の液晶表示装置の場合、層間絶縁膜にカラーフィルタとしての機能を兼ねさせててもよい。例えば、液晶表示装置100であれば、図4(B)において、層間絶縁膜413に、カラーフィルタとして機能する有彩色の透光性樹脂層を用いることができる。

#### 【0085】

カラーフィルタとしての機能を兼ねた層間絶縁膜413を、トランジスタ素子層123が設けられた基板118上に形成する場合、微細なパターンの画素においても、画素領域と精密に位置を合わせることができる。また、カラーフィルタとしての機能を兼ねるため、液晶表示装置の作製工程の簡略化および低成本化を実現できる。さらに、液晶132に高分子安定化のための光照射工程が必要な場合、カラーフィルタによって対向基板120側から照射される光が吸収されないために、液晶132全体に均一に照射することができる。よって、光重合の不均一による液晶の配向乱れやそれに伴う表示ムラなどを防止することができる。

#### 【0086】

カラーフィルタとして用いることのできる有彩色の透光性樹脂としては、感光性、非感光性の有機樹脂を用いることができる。感光性の有機樹脂層を用いるとレジストマスク数を削減することができるため、工程が簡略化し好ましい。

#### 【0087】

有彩色は、黒、灰、白などの無彩色を除く色であり、カラーフィルタとして機能させるため、その着色された有彩色の光のみを透過する材料で形成される。有彩色としては、赤色、緑色、青色などを用いることができる。また、シアン、マゼンダ、イエロー（黄）などを用いてもよい。着色された有彩色の光のみを透過するとは、カラーフィルタにおいて透過する光は、該有彩色の光の波長にピークを有するということである。

#### 【0088】

カラーフィルタは、含ませる着色材料の濃度と光の透過率の関係に考慮して、最適な膜厚を適宜制御するとよい。

#### 【0089】

有彩色の色によって有彩色の透光性樹脂層の膜厚が異なる場合や、遮光層、トランジスタに起因する凹凸を有する場合は、可視光領域の波長の光を透過する（いわゆる無色透明）絶縁層を積層し、平坦化してもよい。平坦性を高めるとその上に形成される画素電極層などの被覆性も良好にし、且つ液晶素子のギャップ（厚さ）を均一にすることができるため、液晶表示装置の視認性を向上させ、高画質化させることが可能になる。

#### 【0090】

カラーフィルタを対向基板120の外側（液晶132と反対側）に設ける場合は、対向基板120に接着して設ければよい。

#### 【0091】

基板118と対向基板120を、液晶132を間に挟持させてシール材料130で固着する。液晶132は、上記列挙した種類を用いることができる。液晶132は、ディスペンサ法（滴下法）や、基板118と対向基板120を貼り合わせてから毛細管現象等を用いる注入法を用いればよい。また、配向膜を用いてラビング工程を行うことで、液晶132を配向させやすくすることができる。

#### 【0092】

また、画素電極126と共に画素電極128との間の距離（セルギャップ）を一定に制御するためにスペーサ415が設けられている。ここでは、ビーズスペーサを用いているが、絶縁層を選択的にエッチングすることで得られるスペーサ（ポストスペーサ）を用いてもよい。セルギャップは1μm以上20μm以下とすることが好ましい。なお、本明細

10

20

30

40

50

書においてセルギャップの厚さとは、液晶の厚さ（膜厚）の最大値とする。

**【0093】**

シール材料130としては、代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いることが好ましい。代表的には、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、光（代表的には紫外線）重合開始剤、熱硬化剤、フィラー、カップリング剤を含んでもよい。

**【0094】**

図4には図示しないが、第1の偏光部材107の外側には照明部108および反射部材138が備えられている。また、対向基板120の外側（液晶132と反対側）に第2の偏光部材122が設けられている。

10

**【0095】**

第1の偏光部材107および第2の偏光部材122の他に、位相差板（位相差フィルムも含む）、反射防止板（反射防止フィルムも含む）などの光学部材などを設けてもよい。

**【0096】**

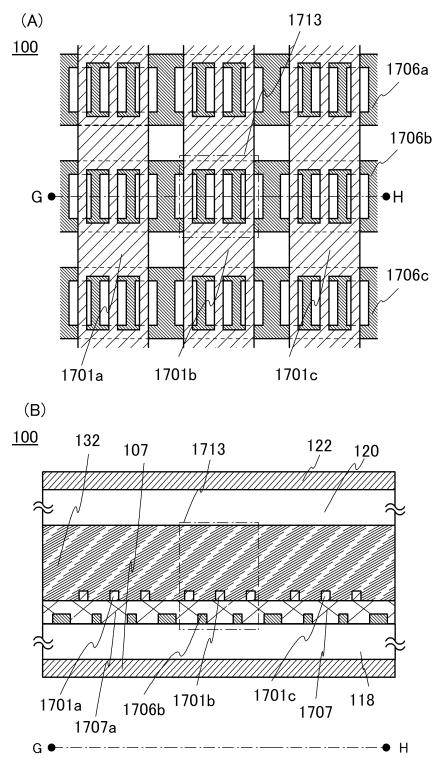

次に、液晶表示装置100をパッシブマトリクス型とした場合について、図5を用いて説明する。なお、パッシブマトリクス型とする場合、液晶表示装置100は、トランジスタ素子層123を設けていない構成となる。液晶表示装置100の上面図を図5（A）に、図5（A）における線G-Hの断面図を図5（B）に示す。また、図5（A）には、液晶132、対向基板120、第1の偏光部材107および第2の偏光部材122などは省略され図示されていないが、それぞれ、図5（B）で示すように設けられている。

20

**【0097】**

液晶表示装置100は、第1の偏光部材107が設けられた基板118と、第2の偏光部材122が設けられた対向基板120とが、液晶132を間に挟持して対向するよう固定されている。基板118と液晶132との間には、共通電極1706a、1706b、1706c、絶縁膜1707、および画素電極1701a、1701b、1701cが設けられている。画素電極1701a、1701b、1701cはコモンドライバ105（図1（B）参照）で制御され、共通電極1706a、1706b、1706cはセグメントドライバ103（図1（B）参照）で制御される。

**【0098】**

画素電極1701a、1701b、1701c、および共通電極1706a、1706b、1706cは開口パターンを有する形状であり、液晶素子1713の画素領域において長方形の開口（スリット）を有している。

30

**【0099】**

画素電極1701a、1701b、1701cと共に共通電極1706a、1706b、1706cとの間に電界を形成することで、液晶132を制御できる。この場合、液晶132には水平方向の電界が加わるため、当該電界を用いて液晶分子を制御できる。また、液晶分子を基板と平行な方向で制御できるため、視野角を広くすることができる。パッシブマトリクス型の液晶表示装置において、好ましいセルギャップは、アクティブマトリクス型の液晶表示装置におけるセルギャップと同様である。

**【0100】**

40

また、パッシブマトリクス型の液晶表示装置は、アクティブマトリクス型の液晶表示装置と同様に、モノクロ表示またはカラーフィルタを用いることでカラー表示とすることができます。カラーフィルタは対向基板120と液晶132との間に設けてもよく、対向基板120と第2の偏光部材122の間に設けてもよい。また、カラーフィルタは、上記した透光性樹脂を用いればよい。

**【0101】**

画素電極1701a、1701b、1701c、共通電極1706a、1706b、1706cは、上記列挙した導電性材料を用いればよい。

**【0102】**

図示していないが、上記アクティブマトリクス型の液晶表示装置100と同様に、セル

50

ギャップを保つためにスペーサ 415 を用いて、さらに、液晶 132 を封止するためにシール材料 130 を用いることができる。

**【0103】**

基板 118 の外側（液晶 132 と反対側）に第 1 の偏光部材 107 が、対向基板 120 の外側（液晶 132 と反対側）に第 2 の偏光部材 122 が設けられている。また、第 1 の偏光部材 107 および第 2 の偏光部材 122 の他に、位相差板（位相差フィルムも含む）、反射防止板（反射防止フィルムも含む）などの光学フィルムなどを設けてもよい。

**【0104】**

また、液晶表示装置 100 は、遮光層（ブラックマトリクス）を設ける構成としてもよい。

10

**【0105】**

遮光層は、液晶 132 を挟持して固着される一対の基板（基板 118 および対向基板 120）の内側（液晶 132 側）に設けてもよいし、一対の基板の外側（液晶 132 と反対側）に設けてもよい。

**【0106】**

一対の基板の内側に遮光層を設ける場合、遮光層は画素電極が設けられる基板 118 に形成してもよいし、対向基板 120 に形成してもよい。遮光層は別途独立して設けてもよく、アクティブマトリクス型の場合、トランジスタ素子層 123 が設けられる基板 118 上に遮光層としての機能を兼ねた層間絶縁膜 413 を設けてもよい。

20

**【0107】**

遮光層は、光を反射、または吸収し、遮光性を有する材料を用いる。例えば、黒色の有機樹脂を用いることができ、感光性または非感光性のポリイミドなどの樹脂材料に、顔料系の黒色樹脂やカーボンブラック、チタンブラック等を混合させて形成すればよい。また、遮光性の金属膜を用いることもでき、例えばクロム、モリブデン、ニッケル、チタン、コバルト、銅、タンクステン、またはアルミニウムなどを用いればよい。

**【0108】**

遮光層の形成方法は特に限定されず、材料に応じて、蒸着法、スパッタリング法、CVD 法などの乾式法、またはスピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）などの湿式法を用い、必要に応じてエッチング法（ドライエッティングまたはウェットエッティング）により所望のパターンに加工すればよい。

30

**【0109】**

遮光層を層間絶縁膜 413 の一部として用いる場合、黒色の有機樹脂を用いることが好ましい。遮光層は液晶表示装置において、トランジスタ素子層 123（特に、トランジスタの半導体層または画素電極 126 とのコンタクトホール）と重畳する領域、または画素間などに設けることが好ましい。

**【0110】**

遮光層を設けることにより、トランジスタ素子層 123（特に、トランジスタの半導体層）に入射する光を遮断でき、光入射によるトランジスタの電気特性の変動を抑制し、安定化することができる。また、遮光層は隣り合う画素への光漏れの防止や、コンタクトホール上に発生しやすい液晶の配向欠陥による光漏れ等の表示ムラを隠すことができる。よって、液晶表示装置 100 の高精細化、高信頼性化を図ることができる。

40

**【0111】**

以上より、高精細且つ色調変化を補正することができ、温度特性が良好な液晶表示装置を提供することができる。また、温度特性が良好であることから屋外での使用に好適な液晶表示装置を提供できる。なお、本実施の形態は、他の実施の形態および実施例に記載した構成と適宜組み合わせて実施することが可能である。

**【0112】**

**(実施の形態 2 )**

本実施の形態では、アクティブマトリクス型の液晶表示装置 100 に設けられ、トラン

50

ジスタ素子層123に含まれるトランジスタ430について説明する(図4(B)参照)。なお、トランジスタ430は逆スタガ型の薄膜トランジスタである。

#### 【0113】

トランジスタ素子層123は、高温下などでも動作するトランジスタ、つまり温度特性の良好なトランジスタを含むことから、トランジスタ430の半導体層408として、複数の結晶領域を有する半導体を用いる。複数の結晶領域を有する半導体としては、微結晶シリコン半導体および多結晶シリコン半導体などがある。また、シリコン半導体だけではなくゲルマニウム半導体でもよく、さらには酸化物半導体も用いることができる。なお、ここでの酸化物半導体は半導体特性を示す金属酸化物をいう。本実施の形態では、半導体層408に微結晶シリコン半導体を含むn型のトランジスタの作製工程を示す。

10

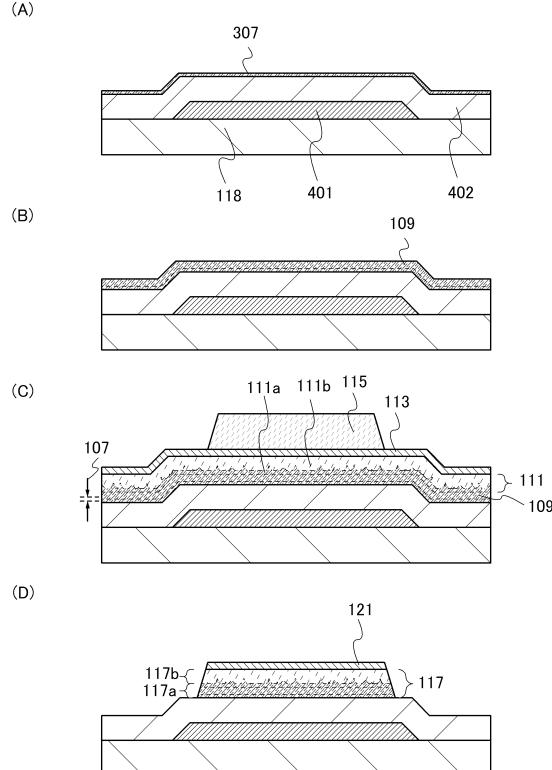

#### 【0114】

図6(A)に示すように、基板118上にゲート電極401を形成する。次に、ゲート電極401(第1のゲート電極ともいう。)を覆うゲート絶縁膜402を形成し、ゲート絶縁膜402の上に種結晶307を形成する。

#### 【0115】

基板118としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス合金等の金属の基板の表面に絶縁膜を設けたものを用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス若しくはアルミニケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、基板118のサイズに限定はなく、例えば上述のフラットパネルディスプレイの分野で汎用される第3世代乃至第10世代のガラス基板を用いることができる。

20

#### 【0116】

ゲート電極401は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム、ニッケル等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、AgPdCu合金、Al-Nd合金、Al-Ni合金などを用いてもよい。

#### 【0117】

例えば、ゲート電極401の積層構造としては、アルミニウム膜上にモリブデン膜を積層した二層構造、または銅膜上にモリブデン膜を積層した二層構造、または銅膜上に窒化チタン膜もしくは窒化タンタル膜を積層した二層構造、窒化チタン膜とモリブデン膜とを積層した二層構造、酸素を含む銅-マグネシウム合金膜と銅膜とを積層した二層構造、酸素を含む銅-マンガン合金膜と銅膜とを積層した二層構造、銅-マンガン合金膜と銅膜とを積層した二層構造などにすることが好ましい。三層の積層構造としては、タングステン膜または窒化タングステン膜と、アルミニウムとシリコンの合金膜またはアルミニウムとチタンの合金膜と、窒化チタン膜またはチタン膜とを積層した三層構造とすることが好ましい。電気的抵抗が低い膜上にバリア膜として機能する膜を積層することで、電気的抵抗を低くでき、且つ金属膜から半導体膜への金属元素の拡散を防止することができる。

30

#### 【0118】

ゲート電極401は、基板118上に、スパッタリング法または真空蒸着法を用いて、上記の金属材料により導電膜を形成し、該導電膜上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電膜をエッチングして形成することができる。また、ゲート電極401は、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、ゲート電極401と、基板118との密着性向上を目的として、上記の金属材料の窒化物膜を、基板118と、ゲート電極401との間に設けてもよい。本実施の形態では、基板118上に導電膜を形成し、フォトリソグラフィ工程により形成したレジストマスクを用いて、当該導電膜をエッチングしてゲート電極401を形成する。

40

#### 【0119】

50

なお、ゲート電極 401 の側面は、テーパ形状とすることが好ましい。これは、後の作製工程で、ゲート電極 401 上に形成される絶縁膜、半導体膜および配線が、ゲート電極 401 の段差箇所において切断されないためである。ゲート電極 401 の側面をテーパ形状にするためには、レジストマスクを後退させつつエッチングを行えばよい。

#### 【0120】

また、ゲート電極 401 を形成する工程により、上記実施の形態で説明したようにゲート配線（走査線）および容量配線 403 も同時に形成することができる。なお、ゲート配線とは画素を選択する配線をいい、容量配線 403 とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線および容量配線 403 の一方または双方はゲート電極 401 と別に設けてもよい。

10

#### 【0121】

ゲート絶縁膜 402 は、CVD 法またはスパッタリング法等を用いて、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、または窒化酸化アルミニウム膜を、単層または積層して形成する。

#### 【0122】

なお、ここでは、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) および水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、組成範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、シリコンが 25 ~ 35 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS および HFS を用いて測定した場合に、組成範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、シリコンが 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、シリコンおよび水素の含有比率が上記の範囲内に含まれるものとする。

20

#### 【0123】

なお、ゲート絶縁膜 402 を酸化シリコンまたは酸化窒化シリコン等の酸化絶縁膜により形成することで、薄膜トランジスタのしきい値電圧の変動を低減することができる。

30

#### 【0124】

ゲート絶縁膜 402 は、CVD 法またはスパッタリング法等を用いて形成することができる。ゲート絶縁膜 402 の CVD 法による形成工程において、グロー放電プラズマの生成は、3 MHz から 30 MHz、代表的には 13.56 MHz、27.12 MHz の HF 帯の高周波電力、または 30 MHz より大きく 300 MHz 程度までの VHF 帯の高周波電力、代表的には、60 MHz を印加することで行われる。また、1 GHz 以上のマイクロ波の高周波電力を印加することで行われる。なお、高周波電力がパルス状に印加されるパルス発振や、連続的に印加される連続発振とすることができます。また、HF 帯の高周波電力と、VHF 帯の高周波電力を重畠させることで、大面積基板においてもプラズマのムラを低減し、均一性を高めることができると共に、堆積速度を高めることができます。また、高周波数が 1 GHz 以上であるマイクロ波プラズマ CVD 装置を用いてゲート絶縁膜 402 を形成すると、ゲート電極と、ドレイン電極およびソース電極との間の耐圧を向上させることができるために、信頼性の高い薄膜トランジスタを得ることができる。

40

#### 【0125】

また、ゲート絶縁膜 402 として、有機シランガスを用いた CVD 法により酸化シリコン膜を形成することで、後に形成する半導体膜の結晶性を高めることができるため、薄膜トランジスタのオン電流および電界効果移動度を高めることができる。有機シランガスとしては、珪酸エチル (TEOS : 化学式 Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン (TMS : 化学式 Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン (TMCS : 化学式 Si(CH<sub>3</sub>)<sub>2</sub>O(CH<sub>2</sub>)<sub>2</sub>Si(CH<sub>3</sub>)<sub>2</sub>) などがある。

50

T S )、オクタメチルシクロテトラシロキサン( O M C T S )、ヘキサメチルジシラザン( H M D S )、トリエトキシシラン( SiH( OC<sub>2</sub>H<sub>5</sub>)<sub>3</sub> )、トリスジメチルアミノシラン( SiH( N( CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub> )等のシリコン含有化合物を用いることができる。

#### 【 0 1 2 6 】

種結晶 307 は、高い結晶性の混相粒を低い粒密度で形成する第 1 の条件で形成することができる。第 1 の条件としては、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を 50 倍以上 1000 倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を 133 Pa より大きく 13332 Pa 以下( 1 Torr より大きく 100 Torr 以下)とするのが好ましい。種結晶 307 には、混相粒と混相粒の間に隙間が存在している。なお、混相粒とは、非晶質半導体領域と、単結晶とみなせる微小結晶である結晶子とを有する。また、混相粒は双晶を有する場合もある。

#### 【 0 1 2 7 】

種結晶 307 の原料ガスとして、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを用いることで、種結晶 307 の結晶性を高めることができる。このため、薄膜トランジスタのオン電流および電界効果移動度が高まると共に、スループットを高めることができる。

#### 【 0 1 2 8 】

次に、図 6 ( B ) に示すように、種結晶 307 上に微結晶半導体膜 109 を形成する。微結晶半導体膜 109 は、種結晶 307 の混相粒の結晶を成長させて、混相粒間の隙間を埋める第 2 の条件を用いて形成することができる。第 1 の条件とは異なる第 2 の条件としては、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を 50 倍以上 1000 倍以下にして且つ処理室内の圧力を 133 Pa 以上 13332 Pa 以下( 1 Torr 以上 100 Torr 以下)とするのが好ましい。さらに好ましくは、第 2 の条件におけるシリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量の割合、および処理室内の圧力を、第 1 の条件より大きくすることである。また、第 2 の条件においては、シリコンまたはゲルマニウムを含む堆積性気体と水素との流量比を周期的に増減させながら形成してもよい。

#### 【 0 1 2 9 】

微結晶半導体膜 109 の原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを添加することで、種結晶 307 と同様に、微結晶半導体膜 109 の結晶性を高めることができる。このため、薄膜トランジスタのオン電流および電界効果移動度が高まると共に、スループットを高めることができる。

#### 【 0 1 3 0 】

次に、微結晶半導体膜 109 上に半導体膜 111 を形成する。半導体膜 111 は、微結晶半導体領域 111a および非晶質半導体領域 111b で構成される。

#### 【 0 1 3 1 】

微結晶半導体膜 109 を種結晶として、部分的に結晶成長させる条件( 結晶成長を抑制させる条件 ) で、微結晶半導体領域 111a および非晶質半導体領域 111b を有する半導体膜 111 を形成することができる。

#### 【 0 1 3 2 】

半導体膜 111 は、プラズマ C V D 装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを混合し、グロー放電プラズマにより形成する。窒素を含む気体としては、アンモニア、窒素、フッ化窒素、塩化窒素、クロロアミン、フルオロアミン等がある。グロー放電プラズマの生成は、種結晶 307 と同様にして行えばよい。

#### 【 0 1 3 3 】

このとき、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比は、種結晶 307 または微結晶半導体膜 109 と同様に微結晶半導体膜を形成する流量比を用い、さらに原料ガスに窒素を含む気体を添加することで、種結晶 307 および微結晶半導体膜 109 の堆積条件よりも、結晶成長を抑制することができる。具体的には、半導体膜 11

10

20

30

40

50

1の堆積初期においては、原料ガスに窒素を含む気体が含まれるため、部分的に結晶成長が抑制され、錐形状の微結晶半導体領域が成長すると共に、非晶質半導体領域が形成される。さらに、堆積中期または後期では、錐形状の微結晶半導体領域の結晶成長が停止し、非晶質半導体領域のみが堆積される。この結果、半導体膜111において、微結晶半導体領域111a、および欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体膜で形成される非晶質半導体領域111bを形成することができる。

## 【0134】

ここでは、半導体膜111を形成する条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量が10～2000倍、好ましくは10～200倍である。なお、通常の非晶質半導体膜を形成する条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量が0～5倍である。10

## 【0135】

また、半導体膜111の原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを添加することで、成膜速度を高めることができる。

## 【0136】

半導体膜111の厚さは、厚さ50～350nmとすることが好ましく、さらに好ましくは120～250nmとする。

## 【0137】

次に、半導体膜111上に、不純物半導体膜113を形成する。次に、不純物半導体膜113上にレジストマスク115を形成する(図6(C)参照)。20

## 【0138】

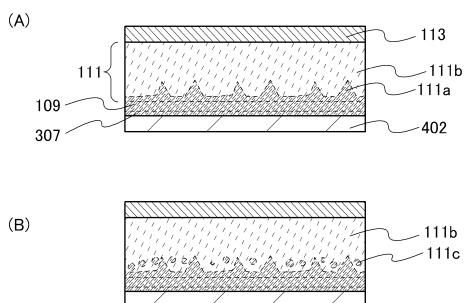

ここで、図6(C)に示すゲート絶縁膜402と、不純物半導体膜113との間の拡大図を、図7に示す。

## 【0139】

図7(A)に示すように、半導体膜111の微結晶半導体領域111aは凹凸状であり、凸部はゲート絶縁膜402から非晶質半導体領域111bに向かって、先端が狭まる(凸部の先端が鋭角である)凸状(錐形状)である。なお、微結晶半導体領域111aの形状は、ゲート絶縁膜402から非晶質半導体領域111bに向かって幅が広がる凸状(逆錐形状)であってもよい。30

## 【0140】

微結晶半導体領域111aの厚さ、即ち、ゲート絶縁膜402と微結晶半導体膜109との界面から、微結晶半導体領域111aの突起(凸部)の先端までの距離を、5nm以上310nm以下とすることで、薄膜トランジスタのオフ電流を低減することができる。

## 【0141】

また、二次イオン質量分析法によって計測される半導体膜111の酸素濃度プロファイルのピーク濃度は、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>未満とすることで、微結晶半導体領域111aの結晶性を高めることができると好ましい。また、二次イオン質量分析法によって計測される半導体膜111の窒素濃度プロファイルのピーク濃度は、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{20}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$  atoms/cm<sup>3</sup>以下である。40

## 【0142】

非晶質半導体領域111bは、窒素を有する非晶質半導体で形成される。窒素を有する非晶質半導体に含まれる窒素は、例えばNH基またはNH<sub>2</sub>基として存在してもよい。非晶質半導体としては、アモルファスシリコンを用いて形成する。

## 【0143】

窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、CPM(Constant photocurrent method)やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体である。即ち、窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、欠陥が少なく、50

価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体である。窒素を含む非晶質半導体は、価電子帯のバンド端における準位のテール(裾)の傾きが急峻であるため、バンドギャップが広くなり、トンネル電流が流れにくく。このため、窒素を含む非晶質半導体を微結晶半導体領域111aおよび不純物半導体膜113の間に設けることで、薄膜トランジスタのオフ電流を低減することができる。また、窒素を含む非晶質半導体を設けることで、薄膜トランジスタのオン電流および電界効果移動度を高めることができる。

## 【0144】

さらに、窒素を含む非晶質半導体は、低温フォトルミネッセンス分光によるスペクトルのピーク領域が、1.31eV以上1.39eV以下である。なお、微結晶半導体、代表的には微結晶シリコンを低温フォトルミネッセンス分光により測定したスペクトルのピーク領域は、0.98eV以上1.02eV以下であり、窒素を含む非晶質半導体は、微結晶半導体とは異なるものである。10

## 【0145】

また、非晶質半導体領域111bの他に、微結晶半導体領域111aにも、NH基またはNH<sub>2</sub>基を有してもよい。

## 【0146】

また、図7(B)に示すように、非晶質半導体領域111bに、粒径が1nm以上10nm以下、好ましくは1nm以上5nm以下の半導体混相粒111cを含ませることで、さらに薄膜トランジスタのオン電流および電界効果移動度を高めることができること。20

## 【0147】

ゲート絶縁膜402から非晶質半導体領域111bに向かって、先端が狭まる凸状(錐形状)の微結晶半導体は、微結晶半導体が堆積する条件で微結晶半導体膜を形成した後、結晶成長を抑制する条件で結晶成長させると共に、非晶質半導体を堆積することで、このような構造となる。

## 【0148】

半導体膜111の微結晶半導体領域111aは錐形状または逆錐形状であるため、オン状態でソース電極およびドレイン電極の間に電圧が印加されたときの縦方向(膜厚方向)における抵抗、即ち、半導体膜111の抵抗を下げる事が可能である。また、微結晶半導体領域111aと不純物半導体膜113との間に、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い、窒素を含む非晶質半導体を有するため、トンネル電流が流れにくくなる。以上の事から、本実施の形態に示す薄膜トランジスタは、オン電流および電界効果移動度を高めるとともに、オフ電流を低減することができる。30

## 【0149】

ここでは、半導体膜111の原料ガスに窒素を含む気体を含ませて、微結晶半導体領域111aおよび非晶質半導体領域111bを有する半導体膜111を形成したが、半導体膜111の他の形成方法として、微結晶半導体膜109の表面を窒素を含む気体に曝して、微結晶半導体膜109の表面に窒素を吸着させた後、シリコンまたはゲルマニウムを含む堆積性気体および水素を原料ガスとして堆積させることで、微結晶半導体領域111aおよび非晶質半導体領域111bを有する半導体膜111を形成することができる。40

## 【0150】

不純物半導体膜113は、リンが添加されたアモルファスシリコン、リンが添加された微結晶シリコン等で形成する。また、リンが添加されたアモルファスシリコンおよびリンが添加された微結晶シリコンの積層構造とすることもできる。なお、薄膜トランジスタとして、p型の薄膜トランジスタを形成する場合は、不純物半導体膜113は、ボロンが添加された微結晶シリコン、ボロンが添加されたアモルファスシリコン等で形成する。なお、半導体膜111と、後に形成するソース電極405aおよびドレイン電極405bがオームик接触である場合は、不純物半導体膜113を形成しなくともよい。

## 【0151】

1020304050

不純物半導体膜 113 は、プラズマ CVD 装置の反応室内において、シリコンを含む堆積性気体と、水素と、ホスフィン（水素希釈またはシラン希釈）とを混合し、グロー放電プラズマにより形成する。これにより、リンが添加されたアモルファスシリコン、またはリンが添加された微結晶シリコンが形成される。なお、p 型の薄膜トランジスタを作製する場合は、不純物半導体膜 113 として、ホスフィンの代わりに、ジボランを用いて、グロー放電プラズマにより形成すればよい。

#### 【0152】

また、不純物半導体膜 113 を、リンが添加された微結晶シリコン、またはボロンが添加された微結晶シリコンで形成する場合は、半導体膜 111 と、不純物半導体膜 113 の間に、微結晶半導体膜、代表的には微結晶シリコン膜を形成することで、界面の特性を向上させることができる。この結果、不純物半導体膜 113 と、半導体膜 111 との界面に生じる抵抗を低減することができる。この結果、薄膜トランジスタのソース領域、半導体膜、およびドレイン領域を流れる電流量を増加させ、薄膜トランジスタのオン電流および電界効果移動度を向上させることが可能となる。10

#### 【0153】

レジストマスク 115 はフォトリソグラフィ工程により形成することができる。

#### 【0154】

次に、レジストマスク 115 を用いて、種結晶 307、微結晶半導体膜 109、半導体膜 111、および不純物半導体膜 113 をエッティングする。この工程により、種結晶 307、微結晶半導体膜 109、半導体膜 111、および不純物半導体膜 113 を素子毎に分離し、島状の半導体積層体 117、および島状の不純物半導体膜 121 を形成する。なお、半導体積層体 117 は、微結晶半導体領域 117a および非晶質半導体領域 117b を有する。微結晶半導体領域 117a は、種結晶 307、微結晶半導体膜 109、および半導体膜 111 の微結晶半導体領域 111a を含む。非晶質半導体領域 117b は、半導膜 111 の非晶質半導体領域 111b を含む。この後、レジストマスク 115 を除去する（図 6 (D) 参照）。20

#### 【0155】

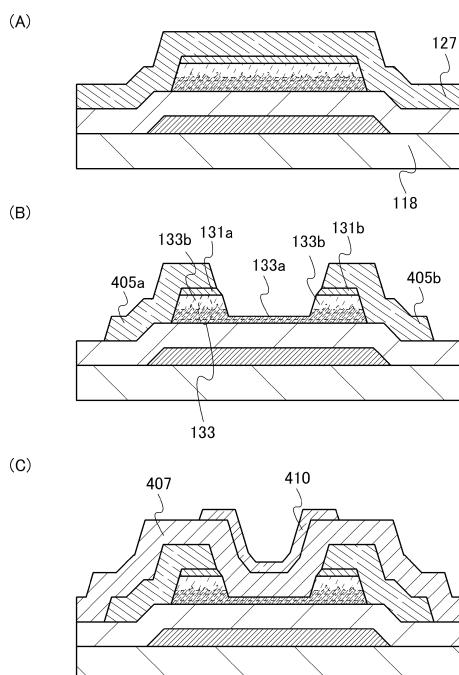

次に、不純物半導体膜 121 上に導電膜 127 を形成する（図 8 (A) 参照）。導電膜 127 は、ゲート電極 401 として機能する導電膜と同様にして形成することができる。

#### 【0156】

次に、フォトリソグラフィ工程によりレジストマスクを形成し、該レジストマスクを用いて導電膜 127 をエッティングして、ソース電極 405a およびドレイン電極 405b を形成する（図 8 (B) 参照）。導電膜 127 のエッティングはドライエッティングまたはウェットエッティングを用いることができる。なお、ソース電極 405a およびドレイン電極 405b は、ソース配線およびドレイン配線（信号線）としても機能する。ただし、これに限定されず、信号線、ソース電極およびドレイン電極は別に設けてもよい。30

#### 【0157】

次に、不純物半導体膜 121 および半導体積層体 117 の一部をエッティングして、ソース領域およびドレイン領域として機能する一対の不純物半導体膜 131a、131b を形成する。また、微結晶半導体領域 133a および一対の非晶質半導体領域 133b を有する半導体積層体 133 を形成する。このとき、微結晶半導体領域 133a が露出されるよう半導体積層体 117 をエッティングすることで、ソース電極 405a およびドレイン電極 405b で覆われる領域では微結晶半導体領域 133a および非晶質半導体領域 133b が積層され、ソース電極 405a およびドレイン電極 405b で覆われず、且つゲート電極と重なる領域においては、微結晶半導体領域 133a が露出する半導体積層体 133 となる。40

#### 【0158】

ここでは、ドライエッティングを用いているため、ソース電極 405a、ドレイン電極 405b の端部と、不純物半導体膜 131a、131b の端部とが揃っているが、導電膜 127 をウェットエッティングし、不純物半導体膜 121 をドライエッティングすると、ソース

電極 405a、ドレイン電極 405b の端部と、不純物半導体膜 131a、131b の端部とがずれ、断面において、ソース電極 405a、ドレイン電極 405b の端部が、不純物半導体膜 131a、131b の端部より内側に位置する。

#### 【0159】

上記エッティング工程の後、さらに、微結晶半導体領域 133a および非晶質半導体領域 133b の表面にドライエッティングを行ってもよい。ドライエッティングの条件は、露出している微結晶半導体領域 133a および非晶質半導体領域 133b にダメージが入らず、且つ微結晶半導体領域 133a および非晶質半導体領域 133b に対するエッティング速度が低い条件を用いる。つまり、露出している微結晶半導体領域 133a および非晶質半導体領域 133b 表面にほとんどダメージを与えず、且つ露出している微結晶半導体領域 133a および非晶質半導体領域 133b の厚さがほとんど減少しない条件を用いる。エッティングガスとして、代表的には  $\text{Cl}_2$ 、 $\text{CF}_4$ 、または  $\text{N}_2$  等を用いる。また、エッティング方法は特に限定はなく、誘導結合型プラズマ (ICP: Inductively Coupled Plasma) 方式、容量結合型プラズマ (CCP: Capacitively Coupled Plasma) 方式、電子サイクロトン共鳴プラズマ (ECR: Electron Cyclotron Resonance) 方式、反応性イオンエッティング (RIE: Reactive Ion Etching) 方式等を用いることができる。10

#### 【0160】

次に、微結晶半導体領域 133a および非晶質半導体領域 133b の表面にプラズマ処理、代表的には水プラズマ処理、酸素プラズマ処理、アンモニアプラズマ処理、窒素プラズマ処理、酸素および水素の混合ガスによるプラズマ処理等を行う。20

#### 【0161】

水プラズマ処理は、水蒸気 ( $\text{H}_2\text{O}$  蒸気) に代表される、水を主成分とするガスを反応空間に導入し、プラズマを生成して、行うことができる。この後、レジストマスクを除去する。なお、当該レジストマスクの除去は、不純物半導体膜 121 および半導体積層体 117 のドライエッティング前に行ってもよい。

#### 【0162】

また、微結晶半導体領域 133a および非晶質半導体領域 133b にダメージを与えない条件で更なるドライエッティングを行うことで、露出した微結晶半導体領域 133a および非晶質半導体領域 133b 上に存在する残渣などの不純物を除去することができる。そして、該ドライエッティングに続けて水プラズマ処理を行うことで、レジストマスクの残渣を除去すると共に、微結晶半導体領域 133a の欠陥を低減することができる。さらに、プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁を確実なものにすることができ、完成する薄膜トランジスタのオフ電流を低減し、電気的特性のばらつきを低減することができる。30

#### 【0163】

なお、図 8 (A) および図 8 (B)において、上記の工程とは異なる方法を用いてもよく、例えば、フォトリソグラフィ工程によりレジストマスクを導電膜 127 上に形成し、当該レジストマスクを用いて導電膜 127 をエッティングして、ソース電極 405a およびドレイン電極 405b を形成する。次に、不純物半導体膜 121 をエッティングして、ソース領域およびドレイン領域として機能する一対の不純物半導体膜 131a、131b を形成する。この際、半導体積層体 117 の一部がエッティングされる場合もある。次に、レジストマスクを除去した後、半導体積層体 117 の一部をエッティングして、微結晶半導体領域 133a および一対の非晶質半導体領域 133b を有する半導体積層体 133 を形成してもよい。40

#### 【0164】

この結果、レジストマスクを除去する工程において、微結晶半導体領域 117a が非晶質半導体領域 117b に覆われているため、微結晶半導体領域 117a が剥離液、およびレジストの残渣物に触れることがない。また、レジストマスクを除去した後、ソース電極50

405aおよびドレイン電極405bを用いて、非晶質半導体領域117bをエッチングして、微結晶半導体領域133aを露出する。このため、剥離液、およびレジストマスクの残渣物に触れた非晶質半導体領域は、バックチャネルには残存しない。この結果、バックチャネルに残存した剥離液、およびレジストマスクの残渣物によるリーク電流が発生しないため、薄膜トランジスタのオフ電流をより低減することができる。

#### 【0165】

以上の工程により高温下などでも動作する、つまり温度特性の良好なシングルゲート型の薄膜トランジスタを作製することができる。

#### 【0166】

次に、半導体積層体133およびソース電極405aおよびドレイン電極405b上に絶縁膜407（第2のゲート絶縁膜ともいう。）を形成する。絶縁膜407は、ゲート絶縁膜402と同様に形成することができる。

10

#### 【0167】

次に、絶縁膜407上にバックゲート電極410（第2のゲート電極ともいう。）を形成する（図8（C）参照）。以上の工程により、デュアルゲート型の薄膜トランジスタを作製することができる。

#### 【0168】

バックゲート電極410は、ゲート電極401と同様にして形成することができる。また、バックゲート電極410は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を用いて形成してもよい。

20

#### 【0169】

また、バックゲート電極410は、透光性を有する導電性高分子（導電性ポリマーともいう。）を含む導電性組成物を用いて形成することができる。バックゲート電極410は、シート抵抗が10000 / sq以下であって、且つ波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

#### 【0170】

30

導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンもしくはその誘導体、ポリピロールもしくはその誘導体、ポリチオフェンもしくはその誘導体、またはアニリン、ピロールおよびチオフェンから選択される2種以上モノマーの共重合体等が挙げられる。

#### 【0171】

バックゲート電極410は、スパッタリング法により、上記材料のいずれかを用いた導電膜を形成した後、フォトリソグラフィ工程によって形成したレジストマスクを用いて該導電膜をエッチングすることで、形成できる。また、透光性を有する導電性高分子を含む導電性組成物を塗布法または印刷法で形成し、焼成することでも得られる。

#### 【0172】

40

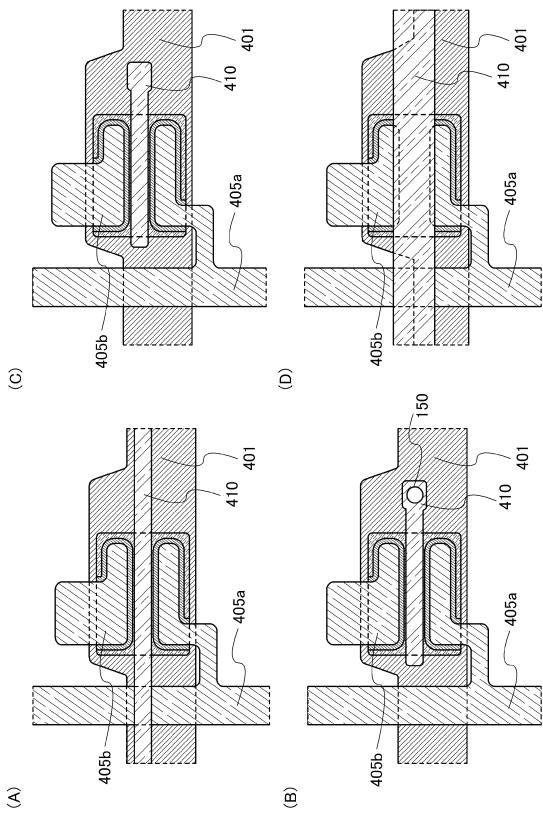

次に、薄膜トランジスタの上面図である図9を用いて、バックゲート電極の形状を説明する。

#### 【0173】

図9（A）に示すように、バックゲート電極410は、ゲート電極401と平行に形成することができる。この場合、バックゲート電極410に印加する電位と、ゲート電極401に印加する電位とを、それぞれ任意に制御することが可能である。このため、薄膜トランジスタのしきい値電圧を制御することができる。また、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜402側、および絶縁膜407側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

#### 【0174】

50

また、以下の3パターンについては上記実施の形態では図示していないが、図9(B)に示すように、バックゲート電極410は、ゲート電極401に接続させることができる。即ち、ゲート絶縁膜402および絶縁膜407に形成した開口部150において、ゲート電極401およびバックゲート電極410が接続する構造とすることができます。この場合、バックゲート電極410に印加する電位と、ゲート電極401に印加する電位とは、等しい。この結果、半導体膜において、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜402側、および絶縁膜407側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

#### 【0175】

また、図9(C)に示すように、バックゲート電極410は、ゲート電極401と接続せず、フローティングでもよい。バックゲート電極410に電圧を印加せずとも、チャネル領域が、微結晶半導体領域のゲート絶縁膜402側、および絶縁膜407側に形成されるため、薄膜トランジスタのオン電流を高めることができる。10

#### 【0176】

さらには、図9(D)に示すように、バックゲート電極410は、絶縁膜407を介してソース電極405aおよびドレイン電極405bと重畠してもよい。ここでは、図9(A)に示す構造のバックゲート電極410を用いて示したが、図9(B)および図9(C)に示すバックゲート電極410も同様にソース電極405aおよびドレイン電極405bと重畠してもよい。20

#### 【0177】

本実施の形態に示すシングルゲート型の薄膜トランジスタおよびデュアルゲート型の薄膜トランジスタは、混相粒の隙間を低減することで結晶性を高めた微結晶半導体膜でチャネル領域が形成される。このため、シングルゲート型の薄膜トランジスタおよびデュアルゲート型の薄膜トランジスタのキャリアの移動量が増加し、オン電流および電界効果移動度が高くなる。また、微結晶半導体領域133aと、不純物半導体膜131a、131bの間に、非晶質半導体領域133bを有する。このため、薄膜トランジスタのオフ電流を低減することができる。以上のことから、薄膜トランジスタの面積を小さくすることが可能であり、半導体装置への高集積化が可能である。また、表示装置の駆動回路に本実施の形態に示す薄膜トランジスタを用いることで、駆動回路の面積を低減できるため、表示装置の狭額縫化が可能である。30

#### 【0178】

以上の工程により高温下などでも動作する、つまり温度特性の良好なシングルゲート型の薄膜トランジスタおよびデュアルゲート型の薄膜トランジスタを作製することができる。。

#### 【0179】

本実施の形態は、他の実施の形態および実施例と適宜組み合わせて用いることができる。。

#### 【0180】

##### (実施の形態3)

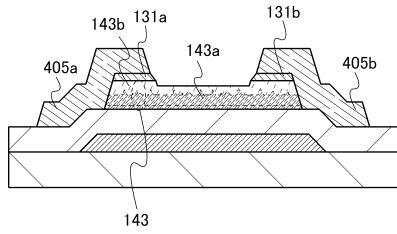

本実施の形態では、実施の形態2で説明した薄膜トランジスタと構造が異なる薄膜トランジスタの作製方法について、図6、図8、および図10を参照して説明する。図10は、図8(B)に示す工程に対応する工程である。40

#### 【0181】

実施の形態2と同様に、図6(A)～(D)および図8(A)の工程を経て、導電膜127を形成する。

#### 【0182】

次に、図10に示すように、実施の形態2と同様に、ソース電極405aおよびドレイン電極405bを形成し、不純物半導体膜121および半導体積層体117の一部をエッチングして、ソース領域およびドレイン領域として機能する一対の不純物半導体膜131a、131bを形成する。また、微結晶半導体領域143aおよび非晶質半導体領域14

3 b を有する半導体積層体 1 4 3 を形成する。このとき、非晶質半導体領域 1 4 3 b が露出されるように半導体積層体 1 1 7 をエッティングすることで、ソース電極 4 0 5 a およびドレイン電極 4 0 5 b で覆われる領域では、微結晶半導体領域 1 4 3 a および非晶質半導体領域 1 4 3 b が積層され、ソース電極 4 0 5 a およびドレイン電極 4 0 5 b によって覆われず、且つゲート電極と重なる領域においては、微結晶半導体領域 1 4 3 a が露出せず、非晶質半導体領域 1 4 3 b が露出する半導体積層体 1 4 3 となる。なお、ここでの半導体積層体 1 1 7 のエッティング量は図 8 ( B ) より少ないものとする。

#### 【 0 1 8 3 】

この後の工程は、実施の形態 2 と同様である。

#### 【 0 1 8 4 】

以上の工程によりシングルゲート型の薄膜トランジスタを作製することができる。該薄膜トランジスタは、バックチャネル側が非晶質であるため、図 8 ( B ) に示す薄膜トランジスタに比べてオフ電流を低減することができる。

10

#### 【 0 1 8 5 】

また、本実施の形態では、図 1 0 に示す工程の後に、図 8 ( C ) に示す工程と同様に、絶縁膜 4 0 7 を介してバックゲート電極 4 1 0 を形成してもよい。

#### 【 0 1 8 6 】

本実施の形態および実施の形態 2 で説明した薄膜トランジスタは、半導体層として、非晶質の酸化物半導体または複数の結晶領域を有している酸化物半導体を用いて形成してもよい。なお、該酸化物半導体は、非単結晶であればよい。

20

#### 【 0 1 8 7 】

酸化物半導体には、In、Ga、およびZnを含むIn - Ga - Zn系金属酸化物を用いて、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される構造とすることができます。なお、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)もしくはコバルト(Co)から選ばれた一の金属元素または複数の金属元素を示す。例えばMとして、Gaの場合があることの他、GaとNiまたはGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。そして、金属酸化物ターゲット中の金属酸化物の相対密度は80%以上、好ましくは95%以上、さらに好ましくは99.9%以上とする相対密度の高い金属酸化物ターゲットを用いる。

30

#### 【 0 1 8 8 】

さらに具体的には、四元系金属酸化物であるIn - Sn - Ga - Zn系金属酸化物や、三元系金属酸化物であるIn - Ga - Zn系金属酸化物、In - Sn - Zn系金属酸化物、In - Al - Zn系金属酸化物、Sn - Ga - Zn系金属酸化物、Al - Ga - Zn系金属酸化物、Sn - Al - Zn系金属酸化物、In - Hf - Zn系金属酸化物、In - La - Zn系金属酸化物、In - Ce - Zn系金属酸化物、In - Pr - Zn系金属酸化物、In - Nd - Zn系金属酸化物、In - Sm - Zn系金属酸化物、In - Eu - Zn系金属酸化物、In - Gd - Zn系金属酸化物、In - Tb - Zn系金属酸化物、In - Dy - Zn系金属酸化物、In - Ho - Zn系金属酸化物、In - Er - Zn系金属酸化物、In - Tm - Zn系金属酸化物、In - Yb - Zn系金属酸化物、In - Lu - Zn系金属酸化物や、二元系金属酸化物であるIn - Zn系金属酸化物、Sn - Zn系金属酸化物、Al - Zn系金属酸化物、Zn - Mg系金属酸化物、Sn - Mg系金属酸化物、In - Mg系金属酸化物、In - Ga系金属酸化物や、インジウム、スズまたは亜鉛などを含む金属酸化物を用いて形成することができる。なお、上記列挙した金属酸化物において、例えば、In - Ga - Zn系金属酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

40

#### 【 0 1 8 9 】

酸化物半導体の形成方法としては、スパッタリング法、分子線エピタキシー法、原子層

50

堆積法、パルスレーザー蒸着法、塗布法、または印刷法等を用いることができる。

【0190】

酸化物半導体を形成する以外の作製工程は、本実施の形態および実施の形態2で説明した工程と同様である。

【0191】

また、酸化物半導体を用いる場合、作製工程中に適宜加熱処理を施すことで、酸化物半導体中の水素含有量を低減させ、酸化物半導体中の酸素欠損を補充することができ、オフ電流の低下など電気特性を向上させることができる。

【0192】

以上の工程により高温下などでも動作する、つまり温度特性の良好な薄膜トランジスタを作製することができる。 10

【0193】

本実施の形態は、他の実施の形態および実施例と適宜組み合わせて用いることができる。

【0194】

(実施の形態4)

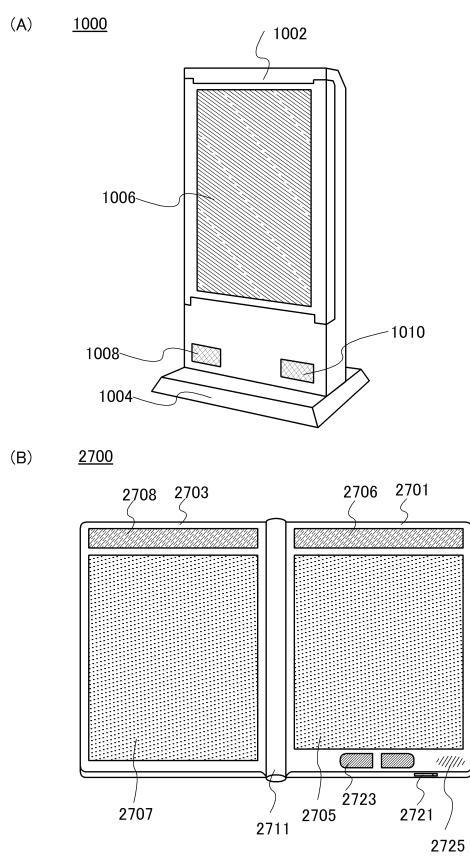

本明細書に開示する液晶表示装置は、電子書籍(電子ブック)、P I D ( P u b l i c I n f o r m a t i o n D i s p l a y )、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。特に、本明細書に開示する液晶表示装置は、高温下や低温下など厳しい環境下で高精細且つ色調変化の少ないため、晴れた屋外など高温下で動作させる必要のあるデジタルサイネージなどに用いることはとても有用である。電子機器の一例を図11に示す。 20

【0195】

図11(A)は、デジタルサイネージの一例を示している。例えば、デジタルサイネージ1000は、2つの筐体1002および筐体1004から構成されている。筐体1002には、表示部1006および2つのスピーカ1008、1010が備わっている。

【0196】

本発明の一態様である液晶表示装置は、表示部1006に用いることができ、先の実施の形態で記したように、晴れた屋外など高温下でも、液晶の屈折率が原因で生じる色調変化を補正することができ、高精細な画像を表示することができる。 30

【0197】

さらに、上記構成に加えて、新たにセンサを設けて人が近くにいないときは画像が表示されないなど、他の構成を設けてもよい。

【0198】

図11(B)は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0199】

筐体2701には表示部2705および光電変換装置2706が組み込まれ、筐体2703には表示部2707および光電変換装置2708が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図11(B)では表示部2705)に文章を表示し、左側の表示部(図11(B)では表示部2707)に画像を表示することができる。 40

【0200】

また、図11(B)では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一

面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、U S B 端子、またはA C アダプタおよびU S B ケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

#### 【0201】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とともに可能である。

#### 【0202】

本実施の形態は、他の実施の形態および実施例に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0203】

##### （実施の形態5）

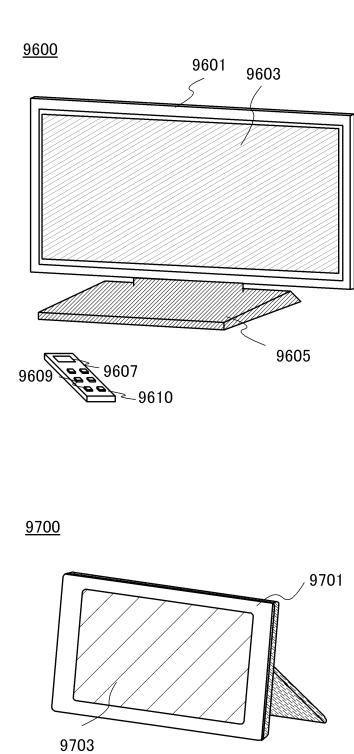

本明細書に開示する液晶表示装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

#### 【0204】

図12(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

#### 【0205】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機9610から出力する情報を表示する表示部9607を設ける構成としてもよい。

#### 【0206】

なお、テレビジョン装置9600は、受信機やモ뎀などを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモ뎀を介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

#### 【0207】

図12(B)は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することができる、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

#### 【0208】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子（U S B 端子、U S B ケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

#### 【0209】

10

20

30

40

50

また、デジタルフォトフレーム 9700 は、無線で情報を送受信できる構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

#### 【0210】

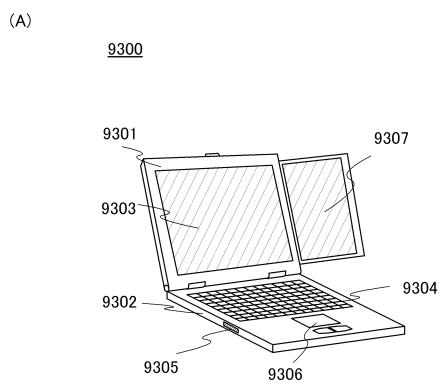

図13(A)は携帯型のコンピュータの一例を示す斜視図である。

#### 【0211】

図13(A)の携帯型のコンピュータは、上部筐体9301と下部筐体9302とを接続するヒンジユニットを閉状態として表示部9303を有する上部筐体9301と、キーボード9304を有する下部筐体9302とを重ねた状態とすることができる、持ち運ぶことが便利であるとともに、使用者がキーボード入力する場合には、ヒンジユニットを開状態として、表示部9303を見て入力操作を行うことができる。

10

#### 【0212】

また、下部筐体9302はキーボード9304の他に入力操作を行うポインティングデバイス9306を有する。また、表示部9303をタッチ入力パネルとすれば、表示部の一部に触れることで入力操作を行うこともできる。また、下部筐体9302はCPUやハードディスク等の演算機能部を有している。また、下部筐体9302は他の機器、例えばUSBの通信規格に準拠した通信ケーブルが差し込まれる外部接続ポート9305を有している。

#### 【0213】

上部筐体9301には更に上部筐体9301内部にスライドさせて収納可能な表示部9307を有しており、広い表示画面を実現することができる。また、収納可能な表示部9307の画面の向きを使用者は調節できる。また、収納可能な表示部9307をタッチ入力パネルとすれば、収納可能な表示部の一部に触れることで入力操作を行うこともできる。

20

#### 【0214】

表示部9303または収納可能な表示部9307は、液晶表示パネル、有機発光素子または無機発光素子などの発光表示パネルなどの映像表示装置を用いる。

#### 【0215】

また、図13(A)の携帯型のコンピュータは、受信機などを備えた構成として、テレビ放送を受信して映像を表示部に表示することができる。また、上部筐体9301と下部筐体9302とを接続するヒンジユニットを閉状態としたまま、表示部9307をスライドさせて画面全面を露出させ、画面角度を調節して使用者がテレビ放送を見る 것도できる。この場合には、ヒンジユニットを開状態として表示部9303を表示させることなく、さらにテレビ放送を表示するだけの回路の起動のみを行うため、最小限の消費電力とすることができ、バッテリー容量の限られている携帯型のコンピュータにおいて有用である。

30

#### 【0216】

図13(B)は、携帯電話機の一例を示している。図13(B)に示す携帯電話機1700は、筐体1731に組み込まれた表示部1732の他、操作ボタン1733、操作ボタン1737、外部接続ポート1734、スピーカ1735、およびマイク1736等を備えている。

40

#### 【0217】

図13(B)に示す携帯電話機1700は、表示部1732がタッチパネルになっており、指等の接触により、表示部1732の表示内容を操作することができる。また、電話の発信、或いはメールの作成等は、表示部1732を指等で接触することにより行うことができる。

#### 【0218】

表示部1732の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

#### 【0219】

50

例えば、電話の発信、またはメールを作成する場合には、表示部 1732 を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合には、表示部 1732 の画面の大部分を使用してキーボードまたは番号ボタンを表示させることが好ましい。

#### 【0220】

また、図 13 (B) に示す携帯電話機 1700 の内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを備えた検出装置を設けることで、携帯電話機の向き（縦または横）を判別して、表示部 1732 の表示情報を自動的に切り替える構成とすることもできる。

#### 【0221】

また、画面モードの切り替えは、表示部 1732 への接触、または筐体 1731 の操作ボタン 1737 の操作により行われる。また、表示部 1732 に表示される画像の種類によって切り替える構成とすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替えることができる。

#### 【0222】

また、入力モードにおいて、表示部 1732 の光センサで検出される信号を検知し、表示部 1732 のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

#### 【0223】

表示部 1732 は、イメージセンサとして機能させることもできる。例えば、表示部 1732 を掌や指で触れ、掌紋および指紋等をイメージセンサで撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈等を撮像することもできる。

#### 【0224】

本実施の形態は、他の実施の形態および実施例に記載した構成と適宜組み合わせて実施することが可能である。

#### 【実施例 1】

#### 【0225】

本実施例では、本発明の一態様である液晶表示装置に含まれる薄膜トランジスタの電気特性について説明する。

#### 【0226】

はじめに、チャネル形成領域に微結晶シリコン半導体を用いた薄膜トランジスタの作製方法について、図 6 および図 8 を参照して説明する。

#### 【0227】

まず、基板 118 上に下地絶縁膜（図示せず）を形成し、下地絶縁膜上にゲート電極 401 を形成した。

#### 【0228】

ここでは、基板 118 として、ガラス基板（コーニング製 EAGLE XG）を用いた。

#### 【0229】

ゲート電極 401 は、アルミニウム層をチタン層により挟持した構造とした。具体的には、まず、チタンターゲットをアルゴンイオンでスパッタリングして、厚さ 50 nm の第 1 のチタン膜を下地絶縁膜上に形成した。このとき、導入するアルゴンの流量は 20 sccm とし、処理室内の圧力は 0.1 Pa、印加電圧は 12 kW、温度は室温とした。そして、その上にアルミニウムターゲットをアルゴンイオンでスパッタリングして、厚さ 100 nm のアルミニウム膜を形成した。このとき、導入するアルゴンの流量は 50 sccm とし、処理室内の圧力は 0.4 Pa、印加電圧は 4 kW、温度は室温とした。そして、その上にチタンターゲットをアルゴンイオンでスパッタリングして、厚さ 50 nm の第 2 のチタン膜を形成した。第 2 のチタン膜は第 1 のチタン膜と同様の方法で形成した。つまり

10

20

30

40

50

、導入するアルゴンの流量は 2 0 s c c m とし、処理室内の圧力は 0 . 1 P a 、印加電圧は 1 2 k W 、温度は室温とした。

#### 【 0 2 3 0 】

次に、チタン膜上にレジストを塗布し、第 1 のフォトマスクを用いて露光した後、現像してレジストマスクを形成した。

#### 【 0 2 3 1 】

次に、該レジストマスクを用いてエッチング処理を行って、ゲート電極 4 0 1 を形成した。ここでは、 I C P ( Inductive Coupled Plasma : 誘導結合型プラズマ ) 装置を用いて 2 段階のエッチングを行った。すなわち、 I C P パワー 6 0 0 W 、バイアスパワー 2 5 0 W 、エッチングガスとして三塩化ホウ素を流量 6 0 s c c m で導入し、塩素を流量 2 0 s c c m で導入して、処理室内の圧力を 1 . 2 P a とし、第 1 のエッチングを行った後、 I C P パワー 5 0 0 W 、バイアスパワー 5 0 W 、圧力 2 . 0 P a 、エッチングガスとして四フッ化炭素を流量 8 0 s c c m で導入して処理室内の圧力を 2 . 0 P a とし、第 2 のエッチングを行った。その後、該レジストマスクを除去した。

10

#### 【 0 2 3 2 】

次に、ゲート電極 4 0 1 および下地絶縁膜上に、ゲート絶縁膜 4 0 2 を形成した後、ゲート絶縁膜 4 0 2 にプラズマ処理を行った。

#### 【 0 2 3 3 】

本実施例では、ゲート絶縁膜 4 0 2 として、厚さ 3 0 0 n m の窒化シリコン膜をプラズマ C V D 法によって堆積させて形成した後、プラズマ処理を行った。窒化シリコン膜の堆積は、シランの流量を 1 5 s c c m 、水素の流量を 2 0 0 s c c m 、窒素の流量を 1 8 0 s c c m 、アンモニアの流量を 5 0 0 s c c m として原料ガスを導入して、処理室内の圧力を 1 0 0 P a 、 R F 電源周波数を 1 3 . 5 6 M H z 、 R F 電源の電力を 2 0 0 W としてプラズマ放電を行った。なお、ゲート絶縁膜 4 0 2 の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を 2 5 0 、下部電極温度を 2 9 0 とし、上部電極と下部電極との間隔（ギャップ）を 3 0 m m とした。

20

#### 【 0 2 3 4 】

形成した窒化シリコン膜へのプラズマ処理は、一酸化二窒素の流量を 4 0 0 s c c m として処理室内に導入し、処理室内の圧力を 6 0 P a として、電力を 3 0 0 W として 3 分間のプラズマ放電を行った。なお、該プラズマ処理は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を 2 5 0 、下部電極温度を 2 9 0 とし、上部電極と下部電極との間隔を 3 0 m m とした。

30

#### 【 0 2 3 5 】

次に、ゲート絶縁膜 4 0 2 上に、厚さ 5 n m の種結晶 3 0 7 をプラズマ C V D 法にて形成した。種結晶 3 0 7 の堆積は、シランの流量を 6 s c c m 、水素の流量を 7 5 0 s c c m 、アルゴンの流量を 7 5 0 s c c m として原料ガスを導入して、処理室内の圧力を 5 3 2 P a 、 R F 電源周波数を 1 3 . 5 6 M H z 、 R F 電源の電力を 2 5 0 W としてプラズマ放電を行った。なお、種結晶 3 0 7 の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極の温度を 2 5 0 、下部電極の温度を 2 9 0 とし、上部電極と下部電極との間隔を 1 5 m m とした。

40

#### 【 0 2 3 6 】

ここまで得られた構成を図 6 ( A ) に示す。

#### 【 0 2 3 7 】

次いで、ゲート絶縁膜 4 0 2 および種結晶 3 0 7 の上に、厚さ 8 5 n m の微結晶半導体膜 1 0 9 をプラズマ C V D 法にて形成した。微結晶半導体膜 1 0 9 の堆積は、シランの流量を 1 . 8 s c c m 、水素の流量を 7 5 0 s c c m 、アルゴンの流量を 7 5 0 s c c m として原料ガスを導入して、処理室内の圧力を 5 0 0 0 P a 、 R F 電源周波数を 1 3 . 5 6 M H z 、 R F 電源の電力を 1 2 5 W としてプラズマ放電を行った。なお、微結晶半導体膜 1 0 9 の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極の温度を 2 5 0 、下部電極の温度を 2 9 0 とし、上部電極と下部電極との間隔を 7 m m とした。

50

**【0238】**

本工程で得られた構成を図6(B)に示す。

**【0239】**

次に、微結晶半導体膜109上に厚さ80nmの半導体膜111を形成し、半導体膜111上に厚さ50nmの不純物半導体膜113を形成した。半導体膜111および不純物半導体膜113は、プラズマCVD法によって形成した。

**【0240】**

半導体膜111の堆積は、シランの流量を20sccm、1000ppmアンモニア(水素希釈)の流量を50sccm、水素の流量を700sccm、アルゴンの流量を750sccmとして材料ガスを導入して、処理室内の圧力を350Paとし、RF電源周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行った。なお、半導体膜111の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を200、下部電極温度を290とし、上部電極と下部電極との間隔を25mmとした。

10

**【0241】**

不純物半導体膜113としては、リンが添加されたアモルファスシリコン膜を形成した。不純物半導体膜113の堆積は、シランの流量を80sccm、5%ホスフィン(シラン希釈)の流量を50sccm、水素の流量を750sccmとして材料ガスを導入して安定させ、処理室内の圧力を1250Pa、RF電源周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行った。なお、不純物半導体膜113の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を250、下部電極温度を290とし、上部電極と下部電極との間隔を15mmとした。

20

**【0242】**

次に、不純物半導体膜113上にレジストを塗布した後、第2のフォトマスクを用いて露光し、現像してレジストマスク115を形成した。ここまで得られた構成を図6(C)に示す。

**【0243】**

次に、レジストマスク115を用いて、微結晶半導体膜109、半導体膜111、不純物半導体膜113をエッティングして、微結晶半導体領域117aおよび非晶質半導体領域117bを有する半導体積層体117、および不純物半導体膜121を形成した。

30

**【0244】**

エッティングを行うにあたり、本実施例では、ICP装置を用いて、ICPパワー450W、バイアスパワー100W、エッティングガスとして三塩化ホウ素を流量36sccm、四フッ化炭素を36sccm、酸素を8sccmで導入し、処理室内の圧力を2Paとしてエッティングを行った。

**【0245】**

その後、酸素プラズマ処理を行い、微結晶半導体領域117aおよび非晶質半導体領域117bを有する半導体積層体117および不純物半導体膜121の側壁の酸化膜を形成した後、レジストマスク115を除去した(図示せず)。

**【0246】**

酸素プラズマ処理は、酸素の流量を100sccmとして導入して処理室内の圧力を0.67Paとし、基板温度を-10とし、ソースパワーを2000W、バイアスパワーを350Wでプラズマ放電を行った。

40

**【0247】**

ここまで得られた構成を図6(D)に示す。

**【0248】**

次に、ゲート絶縁膜402、半導体積層体117および不純物半導体膜121を覆って導電膜127を形成した。本工程で得られた構成を図8(A)に示す。

**【0249】**

本実施例では、導電膜127は、アルミニウム層をチタン層により挟持した構造とし、ゲート電極401と同様に形成した。ただし、第1のチタン膜の厚さを50nmとし、ア

50

ルミニウム膜の厚さを 200 nm とし、第 2 のチタン膜の厚さを 50 nm とした。

#### 【0250】

次に、導電膜 127 上にレジストを塗布した後、第 3 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。該レジストマスクを用いて導電膜 127 をドライエッティングして、ソース電極 405a およびドレイン電極 405b を形成すると同時に、半導体積層体 117 を一部エッティングし、微結晶半導体領域 133a および一対の非晶質半導体領域 133b を有する半導体積層体 133 を形成した。

#### 【0251】

本工程では、ICP 装置を用いて、ICP パワー 450 W、バイアスパワー 100 W、エッティングガスとして三塩化ホウ素を流量 60 sccm で導入し、塩素を 20 sccm で導入し、処理室内の圧力を 1.9 Pa としてエッティングを行った。

10

#### 【0252】

なお、半導体積層体 117 の表面から 160 nm をエッティングした。なお、本実施例では、ソース電極 405a およびドレイン電極 405b の平面形状は、直線型である。

#### 【0253】

次に、半導体積層体 133 の表面を水プラズマ処理し、半導体積層体 133 表面に残る不純物を除去した。本工程では、パワー 1800 W として水蒸気を流量 300 sccm で導入し、処理室内の圧力を 66.5 Pa として水プラズマ処理を行った。

#### 【0254】

ここまで得られた構成を図 8 (B) に示す。

20

#### 【0255】

次に、絶縁膜 407 として、厚さ 300 nm の窒化シリコン膜を形成した。絶縁膜 407 の堆積は、シランの流量を 20 sccm、アンモニアの流量を 220 sccm、窒素の流量を 450 sccm、水素の流量を 450 sccm として材料ガスを導入し、処理室内の圧力を 160 Pa、RF 電源周波数を 27 MHz、RF 電源の電力を 200 W としてプラズマ放電を行った。なお、絶縁膜 407 の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を 250°、下部電極温度を 290° とし、上部電極と下部電極との間隔を 21 mm とした。

#### 【0256】

次に、絶縁膜 407 上にレジストを塗布した後、第 4 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。該レジストマスクを用いて絶縁膜の一部をドライエッティングして、ソース電極 405a およびドレイン電極 405b を露出させた。また、絶縁膜 407 およびゲート絶縁膜 402 の一部をドライエッティングして、ゲート電極 401 を露出した。その後、該レジストマスクを除去した。

30

#### 【0257】

次に、絶縁膜 407 上に導電膜を形成した後、該導電膜上にレジストを塗布し、第 5 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストで形成されたマスクを用いて導電膜の一部をウェットエッティングして、バックゲート電極 410 を形成した。

#### 【0258】

ここでは、導電膜として、スパッタリング法により厚さ 50 nm のインジウム錫酸化物を形成した後、ウェットエッティング処理によりバックゲート電極 410 を形成した。なお、ここでは図示しないが、バックゲート電極 410 は、ゲート電極 401 と接続されている。その後、レジストで形成されたマスクを除去した。

40

#### 【0259】

以上の工程により、デュアルゲート型薄膜トランジスタ (TFT1 と示す) を作製した (図 8 (C) 参照)。

#### 【0260】

次に、比較例としてチャネル形成領域にアモルファスシリコンを用いた薄膜トランジスタの作製方法を説明する。アモルファスシリコンを用いた薄膜トランジスタは、種結晶 3

50

07、微結晶半導体膜109および半導体膜111をアモルファスシリコン半導体膜とすることで作製できる。それゆえ、図8および図10を参照できるが、作製工程中に示される半導体膜111、微結晶半導体領域111a、非晶質半導体領域111b、島状の半導体積層体117、微結晶半導体領域117a、非晶質半導体領域117b、半導体積層体133、微結晶半導体領域133a、非晶質半導体領域133bはアモルファルシリコン膜とする。

#### 【0261】

薄膜トランジスタを形成する下地絶縁膜および基板118は、上記と同様のものを用いた。ゲート電極401においても上記と同様にして形成した。

#### 【0262】

ゲート絶縁膜402として、厚さ300nmの窒化シリコン膜をプラズマCVD法によって堆積させて形成した後、プラズマ処理を行った。窒化シリコン膜の堆積は、シランの流量を40sccm、水素の流量を500sccm、窒素の流量を550sccm、アンモニアの流量を140sccmとして原料ガスを導入して、処理室内の圧力を100Pa、RF電源周波数を13.56MHz、RF電源の電力を370Wとしてプラズマ放電を行った。なお、ゲート絶縁膜402の堆積は、平行平板型のプラズマ処理装置を用いて行い、基板温度が280となるようにし、上部電極と下部電極との間隔(ギャップ)を24.5mmとした。

#### 【0263】

形成した窒化シリコン膜へのプラズマ処理は、水素の流量を1500sccmとして処理室内に導入し、処理室内の圧力を280Paとして、電力を50Wとして5分間のプラズマ放電を行った。なお、該プラズマ処理は、平行平板型のプラズマ処理装置を用いて行い、基板温度が280となるようにし、上部電極と下部電極との間隔を24.5mmとした。

#### 【0264】

次に、微結晶半導体膜109および半導体膜111の代わりに厚さ205nmのアモルファスシリコン膜を形成し、アモルファスシリコン膜上に厚さ50nmの不純物半導体膜113を形成した。アモルファスシリコン膜および不純物半導体膜113は、プラズマCVD法によって堆積させて形成した。

#### 【0265】

アモルファスシリコン膜は、シランの流量を280sccm、水素の流量を300sccmとして導入し、処理室内の圧力を170Paとし、RF電源周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行った。なお、半導体膜111の堆積は、平行平板型のプラズマ処理装置を用いて行い、基板温度が280となるようにし、上部電極と下部電極との間隔を24.5mmとした。

#### 【0266】

不純物半導体膜113としては、リンが添加されたアモルファスシリコン膜を形成した。不純物半導体膜113の堆積は、シランの流量を100sccm、0.5%ホスフィン(水素希釈)の流量を170sccm、として材料ガスを導入して、処理室内の圧力を100Pa、RF電源周波数を13.56MHz、RF電源の電力を370Wとしてプラズマ放電を行った。なお、不純物半導体膜113の堆積は、平行平板型のプラズマ処理装置を用いて行い、基板温度が280となるようにし、上部電極と下部電極との間隔を24.5mmとした。

#### 【0267】

次に、不純物半導体膜113上にレジストを塗布した後、第2のフォトマスクを用いて露光し、現像してレジストマスク115を形成した。

#### 【0268】

次に、レジストマスク115を用いて、アモルファスシリコン膜、不純物半導体膜113をエッティングして、島状のアモルファスシリコン膜および不純物半導体膜121を形成した。

10

20

30

40

50

**【0269】**

エッチングを行うにあたり、本実施例では、ICP装置を用いて、ソースパワー100W、バイアスパワー80W、エッチングガスとして塩素を流量100sccm、で導入し、処理室内の圧力を1.51Paとしてエッチングを行った。

**【0270】**

次に、ゲート絶縁膜402、アモルファスシリコン膜および不純物半導体膜121を覆って導電膜127を形成した。

**【0271】**

本実施例では、導電膜127は、アルミニウム層をチタン層により挟持した構造とし、ゲート電極401と同様に形成した。ただし、第1のチタン膜の厚さを50nmとし、アルミニウム膜の厚さを200nmとし、第2のチタン膜の厚さを50nmとした。

10

**【0272】**

次に、導電膜127上にレジストを塗布した後、第3のフォトマスクを用いて露光し、現像してレジストマスクを形成した。該レジストマスクを用いて導電膜127をドライエッチングして、ソース電極405aおよびドレイン電極405bを形成すると同時に、アモルファスシリコン膜および不純物半導体膜121の一部をエッチングした。

**【0273】**

本工程では、ICP装置を用いて、ICPパワー450W、バイアスパワー100W、エッチングガスとして三塩化ホウ素を流量60sccmで導入し、塩素を20sccmで導入し、処理室内の圧力を1.9Paとしてエッチングを行った。

20

**【0274】**

なお、本工程により、導電膜127の一部に加え、アモルファスシリコン膜および不純物半導体膜121の一部を80nm程エッチングした。なお、本実施例では、ソース電極405aおよびドレイン電極405bの平面形状は、直線型である。

**【0275】**

次に、絶縁膜407として、厚さ300nmの窒化シリコン膜を形成した。絶縁膜407の堆積は、シランの流量を20sccm、アンモニアの流量を220sccm、窒素の流量を450sccm、水素の流量を450sccmとして材料ガスを導入し、処理室内の圧力を160Pa、RF電源周波数を27MHz、RF電源の電力を200Wとしてプラズマ放電を行った。なお、絶縁膜407の堆積は、平行平板型のプラズマ処理装置を用いて行い、上部電極温度を250、下部電極温度を290とし、上部電極と下部電極との間隔を21mmとした。

30

**【0276】**

次に、絶縁膜407上にレジストを塗布した後、第4のフォトマスクを用いて露光し、現像してレジストマスクを形成した。該レジストマスクを用いて絶縁膜の一部をドライエッチングして、ソース電極405aおよびドレイン電極405bを露出させた。また、絶縁膜407およびゲート絶縁膜402の一部をドライエッチングして、ゲート電極401を露出した。その後、該レジストマスクを除去した。

**【0277】**

以上の工程により、シングルゲート型アモルファスシリコン薄膜トランジスタ(TFT2と示す)を作製した。

40

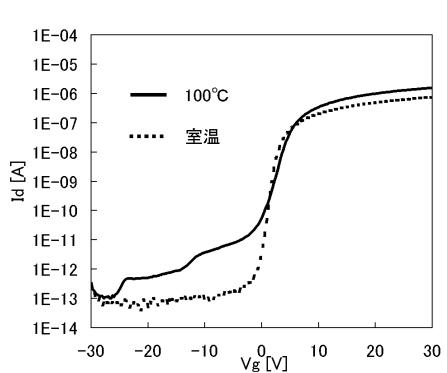

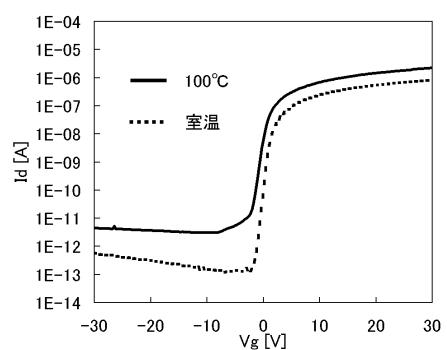

**【0278】**

図14(A)に、本実施例で作製したTFT1の電気特性を、図14(B)にTFT2の電気特性を測定した結果を示す。図14(A)および(B)において、点線は室温で測定した電気特性結果で、実線は100で測定した電気特性結果である。なお、ゲート電極401のみにゲート電圧を印加し、ドレイン電圧が1Vでの電気特性を示す。また、本実施例のTFT1のチャネル長を3.2μm、チャネル幅を22.1μm、ゲート絶縁膜の厚さを300nm、平均誘電率を7.0として電界効果移動度を計算し、TFT2のチャネル長を3.7μm、チャネル幅を22.0μm、ゲート絶縁膜の厚さを300nm、平均誘電率を7.0として電界効果移動度を計算した。

50

## 【0279】

図14(A)および図14(B)から、チャネル形成領域に微結晶シリコン半導体を用いたTFT1は、室温と100°で測定した電気特性は共に良好であるのに対して、チャネル形成領域にアモルファスシリコンを用いたTFT2は、室温では良好な電気特性を示すが、100°で測定した場合、良好な電気特性を得られないことが確認された。

## 【0280】

以上より、チャネル形成領域に微結晶半導体を用いた薄膜トランジスタは、高温下においても良好な電気特性が得られるため、該薄膜トランジスタを有する液晶表示装置は、屋外での使用が可能で、高精細且つ色調変化を補正することができる液晶表示装置とすることができる。

10

## 【符号の説明】

## 【0281】

|       |            |    |

|-------|------------|----|

| 100   | 液晶表示装置     |    |

| 102   | 画素部        |    |

| 103   | セグメントドライバ  |    |

| 105   | コモンドライバ    |    |

| 108   | 照明部        |    |

| 110   | モニタリング用画素部 |    |

| 104   | 信号線駆動回路    |    |

| 106   | 走査線駆動回路    | 20 |

| 107   | 第1の偏光部材    |    |

| 109   | 微結晶半導体膜    |    |

| 111   | 半導体膜       |    |

| 111 a | 微結晶半導体領域   |    |

| 111 b | 非晶質半導体領域   |    |

| 112   | 第1の光センサ    |    |

| 113   | 不純物半導体膜    |    |

| 114   | 第2の光センサ    |    |

| 115   | マスク        |    |

| 116   | 制御部        | 30 |

| 117   | 半導体積層体     |    |

| 117 a | 微結晶半導体領域   |    |

| 117 b | 非晶質半導体領域   |    |

| 118   | 基板         |    |

| 120   | 対向基板       |    |

| 121   | 不純物半導体膜    |    |

| 122   | 第2の偏光部材    |    |

| 123   | トランジスタ素子層  |    |

| 126   | 画素電極       |    |

| 127   | 導電膜        | 40 |

| 128   | 共通画素電極     |    |

| 130   | シール材料      |    |

| 131 a | 不純物半導体膜    |    |

| 131 b | 不純物半導体膜    |    |

| 132   | 液晶         |    |

| 133   | 半導体積層体     |    |

| 133 a | 微結晶半導体領域   |    |

| 133 b | 非晶質半導体領域   |    |

| 134   | 光源         |    |

| 136   | 導光部材       | 50 |

|           |          |    |

|-----------|----------|----|

| 1 3 8     | 反射部材     |    |

| 1 4 0     | 反射シート    |    |

| 1 4 3     | 半導体積層体   |    |

| 1 4 3 a   | 微結晶半導体領域 |    |

| 1 4 3 b   | 非晶質半導体領域 |    |

| 3 0 0     | 入射光      |    |

| 3 0 2     | 偏光       |    |

| 3 0 3     | 入射光      |    |

| 3 0 5     | 偏光       |    |

| 3 0 4     | 入射光      | 10 |

| 3 0 6     | 偏光       |    |

| 3 0 7     | 種結晶      |    |

| 3 0 8     | 入射光      |    |

| 3 1 0     | 偏光       |    |

| 3 1 2     | 入射光      |    |

| 3 1 4     | 偏光       |    |

| 4 0 1     | ゲート電極    |    |

| 4 0 3     | 容量配線     |    |

| 4 0 6     | 保持容量素子   |    |

| 4 0 5 a   | ソース電極    | 20 |

| 4 0 5 b   | ドレイン電極   |    |

| 4 3 0     | トランジスタ   |    |

| 4 0 2     | ゲート絶縁膜   |    |

| 4 0 8     | 半導体層     |    |

| 4 0 7     | 絶縁膜      |    |

| 4 1 0     | バックゲート電極 |    |

| 4 1 3     | 層間絶縁膜    |    |

| 1 7 0 1 a | 画素電極     |    |

| 1 7 0 1 b | 画素電極     |    |

| 1 7 0 1 c | 画素電極     | 30 |

| 1 7 0 6 a | 共通電極     |    |

| 1 7 0 6 b | 共通電極     |    |

| 1 7 0 6 c | 共通電極     |    |

| 1 7 0 7   | 絶縁膜      |    |

| 1 7 1 3   | 液晶素子     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2008-009090 (JP, A)

特開2002-277872 (JP, A)

特開2000-029022 (JP, A)

特開2004-361618 (JP, A)

特開2000-002890 (JP, A)

特開2008-085312 (JP, A)

特開2010-141306 (JP, A)

特開2009-265635 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                      |

|--------|----------------------|

| G 02 F | 1 / 133              |

| G 02 F | 1 / 1335 - 1 / 13363 |

| G 02 F | 1 / 136 - 1 / 1368   |