(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5813067号

(P5813067)

(45) 発行日 平成27年11月17日(2015.11.17)

(24) 登録日 平成27年10月2日(2015.10.2)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/378 (2011.01)  | HO4N 5/335 780 |

| HO4N 5/357 (2011.01)  | HO4N 5/335 570 |

| HO4N 5/369 (2011.01)  | HO4N 5/335 690 |

| HO4N 5/374 (2011.01)  | HO4N 5/335 740 |

| HO1L 27/146 (2006.01) | HO1L 27/14 A   |

請求項の数 23 (全 29 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2013-176254 (P2013-176254)  |

| (22) 出願日     | 平成25年8月28日 (2013.8.28)        |

| (65) 公開番号    | 特開2014-140152 (P2014-140152A) |

| (43) 公開日     | 平成26年7月31日 (2014.7.31)        |

| 審査請求日        | 平成27年2月17日 (2015.2.17)        |

| (31) 優先権主張番号 | 特願2012-278320 (P2012-278320)  |

| (32) 優先日     | 平成24年12月20日 (2012.12.20)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

早期審査対象出願

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 武藤 隆<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内         |

| (72) 発明者  | 松野 靖司<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

最終頁に続く

(54) 【発明の名称】撮像装置の駆動方法、デジタル信号の補正方法、撮像装置、撮像システムの駆動方法、撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

画素信号を出力する画素と、

アナログ信号をデジタル信号に変換するA/D変換部と、を有する撮像装置の駆動方法であって、

前記A/D変換部は、アナログ信号と、時間に依存して電位が変化する参照信号と、を比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタとを有し、

前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第1デジタル信号を生成し、

前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第2デジタル信号を生成し、

前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記

10

20

第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第3デジタル信号を生成し、

前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とする撮像装置の駆動方法。

#### 【請求項2】

さらに、前記カウンタが、前記第1の参照信号の電位が変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値とは異なる第2の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第4デジタル信号を生成し、

前記カウンタが、前記第2の参照信号の電位が変化を開始するタイミングに対応して前記カウントを開始してから、前記第2の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第5デジタル信号を生成し、

前記第1デジタル信号と前記第4デジタル信号との信号値の差と、前記第2デジタル信号と前記第5デジタル信号との信号値の差と、に基づいて、前記第3デジタル信号の補正を行うことを特徴とする請求項1に記載の撮像装置の駆動方法。

#### 【請求項3】

前記A/D変換部が、

前記第1デジタル信号と前記第2デジタル信号を生成した後、

前記第4デジタル信号と前記第5デジタル信号を生成することを特徴とする請求項2に記載の撮像装置の駆動方法。

#### 【請求項4】

前記第1デジタル信号の信号値をDN1、前記第2デジタル信号の信号値をDN2、前記第4デジタル信号の信号値をDS1、前記第5デジタル信号の信号値をDS2、前記第1の変化量に対する前記第2の変化量の比をGとして、以下の式で求められる補正值 および を用いて、前記第3デジタル信号を補正することを特徴とする請求項2または3に記載の撮像装置の駆動方法。

$$= DS1 - G \times DS2$$

#### 【数1】

$$\beta = \frac{DS1 - DN1}{G \times (DS2 - DN2)}$$

#### 【請求項5】

前記第1デジタル信号の信号値をDN1、前記第2デジタル信号の信号値をDN2、前記第1の変化量に対する前記第2の変化量の比をGとして、以下の式で求められる補正值 を用いて、前記第3デジタル信号を補正することを特徴とする請求項1～3のいずれかに記載の撮像装置の駆動方法。

$$= DN1 - G \times DN2$$

#### 【請求項6】

前記撮像装置は、複数行に設けられた複数の前記画素と、

前記複数の画素を走査する垂直走査回路と、を有し、

前記第1デジタル信号と前記第2デジタル信号とを生成して前記補正值 を取得する動

10

20

30

40

50

作を、垂直走査回路が前記画素の走査を行わない期間、あるいは、前記画素から前記比較部にノイズ信号が出力されている期間に行うことの特徴とする請求項4または5に記載の撮像装置の駆動方法。

#### 【請求項7】

前記A D変換部が前記第1デジタル信号を生成した後、

前記画素信号に基づく信号の電位と閾値信号の電位とを前記比較部が比較し、前記第3デジタル信号の生成に用いる前記参照信号を、前記閾値信号の電位の方が大きい場合には前記第1の参照信号とし、前記閾値信号の電位の方が小さい場合には前記第2の参照信号とすることの特徴とする請求項1～6のいずれかに記載の撮像装置の駆動方法。

#### 【請求項8】

前記撮像装置は、複数の前記画素と、複数の前記A D変換部と、を有し、

前記複数の画素は、前記画素が複数列設けられ、

前記複数のA D変換部は、それぞれが、前記画素が設けられた列に対応して設けられ、前記複数のA D変換部の各々の、前記第2デジタル信号と前記第1デジタル信号との差の信号値の平均値を得て、

前記平均値に基づいて、前記複数のA D変換部の各々が生成した前記第3デジタル信号の補正を行うことを特徴とする請求項1～7のいずれかに記載の撮像装置の駆動方法。

#### 【請求項9】

前記撮像装置は、複数の前記画素と、複数の前記A D変換部と、を有し、

前記複数の画素は、前記画素が複数列設けられ、

前記複数のA D変換部は、それぞれが、前記画素が設けられた列に対応して設けられ、前記複数のA D変換部の各々の前記第2デジタル信号の平均値と各々の前記第1デジタル信号の平均値との差に基づいて、前記複数のA D変換部の各々が生成した前記第3デジタル信号の補正を行うことを特徴とする請求項1～7のいずれかに記載の撮像装置の駆動方法。

#### 【請求項10】

前記撮像装置はさらに増幅部を有し、

前記画素信号に基づく信号が、前記増幅部が前記画素信号を増幅して出力した信号であることを特徴とする請求項1～9のいずれかに記載の撮像装置の駆動方法。

#### 【請求項11】

前記増幅部の入力ノードに前記画素信号が与えられ、

前記第1の信号値のアナログ信号が、前記増幅部の前記入力ノードのリセットされた電位に基づいて前記増幅部が出力する信号であることを特徴とする請求項10に記載の撮像装置の駆動方法。

#### 【請求項12】

前記第1の信号値のアナログ信号が、前記画素の出力するノイズ信号に基づく信号であることを特徴とする請求項1～10のいずれかに記載の撮像装置の駆動方法。

#### 【請求項13】

A D変換部が、参照信号とアナログ信号との比較によって得られる比較結果信号を出力する比較部と、クロック信号をカウントするカウンタとを有し、

前記A D変換部が前記アナログ信号をA D変換して生成するデジタル信号の補正方法であって、

前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始し、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第1デジタル信号を生成し、

前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始し、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第2デジタル

10

20

30

40

50

信号を生成し、

前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始し、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記アナログ信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第3デジタル信号を生成し、

前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とするデジタル信号の補正方法。 10

#### 【請求項14】

画素信号を出力する画素と、

アナログ信号をデジタル信号に変換するA/D変換部と、を有する撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と、を有し、

前記A/D変換部が、アナログ信号と時間に依存して電位が変化する参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタとを有する撮像システムの駆動方法であって、

前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第1デジタル信号を生成し、 20

前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第2デジタル信号を生成し、

前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第3デジタル信号を生成し、 30

前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とする撮像システムの駆動方法。

#### 【請求項15】

前記撮像装置がさらに補正演算部を有し、

前記信号処理部が、前記第1デジタル信号と前記第2デジタル信号とに基づいて補正值を生成するとともに前記補正值を前記補正演算部に出力し、

前記補正演算部が、前記補正值に基づいて前記第3デジタル信号の補正を行うことを特徴とする請求項14に記載の撮像システムの駆動方法。

#### 【請求項16】

前記信号処理部が、前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第3デジタル信号の補正を行うことを特徴とする請求項14に記載の撮像システムの駆動方法。

#### 【請求項17】

画素信号を出力する画素と、

10

20

30

40

50

アナログ信号をデジタル信号に変換する A D 変換部と、前記 A D 変換部に時間に依存して電位が変化する参照信号を供給する参照信号供給部と、を有する撮像装置であって、

前記 A D 変換部は、アナログ信号と前記参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタと、メモリ部と、を有し、

前記カウンタが、第 1 の参照信号の電位が単位時間あたり第 1 の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第 1 の信号値のアナログ信号と前記第 1 の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 1 デジタル信号を前記メモリ部が保持し、

10

前記カウンタが、第 2 の参照信号の電位が単位時間あたり第 1 の変化量よりも大きい第 2 の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第 1 の信号値のアナログ信号と前記第 2 の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 2 デジタル信号を前記メモリ部が保持し、

前記カウンタが、前記第 1 の参照信号と前記第 2 の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第 1 の参照信号と前記第 2 の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 3 デジタル信号を前記メモリ部が保持し、

20

さらに前記撮像装置が、

前記第 1 デジタル信号と前記第 2 デジタル信号とに基づいて、前記第 1 の参照信号と前記第 2 の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第 3 デジタル信号に含まれるオフセットを低減するように前記第 3 デジタル信号を補正する補正部を有することを特徴とする撮像装置。

#### 【請求項 1 8】

前記撮像装置は、前記比較部に電気的に接続されたテスト信号供給部をさらに有し、

前記第 1 の信号値のアナログ信号が、前記テスト信号供給部が前記比較部に出力する信号に基づく信号であることを特徴とする請求項 1 7 に記載の撮像装置。

30

#### 【請求項 1 9】

前記撮像装置はさらに、前記画素と前記比較部との間の電気的経路に増幅部を有し、

前記画素信号に基づく信号が、前記増幅部が前記画素信号を増幅して出力した信号であることを特徴とする請求項 1 7 または 1 8 に記載の撮像装置。

#### 【請求項 2 0】

請求項 1 7 ~ 1 9 のいずれかに記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と、を有することを特徴とする撮像システム。

#### 【請求項 2 1】

40

画素信号を出力する画素と、

アナログ信号をデジタル信号に変換する A D 変換部と、前記 A D 変換部に時間に依存して電位が変化する参照信号を供給する参照信号供給部と、を有する撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と、を有する撮像システムであつて、

前記 A D 変換部は、アナログ信号と前記参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタと、メモリ部と、を有し、

前記カウンタが、第 1 の参照信号の電位が単位時間あたり第 1 の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第 1 の信号値のアナログ信号と前

50

記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第1デジタル信号を前記メモリ部が保持し、

前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第2デジタル信号を前記メモリ部が保持し、

前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第3デジタル信号を前記メモリ部が保持し、

さらに前記撮像システムが、前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正する補正部を有することを特徴とする撮像システム。

#### 【請求項22】

前記撮像装置と前記補正部が同一の半導体基板に設けられており、

前記撮像システムは、前記半導体基板とは別の半導体基板に設けられた補正值取得部を有し、

前記補正值取得部が、前記第1デジタル信号と前記第2デジタル信号とに基づいて補正值を生成するとともに前記補正值を前記補正部に出力し、

前記補正部が、前記補正值に基づいて前記第3デジタル信号の補正を行うことを特徴とする請求項21に記載の撮像システム。

#### 【請求項23】

前記第1の信号値とは異なる信号値の第2の信号値のアナログ信号と前記第1の参照信号とを前記比較部が比較して出力する前記比較結果信号に基づいて、前記メモリ部は第4デジタル信号を保持し、

前記第2の信号値のアナログ信号と前記第2の参照信号とを前記比較部が比較して出力する前記比較結果信号に基づいて、前記メモリ部は第5デジタル信号を保持し、

前記補正部が、

前記第1デジタル信号と前記第4デジタル信号との信号値の差と、前記第2デジタル信号と前記第5デジタル信号との信号値の差と、に基づいて、前記第3デジタル信号の補正を行うことを特徴とする請求項21に記載の撮像システム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、画素が出力する画素信号をデジタル信号に変換するA/D変換部を有する撮像装置、撮像システムに関する。

#### 【背景技術】

#### 【0002】

画素が出力する画素信号をデジタル信号に変換するA/D変換部を有する撮像装置がある。特許文献1に記載のA/D変換部は、単位時間当たり第1の変化量で変化する第1の参照信号と、単位時間当たり第1の変化量よりも変化量の大きい第2の変化量で電位が変化する第2の参照信号と、を出力する参照信号供給部を有する。さらに特許文献1に記載のA/D変換部は、画素信号と第1の参照信号との比較と、画素信号と第2の参照信号との比較と、をそれぞれ行う比較部を有する。さらに比較部は、ノイズ信号に基づく電位と第1の

10

20

30

40

50

参照信号との比較と、ノイズ信号に基づく電位と第2の参照信号との比較と、をそれぞれ行う。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011-211535号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

同じ信号値のアナログ信号を、第1の参照信号と第2の参照信号とのそれだけで変換したデジタル信号間で信号値にオフセットが生じることがある。特許文献1に記載の撮像装置では、このデジタル信号に含まれるオフセットを低減する検討がなされていなかった。

【課題を解決するための手段】

【0005】

本発明は上記の課題を鑑みて為されたものであり、一の態様は、画素信号を出力する画素と、アナログ信号をデジタル信号に変換するAD変換部と、を有する撮像装置の駆動方法であって、前記AD変換部は、アナログ信号と、時間に依存して電位が変化する参照信号と、を比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタとを有し、前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第1デジタル信号を生成し、前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第2デジタル信号を生成し、前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第3デジタル信号を生成し、前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とする撮像装置の駆動方法である。

【0006】

また、一の態様は、AD変換部が、参照信号とアナログ信号との比較によって得られる比較結果信号を出力する比較部と、クロック信号をカウントするカウンタとを有し、前記AD変換部が前記アナログ信号をAD変換して生成するデジタル信号の補正方法であって、前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始し、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第1デジタル信号を生成し、前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始し、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第2デジタル信号を生成し、前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始

10

20

30

40

50

するタイミングに対応して前記カウントを開始し、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記アナログ信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって第3デジタル信号を生成し、前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とするデジタル信号の補正方法である。

#### 【0007】

また、一の態様は、画素信号を出力する画素と、アナログ信号をデジタル信号に変換するA D変換部と、を有する撮像装置と、前記撮像装置から出力される信号を処理する信号処理部と、を有し、前記A D変換部が、アナログ信号と時間に依存して電位が変化する参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタとを有する撮像システムの駆動方法であって、前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第1デジタル信号を生成し、前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第2デジタル信号を生成し、前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって第3デジタル信号を生成し、前記第1デジタル信号と前記第2デジタル信号とに基づいて、前記第1の参照信号と前記第2の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第3デジタル信号に含まれるオフセットを低減するように前記第3デジタル信号を補正することを特徴とする撮像システムの駆動方法である。

#### 【0008】

また、一の態様は、画素信号を出力する画素と、アナログ信号をデジタル信号に変換するA D変換部と、前記A D変換部に時間に依存して電位が変化する参照信号を供給する参照信号供給部と、を有する撮像装置であって、前記A D変換部は、アナログ信号と前記参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタと、メモリ部と、を有し、前記カウンタが、第1の参照信号の電位が単位時間あたり第1の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第1の信号値のアナログ信号と前記第1の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第1デジタル信号を前記メモリ部が保持し、前記カウンタが、第2の参照信号の電位が単位時間あたり第1の変化量よりも大きい第2の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の信号値のアナログ信号と前記第2の参照信号との比較によって前記比較部が出力する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第2デジタル信号を前記メモリ部が保持し、前記カウンタが、前記第1の参照信号と前記第2の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第1の参照信号と前記第2の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比

10

20

30

40

50

較によって前記比較部が output する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 3 デジタル信号を前記メモリ部が保持し、さらに前記撮像装置が、前記第 1 デジタル信号と前記第 2 デジタル信号とに基づいて、前記第 1 の参照信号と前記第 2 の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第 3 デジタル信号に含まれるオフセットを低減するように前記第 3 デジタル信号を補正する補正部を有することを特徴とする撮像装置である。

#### 【 0 0 0 9 】

また、一の態様は、画素信号を出力する画素と、アナログ信号をデジタル信号に変換する A/D 変換部と、前記 A/D 変換部に時間に依存して電位が変化する参照信号を供給する参照信号供給部と、を有する撮像装置と、前記撮像装置から出力される信号を処理する信号処理部と、を有する撮像システムであって、前記 A/D 変換部は、アナログ信号と前記参照信号とを比較した比較結果信号を出力する比較部と、クロック信号のカウントを行うことでカウント信号を生成するカウンタと、メモリ部と、を有し、前記カウンタが、第 1 の参照信号の電位が単位時間あたり第 1 の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、第 1 の信号値のアナログ信号と前記第 1 の参照信号との比較によって前記比較部が output する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 1 デジタル信号を前記メモリ部が保持し、前記カウンタが、第 2 の参照信号の電位が単位時間あたり第 1 の変化量よりも大きい第 2 の変化量で変化を開始するタイミングに対応して前記カウントを開始してから、前記第 1 の信号値のアナログ信号と前記第 2 の参照信号との比較によって前記比較部が output する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 2 デジタル信号を前記メモリ部が保持し、前記カウンタが、前記第 1 の参照信号と前記第 2 の参照信号の少なくとも一方の変化を開始するタイミングに対応して前記カウントを開始してから、前記第 1 の参照信号と前記第 2 の参照信号の前記少なくとも一方と、前記画素信号に基づく信号との比較によって前記比較部が output する比較結果信号の信号値が変化するタイミングまで前記カウントを行うことによって生成する前記カウント信号によって生成する第 3 デジタル信号を前記メモリ部が保持し、さらに前記撮像システムが、前記第 1 デジタル信号と前記第 2 デジタル信号とに基づいて、前記第 1 の参照信号と前記第 2 の参照信号の一方の電位の変化を開始するタイミングと前記カウンタが前記カウントを開始するタイミングとの差によって生じる、前記第 3 デジタル信号に含まれるオフセットを低減するように前記第 3 デジタル信号を補正する補正部を有することを特徴とする撮像システムである。

#### 【 発明の効果 】

#### 【 0 0 1 0 】

単位時間当たりの電位の変化量が互いに異なる複数の参照信号を用いた撮像装置において、デジタル信号に含まれるオフセットを低減できる。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 1 】

【 図 1 】撮像装置の構成の一例を示した図。

【 図 2 】撮像装置の動作の一例を示した図。

【 図 3 】デジタル信号のビットシフト動作の一例を示した図と、参照信号供給部とカウンタの動作の一例を示した図。

【 図 4 】撮像装置の補正動作の一例を示した図。

【 図 5 】撮像装置の構成の他の一例を示した図。

【 図 6 】撮像装置の補正動作の他の一例を示した図。

【 図 7 】撮像システムの一例を示した図。

【 図 8 】撮像装置の構成の他の一例を示した図と、撮像装置の動作の他の一例を示した図。

【 図 9 】撮像システムの他の一例を示した図と、撮像装置の D.S.P の構成の他の一例を示す。

10

20

30

40

50

した図。

**【発明を実施するための形態】**

**【0012】**

(実施例1)

以下、図面を参照しながら本実施例の撮像装置について説明する。

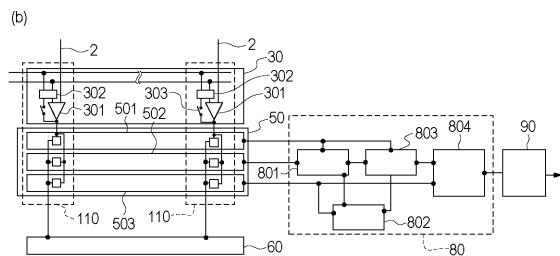

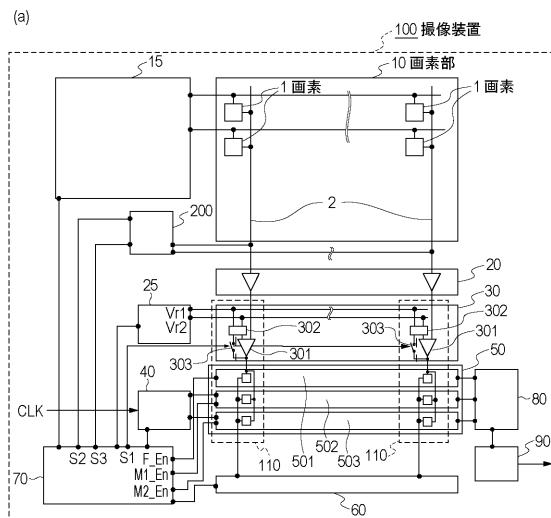

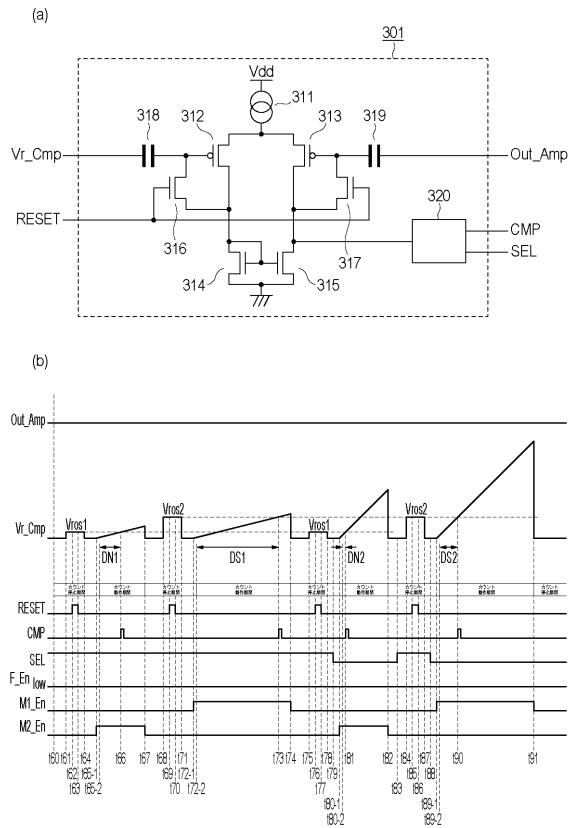

**【0013】**

図1(a)は、本実施例の撮像装置の模式図である。図1(a)に示す撮像装置100は同一半導体基板上に構成されている。

**【0014】**

撮像装置100は、画素1が複数行、複数列並んで配された画素部10を有している。

10

画素1の各々は、垂直走査回路15の走査によって画素信号を増幅部20に出力する。画素1は入射光を光電変換する光電変換部を有する。画素信号とは、ノイズ信号と、入射光を光電変換して得た電荷に基づいて出力する光電変換信号と、を含む。垂直走査回路15はタイミングジェネレータ(以下、TGと表記する)70から出力される信号に基づいて、画素1の行ごとの走査を行う。増幅部20は、画素信号を増幅して比較部30が有する比較回路301に出力する。増幅部20は、比較部30と画素1との間の電気的経路に設けられている。参照信号供給部25は複数の参照信号を各列の選択回路302に出力する。

20

。比較回路301は増幅部20の出力する信号と閾値信号とを比較した結果を示す比較結果信号に基づいて、スイッチ303を介して選択回路302に選択信号SELを出力する。選択回路302は選択信号SELに基づいて、複数の参照信号から比較回路301に出力する参照信号を選択する。比較回路301は、増幅部20が出力する信号と参照信号とを比較した結果を示す比較結果信号をメモリ部50と選択回路302に出力する。メモリ部50はフラグメモリ501、第1メモリ502、第2メモリ503を有する。TG70は、フラグメモリ501に信号F\_Enを出力する。カウンタ40はクロック信号CLKを計数したカウント信号を、第1メモリ502、第2メモリ503に出力する。TG70は、第1メモリ502、第2メモリ503にそれぞれM1\_En、M2\_Enを出力する。

30

。水平走査回路60は各列のフラグメモリ501、第1メモリ502、第2メモリ503が保持したデジタル信号を順次DSP80に出力させる。DSP80は、各列のフラグメモリ501、第1メモリ502、第2メモリ503から出力された信号を処理し、出力回路90に出力する。出力回路90はTG70が出力する信号に基づいて、撮像装置の外部に信号を出力する。

**【0015】**

図1(a)に示した撮像装置では、各列のAD変換部110は、比較部30、メモリ部50を有している。また、AD変換部110の各列は、画素1の各列に対応して設けられている。

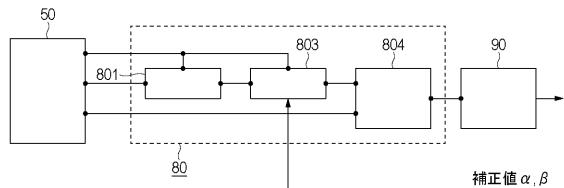

**【0016】**

次に、図1(b)を参照しながら、DSP80の構成について説明する。DSP80は、フラグメモリ501の信号値がLレベルの時に第1メモリ502の信号の各ビットを2ビットずつ上位にシフトするレベルシフト部801を有する。そして、レベルシフト部801は、図4(b)に示す補正動作を行う場合には、補正值取得部802に信号を出力する。さらに、補正值取得部802には、第2メモリ503から信号が出力される。補正值取得部802で生成した補正值は補正演算部803に出力される。補正演算部803は、レベルシフト部801が出力した信号を補正して、S-N部804に補正した信号を出力する。S-N部804は、補正演算部803が出力した信号と第2メモリ503から出力された信号との差を取得し、取得した信号を出力回路90に出力する。DSP80は、本実施例の補正部である。

40

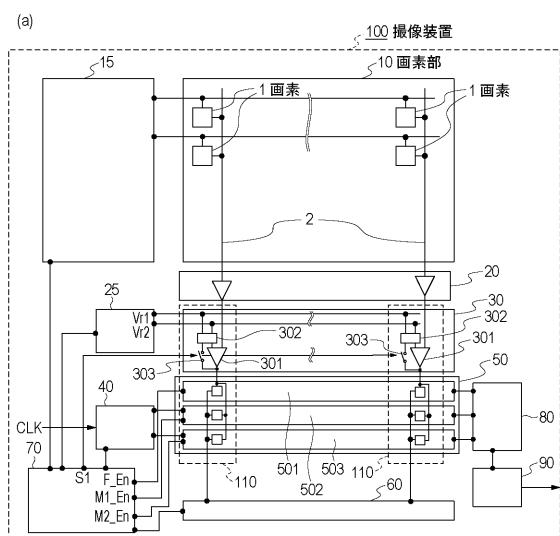

**【0017】**

図2を参照しながら、図1(a)に示した撮像装置の動作について説明する。図2に示したOut\_Ampは、増幅部20の出力する信号を示している。Vr1、Vr2はそれぞれ、参照信号供給部25が出力する参照信号である。参照信号Vr1は単位時間当たり

50

第1の変化量で電位が変化する第1の参照信号である。また、参照信号V<sub>r</sub>2は単位時間当たり第1の変化量よりも大きい第2の変化量で電位が変化する第2の参照信号である。V<sub>r</sub>\_Cmpは、選択回路302が参照信号V<sub>r</sub>1、V<sub>r</sub>2のいずれかを選択して比較回路301に出力する参照信号である。CMPは、比較回路301がOut\_Ampと参照信号V<sub>r</sub>\_CMPとを比較した結果を示す比較結果信号である。S1はスイッチ303の導通を制御する信号であり、Highレベル(以下、Hレベルと表記する)でスイッチ303が導通状態となる。F\_EnをHレベルとすると、フラグメモリ501は比較結果信号CMPを保持する。第1メモリ502は、M1\_EnがHレベルの状態にあり、比較結果信号CMPの信号値が変化した時にカウント信号を保持する。第2メモリ503は、M2\_EnがHレベルの状態にあり、比較結果信号CMPの信号値が変化した時にカウント信号を保持する。10

#### 【0018】

時刻t1では、比較結果信号CMP、信号S1、信号F\_En、M1\_En、M2\_EnはLowレベル(以下、Lレベルと表記する)である。選択信号SELはHレベルである。

#### 【0019】

時刻t2に、画素1からノイズ信号が出力される。増幅部20はノイズ信号を増幅した信号を出力する。

#### 【0020】

時刻t3に、参照信号供給部25は、参照信号V<sub>r</sub>1の間に依存した電位の変化を開始する。選択回路302は、信号SELがHレベルの時、参照信号V<sub>r</sub>1、V<sub>r</sub>2のうち参照信号V<sub>r</sub>1を比較回路301に出力する。また、信号M2\_EnをHレベルとする。20

#### 【0021】

時刻t4に、増幅部20の出力する信号と参照信号V<sub>r</sub>\_CMPとの大小関係が逆転し、比較結果信号CMPの信号値が変化する。第2メモリ503は、この時のカウント信号を保持する。

#### 【0022】

時刻t5に、参照信号供給部25は参照信号V<sub>r</sub>1の間に依存した電位の変化を停止し、参照信号V<sub>r</sub>1の電位を時刻t3の時の電位とする。また、TG70は信号M2\_EnをLレベルとする。30

#### 【0023】

時刻t6に、画素1は光電変換信号を出力する。増幅部20は光電変換信号を増幅した信号を比較回路301に出力する。

#### 【0024】

時刻t7に、参照信号供給部25は参照信号V<sub>r</sub>1の電位を閾値信号VREFとする。閾値信号VREFの電位は、後述する時刻t11の参照信号V<sub>r</sub>1の電位としている。増幅部20の出力する信号が閾値信号VREFよりも大きい場合には、比較回路301はLレベルの比較結果信号を出力する。逆に、閾値信号VREFの方が増幅部20の出力する信号よりも大きい場合には、比較回路301はHレベルの信号を出力する。ここでは、比較回路301の出力する信号がLレベルであるとして説明する。また、TG70は信号S1をHレベルとする。これにより、時刻t7のLレベルの比較結果信号CMPが選択信号SELとして選択回路302に出力される。選択回路302は時刻t9以降に比較回路301に出力する参照信号を、時刻t7の選択信号SELの信号値に基づいて選択する。時刻t7～時刻t9の、選択回路302の動作と選択信号SELの信号値の関係について説明する。時刻t7に選択信号SELがLレベルとなつても、時刻t7から時刻t8の期間、選択回路302は参照信号V<sub>r</sub>1を比較回路301に出力し続ける。そして、時刻t9以降に出力する参照信号を、選択信号SELの信号値に基づいて選択する。また、時刻t7に、TG70は信号F\_EnをHレベルとする。これにより、フラグメモリ501は、時刻t7の比較結果信号CMP、つまり、Lレベルの比較結果信号CMPを保持する。40

#### 【0025】

50

時刻  $t_8$  に、参照信号供給部 25 は参照信号  $V_r 1$  の電位を時刻  $t_3$  での電位とする。また、TG70 は信号  $F\_E_n$  を L レベルとする。

#### 【0026】

時刻  $t_9$  に、参照信号供給部 25 は参照信号  $V_r 1$ 、 $V_r 2$  の時間に依存した電位の変化を開始する。選択回路 302 は、L レベルの選択信号 SEL に基づいて、参照信号  $V_r 2$  を比較回路 301 に出力する。TG70 は、信号  $M1\_E_n$  を H レベルとする。

#### 【0027】

時刻  $t_{10}$  に、増幅部 20 の出力する信号と参照信号  $V_r\_CMP$ との大小関係が逆転し、比較結果信号  $CMP$  の信号値が変化する。第 1 メモリ 502 は、この時のカウント信号を保持する。

10

#### 【0028】

時刻  $t_{11}$  に、参照信号供給部 25 は参照信号  $V_r 1$ 、 $V_r 2$  の時間に依存した電位の変化を停止し、参照信号  $V_r 1$  の電位を時刻  $t_3$  の時の電位とする。TG70 は、信号  $M1\_E_n$  を L レベルとする。

#### 【0029】

時刻  $t_{11}$  の後、水平走査回路 60 は各列のメモリ部 50 を順次走査し、各列のフラグメモリ 501、第 1 メモリ 502、第 2 メモリ 503 の各々から、各々が保持したデジタル信号を DSP80 に出力させる。

#### 【0030】

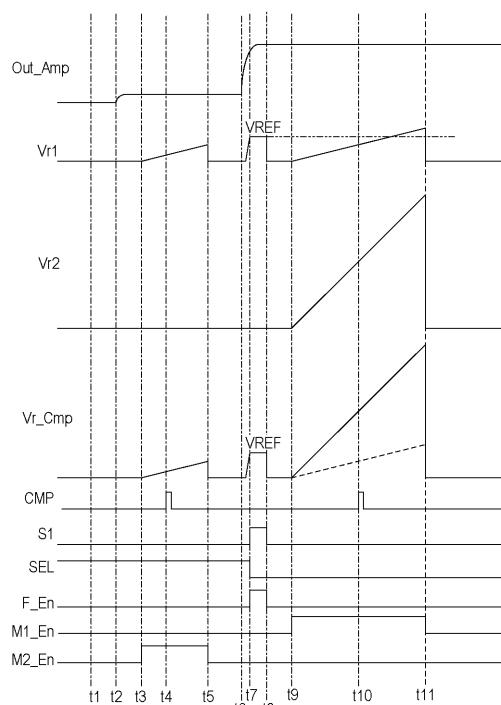

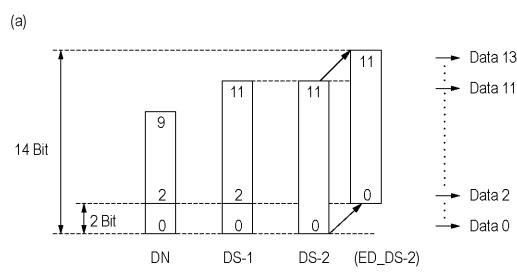

次に図 3 (a) を参照しながら、DSP80 のレベルシフト部 801 の動作について説明する。図 3 (a) で DN として示したのは、第 2 メモリが保持したデジタル信号である。DS-1 として示したのは、参照信号  $V_r 1$  と増幅部 20 の出力する信号との比較によって第 1 メモリ 502 が保持したデジタル信号である。DS-2 として示したのは、参照信号  $V_r 2$  と増幅部 20 の出力する信号との比較によって、先の DS-1 のデジタル信号を保持した第 1 メモリとは異なる列の第 1 メモリが保持したデジタル信号である。第 2 メモリが保持したデジタル信号は 10 ビット、第 1 メモリが保持したデジタル信号は 12 ビットである。ここでは、参照信号  $V_r 1$  の単位時間当たりの電位の変化量に対し、参照信号  $V_r 2$  の単位時間当たりの電位の変化量が 4 倍である例を示している。従って、デジタル信号 DS-2 は、デジタル信号 DS-1 の 4 倍の信号値とする必要がある。 $\log_2 4 = 2$  であるため、デジタル信号 DS-2 の各ビットを上位に 2 ビットずつシフトした信号  $ED\_S-2$  を生成する。S-N 部 804 は、デジタル信号 DS-1 からデジタル信号 DN を差し引く。そして、Data12、Data13 の信号値を 0 として、14 ビットの信号として出力回路 90 に出力する。また、S-N 部 804 は、デジタル信号  $ED\_DS-2$  の Data0、Data1 の信号値を 0 とした後、デジタル信号 DN を差し引く。これにより、DSP80 から出力されるデジタル信号は Data0 から Data13 の 14 ビットの信号となる。尚、第 1 メモリ 502 が保持したデジタル信号が参照信号  $V_r 1$ 、 $V_r 2$  のどちらの参照信号を用いて得たデジタル信号かは、フラグメモリ 501 が保持した信号によって判別できる。つまり、図 2 に示した動作では、フラグメモリ 501 が保持した信号が H レベルであれば、第 1 メモリ 502 が保持した信号は参照信号  $V_r 1$  を用いて得た信号である。同様に、フラグメモリ 501 が保持した信号が L レベルであれば、第 1 メモリ 502 が保持した信号は参照信号  $V_r 2$  を用いて得た信号である。

20

30

30

#### 【0031】

図 3 (b) を参照しながら、参照信号供給部 25 とカウンタ 40 の動作についてさらに述べる。図 3 (b) は、同じ信号値の Out\_Amp を、参照信号  $V_r 1$ 、 $V_r 2$  のそれと比較した場合を示した模式図である。時刻  $t_{20}$  に、参照信号供給部 25 は参照信号  $V_r 1$ 、 $V_r 2$  の時間に依存した電位の変化を開始する。一方、カウンタ 40 は、参照信号  $V_r 1$ 、 $V_r 2$  の電位の変化の開始から遅れて、時刻  $t_{21}$  にクロック信号の計数動作を開始するとする。

40

#### 【0032】

Out\_Amp を参照信号  $V_r 2$  と比較する場合には、時刻  $t_{22}$  に比較結果信号が変

50

化する。Out\_Amp を参照信号 Vr1 と比較する場合には、時刻 t23 に比較結果信号が変化する。時刻 t24 に、参照信号 Vr1、Vr2 の間に依存した電位の変化を停止する。また、カウンタ 40 はクロック信号の計数動作を停止する。

#### 【0033】

ここで、第 1 メモリ 502 が保持したデジタル信号について説明する。まず、参照信号 Vr1 を用いた形態について説明する。参照信号 Vr1 が時間に依存した電位の変化を開始してから、比較結果信号 CMP の信号値が変化するまでの期間 L1 は、

$$L1 = t23 - t20 \quad (1)$$

である。

カウンタ 40 がクロック信号の計数動作を開始してから、比較結果信号 CMP の信号値が変化するまでの期間 LS1 は、

$$LS1 = t23 - t21 \quad (2)$$

である。

さらに、参照信号 Vr1 が時間に依存した電位の変化を開始してから、カウンタ 40 が動作を開始するまでの期間 L0 は、

$$L0 = t21 - t20 \quad (3)$$

である。

LS1 を L1、L0 を用いて表すと、

$$LS1 = L1 - L0 \quad (4)$$

である。

期間 LS1 に相当するカウント信号が、参照信号 Vr1 を用いて生成したデジタル信号である。

#### 【0034】

同様に、参照信号 Vr2 を用いた形態について説明する。参照信号 Vr2 が時間に依存した電位の変化を開始してから、比較結果信号 CMP の信号値が変化するまでの期間 L2 は、

$$L2 = t22 - t20 \quad (4)$$

である。

カウンタ 40 がクロック信号の計数動作を開始してから、比較結果信号 CMP の信号値が変化するまでの期間 LS2 は、

$$LS2 = t22 - t21 \quad (5)$$

である。

LS2 を L2、L0 を用いて表すと、

$$LS2 = L2 - L0 \quad (6)$$

である。

期間 LS2 に相当するカウント信号が、参照信号 Vr2 を用いて生成したデジタル信号である。

#### 【0035】

ここでは、参照信号 Vr1 の単位時間当たりの電位の変化量に対し、参照信号 Vr2 の単位時間当たりの電位の変化量が 4 倍であるとする。この場合、L1 と L2 は、

$$L1 = 4 \times L2 \quad (7)$$

の関係が成り立つ。

そして、図 3 (a) に示したように、参照信号 Vr2 を用いて生成したデジタル信号の各ビットを 2 ビットずつ上位にシフトする。2 ビット上位にシフトしたデジタル信号は期間 LS2 を 4 倍したカウント信号に相当する信号値を有する。4 LS2 を LS1、L0 を用いて表すと、

$$4 LS2 = 4 L2 - 4 L0 = L1 - 4 L0 = LS1 - 3 L0 \quad (8)$$

図 3 (b) では、同じ信号値の增幅部 20 の出力する信号を参照信号 Vr1、Vr2 を用いてそれぞれデジタル信号に変換している。従って、参照信号 Vr2 を用いて得たデジタル信号を 2 ビット上位にシフトした信号の信号値は、理想的には参照信号 Vr1 を用い

10

20

30

40

50

て得たデジタル信号の信号値と一致する。しかし、(8)式に示したように、参照信号  $V_{r1}$ 、 $V_{r2}$  の時間に依存した電位の変化の開始タイミングと、カウンタ 40 のクロック信号の計数の開始タイミングとの差があると、3L0 のオフセットが発生する。

#### 【0036】

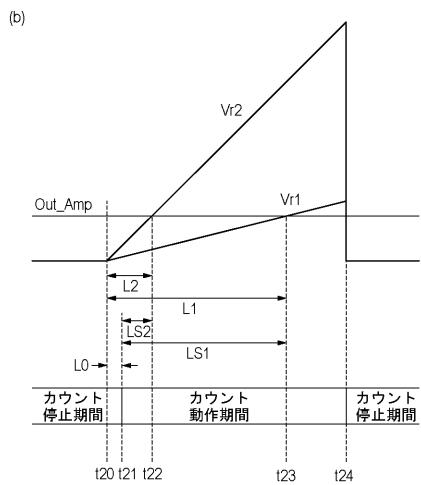

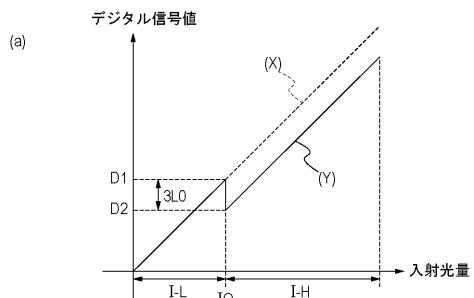

このオフセットを、図 4(a) を用いて説明する。図 4(a) では、後述する本実施例の補正を行わない場合の、DSP80 が出力するデジタル信号について説明する。図 4(a) は、横軸に画素 1 の光電変換部への入射光の光量を示し、縦軸に、DSP80 が出力するデジタル信号の信号値を取っている。(X) は、参照信号  $V_{r1}$  を用いて AD 変換を行った場合、(Y) は、参照信号  $V_{r2}$  を用いて AD 変換を行った場合をそれぞれ示している。I-L は、増幅部 20 の出力する信号と比較する参照信号を  $V_{r1}$  とする領域である。I-H は、増幅部 20 の出力する信号と比較する参照信号を  $V_{r2}$  とする領域である。IO は I-L、I-H との境界である。実線で示したグラフは、領域 I-L では参照信号  $V_{r1}$ 、領域 I-H では、参照信号  $V_{r2}$  を用いて AD 変換を行って生成したデジタル信号と、入射光の光量値との関係を示している。破線で示したグラフは、領域 I-H において、入射光の光量値と、参照信号  $V_{r1}$  を用いて AD 変換して生成したデジタル信号との関係を示している。領域 I-L と領域 I-H の境界 IO の光量値において、3L0 のオフセットが生じる。本実施例では、同一の入射光の光量値において、(X) と (Y) との間で生じるデジタル信号の信号値の差を低減する補正動作を行う。10

#### 【0037】

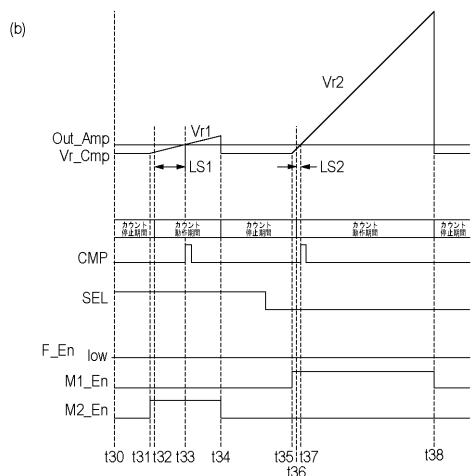

図 4(b) は、本実施例の補正動作を示す図である。図 4(b) に示した補正動作の期間、画素 1 はノイズ信号を出力している。20

#### 【0038】

時刻  $t_{30}$  において、選択信号 SEL は H レベル、信号 M1\_En、M2\_En は L レベルである。

#### 【0039】

時刻  $t_{31}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の時間に依存した電位の変化を開始する。また、TG70 は信号 M2\_En を H レベルとする。時刻  $t_{30}$  から期間 L0 だけ遅れた時刻  $t_{32}$  に、カウンタ 40 はクロック信号の計数を開始する。

#### 【0040】

時刻  $t_{33}$  に、比較結果信号 CMP の信号値が変化する。第 2 メモリ 503 は、この時のカウント信号を保持する。この第 2 メモリ 503 が保持したデジタル信号をデジタル信号 DN1 として表す。デジタル信号 DN1 は、第 1 のアナログ信号と、第 1 の参照信号とを比較して比較部 30 が output する比較結果信号に基づいて AD 変換部 110 が生成した第 1 のデジタル信号である。30

#### 【0041】

時刻  $t_{34}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の時間に依存した電位の変化を停止する。

#### 【0042】

時刻  $t_{34}$  から時刻  $t_{35}$ までの期間に、選択信号 SEL が H レベルから L レベルに変化する。40

#### 【0043】

時刻  $t_{35}$  に、参照信号  $V_{r2}$  の時間に依存した電位の変化を開始する。また、TG70 は信号 M1\_En を H レベルとする。時刻  $t_{35}$  から期間 L0 だけ遅れた時刻  $t_{36}$  に、カウンタ 40 はクロック信号の計数を開始する。

#### 【0044】

時刻  $t_{37}$  に、比較結果信号 CMP の信号値が変化する。第 1 メモリ 502 はこの時のカウント信号を保持する。この第 1 メモリ 502 が保持したデジタル信号を、デジタル信号 DN2 として表す。デジタル信号 DN2 は、第 1 のアナログ信号と、第 2 の参照信号とを比較して比較部 30 が output する比較結果信号に基づいて AD 変換部 110 が生成した第 2 のデジタル信号である。50

**【 0 0 4 5 】**

時刻  $t_{38}$  に、参照信号供給部 25 は参照信号  $V_r 2$  の時間に依存した電位の変化を停止する。

**【 0 0 4 6 】**

次に、補正値取得部 802 の動作について説明する。

**【 0 0 4 7 】**

レベルシフト部 801 で、第 1 メモリが保持したデジタル信号  $D_N 2$  は各ビットが 2 ビットずつ上位にシフトされる。そして、2 ビットずつ上位にシフトされたデジタル信号  $D_N 2$  が、補正値取得部 802 に出力される。補正値取得部 802 は、補正値  $\Delta$  を以下の(9)式で求める。

10

**【 0 0 4 8 】**

$$= D_N 1 - 4 \times D_N 2 \quad (9)$$

$D_N 1$  はデジタル信号  $D_N 1$  の信号値である。 $4 \times D_N 2$  は、デジタル信号  $D_N 2$  を 2 ビットずつ上位にビットシフトしたデジタル信号の信号値である。

**【 0 0 4 9 】**

補正値取得部 802 は、取得した補正値  $\Delta$  を補正演算部 803 に出力する。フラグメモリ 501 が L レベルの列の第 1 メモリ 502 が保持したデジタル信号は、レベルシフト部 801 によって、2 ビットずつ上位にビットシフトされて補正演算部 803 に出力される。補正演算部 803 は、レベルシフト部 801 がビットシフトした信号に補正値  $\Delta$  を加算する。尚、第 1 メモリ 502 が保持したデジタル信号は、画素信号に基づく第 3 のデジタル信号である。

20

**【 0 0 5 0 】**

一方、フラグメモリ 501 が H レベルの列の第 1 メモリ 502 が保持したデジタル信号は、レベルシフト部 801 でのビットシフト動作と補正演算部 803 での補正値  $\Delta$  の加算の動作は行わない。

**【 0 0 5 1 】**

本実施例の撮像装置は、補正値取得部 802、補正演算部 803 を有する。これにより、参照信号の時間に依存した電位の変化の開始とカウンタのクロック信号の計数動作の開始とのタイミング差に起因する、デジタル信号に含まれるオフセットを低減できる。

**【 0 0 5 2 】**

30

本実施例では、参照信号の時間に依存した電位の変化を開始から遅れてカウンタ 40 が計数動作を開始する形態を説明した。他の形態として、参照信号の時間に依存した電位の変化の開始に先立ってカウンタ 40 が計数動作を開始する形態であっても、本実施例の補正動作を適用することができる。図 4(a) で説明した(X) と(Y) では、(X) - (Y) とすると +3L0 のオフセットが生じていた。参照信号の時間に依存した電位の変化を開始に先立ってカウンタ 40 が計数動作を開始する形態では、(X) - (Y) では -3L0 のオフセットが生じる。この形態でも、図 4(b) を参照しながら説明した補正動作を行うことにより、参照信号の時間に依存した電位の変化を開始に先立ってカウンタ 40 が計数動作を開始することによって生じるオフセットを低減したデジタル信号を得ることができる。

40

**【 0 0 5 3 】**

尚、本実施例の補正値  $\Delta$  を、各列の A/D 変換部 110 毎に設ける形態であっても良い。また、複数列の A/D 変換部 110 が出力するデジタル信号を用いて補正値  $\Delta$  を求め、平均化した補正値を補正演算部 803 が用いる形態であっても良い。また、全列の A/D 変換部 110 を複数のブロックに分割し、ブロックごとに補正値  $\Delta$  の平均値を求める形態であっても良い。例えば、このブロックの分割は、複数列の A/D 変換部 110 ごとに、カウント信号を中継するバッファが設けられている場合には、バッファごとにブロックを分割する形態としても良い。これは、バッファはカウント信号の遅延の発生原因となる事があるためである。さらに言えば、参照信号の時間に依存した電位の変化の開始と、メモリ部 50 の各列へのカウント信号の入力タイミングとの差が、バッファを境に異なることがある為

50

である。補正值  $V_{corr}$  を求める際には、複数列の A/D 変換部 110 の第 1 のデジタル信号と第 2 のデジタル信号をそれぞれ平均化し、平均化したそれぞれの第 1 のデジタル信号と第 2 のデジタル信号との差から、複数列の A/D 変換部 110 で共通の補正值  $V_{corr}$  を求めても良い。さらに、補正值  $V_{corr}$  を複数のフレームのそれぞれで取得することで、複数の補正值  $V_{corr}$  を得るようにも良い。この場合には、複数の補正值  $V_{corr}$  を平均化した値を、補正演算部 803 が用いるようにしてもよい。複数の補正值  $V_{corr}$  を平均化することにより、補正值  $V_{corr}$  に含まれるランダムノイズが低減できるので、補正演算部 803 は、入力されるデジタル信号からランダムノイズの影響を低減したデジタル信号を生成することができる。

#### 【0054】

また、本実施例の補正動作は、撮像装置の電源投入直後に行う形態であっても良い。他に、垂直走査回路 15 が画素部 10 の全行を走査した後、次に画素部 10 の走査を開始するまでのブランкиング期間に行う形態であっても良い。また本実施例の補正動作は、動画、静止画などの撮像モードを切り替えた時に行う形態であっても良い。10

#### 【0055】

本実施例の図 4 (b) では、画素 1 がノイズ信号を出力する形態を示した。ノイズ信号以外の形態として、増幅部 20 の入力ノードの電位をリセットし、リセットされた電位に基づいて増幅部 20 が output した信号を用いる形態であっても良い。増幅部 20 が容量帰還型の増幅回路の場合には、差動アンプの出力ノードから差動アンプの入力ノードへの帰還経路を導通させてリセットする形態とすることができる。ここでいう差動アンプの入力ノードが、増幅部 20 の入力ノードである。増幅部 20 の入力ノードの電位がリセットされている形態以外でも、比較回路 301 に入力される信号が時刻  $t_{31}$  から時刻  $t_{34}$  との間と、時刻  $t_{35}$  と時刻  $t_{38}$  との間とで略一定であれば良い。図 4 (b) の補正動作で比較回路 301 に入力される信号が、増幅部 20 のリセットされた入力ノードの電位に基づく信号の場合には、静止画撮影時の画素 1 が露光されている露光蓄積期間中に補正值を求める補正動作を行う形態であっても良い。露光蓄積期間に行う場合は、垂直走査回路 15 が画素部 10 の画素 1 の垂直走査を行わない期間、あるいは、画素部 10 からノイズ信号が出力されている期間に補正值  $V_{corr}$  を求める補正動作を行うのが好適である。20

#### 【0056】

また、本実施例では、参照信号  $V_{ref2}$  の参照信号  $V_{ref1}$  に対する単位時間当たりの電位の変化量の比を 4 倍として説明したが、他の倍率であっても好適に実施することができる。例えば、参照信号  $V_{ref2}$  の参照信号  $V_{ref1}$  に対する単位時間当たりの電位の変化量の比が 8 倍であったとする。レベルシフト部 801 は、フラグメモリ 501 が L レベルの列の第 1 メモリ 502 が保持したデジタル信号を、3 ビットずつ上位にシフトして補正演算部 803 に出力する。補正值取得部 802 は、補正值  $V_{corr}$  を以下の (10) 式で求めればよい。30

#### 【0057】

$$= DN1 - 8 \times DN2 \quad (10)$$

つまり、参照信号  $V_{ref2}$  の参照信号  $V_{ref1}$  に対する単位時間当たりの電位の変化量の比が G とすると、補正值  $V_{corr}$  を以下の (11) 式で求めればよい。

#### 【0058】

$$= DN1 - G \times DN2 \quad (11)$$

また、本実施例では、参照信号  $V_{ref2}$  を用いて生成したデジタル信号を補正する形態について述べた。他の形態として、参照信号  $V_{ref1}$  を用いて生成したデジタル信号を補正するようにも良い。つまり、フラグメモリ 501 が H レベルの列の第 1 メモリ 502 が保持したデジタル信号から (9) 式で得た補正值  $V_{corr}$  を差し引くようにしても良い。この形態であっても、単位時間当たりの電位の変化量が互いに異なる複数の参照信号を用いた撮像装置において、参照信号の時間に依存した電位の変化の開始とカウンタのクロック信号の計数動作の開始とのタイミング差に起因するオフセットを低減できる。また、本実施例では、補正值  $V_{corr}$  を第 1 のデジタル信号と第 2 のデジタル信号との差に基づいて求める形態について述べたが、他の形態としても良い。例えば、第 1 のデジタル信号と第 2 のデジタル信号の時間に依存した電位の変化の開始とカウンタのクロック信号の計数動作の開始とのタイミング差に起因するオフセットを低減できる。また、本実施例では、補正值  $V_{corr}$  を第 1 のデジタル信号と第 2 のデジタル信号との差に基づいて求める形態について述べたが、他の形態としても良い。例えは、第 1 のデジタル信号と第 2 のデジタル信号の時間に依存した電位の変化の開始とカウンタのクロック信号の計数動作の開始とのタイミング差に起因するオフセットを低減できる。40

ル信号の比に基づいて、補正值  $\Delta V$  を求めるようにしても良い。

#### 【0059】

特許文献1に記載の撮像装置では、光電変換信号に基づく電位と、ノイズ信号に基づく電位とをそれぞれ第1の参照信号と第2の参照信号のそれぞれと比較していた。一方、本実施例では、第1の参照信号と第2の参照信号のいずれか一方と、光電変換信号に基づく電位と、の比較とすることができます。また、ノイズ信号に基づく電位と、第1の参照信号と、の比較とすることができます。本実施例の撮像装置は、DSP80がビットシフト動作および、ビットシフト後の下位ビットの信号値を補完する動作を行う。従って、光電変換信号に基づく電位と、ノイズ信号に基づく電位とをそれぞれ第1の参照信号と第2の参照信号のそれぞれと比較せずとも、光電変換信号に基づくデジタル信号と、ノイズ信号に基づくデジタル信号の解像度を合わせることができます。これにより、本実施例の撮像装置は、特許文献1の撮像装置に比して、1行の画素から出力される画素信号のAD変換に要する期間を短縮することができます。10

#### 【0060】

##### (実施例2)

以下、図面を参照しながら本実施例の撮像装置を実施例1と異なる点を中心に説明する。。

#### 【0061】

本実施例の撮像装置では、実施例1の撮像装置で得られた効果に加えて、複数の参照信号間の、単位時間当たりの電位の変化量の比がばらつくことによって生じるデジタル信号の誤差を低減することができます。20

#### 【0062】

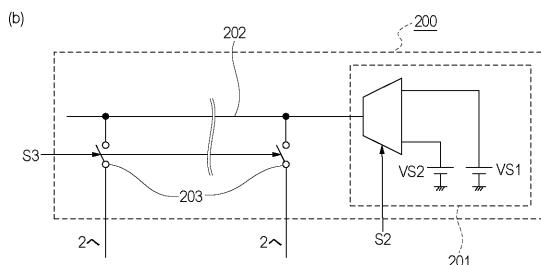

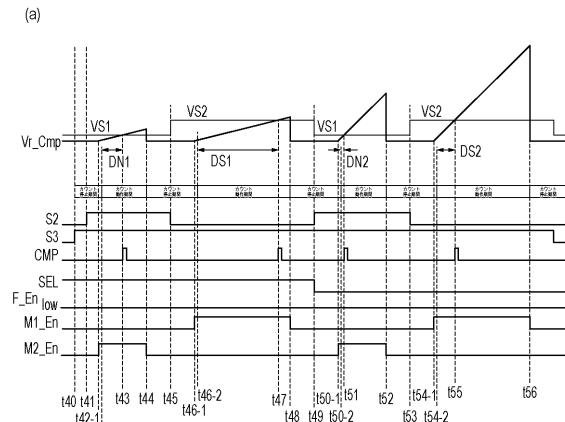

図5(a)は本実施例の撮像装置である。図1(a)に示した撮像装置と同じ機能を有するものについては、図1(a)で付した符号と同じ符号を図5(a)でも付している。本実施例の撮像装置は、垂直信号線2に電気的に接続されたテスト信号供給部200を有する。テスト信号供給部200には、TG70から信号S2、S3が出力される。

#### 【0063】

図5(b)は、テスト信号供給部200の構成の一例を示した図である。テスト信号供給部200は、テスト信号選択部201、テスト信号供給線202、スイッチ203を有している。テスト信号選択部201は、異なる信号値のテスト信号VS1, VS2のいずれかを信号S2に基づいてテスト信号供給線202に出力する。本実施例のテスト信号VS1は、実施例1の画素1のノイズ信号の信号値としている。また、本実施例のテスト信号VS2は、後述する時刻t48における参照信号Vr1の電位以下の信号値としている。テスト信号供給線202は、スイッチ203を介して各列の垂直信号線2に電気的に接続されている。スイッチ203は信号S3をHレベルとすると導通する。30

#### 【0064】

図6(a)を参照しながら、本実施例の撮像装置の補正動作を説明する。

#### 【0065】

時刻t40において、信号S3はHレベルであり、テスト信号供給線202の信号が各列の垂直信号線2に出力されている。選択信号SELはHレベルである。40

#### 【0066】

時刻t41に、信号S2をHレベルとする。これにより、テスト信号VS1が各列の垂直信号線2に出力される。

#### 【0067】

時刻t42-1に、参照信号供給部25は、参照信号Vr1の時間に依存した電位の変化を開始する。TG70は、信号M2\_EnをHレベルとする。続いて、時刻t42-2に、カウンタ40はクロック信号の計数動作を開始する。

#### 【0068】

時刻t43に、テスト信号VS1と参照信号Vr1の電位との大小関係が逆転し、比較結果信号CMPの信号値が変化する。第2メモリ503は、この時点のカウント信号を保50

持する。この第2メモリ503が保持したカウント信号を、本実施例でデジタル信号DN1と表記する。デジタル信号DN1は、第1の参照信号と、第1のアナログ信号と、を比較して比較部30が出力する比較結果信号に基づいて、AD変換部110が生成する第1のデジタル信号である。

【0069】

時刻t44に、参照信号供給部25は参照信号Vr1の電位の変化を停止する。

【0070】

時刻t45に、TG70は信号S2をLレベルとする。これにより、テスト信号VS2がテスト信号供給線202、スイッチ203を介して各列の垂直信号線2に出力される。

【0071】

時刻t46-1に、参照信号供給部25は、参照信号Vr1の時間に依存した電位の変化を開始する。また、TG70は信号M1\_EnをHレベルとする。続いて、時刻t46-2にカウンタ40はクロック信号の計数動作を開始する。

【0072】

時刻t47に、テスト信号VS2と参照信号Vr1との大小関係が逆転し、比較結果信号CMPの信号値が変化する。第1メモリ502は、この時点のカウント信号を保持する。この第1メモリ502が保持したカウント信号を、本実施例でデジタル信号DS1と表記する。デジタル信号DS1は、第1の参照信号と、第1のアナログ信号とは信号値の異なる第2のアナログ信号と、を比較して比較部30が出力する比較結果信号に基づいて、AD変換部110が生成する第4のデジタル信号である。

【0073】

時刻t48に、参照信号供給部25は参照信号Vr1の時間に依存した電位の変化を停止する。時刻t48から時刻t50までの期間に、水平走査回路60は、各列の第1メモリ502、第2メモリ503のそれぞれが保持した信号を順次、DSP80に転送する。

【0074】

時刻t49に、TG70は信号S2をHレベルとする。これにより、テスト信号VS1がテスト信号供給線202、スイッチ203を介して各列の垂直信号線2に出力される。また、TG70は選択信号SELをLレベルとする。

【0075】

時刻t50-1に、参照信号供給部25は参照信号Vr2の時間に依存した電位の変化を開始する。また、TG70は、信号M2\_EnをHレベルとする。続いて、時刻t50-2にカウンタ40はクロック信号の計数動作を開始する。

【0076】

時刻t51に、テスト信号VS1と参照信号Vr2との大小関係が逆転し、比較結果信号の信号値が変化する。第2メモリ503は、この時点のカウント信号を保持する。この第2メモリ503が保持したカウント信号を、本実施例でデジタル信号DN2と表記する。デジタル信号DN2は、第2の参照信号と、第1のアナログ信号と、を比較して比較部30が出力する比較結果信号に基づいて、AD変換部110が生成する第2のデジタル信号である。

【0077】

時刻t52に、参照信号供給部25は参照信号Vr2の時間に依存した電位の変化を停止する。

【0078】

時刻t53に、TG70は信号S2をLレベルとする。

【0079】

時刻t54-1に、参照信号供給部25は、参照信号Vr2の時間に依存した電位の変化を開始する。また、TG70は、信号M1\_EnをHレベルとする。続いて、時刻t54-2にカウンタ40はクロック信号の計数動作を開始する。

【0080】

時刻t55に、テスト信号VS2と参照信号Vr2との大小関係が逆転し、比較結果信

10

20

30

40

50

号の信号値が変化する。第1メモリ502は、この時点のカウント信号を保持する。この第1メモリ502が保持したカウント信号を、本実施例でデジタル信号DS2と表記する。デジタル信号DS2は、第2の参照信号と、第2のアナログ信号と、を比較して比較部30が出力する比較結果信号に基づいて、A/D変換部110が生成する第5のデジタル信号である。

#### 【0081】

時刻t56に、参照信号供給部25は参照信号Vr2の時間に依存した電位の変化を停止する。

#### 【0082】

時刻t56以降、水平走査回路60は、各列の第1メモリ502、第2メモリ503のそれぞれの保持した信号を順次、DSP80に転送する。 10

#### 【0083】

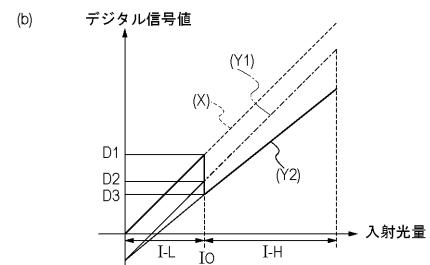

本実施例の補正動作を行わない場合に得られるデジタル信号の信号値について、図6(b)を参照しながら説明する。図6(b)の(Y1)、(Y2)は共に、参照信号Vr2でA/D変換を行った場合について示している。(Y1)は、参照信号Vr2の参照信号Vr1に対する単位時間当たりの電位の変化量の比が4倍になっているものを示している。一方、(Y2)は、参照信号Vr2の参照信号Vr1に対する単位時間当たりの電位の変化量の比が、誤差により4倍よりも小さくなっているものを示している。領域I-L、領域I-H間の境界IOにおいて、(X)と(Y1)では得られるデジタル信号の信号値がそれぞれD1、D2となることは図4(a)で述べた通りである。さらに、(Y2)の場合では、参照信号Vr2の参照信号Vr1に対する単位時間当たりの電位の変化量の比が、誤差により4倍よりも小さいことにより、得られるデジタル信号の信号値は、D2よりも小さいD3となる。本実施例では、同一の入射光の光量値において、(X)と(Y2)との間で生じるデジタル信号の信号値の差を低減する補正動作を行う。 20

#### 【0084】

次に、本実施例の補正動作を説明する。補正動作を行うDSP80の構成は、実施例1と同様とすることができます。

#### 【0085】

補正值取得部802は、以下の(12)式、(13)式により、補正值、を取得する。 30

#### 【0086】

$$= DS_1 - 4 \times DS_2 \quad (12)$$

#### 【0087】

#### 【数1】

$$\beta = \frac{DS_1 - DN_1}{4 \times (DS_2 - DN_2)} \quad (13)$$

#### 【0088】

補正值取得部802は、取得した補正值、を補正演算部803に出力する。フラグメモリ501がLレベルの列の第1メモリ502が保持したデジタル信号は、レベルシフト部801によって、2ビットずつ上位にシフトされて補正演算部803に出力される。補正演算部803は、レベルシフト部801がビットシフトした信号に、以下の(14)式に基づいて補正を行う。 40

#### 【0089】

$$CAL\_DS = + ED\_DS \times \quad (14)$$

(14)式のED\_DSは、フラグメモリ501がLレベルの列の第1メモリ502が保持したデジタル信号を、レベルシフト部801が、2ビットずつ上位にシフトして補正演算部803に出力した信号である。CAL\_DSは、補正演算部803が出力する補正後のデジタル信号である。

#### 【0090】

一方、フラグメモリ 501 が H レベルの列の第 1 メモリ 502 が保持したデジタル信号は、レベルシフト部 801 でのビットシフト動作と補正演算部 803 での補正值 の加算の動作は行わない。

#### 【 0091 】

S N 部 804、出力回路 90 の動作は、実施例 1 と同様とすることができます。

また、補正值 については、(12)式の代わりに、以下の(15)式からでも取得する

ことができる。

#### 【 0092 】

$$= D N 1 - 4 \times \times D N 2 \quad (15)$$

テスト信号 V S 2 を用いて生成したデジタル信号を用いる(12)式に対し、(15)

式は、テスト信号 V S 2 よりも信号値の小さいテスト信号 V S 1 を用いて生成したデジタル信号を用いる。よって、(15)式の方がノイズの影響を受けやすく、補正值 の精度が低くなる可能性がある為、(12)式を用いるのが好ましい。

#### 【 0093 】

本実施例の撮像装置においても、実施例 1 と同様の効果を得ることができる。さらに、本実施例の撮像装置では、複数の参照信号間の、単位時間当たりの電位の変化量の比がばらつくことによって生じるデジタル信号の誤差を低減することができる。

#### 【 0094 】

本実施例の図 6 ( a ) に示した動作では、デジタル信号を生成する順を D N 1、D S 1、D N 2、D S 2 としていた。他の形態として、例えば、デジタル信号を生成する順を、D N 1、D N 2、D S 1、D S 2 としても良い。この形態の場合には、第 1 メモリ 502 にデジタル信号 D N 1、第 2 メモリ 503 にデジタル信号 D N 2 を保持させる。そして、水平走査回路 60 が各列のメモリ部 50 から順次 D S P にデジタル信号を転送する。その後、第 1 メモリ 502 にデジタル信号 D S 1、第 2 メモリ 503 にデジタル信号 D S 2 を保持させる。そして、再び水平走査回路 60 が各列のメモリ部 50 から順次 D S P にデジタル信号を転送する形態とすれば良い。他の撮像装置の例として、2つの第 1 メモリと 2 つの第 2 メモリを有する形態がある。2つの第 1 メモリの各々が、デジタル信号 D N 1、D N 2 をそれぞれ保持する。2つの第 2 メモリがデジタル信号 D S 1、D S 2 をそれぞれ保持する。この形態の場合には、4つのメモリが必要となる。一方、本実施例の撮像装置では、各列の A D 変換部 110 の第 1 メモリ 502 と第 2 メモリ 503 とを、それぞれ 1 つずつとすることができます。これにより、メモリ部 50 の回路規模を、各列の A D 変換部 110 が第 1 メモリ 502 と第 2 メモリとをそれぞれ 2 つずつ設ける場合に比して縮小することができる。

#### 【 0095 】

先に述べた、デジタル信号 D N 1、D N 2、D S 1、D S 2 の順にデジタル信号を得る形態について再び説明する。この形態では、図 6 ( a ) の形態に比して、信号値の揃ったテスト信号 V S 1 をデジタル信号に変換できるため、デジタル信号 D N 1 とデジタル信号 D N 2 に含まれるノイズ成分の変動を低減することができる。これは、テスト信号供給部 200 の出力するテスト信号ではなく、画素 1 の出力する信号を用いる場合も同様である。つまり、画素 1 のノイズ信号に基づく信号を参照信号 V r 1、V r 2 のそれぞれで A D 変換する。その後、画素 1 の光電変換信号に基づく信号を参照信号 V r 1、V r 2 のそれぞれで A D 変換する。この形態であっても、(12)、(13)式の補正值 、 を取得できる。そして、図 6 ( a ) の順で A D 変換を行う構成に比して、参照信号 V r 1、V r 2 のそれぞれで A D 変換されるノイズ信号と光電変換信号のそれぞれの信号値に変動が生じにくい。これにより、ノイズ信号、光電変換信号の信号値の変動を低減したデジタル信号を得ることができる。よって、補正值 、 をより正確に求めることができる。この効果は、デジタル信号 D N 1、D N 2、D S 1、D S 2 の順にデジタル信号を得る形態に限定されない。テスト信号 V S 1 に基づく 2 つのデジタル信号の生成動作を順に行う。また、テスト信号 V S 2 に基づく 2 つのデジタル信号の生成動作を順に行う。例えば、デジタル信号の生成順を、D N 2、D N 1、D S 2、D S 1 であっても良い。また、D S 1、D

10

20

30

40

50

S 2、D N 2、D N 1であっても良い。つまり、第1のデジタル信号と第2のデジタル信号の一方を生成した後、第1のデジタル信号と第2のデジタル信号の他方を生成する。また、第4のデジタル信号と第5のデジタル信号の一方を生成した後、第4のデジタル信号と第5のデジタル信号の他方を生成する形態であれば良い。

#### 【0096】

また、本実施例の撮像装置では、参照信号V r 2を用いて生成したデジタル信号を補正する形態を説明した。他の形態として、実施例1でも述べた様に、参照信号V r 1を用いて生成したデジタル信号を補正するようにしても良い。つまり、フラグメモリ501がHレベルの列の第1メモリ502が保持したデジタル信号を補正值で除した後、補正值を差し引く。これにより、実施例1で述べた効果と同様の効果を得ることができる。また、本実施例の撮像装置では、複数の参照信号間の、単位時間当たりの電位の変化量の比がばらつくことによって生じるデジタル信号の誤差を低減することができる。10

#### 【0097】

本明細書では、カウンタ40が各列のA D変換部110に共通のカウント信号を供給する形態を基に説明した。他の形態として、各列のA D変換部110が、カウンタを有する形態であっても良い。この形態の一例としては、各列のA D変換部110が、カウンタ、フラグメモリ、第1メモリ、第2メモリを有する形態がある。この形態でも、カウンタ、フラグメモリ、第1メモリ、第2メモリの動作については、各実施例で述べた動作と同様とすることができる。

#### 【0098】

また、本明細書では、参照信号の時間に依存した電位の変化がスロープ状に行われる形態として説明したが、階段状に変化する形態の参照信号であっても良い。階段状に電位が変化する参照信号についても、時間に依存して電位が変化する参照信号の一例である。20

#### 【0099】

##### (実施例3)

本実施例は、テスト信号供給部200が出力するテスト信号の代わりに、参照信号供給部25の出力信号を用いて補正值及びを取得する撮像装置である。

#### 【0100】

以下、図面を参照しながら実施例2と異なる点を中心に説明をする。

#### 【0101】

本実施例の撮像装置の構成は、図1と同様である。30

#### 【0102】

本実施例の比較回路301の構成について図8(a)に示す。

#### 【0103】

電流源311は、一端は電源電圧V d dが供給され、他の一端がP M O Sトランジスタ312、313のそれぞれの一方の主ノードに電気的に接続される。P M O Sトランジスタ312、313のそれぞれの他方の主ノードは、N M O Sトランジスタ314、315のそれぞれの一方の主ノードに電気的に接続される。N M O Sトランジスタ314、315のそれぞれの他方の主ノードにはグランド電圧が供給される。N M O Sトランジスタ314、315の制御ノードは共通して、N M O Sトランジスタ314の一方の主ノードに電気的に接続される。P M O Sトランジスタ312、313のそれぞれの制御ノードは、容量素子318、319のそれぞれの一方のノードに電気的に接続される。容量素子318の他方のノードには、参照信号V r \_ C m pが入力される。容量素子319の他方のノードには、出力信号O u t \_ A m pが入力される。40

#### 【0104】

P M O Sトランジスタ312、313の制御ノードは、それぞれN M O Sトランジスタ316、317のそれぞれの一方の主ノードに電気的に接続されている。また、P M O Sトランジスタ312とN M O Sトランジスタ314の主ノード同士が電気的に接続されたノードと、N M O Sトランジスタ316の他方の主ノードとが電気的に接続されている。また、P M O Sトランジスタ313とN M O Sトランジスタ315の主ノード同士が電気50

的に接続されたノードと、NMOSトランジスタ317の他方の主ノードとが電気的に接続されている。NMOSトランジスタ316、317のそれぞれの制御ノードには、TG70から信号RESETが入力される。TG70が信号RESETをHレベルとすると、PMOSトランジスタ312とNMOSトランジスタ314の主ノード同士が電気的に接続されたノードと、PMOSトランジスタ312の制御ノードとが短絡される。また、PMOSトランジスタ313とNMOSトランジスタ317の主ノード同士が電気的に接続されたノードと、PMOSトランジスタ313の制御ノードとが短絡される。これにより、PMOSトランジスタ312、313のそれぞれの制御ノードの電位はほぼ同電位となる。

## 【0105】

比較回路301は、比較出力回路320を有する。

## 【0106】

PMOSトランジスタ313とNMOSトランジスタ313の主ノード同士が電気的に接続されたノードは、さらに比較出力回路320に電気的に接続されている。比較出力回路320は、参照信号Vr\_Cmpと出力信号Out\_Ampとの比較結果に基づき比較結果信号CMPと選択信号SELを選択回路302に出力する。また、図8(a)では不図示であるが、比較出力回路320が出力する信号SELの信号値は、参照信号Vr\_Cmpと出力信号Out\_Ampとの比較結果によらず、TG70による制御によって強制的に設定することができる。

## 【0107】

続いて、本実施例の撮像装置の動作について説明する。

## 【0108】

図8(b)は本実施例の動作を示したタイミング図である。図8(b)に示す期間、画素1はノイズ信号を出力している。出力信号Out\_Ampは図8(b)に示す期間、ノイズ信号を増幅した信号レベルである。また、図8(b)に示す期間、比較出力回路320は、TG70の制御に基づく信号値の選択信号SELを選択回路302に出力する。

## 【0109】

時刻t60において、TG70は選択信号SELをHレベルとしているため、選択回路302は参照信号Vr1を比較回路301に出力している。また、TG70は信号RESETをLレベルとしている。

## 【0110】

時刻t61に、参照信号供給部25は、参照信号Vr1の電位をVros1とする。

## 【0111】

時刻t62に、TG70は信号RESETをHレベルとした後、時刻t63に信号RESETをLレベルとする。これにより、PMOSトランジスタ312、313の制御ノード同士の電位がほぼ等しくなる。出力信号Out\_Ampの信号値は一定のため、参照信号Vr1の電位が、電位Vros1よりも振幅が大きくなった時に、信号CMPの信号値がLレベルからHレベルに変化する。

## 【0112】

時刻t64に、参照信号供給部25は参照信号Vr1の電位を時刻t60の電位とする。

## 【0113】

時刻t65-1に、参照信号供給部25は、参照信号Vr1の時間に依存した電位の変化を開始する。TG70は、信号M2\_EnをHレベルとする。続いて、時刻t65-2に、カウンタ40はクロック信号の計数動作を開始する。

## 【0114】

時刻t66に、参照信号Vr\_Cmpが電位Vros1の振幅よりも大きくなる。この時、比較結果信号CMPの信号値がLレベルからHレベルに変化する。時刻t66に信号CMPの信号値がLレベルからHレベルに変化したことを受け、第2メモリ503がデジタル信号DN1を保持する。

10

20

30

40

50

**【0115】**

時刻  $t_{6.7}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の電位の変化を終了する。

**【0116】**

時刻  $t_{6.8}$  に、参照信号供給部 25 は、参照信号  $V_{r1}$  の電位を  $V_{ros1}$  より振幅の大きい電位  $V_{ros2}$  とする。時刻  $t_{6.9}$  に TG70 は信号 Reset を H レベルとした後、時刻  $t_{6.3}$  に信号 Reset を L レベルとする。出力信号 Out\_Amp の信号値は一定のため、参照信号  $V_{r1}$  の電位が、電位  $V_{ros2}$  よりも振幅が大きくなった時に、信号 CMP の信号値が L レベルから H レベルに変化する。

**【0117】**

時刻  $t_{7.1}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の電位を時刻  $t_{6.0}$  の電位とする 10

。

**【0118】**

時刻  $t_{7.2-1}$  に、参照信号供給部 25 は、参照信号  $V_{r1}$  の時間に依存した電位の変化を開始する。また、TG70 は信号 M1\_En を H レベルとする。続いて、時刻  $t_{7.2-2}$  にカウンタ 40 はクロック信号の計数動作を開始する。

**【0119】**

時刻  $t_{7.3}$  に、参照信号  $V_{r_Cmp}$  が  $V_{ros2}$  を越える。このとき、比較器 301 は大小関係が逆転したと判断し、比較結果信号 CMP の信号値が変化する。時刻  $t_{7.3}$  に信号 CMP の信号値が L レベルから H レベルに変化したことを受け、第 1 メモリ 502 がデジタル信号 DS1 を保持する。 20

**【0120】**

時刻  $t_{7.4}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の時間に依存した電位の変化を終了する。

**【0121】**

時刻  $t_{7.4}$  から時刻  $t_{7.5}$ までの期間に、水平走査回路 60 は、各列の第 1 メモリ 502、第 2 メモリ 503 のそれぞれが保持した信号を順次、DSP80 に転送する。

**【0122】**

時刻  $t_{7.5}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の電位を  $V_{ros1}$  にする。

**【0123】**

時刻  $t_{7.6}$  に、TG70 は信号 Reset を H レベルとした後、時刻  $t_{7.6}$  に信号 Reset を L レベルとする。出力信号 Out\_Amp の信号値は一定のため、後に入力される参照信号  $V_{r2}$  の電位が、電位  $V_{ros1}$  よりも振幅が大きくなった時に、信号 CMP の信号値が L レベルから H レベルに変化する。 30

**【0124】**

時刻  $t_{7.8}$  に、参照信号供給部 25 は参照信号  $V_{r1}$  の電位を時刻  $t_{6.0}$  の電位とする 。

**【0125】**

時刻  $t_{7.9}$  に、TG70 は選択信号 SEL を L レベルとする。選択回路 302 は参照信号  $V_{r2}$  を比較回路 301 に出力する。

**【0126】**

時刻  $t_{8.0-1}$  に、参照信号供給部 25 は、参照信号  $V_{r2}$  の時間に依存した電位の変化を開始する。TG70 は、信号 M2\_En を H レベルとする。続いて、時刻  $t_{8.0-2}$  に、カウンタ 40 はクロック信号の計数動作を開始する。 40

**【0127】**

時刻  $t_{8.1}$  に、参照信号  $V_{r2}$  の電位が電位  $V_{ros1}$  よりも振幅が大きくなる。この時、比較結果信号 CMP の信号値が L レベルから H レベルに変化する。時刻  $t_{8.1}$  に信号 CMP の信号値が L レベルから H レベルに変化したことを受け、第 2 メモリ 503 がデジタル信号 DN2 を保持する。

**【0128】**

時刻  $t_{8.2}$  に、参照信号供給部 25 は参照信号  $V_{r2}$  の電位の変化を終了する。 50

**【 0 1 2 9 】**

時刻  $t_{83}$  に、TG70 は選択信号 SEL を H レベルとなる。選択回路 302 は参照信号 Vr1 を比較回路 301 に出力する。

**【 0 1 3 0 】**

時刻  $t_{84}$  に、参照信号供給部 25 は参照信号 Vr1 の電位を Vros2 とする。

**【 0 1 3 1 】**

時刻  $t_{85}$  に TG70 は信号 Reset を H レベルとした後、時刻  $t_{86}$  に信号 Reset を L レベルとする。出力信号 Out\_Amp の信号値は一定のため、後に入力される参照信号 Vr2 の電位が、電位 Vros2 よりも振幅が大きくなつた時に、信号 CMP の信号値が L レベルから H レベルに変化する。

10

**【 0 1 3 2 】**

時刻  $t_{87}$  に、参照信号供給部 25 は参照信号 Vr1 の電位を時刻  $t_{60}$  の電位とする。

**【 0 1 3 3 】**

時刻  $t_{88}$  に、TG70 は選択信号 SEL を L レベルとする。選択回路 302 は参照信号 Vr2 を比較回路 301 に出力する。

**【 0 1 3 4 】**

時刻  $t_{89-1}$  に、参照信号供給部 25 は、参照信号 Vr2 の時間に依存した電位の変化を開始する。また、TG70 は信号 M1\_En を H レベルとする。続いて、時刻  $t_{89-2}$  にカウンタ 40 はクロック信号の計数動作を開始する。

20

**【 0 1 3 5 】**

時刻  $t_{90}$  に、参照信号 Vr\_Cmp の電位が電位 Vros2 よりも振幅が大きくなる。この時、比較結果信号 CMP の信号値が L レベルから H レベルに変化する。時刻  $t_{90}$  に信号 CMP の信号値が L レベルから H レベルに変化したことを受け、第 1 メモリ 502 にデジタル信号 DS2 が保持される。

**【 0 1 3 6 】**

時刻  $t_{91}$  に、参照信号供給部 25 は参照信号 Vr2 の時間に依存した電位の変化を停止する。

**【 0 1 3 7 】**

時刻  $t_{91}$  以降の期間に、水平走査回路 60 は、各列の第 1 メモリ 502、第 2 メモリ 503 のそれぞれが保持した信号を順次、DSP80 に転送する。

30

**【 0 1 3 8 】**

DSP80 及び出力回路 90 は、上記動作で取得したデジタル信号 DN1、DN2、DS1、DS2 を用いて、実施例 2 と同様の動作を行うことができる。

**【 0 1 3 9 】**

以上述べた通り、本実施例の撮像装置は、テスト信号供給部 200 の出力するテスト信号の代わりに、参照信号供給部 25 の出力信号を用いて補正值 及び を取得することができる。

**【 0 1 4 0 】**

(実施例 4 )

40

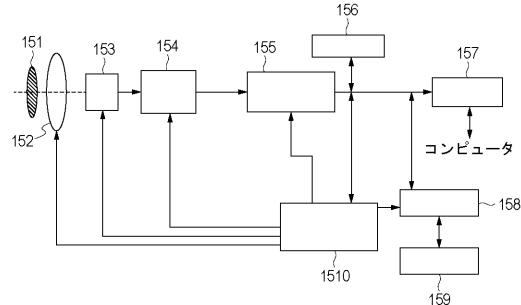

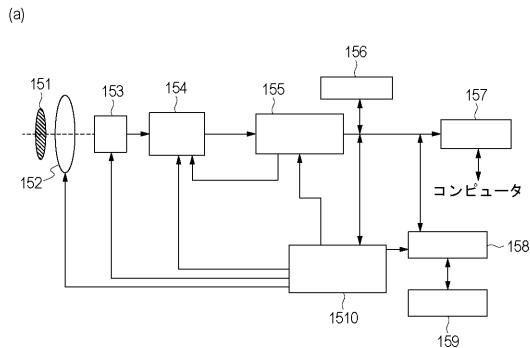

図 7 は、実施例 1 ~ 3 で述べた撮像装置を撮像装置 154 として用いた撮像システムである。

**【 0 1 4 1 】**

図 7 において、撮像システムはレンズの保護のためのバリア 151、被写体の光学像を撮像装置 154 に結像させるレンズ 152、レンズ 152 を通った光量を可変にするための絞り 153 を有する。さらに撮像システムは、撮像装置 154 より出力される信号の処理を行う出力信号処理部 155 を有する。撮像装置 154 から出力される信号は、被写体を撮影した画像を生成するための撮像信号である。出力信号処理部 155 は撮像装置 154 から出力される撮像信号を必要に応じて各種の補正、圧縮を行つて画像を生成する。レンズ 152、絞り 153 は撮像装置 154 に光を集光する光学系である。

50

**【 0 1 4 2 】**

図7に例示した撮像システムはさらに、画像データを一時的に記憶する為のバッファメモリ部156、外部コンピュータ等と通信する為の外部インターフェース部157を有する。さらに撮像システムは、撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体159、記録媒体159に記録または読み出しを行うための記録媒体制御インターフェース部158を有する。さらに撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510を有する。

**【 0 1 4 3 】**

図7に示した撮像システムでは、実施例1～3で述べたDSP80を、撮像装置154の外部に設けられた出力信号処理部155が有する形態とすることができます。この形態の場合には、出力信号処理部155が、補正部を有する信号処理部である。この形態としても、本実施例の撮像システムは、実施例1～3で述べた効果と同様の効果を得ることができます。他の形態として、実施例1～3で述べたDSP80を、撮像装置154の外部に設けられた全体制御・演算部1510が有する形態とすることができます。この形態の場合は、全体制御・演算部1510が、補正部を有する信号処理部である。

10

**【 0 1 4 4 】****( 実施例 5 )**

図9(a)は、本実施例の撮像システムである。図7と同じ機能を有するものについては、図7で付した符号と同じ符号を図9(a)でも付している。以下では、実施例4と異なる部分を中心に説明する。

20

**【 0 1 4 5 】**

本実施例の撮像システムの撮像装置154の実施例2に記載の撮像装置100と異なる点は、補正值取得部802を有さない点である。

**【 0 1 4 6 】**

図9(b)に本実施例における、撮像装置154内のDSP80の構成を示す。図1で付した符号と同じ機能を有するものについては、図1で付した符号と同じ符号を図9(b)でも付している。DSP80は、レベルシフト部801、補正演算部803、S-N部804から構成される。尚、実施例2で述べた補正值取得部802は、本実施例の撮像システムでは出力信号処理部155が有している。撮像装置154は、同一半導体基板上に設けられており、補正值取得部802は、撮像装置154が設けられた半導体基板とは別の半導体基板上に設けられている。

30

**【 0 1 4 7 】**

DSP80は、AD変換部110がテスト信号をAD変換した際には、得られたデジタル信号DN1、DN2、DS1、DS2を、出力回路90を介して出力信号処理部155に出力する。出力信号処理部155に設けられた補正值取得部802は、デジタル信号DN1、DN2、DS1、DS2に基づき補正值 及び を取得する。補正值取得部802は、取得された補正值 及び を補正演算部803に出力する。

**【 0 1 4 8 】**

補正演算部803は、出力信号処理部155から出力された補正值 及び を保持する。また、AD変換部110が画素信号に基づく信号をAD変換した際には、補正演算部803は、補正值 及び を用いて、実施例2と同様の補正動作を行う。つまり、補正演算部803は、補正值取得部802から出力される補正值に基づいて、画素信号に基づくデジタル信号を補正する補正部である。

40

**【 0 1 4 9 】**

以上述べたように、デジタル信号DN1、DN2、DS1、DS2から補正值 および を取得する回路を、撮像装置と異なる半導体基板上に設けても、実施例2と同様の効果を得ることができます。

**【 0 1 5 0 】**

尚、本実施例の撮像システムが有する撮像装置154は、DSP80の構成を除いて実施例2の撮像装置と同様とした。他の例として、本実施例の撮像システムが有する撮像装

50

置 1 5 4 が、D S P 8 0 の構成を除いて実施例 3 の撮像装置と同様としても良い。この例の撮像システムにおいても、実施例 3 と同様の効果を得ることができる。

### 【 0 1 5 1 】

また、本実施例では撮像装置 1 5 4 がデジタル信号 D N 1 、 D N 2 、 D S 1 、 D S 2 を生成する例を説明した。他の例として、撮像装置 1 5 4 がデジタル信号 D S 1 、 D S 2 を生成せず、デジタル信号 D N 1 、 D N 2 を生成する場合には、実施例 1 と同様の効果を得ることができる。

### 【 符号の説明 】

#### 【 0 1 5 2 】

1 画素

10

1 0 画素部

1 5 垂直走査回路

2 0 増幅部

3 0 比較部

4 0 カウンタ

5 0 メモリ部

6 0 水平走査回路

7 0 タイミングジェネレータ ( T G )

8 0 D S P

9 0 出力回路

20

1 0 0 撮像装置

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

(b)

---

フロントページの続き

(72)発明者 吉田 大介

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 橋本 誠二

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2013-229852(JP,A)

特開2011-244249(JP,A)

特開2009-296423(JP,A)

特開2008-067357(JP,A)

特開2003-219279(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762

H03M 1/00 - 1/88