(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-140972

(P2010-140972A)

(43) 公開日 平成22年6月24日(2010.6.24)

(51) Int.Cl.

**H01L 21/822 (2006.01)**

**H01L 27/04 (2006.01)**

**H01L 21/3205 (2006.01)**

**H01L 23/52 (2006.01)**

F 1

H01L 27/04

H01L 27/04

H01L 21/88

C

H

Z

テーマコード(参考)

5FO33

5FO38

審査請求 未請求 請求項の数 14 O L (全 12 頁)

(21) 出願番号

特願2008-313662 (P2008-313662)

(22) 出願日

平成20年12月9日 (2008.12.9)

(71) 出願人 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100146178

弁理士 浜田 满広

(72) 発明者 松井 孝二郎

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

F ターム(参考) 5F033 HH11 HH12 JJ11 JJ12 KK11

KK12 MM22 NN38 RR04 UU04

VV105F038 AC04 AC05 AC15 BH10 BH19

CA02 CA07 EZ20

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】ノイズの影響を低減できるとともに、レイアウト効率のよいMIM型容量素子を提供する。

【解決手段】半導体装置100は、下部電極112と、下部電極112上に設けられた中間電極116と、中間電極116上に設けられた上部電極124と、下部電極112と中間電極116との間に設けられた第1の絶縁膜と、中間電極116と上部電極124との間に設けられた第2の絶縁膜と、中間電極116と同層に設けられている第1の接続配線118と、下部電極112と第1の接続配線118とを電気的に接続する第1のビア114と、第1の接続配線118と上部電極124とを電気的に接続する第2のビア122とを有し、第1の接続配線118、第1のビア114、および、第2のビア122が、中間電極116の第1の辺に隣接して設けられているとともに、中間電極116の第1の辺と対向する第2の辺に隣接して設けられている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

前記半導体基板上に設けられた下部電極と、

前記下部電極上に設けられた中間電極と、

前記中間電極上に設けられた上部電極と、

前記下部電極と前記中間電極との間に設けられた第1の絶縁膜と、

前記中間電極と前記上部電極との間に設けられた第2の絶縁膜と、

前記中間電極と同層に設けられ、前記中間電極と電気的に絶縁されている第1の接続配線と、

10

前記下部電極と前記第1の接続配線とを電気的に接続する第1のビアと、

前記第1の接続配線と前記上部電極とを電気的に接続する第2のビアと、

を有し、

前記下部電極と、前記中間電極と、前記上部電極と、前記第1の絶縁膜と、前記第2の絶縁膜とが、MIM型容量素子を構成していて、

前記第1の接続配線、前記第1のビア、および、前記第2のビアが、前記中間電極の第1の辺に隣接して設けられているとともに、前記中間電極の前記第1の辺と対向する第2の辺に隣接して設けられていることを特徴とする半導体装置。

**【請求項 2】**

請求項1に記載の半導体装置において、

20

前記上部電極は、前記上部電極と同層に設けられた上部電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

**【請求項 3】**

請求項1または請求項2に記載の半導体装置において、

前記中間電極は、前記中間電極と同層に設けられた中間電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

**【請求項 4】**

請求項1に記載の半導体装置において、

前記下部電極、前記中間電極、および、前記上部電極には、スリット状の溝が設けられていることを特徴とする半導体装置。

30

**【請求項 5】**

請求項4に記載の半導体装置において、

前記上部電極は、前記上部電極と同層に設けられた上部電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

**【請求項 6】**

請求項4または請求項5に記載の半導体装置において、

前記中間電極は、前記中間電極と同層に設けられた中間電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

**【請求項 7】**

請求項1または請求項4に記載の半導体装置において、

前記中間電極と同層に設けられ、前記中間電極と電気的に絶縁されている第2の接続配線と、

前記下部電極と前記第2の接続配線とを接続する第3のビアと、

前記第2の接続配線と前記上部電極とを接続する第4のビアと、

をさらに有し、

前記第2の接続配線、前記第3のビア、および、前記第4のビアが、前記中間電極の前記第1の辺と直交する第3の辺に隣接して設けられているとともに、前記中間電極の前記第3の辺と対向する第4の辺に隣接して設けられていることを特徴とする半導体装置。

**【請求項 8】**

請求項7に記載の半導体装置において、

50

前記上部電極は、前記上部電極と同層に設けられた上部電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

【請求項 9】

請求項 7 または請求項 8 に記載の半導体装置において、

前記中間電極は、前記中間電極と同層に設けられた中間電極引き出し配線に電気的に接続されていることを特徴とする半導体装置。

【請求項 10】

請求項 1 乃至請求項 6 のいずれか一項に記載の半導体装置において、前記第 1 のビアおよび前記第 2 のビアは、スリット状のビアであることを特徴とする半導体装置。

【請求項 11】

請求項 7 乃至請求項 9 のいずれか一項に記載の半導体装置において、

前記第 1 のビア、前記第 2 のビア、前記第 3 のビア、および前記第 4 のビアは、スリット状のビアであることを特徴とする半導体装置。

【請求項 12】

請求項 1 乃至請求項 11 のいずれか一項に記載の半導体装置において、複数の前記 MIM 型容量素子が、マトリックス状に配置されていることを特徴とする半導体装置。

【請求項 13】

請求項 2、請求項 5、請求項 8 のいずれか一項に記載の半導体装置において、複数の前記 MIM 型容量素子が、マトリックス状に配置されるとともに、複数の前記 MIM 型容量素子が、前記上部電極引き出し配線を介して電気的に接続されていることを特徴とする半導体装置。

【請求項 14】

請求項 3、請求項 6、請求項 9 のいずれか一項に記載の半導体装置において、複数の前記 MIM 型容量素子が、マトリックス状に配置されるとともに、複数の前記 MIM 型容量素子が、前記上部電極引き出し配線および前記中間電極引き出し配線を介して電気的に接続されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に高精度な容量素子を有する半導体装置に関する。

30

【背景技術】

【0002】

アナログ回路を有する半導体装置には、容量素子が使用されることがある。例えば、特許文献 1 には、MIM (Metal-Insulator-Metal) 型容量素子の上部電極および下部電極と同層にダミー配線を形成し、上部電極の上層および下部電極の下層にさらにダミー配線を形成し、これらのダミー配線を接地することによって、容量素子へのノイズの影響を少なくすることが開示されている。

【0003】

また、特許文献 2 には、MIM 型容量素子の上部電極の上層に上部シールド層を設け、下部電極の下層に下部シールド層を設け、上部シールド層と下部シールド層との間をビアで接続することによって、容量素子へのノイズの結合を防止することが開示されている。

【0004】

さらに、特許文献 3 には、上部電極と中間電極と下部電極とを有し、上部電極と下部電極がビアを介して接続されている MIM 型容量素子によって、容量素子の占有面積を低減させながら、容量素子の寄生容量を低減することを開示している。

【0005】

【特許文献 1】特開 2004-146632 号公報

【特許文献 2】特開 2003-152085 号公報

【特許文献 3】特開 2007-5719 号公報

【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】****【0006】**

しかしながら、特許文献1においては、MIM型容量素子の上部電極および下部電極がビアによって囲まれていないので、ノイズの低減の点で改善の余地があった。また、上部電極の上層および下部電極の下層にさらにダミー配線を形成しているので、容量値に寄与する配線の割合が小さく、レイアウト効率の点で改善の余地があった。

**【0007】**

また、特許文献2においては、MIM型容量素子の上部電極の上層に上部シールド層を設け、MIM型容量素子の下部電極の下層に下部シールド層を設けているので、容量値に寄与する配線の割合が小さく、レイアウト効率の点で改善の余地があった。

10

**【0008】**

さらに、特許文献3においては、MIM型容量素子の上部電極と下部電極を電気的に接続するビアが片側だけにしか設けられてないので、ノイズの低減の点で改善の余地があった。

**【課題を解決するための手段】****【0009】**

上述した課題を鑑みて、本発明によれば、半導体基板と、半導体基板上に設けられた下部電極と、下部電極上に設けられた中間電極と、中間電極上に設けられた上部電極と、下部電極と前記中間電極との間に設けられた第1の絶縁膜と、中間電極と上部電極との間に設けられた第2の絶縁膜と、中間電極と同層に設けられ、中間電極と電気的に絶縁されている第1の接続配線と、下部電極と第1の接続配線とを電気的に接続する第1のビアと、第1の接続配線と上部電極とを電気的に接続する第2のビアとを有し、下部電極と、中間電極、上部電極と、第1の絶縁膜と、第2の絶縁膜とが、MIM型容量素子を構成していて、第1の接続配線、第1のビア、および、第2のビアが、中間電極の第1の辺に隣接して設けられるとともに、中間電極の第1の辺と対向する第2の辺に隣接して設けられていることを特徴とする半導体装置が提供される。

20

**【0010】**

本発明によれば、第1の接続配線、第1のビア、および、第2のビアが、中間電極を取り囲むように設けられているので、MIM型容量素子への外部からのノイズの影響をより少なくすることができるとともに、シールド層として機能する下部電極および上部電極がMIM型容量素子の容量値に寄与するので、レイアウト効率を向上させることができる。

30

**【発明の効果】****【0011】**

本発明によれば、ノイズの影響を低減できるとともに、レイアウト効率のよいMIM型容量素子を提供することができる。

**【発明を実施するための最良の形態】****【0012】**

以下、本発明の実施の形態について図面を参照して説明する。

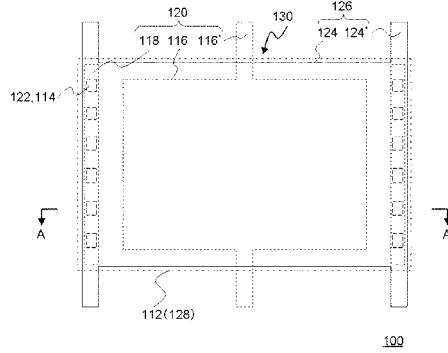

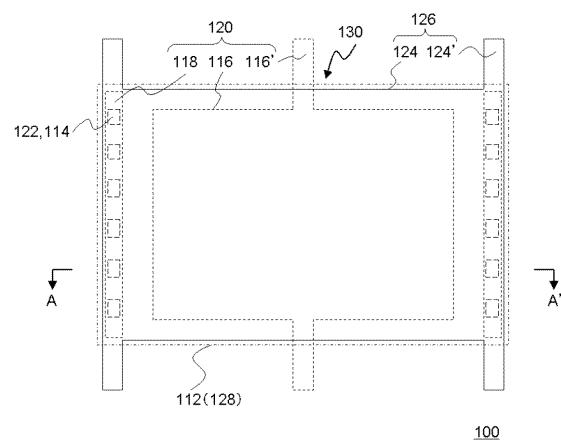

**【0013】****(第1の実施形態)**

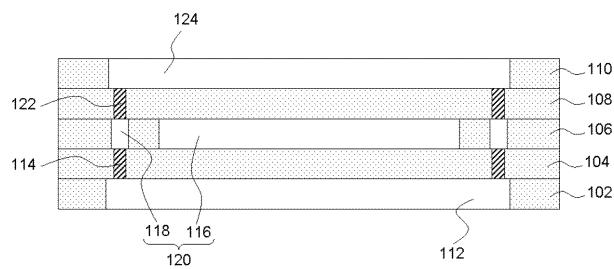

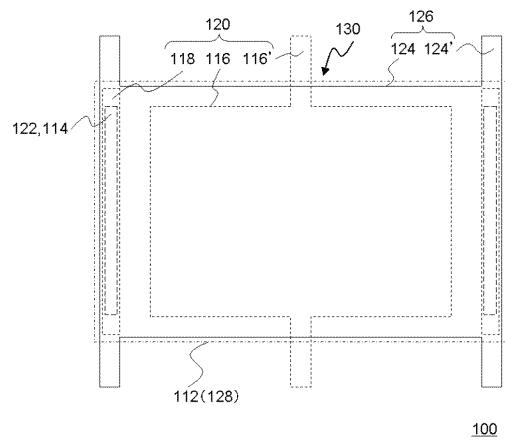

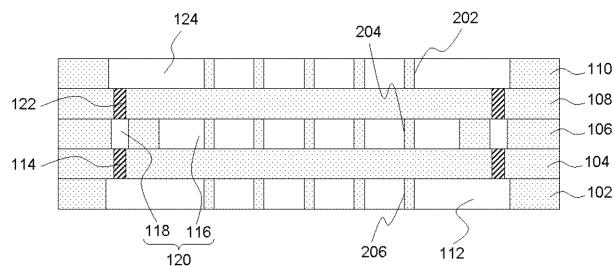

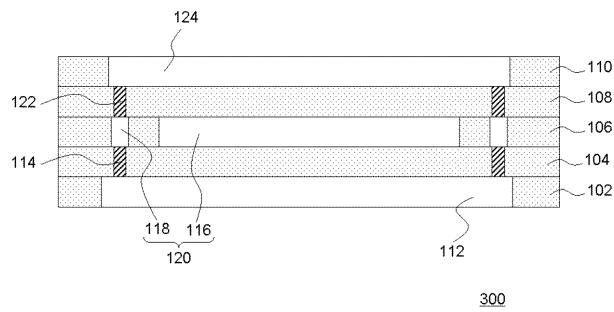

図1乃至図3は、本発明の第1の実施形態を示すための図である。図1は本発明の第1の実施形態によるMIM型容量素子130を有する半導体装置100の平面図であり、図2(a)乃至図2(c)は各配線層を表す平面図であり、図3は、図1のA-A'断面図である。

40

**【0014】**

図1および図3を参照すると、本発明の第1の実施形態による半導体装置100は、半導体基板(不図示)、例えばシリコン基板上に設けられた第1の層間絶縁膜102と、第1の層間絶縁膜102上に設けられた第2の層間絶縁膜104と、第2の層間絶縁膜104上に設けられた第3の層間絶縁膜106と、第3の層間絶縁膜106上に設けられた第4の層間絶縁膜108と、第4の層間絶縁膜108上に設けられた第5の層間絶縁膜111

50

0と有している。

【0015】

第1の層間絶縁膜102には、下部電極112を含む第1の配線層128が埋め込まれている。下部電極112は、例えば、銅または銅を主成分とする合金からなる。第1の層間絶縁膜102は、例えば、シリコン酸化膜またはLow-k膜からなる。第3の層間絶縁膜106には、中間電極116、中間電極引き出し配線116'、および、第1の接続配線118を含む第2の配線層120が埋め込まれている。中間電極116、中間電極引き出し配線116'、および、第1の接続配線118は、例えば、銅または銅を主成分とする合金からなる。第3の層間絶縁膜106は、例えば、シリコン酸化膜またはLow-k膜からなる。第5の層間絶縁膜110には、上部電極124および上部電極引き出し配線124'を含む第3の配線層126が埋め込まれている。上部電極124および上部電極引き出し配線124'は、例えば、銅または銅を主成分とする合金からなる。第5の層間絶縁膜110は、例えば、シリコン酸化膜またはLow-k膜からなる。中間電極116および中間電極引き出し配線116'は電気的に接続されていて、上部電極124および上部電極引き出し配線124'は電気的に接続されている。第1の接続配線118と中間電極116とは、第3の層間絶縁膜106によって、電気的に絶縁されている。第1の接続配線118は、中間電極116の両側に中間電極引き出し配線116'と平行な方向に延在するように設けられている。

10

【0016】

第2の層間絶縁膜104には、下部電極112と第1の接続配線118とを電気的に接続する第1のビア114が埋め込まれている。第1のビア114は、例えば、銅または銅を主成分とする合金からなる。第2の層間絶縁膜104は、例えば、シリコン酸化膜またはLow-k膜からなる。第4の層間絶縁膜108には、上部電極124と第1の接続配線118とを電気的に接続する第2のビア122が埋め込まれている。第2のビア122は、例えば、銅または銅を主成分とする合金からなる。第4の層間絶縁膜108は、例えば、シリコン酸化膜またはLow-k膜からなる。

20

【0017】

下部電極112と、第2の層間絶縁膜104と、中間電極116と、第4の層間絶縁膜108と、上部電極124は、MIM型容量素子130を構成していて、第1のビア114、第1の接続配線118、および、第2のビア122を介して互いに電気的に接続されている下部電極112および上部電極はMIM型容量素子130の一方の電極として機能し、中間電極116はMIM型容量素子の他方の電極として機能し、第2の層間絶縁膜104および第4の層間絶縁膜108は、容量絶縁膜として機能する。

30

【0018】

また、上部電極124に電気的に接続された上部電極引き出し配線124'は、MIM型容量素子130の一方の電極からの引き出し配線として機能し、中間電極116に電気的に接続された中間電極引き出し配線116'は、MIM型容量素子130の他方の電極からの引き出し配線として機能する。

【0019】

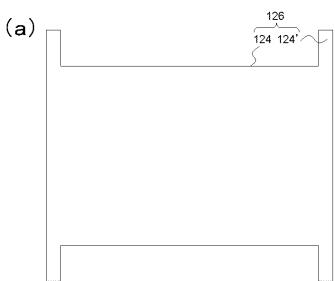

図2は、図1の各配線層を示す図であり、図2(a)は第3の配線層126を示しており、図2(b)は第2の配線層120を示しており、図2(c)は第1の配線層128を示している。図2(a)の第3の配線層126は、上部電極124と上部電極引き出し配線124'を含んでおり、図2(b)の第2の配線層120は、中間電極116と中間電極引き出し配線116'と第1の接続配線118を含んでおり、図2(c)の第1の配線層128の上層に設けられている。

40

図2(c)の第1の配線層120は、下部電極112を含んでおり、図2(b)の第2の配線層120の下層に設けられている。

【0020】

図1および図3に示される半導体装置100は、既知のデュアルダマシンプロセスまた

50

はシングルダマシンプロセスを用いて形成することができる。また、第1配線層128は、MIM型容量素子形成領域以外の回路領域の配線を含んでいてもよいし、第2配線層120は、MIM形成領域以外の回路領域の配線を含んでいてもよいし、第3配線層126は、MIM型容量素子形成領域以外の回路領域の配線を含んでいてもよい。

【0021】

本実施形態では、電気的に接続された第1のビア114、第1のビア122、下部電極112、上部電極124、第1の接続電極118が、中間電極116を3次元的に包囲する構成になっているので、MIM型容量への外部のノイズからの影響をより少なくことができるとともに、シールド層として機能する上部電極124および下部電極112がMIM型容量素子の容量値に寄与することができるので、レイアウトの効率化を図ることが可能になる。

10

【0022】

なお、本実施形態においては、ビア114、122を複数の矩形のビアによって形成しているけれども、図4に示すように、ビア114、122をスリット状のビアによって形成することもできる。ビア114、122をスリット状のビアにすることにより、MIM型容量素子への外部のノイズからの影響をより一層少なくことができる。

【0023】

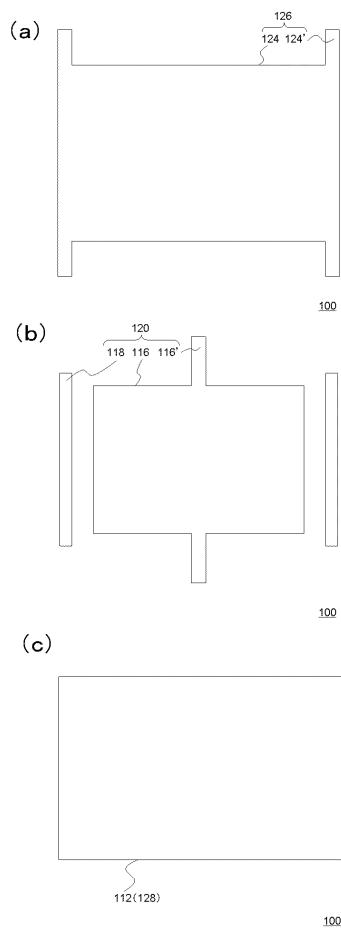

(第2の実施形態)

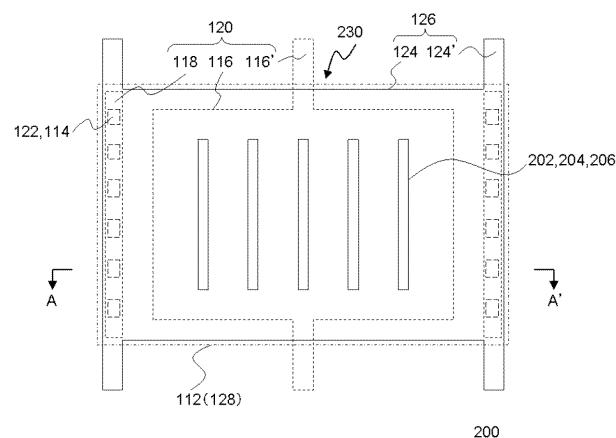

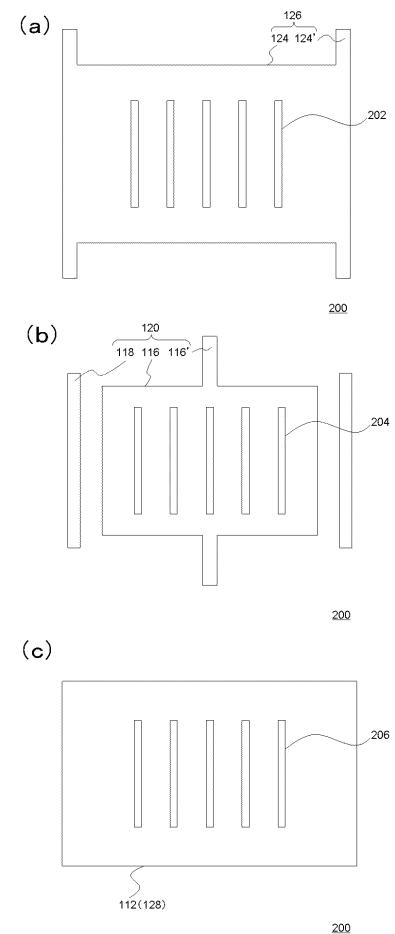

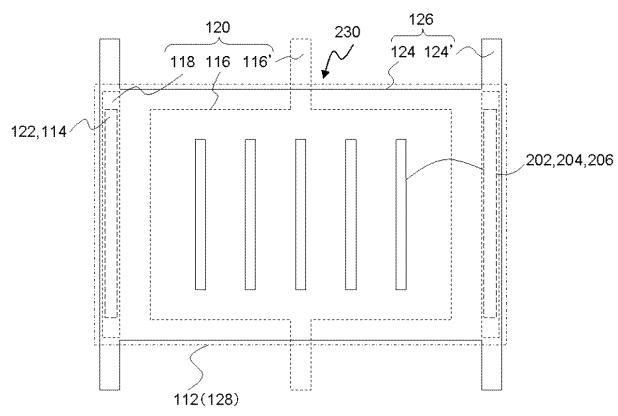

図5乃至図7は、本発明の第2の実施形態を示すための図である。図5は本発明の第2の実施形態によるMIM型容量素子230を有する半導体装置200の平面図であり、図6(a)乃至図6(c)は各配線層を表す平面図であり、図7は、図5のA-A'断面図である。

20

【0024】

第2の実施形態が第1の実施形態と異なる点は、MIM型容量素子230を構成する上部電極124、中間電極116、下部電極112がそれぞれスリット状の溝202、204、206を有していることである。第1の実施形態と異ならない点については、説明を省略する。

【0025】

図5および図6(a)に示されているように、第3の配線層126に含まれる上部電極124は、スリット状の溝202を有しており、図7に示されるように、スリット状の溝202は、第5の層間絶縁膜110から構成されている。

30

【0026】

図5および図6(b)に示されているように、第2の配線層120に含まれる中間電極124は、スリット状の溝204を有しており、図7に示されるように、スリット状の溝204の箇所は、第3の層間絶縁膜106から構成されている。

【0027】

図5および図6(c)に示されているように、第1の配線層128に含まれる下部電極112は、スリット状の溝206を有しており、図7に示されるように、スリット状の溝206の箇所は、第1の層間絶縁膜102から構成されている。

40

【0028】

第1の実施形態と同様に本実施形態の半導体装置200は、既知のデュアルダマシンプロセスまたはシングルダマシンプロセスを用いて形成することができる。ダマシンプロセルにおいては、配線形成工程において、CMP (Chemical Mechanical Polishing) による平坦化を使う。CMP (Chemical Mechanical Polishing) による平坦化を行うプロセスを用いる場合には、大面積を有する配線パターン中にスリット状の溝を設けることにより、配線の上表面の平坦度が改善される。したがって、MIM型容量素子を構成する各電極にスリット状の溝を設けることによって、各電極の上表面の平坦度が改善され、MIM型容量素子の容量値の精度を向上させることができる。

【0029】

なお、本実施形態においても、ビア114、122を複数の矩形のビアによって形成し

50

ているけれども、図8に示すように、ビア114, 122をスリット状のビアによって形成することもできる。ビア114, 122をスリット状のビアにすることにより、MIM型容量素子への外部のノイズからの影響をより一層少なくことができる。

【0030】

(第3の実施形態)

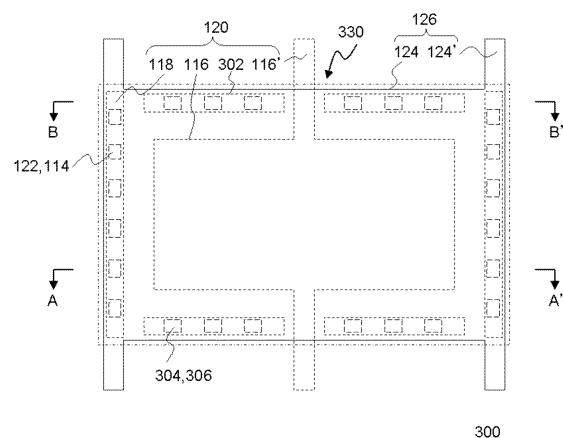

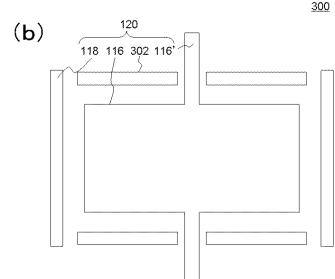

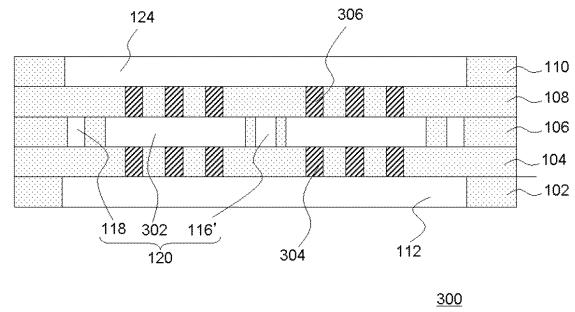

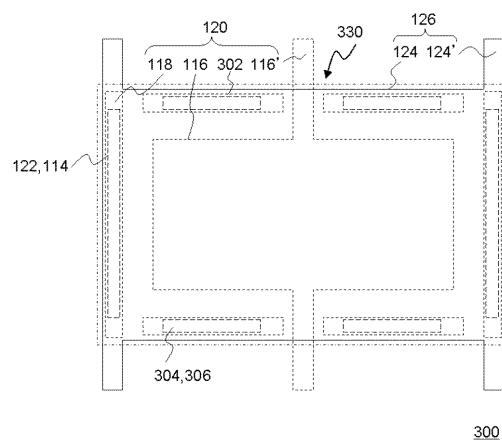

図9乃至図12は、本発明の第3の実施形態を示すための図である。図9は本発明の第3の実施形態によるMIM型容量素子330を有する半導体装置300の平面図であり、図10(a)乃至図10(c)は各配線層を表す平面図であり、図11は、図9のA-A'断面図であり、図12は、図9のB-B'断面図である。

【0031】

第3の実施形態が第1の実施形態と異なる点は、MIM型容量素子330を構成する上部電極124と下部電極112がさらに、第3のビア304と第2の接続配線302と第4のビア306によって電気的に接続されていることである。第1の実施形態と異なる点については、説明を省略する。

【0032】

図9乃至図12に示されているように、半導体装置第300はさらに、第2の配線層120に含まれる第2の接続配線302と、第2層間絶縁膜104内に埋め込まれ、下部電極112と第2の接続配線302とを電気的に接続する第3のビア304と、第4層間絶縁膜108内に埋め込まれ、第2の接続配線302と上部電極124とを電気的に接続する第4のビア306とを有している。第2の接続配線302は、例えば、銅または銅を主成分とする合金からなる。第3のビア304は、例えば、銅または銅を主成分とする合金からなる。第4のビア306は、例えば、銅または銅を主成分とする合金からなる。第2の接続配線302は、中間電極116の両側に第1の接続配線118と直交する方向に延在するように設けられている。すなわち、上部電極124は、第1のビア114、第1の接続配線118、および、第2のビア122を介して、下部電極112に電気的に接続されるとともに、第3のビア304、第2の接続配線302、および、第4のビアを介して、下部電極112に電気的に接続されている。

【0033】

本実施形態においては、第1の実施形態の構成に加えて、上部電極124が、第3のビア304、第2の接続配線302、および、第4のビアを介して、下部電極112に電気的に接続されているので、中間電極116の四方をビアで囲むことが可能となり、MIM型容量素子への外部のノイズからの影響をより一層少なくことができる。

【0034】

なお、本実施形態においても、ビア114, 122, 304, 306を複数の矩形のビアによって形成しているけれども、図13に示すように、ビア114, 122, 304, 306をスリット状のビアによって形成することもできる。ビア114, 122, 304, 306をスリット状のビアにすることにより、MIM型容量素子への外部のノイズからの影響をより一層少なくことができる。

【0035】

(第4の実施形態)

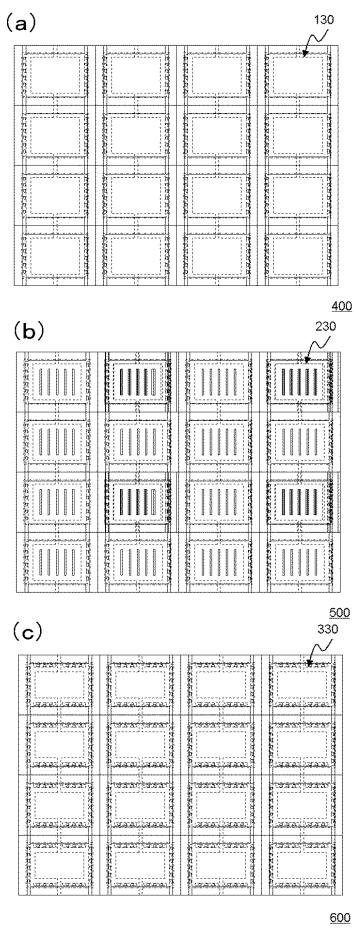

図14は、本発明の第4の実施形態を示すための図である。本実施形態は、第1実施形態乃至第3の実施形態のいずれかのMIM型容量素子を単位容量として用い、上記の単位容量をマトリックス状に配置したものである。

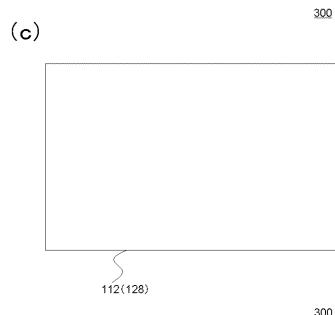

【0036】

図14(a)は本発明の第1の実施形態によるMIM型容量素子130(図1を参照)を単位容量としてマトリックス状に配置した半導体装置400であり、図14(b)は本発明の第2の実施形態によるMIM型容量素子230(図5を参照)を単位容量としてマトリックス状に配置した半導体装置500であり、図14(c)は本発明の第3の実施形態によるMIM型容量素子330(図9を参照)を単位容量としてマトリックス状に配置した半導体装置600である。

## 【0037】

図14(a)において、単位容量であるMIM型容量素子130は、上部電極引き出し配線124'および中間電極引き出し配線116'(図1を参照)を介して、相互に接続されている。また、図14(b)において、単位容量であるMIM型容量素子230は、上部電極引き出し配線124'および中間電極引き出し配線116'(図5を参照)を介して、相互に接続されている。さらに、図14(c)において、単位容量であるMIM型容量素子330は、上部電極引き出し配線124'および中間電極引き出し配線116'(図9を参照)を介して、相互に接続されている。

## 【0038】

本実施形態においては、外部のノイズからの影響をより少なくした第1実施形態乃至第3の実施形態のいずれかのMIM型容量素子を単位容量として、マトリックス状に配置することにより、ノイズレベルが場所によって異なるような場合においても、ノイズに起因する単位容量の容量値のバラつきを小さくできるので、より高精度な容量素子を得ることができる。

10

## 【図面の簡単な説明】

## 【0039】

【図1】本発明の第1の実施形態の半導体装置の平面図を示す図である。

20

【図2】本発明の第1の実施形態の半導体装置の各配線層の平面図を示す図である。

【図3】本発明の第1の実施形態の半導体装置の断面図を示す図である。

【図4】本発明の第1の実施形態の半導体装置の変形例を示す平面図である。

20

【図5】本発明の第2の実施形態の半導体装置の平面図を示す図である。

【図6】本発明の第2の実施形態の半導体装置の各配線層の平面図を示す図である。

【図7】本発明の第2の実施形態の半導体装置の断面図を示す図である。

【図8】本発明の第2の実施形態の半導体装置の変形例を示す平面図である。

【図9】本発明の第3の実施形態の半導体装置の平面図を示す図である。

【図10】本発明の第3の実施形態の半導体装置の各配線層の平面図を示す図である。

【図11】本発明の第3の実施形態の半導体装置の断面図を示す図である。

30

【図12】本発明の第3の実施形態の半導体装置の断面図を示す図である。

【図13】本発明の第3の実施形態の半導体装置の変形例を示す平面図である。

【図14】本発明の第4の実施形態の半導体装置の平面図を示す図である。

## 【符号の説明】

## 【0040】

100 半導体装置

40

102 第1の層間絶縁膜

104 第2の層間絶縁膜

106 第3の層間絶縁膜

108 第4の層間絶縁膜

110 第5の層間絶縁膜

112 下部電極

114 第1のピア

116 中間電極

116' 中間電極引き出し配線

118 第1の接続配線

120 第2の配線層

122 第2のピア

124 上部電極

124' 上部電極引き出し配線

126 第3の配線層

128 第1の配線層

130 MIM型容量素子

50

2 0 0 半導体装置

2 0 2 スリット状の溝

2 0 4 スリット状の溝

2 0 6 スリット状の溝

2 3 0 M I M 型容量素子

3 0 0 半導体装置

3 0 2 第2の接続配線

3 0 4 第3のビア

3 0 6 第4のビア

3 3 0 M I M 型容量素子

4 0 0 半導体装置

5 0 0 半導体装置

6 0 0 半導体装置

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

200

【図8】

200

【図9】

300

【図10】

300

300

【図11】

【図12】

【図13】

【図14】