(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-25110

(P2016-25110A)

(43) 公開日 平成28年2月8日(2016.2.8)

| (51) Int.Cl.            | F 1 | HO 1 L 33/48 (2010.01) | HO 1 L 33/00 | 4 O O | テーマコード (参考)<br>2 C 1 6 2 |

|-------------------------|-----|------------------------|--------------|-------|--------------------------|

| B 4 1 J 2/447 (2006.01) |     | B 4 1 J 2/447          | 1 O 1 A      |       | 2 H O 7 6                |

| B 4 1 J 2/45 (2006.01)  |     | B 4 1 J 2/45           |              |       | 5 C O 5 1                |

| G 0 3 G 15/04 (2006.01) |     | G 0 3 G 15/04          | 1 1 1        |       | 5 F 1 4 2                |

| H 0 4 N 1/036 (2006.01) |     | H 0 4 N 1/036          | A            |       |                          |

審査請求 未請求 請求項の数 8 O L (全 14 頁)

|           |                              |          |                                          |

|-----------|------------------------------|----------|------------------------------------------|

| (21) 出願番号 | 特願2014-146020 (P2014-146020) | (71) 出願人 | 000006747<br>株式会社リコー<br>東京都大田区中馬込1丁目3番6号 |

| (22) 出願日  | 平成26年7月16日 (2014.7.16)       | (74) 代理人 | 100081422<br>弁理士 田中 光雄                   |

|           |                              | (74) 代理人 | 100100158<br>弁理士 鮫島 瞳                    |

|           |                              | (72) 発明者 | 道吉 啓<br>東京都大田区中馬込1丁目3番6号 株式会社リコー内        |

|           |                              | (72) 発明者 | 建部 哲郎<br>東京都大田区中馬込1丁目3番6号 株式会社リコー内       |

最終頁に続く

(54) 【発明の名称】発光素子アレイチップ、チップ実装基板、及び画像形成装置

## (57) 【要約】

【課題】発光素子アレイチップの基板上への実装における配置マージンを大きくさせることができる発光素子アレイチップを提供する。

【解決手段】副走査方向に配置される自然数N個の発光素子を有する複数の発光素子群が配置される発光素子アレイチップであって、複数の発光素子群が主走査方向に互いに所定の第1の間隔で配置された第1の発光素子群プロックと、発光素子アレイチップのいずれか一方の端部側の1つ以上の発光素子群が、第1の発光素子群プロックの各発光素子群の位置を基準位置として、当該基準位置から所定の第2の間隔だけ副走査方向にずらして配置された第2の発光素子群プロックとを備えた。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

副走査方向に配置される自然数N個の発光素子を有する複数の発光素子群が配置される発光素子アレイチップであって、

上記複数の発光素子群が主走査方向に互いに所定の第1の間隔で配置された第1の発光素子群ブロックと、

上記発光素子アレイチップのいずれか一方の端部側の1つ以上の発光素子群が、上記第1の発光素子群ブロックの各発光素子群の位置を基準位置として、当該基準位置から所定の第2の間隔だけ副走査方向にずらして配置された第2の発光素子群ブロックとを備えたことを特徴とする発光素子アレイチップ。

10

**【請求項 2】**

上記第2の間隔は、上記各発光素子群の副走査方向の幅以上に設定されることを特徴とする請求項1記載の発光素子アレイチップ。

**【請求項 3】**

上記第2の発光素子群ブロックの各発光素子群の発光素子の数はそれぞれ、(N+1)個以上であることを特徴とする請求項1または2記載の発光素子アレイチップ。

**【請求項 4】**

上記第2の発光素子群ブロックの各発光素子群の発光素子は、主走査方向に互いに等間隔だけずらして配置されることを特徴とする請求項3記載の発光素子アレイチップ。

20

**【請求項 5】**

請求項4記載の発光素子アレイチップが主走査方向に互いに隣接して配置されるチップ実装基板であって、

上記第2の発光素子群ブロックの各発光素子群の発光素子から、動作させるN個の発光素子を選択するデータを格納する記憶手段を備えたことを特徴とするチップ実装基板。

**【請求項 6】**

請求項1から4のうちのいずれか1つに記載の発光素子アレイチップが主走査方向に互いに隣接して配置されるチップ実装基板であって、

上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿ってダイシングされることを特徴とするチップ実装基板。

**【請求項 7】**

上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿って矩形状でもしくは所定の角度で屈曲してダイシングされることを特徴とする請求項6記載のチップ実装基板。

30

**【請求項 8】**

請求項5から7のうちのいずれか1つに記載のチップ実装基板を備えたことを特徴とする画像形成装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、例えば複写機、プリンタ、ファクシミリなどの画像形成装置のための発光素子アレイチップ、チップ実装基板、及び画像形成装置に関する。

40

**【背景技術】****【0002】**

例えば複写機、プリンタ、ファクシミリなどの画像形成装置における画像書き込み装置または露光装置として、LED(発光ダイオード)、OLED(有機エレクトロルミネッセンス)素子などの発光素子を、複数ライン状に配列してなる発光素子アレイチップ、もしくは例えば発光アレイヘッドなどの固体走査型ラインヘッド(以下、ラインヘッドという。)を用いたものがある。ラインヘッドを用いたプリンタでは、帯電させられた感光体ドラムの表面をラインヘッドによって照射して静電潜像を形成し、この静電潜像にトナーを付着させてトナー像を形成することにより現像を行い、このトナー像を用紙に転写し定

50

着させる。

#### 【0003】

近年、複写機やプリンタにおいては、印字品質の向上に向けて更なる高密度印字が行なわれつつある。従って、従来の 600 dpi 程度の印字密度から 1200 dpi 以上の印字密度が要求されている。

#### 【0004】

ここで、1200 dpi 間隔の場合には、発光素子間距離は約 21 μm 間隔となる。発光素子アレイチップを隣り合わせて 1 列に基板上に実装するうえでは、チップの実装誤差及び発光素子とチップ端との距離を考慮する必要がある。近年の製造技術では、チップの実装誤差は ± 6 μm 程度、発光素子とチップ端との距離は 3 μm 程度が可能である。従って、発光素子のサイズは、一辺 3 μm とする必要がある（実際には、さらにチップのダイシング誤差も重畠されるため、さらに発光素子サイズを小さくする必要がある。）。感光体への露光エネルギーは発光素子サイズに比例する。発光素子サイズが小さい場合には、エネルギーの不足分は発光素子を駆動する電流量を増やすことで補うことが可能ではあるが、その場合には、発光素子の寿命劣化が進んでしまい、機器寿命は十分に満足することができないという問題が生じる。これに対して、駆動電流量を減らすために発光素子サイズは極力大きくすることで対応していた。

#### 【0005】

このような問題を解決するために、特許文献 1 には、隣接する LED チップを発光部の配列方向に一部重ねて配列する方法が開示されている。また、特許文献 2 には、各発光素子アレイチップの両端の発光部の幅を他の発光部の幅より狭くする方法が開示されている。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、特許文献 1 では、発光素子アレイチップを副走査方向に複数列並べるのヘッド幅が広くなりヘッドが大型化することによりコストアップとなるという問題があった。また、副走査方向にずれた発光点で印字するために複雑な発光部制御を行わなくてはならないため、制御にかかるコストがアップするという問題があった。また、特許文献 2 では、発光素子アレイチップの両端部の発光素子が他の発光素子より小さいため、両端部の発光素子に印加する電流値を高くして、他の発光素子と同じ明るさとするように発光させることが必要になるが、この両端の発光素子の電流密度は高くなるため、他の発光素子に比べ両端の素子の劣化が加速されるという問題があった。

#### 【0007】

本発明の目的は上記の問題点を解決し、発光素子アレイチップの端部の発光素子を小さくすることなしに、発光素子アレイチップの基板上への実装における配置マージンを大きくさせることができる発光素子アレイチップを提供することにある。

#### 【課題を解決するための手段】

#### 【0008】

本発明の一態様に係る発光素子アレイチップは、

副走査方向に配置される自然数 N 個の発光素子を有する複数の発光素子群が配置される発光素子アレイチップであって、

上記複数の発光素子群が主走査方向に互いに所定の第 1 の間隔で配置された第 1 の発光素子群ブロックと、

上記発光素子アレイチップのいずれか一方の端部側の 1 つ以上の発光素子群が、上記第 1 の発光素子群ブロックの各発光素子群の位置を基準位置として、当該基準位置から所定の第 2 の間隔だけ副走査方向にずらして配置された第 2 の発光素子群ブロックとを備えたことを特徴とする。

#### 【発明の効果】

#### 【0009】

10

20

30

40

50

本発明によれば、発光素子アレイチップの基板上への実装において、従来の方法に比べ、発光素子アレイチップの端部の発光素子を小さくすることなしに、発光素子アレイチップの基板上への実装における配置マージンを大きくさせることが可能となる。

**【図面の簡単な説明】**

**【0 0 1 0】**

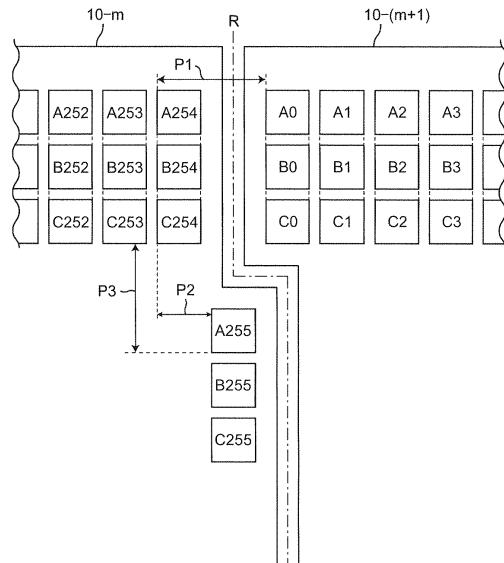

【図1】本発明の実施形態1に係る画像形成装置100の構成を示す概略側面図である。

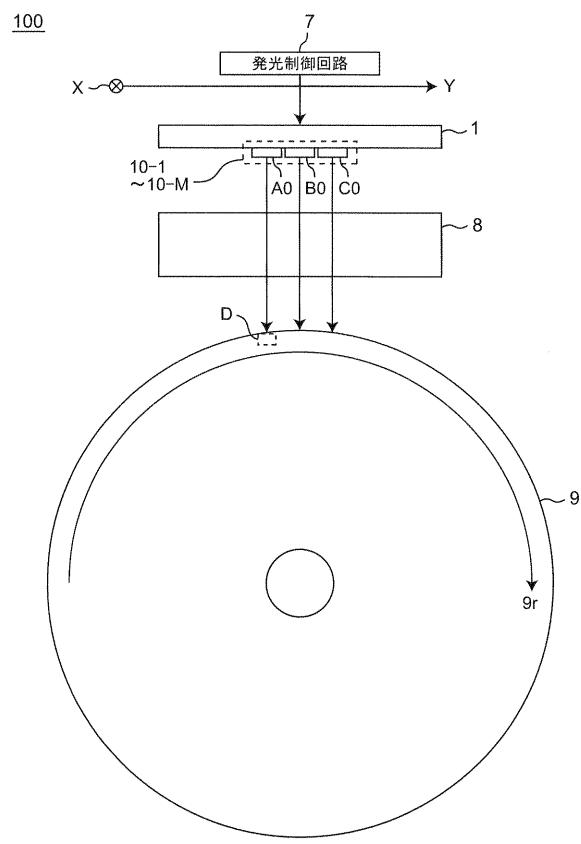

【図2】図1のチップ実装基板1の平面図である。

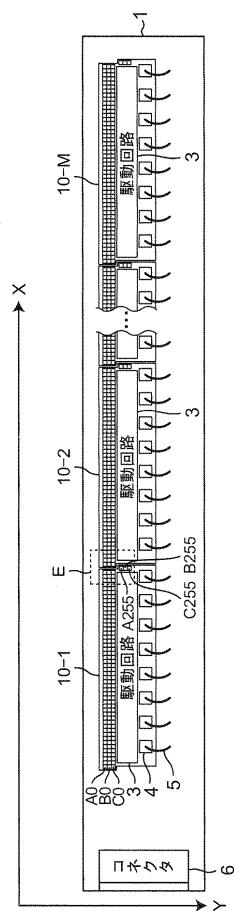

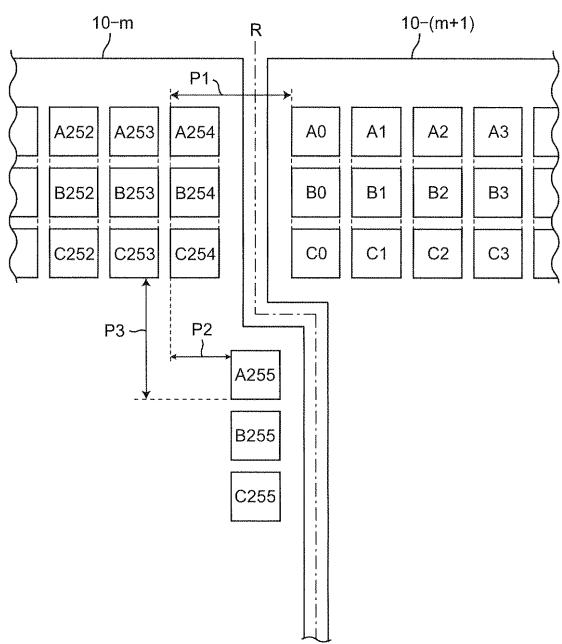

【図3】図2の領域Eの拡大図である。

【図4】本発明の実施形態2に係る画像形成装置100Aの構成を示す概略側面図である。

10

【図5】図4の発光素子アレイチップ10A-mの端部の要部拡大図である。

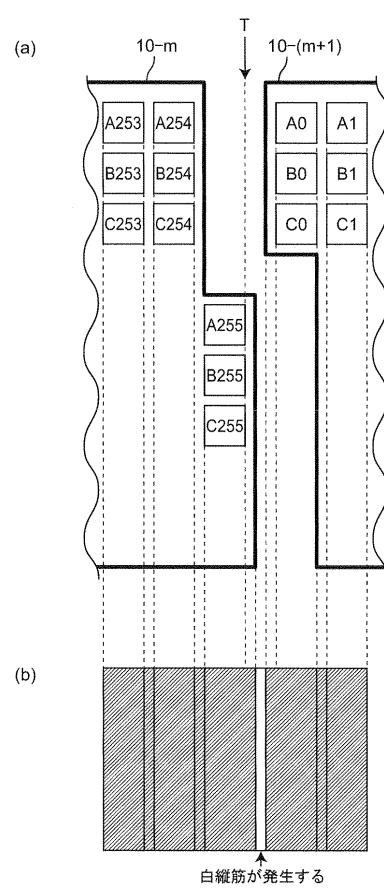

【図6】(a)は、図2の発光素子アレイチップ10-mと発光素子アレイチップ10-(m+1)とを隣接して配置された第1の状態を示す発光素子10-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

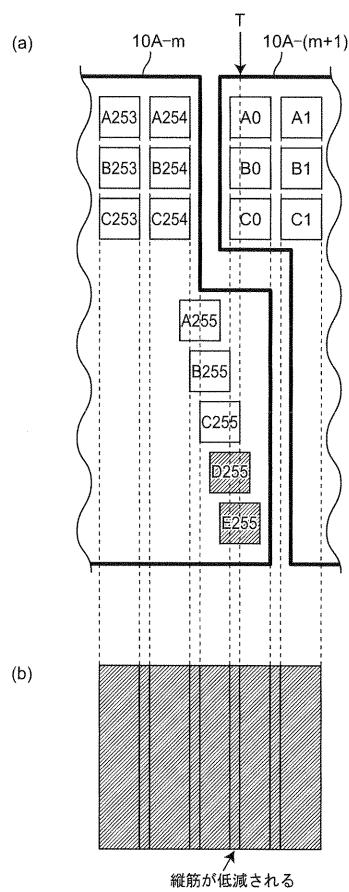

【図7】(a)は、図5の発光素子アレイ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第1の状態を示す発光素子10A-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

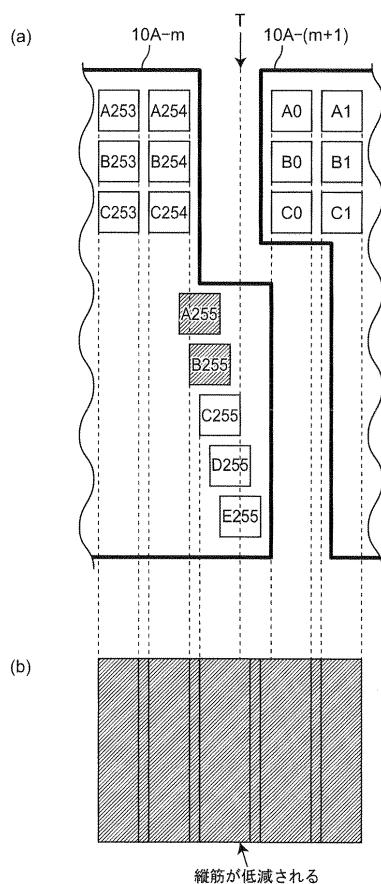

【図8】(a)は、図2の発光素子アレイチップ10-mと発光素子アレイチップ10-(m+1)とを隣接して配置された第2の状態を示す発光素子10A-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

20

【図9】(a)は、図5の発光素子アレイ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第2の状態を示す発光素子10A-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

【図10】(a)は、図2の発光素子アレイチップ10-mと発光素子アレイチップ10-(m+1)とを隣接して配置された第3の状態を示す発光素子10-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

【図11】(a)は、図5の発光素子アレイ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第3の状態を示す発光素子10A-mの端部の拡大図であり、(b)は、(a)の印字結果を示す概略図である。

30

**【発明を実施するための形態】**

**【0 0 1 1】**

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

**【0 0 1 2】**

**実施形態1.**

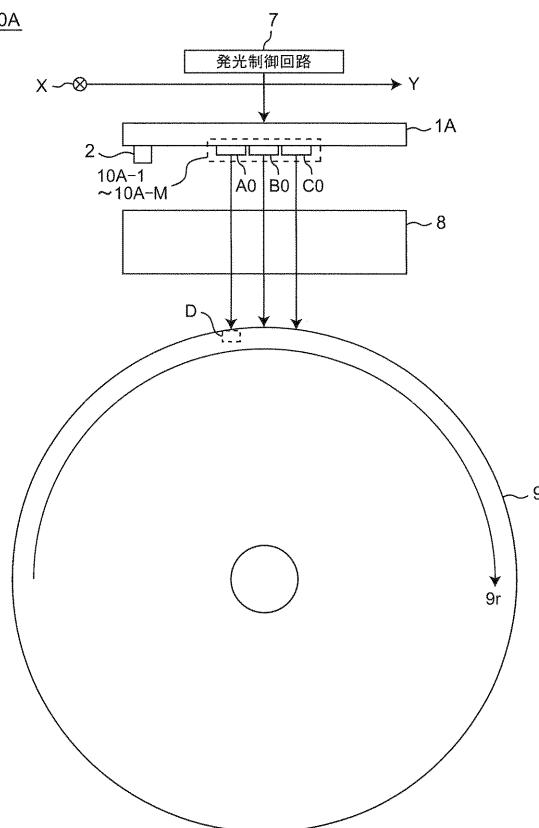

図1は、本発明の実施形態1に係る画像形成装置100の構成を示す概略側面図である。また、図2は、図1のチップ実装基板1の平面図である。図1の画像形成装置100は、発光制御回路7と、複数M個の発光素子アレイチップ(以下、チップという。)10-1, ..., 10-Mが主走査方向Xで互いに隣接して形成されるチップ実装基板1と、光を集光する結像素子からなる光書き込みユニット8と、当該光書き込みユニット8を介して光を照射して画像(静電潜像)を形成する感光体ドラム9とを備えて構成される。また、図2に示すように、発光素子アレイチップ10-m(m=1, 2, ..., M)は、複数の発光素子A0~C0, ..., A255~C255が1列に主走査方向Xで整列配置される。すなわち、発光素子アレイチップ10-mは、3個の発光素子An~Cn(n=0, 1, ..., 255)が副走査方向Yに等間隔で配置されて形成される発光素子群を主走査方向Xに等間隔で256列配置して形成される。なお、本実施形態では、発光素子A0~C0, ..., A255~C255は、例えば無機LED、有機LED、有機エレクトロルミネッセンス素子などを用いて構成される。

40

**【0 0 1 3】**

図2のチップ実装基板1は、主走査方向Xにワイヤーボンディングパッド4を有する発

50

光素子アレイチップ 10 - 1 ~ 10 - M が互いに隣接して配置される。各発光素子アレイチップ 10 - m は、発光素子 A0 ~ C0, …, A255 ~ C255 と、当該各発光素子 A0 ~ C0, …, A255 ~ C255 を選択的に点灯もしくは非点灯させるように制御する駆動回路 3 とをそれぞれ備える。

#### 【0014】

図 2において、各発光素子アレイチップ 10 - 1, …, 10 - M は、ボンディングワイヤ 5 を介してチップ実装基板 1 と電気的に接続される。次に、各発光素子アレイチップ 10 - 1, …, 10 - M は、当該チップ実装基板 1 のコネクタ 6 を介して発光制御回路 7 から発光制御信号を受信する。次に、各発光素子アレイチップ 10 - 1, …, 10 - M は、当該発光制御信号に基づいて、各発光素子 A0 ~ C0, …, A255 ~ C255 を選択的に点灯もしくは非点灯して感光体ドラム 9 を多重露光することにより各画素を階調表現する。図 2において、各発光素子アレイチップ 10 - 1 ~ 10 - M の端部の一端の発光素子 A255 ~ C255 を副走査方向 Y にずらして配置する。次に、このずらした発光素子 A255 ~ C255 の配置に沿って各発光素子アレイチップ 10 - 1 ~ 10 - M の端部を矩形状でもしくは所定の角度で屈曲してダイシングする。次に、ダイシングされた各発光素子アレイチップ 10 - 1 ~ 10 - M は、チップ実装基板 1 上に 1 列に主走査方向 X で配置して実装される。

10

#### 【0015】

図 3 は、図 2 の領域 E の拡大図である。すなわち、図 3 は、発光素子アレイチップ 10 - m と発光素子アレイチップ 10 - (m + 1) とを隣接して配置する場合の発光素子 10 - m の端部の拡大図を図示する。図 3において、各発光素子 An ~ Cn (n = 0 ~ 255) の発光素子サイズは  $18 \mu\text{m} \times 18 \mu\text{m}$  の正方形である。また、各発光素子 An ~ Cn (n = 0, 1, …, 255) は、ピッチ P2 (P2 =  $21 \mu\text{m}$ ) の間隔 (1200 dpi) で、主走査方向 X に 256 個、副走査方向 Y に 3 個の発光素子が整列配置される。本実施形態では、発光素子アレイチップ 10 - m の右端の発光素子 A255 ~ C255 が副走査方向 Y に (発光素子ピッチ P2 × (副走査方向に整列配置される発光素子の数 + 1)) の距離だけ移動して配置する。すなわち、発光素子アレイチップ 10 - m は、各発光素子 A0 ~ C0, …, A254 ~ C254 からなる各発光素子群が主走査方向 X に互いに所定の第 1 の間隔で複数列配置された第 1 の発光素子群ブロックを備える。また、発光素子アレイチップ 10 - m は、発光素子アレイチップ 10 - m のいずれか一方の端部側の発光素子 A255 ~ C255 からなる発光素子群が、基準位置から所定の間隔だけ副走査方向 Y にずらして配置された第 2 の発光素子群ブロックを備える。ここで、第 1 の発光素子群ブロックの各発光素子群の位置を基準位置とし、第 2 の間隔は、各発光素子群の副走査方向 Y の幅以上に設定される。

20

30

#### 【0016】

図 3において、発光素子アレイチップ 10 - m の発光素子 A254 ~ C254 からなる発光素子群の左端から発光素子アレイチップ 10 - (m + 1) の発光素子 A0 ~ C0 からなる発光素子群の左端までの距離 P1 は  $42 \mu\text{m}$  である。また、第 1 の発光素子群ブロックの下端から第 2 の発光素子群ブロックの発光素子 A255 の下端までの距離 P3 は  $42 \mu\text{m}$  である。この移動により、発光素子アレイチップ 10 - m のダイシング領域に配置マージンを従来例に比較してより大きく持たせることが可能となる。同時に、隣接するチップ間での実装時のダイボンド基準位置 R に対する配置マージンを従来例に比較してより大きく持たせることが可能となる。

40

#### 【0017】

以上のように構成された実施形態 1 に係る画像形成装置 100 の動作について以下に説明する。

#### 【0018】

図 1 の発光制御回路 7 からの発光制御信号に基づいて 3 つの発光素子 An ~ Cn (n = 0, 1, …, 255) を選択的に点灯もしくは非点灯して感光体ドラム 9 を多重露光することにより各画素を 3 階調表現する。すなわち、3 つの発光素子 An ~ Cn (n = 0, 1

50

、 …、 2 5 5 ) は主走査方向 X の同一位置を多重露光して 1 画素を形成する。

#### 【 0 0 1 9 】

図 1において、発光素子 A n より描画領域 D に対して露光を行い、感光体ドラム 9 を時計方向 9 r に回転させることで、発光素子アレイチップ 1 0 - m に対して描画領域 D を相対的に副走査方向 Y に移動させる。次に、発光素子 B n より描画領域 D に対して露光を行い、感光体ドラム 9 を時計方向 9 r に回転させることで発光素子アレイチップ 1 0 - m に対して描画領域 D を相対的に副走査方向 Y に移動させる。同様に、発光素子 C n より描画領域 D に対して露光を行うことができる。

#### 【 0 0 2 0 】

以上の実施形態に係る画像形成装置 1 0 0 によれば、発光素子アレイチップ 1 0 - m のチップ実装基板 1 上への実装において、発光素子アレイチップ 1 0 - m の両端部のいずれか一端の発光素子群を副走査方向 Y にずらして配置する。さらに、このずらした発光素子群の各発光素子の配置に沿って発光素子アレイチップ 1 0 - m の端部を矩形状でダイシングした発光素子アレイチップ 1 0 - m を 1 列に主走査方向 X で配列する。従って、発光素子アレイチップ 1 0 - m のチップ実装基板 1 上への実装における配置マージンを従来例に比較してより大きくすることが可能となる。さらに、密度の高い印刷を行う場合でも画像品位を低下させることができない画像形成装置を提供することができる。

#### 【 0 0 2 1 】

なお、上述した実施形態では、発光素子アレイチップ 1 0 - m の右端の 1 列分の発光素子 A 2 5 5 ~ C 2 5 5 のみを副走査方向 Y に移動させたが、本発明はこれに限定されない。例えば、発光素子アレイチップ 1 0 - m の右端の 2 列の発光素子 A 2 5 4 ~ C 2 5 4 及び A 2 5 5 ~ C 2 5 5 を副走査方向 Y に移動させて配置してもよい。また、発光素子アレイチップ 1 0 - m の右端の 3 列以上の発光素子をそれぞれ副走査方向 Y に移動させてもよい。この場合には、本実施形態に比較すると、発光素子アレイチップ 1 0 - m のチップ実装基板 1 上への実装における配置マージンをさらに大きくすることが可能となる

#### 【 0 0 2 2 】

##### 実施形態 2 .

上述した実施形態 1 に係る画像形成装置 1 0 0 においては、各発光素子アレイチップ 1 0 - m のチップ実装基板 1 上への実装時の誤差が発生する。従って、印字結果に縦方向の筋上の濃淡(縦筋)が発生する。これに対して、本実施形態では、当該実装時の誤差を低減させるための発光素子を追加させて印字結果に現れる縦筋を低減させることを特徴とする。

#### 【 0 0 2 3 】

図 4 は、本発明の実施形態 2 に係る画像形成装置 1 0 0 A の構成を示す概略側面図である。図 4 の画像形成装置 1 0 0 A は、図 1 の画像形成装置 1 0 0 に比較すると、チップ実装基板 1 の代わりにチップ実装基板 1 A を備えたことを特徴とする。チップ実装基板 1 A は、チップ実装基板 1 に比較すると、発光素子アレイチップ 1 0 - m ( m = 0, 1, …, M ) の代わりに発光素子アレイチップ 1 0 A - m ( m = 0, 1, …, M ) を備えたことを特徴とする。また、チップ実装基板 1 A は、実装時の発光素子の位置ばらつき(実装時の誤差)を補正するための素子選択のための補正用データを格納する記憶手段であるレジスタ 2 をさらに備えたことを特徴とする。すなわち、補正用データに基づいて、第 2 の発光素子群プロックの各発光素子群の発光素子から、動作させる 3 個の発光素子が選択される。ここで、レジスタ 2 は、例えばマスク ROM、F R A M (登録商標)、E P R O M、E E P R O M, F e R O M、及びフラッシュメモリなどの不揮発性メモリなどの記憶保持型メモリである。なお、補正用データは、出荷前に予め設定され、発光素子 A 0 ~ C 0 , …, A 2 5 5 ~ C 2 5 5 は、例えば無機 L E D、有機 L E D、もしくは有機エレクトロルミネッセンス素子などを用いて構成される。

#### 【 0 0 2 4 】

10

20

30

40

50

図5は、図4の発光素子アレイチップ10A-mの端部の要部拡大図である。すなわち、図5は、発光素子アレイチップ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置する場合の発光素子10A-mの端部の拡大図を図示する。図5の発光素子アレイチップ10A-mは、図3の発光素子アレイチップ10A-mに比較すると、発光素子A255~C255の代わりに発光素子A255~E255を備えたことを特徴とする。ここで、発光素子A255~E255は第2の発光素子群プロックを構成し、各発光素子A255~E255は主走査方向Xに互いに等間隔でずらして配置される。

#### 【0025】

以上のように構成された実施形態2に係る画像形成装置100Aの動作は、実施形態1に係る画像形成装置100の動作と同様である。以下に、実施形態1に係る画像形成装置100の動作との差異について説明する。

10

#### 【0026】

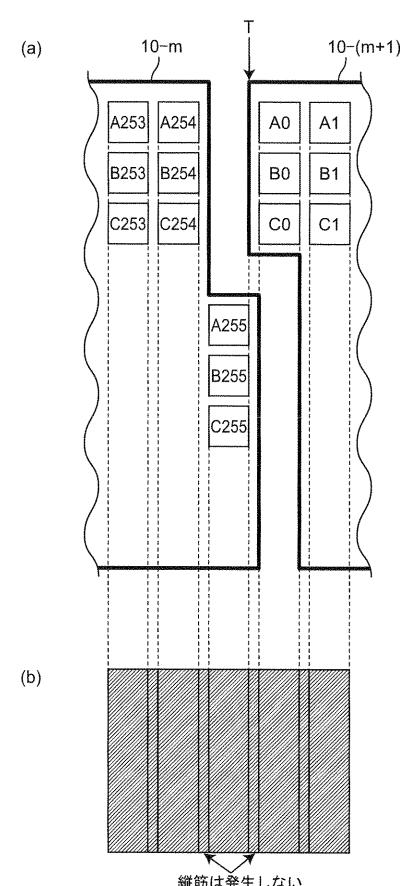

図6(a)は、図2の発光素子アレイチップ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第1の状態を示す発光素子10A-mの端部の拡大図であり、図6(b)は、図6(a)の印字結果を示す概略図である。図6(a)では、隣接チップ10A-(m+1)が目標位置T近辺、すなわち隣接チップ同士の間隔が、右端の発光素子を含めて、主走査方向Xに見た発光素子間隔がほぼピッチ通りとなるように実装された場合が図示される。この場合には、図6(b)に図示するように、主走査方向Xの発光素子ピッチは隣接チップ間ににおいてもほぼ等間隔となるので、印字結果に縦筋は発生しない。なお、発光素子は、当該発光素子自身のサイズよりも広がって発光するので、発光素子の外側にも印字されている。

20

#### 【0027】

図7(a)は、図5の発光素子アレイ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第1の状態を示す発光素子10A-mの端部の拡大図であり、図7(b)は、図7(a)の印字結果を示す概略図である。図7(a)では、隣接チップ10A-(m+1)が目標位置T近辺、すなわち隣接チップ同士の間隔が、右端の発光素子を含めて、主走査方向Xに見た発光素子間隔がほぼピッチ通りとなるように実装された場合が図示される。この場合には、補正用データに基づいて、発光素子B255、C255、D255が使用され、発光素子A255、E255が使用されないように設定される。この設定により、右端の発光素子と、その隣の列の発光素子との間での重なりは発生しないので、発光素子を少しずつ主走査方向Xにずらして配置した場合でも縦筋は発生することはない。

30

#### 【0028】

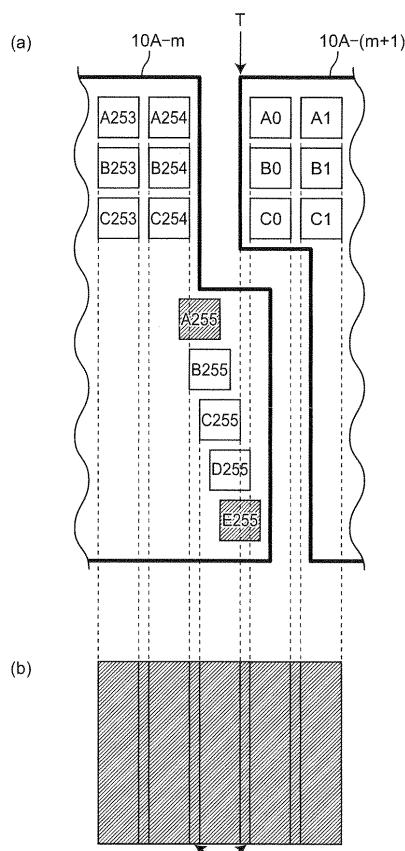

図8(a)は、図2の発光素子アレイチップ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第2の状態を示す発光素子10A-mの端部の拡大図であり、図8(b)は、図8(a)の印字結果を示す概略図である。図8(a)では、隣接チップ10A-(m+1)が目標位置Tより内側の場合、すなわち隣接チップ同士の間隔が狭く、主走査方向Xに見た発光素子間隔がピッチより狭くなっている場合が図示される。この場合には、主走査方向Xの発光素子ピッチが隣接チップ間で重なりを持つ。すなわち、発光素子A255~C255の右端と発光素子A0~C0の左端の6個の部分での重なりが発生する。なお、露光量が多ければ印字が濃くなると仮定すれば、この重なり部分での露光量増大により、印字結果に縦筋が発生する。

40

#### 【0029】

図9(a)は、図5の発光素子アレイ10A-mと発光素子アレイチップ10A-(m+1)とを隣接して配置された第2の状態を示す発光素子10A-mの端部の拡大図であり、図9(b)は、図9(a)の印字結果を示す概略図である。図9(a)では、隣接チップ10A-(m+1)が目標位置Tより内側の場合、すなわち隣接チップ同士の間隔が狭く、主走査方向Xに見た発光素子間隔がピッチより狭くなっている場合が図示される。この場合には、補正用データに基づいて、発光素子A255、B255、C255が使用され、発光素子D255、E255が使用されないように設定される。この設定に

50

より、右端の発光素子と、その隣の列の発光素子との間での重なりは発生するが、図 8 (b) に比較すると重なり部分が減少するので、印字結果に発生する縦筋を低減させることができる。

#### 【0030】

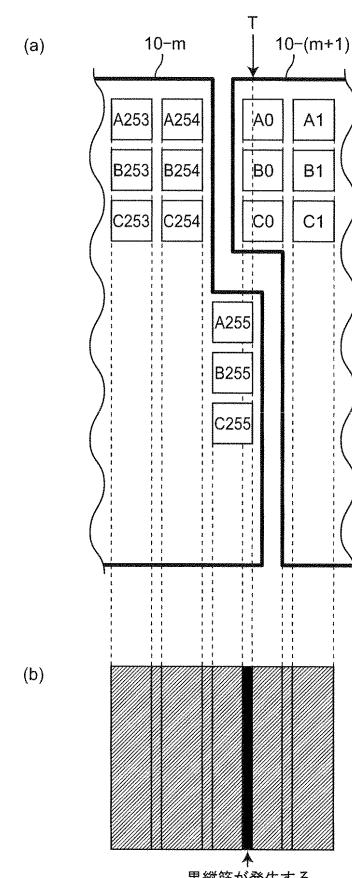

図 10 (a) は、図 2 の発光素子アレイチップ 10 - m と発光素子アレイチップ 10 - (m + 1) を隣接して配置された第 3 の状態を示す発光素子 10 - m の端部の拡大図であり、図 10 (b) は、図 10 (a) の印字結果を示す概略図である。図 10 (a) では、隣接チップ 10 - (m + 1) が目標位置 T より外側の場合、すなわち隣接チップ同士の間隔が広く、主走査方向 X に見た発光素子間隔がピッチより広くなつて実装された場合が図示される。この場合には、主走査方向 X の発光素子ピッチが隣接チップ間で離れるので、露光が行われないかもしくは露光が弱い部分が発生する。従つて、印字結果に縦筋（白縦筋）が発生する。10

#### 【0031】

図 11 (a) は、図 5 の発光素子アレイ 10 A - m と発光素子アレイチップ 10 A - (m + 1) を隣接して配置された第 3 の状態を示す発光素子 10 A - m の端部の拡大図であり、図 11 (b) は、図 11 (a) の印字結果を示す概略図である。図 11 (a) では、隣接チップ 10 A - (m + 1) が目標位置 T より外側の場合、すなわち隣接チップ同士の間隔が広く、主走査方向 X に見た発光素子間隔がピッチより広くなつて実装された場合が図示される。この場合には、補正用データに基づいて、発光素子 C 255、D 255、E 255 が使用され、発光素子 A 255、B 255 が使用されないように設定される。この設定により、右端の発光素子と、その隣の列の発光素子との間の間隔が縮まる。従つて、図 10 (b) に比較すると露光が弱い部分が減少するので、印字結果に発生する白縦筋を低減させることができる。20

#### 【0032】

以上の実施形態に係る画像形成装置 100 A によれば、実施形態 1 に係る画像形成装置 100 と同様の効果を得ることができ。さらに、実施形態 1 に係る画像形成装置 100 と比較すると、チップの基板上への実装時の誤差を低減させるための発光素子を追加するので、実装時の誤差による印字結果の縦筋を低減することが可能となる。

#### 【0033】

なお、上述した実施形態では、第 2 の発光素子群ブロックの各発光素子群を構成する発光素子の数を第 1 の発光素子群ブロックの各発光素子群を構成する発光素子の数よりも 2 個多く設定した。しかしながら、本発明はこれに限定されず、さらに多くの発光素子を追加してもよい。その場合には、チップの隣接間距離に応じてさらに細かな制御を行うことができる。30

#### 【0034】

なお、上述した実施形態では、第 2 の発光素子群ブロックの各発光素子群を構成する発光素子の数を第 1 の発光素子群ブロックの各発光素子群を構成する発光素子の数よりも 2 個多く設定した。しかしながら、本発明はこれに限定されない。例えば、発光素子 A 255 や発光素子 C 255 の光量を増減させることにより、実装時の誤差を補正して印字結果の縦筋を低減させててもよい。40

#### 【0035】

変形例 1.

上述した実施形態では、3 個の発光素子が副走査方向 Y に配置される発光素子群を主走査方向 X に等間隔で複数列配置される発光素子アレイチップの場合について説明した。しかしながら、本発明はこれに限定されない。例えば、副走査方向に配置される自然数 N 個の発光素子を有する複数の発光素子群が配置される発光素子アレイチップにも本発明を適用することが可能である。

#### 【0036】

例えば、発光素子アレイチップは、副走査方向に配置される自然数 N 個の発光素子を有する複数の発光素子群を配置するように構成してもよい。ここで、発光素子アレイチップ

10

20

30

40

50

は、複数の発光素子群が主走査方向に互いに所定の第1の間隔で配置された第1の発光素子群ブロックを備える。また、発光素子アレイチップは、上記発光素子アレイチップのいずれか一方の端部側の1つ以上の発光素子群が、基準位置から所定の第2の間隔だけ副走査方向にずらして配置された第2の発光素子群ブロックを備える。ここで、第1の発光素子群ブロックの各発光素子群の位置を基準位置とする。また、上記第2の間隔は、上記各発光素子群の副走査方向の幅以上に設定される。また、上記第2の発光素子群ブロックの各発光素子群の発光素子の数はそれぞれ、(N + 1)個以上であり、上記第2の発光素子群ブロックの各発光素子群の発光素子は、主走査方向に互いに等間隔だけずらして配置される。

## 【0037】

10

また、チップ実装基板は、上述した発光素子アレイチップが主走査方向に互いに隣接して配置され、上記第2の発光素子群ブロックの各発光素子群の発光素子から、動作させるN個の発光素子を選択するデータを格納する記憶手段を備える。さらに、チップ実装基板は、上述した発光素子アレイチップが主走査方向に互いに隣接して配置され、上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿ってダイシングされる。またさらに、上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿って矩形状でもしくは所定の角度で屈曲してダイシングされる。また、画像形成装置は、上述したチップ実装基板を備える。

## 変形例2.

20

上述した実施形態及び変形例では、発光素子として無機LEDを使用したが、本発明はこれに限定されない。例えば、発光素子として無機LEDの代わりに有機EL素子を用いてもよい。

## 【0038】

なお、上述した画像形成装置100及び100Aには、感光体ドラム9をトナーで現像する画像形成手段と、当該画像形成手段が形成したトナー像が用紙に転写される位置まで用紙を搬送する用紙搬送手段と、用紙にトナー像を転写する転写手段とを含んでもよい。ここで、画像形成装置は、例えば複写機、プリンタ、ファクシミリなどであってもよい。

## 【0039】

## 実施形態のまとめ

30

第1の態様に係る発光素子アレイチップは、副走査方向に配置される自然数N個の発光素子を有する複数の発光素子群が配置される発光素子アレイチップであって、

上記複数の発光素子群が主走査方向に互いに所定の第1の間隔で配置された第1の発光素子群ブロックと、

上記発光素子アレイチップのいずれか一方の端部側の1つ以上の発光素子群が、上記第1の発光素子群ブロックの各発光素子群の位置を基準位置として、当該基準位置から所定の第2の間隔だけ副走査方向にずらして配置された第2の発光素子群ブロックとを備えたことを特徴とする。

## 【0040】

40

第2の態様に係る発光素子アレイチップは、第1の態様に係る発光素子アレイチップにおいて、上記第2の間隔は、上記各発光素子群の副走査方向の幅以上に設定されることを特徴とする。

## 【0041】

第3の態様に係る発光素子アレイチップは、第1または第2の態様に係る発光素子アレイチップにおいて、上記第2の発光素子群ブロックの各発光素子群の発光素子の数はそれぞれ、(N + 1)個以上であることを特徴とする。

## 【0042】

第4の態様に係る発光素子アレイチップは、第3の態様に係る発光素子アレイチップにおいて、上記第2の発光素子群ブロックの各発光素子群の発光素子は、主走査方向に互い

50

に等間隔だけずらして配置されることを特徴とする。

【0043】

第5の態様に係るチップ実装基板は、第4の態様に係る発光素子アレイチップが主走査方向に互いに隣接して配置されるチップ実装基板であって、上記第2の発光素子群ブロックの各発光素子群の発光素子から、動作させるN個の発光素子を選択するデータを格納する記憶手段を備えたことを特徴とする。

【0044】

第6の態様に係るチップ実装基板は、第1～第4のうちのいずれか1つに記載の態様に係る発光素子アレイチップが主走査方向に互いに隣接して配置されるチップ実装基板であって、上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿ってダイシングされることを特徴とする。

10

【0045】

第7の態様に係るチップ実装基板は、第6の態様に係るチップ実装基板において、上記各発光素子アレイチップは、上記第2の発光素子群ブロックの端部側の発光素子群の各発光素子配置に沿って矩形状でもしくは所定の角度で屈曲してダイシングされることを特徴とする。

【0046】

第8の態様に係る画像形成装置は、第5～第7のうちのいずれか1つに記載の態様に係るチップ実装基板を備えたことを特徴とする。

20

【符号の説明】

【0047】

- 1 , 1 A ... チップ実装基板、

- 2 ... レジスタ、

- 3 ... 駆動回路、

- 4 ... ワイヤーボンディングパッド、

- 5 ... ボンディングワイヤ、

- 6 ... コネクタ、

- 7 ... 発光制御回路、

- 8 ... 光書き込みユニット、

- 9 ... 感光体ドラム、

- 10 - 1 , … , 10 - M , 10A - 1 , … , 10A - M ... 発光素子アレイチップ、

A0 ~ C0 , … , A255 ~ C255 , D255 , E255 ... 発光素子、

100 , 100A ... 画像形成装置。

30

【先行技術文献】

【特許文献】

【0048】

【特許文献1】特開平09-263004号公報

【特許文献2】特開平10-244706号公報

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

F ターム(参考) 2C162 AE04 AE21 AE28 AE40 AE73 AF05 AF06 AF13 AF24 AF40

FA04 FA16 FA17

2H076 AB42 AB51 AB53 AB54 DA31

5C051 AA02 CA08 DA06 DB02 DB29 DC02 DC05 EA03 FA01

5F142 AA56 AA66 BA32 CA03 CB18 CB22 CD01 DB24 GA06