(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6300349号

(P6300349)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO2M 3/155 (2006.01)  | HO2M 3/155 E  |

| HO2M 1/08 (2006.01)   | HO2M 1/08 A   |

| HO3K 17/16 (2006.01)  | HO3K 17/16 H  |

| HO3K 17/687 (2006.01) | HO3K 17/687 F |

請求項の数 5 (全 18 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2014-21259 (P2014-21259)    |

| (22) 出願日     | 平成26年2月6日(2014.2.6)           |

| (65) 公開番号    | 特開2014-176290 (P2014-176290A) |

| (43) 公開日     | 平成26年9月22日(2014.9.22)         |

| 審査請求日        | 平成29年1月13日(2017.1.13)         |

| (31) 優先権主張番号 | 13/794, 038                   |

| (32) 優先日     | 平成25年3月11日(2013.3.11)         |

| (33) 優先権主張国  | 米国(US)                        |

|           |                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 300057230<br>セミコンダクター・コンポーネンツ・イン<br>ダストリーズ・リミテッド・ライアビリテ<br>イ・カンパニー<br>アメリカ合衆国 アリゾナ州 85008<br>フェニックス イースト・マクドウェル<br>・ロード50005 |

| (74) 代理人  | 100091915<br>弁理士 本城 雅則                                                                                                       |

| (74) 代理人  | 100099106<br>弁理士 本城 吉子                                                                                                       |

| (72) 発明者  | ゲイリー・エイチ・ローケルト<br>アメリカ合衆国 アリゾナ州 85281<br>テンピ イースト・14ス・ストリート<br>231                                                           |

最終頁に続く

(54) 【発明の名称】スイッチング素子、整流素子、および電荷蓄積素子を含む回路

## (57) 【特許請求の範囲】

## 【請求項 1】

回路において、

第1の通電電極および第2の通電電極を有する第1のスイッチング素子と、

第1の通電電極および第2の通電電極を有する第2のスイッチング素子であって、前記第2のスイッチング素子の前記第1の通電電極は、前記第1のスイッチング素子の前記第2の通電電極に結合される、第2のスイッチング素子と、

アノードおよびカソードを有する第1の整流素子であって、前記第1の整流素子の前記カソードは、前記第1のスイッチング素子の前記第2の通電電極に結合される、第1の整流素子と、

アノードおよびカソードを有する第2の整流素子であって、前記第2の整流素子の前記アノードは、前記第2のスイッチング素子の前記第1の通電電極に結合される、第2の整流素子と、

第1の端子および第2の端子を有する第1の電荷蓄積素子であって、前記第1の電荷蓄積素子の前記第1の端子は、前記第1のスイッチング素子の前記第1の通電電極に結合され、前記第1の電荷蓄積素子の前記第2の端子は、前記第1の整流素子の前記アノードに結合される、第1の電荷蓄積素子と、

第1の端子および第2の端子を有する第2の電荷蓄積素子であって、前記第2の電荷蓄積素子の前記第1の端子は、前記第2の整流素子の前記カソードに結合され、前記第2の電荷蓄積素子の前記第2の端子は、前記第2のスイッチング素子の前記第2の通電電極に

10

20

結合される、第2の電荷蓄積素子と、を備え、

前記回路の負極端子と前記第1の電荷蓄積素子との間の寄生特徴は、前記第1のスイッチング素子と前記第1の電荷蓄積素子との間の寄生特徴より大きいか、あるいは、

前記回路の正極端子と前記第2の電荷蓄積素子との間の寄生特徴は、前記第2のスイッチング素子と前記第2の電荷蓄積素子との間の寄生特徴より大きい、

ことを特徴とする回路。

#### 【請求項2】

回路において、

第1の通電電極および第2の通電電極を有するハイサイドトランジスタと、

第1の通電電極および第2の通電電極を有するローサイドトランジスタであって、前記ローサイドトランジスタの前記第1の通電電極は、前記ハイサイドトランジスタの前記第2の通電電極に結合される、ローサイドトランジスタと、10

アノードおよびカソードを有する第1の整流素子であって、前記第1の整流素子の前記カソードは、前記ハイサイドトランジスタの前記第2の通電電極に結合される、第1の整流素子と、

アノードおよびカソードを有する第2の整流素子であって、前記第2の整流素子の前記アノードは、前記ローサイドトランジスタの前記第1の通電電極に結合される、第2の整流素子と、

第1の端子および第2の端子を有する第1の電荷蓄積素子であって、前記第1の電荷蓄積素子の前記第1の端子は、前記ハイサイドトランジスタの前記第1の通電電極に結合され、前記第1の電荷蓄積素子の前記第2の端子は、前記第1の整流素子の前記アノードに結合される、第1の電荷蓄積素子と、20

第1の端子および第2の端子を有する第2の電荷蓄積素子であって、前記第2の電荷蓄積素子の前記第1の端子は、前記第2の整流素子の前記カソードに結合され、前記第2の電荷蓄積素子の前記第2の端子は、前記ローサイドトランジスタの前記第2の通電電極に結合される、第2の電荷蓄積素子と、を備え、

前記回路の負極端子と前記第1の電荷蓄積素子との間の寄生特徴は、前記ハイサイドトランジスタと前記第1の電荷蓄積素子との間の寄生特徴より大きいか、あるいは、

前記回路の正極端子と前記第2の電荷蓄積素子との間の寄生特徴は、前記ローサイドトランジスタと前記第2の電荷蓄積素子との間の寄生特徴より大きく、30

前記第1の整流素子は、前記回路の負極端子より前記ハイサイドトランジスタに近接するか、あるいは、

前記第2の整流素子は、前記回路の正極端子より前記ローサイドトランジスタに近接する、

ことを特徴とする回路。

#### 【請求項3】

前記第1または第2の電荷蓄積素子は静電容量を有し、前記ハイサイドトランジスタ、前記ローサイドトランジスタ、または前記ハイサイドおよびローサイドトランジスタのそれぞれは、その対応する第1および第2の通電電極間に静電容量を有し、前記第1または第2の電荷蓄積素子の前記静電容量と、前記その対応する第1および第2の通電電極間の静電容量との比率は、少なくとも1.5:1であることを特徴とする請求項2記載の回路。40

。

#### 【請求項4】

前記第1または第2の整流素子は、並列に電気的に接続されるショットキーダイオードおよびpn接合ダイオードを含むことを特徴とする請求項2記載の回路。

#### 【請求項5】

スイッチング回路において、

ソース、ゲート、およびドレインを有するハイサイドトランジスタであって、

前記ハイサイドトランジスタの前記ドレインは、第1の電力端子に電気的に接続され50

、

前記ハイサイドトランジスタの前記ゲートは、前記スイッチング回路の第1の入力に電気的に接続され、

前記ハイサイドトランジスタの前記ソースは、前記スイッチング回路の出力端子に電気的に接続される、ハイサイドトランジスタと、

ソース、ゲート、およびドレインを有するローサイドトランジスタであって、

前記ローサイドトランジスタの前記ドレインは、前記出力端子に電気的に接続され、

前記ローサイドトランジスタの前記ゲートは、前記スイッチング回路の第2の入力に電気的に接続され、

前記ローサイドトランジスタの前記ソースは、第2の電力端子に電気的に接続される、ローサイドトランジスタと、

アノードおよびカソードを有する第1のショットキーダイオードであって、前記第1のショットキーダイオードの前記カソードは、前記ハイサイドトランジスタの前記ソースに電気的に接続される、第1のショットキーダイオードと、

アノードおよびカソードを有する第2のショットキーダイオードであって、前記第2のショットキーダイオードの前記アノードは、前記ローサイドトランジスタの前記ドレインに電気的に接続される、第2のショットキーダイオードと、

第1の端子および第2の端子を有する第1のコンデンサであって、前記第1のコンデンサの前記第1の端子は、前記第1の電力端子に電気的に接続され、前記第1のコンデンサの前記第2の端子は、前記第1のショットキーダイオードの前記アノードに電気的に接続される、第1のコンデンサと、

第1の端子および第2の端子を有する第2のコンデンサであって、前記第2のコンデンサの前記第1の端子は、前記第2の電力端子に電気的に接続され、前記第2のコンデンサの前記第2の端子は、前記第2のショットキーダイオードの前記カソードに電気的に接続される、第2のコンデンサと、を備え、

前記スイッチング回路の負極端子と前記第1のコンデンサとの間の寄生特徴は、前記ハイサイドトランジスタと前記第1のコンデンサとの間の寄生特徴より大きいか、あるいは、

前記スイッチング回路の正極端子と前記第2のコンデンサとの間の寄生特徴は、前記ローサイドトランジスタと前記第2のコンデンサとの間の寄生特徴より大きい、

ことを特徴とするスイッチング回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本開示は、スイッチング素子、整流素子、および電荷蓄積素子を含む回路に関する。

##### 【背景技術】

##### 【0002】

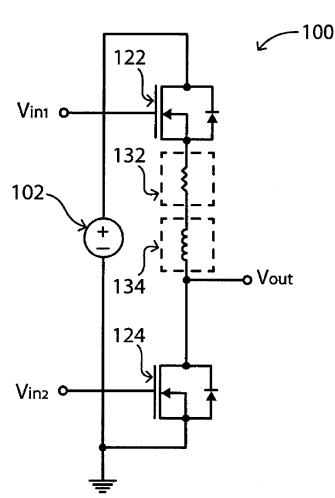

絶縁ゲート型電界効果トランジスタ（IGFET）は、よくあるタイプの電力スイッチングデバイスである。IGFETは、図1のスイッチング回路100等のスイッチング回路を提供するように接続することができ、該スイッチング回路は、出力電圧を、電源102よりも大幅に高い電圧または低い電圧とすることを可能にする。2つのnチャネルIGFET122, 124は、IGFET122のドレインが電源102の正極端子に電気的に接続され、かつIGFET124のソースが電源102の負極端子に電気的に接続されるように接続される。IGFET122のソースおよびIGFET124のドレインは、 $V_{out}$ を提供する出力端子に電気的に接続される。IGFET122, 124のゲートは、 $V_{in1}$ および $V_{in2}$ を提供する入力端子に電気的に接続される。

##### 【0003】

入力端子は、スイッチング回路100を制御する。理想的には、IGFET122がオンになり、かつIGFET124がオフになるようにIGFET122, 124の状態が切り替わると、 $V_{out}$ は、出力端子においていかなる電圧のオーバーシュート、電圧のアンダーシュート、またはリングング（オーバーシュート電圧とアンダーシュート電圧と

10

20

30

40

50

の間の変動)も伴わずに、即座に電源 102 の正極端子の電圧になる。理想的には、IGFET 122 がオフになり、かつ IGFET 124 がオンになるよう IGFET 122, 124 の状態が切り替わると、 $V_{out}$  は、出力端子においていかなる電圧のオーバーシュート、電圧のアンダーシュート、またはリングング(オーバーシュート電圧とアンダーシュート電圧との間の変動)も伴わずに、即座に電源 102 の負極端子の電圧になる。

#### 【0004】

スイッチング回路 100 は、IGFET 122 のソース、IGFET 124 のドレイン、および出力端子  $V_{out}$  が互いに電気的に接続される場合であっても、理想的でなく、それら 3 つの間で寄生特徴を有する。寄生特徴は、寄生抵抗および寄生インダクタンス等の寄生素子としてモデル化することができ、図では破線の箱内に表される。スイッチング回路 100 において、寄生特徴は、IGFET 122 のソースと出力端子との間で直列に接続される寄生抵抗 132 および寄生インダクタンス 134 によってモデル化される。本明細書において後で論じられるように、寄生特徴は、出力ノードでリングングを生じさせる可能性があり、IGFET 124 のドレイン - ソース間の絶縁破壊電圧を超える可能性がある顕著な電圧オーバーシュート、出力端子に結合される負荷(図示せず)への損傷、または別の悪影響が挙げられる。

#### 【図面の簡単な説明】

#### 【0005】

実施形態は、一例として図示されるものであり、添付図面に限定されない。

#### 【0006】

【図 1】スイッチング回路の図である。(従来技術)

【図 2】実施形態に従う、回路の図である。

【図 3】特定の実施形態に従う特定の回路要素を伴う、図 2 の回路の図である。

【図 4】寄生回路要素で表される寄生特徴を伴う、図 3 の回路の図である。

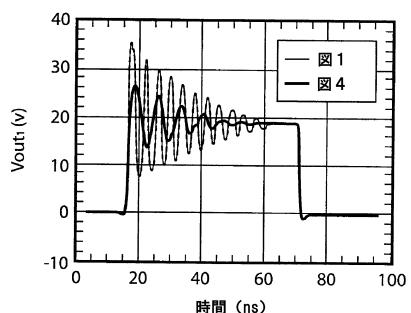

【図 5】出力端子の電圧が比較的低い電圧から比較的高い電圧に変化した後の、図 1 および図 4 に従う回路の出力電圧を図示するプロット図である。

#### 【0007】

当業者は、図中の要素が、簡潔かつ明確にするために図示されたものであり、必ずしも一定の縮尺で描かれたものではないことを認識するであろう。例えば、図中の要素のいくつかの寸法は、本発明の実施形態の理解を高めるのを補助するために、他の要素に対して誇張され得る。また、概念的に簡潔にするために、单一の回路素子によって表されるいくつかの構造は、実際には、直列、並列、または他の何らかの直列および並列の組み合わせのいずれかで接続される、複数の物理素子に対応し得る。

#### 【発明を実施するための形態】

#### 【0008】

図面と組み合せた以下の説明は、本明細書で開示される教示を理解する際に支援するために提供される。以下の議論は、本教示の具体的な実現例および実施形態に重点を置く。この重点は、本教示を説明する際に支援するために提供されるものであり、本教示の範囲または適用範囲を限定するものとして解釈されるべきではない。しかしながら、本出願では、当然、他の教示も利用することができる。

#### 【0009】

本明細書で使用される「結合される」という用語は、信号(例えば、電流、電圧、または光信号)が一方からもう一方に伝達され得るような、2つ以上の電子構成要素、回路、システム、または(1)少なくとも1つの電子構成要素、(2)少なくとも1つの回路、もしくは(3)少なくとも1つのシステムの任意の組み合せの接続、結合、関連付けを意味することを意図する。「結合される」の限定的でない例としては、電子構成要素(複数可)間の電気的接続、スイッチ(例えば、トランジスタ(複数可))がそれらの間に接続された回路(複数可)または電子構成要素(複数可)等が挙げられる。

#### 【0010】

電子構成要素、回路、またはそれらの一部分に関する「電気的に接続される」という用

10

20

30

40

50

語は、2つ以上の電子構成要素、回路、または少なくとも1つの電子構成要素および少なくとも1つの回路の任意の組み合わせが、それらの間に存在するいかかる介在電子構成要素も有しないことを意味することを意図する。寄生抵抗、寄生容量、寄生インダクタンス、またはそれらの任意の組み合わせは、この定義の目的で、電子構成要素とみなされない。一実施形態において、電子構成要素は、それらが互いに電気的に短絡し、実質的に同じ電圧であるときに電気的に接続される。

#### 【0011】

「通常動作」および「通常動作状態」という用語は、それらの下で電子構成要素またはデバイスが動作するように設計される条件を指す。この条件は、電圧、電流、静電容量、抵抗、または他の電気条件に関するデータシートまたは他の情報から取得され得る。10したがって、通常動作は、電気構成要素またはデバイスがその設計限界を大幅に超えて動作することを含まない。

#### 【0012】

「電力トランジスタ」という用語は、電界効果トランジスタまたはバイポーラトランジスタがオフ状態であるときに、電界効果トランジスタのドレインとソースとの間で、またはバイポーラトランジスタのコレクタとエミッタとの間で、少なくとも10Vの差を維持することができるトランジスタを意味することを意図する。

#### 【0013】

「備える (comprises)」、「備えている (comprising)」、「含む (includes)」、「含んでいる (including)」、「有する (has)」、「有している (having)」という用語、またはその任意の他の変形は、非排他的な包含を対象とすることを意図する。例えば、列記された特徴を備える方法、部品、または装置は、必ずしもこれらの特徴だけに限定されず、明確に列記されていない他の特徴、またはそのような方法、部品、または装置に固有の特徴を含み得る。さらに、明確に逆の意味で述べられていない限り、「または (or)」は、排他的論理和ではなく、包含的論理和を指す。例えば、AまたはBという条件は、Aが真（または存在する）かつBが偽（または存在しない）である、Aが偽（または存在しない）かつBが真（または存在する）である、ならびにAとBの両方が真（または存在する）である、という条件のうちのいずれか1つによって満たされる。20

#### 【0014】

また、本明細書で説明される要素および構成要素を説明するために、単数形（「a」または「a n」）も使用される。これは、単に便宜的なものであり、本発明の範囲の一般的な意味を提供するために行われる。この説明は、1つまたは少なくとも1つを含むものと読み取られるべきであり、他の意味になることが明らかでない限り、単数形は、複数形も含み、その逆もまた同じである。例えば、单一の品目が本明細書で説明されるときに、2つ以上の品目が单一の品目の代わりに使用され得る。同様に、2つ以上の品目が本明細書で説明される場合、单一の品目がその2つ以上の品目の代わりになり得る。30

#### 【0015】

別途定義されない限り、本明細書で使用される全ての技術用語および科学用語は、本発明が属する技術分野の当業者によって共通に理解されるものと同じ意味を有する。材料、方法、および実施例は、例示的なものに過ぎず、限定することを意図していない。本明細書で説明されない限り、特定の材料および処理行為に関する数多くの詳細は、慣習的なものであり、半導体および電子技術の範囲内の教科書および他の出典で見出され得る。40

#### 【0016】

回路は、電源の端子に電気的に接続される端子を有し、かつ出力端子に電気的に接続されるもう一方の端子を有する、1対のスイッチング素子を含むことができる。回路は、対応するスイッチング素子と並列に電気的に接続される、1つ以上の整流素子を含むことができる。回路はさらに、電源の端子間に電気的に接続される、1つ以上の電荷蓄積素子を含むことができる。特定の実施形態において、スイッチング素子はトランジスタであり、各トランジスタは、トランジスタと並列に電気的に接続される、対応する整流素子を有す50

る。整流素子は、p n 接合ダイオード、ショットキーダイオード、またはそれらの任意の組み合わせとすることができます。蓄積素子は、平行板コンデンサ構造、トランジスタ構造等を有する、コンデンサ（キャパシタ）とすることができます。特定の実施形態において、コンデンサは、コンデンサの一方の電極と電源の端子の一方との間の寄生特徴が、コンデンサのもう一方の電極と電源のもう一方の端子との間の寄生特徴よりも大幅に少なくなるように実現される。特定の実施形態において、回路は、バックコンバータとすることができます。回路に関する詳細は、下で説明される特定の実施形態に関してより良く理解され、そのような実施形態は、単なる実例に過ぎず、本発明の範囲を限定するものではない。

#### 【0017】

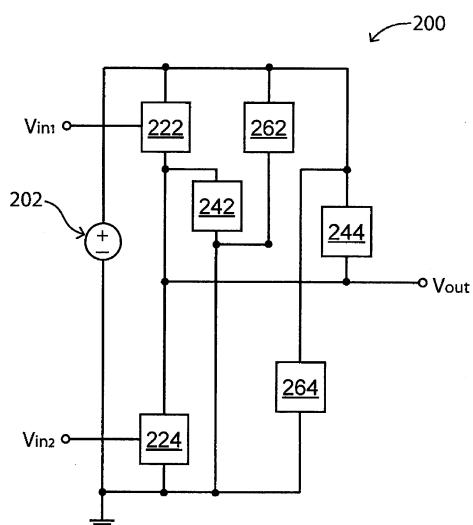

図2は、実施形態に従う、回路200の図を含む。電源202は、電力を回路200に提供し、正極端子と、接地に結合される負極端子とを含む。別の実施形態では、2つ以上の電源が使用され得、または電源202の端子の一方だけが回路200に結合される。さらなる実施形態において、回路200は、接地電位でない端子を有する電源の端子に結合される。電源202は、1V、5V、12V、19Vの公称電圧、または別の好適な電圧を提供し得る。特定の実施形態において、電源202は、直流(DC)電源である。電源202としては、電池、直流発電機、交流発電機、コンデンサ、または電力を回路202に提供することができる別の好適なデバイスが挙げられる。必要または所望に応じて、さらなる回路が使用され得る。例えば、電源202が交流発電機であるときには、ブリッジ整流器(図示せず)または別の好適な回路が使用され得、回路200は、交流(AC)電圧の代わりにDC電圧を受け取るものである。特定の実施形態において、電源202の端子は、回路200に電気的に接続される。

#### 【0018】

回路200は、電源202の正極端子に結合される通電端子、および $V_{out}$ を提供する回路200の出力端子に結合される別の通電端子を有する、スイッチング素子222を含む。回路200は、電源202の負極端子に結合される通電端子、および出力端子に結合される別の通電端子を有する、スイッチング素子224を含む。スイッチング素子222, 224は、 $V_{in1}$ および $V_{in2}$ をそれぞれ回路200に提供する回路200の入力端子に結合される、制御電極を有する。

#### 【0019】

スイッチング素子222, 224は、電界効果トランジスタ、バイポーラトランジスタ、スイッチング回路のための別の好適なスイッチング素子構造、またはそれらの任意の組み合わせとすることができます。スイッチング素子222, 224のそれぞれは、並列に接続された複数のトランジスタ構造を含むことができ、よって、トランジスタ構造の組み合わせは、单一のトランジスタと電気的に均等である。

#### 【0020】

回路200はさらに、整流素子242, 244を含む。整流素子242は、電源202の負極端子に結合されるアノードと、スイッチング素子222, 224の通電電極に結合されるカソードとを有する。整流素子244は、スイッチング素子222, 224の通電電極に結合されるアノードと、電源202の正極端子に結合されるカソードとを有する。

#### 【0021】

整流素子242, 244は、p n 接合ダイオード、ショットキーダイオード、別の好適な整流素子構造、またはそれらの任意の組み合わせとすることができます。整流素子242, 244のそれぞれは、並列に接続された複数のダイオードを含むことができ、よって、ダイオードの組み合わせは、单一のダイオードと電気的に均等である。

#### 【0022】

回路200はなおさらに、電荷蓄積素子262, 264を含む。電荷蓄積素子262は、電源202の正極端子に結合される電極と、整流素子242のアノードに結合される別の電極とを有する。電荷蓄積素子264は、整流素子244のカソードに結合される電極と、電源202の負極端子に結合される別の電極とを有する。

#### 【0023】

10

20

30

40

50

電荷蓄積素子 262, 264 は、平行板コンデンサ構造、電界効果トランジスタ構造、別の好適な電荷蓄積素子構造、またはそれらの任意の組み合わせの形態とすることができます。電荷蓄積素子 262, 264 のそれぞれは、並列に接続された複数の構造を含むことができ、よって、構造の組み合わせは、単一のコンデンサに電気的に均等である。

#### 【0024】

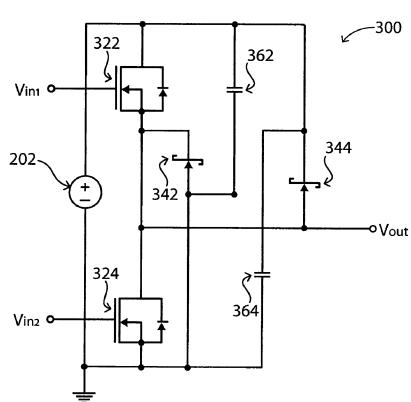

図 3 は、実施形態に従う回路 200 の限定的でない実現例である、特定の回路 300 の図を含む。図 3 で図示される回路 300 は、スイッチング回路であり、より具体的には、バックコンバータであり、高周波電圧調整器として使用することができる。図 2 のスイッチング素子 222, 224 は、図 3 において n チャネル IGBT 322, 324 である。IGBT 322, 324 は、それらのソースに結合されるそれらの本体を有する。

10

#### 【0025】

IGBT 322, 324 の活性領域は、pn 接合ダイオードを形成する。IGBT 322, 324 の pn 接合ダイオードは、IGBT 322, 324 のドレインおよびソースの間で維持することができる、最大持続可能電圧差を決定するために使用することができる。そのような電圧差は、ドレイン - ソース間絶縁破壊電圧と称することができる。スイッチング回路 200 の標準動作電圧は、IGBT を選択する際の絶縁破壊電圧を決定し得る。絶縁破壊電圧は、電源 202 の端子間の電圧の少なくとも 2 倍であり得る。例えば、電源 202 が 12V の公称電圧を有する場合、IGBT 322, 324 は、少なくとも約 24V のドレイン - ソース間絶縁破壊電圧を有することができる。限定的でない実施形態において、IGFET 322, 324 のドレイン - ソース間絶縁破壊電圧は、少なくとも約 30V である。IGFET 322, 324 は、ほぼ同じドレイン - ソース間絶縁破壊電圧または異なるドレイン - ソース間絶縁破壊電圧を有し得る。本明細書の後半で論じられるように、整流素子および電荷蓄積素子は、IGBT の一方または双方の状態が変化した後の過渡時間中に、IGBT のドレイン - ソース間絶縁破壊が起こらない可能性を低減させるのを補助する。

20

#### 【0026】

図 2 の整流素子 242, 244 は、図 3 においてショットキーダイオード 342, 344 である。別の実施形態において、ショットキーダイオード 342, 344 のそれぞれは、pn ダイオード、または pn 接合ダイオードおよびショットキーダイオードの組み合わせによって置き換えることができる。逆バイアス絶縁破壊電圧は、ドレイン - ソース間絶縁破壊電圧の約 2.0 倍以下であり得る。特定の実施形態において、逆バイアス絶縁破壊電圧は、ドレイン - ソース間絶縁破壊電圧の約 1.5 倍以下であり得、より具体的な実施形態において、逆バイアス絶縁破壊電圧は、ドレイン - ソース間絶縁破壊電圧の約 1.2 倍以下であり得る。さらにより具体的な実施形態において、逆バイアス絶縁破壊電圧は、ドレイン - ソース間絶縁破壊電圧の約 1.0 倍以下であり得る。ショットキーダイオード 342, 344 は、同じ逆バイアス絶縁破壊電圧または異なる逆バイアス絶縁破壊電圧を有することができる。一実施形態において、整流素子 242、整流素子 244、または整流素子 242, 244 のそれぞれは、複数のダイオードを含むことができ、ダイオードの少なくとも 1 つは、上で説明される逆バイアス絶縁破壊を有する。特定の実施形態において、整流素子 242、整流素子 244、または整流素子 242, 244 のそれぞれを形成する 1 組のダイオード内の全てのダイオードは、上で説明される逆バイアス絶縁破壊を有することができる。

30

#### 【0027】

図 2 の電荷蓄積素子 262, 264 は、図 3 においてコンデンサ 362, 364 である。コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、IGBT 322、IGFET 324、または IGBT 322, 324 のそれぞれのドレイン - ソース間静電容量との比率は、少なくとも約 1.5 : 1 とすることができます。特定の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、ドレイン - ソース間静電容量とは、少なくとも約 2 : 1 とすることでき、より具体的な実施形態において、コンデンサ 362、コ

40

50

ンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、ドレイン - ソース間静電容量とは、少なくとも約 4 : 1 とすることができます。別の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、ドレイン - ソース間静電容量とは、約 25 : 1 以下であり得る。特定の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、ドレイン - ソース間静電容量とは、約 16 : 1 以下であり得、より具体的な実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量と、ドレイン - ソース間静電容量とは、約 9 : 1 以下であり得る。

## 【0028】

10

コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、相対条件ではなく、絶対条件で表すことができる。一実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、少なくとも約 80 pF とすることができます。特定の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、少なくとも約 200 pF とでき、より具体的な実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、少なくとも約 1.5 nF とすることができます。別の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、約 40 nF 以下であり得る。特定の実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、約 30 nF 以下であり得、より具体的な実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、約 20 nF 以下であり得る。さらなる実施形態において、コンデンサ 362、コンデンサ 364、またはコンデンサ 362, 364 のそれぞれの静電容量は、約 1.5 nF ~ 約 40 nF の範囲とすることができます。

20

## 【0029】

数多くの値を回路 200, 300 内の電子素子に提供した。そのような値は、例示するために提供されており、本明細書で説明される概念の範囲を限定するものではない。本明細書を読んだ後に、当業者は、絶対値または相対値の選択が、回路が動作する特定の応用例または環境に依存することを認識するであろう。

30

## 【0030】

図 2 の 200 および図 3 の 300 で説明される回路において、回路要素間の結合は、電気的接続とすることができます。図 3 に関して、回路 300 の出力ノードは、IGFET 322 のソースと、IGFET 324 のドレインと、ショットキーダイオード 342 のカソードと、ショットキーダイオード 344 のアノードとを含むことができる。別のノードは、電源 202 の正極端子と、IGFET 322 のドレインと、コンデンサ 362, 364 の電極と、ショットキーダイオード 344 のカソードとを含むことができる。さらなるノードは、電源 202 の負極端子と、IGFET 324 のソースと、コンデンサ 362, 364 の他の電極と、ショットキーダイオード 342 のアノードとを含むことができる。

## 【0031】

40

図 3 の回路 300 は、構成要素間の相互接続による寄生特徴を考慮しない。例えば、IGFET 322, 324 は、異なるダイ上にあり得、IGFET 322 のソース、IGFET 324 のドレイン、および出力端子を互いに電気的に接続する金属ストラップを含み得る。これらの接続は、回路の動作に大きな影響を及ぼすことができる、寄生特徴を有することができる。寄生特徴は、回路をモデル化するときに使用することができる。

## 【0032】

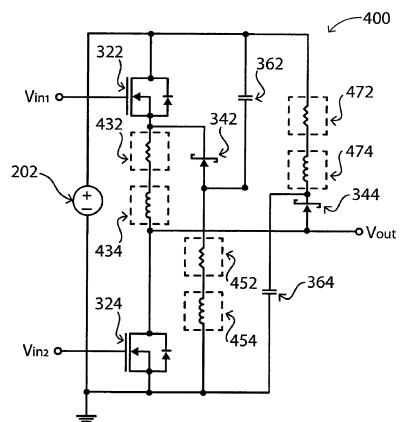

図 4 は、図 3 の回路 300 と類似する、回路 400 を含む。回路 400 は、破線の箱内に図示される寄生抵抗および寄生インダクタンスを含む。寄生抵抗 432 および寄生インダクタ 434 は、ショットキーダイオード 342 のカソードと出力端子との間で直列に電気的に接続される。ショットキーダイオード 342 およびコンデンサ 362 は、電源 20

50

2 の負極端子よりも I G F E T 3 2 2 の近くに物理的に位置する。電源 2 0 2 の負極端子とショットキーダイオード 3 4 2 およびコンデンサ 3 6 2 のそれぞれとの間の寄生特徴は、 I G F E T 3 2 2 とショットキーダイオード 3 4 2 およびコンデンサ 3 6 2 のそれぞれとの間の寄生特徴よりも顕著である。したがって、寄生特徴は、電源 2 0 2 の負極端子とショットキーダイオード 3 4 2 およびコンデンサ 3 6 2 のそれぞれとの間で直列に接続される、寄生抵抗 4 5 2 および寄生インダクタ 4 5 4 を使用してモデル化される。ショットキーダイオード 3 4 4 およびコンデンサ 3 6 4 は、電源 2 0 2 の正極端子よりも I G F E T 3 2 4 の近くに物理的に位置する。電源 2 0 2 の正極端子とショットキーダイオード 3 4 4 およびコンデンサ 3 6 4 のそれぞれとの間の寄生特徴は、 I G F E T 3 2 4 とショットキーダイオード 3 4 4 およびコンデンサ 3 6 4 のそれぞれとの間の寄生特徴よりも顕著である。したがって、寄生特徴は、電源 2 0 2 の正極端子とショットキーダイオード 3 4 4 およびコンデンサ 3 6 4 のそれぞれとの間で直列に接続される、寄生抵抗 4 7 2 および寄生インダクタ 4 7 4 を使用してモデル化される。

10

### 【 0 0 3 3 】

モデル化する目的で、図 1 および図 4 の寄生抵抗は、 1 m 未満の値を割り当てることができ、図 1 および図 4 の寄生インダクタは、 1 n H 未満の値を割り当てることができる。インダクタンスは比較的低いが、図 1 を含む本明細書で説明される回路は、約 1 M H z 程度の周波数で動作するものであり、メモリ等のデジタル論理回路で使用されるトランジスタで一般的に見られる電流よりも 1 0 0 0 倍を超えて大きい、顕著な電流を伴う。電圧とインダクタンスとの間の関係は、  $V = L \times (d i / d t)$  であり、したがって、非常に大きい  $d i / d t$  の値は、図 1 の回路に関して分かるように、リングを生じさせる可能性がある。

20

### 【 0 0 3 4 】

本明細書で説明される回路は、ラップトップコンピュータ、ネットブック、テーブルパソコン等のモバイル電子デバイスのため、高周波電圧調整器として使用することができる。限定的でない実施形態において、電源は、 1 2 V D C の電池とすることができます。モバイル電子デバイスの通常動作中に、電池は、充電器に接続することができ、電源の端子間の電圧は、 1 9 V 程度の高さに到達する可能性がある。したがって、回路は、そのような電圧に耐えることが必要であり得る。

30

### 【 0 0 3 5 】

様々な態様および実施形態が可能である。そうした態様および実施形態のいくつかは、下で説明される。本明細書を読んだ後に、当業者は、そうした態様および実施形態が、単なる実例に過ぎず、本発明の範囲を限定するものではないことを認識するであろう。実施形態は、下に列記される付記の任意の 1 つ以上に従い得る。

### 【 0 0 3 6 】

付記 1 . 回路は、第 1 の通電電極および第 2 の通電電極を有する、第 1 のスイッチング素子と、第 1 の通電電極および第 2 の通電電極を有する、第 2 のスイッチング素子であつて、第 2 のスイッチング素子の第 1 の通電電極は、第 1 のスイッチング素子の第 2 の通電電極に結合される、第 2 のスイッチング素子とを含むことができる。回路はさらに、第 1 の整流素子と、第 2 の整流素子とを含むことができ、それぞれがアノードおよびカソードを有する。第 1 の整流素子のアノードは、第 1 のスイッチング素子の第 2 の通電電極に結合することができ、かつ第 1 の整流素子のカソードは、第 1 のスイッチング素子の第 1 の通電電極に結合することができる。第 2 の整流素子のアノードは、第 2 のスイッチング素子の第 2 の通電電極に結合することができ、かつ第 2 の整流素子のカソードは、第 2 のスイッチング素子の第 1 の通電電極に結合することができる。回路はなおさらに、第 1 の端子および第 2 の端子を有する、第 1 の電荷蓄積素子を含むことができ、第 1 の電荷蓄積素子の第 1 の端子は、第 1 の整流素子のカソードに結合され、かつ第 1 の電荷蓄積素子の第 2 の端子は、第 2 のスイッチング素子の第 2 の通電電極に結合される。

40

### 【 0 0 3 7 】

付記 2 . 第 1 の端子および第 2 の端子を有する、第 2 の電荷蓄積素子をさらに含み、第

50

2 の電荷蓄積素子の第 1 の端子は、第 1 のスイッチング素子の第 1 の通電電極に結合され、第 2 の電荷蓄積素子の第 2 の端子は、第 2 の整流素子のアノードに結合される、付記 1 に記載の回路。

**【 0 0 3 8 】**

付記 3 . 第 1 の電荷蓄積素子、第 2 の電荷蓄積素子、または第 1 および第 2 の電荷蓄積素子のそれぞれは、コンデンサを含む、付記 2 に記載の回路。

**【 0 0 3 9 】**

付記 4 . 第 1 の電荷蓄積素子、第 2 の電荷蓄積素子、または第 1 および第 2 の電荷蓄積素子のそれぞれは、少なくとも約 80 pF の静電容量を有する、付記 3 に記載の回路。

**【 0 0 4 0 】**

付記 5 . 第 1 の電荷蓄積素子、第 2 の電荷蓄積素子、または第 1 および第 2 の電荷蓄積素子のそれぞれは、約 1.5 nF ~ 約 40 nF の範囲の静電容量を有する、付記 3 に記載の回路。

**【 0 0 4 1 】**

付記 6 . 第 1 の電荷蓄積素子、第 2 の電荷蓄積素子、または第 1 および第 2 の電荷蓄積素子のそれぞれは、特定の静電容量を有し、第 1 のスイッチング素子、第 2 のスイッチング素子、または第 1 および第 2 のスイッチング素子のそれぞれは、その対応する第 1 および第 2 の通電電極間に静電容量を有し、特定の静電容量と、その対応する第 1 および第 2 の通電電極間の静電容量との比率は、少なくとも 1.5 : 1 である、付記 3 に記載の回路。

。

**【 0 0 4 2 】**

付記 7 . 第 1 の整流素子、第 2 の整流素子、または第 1 および第 2 の整流素子のそれぞれは、ショットキーダイオードまたはpn接合ダイオードを含む、付記 1 に記載の回路。

**【 0 0 4 3 】**

付記 8 . 第 1 の整流素子、第 2 の整流素子、または第 1 および第 2 の整流素子のそれぞれは、並列に電気的に接続されるショットキーダイオードおよびpn接合ダイオードを含む、付記 1 に記載の回路。

**【 0 0 4 4 】**

付記 9 . 第 1 の整流素子は、第 1 のスイッチング素子のドレイン - ソース間絶縁破壊電圧の約 2.0 倍以下である絶縁破壊電圧を有し、第 2 の整流素子は、第 2 のスイッチング素子のドレイン - ソース間絶縁破壊電圧の約 2.0 倍以下である絶縁破壊電圧を有する、付記 8 に記載の回路。

。

**【 0 0 4 5 】**

付記 10 . 第 1 のスイッチング素子は、ゲートを含む、絶縁ゲート型電界効果トランジスタであり、第 1 のスイッチング素子の第 1 の通電電極は、ドレインであり、第 1 のトランジスタの第 2 の通電電極は、ソースであり、第 2 のスイッチング素子は、ゲートを含む、別の絶縁ゲート型電界効果トランジスタであり、第 2 のスイッチング素子の第 1 の通電電極は、ドレインであり、第 2 のスイッチング素子の第 2 の通電電極は、ソースである、付記 1 に記載の回路。

**【 0 0 4 6 】**

付記 11 . 回路は、電圧調整器のスイッチング回路である、付記 1 に記載の回路。

**【 0 0 4 7 】**

付記 12 . 回路は、第 1 の通電電極および第 2 の通電電極を有する、ハイサイドトランジスタと、第 1 の通電電極および第 2 の通電電極を有する、ローサイドトランジスタとを含むことができ、ローサイドトランジスタの第 1 の通電電極は、ハイサイドトランジスタの第 2 の通電電極に結合される。回路はさらに、アノードおよびカソードを有する、整流素子をさらに含むことができ、整流素子のアノードは、ハイサイドトランジスタの第 2 の通電電極に結合され、整流素子のカソードは、ハイサイドトランジスタの第 1 の通電電極に結合される。回路はなおさらに、第 1 の端子および第 2 の端子を有する、電荷蓄積素子を含み、電荷蓄積素子の第 1 の端子は、ハイサイドトランジスタの第 1 の通電電極に結合

10

20

30

40

50

され、電荷蓄積素子の第2の端子は、ローサイドトランジスタの第2の通電電極に結合される。

**【0048】**

付記13. 電荷蓄積素子は、コンデンサを含む、付記12に記載の回路。

**【0049】**

付記14. 電荷蓄積素子は、静電容量を有し、ハイサイドトランジスタ、ローサイドトランジスタ、またはハイサイドおよびローサイドトランジスタのそれぞれは、その対応する第1および第2の通電電極間に静電容量を有し、静電容量と、その対応する第1および第2の通電電極間の静電容量との比率は、少なくとも1.5:1である、付記13に記載の回路。

10

**【0050】**

付記15. 整流素子は、並列に電気的に接続されるショットキーダイオードおよびpnダイオードを含む、付記12に記載の回路。

**【0051】**

付記16. 整流素子は、ハイサイドトランジスタのドレイン-ソース間絶縁破壊電圧の約2.0倍以下である絶縁破壊電圧を有する、付記15に記載の回路。

**【0052】**

付記17. スイッチング回路は、ハイサイドトランジスタおよびローサイドトランジスタを含むことができ、それぞれがソース、ゲート、およびドレインを有する。ハイサイドトランジスタのドレインは、第1の電力端子に電気的に接続することができ、ハイサイドトランジスタのゲートは、スイッチング回路の第1の入力に電気的に接続することができ、ハイサイドトランジスタのソースは、スイッチング回路の出力端子に電気的に接続することができる。ローサイドトランジスタのドレインは、出力端子に電気的に接続することができ、ローサイドトランジスタのゲートは、スイッチング回路の第2の入力に電気的に接続することができ、ローサイドトランジスタのソースは、第2の電力端子に電気的に接続することができる。スイッチング回路はさらに、第1のショットキーダイオードと、第2のショットキーダイオードとを含むことができ、それぞれがアノードおよびカソードを有する。第1のショットキーダイオードのアノードは、出力端子に電気的に接続することができ、第1のショットキーダイオードのカソードは、第1の電力端子に電気的に接続することができ、第2のショットキーダイオードのアノードは、第2の電力端子に電気的に接続することができ、ショットキーダイオードのカソードは、出力端子に電気的に接続することができる。スイッチング回路はなおさらに、第1のコンデンサと、第2のコンデンサとを含むことができ、それぞれが第1の端子および第2の端子を有する。第1のコンデンサの第1の端子は、第1の電力端子に電気的に接続することができ、第1のコンデンサの第2の端子は、第2の電力端子に電気的に接続することができ、第2のコンデンサの第1の端子は、第1の電力端子に電気的に接続することができ、第2のコンデンサの第2の端子は、第2の電力端子に電気的に接続することができる。

20

30

**【0053】**

付記18. 第1および第2のコンデンサのそれぞれは、約1.5nF～約40nFの範囲の静電容量を有する、付記17に記載の回路。

40

**【0054】**

付記19. 第1および第2のショットキーダイオードのそれぞれは、ローサイドおよびハイサイドトランジスタのそれぞれのドレイン-ソース間絶縁破壊電圧の約2.0倍以下の絶縁破壊電圧を有する、付記17に記載の回路。

実施例

**【0055】**

本明細書で説明される概念はさらに実施例において説明されるが、特許請求の範囲で説明される本発明の範囲を限定するものではない。実施例は、電力スイッチング回路の出力端子でのリングングを低減させるために、整流素子および電荷蓄積コンデンサの組み合わせを使用できることを実証する。

50

**【0056】**

図1および図4の回路は、図5のタイミング図のデータを生成するために使用される。以下の値は、図1および図4の寄生抵抗およびインダクタに割り当てられる。

**【0057】**

寄生抵抗 132、250  $\mu$  、

**【0058】**

寄生インダクタ 134、300 pH、

**【0059】**

寄生抵抗 432、250  $\mu$  、

**【0060】**

寄生インダクタ 434、300 pH、

10

**【0061】**

寄生抵抗 452、25 m 、

**【0062】**

寄生インダクタ 454、150 pH、

**【0063】**

寄生抵抗 472、50 m 、および

**【0064】**

寄生インダクタ 474、250 pH。

**【0065】**

図5は、電源がその端子の間で19Vであるときにスイッチング事象が起こった後の時間の関数として $V_{out}$ を提供する、出力端子上の電圧を比較する、タイミング図である。 $t = 0$ で、IGFET 122はオフであり、IGFET 124はオンである。出力端子上の電圧は、約0Vである。 $t =$ 約15ナノ秒で、IGFET 124をオフにし、次いで、IGFET 122をオンにする。 $t = 0$ でIGFET 322はオフでIGFET 324はオンである。出力端子上の電圧は、約0Vである。 $t =$ 約15ナノ秒で、IGFET 324をオフにし、次いで、IGFET 322をオンにする。理想的には、出力端子上の電圧は、いかなる電圧オーバーシュート、電圧アンダーシュート、またはリングングも伴わずに、0Vから19Vに即座に上昇する。図1および図4で図示される回路は理想的なものではなく、したがって、電圧オーバーシュート、電圧アンダーシュート、およびリングングが起こる。

20

**【0066】**

明らかに、図4の回路400は、図1の回路100と比較して、かなり良好な性能を提供する。コンデンサ362, 364は、急速に充電することができ、過剰な電荷を蓄積することを可能にすことができる、そして電圧オーバーシュートおよび電圧アンダーシュートの量を低減させることができる。ショットキーダイオード342, 344は、電圧オーバーシュートまたは電圧アンダーシュート中に、低インピーダンスの電流経路をコンデンサ362, 364に提供するのを補助する一方で、出力端子が、電源の正極端子および負極端子上の電圧に等しいか、またはそれらの間の電圧であるときに、電流を遮断する。図1の回路100のように、コンデンサ362, 364、ならびにショットキーダイオード342, 344を伴っていないければ、 $V_{out}$ は、34Vに達する可能性があり、それは、IGFET 124の30Vというドレイン-ソース間絶縁破壊電圧を超える。図4の回路400のように、コンデンサ362, 364、ならびにショットキーダイオード342, 344を伴ていれば、 $V_{out}$ は、26Vに達することになり、それは、IGFET 324の30Vというドレイン-ソース間絶縁破壊電圧未満である。さらに、図4の回路400の出力端子で見られるリングングは、少なくとも15ナノ秒でほぼなくなり、図1の回路100の出力端子の場合よりも早い。

30

**【0067】**

以下に示す構成は、本発明の実施態様の例を示す。

**【0068】**

40

50

回路において、

第1の通電電極および第2の通電電極を有する、第1のスイッチング素子と、

第1の通電電極および第2の通電電極を有する、第2のスイッチング素子であって、前記第2のスイッチング素子の前記第1の通電電極は、前記第1のスイッチング素子の前記第2の通電電極に結合される、第2のスイッチング素子と、

アノードおよびカソードを有する、第1の整流素子であって、前記第1の整流素子の前記アノードは、前記第1のスイッチング素子の前記第2の通電電極に結合され、前記第1の整流素子の前記カソードは、前記第1のスイッチング素子の前記第1の通電電極に結合される、第1の整流素子と、

アノードおよびカソードを有する、第2の整流素子であって、前記第2の整流素子の前記アノードは、前記第2のスイッチング素子の前記第2の通電電極に結合され、前記第2の整流素子の前記カソードは、前記第2のスイッチング素子の前記第1の通電電極に結合される、第2の整流素子と、

第1の端子および第2の端子を有する、第1の電荷蓄積素子であって、前記第1の電荷蓄積素子の前記第1の端子は、前記第1の整流素子の前記カソードに結合され、前記第1の電荷蓄積素子の前記第2の端子は、前記第2のスイッチング素子の前記第2の通電電極に結合される、第1の電荷蓄積素子と、

を備えることを特徴とする回路（米国特許出願（13 / 794,038）の出願時の請求項1に対応、以下同様）。

#### 【0069】

第1の端子および第2の端子を有する、第2の電荷蓄積素子をさらに備え、前記第2の電荷蓄積素子の前記第1の端子は、前記第1のスイッチング素子の前記第1の通電電極に結合され、前記第2の電荷蓄積素子の前記第2の端子は、前記第2の整流素子の前記アノードに結合されることを特徴とする、段落0068に記載された回路（請求項2に対応）。

#### 【0070】

前記第1の電荷蓄積素子、前記第2の電荷蓄積素子、または前記第1および第2の電荷蓄積素子のそれぞれは、コンデンサを含む、段落0069に記載された回路（請求項3に対応）。

#### 【0071】

前記第1の電荷蓄積素子、前記第2の電荷蓄積素子、または前記第1および第2の電荷蓄積素子のそれぞれは、少なくとも約80pFの静電容量を有する、段落0070に記載された回路（請求項4に対応）。

#### 【0072】

前記第1の電荷蓄積素子、前記第2の電荷蓄積素子、または前記第1および第2の電荷蓄積素子のそれぞれは、約1.5nF～約40nFの範囲の静電容量を有する、段落0070に記載された回路（請求項5に対応）。

#### 【0073】

前記第1の電荷蓄積素子、前記第2の電荷蓄積素子、または前記第1および第2の電荷蓄積素子のそれぞれは、特定の静電容量を有し、前記第1のスイッチング素子、前記第2のスイッチング素子、または前記第1および第2のスイッチング素子のそれぞれは、その対応する第1および第2の通電電極間に静電容量を有し、前記特定の静電容量と、前記その対応する第1および第2の通電電極間の特定の静電容量との比率は、少なくとも1.5:1である、段落0070に記載された回路（請求項6に対応）。

#### 【0074】

前記第1の整流素子、前記第2の整流素子、または前記第1および第2の整流素子のそれぞれは、ショットキーダイオードまたはpn接合ダイオードを含む、段落0068に記載された回路（請求項7に対応）。

#### 【0075】

前記第1の整流素子、前記第2の整流素子、または前記第1および第2の整流素子の回

10

20

30

40

50

路のそれぞれは、並列に電気的に接続されるショットキーダイオードおよびp n接合ダイオードを含む、段落0068に記載された回路（請求項8に対応）。

#### 【0076】

前記第1の整流素子は、前記第1のスイッチング素子のドレイン-ソース間絶縁破壊電圧の約2.0倍以下である絶縁破壊電圧を有し、

前記第2の整流素子は、前記第2のスイッチング素子のドレイン-ソース間絶縁破壊電圧の約2.0倍以下である絶縁破壊電圧を有する、段落0075に記載された回路（請求項9に対応）。

#### 【0077】

前記第1のスイッチング素子は、ゲートを含む、絶縁ゲート型電界効果トランジスタであり、前記第1のスイッチング素子の前記第1の通電電極は、ドレインであり、前記第1のトランジスタの前記第2の通電電極は、ソースであり、10

前記第2のスイッチング素子は、ゲートを含む、別の絶縁ゲート型電界効果トランジスタであり、前記第2のスイッチング素子の前記第1の通電電極は、ドレインであり、前記第2のスイッチング素子の前記第2の通電電極は、ソースである、段落0068に記載された回路（請求項10に対応）。

#### 【0078】

前記回路は、電圧調整器のスイッチング回路である、段落0068に記載された回路（請求項11に対応）。

#### 【0079】

回路において、20

第1の通電電極および第2の通電電極を有する、ハイサイドトランジスタと、

第1の通電電極および第2の通電電極を有する、ローサイドトランジスタであって、前記ローサイドトランジスタの前記第1の通電電極は、前記ハイサイドトランジスタの前記第2の通電電極に結合される、ローサイドトランジスタと、

アノードおよびカソードを有する整流素子であって、前記整流素子の前記アノードは、前記ハイサイドトランジスタの前記第2の通電電極に結合され、前記整流素子の前記カソードは、前記ハイサイドトランジスタの前記第1の通電電極に結合される、整流素子と、

第1の端子および第2の端子を有する、電荷蓄積素子であって、前記電荷蓄積素子の前記第1の端子は、前記ハイサイドトランジスタの前記第1の通電電極に結合され、前記電荷蓄積素子の前記第2の端子は、前記ローサイドトランジスタの前記第2の通電電極に結合される、電荷蓄積素子と、30

を備える、回路（請求項12に対応）。

#### 【0080】

前記電荷蓄積素子は、コンデンサを含む、段落0079に記載された回路（請求項13に対応）。

#### 【0081】

前記電荷蓄積素子は、静電容量を有し、前記ハイサイドトランジスタ、前記ローサイドトランジスタ、または前記ハイサイドおよびローサイドトランジスタのそれぞれは、その対応する第1および第2の通電電極間に静電容量を有し、前記静電容量と、前記その対応する第1および第2の通電電極間の静電容量との比率は、少なくとも1.5:1である、段落0080に記載された回路（請求項14に対応）。40

#### 【0082】

前記整流素子は、並列に電気的に接続されるショットキーダイオードおよびp n接合ダイオードを含む、段落0079に記載された回路（請求項15に対応）。

#### 【0083】

前記整流素子は、前記ハイサイドトランジスタのドレイン-ソース間絶縁破壊電圧の約2.0倍以下である絶縁破壊電圧を有する、段落0082に記載された回路（請求項16に対応）。

#### 【0084】

10

20

30

40

50

スイッチング回路において、

ソース、ゲート、およびドレインを有する、ハイサイドトランジスタであって、

前記ハイサイドトランジスタの前記ドレインは、第1の電力端子に電気的に接続され、

前記ハイサイドトランジスタの前記ゲートは、前記スイッチング回路の第1の入力に電気的に接続され、

前記ハイサイドトランジスタの前記ソースは、前記スイッチング回路の出力端子に電気的に接続される、ハイサイドトランジスタと、

ソース、ゲート、およびドレインを有する、ローサイドトランジスタであって、

前記ローサイドトランジスタの前記ドレインは、前記出力端子に電気的に接続され、

10

前記ローサイドトランジスタの前記ゲートは、前記スイッチング回路の第2の入力に電気的に接続され、

前記ローサイドトランジスタの前記ソースは、第2の電力端子に電気的に接続される、ローサイドトランジスタと、

アノードおよびカソードを有する、第1のショットキーダイオードであって、前記第1のショットキーダイオードの前記アノードは、前記出力端子に電気的に接続され、前記第1のショットキーダイオードの前記カソードは、前記第1の電力端子に電気的に接続される、第1のショットキーダイオードと、

アノードおよびカソードを有する、第2のショットキーダイオードであって、前記第2のショットキーダイオードの前記アノードは、前記第2の電力端子に電気的に接続され、前記ショットキーダイオードの前記カソードは、前記出力端子に電気的に接続される、第2のショットキーダイオードと、

第1の端子および第2の端子を有する、第1のコンデンサであって、前記第1のコンデンサの前記第1の端子は、前記第1の電力端子に電気的に接続され、前記第1のコンデンサの前記第2の端子は、前記第2の電力端子に電気的に接続される、第1のコンデンサと、

第1の端子および第2の端子を有する、第2のコンデンサであって、前記第2のコンデンサの前記第1の端子は、前記第1の電力端子に電気的に接続され、前記第2のコンデンサの前記第2の端子は、前記第2の電力端子に電気的に接続される、第2のコンデンサと、

を備える、スイッチング回路（請求項17に対応）。

#### 【0085】

前記第1および第2のコンデンサのそれぞれは、約1.5nF～約40nFの範囲の静電容量を有する、段落0084に記載されたスイッチング回路（請求項18に対応）。

#### 【0086】

前記第1および第2のショットキーダイオードのそれぞれは、前記ローサイドおよびハイサイドトランジスタのそれぞれのドレイン-ソース間絶縁破壊電圧の約2.0倍以下の絶縁破壊電圧を有する、段落0084に記載されたスイッチング回路（請求項19に対応）。

#### 【0087】

概要または実施例において上で説明される行為の全てが必要とされるわけではなく、特定の行為の一部が必要とされない場合があること、また、1つ以上のさらなる行為が、上で説明した行為に加えて行われ得ることに留意されたい。さらに、行為が列記される順序は、必ずしもそれらが行われる順序であるとは限らない。

#### 【0088】

利益、他の長所、および問題点に対する解決策を特定の実施形態に関して上で説明してきた。しかしながら、利益、長所、問題点の解決策、およびあらゆる利益、長所、または解決策を生じさせ得る、あるいはより明白にさせ得るあらゆる特徴は、特許請求の範囲のいずれかまたは全ての重要な、必要な、または必須の特徴として解釈されるべきではない。

50

## 【0089】

本明細書で説明される実施形態の仕様および具体例は、種々の実施形態の構造の一般的な理解を提供することを意図する。本仕様および具体例は、本明細書で説明される構造または方法を使用する装置およびシステムの要素および特徴の全ての網羅的かつ包括的な説明としての役割を果たすことを意図しない。特定の特徴は、明確にするために、別個の実施形態の状況において本明細書で説明されており、また、单一の実施形態において組み合わせて提供され得る。逆に、簡潔にするために、1つの実施形態の状況において説明される種々の特徴はまた、別々に提供されるか、またはあらゆる副次的な組み合わせでも提供され得る。さらに、範囲で提示される値への言及は、その範囲内のあらゆる値を含む。本明細書を読み終わった後にだけ、多くの他の実施形態が当業者に明らかになり得る。故に、本開示は、限定的ではなく例示的なものとみなされるべきである。

10

## 【符号の説明】

## 【0090】

200 回路

202 電源

222, 224 スイッチング素子

242, 244 整流素子

262, 264 電荷蓄積素子

322, 324 nチャネルIGFET

342, 344 ショットキーダイオード

20

362, 364 コンデンサ

474 寄生インダクタ

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 キャロル・キャスティール

アメリカ合衆国 アリゾナ州 85249 チャンドラー イースト・チェリーウッド・プレイス

789

審査官 栗栖 正和

(56)参考文献 國際公開第2012/073571(WO,A1)

特開2011-250589(JP,A)

特開2009-195054(JP,A)

特開2012-156548(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/08

H02M 3/155

H03K 17/16

H03K 17/687