【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成28年4月14日(2016.4.14)

【公開番号】特開2015-135917(P2015-135917A)

【公開日】平成27年7月27日(2015.7.27)

【年通号数】公開・登録公報2015-047

【出願番号】特願2014-7265(P2014-7265)

【国際特許分類】

H 01 L 49/00 (2006.01)

H 01 L 27/105 (2006.01)

H 01 L 21/8246 (2006.01)

H 01 L 45/00 (2006.01)

【F I】

H 01 L 49/00 Z

H 01 L 27/10 4 4 8

H 01 L 27/10 4 4 7

H 01 L 45/00 A

H 01 L 45/00 Z

【手続補正書】

【提出日】平成28年2月24日(2016.2.24)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1電極および前記第1電極に対向配置された第2電極と、前記第1電極と前記第2電極との間に設けられたスイッチ層とを有し、

前記スイッチ層は、

カルコゲン元素を含む第1層と、

高抵抗材料を含む第2層と

を備えたスイッチ素子。

【請求項2】

前記第2層は前記第1層の少なくとも一方の面に接して設けられている、請求項1に記載のスイッチ素子。

【請求項3】

前記第1層は酸素(O)、硫黄(S)、セレン(Se)およびテルル(Te)のうちの少なくとも1種を含んでいる、請求項1に記載のスイッチ素子。

【請求項4】

前記第1層はさらに、ゲルマニウム(Ge)、アンチモン(Sb)、ケイ素(Si)、ヒ素(As)のうちの少なくとも1種を含んでいる、請求項3に記載のスイッチ素子。

【請求項5】

前記第2層は金属元素または非金属元素の酸化物あるいは窒化物を含む、請求項1に記載のスイッチ素子。

【請求項6】

前記金属元素はアルミニウム(Al)、ガリウム(Ga)、マグネシウム(Mg)、ケイ素(Si)、ハフニウム(Hf)および希土類元素のうちの少なくとも1種である、請

求項 5 に記載のスイッチ素子。

【請求項 7】

前記第 1 層は、印加電圧を所定の閾値電圧以上とすることにより低抵抗状態に、該所定の閾値電圧未満に減少させることにより高抵抗状態に変化する、請求項 1 に記載のスイッチ素子。

【請求項 8】

前記第 2 層は層内に伝導バスを有する、請求項 1 に記載のスイッチ素子。

【請求項 9】

前記第 2 層の抵抗値は前記第 1 層よりも高い、請求項 1 に記載のスイッチ素子。

【請求項 10】

記憶素子および該記憶素子に接続されたスイッチ素子を含むメモリセルを複数備え、前記スイッチ素子は、

第 1 電極および前記第 1 電極に対向配置された第 2 電極と、前記第 1 電極と前記第 2 電極との間に設けられたスイッチ層とを有し、

前記スイッチ層は、

カルコゲン元素を含む第 1 層と、

高抵抗材料を含む第 2 層と

を備えた記憶装置。

【請求項 11】

前記記憶素子は前記スイッチ素子の前記第 1 電極および前記第 2 電極間に記憶層を有する、請求項 10 に記載の記憶装置。

【請求項 12】

前記記憶層はテルル (Te)、硫黄 (S) およびセレン (Se) から選ばれる少なくとも 1 種のカルコゲン元素を含むイオン源層と、抵抗変化層とを含む、請求項 11 に記載の記憶装置。

【請求項 13】

前記記憶層および前記スイッチ層は前記第 1 電極と前記第 2 電極との間に第 3 電極を介して積層されている、請求項 11 に記載の記憶装置。

【請求項 14】

前記記憶層および前記スイッチ層は前記第 2 層を介して積層されている、請求項 12 に記載の記憶装置。

【請求項 15】

前記記憶層および前記スイッチ層は前記抵抗変化層を介して積層されている、請求項 12 に記載の記憶装置。

【請求項 16】

前記スイッチ層の前記第 2 層は、前記記憶層の前記抵抗変化層を兼ねている、請求項 12 に記載の記憶装置。

【請求項 17】

複数の行ラインおよび複数の列ラインを有し、前記複数の行ラインと複数の列ラインとの各交差領域付近に前記メモリセルが配置されている、請求項 10 に記載の記憶装置。

【請求項 18】

前記記憶層は、遷移金属酸化物からなる抵抗変化層、相変化型メモリ層、磁気抵抗変化型メモリ層のいずれかである、請求項 11 に記載の記憶装置。

【請求項 19】

前記スイッチ素子は、オボニック閾値スイッチ素子である、請求項 10 に記載の記憶装置。

【請求項 20】

前記記憶素子は、書き込み閾値電圧が 1.5 V 以上である、請求項 10 に記載の記憶装置。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0015

【補正方法】変更

【補正の内容】

【0015】

【図1】本開示の一実施の形態に係るスイッチ素子の構成の一例を表す断面図である。

【図2】本開示の比較例としてのスイッチ素子の断面図である。

【図3】図1に示したスイッチ素子のIV特性を表す図である。

【図4A】図3に示したIV曲線の各領域におけるスイッチ素子の断面模式図である。

【図4B】同じく、図3に示したIV曲線の各領域におけるスイッチ素子の断面模式図である。

【図4C】同じく、図3に示したIV曲線の各領域におけるスイッチ素子の断面模式図である。

【図4D】同じく、図3に示したIV曲線の各領域におけるスイッチ素子の断面模式図である。

【図4E】同じく、図3に示したIV曲線の各領域におけるスイッチ素子の断面模式図である。

【図5】各フォーミング(A)～(D)条件におけるIV特性を表す図である。

【図6A】フォーミング条件(A)におけるスイッチ素子の断面模式図である。

【図6B】フォーミング条件(B)におけるスイッチ素子の断面模式図である。

【図6C】フォーミング条件(C)におけるスイッチ素子の断面模式図である。

【図6D】フォーミング条件(D)におけるスイッチ素子の断面模式図である。

【図7A】本開示の実施の形態に係るスイッチ素子の構成の他の例を表す断面図である。

【図7B】本開示の実施の形態に係るスイッチ素子の構成の他の例を表す断面図である。

【図8】図1に示したスイッチ素子を備えたメモリセルアレイの斜視図である。

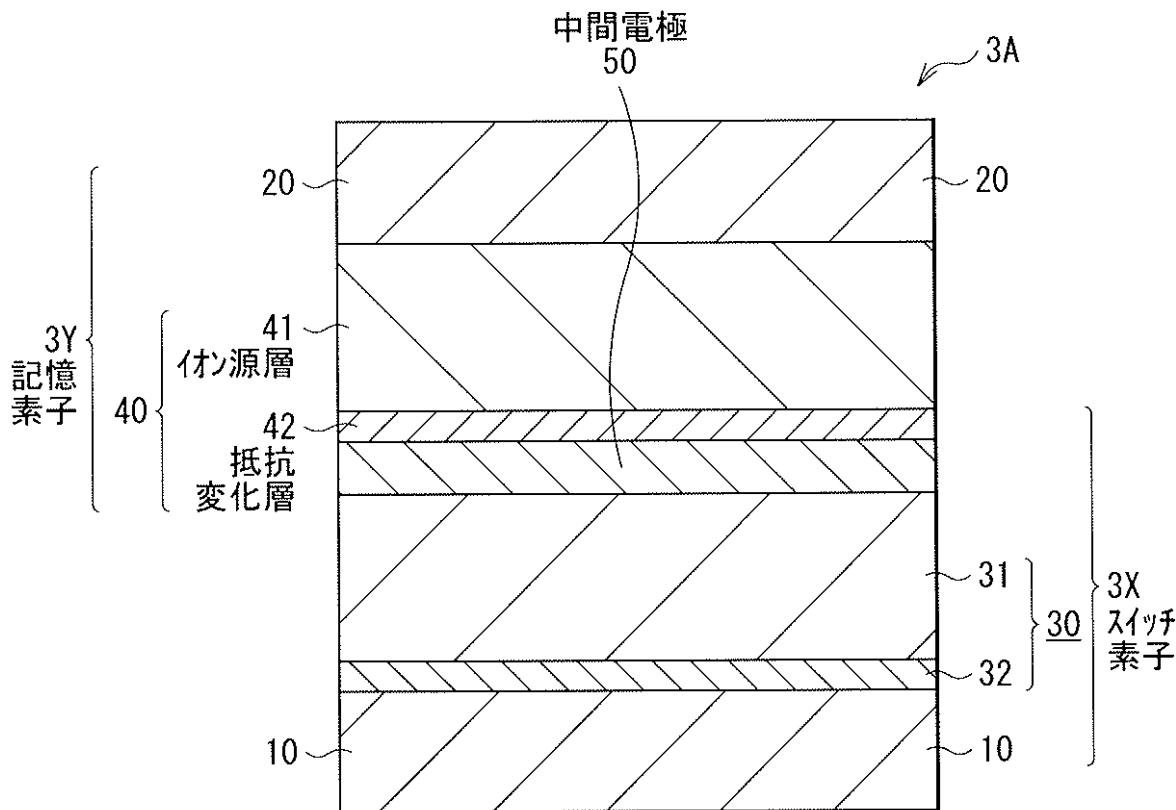

【図9A】図8に示したメモリセルの構成の一例を表す断面図である。

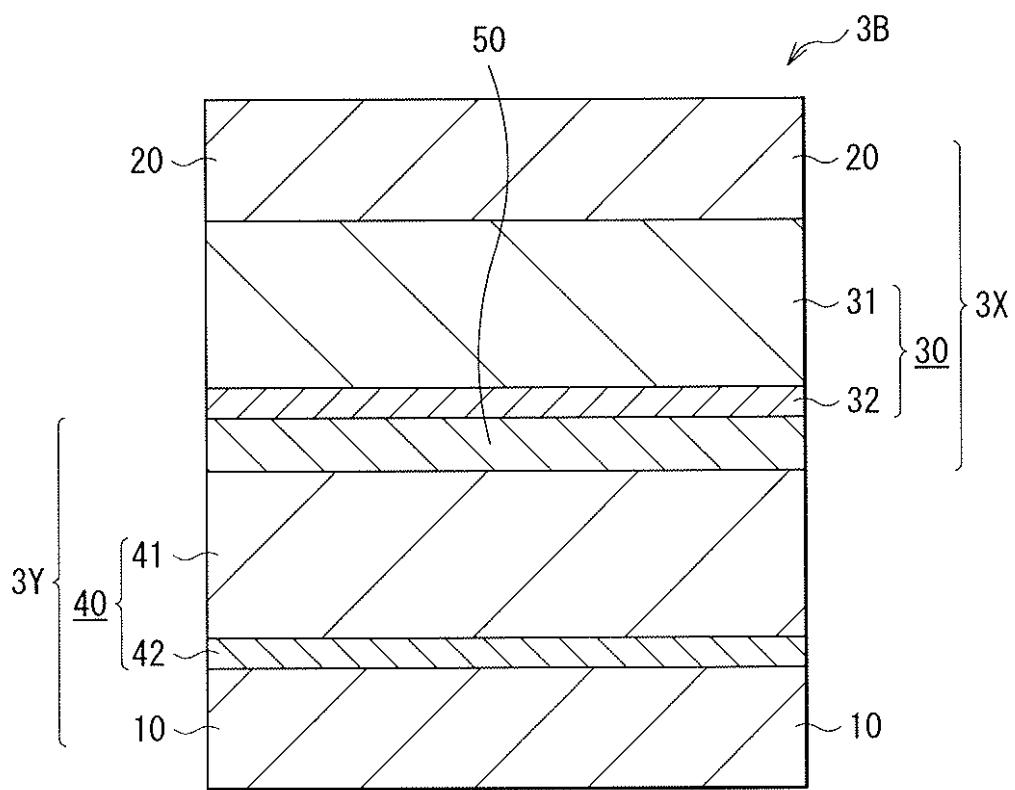

【図9B】図8に示したメモリセルの構成の他の例を表す断面図である。

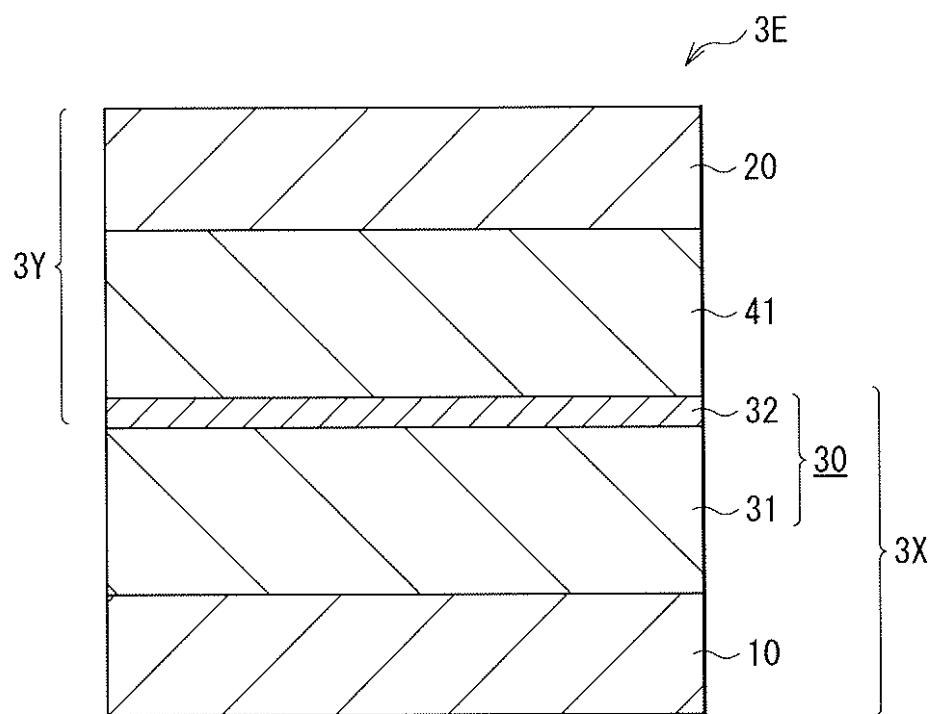

【図9C】図8に示したメモリセルの構成の他の例を表す断面図である。

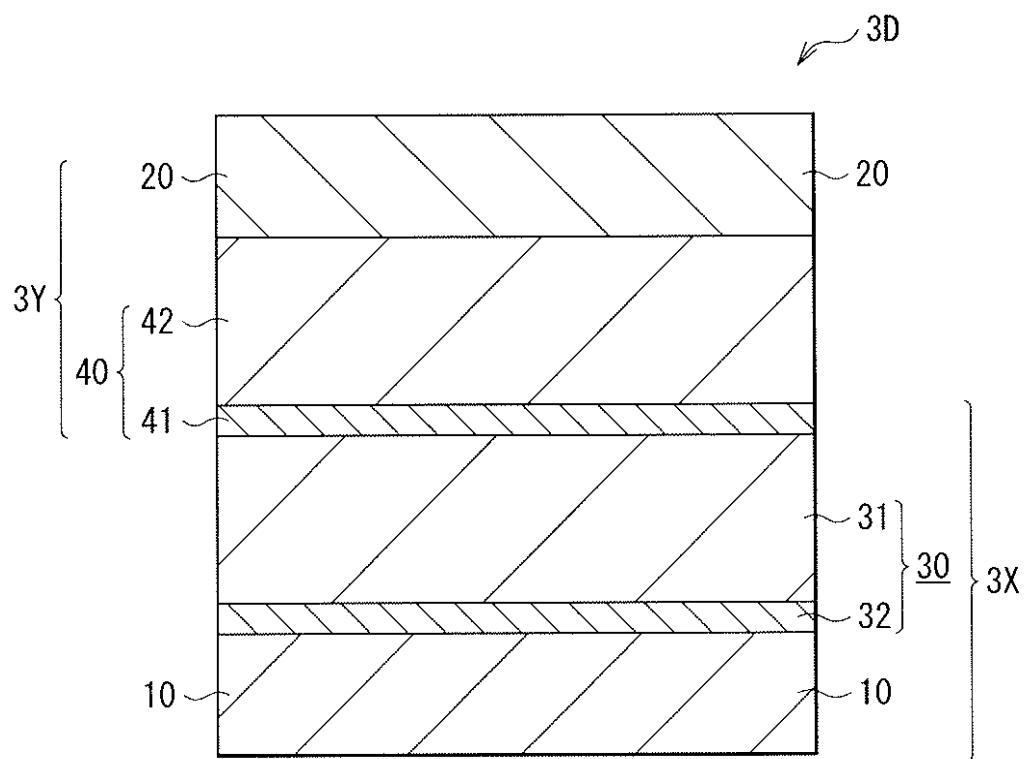

【図10A】図8に示したメモリセルの構成の他の例を表す断面図である。

【図10B】図8に示したメモリセルの構成の他の例を表す断面図である。

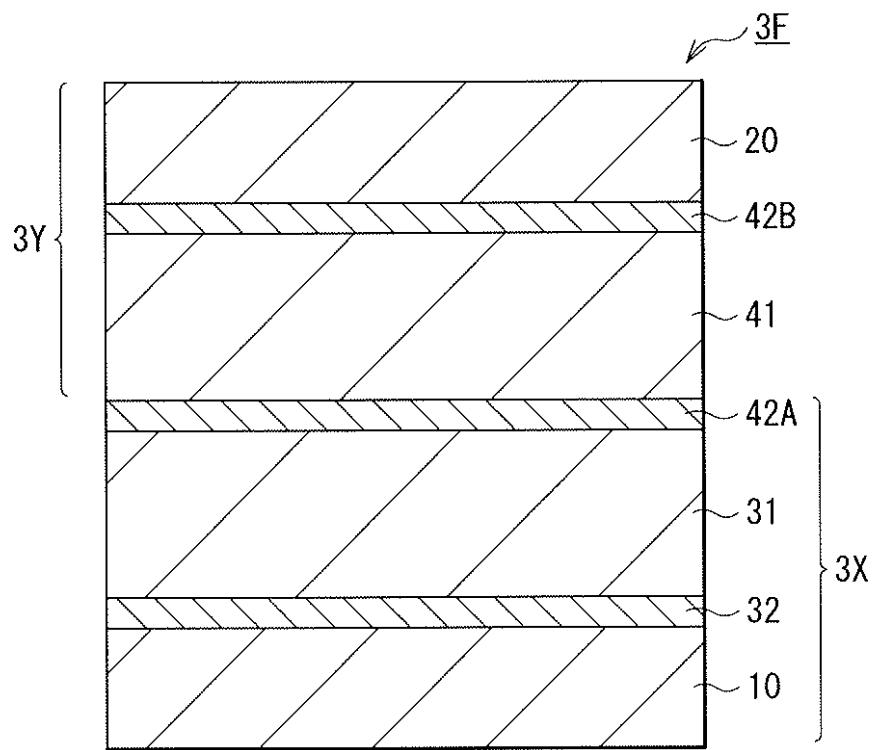

【図10C】図8に示したメモリセルの構成の他の例を表す断面図である。

【図11A】図8に示したメモリセルの書き込みおよび消去におけるIV特性を表す図である。

【図11B】図8に示したメモリセル(記憶素子)におけるIV特性を表す図である。

【図11C】図8に示したメモリセルにおけるIV特性を表す図である。

【図11D】図8に示したメモリセルにおけるIV特性を表す図である。

【図12】本開示の実験1におけるIV特性図である。

【図13A】本開示の実験2(サンプル3)におけるIV特性図である。

【図13B】同じく実験2(サンプル4)におけるIV特性図である。

【図13C】同じく実験2(サンプル5)におけるIV特性図である。

【図14】サンプル3～5のIV曲線をまとめた特性図である。

【図15】本開示の実験3におけるIV特性図である。

【図16A】実験3における最大電流とリーキ電流との関係を表す特性図である。

【図16B】実験3における最大電流とスイッチング閾値電圧との関係を表す特性図である。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正の内容】

**【0029】**

これは、スイッチ素子100を構成する下部電極110および上部電極120の電極面積がそのまま動作領域となるためであり、非選択（オフ）状態のリーク電流が大きいものが多く誤作動（誤書き込みや誤消去）を起こしやすくなる。また、リーク電流が小さいというお点で優れているものもあるが、スイッチング閾値電圧が1V以下と小さかった。このため、このスイッチ素子100が上記条件を満たすためには、スイッチ層130の膜厚を大きく（例えば、180nm程度）する必要があり、その場合には微細化することができなくなるという問題があった。

**【手続補正4】**

【補正対象書類名】明細書

【補正対象項目名】0033

【補正方法】変更

【補正の内容】

**【0033】**

以上のことから、上記スイッチ素子100のようにスイッチ層130（ここではOTS層31）を厚膜化することなく、オン状態における十分な電流密度を確保することができ、且つオフ状態における非選択素子および半選択素子へのリーク電流を抑えることが可能となる。即ち、オン／オフ比を増大させることができる。

**【手続補正5】**

【補正対象書類名】明細書

【補正対象項目名】0042

【補正方法】変更

【補正の内容】

**【0042】**

以上のように、本実施の形態では、スイッチ層30を構成するOTS層31に高抵抗層32を積層するようにしたので、スイッチ層30の動作領域が制限され、非選択あるいは半選択時（オフ状態）におけるリーク電流の発生を低減することが可能となる。また、スイッチング閾値電圧およびオン／オフ比が大きくなる。よって、高密度且つ大容量な記憶装置を提供することが可能となる。

**【手続補正6】**

【補正対象書類名】明細書

【補正対象項目名】0053

【補正方法】変更

【補正の内容】

**【0053】**

具体的には、記憶素子3Yでは、初期状態（高抵抗状態）の素子に対して「正方向」（例えば第1電極側を負電位、第2電極側を正電位）の電圧または電流パルスが印加されると、イオン源層に含まれる金属元素（例えば、遷移金属元素）がイオン化して記憶層中（例えば、抵抗変化層中）に拡散、あるいは酸素イオンが移動することによって抵抗変化層中に酸素欠陥が生成する。これにより記憶層内に酸化状態の低い低抵抗部（伝導パス）が形成され、抵抗変化層の抵抗が低くなる（記録状態）。この低抵抗な状態の素子に対して「負方向」（例えば第1電極側を正電位、第2電極側を負電位）へ電圧パルスが印加されると、抵抗変化層中の金属イオンがイオン源層中へ移動、あるいはイオン源層から酸素イオンが移動して伝導パス部分の酸素欠陥が減少する。これにより金属元素を含む伝導パスが消滅し、抵抗変化層の抵抗が高い状態となる（初期状態または消去状態）。なお、記憶層40を抵抗変化層42の単層で構成する場合には、正方向の電圧（または電流パルス）が印加されると、抵抗変化層42に印加される電界によって欠陥が生成され、負方向へ電圧パルスが印加されると、欠陥は抵抗変化層内の酸素イオンや窒素イオンの移動によって修復される。

**【手続補正7】**

【補正対象書類名】明細書

【補正対象項目名】0055

【補正方法】変更

【補正の内容】

【0055】

更に、メモリセル3は中間電極50を省略した構成としてもよい。この場合には、図10Aに示したメモリセル3Dのように、下部電極10側から高抵抗層32,OTS層31の順に設けられたスイッチ層30と、下部電極10側から抵抗変化層42、イオン源層41の順に設けられた記憶層40とを単純に積層させた構成としてもよい。なお、スイッチ層30とイオン源層40との積層順序は入れ替えて形成してもかまわない。また、上述した高抵抗層32における伝導バスの生成および消滅は、記憶素子3Yにおける抵抗変化層42と同様の動作であるため、高抵抗層32および抵抗変化層42を互いに共有することができる。このため、例えば図10Bに示したメモリセル3Eのように、スイッチ層30の高抵抗層32が記憶層40の抵抗変化層42を兼ねるように、高抵抗層32を間にOTS層31およびイオン源層41が配置される構成としてもよい。更に、例えば図10Cに示したメモリセル3Fのように、抵抗変化層42を2層設け（抵抗変化層42A,42B）、イオン源層41の下部電極10側および上部電極20側の両方に設け、スイッチ層30と積層して構成としてもよい。

【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0058

【補正方法】変更

【補正の内容】

【0058】

図11Aは、スイッチ素子3XのIV特性を表したものである。順バイアス（ここでは、書き込み電圧）を印加すると、スイッチ素子3Xは上述したように印加電圧の増加に伴って電流が上昇するが、ある閾値電圧（スイッチング閾値電圧）を超えるとオボニック閾値スイッチにより急激に電流が増大、あるいは抵抗が低くなりオン状態となる。この後、印加電圧を減少させていくと、スイッチ素子3Xの電極に流れる電流値は徐々に減少し、2回目以降の動作では、印加電圧の増加時および減少時共に近似した抵抗変化、具体的には、増加時と同等の電圧で急激に抵抗が上昇してオフ状態となる（B1）。即ち、スイッチ素子3Xの抵抗値は書き込み電圧の印加によって低抵抗状態となるが、印加電圧を閾値以下に下げると高抵抗状態に戻り、電圧印加時の抵抗値は維持されない。

【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0059

【補正方法】変更

【補正の内容】

【0059】

図11Bは、記憶素子3YのIV特性を表したものである。図11Bからわかるように、記憶素子3Yでは、印加電圧の増加に伴って電流値が上昇するが、ある閾値電圧において記憶層40の抵抗変化層42における伝導バス形成による書き込み動作が行われ、低抵抗状態へと変化する。即ち、記憶素子3Yの抵抗値は書き込み電圧の印加によって低抵抗状態となり、印加電圧停止後もその抵抗状態は維持される（B1）。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0060

【補正方法】変更

【補正の内容】

【0060】

図 11C は、メモリセル 3 の I-V 特性を表したものである。上記記憶素子 3Y とスイッチ素子 3X を組み合わせたメモリセル 3 の書き込み電圧の印加開始および停止における電流値のスイッチング挙動は、記憶素子 3Y (A1) およびスイッチ素子 3X (B1) を合わせたものとなる (C1)。例えば、V/2 バイアス方式のクロスポイントアレイの場合には、メモリセル 3 の C1 の I-V 曲線上で急激に抵抗変化する閾値よりも大きな電圧を読み出し電圧 (V<sub>read</sub>) を設定し、V<sub>read</sub>/2 は抵抗変化の閾値よりも小さい電圧となるように設定する。これにより、バイアス(オン)とV<sub>read</sub>/2 バイアス(オフ)との電流比で定義される選択比を大きくとることが可能となる。また、上記のように、メモリセル 3 の I-V 曲線 C1 はスイッチ素子 3X の I-V 曲線 B1 と記憶素子 3Y の I-V 曲線の合成であるので、スイッチ素子 3X のオボニック閾値スイッチの閾値前後の抵抗変化 (あるいは電流変化) が大きいほど選択比を大きくとることができる。これにより、本実施の形態におけるスイッチ素子 3X では大きなオン / オフ比を得ることが選択比の増大となって好ましいといえる。更に、選択比が大きければ大きいほど読み出しマージンが大きくなるため、誤読み出しそれぞれなくクロスポイントアレイサイズを大きくすることが可能となり、メモリセルアレイの更なる大容量化が可能となる。

#### 【手続補正 11】

【補正対象書類名】明細書

【補正対象項目名】0061

【補正方法】変更

【補正の内容】

#### 【0061】

これは、読み出し動作だけでなく、書き込み動作についても同様である。図 11D は、図 11C と同様にメモリセル 3 の I-V 特性を表したものである。上述したように、クロスポイントアレイでは、対象のメモリセルと同じビット線 BL あるいはワード線 WL に多数のビットが接続されている。このため、図 11D に示したように、V<sub>write</sub>/2 と I-V 曲線 C1 の点線の Set 状態の I-V ループの交点で示される、V<sub>write</sub>/2 にバイアスされた非選択時のリーク電流が大きいと非選択のメモリセルで誤書き込みを生じる虞がある。よって、書き込み動作では、記憶素子 3Y を書き込む際に必要な電流が得られる電圧に書き込み電圧 V<sub>write</sub> を設定したうえで、V<sub>write</sub>/2 にバイアスされた非選択のメモリセルが誤書き込みを生じない程度のリーク電流に抑える必要がある。V<sub>write</sub>/2 にバイアスされた非選択時のリーク電流が小さければ小さいほど大規模なクロスポイントアレイを誤書き込みなく動作させることができる。従って、書き込み動作時もスイッチ素子 3X の選択比を大きくすることが、メモリセルアレイの大容量化につながる。

#### 【手続補正 12】

【補正対象書類名】明細書

【補正対象項目名】0062

【補正方法】変更

【補正の内容】

#### 【0062】

一方、逆バイアス (ここでは消去電圧) を印加すると、スイッチ素子 3X の消去電圧印加における電流値の変化は、書き込み電圧を印加したサイト同様の挙動を示す (B2)。これに対して、記憶素子 3Y の消去電圧印加における電流値の変化は、消去閾値電圧以上の電圧印加によって、低抵抗状態から高抵抗状態へと変化する (A2)。図 11A ~ 11C に示したように、A2 および B2 の I-V 特性を合成すると消去バイアスでのメモリセルの I-V 特性 C2 が得られる。V/2 バイアス方式のクロスポイントアレイでは、通常の読み出しバイアスを書き込み側に設定するため、V<sub>reset</sub>/2 バイアスでのディスター ブ電流が問題となるが、これについても、正バイアスの場合と同様に、スイッチ素子 3X のオン / オフ比、即ち選択比が大きく、オフ時のリーク電流が小さいほどクロスポイントアレイの大規模化に有利となる。

#### 【手続補正 13】

【補正対象書類名】明細書

【補正対象項目名】0066

【補正方法】変更

【補正の内容】

【0066】

(実験1)

まず、TiNよりなる下部電極10を逆スパッタによってクリーニングしたのち、TiN上にSiO<sub>2</sub>膜を2nmの膜厚に形成して高抵抗層32とする。次に、OTS層31としてGeTe膜を40nmの膜厚で形成したのち、Wを30nmの膜厚で形成して上部電極20とした。続いて、フォトリソグラフィやドライエッチングなどの公知の技術を用いて素子サイズが100nmとなるように微細加工を行い、スイッチ素子1A(サンプル1)を作製した。また、比較例として、高抵抗層32を形成していないスイッチ素子100(サンプル2)を作製した。これらサンプル1およびサンプル2の印加電圧と各電極に流れる電流値との関係を測定し、そのIV特性を図12に示した。

【手続補正14】

【補正対象書類名】明細書

【補正対象項目名】0067

【補正方法】変更

【補正の内容】

【0067】

図12からわかるように、本実施の形態であるサンプル1では、サンプル2と比較して閾値電圧が増大した。また、オン／オフ比もサンプル2よりも大きくなっている。即ち、スイッチ素子1Aは閾値電圧の増加と抵抗変化比の増大とが同時に実現していることがわかる。

【手続補正15】

【補正対象書類名】明細書

【補正対象項目名】0070

【補正方法】変更

【補正の内容】

【0070】

図13A～図13Cからわかるように、スイッチ素子1A(サンプル3,4)およびスイッチ素子100(サンプル5)は、高抵抗層32の有無によらず、ある閾値電圧を境に急激に抵抗が低下して電流が増大するオボニック閾値スイッチが見られる。図14は、図13A～図13Cに示したサンプル3～5の正バイアスの印加電圧増加方向のIV曲線をまとめたものである。サンプル3,4を高抵抗層32を設けていないサンプル5と比較すると、サンプル3およびサンプル4は共にオフ状態(電圧0)におけるリーク電流が低減(ほぼ0)され、さらに閾値電圧が増大している。即ち、本開示のスイッチ素子1Aは書き込み閾値電圧の高い記憶素子(例えば、記憶素子3Y)に対応可能な良好な特性を有することがわかる。なお、サンプル3とサンプル4とを比較した場合には、SiO<sub>2</sub>を用いたサンプル3よりもSiNを用いたサンプル4の方が、閾値電圧が高くリーク電流が小さかった。これは、SiO<sub>2</sub>およびSiNの膜厚や成膜条件によって適宜制御することができる。

【手続補正16】

【補正対象書類名】明細書

【補正対象項目名】0072

【補正方法】変更

【補正の内容】

【0072】

(実験3)

次に、サンプル3を用いて最大印加電圧を6V一定とし、スイッチ素子1Aに直列に接

続されている抵抗値を変化（ $5\text{ k}\Omega$ ， $12.5\text{ k}\Omega$ ， $50\text{ k}\Omega$ ）させることにより最大電流値を変化させた。図15は各抵抗値における正バイアスのIV曲線を示したものである。スイッチ素子1Aに流れる最大電流値が変化することにより、リーク電流と閾値電圧が変化することがわかった。次に、これらの測定から求めたサンプル3に流す最大電流とリーク電流との関係および最大電流と閾値電圧との関係を図16A，図16Bに示した。なお、リーク電流の定義は正バイアス $0.5\text{ V}$ の電流とした。

## 【手続補正17】

【補正対象書類名】図面

【補正対象項目名】図9A

【補正方法】変更

【補正の内容】

【図9A】

## 【手続補正18】

【補正対象書類名】図面

【補正対象項目名】図9B

【補正方法】変更

【補正の内容】

【図 9 B】

【手続補正 1 9】

【補正対象書類名】図面

【補正対象項目名】図 10 A

【補正方法】変更

【補正の内容】

【図 10 A】

【手続補正 20】

【補正対象書類名】図面

【補正対象項目名】図 10 B

【補正方法】変更

【補正の内容】

【図 10B】

【手続補正 21】

【補正対象書類名】図面

【補正対象項目名】図 10C

【補正方法】変更

【補正の内容】

【図 10C】