(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4527345号

(P4527345)

(45) 発行日 平成22年8月18日(2010.8.18)

(24) 登録日 平成22年6月11日(2010.6.11)

|                   |                          |

|-------------------|--------------------------|

| (51) Int.Cl.      | F 1                      |

| <b>H04L 27/38</b> | (2006.01) HO 4 L 27/00 G |

| <b>H03G 3/20</b>  | (2006.01) HO 3 G 3/20 A  |

| <b>H03G 3/30</b>  | (2006.01) HO 3 G 3/30 B  |

| <b>H04B 1/16</b>  | (2006.01) HO 4 B 1/16 A  |

| <b>H04B 1/18</b>  | (2006.01) HO 4 B 1/18 C  |

請求項の数 22 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2001-570041 (P2001-570041)  |

| (86) (22) 出願日 | 平成12年10月6日 (2000.10.6)        |

| (65) 公表番号     | 特表2003-528542 (P2003-528542A) |

| (43) 公表日      | 平成15年9月24日 (2003.9.24)        |

| (86) 國際出願番号   | PCT/US2000/027616             |

| (87) 國際公開番号   | W02001/071999                 |

| (87) 國際公開日    | 平成13年9月27日 (2001.9.27)        |

| 審査請求日         | 平成19年9月10日 (2007.9.10)        |

| (31) 優先権主張番号  | 09/533,342                    |

| (32) 優先日      | 平成12年3月23日 (2000.3.23)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 591016172<br>アバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>ADVANCED MICRO DEVICES INCORPORATED<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンディベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・プレイス、メイル・ストップ<br>・68 (番地なし) |

| (74) 代理人  | 100064746<br>弁理士 深見 久郎                                                                                                                                                                         |

| (74) 代理人  | 100085132<br>弁理士 森田 俊雄                                                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】データネットワークにおいて複数の信号フォーマットのための入力利得を調整するための装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ネットワーク媒体を介して別のネットワーク送受信機から変調キャリア信号を受信するよう構成されたネットワーク受信機であって、

a) 複数の増幅器利得設定のうち1つに従い、受信された変調キャリア信号を増幅し、増幅されたキャリア信号を出力するための入力増幅器と、

b) 前記増幅されたキャリア信号に応答して包絡線信号を出力するよう構成された包絡線検波器と、

c) 前記包絡線信号に応答して第1の利得設定を選択するよう構成された第1の利得制御回路とを含み、前記第1の利得設定はパルス位置変調キャリア信号を受信するのに最適であり、前記ネットワーク受信機はさらに

d) 前記包絡線信号に応答して第2の利得制御設定を選択するよう構成された第2の利得制御回路とを含み、前記第2の利得設定は直交振幅変調信号を受信するのに最適であり、前記ネットワーク受信機はさらに

e) 前記包絡線信号がパルス位置変調キャリアを表わすのか、または振幅変調キャリアを表わすのかを判断し、前記増幅器利得設定をそれぞれ前記第1の利得設定に設定するか、または第2の利得設定に設定するかを判断するよう構成された、選択回路を含む、ネットワーク受信機。

## 【請求項 2】

前記増幅されたキャリア信号に応答してデジタルキャリア信号を発生するアナログ・デ

ジタル変換器をさらに含み、前記包絡線検波器は前記デジタルキャリア信号に応答する、請求項1に記載のネットワーク受信機。

【請求項3】

前記増幅されたキャリア信号に応答してデジタルIチャネルキャリア信号およびデジタルQチャネルキャリア信号を発生するヒルベルト変換器をさらに含み、前記包絡線検波器は、前記デジタルIチャネルキャリア信号および前記デジタルQチャネルキャリア信号に応答する、請求項2に記載のネットワーク受信機。

【請求項4】

前記選択回路は、前記包絡線信号の中の電力パルスの持続時間を検出するためのキャリアセンス回路を含む、請求項3に記載のネットワーク受信機。

10

【請求項5】

前記選択回路は、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間未満である場合に前記第1の利得設定を選択する、請求項4に記載のネットワーク受信機。

【請求項6】

前記選択回路は、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間よりも大きい場合に前記第2の利得設定を選択する、請求項5に記載のネットワーク受信機。

【請求項7】

前記包絡線信号は、前記Iチャネルキャリア信号の平方と、前記Qチャネルキャリア信号の平方との和の平方根を表わす、請求項6に記載のネットワーク受信機。

20

【請求項8】

前記第1の利得制御回路は複数の比較器を含み、各々の比較器は前記包絡線信号を複数の参照信号のうち1つと比較するよう構成され、前記第1の利得設定は、複数の利得設定の各々を反復的にテストする際に少なくとも1つの比較器の飽和を検出することにより決定される、請求項7に記載のネットワーク受信機。

【請求項9】

前記第2の利得制御回路は、前記包絡線信号を表わす対数信号を発生する対数ルックアップテーブルと、前記対数信号を参照信号と比較して差信号を発生する比較器と、前記差信号をループ利得定数で乗じて積を発生する乗算器と、前記積を積分して前記第2の利得設定を発生する積分器とを含む、請求項8に記載のネットワーク受信機。

30

【請求項10】

前記ループ利得定数は、検出された電力パルスの第1の部分のためには或る大きな値、検出された電力パルスの第2の部分のためにはより小さな値、および検出された電力パルスの残りの持続時間のためには0となるよう選択される、請求項9に記載のネットワーク受信機。

【請求項11】

ネットワーク媒体から変調キャリア信号を受信するよう構成された受信機において、増幅されたキャリア信号を発生する入力増幅器のための利得設定を決定する方法であって、

a) 前記増幅されたキャリア信号の電力を表わす前記増幅されたキャリア信号から包絡線信号を発生するステップと、

40

b) 前記包絡線信号に応答して第1の利得設定を決定するステップとを含み、前記第1の利得設定はパルス位置変調キャリア信号を受信するために選択され、前記方法はさらに

c) 前記包絡線信号に応答して第2の利得設定を決定するステップを含み、前記第2の利得設定は直交振幅変調キャリア信号を受信するために選択され、前記方法はさらに

d) 前記変調キャリア信号がパルス位置変調キャリアであるか、または直交振幅変調キャリアであるかを判断するステップと、

e) 前記変調キャリア信号がパルス位置変調キャリアであると判断された場合に前記入力増幅器の利得を前記第1の利得設定に設定し、前記変調キャリア信号が直交振幅変調

50

キャリアであると判断された場合に前記入力増幅器利得を前記第2の利得設定に設定するステップとを含む、方法。

【請求項12】

前記増幅されたキャリア信号をデジタルキャリア信号へと変換するステップをさらに含み、前記包絡線信号は前記デジタルキャリア信号から発生される、請求項11に記載の方法。

【請求項13】

前記デジタルキャリア信号からIチャネル信号およびQチャネル信号を発生するステップをさらに含み、前記包絡線信号は前記Iチャネル信号および前記Qチャネル信号から発生される、請求項12に記載の方法。

10

【請求項14】

前記入力増幅器の利得を設定する前記ステップは、前記包絡線信号の中の電力パルスの持続時間を検出するステップを含む、請求項13に記載の方法。

【請求項15】

電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間未満である場合に前記入力増幅器の利得は前記第1の利得設定に設定される、請求項14に記載の方法。

【請求項16】

電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間よりも大きい場合に前記入力増幅器の利得は前記第2の利得設定に設定される、請求項15に記載の方法。

20

【請求項17】

前記包絡線信号は、前記Iチャネル信号の平方と前記Qチャネル信号の平方との和の平方根を表わす、請求項16に記載の方法。

【請求項18】

前記第1の利得設定は、前記包絡線信号を複数の参照レベルと比較し、複数の利得設定の各々を、少なくとも1つの参照レベルで飽和が生じているかどうかに関し反復的にテストして前記第1の利得設定を決定することにより決定される、請求項17に記載の方法。

30

【請求項19】

前記第2の利得設定は、前記包絡線信号を、前記包絡線信号を表わす対数信号に変換し、前記対数信号を参照レベルと比較して差を求め、前記差をループ利得定数で乗じて積を求め、前記積を積分して前記第2の利得設定を決定することにより決定される、請求項18に記載の方法。

【請求項20】

前記ループ利得定数は、検出された電力パルスの第1の部分のためには或る大きな値、検出された電力パルスの第2の部分のためにはより小さな値、および検出された電力パルスの残りの持続時間のためには0となるよう選択される、請求項19に記載の方法。

【請求項21】

ネットワーク媒体を介して別のネットワーク送受信機から変調キャリア信号を受信するよう構成されたネットワーク受信機であって、

40

a) 複数の増幅器利得設定のうち1つに従い、受信された変調キャリア信号を増幅し、増幅されたキャリア信号を出力するための入力増幅器と、

b) 第1の変調方法に従って変調されたキャリア信号に基づき、第1の増幅器利得設定を与えるための第1の利得制御回路と、

c) 第2の変調方法に従って変調されたキャリア信号に基づき、第2の増幅器利得設定を与えるための第2の利得制御回路と、

d) 前記キャリア信号を分析し、前記キャリア信号が前記第1の変調方法に従って変調されたか、または前記第2の変調方法に従って変調されたかを自動的に識別し、利得制御信号を前記入力増幅器に与えて、選択回路によって識別される前記変調方法に基づき前

50

記第1の増幅器利得設定または前記第2の増幅器利得設定で前記キャリア信号を増幅するための、選択回路とを含み、前記選択回路は前記包絡線信号の中の電力パルスの持続時間を検出するための包絡線検波回路を含み、前記選択回路は、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間未満である場合に、前記第1の増幅器利得設定を前記入力増幅器に結合する利得制御信号を与える、ネットワーク受信機。

**【請求項22】**

前記選択回路は、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間よりも大きい場合に、前記第2の増幅器利得設定を前記入力増幅器に結合する利得制御信号を与える、請求項21に記載のネットワーク受信機。

**【発明の詳細な説明】**

10

**【0001】**

**【発明の分野】**

この発明は一般的にネットワークインターフェイスに関し、より特定的には、ネットワーク媒体に接続されたネットワークステーション間のデータ伝送を制御するためのシステムと、データネットワークにおいて複数の信号フォーマットのための入力利得を調整するための装置および方法とに関するものである。

**【0002】**

**【発明の背景】**

さまざまな種類のデジタルデータをコンピュータ間で伝送することが重要性を増し続けている。このようなデジタルデータを伝送する一般的な方法は、デジタルデータを低周波のベースデータ信号に符号化するステップと、ベースデータ信号を高周波のキャリア信号上に変調するステップとを含む。次に高周波のキャリア信号は、ネットワークケーブル媒体にわたって、RF信号、変調された光照射、またはその他のネットワーク媒体を介し、遠隔の計算ステーションへと送信される。

20

**【0003】**

高周波のキャリア信号は遠隔の計算ステーションで受信されて復調され、こうして最初のベースデータ信号が回復されることになる。ネットワーク媒体にわたってキャリア信号に歪が全く生じなければ、受信されたキャリアは位相、振幅、および周波数に関して送信されたキャリアと同一であり、これを公知の混合の技術を用い復調してベースデータ信号を回復できるはずである。次に、公知のサンプリングアルゴリズムを用いてベースデータ信号をデジタルデータへと回復できるはずである。

30

**【0004】**

しかしながら、ネットワークトポロジーは高周波キャリア信号を歪める傾向にあり、これは、数々の分岐接続およびこれら分岐の異なる長さが、伝送されたキャリアの数々の反射を引起することによる。高周波のキャリアはさらに、ケーブル媒体付近で動作する電気機器により引起されるスプリアス雑音によって歪められる。これらの問題は、家庭用電話配線をネットワークケーブル媒体として用いたネットワークにおいてより顕著となるが、これは、数々の分岐および接続は典型的には3-3.4キロヘルツの周波数の単純旧式電話システムPOTS信号の伝送用に設計されたものであり、7メガヘルツのオーダの高周波キャリア信号の伝送用に設計されたものではないからである。さらにまた、高周波キャリア信号は、ネットワークケーブルを利用しているPOTSのオンフック雑音パルスおよびオフフック雑音パルスによるターンオン過渡によってもまた歪められる。

40

**【0005】**

このように高周波キャリア信号の周波数、振幅および位相が歪むことは、ネットワークの性能を低下させ、よりデータレートの高いネットワークの設計を妨げる傾向にあり、設計者に対し変調技術およびデータ回復技術を絶えず向上させてデータレートを向上させることを要求する。たとえばHPNA1.0規格の下ではキャリアのパルス位置変調(PPM)を用いて1メガビットのデータレートが達成され、一方でより最近の2.0規格は、周波数分散直交振幅変調(QAM)を利用する複雑な変調方式を用いて10メガビットのデータレートを達成する。

50

## 【0006】

規格の進歩およびデータレートの増加に関連する1つの問題は、H P N Aの例におけるように、変調技術が同じでないことがある。このため、旧版との互換性は、より新しいシステムの設計に固有のものとはならない。たとえばH P N Aシステムにおいて、旧版との互換性を保とうとすれば、より新しい2.0式受信機は、1.0規格に従うP P M変調キャリアと、2.0規格に従う周波数分散Q A M変調キャリアとの両方を復調できなければならない。このため、受信機における機能の多くを、P P M用の1回路とQ A M用の1回路との2つの別個の回路において実現しなければならず、受信機のコストおよび複雑さを増加させる。

## 【0007】

たとえば、典型的に受信機は変調キャリア信号をサンプリングし、或るサンプリング周波数で生じる一連のサンプルを発生させるための、A / D変換器を含む。これら一連のサンプルは、典型的にデジタル信号プロセッサ(D S P)上で実現される受信機回路の残りへと入力される。

## 【0008】

信号パラメータがA / D変換器のダイナミックレンジ内にあるようA / D変換器が保証するのに先立ち、増幅器がその利得設定に従い信号を調節する。典型的に増幅器の利得は、閉ループフィードバックシステムを用いて設定される。1つの問題は、P P M変調キャリア信号とQ A M変調キャリア信号との電力包絡線が著しく異なることに存する。より具体的には、P P M変調キャリア上の電力は3 μsecのオーダの短いパルスで生じ、Q A M変調キャリア上の電力は伝送フレーム全体にわたる連続的なものである。パルス化した電力の環境で入力利得を設定するのに用いられ得るフィードバック回路は、連続的な電力の環境で入力利得を設定するのに用いられ得るフィードバック回路と根本的に異なる。このため、P P M信号とQ A M信号との両方のための急速利得調整に対処するためには複雑なフィードバック回路が必要となる。このような回路は受信機のサイズおよびコストを著しく増加させるであろう。

## 【0009】

したがって、サイズおよびコストの低減という業界で認知された目標に基づき、複数の変調技術を用いて変調された変調キャリア信号を受信できる受信機において増幅器のための入力利得を調整するための装置および方法が必要とされている。

## 【0010】

## 【発明の概要】

この発明の第1の局面は、ネットワーク媒体を介して別のネットワーク送受信機から変調キャリア信号を受信するよう構成されたネットワーク受信機を提供することである。ネットワーク受信機は、a)受信された変調キャリア信号を複数の増幅器利得設定の1つに従い増幅し、増幅されたキャリア信号を出力するための入力増幅器と、b)増幅されたキャリア信号に応答して包絡線信号を出力するよう構成された包絡線検波器と、c)包絡線信号に応答して第1の利得設定を選択するよう構成された第1の利得制御回路とを含み、第1の利得設定はパルス位置変調キャリア信号を受信するのに最適であり、ネットワーク受信機はさらに、d)包絡線信号に応答して第2の利得制御設定を選択するよう構成された第2の利得制御回路を含み、第2の利得設定は直交振幅変調信号を受信するのに最適であり、ネットワーク受信機はさらに、e)包絡線信号がパルス位置変調キャリアを表わすのか、または振幅変調キャリアを表わすのかを判断し、増幅器利得設定をそれぞれ第1の利得設定または第2の利得設定に設定するよう構成された選択回路を含む。

## 【0011】

ネットワーク受信機はさらに、増幅されたキャリア信号に応答してデジタルキャリア信号を発生するアナログ - デジタル変換器と、増幅されたキャリア信号に応答してデジタルIチャネルキャリア信号およびデジタルQチャネルキャリア信号を発生するヒルベルト変換器とを含むことができ、包絡線検波器は、Iチャネルキャリア信号およびQチャネルキャリア信号に応答する。

10

20

30

40

50

## 【0012】

選択回路は、包絡線信号中の電力パルスの持続時間を検出するためのキャリアセンス回路を含み、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間未満である場合に第1の利得設定を選択し、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間よりも大きい場合に第2の利得設定を選択することができる。

## 【0013】

包絡線信号は、Iチャネルキャリア信号の平方と、Qチャネルキャリア信号の平方との和の平方根を表わし得る。第1の利得制御回路は複数の比較器を含むことができ、各々の比較器は包絡線信号を複数の参照信号のうち1つと比較するよう構成され、第1の利得設定は、複数の利得設定の各々を反復的にテストする際に少なくとも1つの比較器の飽和を検出することにより決定される。第2の利得制御回路は、包絡線信号を表わす対数信号を発生する対数ルックアップテーブルと、対数信号を参照信号と比較して差信号を発生する比較器と、差信号をループ利得定数で乗じて積を発生する乗算器と、積を積分して第2の利得設定を発生する積分器とを含み得る。ループ利得定数は、検出された電力パルスの第1の部分のためには或る大きな値、検出された電力パルスの第2の部分のためにはより小さな値、および検出された電力パルスの残りの持続時間のためには0となるよう選択され得る。

10

## 【0014】

この発明の第2の局面は、ネットワーク媒体から変調キャリア信号を受信するよう構成された受信機において、増幅されたキャリア信号を発生する入力増幅器のための利得設定を決定する方法を提供することである。この方法は、a) 増幅されたキャリア信号電力を表わす増幅されたキャリア信号から包絡線信号を発生するステップと、b) 包絡線信号に応答して第1の利得設定を決定するステップとを含み、第1の利得設定はパルス位置変調キャリア信号を受信するために選択され、この方法はさらに、c) 包絡線信号に応答して第2の利得設定を決定するステップを含み、第2の利得設定は直交振幅変調キャリア信号を受信するために選択され、この方法はさらに、d) 変調キャリア信号がパルス位置変調キャリアであるのか、または直交振幅変調キャリアであるのかを判断するステップと、e) 変調キャリア信号がパルス位置変調キャリアであると判断された場合に入力増幅器利得を第1の利得設定に設定し、変調キャリア信号が直交振幅変調キャリアであると判断された場合に入力増幅器利得を第2の利得設定に設定するステップとを含み得る。

20

## 【0015】

この方法はさらに、増幅されたキャリア信号をデジタルキャリア信号へと変換するステップと、デジタルキャリア信号からIチャネル信号およびQチャネル信号を発生するステップとを含むことができ、Iチャネル信号およびQチャネル信号から包絡線信号が発生される。

30

## 【0016】

入力増幅器の利得を設定するステップは、包絡線信号中の電力パルスの持続時間を検出するステップと、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間未満である場合に入力増幅器利得を第1の利得設定に設定するステップと、電力パルスの持続時間がパルス位置変調電力パルスの持続時間のオーダの持続時間よりも大きい場合に入力増幅器利得を第2の利得設定に設定するステップとを含み得る。包絡線信号は、Iチャネル信号の平方とQチャネル信号の平方との和の平方根を表わし得る。

40

## 【0017】

第1の利得設定は、包絡線信号を複数の参照レベルと比較し、複数の利得設定の各々を、少なくとも1つの参照レベルで飽和が生じているかどうかに關し反復的にテストして第1の利得設定を決定することにより決定され得る。第2の利得設定は、包絡線信号を、包絡線信号を表わす対数信号に変換し、対数信号を参照レベルと比較して差を求め、この差をループ利得定数で乗じて積を求め、この積を積分して第2の利得設定を決定することにより決定され得る。ループ利得定数は、検出された電力パルスの第1の部分のためには或る

50

大きな値、検出された電力パルスの第2の部分のためにはより小さな値、および検出された電力パルスの残りの持続時間のためには0となるよう選択され得る。

#### 【0018】

##### 【好ましい実施例の説明】

次に、図面を参照しながらこの発明を詳細に説明する。図面においては、同じ参照番号は全体を通じて同じ要素を示すのに用いられる。

#### 【0019】

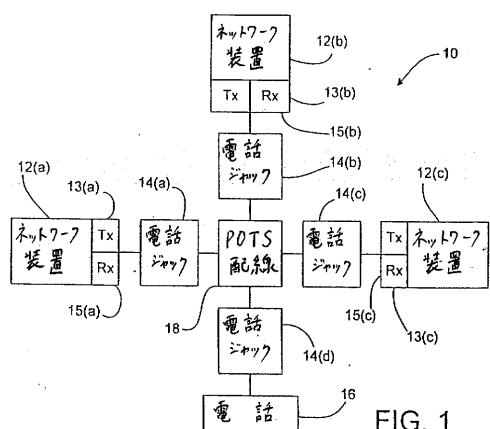

図1は、撲滅対ネットワーク媒体を用いた家庭における環境で実現される、この発明の実施例に従うローカルエリヤネットワーク10の図である。図1に示すように、ネットワーク10はネットワークステーション12(a)-12(c)を含み、これらはそれぞれRJ-11電話ジャック14(a)-14(c)を介して電話回線(撲滅)配線18に接続される。電話16がRJ-11電話ジャック14(d)に接続され、ネットワーク装置12(a)-12(c)がネットワークデータの通信を行なっている間でも通話を続けることができる。

10

#### 【0020】

図1に示すように、各々のネットワーク装置12は、パーソナルコンピュータ、プリンタ、サーバ、またはその他の民生用情報機器であることができ、各々のネットワーク装置は、ネットワーク媒体18を介し他のネットワーク装置12(a)-12(c)と通信を行なうための送受信機13(a)-13(c)をそれぞれ含む。

20

#### 【0021】

ネットワーク装置12(a)-12(c)の各々は、ネットワークデータで変調されたキャリア信号を含むアナログネットワーク信号を伝送することにより通信を行なう。ネットワーク装置12(a)-12(c)の一部はパルス位置変調(PPM)を利用でき、ネットワークデータは離散的な帯域制限されたパルスを利用したキャリア上で変調される。ネットワーク装置12(a)-12(c)の別の部分はPPM変調または直交振幅変調(QAM)を選択的に利用でき、ネットワークデータは、複雑な符号化コンステレーションに従いキャリアの振幅と位相との両方を変化させることによりキャリア上で変調される。好ましい実施例においてPPM変調は、カリフォルニア州、サニイベイル(Sunnyvale, California)のアドバンスト・マイクロ・ディバイシズ・インコーポレイテッド(Advanced Micro Devices, Inc.)社を含むネットワーク設備プロバイダの企業共同体によって公表されているホーム・フォンライン・ネットワーク・アライアンス(Home Phoneline Network Alliance)(HPNA)1.0規格に準拠して1メガビットのデータレートに備えるものであり、QAM変調はHPNA2.0規格に準拠して10メガビットのデータレートに備える。このため、PPM変調のみが可能であるネットワーク装置12と他のあらゆる装置との間のデータ通信はPPM変調キャリアを利用することが認められるであろう。しかしながらPPM変調とQAM変調との両方が可能である2つの装置間のデータ通信は、より早いQAM変調キャリアのデータレートを利用することになる。したがって受信ネットワーク装置においては、PPMとQAMとの両方が可能である送受信機13(a)-13(c)は、PPM変調キャリアとQAM変調キャリアとの両方を利用したデータを受信できなければならず、これは、このようなキャリアの各々の存在を検出することと、このようなキャリアの各々を区別することと、このようなキャリアの各々を受信および復調することとを含むことが認められるであろう。

30

#### 【0022】

さらに、HPNA1.0装置とHPNA2.0装置との両方を含むネットワーク10において装置12(a)-12(c)間の通信を容易にするために、互換性モード(CM)と呼ばれる第3の動作モードが存在する。互換性モードフレームは、QAM変調データのすぐ前にあるPPM変調ヘッダを利用する。送受信機13(a)-13(c)はさらに、PPMフレームと互換性モードフレームとを区別して各々を適当に受信できなければならない。

40

#### 【0023】

50

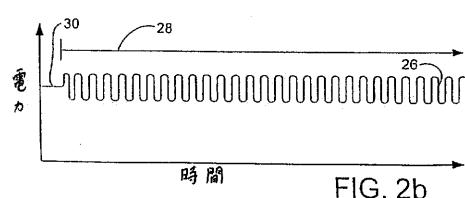

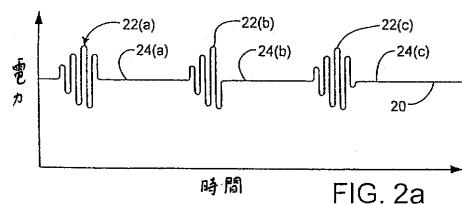

上で論じたように、PPMを利用して変調されたキャリアの電力包絡線と、QAMを用いて変調されたキャリアの電力包絡線とは根本的に異なる。図2aを参照して、PPM変調キャリア20の電力包絡線は複数の別個の電力パルス22(a)-22(c)を含み、各フレーム内でこれらパルスは電力休止24(a)-24(c)により分離される。図2bを参照して、QAM変調キャリア26の電力包絡線は、フレーム間に生じる電力休止30を有するフレーム28の持続時間中の連続的な電力キャリアを含む。

#### 【0024】

さらに、先に論じたように、ネットワーク媒体の配線トポロジー(図1)は著しい歪を引起し、このため信号の強さが著しく変動し、受信されたキャリア信号に複数の局所化した極大値および極小値が生じる恐れがある。送受信機13(a)-13(c)の各々にある各々の受信機15(a)-15(c)は、キャリアの存在の検出、およびQAM変調キャリアとPPM変調キャリアとの区別に加え、ネットワークデータ受信時に上のような歪に対処しなければならない。受信されたアナログ変調キャリアがA/D変換器でサンプリングされてこのようなキャリアのデジタル表現を発生するデジタル環境で実現される受信機15(a)-15(c)においては、上のような歪への対処は、入力増幅器を利用してキャリア信号を増幅し、こうしてA/D変換器のダイナミックレンジを適切に利用することを含む。

10

#### 【0025】

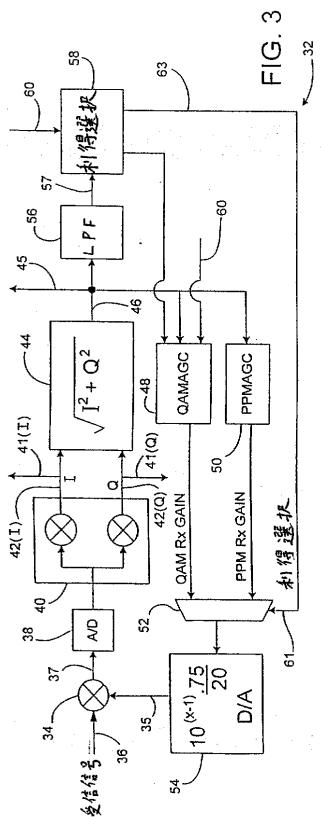

図3を参照して、入力増幅器34の利得を設定してA/D変換器38のダイナミックレンジをいっぱいに利用するのに用いられ得る回路32が示される。動作において、入力増幅器34は受信された信号36を利得設定35に基づき増幅する。次に、増幅された信号37はA/D変換器38に入力される。A/D変換器は増幅された信号37をサンプリングし、変調キャリアを表わす一連のデジタルサンプル値を発生するよう機能する。次に、デジタルサンプル値はヒルベルト変換器40に入力され、これは公知の技術を用いてデジタルサンプル値からのIチャネル信号42(I)とQチャネル信号42(Q)とを分離するよう機能する。Iチャネル信号42(I)およびQチャネル信号42(Q)は包絡線検波器44に入力され、これは公知の技術を利用して $I^2 + Q^2$ の和の平方根を算出し、これを表わす包絡線信号46を発生する。

20

#### 【0026】

Iチャネル信号42(I)およびQチャネル信号42(Q)はさらに、線41(I)および線41(Q)上のQAM変調データを回復するための受信機(図示せず)に結合され、一方で包絡線信号46はPPM変調データを回復するための受信機(図示せず)に結合される。

30

#### 【0027】

包絡線信号46はさらに、QAM自動利得制御(QAM AGC)回路48とPPM自動利得制御(PPM AGC)回路50との各々にも結合される。QAM AGC回路48はQAM利得値(QAM R x Gain)を発生するよう機能し、一方でPPM AGC回路50はPPM利得値(PPM R x Gain)を発生するよう機能する。マルチブレクサ52は、受信された信号36を線61上の利得選択信号に従い増幅するために、QAM R x GainとPPM R x Gainとのうちいずれを用いるかを選択するよう動作する。マルチブレクサ52からの選択された利得信号、QAM R x GainまたはPPM R x Gainのいずれかは、対数D/A変換器54に入力され、これはアナログ利得信号35を発生し、これが入力増幅器34の利得を設定する。

40

#### 【0028】

包絡線信号46はさらにローパスフィルタ56にも入力され、これはフィルタ処理された包絡線信号を発生し、これが今度は利得選択回路58に結合されるが、この利得選択回路は、PPMフレーム、QAMフレームおよび互換性モードフレームの検出に従いQAM R x GainまたはPPM R x Gainを選択するためのものである。

#### 【0029】

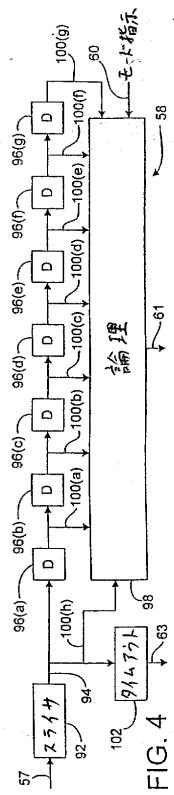

図4を参照して、利得選択回路58は典型的に、線57上のフィルタ処理された包絡線信

50

号を受信するためのスライサ92またはその他のしきい値検出器を含む。スライサ92はフィルタ処理された包絡線信号をしきい値と比較し、線94上にスライサ出力信号を発生し、この信号は、フィルタ処理された包絡線信号がしきい値以上である場合には論理Hであり、フィルタ処理された包絡線信号がしきい値未満の場合には論理Lである。

【0030】

スライサ出力信号は一連の遅延要素96(a) - 96(g)に逐次入力される。遅延要素96(a) - 96(g)は各々がスライサ出力信号を0.5μsecだけ遅延させるよう機能する。スライサ92および遅延要素96(a) - 96(g)の各々からのスライサ出力信号は、タップ線100(a) - 100(h)を通じて論理回路98に入力される。

【0031】

遅延要素96(a) - 96(g)は各々がスライサ出力信号における0.5μsecの遅延を表わすので、スライサ出力信号が3μsecの持続時間だけ論理Hであり続ける場合、タップ線100(a) - 100(h)により論理回路に入力される6つの逐次の遅延要素の出力が論理Hとなることが理解されるであろう。

【0032】

線94上のスライサ出力信号はさらにタイムアウト回路102にも結合される。タイムアウト回路102は線63上にタイムアウト信号を与え、これは、スライサ出力信号が論理Hから論理Lに遷移した後、3.5μsecを超える期間キャリアが検出されなかったことを示すものである。

【0033】

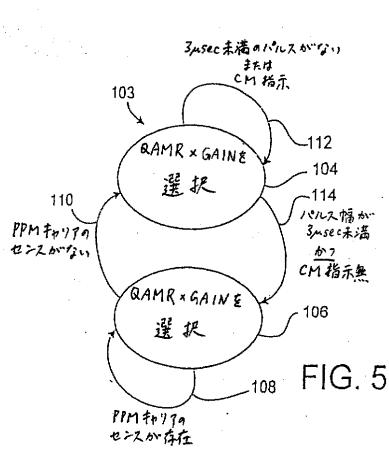

論理回路98は利得選択信号を線61上に発生するよう動作し、これは図5に示す利得選択ステートマシン103に従うPPM RxGainおよびQAM RxGainを表わす。

【0034】

図5のステートマシン図を参照して、104は、利得選択信号がQAM RxGainを表わす状態を表わし、状態106は、利得選択信号がPPM RxGainを表わす状態を表わす。

【0035】

論理回路98が状態104にあるとき、検出されたパルス幅が3μsec未満でない(たとえばタップ線100(a) - 100(h)上で3μsecの間パルスが検出されない、または連続的なパルスが検出される)限り、または、受信機によって互換性モードが線60上に示される限り、論理回路98はループ112を通じて状態104にとどまる。これに対応して、検出されたパルス幅が3μsec未満であり、かつ線60上に互換性モードが示されない場合、ステートマシン103は遷移114を通じて状態106へと遷移する。

【0036】

ステートマシン103は、PPMモードが受信機からの線60上に示される限り、ループ108を通じて状態106にとどまることになる。これに対応して、PPMモードが受信機からの線60上に示されなければ、ステートマシンは遷移110を通じて遷移し状態104へと戻る。

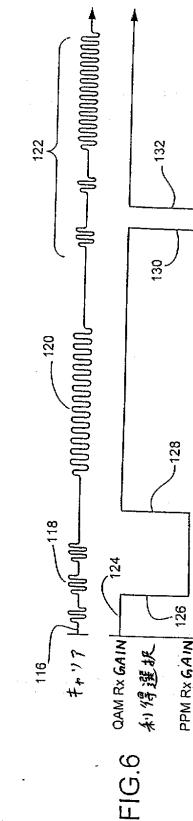

【0037】

図6を参照して、CRSステートマシンの例示の動作を示すタイミング図が示される。キャリア信号116は、PPMフレーム118、QAMフレーム120、および互換性モードフレーム122を含み、互換性モードフレームはPPMヘッダおよびこれに続くQAMデータから構成される。図5を参照して論じたように、利得選択信号124は、3μsec未満のパルスが検出されず、かつ互換性モードが示されない限り、QRM RxGain状態にとどまる。PPMフレーム118の始まりに近い遷移126は、3μsec未満の持続時間のパルスの検出時におけるPPM RxGainへの遷移を示す。同様に、互換性モードフレーム122の始まりに近い遷移130は、3μsec未満の持続時間のパルスの検出時におけるPPM RxGainへの遷移を表わす。しかしながら遷移132

10

20

30

40

50

は、互換性モードが受信機により示されるとすぐに遷移しQ A M利得に戻ることを表わす。受信機が遷移130前に互換性モードを検出しつつ示すことができる場合には、遷移130は生じないことが認められるであろう。

【0038】

P P Mフレーム118の完了時に、Q A M R x G a i nへの遷移128は遷移110(図5)と同時に生じる。

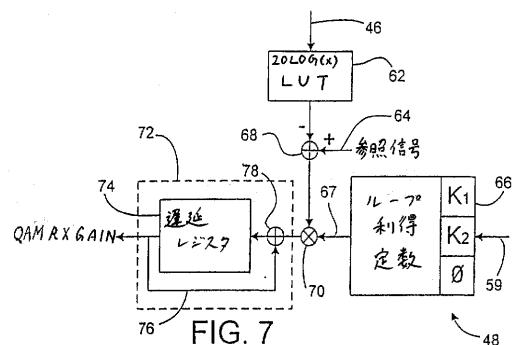

【0039】

図7を参照して、Q A M A G C回路48を表わすブロック図が示される。包絡線信号46が対数ルックアップテーブル62に入力され、これは包絡線信号46の20L o gを表わす対数信号を発生する。対数信号は次に比較器68により予め定められた参照レベル64と比較され、参照レベル64と対数信号との差は乗算器70においてループ利得定数67で乗じられ、積信号を発生する。積信号は次に積分器72に入力され、これが今度はQ A M R x G a i n信号を発生する。積分器72は典型的に、当業者に公知のように、遅延要素74、フィードバック回路76、および加算器78を含む。

10

【0040】

ループ利得定数67はループ利得定数回路66により発生される値であり、ループ利得定数回路は以下のステートマシン規則に従うステートマシンとして機能する。

【0041】

フレームの最初の0.5μsecの間K1を選択(Q A Mキャリアが線60上に示される)

20

0.5μsecから1.5μsecまでK2を選択

1.5μsec後、フレームの終わりまで0(たとえば固定利得)を選択(線63上にタイムアウト信号)

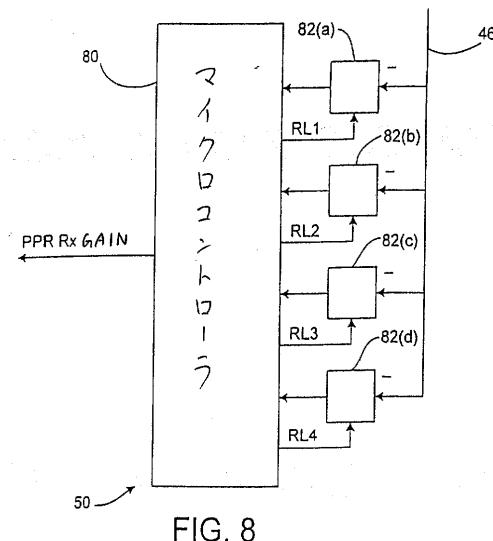

図8を参照して、P P M A G C回路50を表わすブロック図が示される。包絡線信号46は4つの比較器82(a) - 82(d)のバンクに入力され、これら比較器の各々は包絡線信号46を4つの参照レベルR L(1) - (4)のうち1つと比較する。マイクロコントローラ80が比較器82(a) - 82(c)の各々からの値を受信し、これから各々の参照レベル信号R L(1) - R L(4)およびP P M R x G a i n信号を発生する。

【0042】

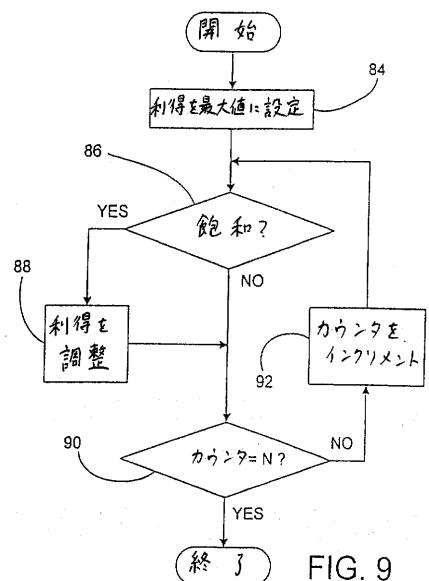

図8との関連で図9を参照して、マイクロコントローラ80の動作を示すフローチャートが示される。ステップ84において、マイクロコントローラ80はP P M R x G a i nを最大利得に設定し、参照レベルR L(1) - R L(4)の各々を予め定められた参照レベルに設定する。好ましい実施例では、R x G a i nは3ビット信号であり、こうして8つの可能な離散利得設定を表わし、ここで最大設定は2進数の111で表わされる。ステップ86でマイクロコントローラ80は、飽和があるかどうか、より具体的には、包絡線信号45が4つの参照レベルR L(1) - R L(4)のうち1つを一貫して上回っているかどうかを判断する。飽和が検出されると、ステップ88で利得が調整される。利得調整は、反復的なプロセスで最上位ビットから最下位ビットまで、正しい利得設定へと急速に収束するようにして達成される。マイクロコントローラ80によりキャリア上に検出される各P P Mパルスにつき1つの反復が行われる。したがってステップ88において、利得は2進数の011に調整される。利得がステップ88で調整された後、ステップ90において、最適利得を選択するのに必要となり得る反復の最大数とカウンタが比較され、もしカウンタがより小さければ、これはステップ92でインクリメントされ、マイクロコントローラは利得調整を停止させ、こうして利得を固定する。ステップ86で飽和が検出されなければ、マイクロコントローラは直接ステップ86からステップ90に進む。

30

【0043】

上述の装置および方法は、ネットワーク環境で動作する受信機のための入力増幅器利得設定を選択するための単純化されたシステムを提供するものであり、ここで受信機は複数の変調技術を利用したデータを区別および受信しなければならないことが認められるであろう。

40

50

## 【0044】

この発明を或る好ましい実施例に関して示しかつ説明したが、当業者がこの明細書を読みかつ理解すれば均等物および変形例に思い至ることは明らかである。たとえば、例示の実施例は P P M 变調および Q A M 变調に向けられたものであるが、周波数变調、位相シフトキーイング、およびその他の变調技术が容易に代用される。さらに、例示の実施例は变调技术を区别するための包络线検波器を利用するものであるが、区别的ための他の技术が、選択された变调技术を利用して变调されたキャリア信号の特性を区别することに基づいて容易に用いられる。この発明はこのような均等物および変形例をすべて含み、前掲の特許請求の範囲の範囲内によってのみ限定される。

## 【図面の簡単な説明】

10

【図 1】 この発明の一実施例に従うローカルエリアネットワークのブロック図である。

【図 2 a】 この発明の一実施例に従うパルス位置变調キャリアの図である。

【図 2 b】 この発明の一実施例に従う直交振幅变調キャリアの図である。

【図 3】 この発明の一実施例に従う利得制御フィードバックループのブロック図である。

【図 4】 この発明の一実施例に従う利得选择回路のブロック図である。

【図 5】 図 4 の利得选择回路の動作を示すステートマシン図である。

【図 6】 図 5 のステートマシンの例示の動作を示す図である。

【図 7】 この発明の一実施例に従う、直交振幅变調キャリアのための增幅器利得設定を决定するのに用いられ得る利得制御回路のブロック図である。

20

【図 8】 この発明の一実施例に従う、パルス位置变調キャリアのための增幅器利得設定を决定するのに用いられ得る利得制御回路のブロック図である。

【図 9】 図 8 の回路で用いられ得るマイクロコントローラの動作を示すフローチャートである。

【図 1】

【図 2 b】

【図 2 a】

【 四 3 】

【 図 4 】

【 义 5 】

【 図 6 】

【図7】

【図8】

【図9】

---

フロントページの続き

(74)代理人 100083703

弁理士 仲村 義平

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100109162

弁理士 酒井 將行

(72)発明者 ネイラー, コリン・ディ

アメリカ合衆国、94087 カリフォルニア州、サンディベイル、オンタリオ・コート、691、

ナンバー・1

審査官 羽岡 さやか

(56)参考文献 特開平9-200286 (JP, A)

特開2000-004409 (JP, A)

特開平8-317012 (JP, A)

特開2000-134271 (JP, A)

特開2000-286908 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 27/00-27/38

H03G 3/20

H03G 3/30

H04B 1/16

H04B 1/18