(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5259807号

(P5259807)

(45) 発行日 平成25年8月7日(2013.8.7)

(24) 登録日 平成25年5月2日(2013.5.2)

(51) Int.Cl.

H01L 23/02 (2006.01)

H01L 23/12 (2006.01)

F 1

H01L 23/02

H01L 23/12 301Z

請求項の数 1 (全 8 頁)

(21) 出願番号 特願2011-253655 (P2011-253655)

(22) 出願日 平成23年11月21日 (2011.11.21)

(62) 分割の表示 特願2010-86000 (P2010-86000)

の分割

原出願日 平成16年12月28日 (2004.12.28)

(65) 公開番号 特開2012-39160 (P2012-39160A)

(43) 公開日 平成24年2月23日 (2012.2.23)

審査請求日 平成23年11月21日 (2011.11.21)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 110000235

特許業務法人 天城国際特許事務所

(72) 発明者 高木 一考

東京都港区芝浦一丁目1番1号 株式会社

東芝内

審査官 宮本 靖史

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

金属製ベース基板と、このベース基板上に配置された半導体素子と、前記ベース基板上に配置され、表面に回路パターンを形成した第1誘電体基板と、前記半導体素子および前記第1誘電体基板を囲んで前記ベース基板上に設けた枠状の側壁と、前記側壁の一部に設けられた絶縁物からなる側壁部分と、前記ベース基板の面を基準にして、前記回路パターンよりも高い位置で前記側壁部分を貫通する帯状導体と、前記ベース基板の面を基準にして、前記第1誘電体基板側が低く前記帯状導体側が高くなる傾斜面を有し、前記第1誘電体基板と前記帯状導体との間の前記ベース基板上に設けられた金属ブロックと、この金属ブロック上に設けられ、表面に線路導体パターンが形成された第2誘電体基板と、この第2誘電体基板表面に形成された前記線路導体パターンを介して前記帯状導体と前記回路パターンとの間および前記回路パターンと前記半導体素子との間をそれぞれ接続するワイヤーとを具備したことを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は高周波帯などで使用する半導体装置に関する。

## 【背景技術】

## 【0002】

近年、高周波帯などで使用する半導体装置、たとえばガリウム砒素電界効果トランジス

タ（以下、G a A s F E Tという）を用いたマイクロ波電力増幅器などの半導体装置は高出力化が進み、高出力化への対応が求められている。

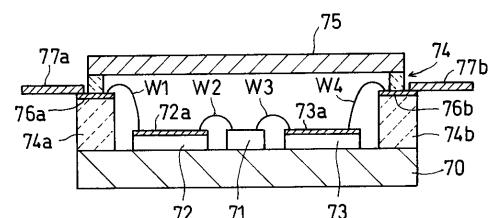

#### 【0003】

ここで、従来の半導体装置について、G a A s F E Tを用いた半導体装置を例にとり図7を参照して説明する。

#### 【0004】

金属製ベース基板70上に電力増幅用などの半導体素子71、たとえばG a A s F E Tが配置されている。半導体素子71のたとえば図示左側に位置する入力側に、第1誘電体基板72が配置されている。第1誘電体基板72上には、たとえば入力側整合回路などを構成する回路パターン72aが形成されている。半導体素子71のたとえば図示右側に位置する出力側に、第2誘電体基板73が配置されている。第2誘電体基板73上には、たとえば出力側整合回路などを構成する回路パターン73aが形成されている。また、半導体素子71および第1誘電体基板72、第2誘電体基板73などを囲んで、ベース基板70上に矩形枠状の側壁74が所定高さに形成されている。側壁74は、たとえば一部を除いて多くの部分が金属で形成され、また上部の矩形状開口はたとえば金属製の蓋75で封止されている。10

#### 【0005】

側壁74の図示左側に位置する入力側側壁部分74aは絶縁物で形成され、その入力側側壁部分74aを入力用帯状導体76aが貫通している。入力用帯状導体76aに入力用リード線77aが接続されている。側壁74の図示右側に位置する出力側側壁部分74bも絶縁物で形成され、その出力側側壁部分74bを出力用帯状導体76bが貫通している。出力用帯状導体76bに出力用リード線77bが接続されている。20

#### 【0006】

また、入力用帯状導体76aと第1誘電体基板72上の回路パターン72aとの間、および、回路パターン72aと半導体素子71との間、半導体素子71と第2誘電体基板73上の回路パターン73aとの間、回路パターン73aと出力用帯状導体76bとの間は、それぞれワイヤーW1～W4で接続されている。

#### 【0007】

上記した構成において、入力用帯状導体76aから入力する入力信号は回路パターン72aなどを経て半導体素子71で増幅される。その後、回路パターン73aなどを経て出力用帯状導体76bから出力される。30

#### 【0008】

上記したような半導体装置、たとえばベース基板上に枠状の側壁を設け、その側壁開口を蓋で覆ったパッケージ内に、半導体素子などを配置する半導体装置は特許文献1などに開示されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

#### 【特許文献1】特開平9-153839号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

従来の半導体装置は高出力化に伴い、たとえばパッケージの側壁部分を貫通する帯状導体に対し、大きな電流が流れても断線しない高い電流溶断容量が求められている。高い電流溶断容量を実現する1つの方法として、たとえば帯状導体の厚さを厚くする方法がある。しかし、帯状導体を厚くすると、次のような問題がある。

#### 【0011】

側壁部分を貫通する帯状導体は、たとえばその上下に側壁部分を構成する絶縁物、たとえばセラミック部材を配置し、上下のセラミック部材の接合により気密に封止されている。したがって、帯状導体が厚くなると、上下のセラミック部材の接合が困難になり、帯状

導体が貫通する部分の気密性が低下し、半導体素子などを封止するパッケージ内の空間の気密性を維持できなくなる。そのため帯状導体の厚さには限界がある。

#### 【0012】

高い電流溶断容量を実現するもう1つの方法として、たとえば帯状導体のパターン幅を広げる方法がある。パターン幅を広げた場合、所望のインピーダンスを保つために、帯状導体とベース基板との間に挟まれた側壁部分、たとえばセラミックの厚さを厚くする必要がある。セラミックを厚くすると、たとえば入力側あるいは出力側の整合回路などを構成する回路パターンと帯状導体との高低差が大きくなる。その結果、回路パターンと帯状導体との間を接続するワイヤーが上下方向に長くなり、たとえば放射損が増大する。

#### 【0013】

本発明は、上記した欠点を解決し、回路間の高低差を小さくし、放射損などを少なくした半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0014】

本発明の半導体装置は、金属製ベース基板と、このベース基板上に配置された半導体素子と、前記ベース基板上に配置され、表面に回路パターンを形成した第1誘電体基板と、前記半導体素子および前記第1誘電体基板を囲んで前記ベース基板上に設けた枠状の側壁と、前記側壁の一部に設けられた絶縁物からなる側壁部分と、前記ベース基板の面を基準にして、前記回路パターンよりも高い位置で前記側壁部分を貫通する帯状導体と、前記ベース基板の面を基準にして、前記第1誘電体基板側が低く前記帯状導体側が高くなる傾斜面を有し、前記第1誘電体基板と前記帯状導体との間の前記ベース基板上に設けられた金属ブロックと、この金属ブロック上に設けられ、表面に線路導体パターンが形成された第2誘電体基板と、この第2誘電体基板表面に形成された前記線路導体パターンを介して前記帯状導体と前記回路パターンとの間および前記回路パターンと前記半導体素子との間をそれぞれ接続するワイヤーとを具備したことを特徴とする。

#### 【発明の効果】

#### 【0015】

本発明は、ベース基板の面を基準にして、誘電体基板側が低く帯状導体側が高くなる傾斜面を有し、かつその傾斜面に線路導体パターンを形成した絶縁ブロックを、誘電体基板と帯状導体との間のベース基板上に配置している。そして、絶縁ブロックの傾斜面に形成された線路導体パターンを介して帯状導体と回路パターンとの間をワイヤーで接続している。したがって、高い電流溶断容量を得るために帯状導体の幅を広げ、これに伴い、ベース基板および帯状導体間の側壁部分が厚くなってしまっても、ワイヤーで接続する回路間の高低差が小さく、放射損の少ない半導体装置を実現できる。

#### 【図面の簡単な説明】

#### 【0016】

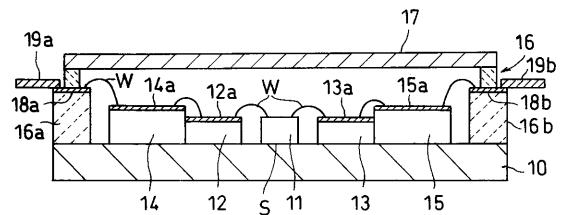

【図1】本発明の実施形態を説明する概略の構造図である。

【図2】本発明の他の実施形態を説明する概略の構造図である。

【図3】本発明の他の実施形態を説明する概略の構造図である。

【図4】本発明の他の実施形態を説明する概略の構造図である。

【図5】本発明の他の実施形態を説明する概略の構造図である。

【図6】本発明の他の実施形態を説明する概略の構造図である。

【図7】従来例を説明する概略の構造図である。

#### 【発明を実施するための形態】

#### 【0017】

本発明の実施形態について、G a A s F E Tを用いた半導体装置を例にとり図1を参照して説明する。

#### 【0018】

金属製ベース基板10上に電力增幅用などの半導体素子11、たとえばG a A s F E Tが配置されている。半導体素子11の図示左側に位置する入力側に第1誘電体基板12が

10

20

30

40

50

配置され、半導体素子 11 の図示右側に位置する出力側に、第 2 誘電体基板 13 が配置されている。第 1 誘電体基板 12 上には、たとえば入力側整合回路などを構成する回路パターン 12a が形成され、第 2 誘電体基板 13 上には、たとえば出力側整合回路などを構成する回路パターン 13a が形成されている。第 1 誘電体基板 12 の図示左側には、第 1 誘電体基板 12 よりも厚い第 3 誘電体基板 14 が配置され、第 2 誘電体基板 13 の図示右側には、第 2 誘電体基板 13 よりも厚い第 4 誘電体基板 15 が配置されている。第 3 誘電体基板 14 上および第 4 誘電体基板 15 上には回路パターン、たとえばマイクロストリップ線路を構成する線路導体 14a、15a が形成されている。

#### 【0019】

また、半導体素子 11 および第 1 誘電体基板 12、第 2 誘電体基板 13、第 3 誘電体基板 14、第 4 誘電体基板 15 などを囲んで、ベース基板 10 上にたとえば矩形枠状の側壁 16 が所定高さに形成されている。側壁 16 は、たとえば一部を除いて多くの部分が金属で形成され、また、上部の矩形状開口はたとえば金属製の蓋 17 で封止されている。

#### 【0020】

側壁 16 の図示左側に位置する入力側側壁部分 16a および側壁 16 の図示右側に位置する出力側側壁部分 16b は絶縁物で形成されている。そして、ベース基板 10 のたとえば中央領域、たとえば半導体素子 11などを配置した領域の平坦な面 S を基準にして、線路導体 14a や線路導体 15a よりも高い位置で、入力用帯状導体 18a および出力用帯状導体 18b がそれぞれ、入力側側壁部分 16a および出力側側壁部分 16b を貫通している。入力用帯状導体 18a には入力用リード線 19a が接続され、出力用帯状導体 18b には出力用リード線 19b が接続されている。

#### 【0021】

また、入力用帯状導体 18a と線路導体 14aとの間、および、線路導体 14a と回路パターン 12a との間、回路パターン 12a と半導体素子 11 との間、半導体素子 11 と回路パターン 13a との間、回路パターン 13a と線路導体 15b との間、線路導体 15b と出力用帯状導体 18b との間は、それぞれワイヤー W で接続されている。

#### 【0022】

上記した構成において、入力用帯状導体 18a から入力する入力信号は、線路導体 14a および回路パターン 12a などを経て半導体素子 11 で増幅される。増幅された入力信号は、回路パターン 13a および線路導体 15b、出力用帯状導体 18b などを経て出力される。

#### 【0023】

上記した構成によれば、第 1 誘電体基板 12 と入力側側壁部分 16a との間に第 3 誘電体基板 14 を配置している。また、第 2 誘電体基板 12 と出力側側壁部分 16b との間に第 4 誘電体基板 15 を配置している。そして、ベース基板 10 の面 S を基準にして、第 3 誘電体基板 14 上の線路導体 14a の高さが、第 1 誘電体基板 12 上の第 1 回路パターン 12a よりも高く、側壁 16 を貫通する帯状導体 18a よりも低くなっている。同様に、第 4 誘電体基板 15 上の線路導体 15a の高さが、第 2 誘電体基板 13 上の第 2 回路パターン 13a よりも高く、側壁 16 を貫通する帯状導体 18b よりも低くなっている。

#### 【0024】

したがって、高い電流溶断容量を得るために帯状導体 18a、18b の幅を広げ、帯状導体 18a、18b とベース基板 10 間の側壁 16 を厚くし、帯状導体 18a、18b の貫通部分の高さが高くなても、ワイヤーで接続する回路間の高低差が小さくなる。その結果、ワイヤーで接続する回路間のインピーダンス変化が抑えられ、また、放射損の少ない半導体装置が得られる。

#### 【0025】

上記の実施形態は、ワイヤーで接続する回路間の高低差を小さくするために、たとえば第 1 誘電体基板 12 と入力側側壁部分 16a との間に 1 つの誘電体基板 14 を配置している。しかし、ワイヤーで接続する回路間の高低差をさらに小さくするために、高さの相違する複数の誘電体基板を配置することもできる。

10

20

30

40

50

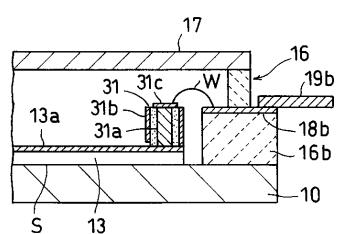

**【0026】**

次に、本発明の他の実施形態について図2を参照して説明する。本発明の半導体装置は、たとえば半導体素子を中心にして左右が対称の構造になっている。したがって、図2はその出力側部分を抜き出した図で、図1に対応する部分に同じ符号を付し重複する説明を一部省略する。

**【0027】**

この実施形態は、第4誘電体基板15と帯状導体18bとの間に、ベース基板10の面Sを基準にして、その表面が帯状導体18bの高さと同じになる厚さの誘電体基板21を配置し、その表面に線路導体21aを設けている。

**【0028】**

たとえば帯状導体18bが側壁16を貫通する部分の近傍、たとえば側壁16の外側や内側、あるいは貫通部分では、側壁16の有無など帯状導体18b周辺の構造が相違している。そのため、インピーダンスが変化しやすく、安定した信号の伝送が困難になっている。

**【0029】**

図2の構成によれば、たとえば帯状導体18bと同じ高さに線路導体21aを設けた誘電体基板21を帯状導体18bに隣接して配置している。したがって、インピーダンスが変化しやすい帯状導体18bの近傍では、ワイヤーで接続する回路間の高低差がなくなり、伝送する信号の乱れを小さくできる。

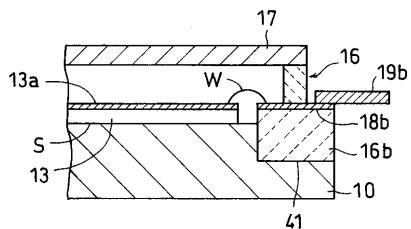

**【0030】**

次に、本発明の他の実施形態について、出力側部分を抜き出した図3を参照して説明する。図3は、図1に対応する部分に同じ符号を付し重複する説明を一部省略する。

**【0031】**

この実施形態は、第2誘電体基板13上に設けた回路パターン13aと帯状導体18bとの間、たとえば第2誘電体基板13上の端部に絶縁ブロック31を配置している。絶縁ブロック31には、貫通穴を設けたVIAホール31aが形成され、また、VIAホール31aを囲むその側面などに導電層31bが形成されている。また、絶縁ブロック31の図示上面に、VIAホール31aに接続する導電パターン31cが形成され、この導電パターン31cと帯状導体18bとの間がワイヤーWで接続されている。

**【0032】**

絶縁ブロック31の高さは、たとえば導電パターン31cと帯状導体18bとの間に高低差がないように、帯状導体18bの貫通部分と同じにしている。しかし、絶縁ブロック31の高さを低くし、導電パターン31cの位置を帯状導体18bの貫通部分よりも低くすることもできる。

**【0033】**

上記した構成によれば、帯状導体18bおよび回路パターン13a間を絶縁ブロック31に設けたVIAホール31aで接続し、VIAホール31aを囲んで導電層31bを形成している。したがって、VIAホール31a部分での放射損を少なくできる。また、VIAホール31aの形状、たとえば貫通穴の径などを変えることにより、VIAホール31a部分のインピーダンスを適宜調整することもできる。

**【0034】**

次に、本発明の他の実施形態について、出力側部分を抜き出した図4を参照して説明する。図4は、図1に対応する部分に同じ符号を付し重複する説明を一部省略する。

**【0035】**

この実施形態は、ベース基板10周辺のたとえばその一部に、中央領域の面Sよりも低い段差面41を設けている。そして、段差面41上に側壁16を形成し、たとえば回路パターン13aと帯状導体18bの高さを同じにしている。

**【0036】**

この構成の場合も、段差面41上に側壁16を形成することによって、ワイヤーWで接続する回路間の高低差を小さくでき、上記した実施形態と同様の効果が得られる。

10

20

30

40

50

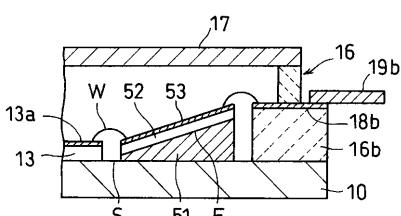

**【0037】**

次に、本発明の他の実施形態について、出力側部分を抜き出した図5を参照して説明する。図5は、図1に対応する部分に同じ符号を付し重複する説明を一部省略する。

**【0038】**

この実施形態は、第2誘電体基板13と帯状導体18bとの間のベース基板10上に、ベース基板10の面Sを基準にして、第2誘電体基板13側が低く帯状導体18b側が高くなる傾斜面Fを有する金属ブロック51を設け、この金属ブロック51の傾斜面Fに第2誘電体基板52を設け、さらに第2誘電体基板52上に第2回路パターン53、たとえば線路導体を形成している。

**【0039】**

10

上記した構成の場合も、金属ブロック51上に形成した回路パターン53が帯状導体18b側から第2誘電体基板13に向かって徐々に低くなっている。そのため、ワイヤーWで接続する回路間の高低差が小さくなり、上記した実施形態と同様の効果が得られる。

**【0040】**

金属ブロック51はベース基板10の表面を加工して形成してよく、別に形成した金属ブロック51をベース基板10上に接合してもよい。

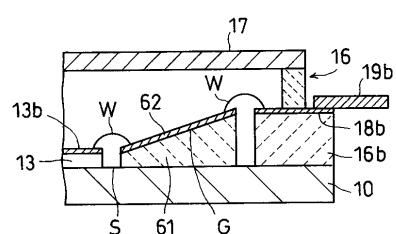

**【0041】**

次に、本発明の他の実施形態について、出力側部分を抜き出した図6を参照して説明する。図6は、図1に対応する部分に同じ符号を付し重複する説明を一部省略する。

**【0042】**

20

この実施形態は、第2誘電体基板13と帯状導体18bとの間のベース基板10上に、ベース基板10の面Sを基準にして、第2誘電体基板13側が低く、帯状導体18b側が高くなる傾斜面Gを有する絶縁ブロック61を配置している。そして、絶縁ブロック61の傾斜面Gに回路パターン62、たとえば線路導体を形成している。

**【0043】**

この場合も、ワイヤーWで接続する回路間の高低差が小さくなり、上記した実施形態と同様の効果が得られる。

**【符号の説明】****【0044】**

30

10...ベース基板

11...半導体素子

12...第1誘電体基板

12a...回路パターン

13...第2誘電体基板

13a...回路パターン

14...第3誘電体基板

14a...線路導体

15...第4誘電体基板

15a...線路導体

16...側壁

40

17...蓋

18a...入力用帯状導体

18b...出力用帯状導体

19a...入力用リード線

19b...出力用リード線

S...ベース基板の面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開2002-335136(JP,A)

実開昭57-138420(JP,U)

実開昭57-138422(JP,U)

特開平02-244711(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/02

H01L 23/12 - 23/15

H05K 7/14