(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년05월09일

(11) 등록번호 10-1618677

(24) 등록일자 2016년04월29일

(51) 국제특허분류(Int. Cl.)

G11C 16/06 (2006.01) G11C 16/10 (2006.01)

G11C 16/32 (2006.01)

(21) 출원번호 10-2011-7002516

(22) 출원일자(국제) 2009년06월30일

심사청구일자 2014년06월30일

(85) 번역문제출일자 2011년01월31일

(65) 공개번호 10-2011-0039310

(43) 공개일자 2011년04월15일

(86) 국제출원번호 PCT/US2009/049328

(87) 국제공개번호 WO 2010/002943

국제공개일자 2010년01월07일

(30) 우선권주장

61/133,675 2008년07월01일 미국(US)

(뒷면에 계속)

(56) 선행기술조사문헌

JP2007323731 A

US20040057284 A1

US20070189073 A1

US20080019188 A1

(73) 특허권자

엘에스아이 코포레이션

미국 캘리포니아주 95131, 새너제이, 라이더 파크

드라이브 1320

(72) 발명자

엔 존슨

미국 캘리포니아주 94539 프리몬트 로엘 클렌 테

라스 600

(74) 대리인

제일특허법인

전체 청구항 수 : 총 10 항

심사관 : 한선경

(54) 발명의 명칭 플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법 및 인터페이스

**(57) 요 약**

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱을 위한 방법 및 장치가 제공된다. 인터페이스는 플래시 메모리 제어기와 플래시 메모리 어레이 사이의 통신 채널을 포함하고, 통신 채널은 클럭 신호의 제 1 에지 상의 플래시 메모리 어레이 내의 타겟 셀에 대한 데이터를 전달하고, 통신 채널은 클럭 신호의 제 2 에지 상의 타겟 셀에 대한 추가의 정보를 전달한다. 예시적인 기록 액세스에 대해, 추가의 정보는 예를 들어 타겟 셀과 관련된 하나 이상의 공격자 셀에 대한 정보를 포함한다. 예시적인 판독 액세스에 대해, 추가의 정보는 예를 들어, 제 1 에지 상에 전송된 타겟 셀에 대한 데이터를 위한 소프트 정보를 포함한다.

**대 표 도**

(30) 우선권주장

61/133,921 2008년07월07일 미국(US)

61/134,688 2008년07월10일 미국(US)

---

## 명세서

### 청구범위

#### 청구항 1

플래시 메모리 제어기(120)와 플래시 메모리 어레이(160) 사이의 인터페이싱 방법에 있어서,

클럭 신호의 제 1 에지를 사용하여 상기 플래시 메모리 어레이 내의 타겟 셀(710)에 대한 데이터를 전송하는 단계와,

상기 클럭 신호의 제 2 에지를 사용하여 상기 타겟 셀에 대한 추가의 정보를 전송하는 단계를 포함하되,

상기 클럭 신호의 각각의 에지의 타입은 하강 에지 타입(a falling edge type) 및 상승 에지 타입(a rising edge type) 중 하나이고, 상기 클럭 신호의 제 1 에지의 타입은 상기 클럭 신호의 제 2 에지의 타입과는 상이하고, 상기 데이터는 상기 추가의 정보와는 상이한 타입인

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 2

제 1 항에 있어서,

상기 전송하는 단계들은 기록 액세스를 포함하고, 상기 추가의 정보는 상기 타겟 셀과 연관된 하나 이상의 공격자 셀(720)에 대한 정보를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 3

제 2 항에 있어서,

상기 하나 이상의 공격자 셀에 대한 상기 정보는 상기 하나 이상의 공격자 셀에 대한 프로그램 데이터의 하나 이상의 비트를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 4

제 1 항에 있어서,

상기 전송하는 단계들은 관독 액세스를 포함하고, 상기 추가의 정보는 상기 제 1 에지 상에 전송된 상기 타겟 셀에 대한 상기 데이터를 위한 소프트 정보를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 5

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법에 있어서,

클럭 신호의 제 1 에지 상의 상기 플래시 메모리 어레이 내의 타겟 셀에 대한 데이터를 수신하는 단계와,

상기 클럭 신호의 제 2 에지 상의 상기 타겟 셀에 대한 추가의 정보를 수신하는 단계를 포함하되,

상기 클럭 신호의 각각의 에지의 타입은 하강 에지 타입 및 상승 에지 타입 중 하나이고, 상기 클럭 신호의 제 1 에지의 타입은 상기 클럭 신호의 제 2 에지의 타입과는 상이하고, 상기 데이터는 상기 추가의 정보와는 상이

#### 한 타입인

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 6

제 5 항에 있어서,

상기 수신하는 단계들은 기록 액세스를 포함하고, 상기 추가의 정보는 상기 타겟 셀과 연관된 하나 이상의 공격자 셀에 대한 정보를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 7

제 6 항에 있어서,

상기 하나 이상의 공격자 셀에 대한 상기 정보는 상기 하나 이상의 공격자 셀에 대한 프로그램 데이터의 하나 이상의 비트를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 8

제 5 항에 있어서,

상기 수신하는 단계들은 판독 액세스를 포함하고, 상기 추가의 정보는 상기 제 1 에지로 전송된 상기 타겟 셀에 대한 상기 데이터를 위한 소프트 정보를 포함하는

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱 방법.

#### 청구항 9

플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱을 위한 인터페이스에 있어서,

상기 플래시 메모리 제어기와 상기 플래시 메모리 어레이 사이의 통신 채널을 포함하되,

상기 통신 채널은 클럭 신호의 제 1 에지로 상기 플래시 메모리 어레이 내의 타겟 셀에 대한 데이터를 전달하고, 상기 통신 채널은 상기 클럭 신호의 제 2 에지로 상기 타겟 셀에 대한 추가의 정보를 전달하며, 상기 클럭 신호의 각각의 에지의 타입은 하강 에지 타입 및 상승 에지 타입 중 하나이고, 상기 클럭 신호의 제 1 에지의 타입은 상기 클럭 신호의 제 2 에지의 타입과는 상이하고, 상기 데이터는 상기 추가의 정보와는 상이한 타입인

인터페이스.

#### 청구항 10

제 9 항에 있어서,

추가의 정보는 상기 타겟 셀과 연관된 하나 이상의 공격자 셀에 대한 정보 및 상기 제 1 에지로 전송된 상기 타겟 셀에 대한 상기 데이터를 위한 소프트 정보 중 하나 이상을 포함하는

인터페이스.

#### 청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

## 발명의 설명

### 기술 분야

#### 관련 출원의 상호 참조

[0001] 본 출원은 본 명세서에 각각 참조로서 포함되어 있는 2008년 7월 1일 출원된 미국 가특허 출원 제 61/133,675호, 2008년 7월 3일 출원된 미국 가특허 출원 제 61/133,921호 및 2008년 7월 10일 출원된 미국 가특허 출원 제 61/134,688호를 우선권 주장한다.

[0003] 본 출원은 2009년 3월 11일 출원된 발명의 명칭이 "페이지간 섹터, 다중 페이지 코딩 및 페이지당 코딩을 갖는 다중 레벨 셀 플래시 메모리 디바이스 내에 데이터를 저장하기 위한 방법 및 장치(Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding)"인 국제 특허 출원 제 PCT/US09/36810호와, 발명의 명칭이 "플래시 메모리 내의 관독측 셀간 간섭 완화를 위한 방법 및 장치(Methods and Apparatus for Read-Side Intercell Interference Mitigation in Flash Memories)"인 국제 특허 출원, "플래시 메모리 내의 기록측 셀간 간섭 완화를 위한 방법 및 장치(Methods and Apparatus for Write-Side Intercell Interference Mitigation in Flash Memories)"인 국제 특허 출원, 발명의 명칭이 "변조 코딩을 사용하는 셀간 간섭 완화를 위한 방법 및 장치(Methods and Apparatus for Intercell Interference Mitigation Using Modulation Coding)"인 국제 특허 출원 및 발명의 명칭이 "플래시 메모리 내의 소프트 디맵핑 및 셀간 간섭 완화를 위한 방법 및 장치(Methods and Apparatus for Soft Demapping and Intercell Interference Mitigation in Flash Memories)"인 국제 특허 출원에 관련되고, 이들 각각의 출원은 본 출원과 동일자로 출원되고 본 명세서에 참조로 포함되어 있다.

#### 발명의 분야

[0005] 본 발명은 일반적으로 플래시 메모리 디바이스에 관한 것으로서, 더 구체적으로는 이러한 플래시 메모리 디바이스 내의 제어기와 메모리 어레이 사이의 인터페이싱을 위한 기술에 관한 것이다.

## 배경 기술

[0006] 플래시 메모리 디바이스와 같은 다수의 메모리 디바이스는 데이터를 저장하기 위해 아날로그 메모리 셀을 사용한다. 각각의 메모리 셀은 스토리지 가치(storage value)라 또한 칭하는 아날로그 값을 저장한다. 스토리지 가치는 셀 내에 저장된 정보를 표현한다. 플래시 메모리 디바이스에서, 예를 들어 각각의 아날로그 메모리 셀은 통상적으로 특정 전압을 저장한다. 각각의 셀에 대한 가능한 아날로그 값의 범위는 통상적으로 임계 영역으로 분할되는데, 각각의 영역은 하나 이상의 데이터 비트값에 대응한다. 데이터는 원하는 하나 이상의 비트에 대응하는 공칭 아날로그 값을 기록함으로써 아날로그 메모리 셀에 기록된다.

[0007] 단일 레벨 셀(SLC) 플래시 메모리 디바이스는 예를 들어 메모리 셀당 하나의 비트(또는 2개의 가능한 메모리 상태)를 저장한다. 다른 한편으로, 다중 레벨 셀(MLC) 플래시 메모리 디바이스는 메모리 셀당 2개 이상의 비트를

저장한다(즉, 각각의 셀은 4개 이상의 프로그램 가능한 상태를 가짐). 다중 레벨 셀 디바이스에서, 적어도 3개의 임계 레벨이 4개 이상의 상이한 임계 상태를 규정하기 위해 이용된다. 따라서, 개별 셀의 작동 범위는 증가된 수의 상태로 분할되고, 각각의 상태의 범위는 단일 레벨 셀 디바이스에 대한 것보다 작다. 따라서, 다중 레벨 셀 디바이스 내의 임의의 단일 비트의 신뢰성은 일반적으로 단일 레벨 셀 디바이스의 신뢰성보다 작다. 다중 레벨 코드의 더 상세한 설명을 위해, 예를 들어, 본 명세서에 참조로서 포함되어 있는 유. 와흐스만(U. Wachsmann) 등의 "다중레벨 코드: 이론적인 개념 및 실용적인 디자인 규칙(Multilevel Codes: Theoretical Concepts and Practical Design Rules)", IEEE Trans. on Information Theory, Vol. 45, NO. 5, 1361-91(1999년)을 참조하라.

[0008] 플래시 메모리는 통상적으로, 플래시 메모리 어레이, 플래시 제어기 및 플래시 메모리와 플래시 제어기 사이의 통신을 위한 인터페이스를 포함한다. 개방 NAND 플래시 인터페이스 작업 그룹(ONFI)은 NAND 플래시 메모리 디바이스 및 이들과 통신하는 디바이스에 대한 개방 표준을 개발하는 산업 컨소시엄이다. ONFI는 NAND 플래시 칩에 대한 표준 인터페이스를 위한 사양을 생성하였다. ONFI 버전 2.0은 클럭 신호의 상승 및 하강 에지의 모두에 대해 데이터를 전달하기 위해 더블 데이터 레이트(DDR) 기술을 사용한다. ONFI 버전 2.0은 NAND 플래시 인터페이스의 데이터 전달 용량을 증가시키지만, 성능을 향상시킬 수 있는 추가의 정보를 전달하기 위한 추가의 대역폭을 제공하지 않는다.

미국 특허 번호 2007/0189073은 비휘발성 메모리 디바이스 및 프로그래밍 프로세스를 개시하고, 이는 인접한 메모리 셀로 후속하는 프로그래밍 사이클에 대해 프로그래밍된 데이터를 고려하여 프로그래밍된 임계 전압 레벨을 조정함으로써 인접 플로팅 게이트 또는 비전도성 플로팅 노드 메모리 셀의 임계 게이트 전압에 대한 커플링 효과를 보상하는 것으로서, 커플링 효과는 셀에 대한 원하는 타겟 임계 전압을 야기한다. 본 발명의 일 실시예에서, 제 2 페이지의 직접 인접 메모리 셀로 기록되는 데이터/프로그래밍 레벨을 고려하여 제 1 페이지의 하나 이상의 메모리 셀의 프로그래밍 레벨을 더 높은 또는 더 낮은 임계 검증 타겟 전압으로 조정함으로써, 메모리 셀 커플링이 보상되며, 제 1 페이지와 제 2 페이지의 직접 인접 메모리 셀들 사이에서의 커플링은 제 1 페이지의 메모리 셀을 이들의 최종 타겟 프로그래밍 레벨에 이르게 할 것이다.

미국 특허 번호 2004/0057284는 SCRAM 호환가능 인터페이스를 갖는 플래시 메모리 디바이스를 향상시키는 향상된 메모리 디바이스 및 아키텍처를 개시한다. 메모리 디바이스는 메모리의 아키텍처가 효율적인 플래시 메모리 구조를 내부적으로 구현하게 하는 가상 페이징 스킴을 이용한다. 외부적으로, 메모리는 내부 플래시 아키텍처를 SCRAM 호환가능 인터페이스 및 가상 아키텍처에 논리적으로 맵핑하여, 호환가능한 SCRAM 제어기 디바이스를 사용한 동작 및 메모리 액세스를 가능하게 한다. 클럭 신호의 상승 및 하강 에지를 모두 갖는 동기화에서 데이터가 메모리로부터의 입력 및 출력이 되게 하는 더블 데이터 레이트 인터페이스가 제공될 것이다.

## 발명의 내용

### 해결하려는 과제

[0009] 따라서, 플래시 메모리 디바이스 내의 제어기와 메모리 어레이 사이의 개량된 인터페이스에 대한 요구가 존재한다. 전송된 데이터에 대한 추가이 정보를 위한 추가의 대역폭을 제공하는 플래시 메모리 디바이스 내의 제어기와 메모리 어레이 사이의 개량된 인터페이스에 대한 또 다른 요구가 존재한다. 상당히 증가하는 전력 소산 또는 표면적 없이 추가의 대역폭을 제공하는 플래시 메모리 디바이스 내의 제어기와 메모리 어레이 사이의 개량된 인터페이스에 대한 추가의 요구가 존재한다.

### 과제의 해결 수단

[0010] 일반적으로, 플래시 메모리 제어기와 플래시 메모리 어레이 사이의 인터페이싱을 위한 방법 및 장치가 제공된다. 본 발명의 일 양태에 따르면, 플래시 메모리 제어기와 플래시 메모리 어레이 사이에 사용을 위한 인터페이스가 제공된다. 인터페이스는 플래시 메모리 제어기와 플래시 메모리 어레이 사이에 통신 채널을 포함하고, 통신 채널은 클럭 신호의 제 1 에지 상의 플래시 메모리 어레이 내의 타겟 셀에 대한 데이터를 전달하고, 통신 채널은 클럭 신호의 제 2 에지 상의 타겟 셀에 대한 추가의 정보를 전달한다.

[0011] 예시적인 기록 액세스에 대해, 추가의 정보는 예를 들어 타겟 셀과 관련된 하나 이상의 공격자 셀에 대한 정보

를 포함한다. 예를 들어, 하나 이상의 공격자 셀에 대한 정보는 하나 이상의 공격자 셀에 대한 프로그램 데이터의 하나 이상의 비트를 포함할 수 있다. 예시적인 관독 액세스에 대해, 추가의 정보는 예를 들어 제 1 에지 상에 전송된 타겟 셀에 대한 데이터에 대한 소프트 정보를 포함한다.

[0012] 본 발명의 더 완전한 이해, 뿐만 아니라 본 발명의 다른 특징 및 장점은 이하의 상세한 설명 및 도면을 참조하여 얻어질 수 있다.

### 도면의 간단한 설명

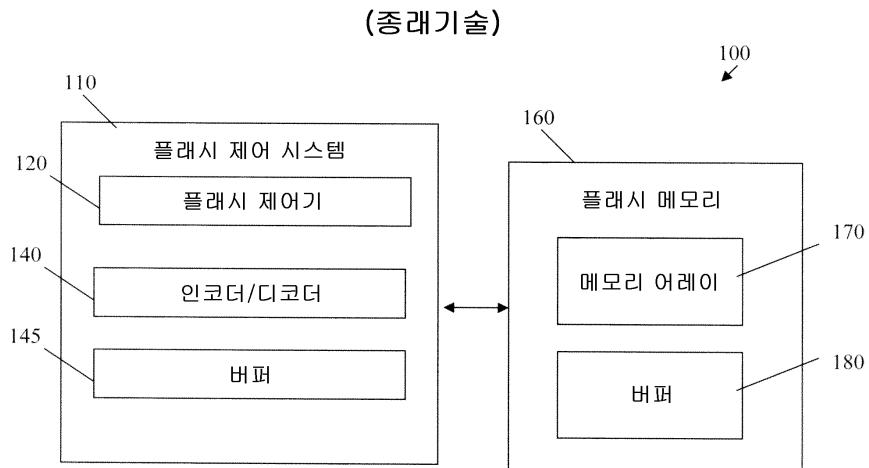

[0013] 도 1은 통상의 플래시 메모리 시스템의 개략 블록 다이어그램.

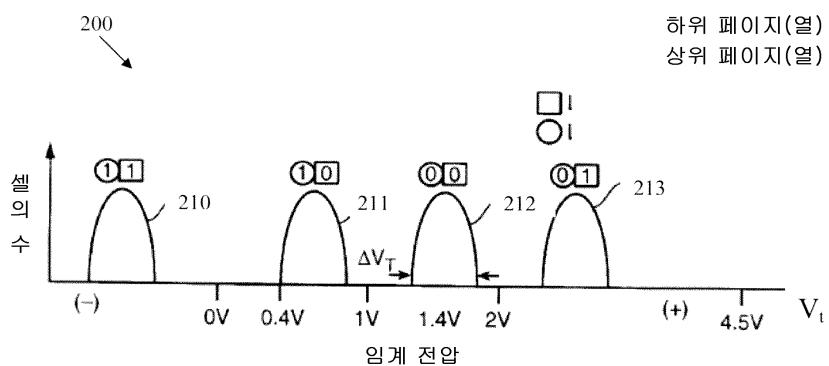

도 2는 도 1의 예시적인 다중 레벨 셀 플래시 메모리에 대한 예시적인 임계 전압 분포를 도시하는 도면.

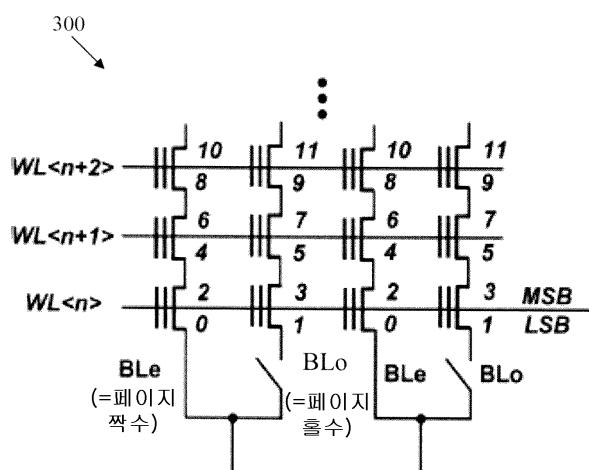

도 3은 다중 레벨 셀(MLC) 플래시 메모리 디바이스 내의 예시적인 플래시 셀 메모리의 아키텍처를 도시하는 도면.

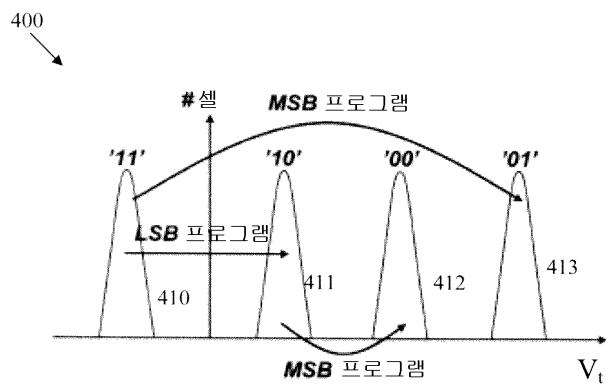

도 4는 도 2의 전압 할당 체계에 대한 예시적인 2단 MLC 프로그래밍 체계를 도시하는 도면.

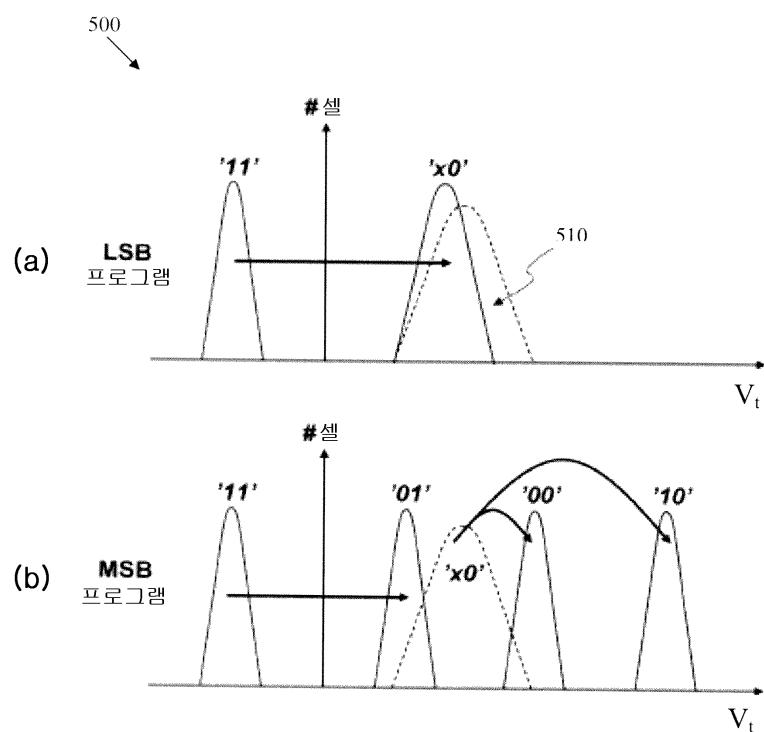

도 5(a) 및 도 5(b)는 집합적으로, 이웃하는 셀에 부과되는 ICI를 감소시키는 대안적인 MLC 프로그래밍 체계를 도시하는 도면.

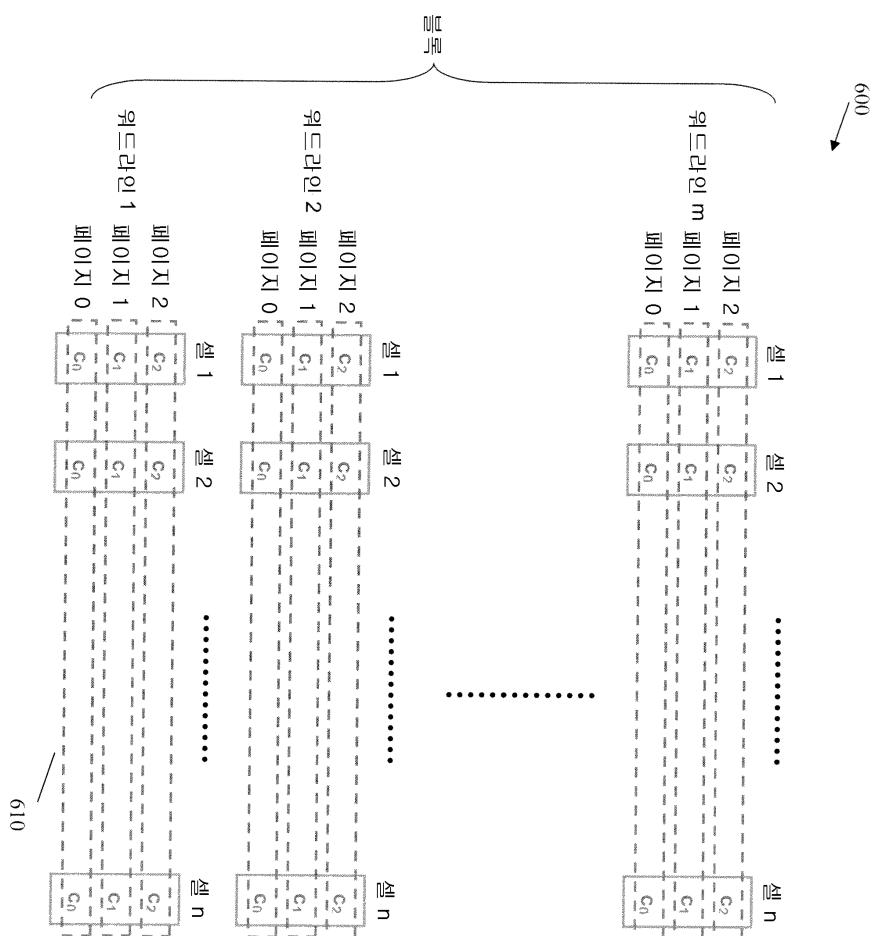

도 6은 다중 레벨 셀(MLC) 플래시 메모리 디바이스 내의 예시적인 플래시 셀 어레이를 더 상세히 도시하는 도면.

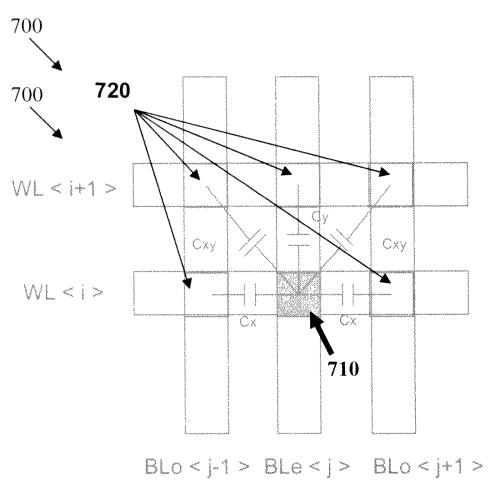

도 7은 다수의 예시적인 공격자 셀로부터의 기생 캐페시턴스에 기인하여 타겟 셀에 대해 존재하는 ICI를 도시하는 도면.

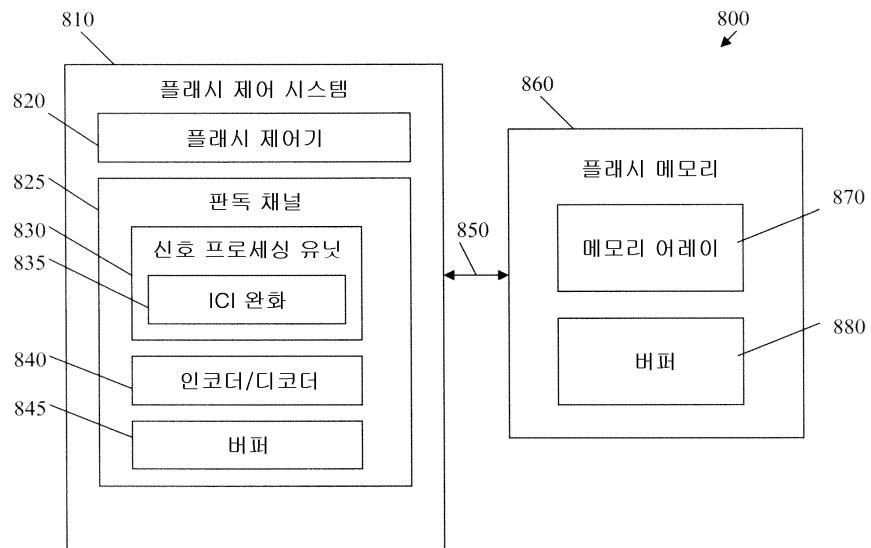

도 8은 본 발명에 따른 제어기 기반 ICI 완화 기술을 통합하는 예시적인 플래시 메모리 시스템의 개략 블록 다이어그램.

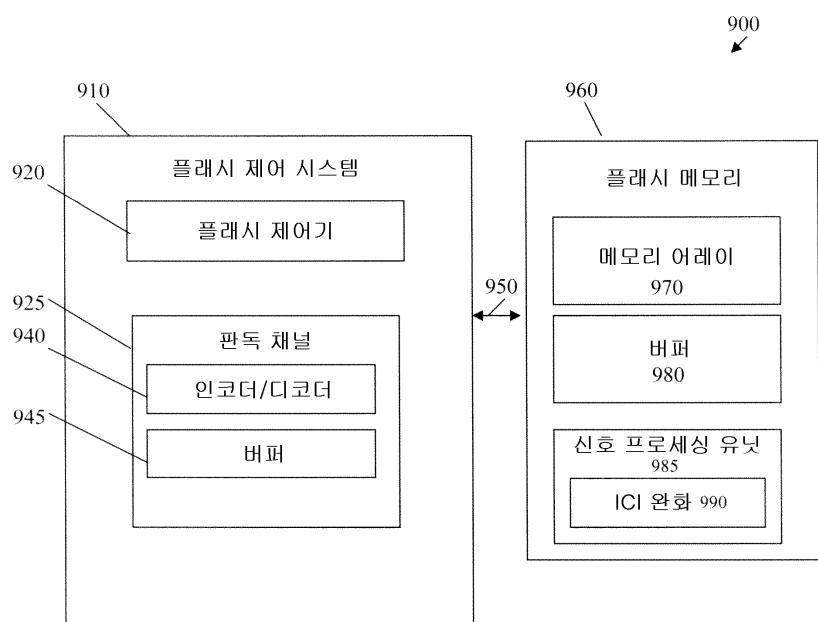

도 9는 본 발명의 대안 실시예에 따른 메모리 기반 ICI 완화 기술을 통합하는 예시적인 플래시 메모리 시스템의 개략 블록 다이어그램.

도 10은 본 발명에 따른 기록 액세스를 위한 관련 과정을 도시하는 도면.

도 11은 본 발명에 따른 관독 액세스를 위한 관련 과정을 도시하는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0014] 본 발명은 플래시 메모리 제어기와 플래시 메모리 어레이 사이의 개량된 인터페이스를 제공한다. 개시된 인터페이스는 전력 소산 또는 표면적을 상당히 증가시키지 않고 전송된 데이터에 대한 추가의 정보에 대한 추가의 대역폭을 제공한다. 본 발명은 추가의 전송된 정보가 예를 들어 전송된 타겟 셀 데이터에 관련된 하나 이상의 인접 셀의 값 또는 전송된 데이터에 대한 소프트 정보를 포함하는 ICI 완화와 관련하여 예시되지만, 본 발명은 당 기술 분야의 숙련자에게 명백할 수 있는 바와 같이, 마찬가지로 다른 용례를 위한 추가의 정보를 전달하기 위해 적용될 수 있다. 본 발명의 일 양태에 따르면, 데이터는 클럭 신호의 제1 에지(상승 에지와 같은) 상에 전달되고, 전달된 데이터에 대한 추가의 정보는 클럭 신호의 제2 에지(하강 에지와 같은) 상에 전달된다.

[0015] 본 발명의 다양한 양태는 단일 레벨 셀 또는 다중 레벨 셀(MLC) NAND 플래시 메모리 디바이스와 같은 메모리 디바이스 내의 ICI를 완화하기 위한 신호 프로세싱 기술에 관한 것이다. 본 명세서에 사용될 때, 다중 레벨 셀 플래시 메모리는 각각의 메모리 셀이 2개 이상의 비트를 저장하는 메모리를 포함한다. 통상적으로, 하나의 플래시 셀 내에 저장된 다중 비트는 상이한 페이지에 속한다. 본 발명은 전압으로서 아날로그 값을 저장하는 메모리 셀을 사용하여 본 명세서에 예시되어 있지만, 본 발명은 당 기술 분야의 숙련자에게 명백할 수 있는 바와 같이, 저장된 데이터를 표현하기 위해 전압 또는 전류의 사용과 같은 플래시 메모리에 대한 임의의 저장 메커니즘과 함께 이용될 수 있다.

[0016] 도 1은 통상의 플래시 메모리 시스템(100)의 개략 블록 다이어그램이다. 도 1에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(100)은 플래시 제어 시스템(110) 및 플래시 메모리 블록(160)을 포함한다. 예시적인 플래시 제어 시스템(110)은 플래시 제어기(120), 인코더/디코더 블록(140) 및 하나 이상의 베폐(145)를 포함한다.

대안 실시예에서, 인코더/디코더 블록(140) 및 몇몇 버퍼(145)는 플래시 제어기(120) 내부에 구현될 수 있다. 인코더/디코더 블록(140) 및 버퍼(145)는 예를 들어 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 구현될 수 있다.

[0017] 예시적인 플래시 메모리 블록(160)은 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 각각 구현될 수 있는 메모리 어레이(170) 및 하나 이상의 버퍼(180)를 포함한다. 메모리 어레이(170)는 NAND 플래시 메모리, 상 변화 메모리(PCM), MRAM 메모리, NOR 플래시 메모리 또는 다른 비휘발성 플래시 메모리와 같은 단일 레벨 또는 다중 레벨 셀 플래시 메모리로서 실시될 수도 있다. 본 발명은 다중 레벨 셀 NAND 플래시 메모리와 관련하여 주로 예시되지만, 본 발명은 당 기술 분야의 숙련자에게 명백할 수 있는 바와 같이, 단일 레벨 셀 플래시 메모리 및 다른 비휘발성 메모리에 마찬가지로 적용될 수 있다.

#### 다중 레벨 셀 플래시 메모리

[0019] 다중 레벨 셀 NAND 플래시 메모리에서, 임계치 검출기는 통상적으로 특정 셀과 관련된 전압값을 사전 정의된 메모리 상태로 변환하도록 이용된다. 도 2는 본 명세서에 참조로서 포함되어 있는 미국 특허 제 6,522,580호의 교시에 기초하여 도 1의 예시적인 다중 레벨 셀 플래시 메모리(170)에 대한 예시적인 임계 전압 분포를 도시한다. 일반적으로, 셀의 임계 전압은 셀이 특정량의 전류를 전도하도록 셀에 인가될 필요가 있는 전압이다. 임계 전압은 셀 내에 저장된 데이터에 대한 척도이다.

[0020] 도 2에 도시된 예시적인 실시예에서, 각각의 저장 소자(storage element)는 각각의 메모리 셀 내에 2개의 비트의 데이터를 저장하기 위해 4개의 가능한 데이터 상태를 이용한다. 도 2는 각각의 피크가 하나의 상태에 대응하는 4개의 피크(210 내지 213)를 도시한다. 다중 레벨 셀 플래시 디바이스에서, 임계 전압 분포 그래프(200)의 상이한 피크(210 내지 213)는 셀 내에 2개의 비트를 저장하기 위해 사용된다.

[0021] 임계 전압 분포 그래프(200)의 피크(210 내지 213)는 대응하는 2진값으로 라벨링되어 있다. 따라서, 셀이 제 1 상태(210)에 있을 때, 이는 하위 비트[또한 최하위 비트(LSB)라 알려짐]에 대해 "1"을 상위 비트[또한 최상위 비트(MSB)라 알려짐]에 대해 "1"을 표현한다. 상태(210)는 일반적으로 셀의 초기의 비프로그래밍된 또는 소거된 상태이다. 마찬가지로, 셀이 제 2 상태(211)에 있을 때, 이는 하위 비트에 대해 "0"을, 상위 비트에 대해 "1"을 표현한다. 셀이 제 3 상태(212)에 있을 때, 이는 하위 비트에 대해 "0"을, 상위 비트에 대해 "0"을 표현한다. 마지막으로, 셀이 제 4 상태(213)에 있을 때, 이는 하위 비트에 대해 "1"을, 상위 비트에 대해 "0"을 표현한다.

[0022] 임계 전압 분포(210)는 0 볼트 미만의 네거티브 임계 전압 레벨을 갖는 소거된 상태("11" 데이터 상태)에 있는 어레이 내의 셀의 임계 전압( $V_t$ )의 분포를 표현한다. "10" 및 "00" 사용자 데이터를 각각 저장하는 메모리 셀의 임계 전압 분포(211, 212)는 각각 0 내지 1 볼트와 1 내지 2 볼트에 있는 것으로 도시되어 있다. 임계 전압 분포(213)는 판독 대역 전압의 2 내지 4.5 볼트 사이의 임계 전압 레벨 세트를 갖고 "01" 데이터로 프로그래밍되어 있는 셀의 분포를 나타낸다.

[0023] 따라서, 도 2의 예시적인 실시예에서, 0 볼트, 1 볼트 및 2 볼트는 각각의 레벨 또는 상태 사이의 전압 레벨 임계치로서 사용될 수 있다. 전압 레벨 임계치는 소정의 셀의 상태 또는 전압 레벨을 결정하기 위해 플래시 메모리(160)[예를 들어, 플래시 메모리(160) 내의 감지 회로]에 의해 사용된다. 플래시 메모리(160)는 전압 레벨 임계치에 대한 측정된 전압의 비교에 기초하여 각각의 셀에 하나 이상의 비트를 할당할 수 있고, 이를 비트는 이어서 플래시 제어 시스템(110)에 경판정으로서 전송된다. 추가로 또는 대안적으로, 소프트 정보를 사용하는 구현예에서, 플래시 메모리(160)는 측정된 전압 또는 측정된 전압의 정량화된 버전을 소프트 정보로서 플래시 제어 시스템(110)에 전송할 수 있고, 여기서 메모리 셀 내에 저장된 비트의 수보다 많은 수의 비트가 측정된 전압을 표현하는데 사용된다.

[0024] 셀은 통상적으로 잘 알려진 프로그램/검증 기술을 사용하여 프로그래밍된다. 일반적으로, 프로그램/검증 사이클 중에, 플래시 메모리(160)는 최소 타겟 임계 전압이 초과될 때까지 셀 트랜지스터 내에 전하를 저장하기 위해 증가하는 전압을 점진적으로 인가한다. 예를 들어, 도 2의 예에서 '10' 데이터 상태를 프로그래밍할 때, 플래시 메모리(160)는 0.4 V의 최소 타겟 임계 전압이 초과될 때까지 셀 트랜지스터 내에 전하를 저장하기 위해 증가하는 전압을 점진적으로 인가할 수 있다.

[0025] 이하에 더 설명되는 바와 같이, 단일의 메모리 셀 내에 저장된 2개의 비트의 각각은 상이한 페이지로부터 온다. 달리 말하면, 각각의 메모리 셀 내에 저장된 2개의 비트의 각각의 비트는 상이한 페이지 어드레스를 전달한다. 도 2에 도시된 우측 비트는 하위 페이지 어드레스가 입력될 때 액세스된다. 좌측 비트는 상위 페이지 어드레스

가 입력될 때 액세스된다.

[0026] 도 3은 다중 레벨 셀(MLC) 플래시 메모리 디바이스(160) 내의 예시적인 플래시 셀 어레이(300)의 아키텍처를 도시하고, 여기서 각각의 예시적인 셀은 통상적으로 2개의 비트를 저장하는 부유 게이트 트랜지스터에 대응한다. 도 3에서, 각각의 셀은 2개의 비트가 속하는 2개의 페이지에 대한 2개의 수와 관련된다. 예시적인 셀 어레이 섹션(300)은 워드라인 n 내지 n+2 및 4개의 비트라인을 나타낸다. 예시적인 플래시 셀 어레이(300)는 짹수 및 홀수 페이지로 분할되고, 여기서 예를 들어 짹수(숫자 0 및 2를 갖는 셀과 같은)를 갖는 셀은 짹수 페이지에 대응하고, 홀수(숫자 1 및 3을 갖는 셀과 같은)를 갖는 셀은 홀수 페이지에 대응한다. 워드라인 n은 예를 들어 짹수 비트라인 내에 짹수 페이지 0 및 2를 저장하고, 홀수 비트라인 내에 홀수 페이지 1 및 3을 저장한다.

[0027] 게다가, 도 3은 짹수 또는 홀수 비트라인 셀이 선택되어 지시된 순서로 순차적으로(상향식) 프로그래밍되는 예시적인 프로그램 시퀀스를 지시한다. 숫자는 페이지가 프로그래밍되는 순서를 지시한다. 예를 들어, 페이지 0은 페이지 1 이전에 프로그램된다. 짹수 및 홀수 페이지의 프로그래밍의 추가의 설명을 위해, 예를 들어, 본 명세서에 참조로서 포함되어 있는 박기태(K. T. Park) 등의 "MLC NAND 플래시 메모리에 대한 일시적인 LSB 저장 및 별별 MSB 프로그램 체계를 갖는 제로화 셀간 간섭 페이지 아키텍처", IEEE Journal of Solid State Circuits, Vol. 43, No. 4, 919-928(2008년 4월)을 참조하라.

[0028] 도 4는 도 2의 전압 할당 체계에 대한 예시적인 2단 MLC 프로그래밍 체계(400)를 도시한다. 도 4에 도시된 바와 같이, LSB 프로그램 단계 중에, 소거된 상태(410)에 있는 선택된 셀의 상태는 LSB가 0이면 최하위 프로그래밍된 상태(411)로 이동한다. 따라서, LSB 프로그래밍 단계에서, 메모리 셀은 소거된 상태 '11'로부터 '10'으로 프로그래밍된다. 다음, MSB 프로그램 단계 중에, 상태 '00'(412) 및 상태 '01'(413)은 이전의 LSB 데이터에 따라 순차적으로 형성된다. 일반적으로, MSB 프로그래밍 단계 중에, '10' 상태는 '00'으로 프로그래밍되고, 상태 '11'은 '01'로 프로그래밍된다.

[0029] 도 4의 프로그래밍 체계(400)는 상태(410)로부터 상태(413)로의 상태의 변화와 관련된 최대 전압 시프트를 도시한다는 것이 주목된다. 다수의 프로그래밍 체계가 상태의 변화와 관련된 최대 전압 시프트를 감소시키고, 이에 의해 전압 시프트에 의해 발생된 ICI를 감소시키기 위해 제안되거나 제의되어 왔다.

[0030] 도 5(a) 및 도 5(b)는 집합적으로 이웃하는 셀 상에 부과된 ICI를 감소시키는 대안적인 MLC 프로그래밍 체계(500)를 도시한다. 도 5(a)에 도시된 바와 같이, LSB 프로그래밍 단계 중에, 메모리 셀은 SLC 프로그래밍과 유사한 방식으로 상태 '11'로부터 일시적인(또는 중간) 상태로서 상태 'x0'으로 프로그래밍된다. 동일한 워드라인 내의 이웃 셀이 또한 LSB 프로그래밍된 후에, ICI에 기인하여 도 5(a)의 퍼크(510)에 의해 도시된 바와 같이 분배가 가능하게는 확장된다. 그 후에, 도 5(b)에 도시된 MSB 프로그래밍 스테이지에서, 'x0' 상태는 입력 데이터 또는 다른 것에 대응하는 최종 데이터로서 '00' 및 '10'으로 프로그래밍되고, '11' 상태는 최종 '01' 상태로 프로그래밍된다. 일반적으로, '11' 셀을 제외한 모든 메모리 셀은 이웃하는 셀에 의해 발생되는 ICI가 상당히 감소될 수 있도록 LSB 데이터에 대한 일시적인 프로그래밍된 상태로부터 MSB 프로그래밍 상태에서 그 최종 상태로 재프로그래밍된다. 최종 상태의 셀은 최종 상태로 재프로그래밍되어 있기 때문에, 중간 상태에 있는 동안 경험되는 ICI를 겪지 않게 될 수 있다. 최종 상태의 셀은 단지 최종 상태에 있는 후에 경험된 ICI만을 겪게 될 수 있다. 전술된 바와 같이, 도 5(a) 및 도 5(b)의 다단계 프로그래밍 시퀀스는, 중간 프로그램 상태를 사용하여, 최대 전압 변화 및 따라서 이를 전압 변화에 의해 발생된 ICI를 감소시킨다. 예를 들어 MSB 프로그래밍 단계 중의 최대 전압 시프트는 각각 상태 '11'로부터 '01'로, 그리고 상태 'x0'으로부터 '10'으로의 전이와 관련된다는 것을 도 5에서 알 수 있다. 이를 전압 시프트는 도 4의 상태 '11'로부터 '01'로의 최대 전압 시프트보다 상당히 작다.

[0031] 도 6은 다중 레벨 셀(MLC) 플래시 메모리 디바이스(130) 내의 예시적인 플래시 셀 어레이(600)를 더 상세히 도시한다. 도 6에 도시된 바와 같이, 플래시 셀 어레이(600)는 플래시 셀( $c_i$ )당 3개의 비트를 저장한다. 도 6은 하나의 블록에 대한 플래시 셀 어레이 아키텍처를 도시하고, 여기서 각각의 예시적인 셀은 통상적으로 3개의 비트를 저장하는 부유 게이트 트랜지스터에 대응한다. 예시적인 셀 어레이(600)는 m개의 워드라인 및 n개의 비트라인으로 이루어진다. 통상적으로, 현재의 다중 페이지 셀 플래시 메모리에서, 단일 셀 내의 비트는 상이한 페이지에 속한다. 도 6의 예에서, 각각의 셀에 대한 3개의 비트가 3개의 상이한 페이지에 대응하고, 각각의 워드라인은 3개의 페이지를 저장한다. 이하의 설명에서, 페이지 0, 1 및 2는 워드라인 내의 하위, 중간 및 상위 페이지 레벨이라 칭한다.

[0032] 전술된 바와 같이, 플래시 셀 어레이에는 짹수 및 홀수 페이지로 더 분할될 수 있고, 여기서 예를 들어 짹수를 갖는 셀(도 6의 셀 2 및 4와 같은)은 짹수 페이지에 대응하고 홀수를 갖는 셀(도 6의 셀 1 및 3과 같은)은 홀수

페이지에 대응한다. 이 경우에, 페이지(페이지 0과 같은)는 짹수 셀 내의 짹수 페이지(짜수 페이지 0) 및 홀수 셀 내의 홀수 페이지(홀수 페이지 0)를 포함할 수 있다.

#### [0033] 셀간 간섭

전술된 바와 같이, ICI는 셀들 사이의 기생 캐페시턴스의 결과이고, 일반적으로 가장 현저한 왜곡의 소스 중 하나로 고려된다. 도 7은 다수의 예시적인 공격자 셀(720)로부터의 기생 캐페시턴스에 기인하여 타겟 셀(710)에 대해 존재하는 ICI를 도시한다. 이하의 표기가 도 7에 이용되고 있다.

[0035] WL: 워드라인,

[0036] BL: 비트라인,

[0037] BLo: 홀수 비트라인

[0038] BLe: 짹수 비트라인, 및

[0039] C: 캐페시턴스.

[0040] 본 발명은 타겟 셀(710)이 프로그래밍된 후에 프로그래밍되는 공격자 셀(720)에 의해 ICI가 발생되는 것을 인식한다. ICI는 타겟 셀(710)의 전압( $V_t$ )을 변경한다. 예시적인 실시예에서, "상향식" 프로그래밍 체계가 취해지고 워드라인 i 및 i+1 내의 인접 공격자 셀이 타겟 셀(710)에 대한 ICI를 발생시킨다. 블록의 이러한 상향식 프로그래밍에 의해, 하위 워드라인 i-1로부터의 ICI가 제거되고, 최대 5개의 이웃하는 셀이 도 7에 도시된 바와 같이 공격자 셀(720)로서 ICI에 기여한다. 그러나, 본 명세서에 개시된 기술은 당 기술 분야의 숙련자에 명백 할 수 있는 바와 같이, 워드라인 i-1과 같은 다른 워드라인으로부터의 공격자 셀이 마찬가지로 ICI에 기여하는 경우에 보편화될 수 있다는 것이 주목된다. 워드라인 i-1, i 및 i+1로부터의 공격자 셀이 ICI에 기여하면, 최대 8개의 가장 근접한 이웃하는 셀이 고려될 필요가 있다. 타겟 셀로부터 멀리 이격된 다른 셀은 ICI에 대한 이들의 기여가 무시할 만하면, 무시될 수 있다. 일반적으로, 공격자 셀(720)은 소정의 타겟 셀(710) 이후에 프로그래밍되는 공격자 셀(720)을 식별하기 위해 프로그래밍 시퀀스 체계(상향식 또는 짹수/홀수 기술과 같은)를 분석함으로써 식별된다.

[0041] 타겟 셀(710) 상에 공격자 셀(720)에 의해 발생된 ICI는 예시적인 실시예에서 이하와 같이 모델링될 수 있는데,

$$\Delta V_{ICI}^{(i,j)} = k_x \Delta V_t^{(i,j-1)} + k_x \Delta V_t^{(i,j+1)} + k_y \Delta V_t^{(i+1,j)} + \\ k_{xy} \Delta V_t^{(i+1,j-1)} + k_{xy} \Delta V_t^{(i+1,j+1)} \quad (1)$$

[0042] 여기서,  $\Delta V_t^{(w,b)}$ 는 공격자 셀 (w,b)의  $V_t$  전압의 변화이고,  $\Delta V_{ICI}^{(i,j)}$ 는 ICI에 기인하는 타겟 셀(i,j)의  $V_t$  전압의 변화이고,  $k_x$ ,  $k_y$  및  $k_{xy}$ 는 x, y 및 xy 방향에 대한 용량성 커플링 계수이다.

[0044] 일반적으로,  $V_t$ 는 셀 상에 저장되고 판독 작업 중에 얻어진 데이터를 표현하는 전압이다.  $V_t$ 는 예를 들어 셀당 저장된 비트의 수보다 높은 정밀도를 갖는 소프트 전압값, 또는 셀당 저장된 비트의 수(예를 들어 3 비트/셀 플래시에 대해 3 비트)와 동일한 분해능을 갖는 하드 전압 레벨로 정량화된 값일 수 있다.

#### [0045] 시스템 레벨 고려

[0046] 도 8은 본 발명에 따른 제어기 기반 ICI 완화 기술을 통합하는 예시적인 플래시 메모리 시스템(800)의 개략 블록 다이어그램이다. 도 8에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(800)은 인터페이스(850)에 의해 접속된 플래시 제어 시스템(810) 및 플래시 메모리 블록(860)을 포함한다. 예시적인 플래시 제어 시스템(810)은 통상적으로 하나 이상의 집적 회로 상에 플래시 제어기(820) 및 판독 채널(825)을 포함한다. 예시적인 플래시 제어기(820)는 예를 들어 본 발명의 특징 및 기능을 지원하기 위해 본 명세서에서 수정된 바와 같이, 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 구현될 수 있다.

[0047] 예시적인 판독 채널(825)은 신호 프로세싱 유닛(830), 인코더/디코더 블록(840) 및 하나 이상의 버퍼(845)를 포함한다. 용어 "판독 채널"은 마찬가지로 기록 채널을 포함할 수 있다. 대안 실시예에서, 인코더/디코더 블록(840) 및 몇몇 버퍼(845)는 플래시 제어기(820) 내부에 구현될 수 있다. 인코더/디코더 블록(840) 및 버퍼(845)는 예를 들어 본 발명의 특징 및 기능을 제공하기 위해 본 명세서에서 수정되는 바와 같이 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 구현될 수 있다.

- [0048] 예시적인 신호 프로세싱 유닛(830)은 예를 들어 도 10 내지 도 12와 관련하여 이하에 더 설명되는 하나 이상의 ICI 완화 프로세스(835)를 구현하는 하나 이상의 프로세서를 포함한다. 게다가, 도 8에 도시된 다양한 블록 사이의 데이터 흐름은 또한 예를 들어 도 10 내지 도 12와 관련하여 이하에 더 설명된다. 일반적으로, 도 11 및 도 12와 관련하여 이하에 더 설명되는 바와 같이, 판독 작업 중에 ICI 완화를 수행하기 위해, 하나 이상의 ICI 완화 프로세스(835)는 하드 또는 소프트 판독값에 기초하여 새로운 판독값을 컴퓨팅한다. 마찬가지로, 도 10과 관련하여 이하에 더 설명되는 바와 같이, 기록 작업 중에 ICI 완화를 수행하기 위해, 하나 이상의 ICI 완화 프로세스(835)는 타겟 및 공격자 셀에 대한 프로그램 데이터에 기초하여 메모리 어레이(870) 내에 저장될 사전 보상된 프로그램 값을 생성한다.

- [0049] 예시적인 플래시 메모리 블록(860)은 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 각각 구현될 수 있는 메모리 어레이(870) 및 하나 이상의 버퍼(880)를 포함한다.

- [0050] 도 10 및 도 11과 관련하여 이하에 더 설명되는 본 발명의 일 양태에 따르면, 예시적인 인터페이스(850)는 공격자 셀과 관련된 정보를 표현하는 값과 같은 통상의 플래시 메모리 시스템에 대한 추가의 정보를 전달할 필요가 있을 수 있다. 따라서, 인터페이스(850)는 통상의 플래시 메모리 시스템의 인터페이스보다 높은 용량(예를 들어, 더 많은 입력 또는 출력 핀) 또는 빠른 레이트를 가질 필요가 있을 수 있다.

- [0051] 기록 작업 중에, 인터페이스(850)는 통상적으로 페이지 또는 워드라인 레벨 액세스 기술을 사용하여 타겟 셀 내에 저장될 사전 보상된 프로그램 값을 전달한다. 예시적인 페이지 또는 워드라인 레벨 액세스 기술의 더 상세한 설명을 위해, 예를 들어 본 명세서에 참조로서 포함되어 있는 2009년 3월 11일 출원된 발명의 명칭이 "페이지간 셱터, 다중 페이지 코딩 및 페이지당 코딩을 갖는 다중 레벨 셀 플래시 메모리 디바이스 내에 데이터를 저장하기 위한 방법 및 장치"인 국제 특허 출원 제 PCT/US09/36810호를 참조하라. 통상적으로, 사전 보상된 프로그램 값의 수는 통상적으로 원래 프로그램 값의 수보다 크기 때문에, 원래 프로그램 값을 표현하기 위한 것보다 많은 비트가 사전 보상된 프로그램 값을 표현하기 위해 요구된다. 따라서, 기록측 ICI 완화를 위해, 인터페이스(850)는 통상의 인터페이스보다 많은 데이터를 전달할 필요가 있다.

- [0052] 판독 작업 중에, 인터페이스(850)는 타겟 및 공격자 셀에 대해 메모리 어레이(870)로부터 얻어지고 있는 하드 및/또는 소프트 판독값을 전달한다. 예를 들어, 타겟 셀을 갖는 페이지에 대한 판독값에 추가하여, 상위/하위 워드라인 또는 이웃하는 짹수 또는 홀수 비트라인 내의 하나 이상의 인접 페이지에 대한 판독값은 인터페이스 버스를 통해 전달된다.

- [0053] 도 8의 실시예에서, 개시된 기록측 또는 판독측 ICI 완화 기술은 통상적으로 최하위 영역을 성취하기 위해 논리 회로에 대해 최적화된 프로세스 기술에서 플래시 메모리 외부에서 구현된다. 그러나, 이는 인터페이스(850) 상에 전달되어야 하는 추가의 공격자 셀 데이터의 희생이다.

- [0054] 도 9는 본 발명의 대안 실시예에 따른 메모리 기반 ICI 완화 기술을 통합하는 예시적인 플래시 메모리 시스템(900)의 개략 블록 다이어그램이다. 도 9에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(900)은 인터페이스(950)에 의해 접속된 플래시 제어 시스템(910) 및 플래시 메모리 블록(960)을 포함한다. 예시적인 플래시 제어 시스템(910)은 통상적으로 하나 이상의 접속 회로 상에 플래시 제어기(920) 및 선택적 판독 채널(925)을 포함한다. 예시적인 판독 채널(925)은 인코더/디코더 블록(940) 및 하나 이상의 버퍼(945)를 포함한다. 대안 실시예에서, 인코더/디코더 블록(940) 및 몇몇 버퍼(945)는 플래시 제어기(920) 내부에 구현될 수 있다. 예시적인 플래시 제어기(920)는 예를 들어 본 발명의 특징 및 기능을 지원하기 위해 본 명세서에서 수정된 바와 같은 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 구현될 수 있다. 인코더/디코더 블록(940) 및 버퍼(945)는 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 구현될 수 있다.

- [0055] 예시적인 플래시 메모리 블록(960)은 잘 알려진 상업적으로 입수 가능한 기술 및/또는 제품을 사용하여 각각 구현될 수 있는 메모리 어레이(970) 및 하나 이상의 버퍼(980)를 포함한다. 게다가, 예시적인 플래시 메모리 블록(960)은 하나 이상의 ICI 완화 프로세스(990)를 구현하는 하나 이상의 프로세서를 포함하는 예시적인 신호 프로세싱 유닛(985)을 포함한다. 일반적으로, 판독 작업 중에 ICI 완화를 수행하기 위해, 하나 이상의 ICI 완화 프로세스(990)가 메모리 어레이(970)로부터 판독된 하드 또는 소프트 판독값에 기초하여 새로운 판독값을 컴퓨팅한다. 마찬가지로, 기록 작업 중에 ICI 완화를 수행하기 위해, 하나 이상의 ICI 완화 프로세스(990)는 타겟 및 공격자 셀에 대해 플래시 제어기(910)로부터 검색된 프로그램 데이터에 기초하여 사전 보상된 프로그램 값을 생성한다.

- [0056] 도 10 및 도 11과 관련하여 이하에 더 설명되는 본 발명의 일 양태에 따르면, 예시적인 인터페이스(950)는 공격

자 셀과 관련된 정보를 표현하는 값과 같은 통상의 플래시 메모리 시스템에 대한 추가의 정보를 전달할 필요가 있을 수 있다. 따라서, 인터페이스(950)는 통상의 플래시 메모리 시스템의 인터페이스보다 높은 용량(예를 들어, 더 많은 입력 또는 출력 편) 또는 빠른 레이트를 가질 필요가 있다.

[0057] 기록 작업 중에, 인터페이스(950)는 타겟 및 공격자 셀 내에 저장될 프로그램 데이터를 전달하고, 사전 보상된 프로그램 값이 플래시 메모리(960) 내부에서 컴퓨팅된다. 인터페이스(950)는 예를 들어 통상의 플래시 메모리 시스템에서와 같이 타겟 셀을 갖는 페이지에 대해 프로그램 데이터를, 게다가 공격자 셀을 갖는 인접 워드라인 또는 짹수 또는 홀수 비트 라인에 대해 프로그램 데이터를 전달할 수 있다. 통상적으로, 사전 보상된 프로그램 값을 표현하기 위한 것보다 적은 비트가 이 프로그램 데이터를 표현하는데 요구된다. 따라서, 기록측 ICI 완화에 대해, 인터페이스(950)는 통상적으로 인터페이스(850)보다 적은 대역폭을 필요로 할 수 있다. 그러나, 이는 통상적으로 논리 회로가 아니라 메모리에 대해 최적화되는 플래시 메모리를 제조하는데 사용된 메모리 프로세스 기술을 사용하여 메모리 내부에서 기록측 ICI 완화 프로세스를 구현하는 것을 희생한다.

[0058] 관독 작업 중에, 인터페이스(950)는 타겟 셀(들) 및 선택적으로 공격자 셀에 대해 ICI 완화 프로세스(990)에 의해 컴퓨팅되었던 새로운 하드 또는 소프트 관독값 또는 데이터를 전달한다. 통상적으로, 단일 관독 액세스에 대해 전달된 정보는 데이터의 페이지 또는 워드라인이다. 통상적으로 논리 회로가 아니라 메모리에 대해 최적화된 플래시 메모리를 제조하는데 사용된 메모리 프로세스 기술을 사용하여 메모리 내부에 관독측 ICI 완화 프로세스를 구현하는 것을 희생시켜, 타겟 셀에 대한 송신 데이터만이 인터페이스(950)의 대역폭 요건을 감소시킨다는 것이 주목된다.

[0059] 도 8 및 도 9의 ICI 완화 기술의 다양한 실시예에서 이용된 용량성 커플링 계수( $k_x$ ,  $k_y$  및  $k_{xy}$ )는 플래시 제어 시스템(810, 910) 및/또는 플래시 메모리 블록(860, 960)에서 컴퓨팅될 수 있다는 것이 주목된다. 용량성 커플링 계수( $k_x$ ,  $k_y$  및  $k_{xy}$ )가 각각의 인터페이스(850, 950)에 전달될 필요가 있을 수 있다. 용량성 커플링 계수는 적응성일 수 있고, 연속적인 임시의 또는 주기적인 기초로 업데이트될 수 있다는 것이 주목된다.

[0060] 예시적인 ICI 완화 프로세스(835, 990)의 더 상세한 설명을 위해, 예를 들어 본 출원과 동일자로 각각 출원되어 본 명세서에 참조로서 포함되어 있는 발명의 명칭이 "플래시 메모리 내의 기록측 셀간 간접 완화 방법 및 장치(Methods and Apparatus for Write-Side Intercell Interference Mitigation in Flash Memories)"인 PCT 특허 출원 제\_\_\_\_호 및 발명의 명칭이 "플래시 메모리 내의 관독측 셀간 간접 완화 방법 및 장치(Methods and Apparatus for Read-Side Intercell Interference Mitigation in Flash Memories)"인 PCT 특허 출원 제\_\_\_\_호를 참조하라.

#### 개량된 인터페이스(850, 950)

[0062] 전술된 바와 같이, 본 발명은 플래시 메모리 제어기(820, 920)와 플래시 메모리 어레이(870, 970) 사이에 개량된 인터페이스(850, 950)를 제공한다. 본 발명의 일 양태에 따르면, 타겟 셀(710)에 대한 데이터는 클럭 신호의 제 1 에지(상승 에지와 같은) 상에 전달되고, 전달된 데이터에 대한 추가의 정보가 클럭 신호의 제 2 에지(하강 에지와 같은) 상에 전송된다. 개시된 인터페이스는 상당히 증가하는 전력 소산 또는 표면적 없이 전송된 데이터에 대한 추가의 정보를 위한 추가의 대역폭을 제공한다.

[0063] 일반적으로, 인터페이스(850, 950)는 예를 들어 본 발명의 특징 및 기능을 제공하도록 본 명세서에서 수정된 바와 같이, 본 명세서에 참조로서 포함되어 있는 ONFI 2.0 표준에 따라 구현될 수 있다. 이 방식으로 동일한 인터페이스(850, 950)가 소프트 데이터를 프로세싱하고 추가의 기록 데이터를 송신하는 능력 없이 레가시 플래시 제어기(820, 920)에 대해 사용될 수 있다. 레가시 플래시 제어기(820, 920)는 본 발명에 따라 하강 에지에 전송되는 추가의 데이터를 무시할 수 있다.

[0064] 전술된 바와 같이, ONFI 버전 2.0은 클럭 신호의 상승 및 하강 에지의 모두에 데이터를 전달하기 위해 더블 데이터 레이트(DDR) 기술을 사용한다. ONFI 버전 2.0은 NAND 플래시 인터페이스의 데이터 전달 용량을 증가시키지만, 성능을 개량할 수 있는 추가의 정보를 전달하기 위한 추가의 대역폭을 제공하지 않는다. 일 예시적인 실시예에서, 타겟 셀(710)을 위한 데이터는 클럭 신호의 제 1 에지(상승 에지와 같은) 상에 전달되고, 소프트 관독 데이터 및 인접 기록 데이터와 같은 전달된 데이터에 대한 추가의 정보는 클럭 신호의 제 2 에지(하강 에지와 같은) 상에 전달된다.

#### A. 기록 액세스

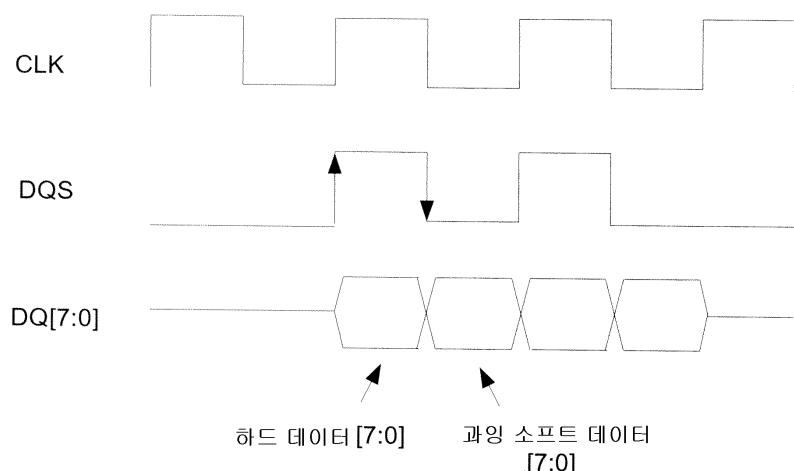

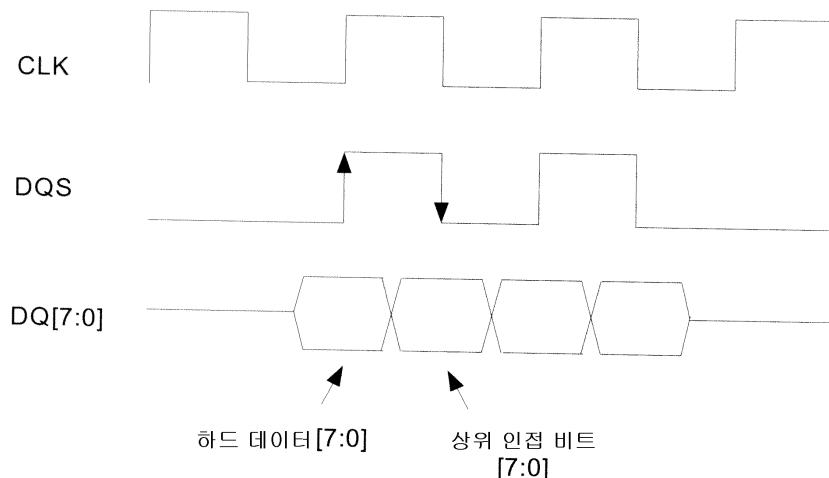

[0066] 도 10은 본 발명에 따른 기록 액세스를 위한 관련 과정을 도시한다. 도 10에 도시된 바와 같이, 플래시 메모리

의 DQ 버스 상의 데이터는 CLK 신호 또는 DQS(스트로브) 신호 또는 양자 모두를 사용하여 통상적으로 클럭킹된다. 일반적으로, DQS 신호가 가능화될 때, DQS 신호는 CLK 신호의 각각의 상승 에지 및 하강 에지에 각각 대응하는 상승 에지 및 하강 에지를 갖는다.

[0067] ONFI 버전 2.0은 클럭 신호의 상승 및 하강 에지의 모두에 데이터를 전달한다. 본 발명은 CLK 신호의 제 1 에지(상승 에지와 같은) 상의 타겟 셀(710)에 대한 데이터를 전달하고, 타겟 셀(710)에 대한 전달된 데이터에 대한 추가의 정보는 CLK 신호의 제 2 에지(하강 에지와 같은) 상에 전달된다. 기록 액세스에서, 하강 에지 상의 증가된 대역폭은 플래시 메모리 제어기(820, 920)로부터 플래시 메모리 어레이(870, 970)로 각각 추가의 정보(공격자 데이터 정보와 같은)를 전달하는데 사용될 수 있다. 일 예시적인 용례에서, 개량된 인터페이스(850, 950)는 ICI 완화를 위한 타겟 셀(710)의 공격자 셀(720)에 대한 정보의 전달을 가능하게 하는 추가의 대역폭을 제공한다. 예를 들어, CLK(또는 DQS) 신호의 하강 에지 상에 래치된 데이터는 타겟 셀(710)에 대한 상위 인접 비트를 전달할 수 있고, 이는 셀간 간섭을 완화하기 위해 프로그래밍된 전압을 조정하도록 ICI 완화 프로세스(835, 990)에 의해 사용될 수 있다.

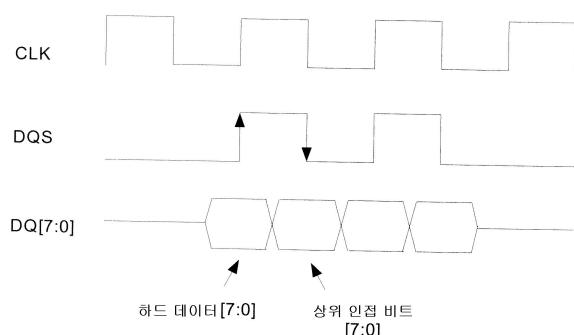

#### [0068] B. 판독 액세스

[0069] 도 11은 본 발명에 따른 판독 액세스를 위한 관련 과정을 도시한다. 도 11에 도시된 바와 같이, 플래시 메모리의 DQ 버스 상의 데이터는 CLK 신호 또는 DQS(스트로브) 신호 또는 양자 모두를 사용하여 통상적으로 클럭킹된다. 일반적으로, DQS 신호가 가능화될 때, DQS 신호는 CLK 신호의 각각의 상승 에지 및 하강 에지에 각각 대응하는 상승 에지 및 하강 에지를 갖는다.

[0070] ONFI 버전 2.0은 클럭 신호의 상승 및 하강 에지의 모두에 데이터를 전달한다. 본 발명은 CLK 신호의 제 1 에지(상승 에지와 같은) 상의 타겟 셀(710)에 대한 데이터를 전달하고, 타겟 셀(710)에 대한 전달된 데이터에 대한 추가의 정보는 CLK 신호의 제 2 에지(하강 에지와 같은) 상에 전달된다. 판독 액세스에서, 하강 에지 상의 증가된 대역폭은 상승 에지 상에 전달되었던 타겟 셀(710)에 대한 하드 데이터와 관련된 타겟 셀(710)에 대한 소프트 데이터(예를 들어, 확률 정보)를 전달하는데 사용될 수 있다. 전달은 플래시 메모리 어레이(870, 970)로부터 플래시 메모리 제어기(820, 920)로 각각 이루어진다. 일 예시적인 용례에서, 개량된 인터페이스(850, 950)는 ICI 완화를 위한 타겟 셀(710)의 소프트 정보의 전달을 가능하게 하는 추가의 대역폭을 제공한다. 예를 들어, CLK(또는 DQS) 신호의 하강 에지 상에 래치된 데이터는 타겟 셀(710)에 대한 소프트 데이터를 전달할 수 있고, 이는 개량된 에러 보정 및 셀간 간섭 완화를 위해 ICI 완화 프로세스(835, 990)에 의해 사용될 수 있다.

#### [0071] 프로세스, 시스템 및 제조 물품 상세

[0072] 본 명세서의 다수의 흐름도는 예시적인 단계의 순서를 설명하지만, 순서가 변경될 수 있는 것도 또한 본 발명의 실시예이다. 알고리즘의 다양한 치환은 본 발명의 대안 실시예로서 구현된다. 본 발명의 예시적인 실시예는 소프트웨어 프로그램 내의 프로세싱 단계에 대해 설명되었지만, 다양한 기능이 소프트웨어 프로그램 내의, 회로 소자 또는 상태 머신에 의해 하드웨어 내의, 또는 소프트웨어 및 하드웨어의 모두의 조합 내의 프로세싱 단계로서 디지털 도메인에서 구현될 수 있다. 이러한 소프트웨어는 예를 들어 디지털 신호 프로세서, 응용 특정 집적 회로, 마이크로 제어기 또는 범용 컴퓨터에서 구체화될 수 있다. 이러한 하드웨어 및 소프트웨어는 집적 회로 내에 구현된 회로 내에서 구체화될 수 있다.

[0073] 따라서, 본 발명의 기능은 이를 방법을 실시하기 위한 방법 및 장치의 형태로 구체화될 수 있다. 본 발명의 하나 이상의 양태는 예를 들어 저장 매체 내에 저장되고, 머신 내에 로딩되고 그리고/또는 머신에 의해 실행되거나 몇몇 전송 매체를 통해 전송되건간에 프로그램 코드의 형태로 구체화될 수 있고, 여기서 프로그램 코드가 컴퓨터와 같은 머신 내에 로딩되어 실행될 때, 머신은 본 발명을 실시하기 위한 장치가 된다. 범용 프로세서 상에서 구현될 때, 프로그램 코드 세그먼트는 프로세서와 조합하여 특정 논리 회로와 유사하게 작동하는 디바이스를 제공한다. 본 발명은 또한 집적 회로, 디지털 신호 프로세서, 마이크로프로세서 및 마이크로 제어기 중 하나 이상으로 구현될 수 있다.

[0074] 당 기술 분야에 공지된 바와 같이, 본 명세서에 설명된 방법 및 장치는 그에 구체화된 컴퓨터 판독 가능 코드 수단을 갖는 컴퓨터 판독 가능 매체를 자체로 포함하는 제조 물품으로서 분배될 수 있다. 컴퓨터 판독 가능 프로그램 코드 수단은 컴퓨터 시스템과 함께, 본 명세서에 설명된 방법을 수행하거나 장치를 생성하기 위한 단계의 전체 또는 일부를 수행하도록 작동 가능하다. 컴퓨터 판독 가능 매체는 판독 가능 매체[예를 들어, 플로피 디스크, 하드 드라이브, 컴팩트 디스크, 메모리 카드, 반도체 디바이스, 칩, 응용 특정 집적 회로(ASIC)]일 수 있고, 또는 전송 매체(예를 들어, 시간 분할 다중 접속, 코드 분할 다중 접속 또는 다른 무선 주파수 채널을 사

용하는 광 파이버, 월드와이드 웹, 케이블 또는 무선 채널을 포함하는 네트워크)일 수 있다. 컴퓨터 시스템과 함께 사용을 위해 적합한 정보를 저장할 수 있는 것으로 공지되거나 개발된 임의의 매체가 사용될 수 있다. 컴퓨터 판독 가능 코드 수단은 자기 매체 상의 자기 편차 또는 컴팩트 디스크의 표면 상의 높이 편차와 같은 명령 및 데이터를 컴퓨터가 판독하는 것을 가능하게 하기 위한 임의의 메커니즘이다.

[0075] 본 명세서에 설명된 컴퓨터 시스템 및 서버는 본 명세서에 개시된 방법, 단계 및 기능을 구현하기 위한 관련 프로세서를 구성할 수 있는 메모리를 각각 포함한다. 메모리는 분배형 또는 로컬형일 수 있고, 프로세서는 분배형 또는 단일형일 수 있다. 메모리는 전기, 자기 또는 광학 메모리, 또는 이를 또는 다른 유형의 저장 디바이스의 임의의 조합으로서 구현될 수 있다. 더욱이, 용어 "메모리"는 관련 프로세서에 의해 액세싱되는 어드레스 가능한 공간 내의 어드레스로부터 판독되거나 그에 기록될 수 있는 임의의 정보를 포함하는데 충분히 광범위하게 해석되어야 한다. 이 정의에서, 네트워크 상의 정보는 관련 프로세서가 네트워크로부터 정보를 검색할 수 있기 때문에 메모리 내에 여전히 있다.

[0076] 본 명세서에 도시되고 설명된 실시예 및 변형에는 단지 본 발명의 원리의 예시이며 다양한 수정이 본 발명의 사상 및 범주로부터 벗어나지 않고 당 기술 분야의 숙련자들에 의해 구현될 수 있다는 것이 이해되어야 한다.

### 부호의 설명

|                  |                  |

|------------------|------------------|

| 100: 플래시 메모리 시스템 | 110: 제어 시스템      |

| 120: 플래시 제어기     | 140: 인코더/디코더 블록  |

| 145: 버퍼          | 160: 플래시 메모리 블록  |

| 170: 메모리 어레이     | 180: 버퍼          |

| 600: 플래시 셀 어레이   | 710: 타겟 셀        |

| 720: 공격자 셀       | 800: 플래시 메모리 시스템 |

| 810: 제어 시스템      | 820: 플래시 제어기     |

| 825: 판독 채널       | 830: 신호 프로세싱 유닛  |

| 840: 인코더/디코더 블록  | 845: 버퍼          |

| 860: 메모리 블록      | 870: 메모리 어레이     |

| 880: 버퍼          | 900: 플래시 메모리 시스템 |

| 910: 플래시 제어 시스템  | 920: 플래시 제어기     |

| 925: 판독 채널       | 940: 인코더/디코더 블록  |

| 945: 버퍼          | 960: 플래시 메모리 블록  |

| 970: 메모리 어레이     | 985: 신호 프로세싱 유닛  |

**도면****도면1****도면2****도면3**

## 도면4

## 도면5

도면6

도면7

## 도면8

## 도면9

**도면10****도면11**