(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5980538号

(P5980538)

(45) 発行日 平成28年8月31日(2016.8.31)

(24) 登録日 平成28年8月5日(2016.8.5)

(51) Int.Cl.

F 1

|                     |                  |             |              |               |

|---------------------|------------------|-------------|--------------|---------------|

| <b>H03K 3/354</b>   | <b>(2006.01)</b> | <b>H03K</b> | <b>3/354</b> | <b>Z NMB</b>  |

| <b>H01L 21/8234</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/08</b> | <b>1 O2 E</b> |

| <b>H01L 27/088</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/08</b> | <b>3 31 E</b> |

| <b>H01L 27/08</b>   | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> | <b>6 13 Z</b> |

| <b>H01L 29/786</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> | <b>6 18 B</b> |

請求項の数 4 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2012-78007(P2012-78007)

(22) 出願日

平成24年3月29日(2012.3.29)

(65) 公開番号

特開2013-207771(P2013-207771A)

(43) 公開日

平成25年10月7日(2013.10.7)

審査請求日

平成27年3月24日(2015.3.24)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 米田 誠一

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のインバータと、第2のインバータと、第1のトランジスタと、第2のトランジスタと、第1の容量素子と、第2の容量素子と、を有し、

前記第1のインバータは、第3のトランジスタと、第4のトランジスタと、を有し、

前記第2のインバータは、第5のトランジスタと、第6のトランジスタと、を有し、

前記第1のトランジスタ及び前記第1の容量素子は、前記第3のトランジスタのゲート電位をブーストストラップする機能を有し、

前記第2のトランジスタ及び前記第2の容量素子は、前記第5のトランジスタのゲート電位をブーストストラップする機能を有し、

前記第4のトランジスタのゲートは、前記第6のトランジスタの第1のゲートと電気的に接続され、

前記第1のインバータの出力端子は、前記第6のトランジスタの第2のゲートと電気的に接続され、

前記第1のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続されていることを特徴とする半導体装置。

## 【請求項 2】

第1のインバータと、第2のインバータと、第1のトランジスタと、第2のトランジスタと、第1の容量素子と、第2の容量素子と、を有し、

前記第1のインバータは、第3のトランジスタと、第4のトランジスタと、を有し、

10

20

前記第2のインバータは、第5のトランジスタと、第6のトランジスタと、を有し、

前記第1のトランジスタ及び前記第1の容量素子は、前記第3のトランジスタのゲート

電位をブーストストラップする機能を有し、

前記第2のトランジスタ及び前記第2の容量素子は、前記第5のトランジスタのゲート

電位をブーストストラップする機能を有し、

前記第4のトランジスタのゲートは、前記第6のトランジスタの第1のゲートと電気的

に接続され、

前記第1のインバータの出力端子は、前記第6のトランジスタの第2のゲートと電気的

に接続され、

前記第1のインバータ及び前記第2のインバータが有するトランジスタと、前記第1の

トランジスタと、前記第2のトランジスタとは、酸化物半導体を有し、且つ、同一の極性

であることを特徴とする半導体装置。 10

#### 【請求項3】

請求項1又は請求項2において、

前記第3のトランジスタ及び前記第5のトランジスタは、ノーマリーオンであり、

前記第4のトランジスタ及び前記第6のトランジスタは、ノーマリーオフであることを

特徴とする半導体装置。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第1のインバータ及び前記第2のインバータをそれぞれ複数個有し、 20

前記複数個の第1のインバータ及び前記複数個の第2のインバータを有するリングオシ

レータ又はインバータチェーンを有することを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置に関する。本明細書において、半導体装置とは、半導体素子自体

または半導体素子を含むものをいい、このような半導体素子として、例えば薄膜トランジ

スタが挙げられる。従って、液晶表示装置及び記憶装置なども半導体装置に含まれる。

##### 【背景技術】

##### 【0002】

半導体装置には、所望の動作をさせるために様々な回路が搭載されている。例えば、持

続した交流を作る発振回路が挙げられる。発振回路の一態様として、リングオシレータが

挙げられる（例えば、特許文献1）。また、発振回路の他には、遅延回路が挙げられる。

遅延回路の一態様として、インバータチェーンが挙げられる（例えば、特許文献2）。

##### 【0003】

このような回路を動作させるには、少なくとも、トランジスタに十分な電界効果移動度

が必要であり、酸化物半導体を用いた薄膜トランジスタが注目されている（例えば、特許

文献3及び特許文献4）。

##### 【0004】

また、n型の酸化物半導体については開発が進んでいるが、p型の酸化物半導体につい

ては、開発が十分には進んでいない。そのため、同一基板上に設けられる酸化物半導体を

用いた薄膜トランジスタはn型とすることが多い。また、同一基板上に十分な電気的特性

を有するp型の酸化物半導体が開発されたとしても、p型とn型を作り分けることで作製

工程数は著しく増加する。そのため、同一基板上に作製する薄膜トランジスタは一の導電

型とすることが好ましく、特に、キャリア移動度が比較的高いn型とすることが好ましい

（例えば、特許文献5）。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】特開2006-217162号公報

10

20

30

40

50

【特許文献2】特開2011-163983号公報

【特許文献3】特開2007-123861号公報

【特許文献4】特開2007-96055号公報

【特許文献5】特開2011-101351号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の一態様は、半導体装置に設けられた容量素子を有するリングオシレータまたはインバータチェーンの占有面積を小さくすることを課題とする。

【0007】

また、リングオシレータまたはインバータチェーンの所定の位置に容量素子が設けられると、所定の位置の電位がトランジスタのしきい値分だけ降下する現象（しきい値落ち）を防止することができる。本発明の一態様は、リングオシレータまたはインバータチェーンにおけるしきい値落ちを防止することも課題とする。

10

【課題を解決するための手段】

【0008】

本発明の一態様は、インバータ回路部と、最後段回路部と、第1乃至第3の配線を有する半導体装置であって、前記インバータ回路部は、第1のインバータ部と第2のインバータ部を有し、前記第1のインバータ部は、第1のインバータと、第1のブートストラップトランジスタと、第1の容量素子と、を有し、前記第1の容量素子と前記第1のブートストラップトランジスタは、前記第1のインバータの一方のトランジスタのゲートの一の電位をブートストラップし、且つ前記第1のインバータの出力電位の降下を抑制し、前記第2のインバータ部は、第2のインバータと、第2のブートストラップトランジスタと、第2の容量素子と、を有し、前記第2の容量素子と前記第2のブートストラップトランジスタは、前記第2のインバータの一方のトランジスタのゲートの一の電位をブートストラップし、且つ前記第2のインバータの出力電位の降下を抑制し、前記最後段回路部は、最後段のインバータと、最後段のブートストラップトランジスタと、最後段の容量素子と、を有し、前記最後段の容量素子と前記最後段のブートストラップトランジスタは、前記最後段のインバータの一方のトランジスタのゲートの一の電位をブートストラップし、且つ前記最後段のインバータの出力電位の降下を抑制することを特徴とする半導体装置である。

20

【0009】

なお、本明細書中において、「複数のトランジスタが重畳」とは、「複数のトランジスタの少なくともチャネル形成領域の一部が重畳すること」をいい、複数のトランジスタのすべての構成要素が必ずしも重畳していなくてもよい。

30

【発明の効果】

【0010】

半導体装置に設けられた容量素子を有するリングオシレータまたはインバータチェーンの占有面積を小さくすることができる。

【0011】

リングオシレータまたはインバータチェーンにおけるしきい値落ちを防止することができる。

40

【図面の簡単な説明】

【0012】

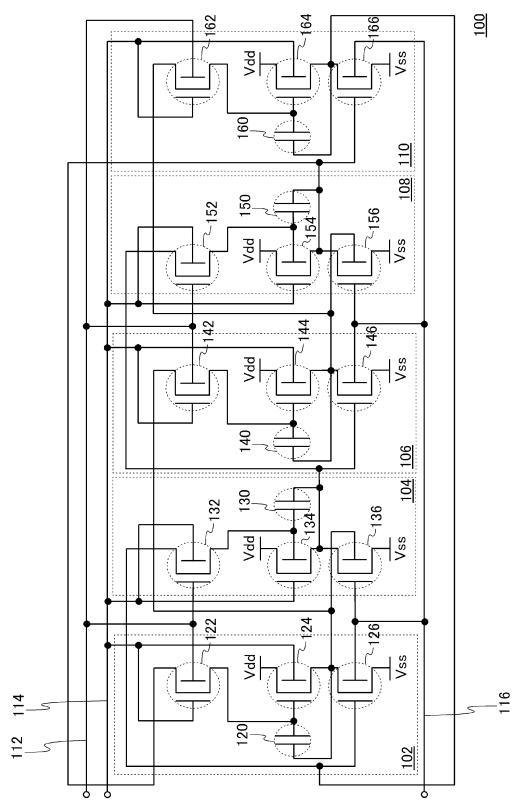

【図1】本発明の一態様である半導体装置を説明する回路図。

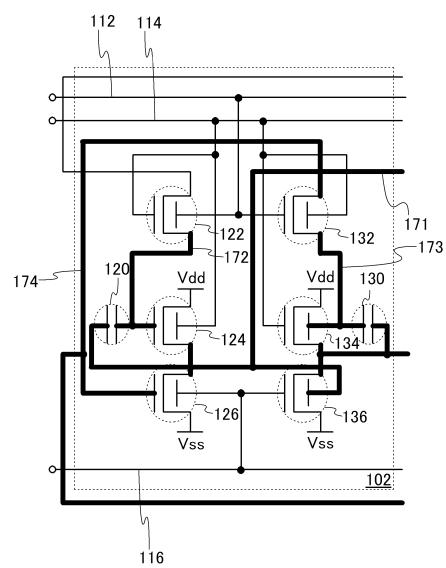

【図2】本発明の一態様である半導体装置を説明する回路図。

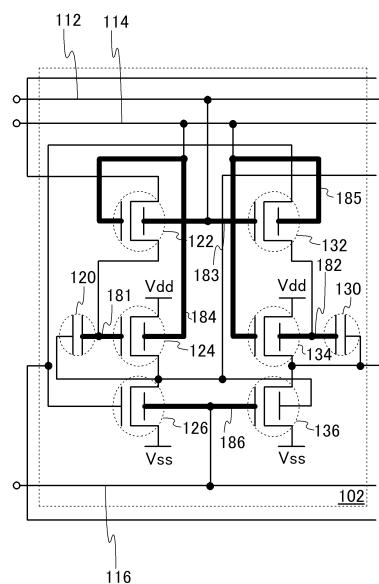

【図3】本発明の一態様である半導体装置を説明する回路図。

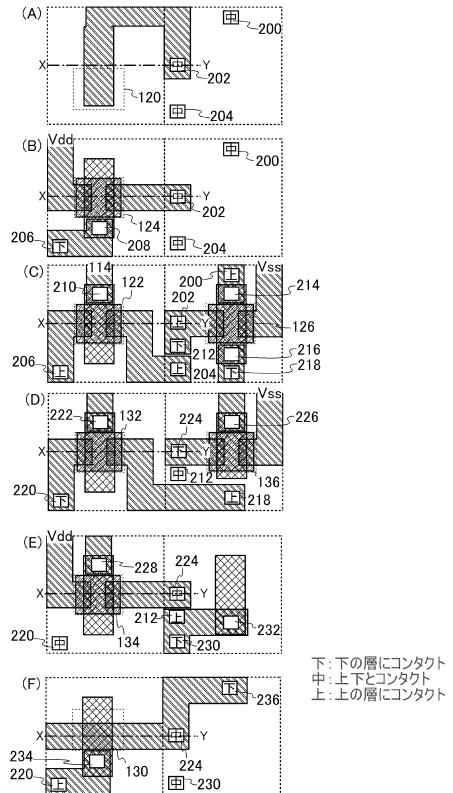

【図4】本発明の一態様である半導体装置の各層を説明する上面図。

【図5】本発明の一態様である半導体装置を説明する断面図。

【図6】本発明の一態様である半導体装置の作製方法を説明する断面図。

【図7】本発明の一態様である半導体装置の作製方法を説明する断面図。

50

**【発明を実施するための形態】****【0013】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

**【0014】**

本実施の形態では、本発明の一態様である半導体装置について説明する。本発明の一態様である半導体装置は、発振回路または遅延回路を有する。

**【0015】**

10

図1には、本実施の形態の半導体装置が有する発振回路または遅延回路として適用することができる回路100を示す。図1に示す回路100は、発振回路としても用いることができるし、遅延回路としても用いることができる。

**【0016】**

図1に示す回路100は、第1の回路102、第2の回路104、第3の回路106、第4の回路108及び最終段の回路110により構成され、第1乃至第15のトランジスタ及び第1乃至第5の容量素子を有する。第1の回路102、第2の回路104、第3の回路106及び第4の回路108にはそれぞれ3のトランジスタが配され、最終段の回路110には3のトランジスタが配されている。また、図1に示されるように、奇数段の回路構成が同様であり、偶数段の回路は構成が同様である。

20

**【0017】**

なお、図示していないが、図1に示す回路100は、更に多段の構成としてもよい。その場合には、第2の回路104と第3の回路106の間または第4の回路108と最終段の回路110の間に、更なる第3の回路106及び第4の回路108を配すればよい。

**【0018】**

ただし、以下では、図1に示される構成について説明するものとする。

**【0019】**

なお、以下の説明において、図示されたトランジスタの図面左側に配されるゲートを第1のゲートと呼び、図面右側に配されるゲートを第2のゲートと呼ぶ。

**【0020】**

30

第2のトランジスタ124のソース及びドレインの一方、第5のトランジスタ134のソース及びドレインの一方、第8のトランジスタ144のソース及びドレインの一方、第11のトランジスタ154のソース及びドレインの一方、第14のトランジスタ164のソース及びドレインの一方は、高電位電源線に電気的に接続されている。

**【0021】**

第3のトランジスタ126のソース及びドレインの一方、第6のトランジスタ136のソース及びドレインの一方、第9のトランジスタ146のソース及びドレインの一方、第12のトランジスタ156のソース及びドレインの一方、第15のトランジスタ166のソース及びドレインの一方は、低電位電源線に電気的に接続されている。

**【0022】**

40

ここで、まず、主に第1の回路102及び第2の回路104に注目して説明する。第2のトランジスタ124のソース及びドレインの他方と、第3のトランジスタ126のソース及びドレインの他方と、第1の容量素子120の一方の電極と、第6のトランジスタ136の第2のゲートは、第3の回路106の第7のトランジスタ142のソース及びドレインの一方と電気的に接続されている。

**【0023】**

この、第2のトランジスタ124のソース及びドレインの他方と、第3のトランジスタ126のソース及びドレインの他方と、第1の容量素子120の一方の電極と、第6のトランジスタ136の第2のゲートが接続して形成された部分を第1の同電位部171と呼ぶものとする(図2を参照)。

50

## 【0024】

第1の容量素子120の他方の電極と、第2のトランジスタ124の第1のゲートは、第1のトランジスタ122のソース及びドレインの一方に電気的に接続されている。

## 【0025】

この、第1の容量素子120の他方の電極と、第2のトランジスタ124の第1のゲートと、第1のトランジスタ122のソース及びドレインの一方が接続して形成された部分を第2の同電位部172と呼ぶものとする(図2を参照)。

## 【0026】

第5のトランジスタ134の第2のゲートと、第2の容量素子130の一方の電極は、第4のトランジスタ132のソース及びドレインの一方に電気的に接続されている。 10

## 【0027】

この、第5のトランジスタ134の第2のゲートと、第2の容量素子130の一方の電極と、第4のトランジスタ132のソース及びドレインの一方が接続して形成された部分を第3の同電位部173と呼ぶものとする(図2を参照)。

## 【0028】

第2の容量素子130の他方の電極と、第5のトランジスタ134のソース及びドレインの他方と、第6のトランジスタ136のソース及びドレインの他方は、第4の回路108の第10のトランジスタ152のソース及びドレインの一方と、第3の回路106の第9のトランジスタ146の第1のゲートに電気的に接続されている。 20

## 【0029】

この、第2の容量素子130の他方の電極と、第5のトランジスタ134のソース及びドレインの他方と、第6のトランジスタ136のソース及びドレインの他方が接続して形成された部分を第4の同電位部174と呼ぶものとする(図2を参照)。

## 【0030】

第1のトランジスタ122のソース及びドレインの他方は、第4の回路108の第11のトランジスタ154のソース及びドレインの他方と、第12のトランジスタ156のソース及びドレインの他方と、第4の容量素子150の一方の電極と、最終段の回路110の第15のトランジスタ166の第1のゲートに電気的に接続されている。 30

## 【0031】

第1のトランジスタ122の第2のゲートと、第4のトランジスタ132の第1のゲートは、第1の配線112に電気的に接続されている。

## 【0032】

第1のトランジスタ122の第1のゲートと、第2のトランジスタ124の第2のゲートと、第4のトランジスタ132の第2のゲートと、第5のトランジスタ134の第1のゲートは、第2の配線114に電気的に接続されている。

## 【0033】

第3のトランジスタ126の第2のゲートと、第6のトランジスタ136の第1のゲートは、第3の配線116に電気的に接続されている。

## 【0034】

次に、主に第3の回路106及び第4の回路108に注目して説明する。第8のトランジスタ144のソース及びドレインの他方と第9のトランジスタ146のソース及びドレインの他方と、第3の容量素子140の一方の電極と、第12のトランジスタ156の第2のゲートは、最終段の回路110の第13のトランジスタ162のソース及びドレインの一方と電気的に接続されている。 40

## 【0035】

第3の容量素子140の他方の電極と、第7のトランジスタ142のソース及びドレインの他方は、第8のトランジスタ144の第1のゲートに電気的に接続されている。

## 【0036】

第10のトランジスタ152のソース及びドレインの他方と、第11のトランジスタ154の第2のゲートは、第4の容量素子150の他方の電極に電気的に接続されている。 50

**【0037】**

第7のトランジスタ142の第2のゲートと、第10のトランジスタ152の第1のゲートは、第1の配線112に電気的に接続されている。

**【0038】**

第7のトランジスタ142の第1のゲートと、第8のトランジスタ144の第2のゲートと、第10のトランジスタ152の第2のゲートと、第11のトランジスタ154の第1のゲートは、第2の配線114に電気的に接続されている。

**【0039】**

第9のトランジスタ146の第2のゲートと、第12のトランジスタ156の第1のゲートは、第3の配線116に電気的に接続されている。 10

**【0040】**

最後に、主に最終段の回路110に注目して説明する。第5の容量素子160の他方の電極と、第13のトランジスタ162のソース及びドレインの他方は、第14のトランジスタ164の第1のゲートに電気的に接続されている。

**【0041】**

第13のトランジスタ162の第2のゲートは、第1の配線112に電気的に接続されている。

**【0042】**

第13のトランジスタ162の第1のゲートと、第14のトランジスタ164の第2のゲートは、第2の配線114に電気的に接続されている。 20

**【0043】**

第15のトランジスタ166の第2のゲートは、第3の配線116に電気的に接続されている。

**【0044】**

第1乃至第15のトランジスタがnチャネル型トランジスタである場合には、第1の配線112及び第2の配線114の電位は、低電位電源線の電位よりも高く（正電位）する。第3の配線116の電位は、低電位電源線の電位よりも低くする（負電位）とよい。すなわち、第1乃至第15のトランジスタがnチャネル型トランジスタである場合には、ソース及びドレインの一方が高電位電源線に電気的に接続されているトランジスタでは、常時電流が流れる（ノーマリーオンになる）ようにするとよい。出力電位が、しきい値分だけ降下することを防ぐためである。ソース及びドレインの一方が低電位電源線に電気的に接続されているトランジスタでは、オフすると電流がほとんど流れない（ノーマリーオフになる）ようにするとよい。消費電流を抑えるためである。 30

**【0045】**

次に、図1に示す回路100の動作について、第1の回路102及び第2の回路104に注目して説明する。

**【0046】**

まず、第1の配線112及び第2の配線114の電位を低電位電源線の電位よりも高くし（正電位とし）、ブートストラップ用トランジスタ（第1のトランジスタ122及び第4のトランジスタ132）と高電位電源線に電気的に接続されているトランジスタ（第2のトランジスタ124及び第5のトランジスタ134）をオンさせる。第1の配線112及び第2の配線114の電位は、ブートストラップ用トランジスタと高電位電源線に電気的に接続されているトランジスタのオン抵抗が、低電位電源線に電気的に接続されているトランジスタ（第3のトランジスタ126及び第6のトランジスタ136）のオン抵抗よりも十分に高くなるように制御する。 40

**【0047】**

第3の配線116の電位は低電位電源線の電位以下（負電位）とする。

**【0048】**

まず、初期状態として、第2のトランジスタ124と第3のトランジスタ126で構成されるインバータ（第1の回路102）の入力に相当する部分（第3のトランジスタ12 50

6の第1のゲートの電位)が、第3のトランジスタ126をオフさせる電位(低電位)であるものとし、第1のトランジスタ122のソース及びドレインの他方の電位を高電位とする。すなわち、第1の回路102の入力は低電位(Low)となる。

#### 【0049】

第3のトランジスタ126がオフしているので、第2のトランジスタ124と第3のトランジスタ126で構成されるインバータ(第1の回路102)の出力に相当する部分(第6のトランジスタ136の第2のゲートに電気的に接続されている部分)の電位は高電位となるが、その電位は第2のトランジスタ124のオン抵抗によってしきい値落ちした電位となる。

#### 【0050】

また、第1のトランジスタ122はオンしているので、第2のトランジスタ124の第1のゲートの電位は高電位である。そのため、第2のトランジスタ124の第1のゲートの電位は高電位となる。ここで、第2のトランジスタ124の第1のゲートの電位は、第1の容量素子120における容量結合によって高電位電源線の電位よりも高くなる。すなわち、第2のトランジスタ124の第1のゲートの電位がブートストラップされるため、第2のトランジスタ124と第3のトランジスタ126で構成されるインバータ(第1の回路102)の出力における第2のトランジスタ124によるしきい値落ちを防止することができる。すなわち、第1の回路102の出力は高電位(High)となる。

#### 【0051】

第2のトランジスタ124と第3のトランジスタ126で構成されるインバータの出力が高電位であるため、第5のトランジスタ134と第6のトランジスタ136で構成されるインバータ(第2の回路104)の入力に相当する部分の電位(第6のトランジスタ136の第2のゲートの電位)は、第6のトランジスタ136をオンさせる電位(高電位)である。

#### 【0052】

第6のトランジスタ136の第2のゲートの電位はブートストラップされた高電位であるため、第6のトランジスタ136はオンし、且つ第5のトランジスタ134のオン抵抗は第6のトランジスタ136のオン抵抗よりも大きい。そのため、第5のトランジスタ134と第6のトランジスタ136で構成されるインバータ(第2の回路104)の出力に相当する部分の電位(第2の容量素子130の他方の電極の電位)は低電位となる。すなわち、第2の回路104の出力は低電位(Low)となる。

#### 【0053】

なお、第4のトランジスタ132はオンしているので、第5のトランジスタ134の第2のゲートの電位は低電位となる。

#### 【0054】

従って、第8のトランジスタ144と第9のトランジスタ146で構成されるインバータ(第3の回路106)の入力は低電位(Low)となる。そのため、同様に考えると、第3の回路106の出力は高電位(High)となり、第11のトランジスタ154と第12のトランジスタ156で構成されるインバータ(第4の回路108)の出力は低電位(Low)となる。さらには、第14のトランジスタ164と第15のトランジスタ166で構成されるインバータ(最終段の回路110)の出力は高電位(High)となるため、第1の回路102の入力が低電位(Low)から高電位(High)になる。

#### 【0055】

図1の回路100は以上説明したように動作する。図1の回路100には、第3の回路106及び第4の回路108を複数設けることで、更に多段としてもよい。

#### 【0056】

すなわち、本発明の一態様は、インバタ回路部と、最後段回路部と、第1乃至第3の配線を有する半導体装置であって、前記インバタ回路部は、第1のインバタ部と第2のインバタ部を有し、前記第1のインバタ部は、第1のインバタと、第1のブートストラップトランジスタと、第1の容量素子と、を有し、前記第1の容量素子と前記第1

10

20

30

40

50

のブーストストラップトランジスタは、前記第1のインバータの一方のトランジスタのゲートの一の電位をブーストストラップし、且つ前記第1のインバータの出力電位の降下を抑制し、前記第2のインバータ部は、第2のインバータと、第2のブーストストラップトランジスタと、第2の容量素子と、を有し、前記第2の容量素子と前記第2のブーストストラップトランジスタは、前記第2のインバータの一方のトランジスタのゲートの一の電位をブーストストラップし、且つ前記第2のインバータの出力電位の降下を抑制し、前記最後段回路部は、最後段のインバータと、最後段のブーストストラップトランジスタと、最後段の容量素子と、を有し、前記最後段の容量素子と前記最後段のブーストストラップトランジスタは、前記最後段のインバータの一方のトランジスタのゲートの一の電位をブーストストラップし、且つ前記最後段のインバータの出力電位の降下を抑制することを特徴とする半導体装置であるが、更に多段にした場合を考慮すると、本発明の一態様は、前記第1のインバータ部を奇数段インバータ部とし、前記第2のインバータ部を偶数段インバータ部とし、前記奇数段のインバータ部と前記偶数段のインバータ部を交互に配した、前記第1のインバータ部と前記第2のインバータ部を複数有する構成とする。

【 0 0 5 7 】

または、本発明の一態様は、3つのトランジスタが含まれる奇数個の単位回路を有する半導体装置であって、第2m-1の回路は、第1乃至第3のトランジスタと第1の容量素子を有し、第2mの回路は、第4乃至第6のトランジスタと第2の容量素子を有し、最終段の回路は、第7乃至第9のトランジスタと第3の容量素子を有し、第2n-1の回路の第2のトランジスタのソース及びドレインの一方、第2nの回路の第5のトランジスタのソース及びドレインの一方は、高電位電源線に電気的に接続され、第2n-1の回路の第3のトランジスタのソース及びドレインの一方、第2nの回路の第6のトランジスタのソース及びドレインの一方は、低電位電源線に電気的に接続され、第2n-1の回路の前記第2のトランジスタのソース及びドレインの他方と、第2n-1の回路の前記第3のトランジスタのソース及びドレインの他方と、第1の容量素子の一方の電極と、第2nの回路の前記第6のトランジスタの第2のゲートは、第2n+1の回路の第1のトランジスタのソース及びドレインの一方と電気的に接続され、第2n-1の回路の前記第1の容量素子の他方の電極と、第2n-1の回路の前記第2のトランジスタの第1のゲートは、第2n-1の回路の第1のトランジスタのソース及びドレインの一方に電気的に接続され、第2nの回路の前記第5のトランジスタの第2のゲートと、第2nの回路の第2の容量素子の一方の電極は、第2nの回路の第4のトランジスタのソース及びドレインの一方に電気的に接続され、第2nの回路の前記第2の容量素子の他方の電極と、第2nの回路の前記第5のトランジスタのソース及びドレインの他方と、第2nの回路の前記第6のトランジスタのソース及びドレインの他方と、第2n-1の回路の前記第3のトランジスタの第1のゲートは、第2n+2の回路の前記第4のトランジスタのソース及びドレインの一方と、第2n+1の回路の第3のトランジスタの第1のゲートに電気的に接続され、第2n-1の回路の前記第1のトランジスタのソース及びドレインの他方は、第2n-3の回路の第2のトランジスタのソース及びドレインの一方と、第2n-3の回路の第3のトランジスタのソース及びドレインの一方と、第2n-2の回路の第1の容量素子の一方の電極と、第2n-2の回路の第6のトランジスタの第2のゲートに電気的に接続され、第2n-1の回路の前記第1のトランジスタの第2のゲートと、第2nの回路の前記第4のトランジスタの第1のゲートは、第1の配線に電気的に接続され、第2n-1の回路の前記第1のトランジスタの第1のゲートと、第2n-1の回路の前記第2のトランジスタの第2のゲートと、第2nの回路の前記第4のトランジスタの第2のゲートと、第2nの回路の前記第5のトランジスタの第1のゲートは、第2の配線に電気的に接続され、第2n-1の回路の前記第3のトランジスタの第2のゲートと、第2nの回路の前記第6のトランジスタの第1のゲートは、第3の配線に電気的に接続され、第2n-1の回路の前記第3のトランジスタの第1のゲートと、第2nの回路の前記第4のトランジスタのソース及びドレインの他方は、第2n-2の回路の第5のトランジスタのソース及びドレインの一方と、第2n-2の回路の前記第6のトランジスタのソース及びドレインの一方と、第2n-2の

回路の第2の容量素子の一方の電極に接続され、第1の回路の第2のトランジスタのソース及びドレインの一方、第2の回路の第5のトランジスタのソース及びドレインの一方は、前記高電位電源線に電気的に接続され、第1の回路の第3のトランジスタのソース及びドレインの一方、第2の回路の第6のトランジスタのソース及びドレインの一方は、前記低電位電源線に電気的に接続され、第1の回路の前記第1の容量素子の他方の電極と、第1の回路の前記第2のトランジスタの第1のゲートは、第1の回路の第1のトランジスタのソース及びドレインの一方電気的に接続され、第2の回路の前記第5のトランジスタの第2のゲートと、第2の回路の第2の容量素子の一方の電極は、第2の回路の第4のトランジスタのソース及びドレインの一方に電気的に接続され、第1の回路の前記第1のトランジスタのソース及びドレインの他方は、第 $2N+2$ の回路の第5のトランジスタのソース及びドレインの他方と、第 $2N+2$ の回路の第6のトランジスタのソース及びドレインの他方と、第 $2N+2$ の回路の第2の容量素子の一方の電極と、前記第9のトランジスタの第1のゲートに電気的に接続され、第1の回路の前記第1のトランジスタの第2のゲートと、第2の回路の前記第4のトランジスタの第1のゲートは、前記第1の配線に電気的に接続され、第1の回路の前記第1のトランジスタの第1のゲートと、第1の回路の前記第2のトランジスタの第2のゲートと、第2の回路の前記第4のトランジスタの第2のゲートと、第2の回路の前記第5のトランジスタの第1のゲートは、前記第2の配線に電気的に接続され、第1の回路の前記第3のトランジスタの第2のゲートと、第2の回路の前記第6のトランジスタの第1のゲートは、前記第3の配線に電気的に接続され、第1の回路の前記第3のトランジスタの第1のゲートと、第2の回路の前記第4のトランジスタのソース及びドレインの他方は、前記第8のトランジスタのソース及びドレインの一方と、前記第9のトランジスタのソース及びドレインの一方と、前記第3の容量素子の一方の電極に接続され、第 $2N+1$ の回路の第2のトランジスタのソース及びドレインの一方、第 $2N+2$ の回路の第5のトランジスタのソース及びドレインの一方は、前記高電位電源線に電気的に接続され、第 $2N+1$ の回路の第3のトランジスタのソース及びドレインの一方、第 $2N+2$ の回路の第6のトランジスタのソース及びドレインの一方は、前記低電位電源線に電気的に接続され、第 $2N+1$ の回路の前記第2のトランジスタのソース及びドレインの他方と、第 $2N+1$ の回路の前記第3のトランジスタのソース及びドレインの他方と、第1の容量素子の一方の電極と、第 $2N+2$ の回路の前記第6のトランジスタの第2のゲートは、前記第7のトランジスタのソース及びドレインの一方と電気的に接続され、第 $2N+1$ の回路の前記第1の容量素子の他方の電極と、第 $2N+1$ の回路の前記第2のトランジスタの第1のゲートは、第 $2N+1$ の回路の第1のトランジスタのソース及びドレインの一方に電気的に接続され、第 $2N+2$ の回路の前記第5のトランジスタの第2のゲートと、第 $2N+2$ の回路の第2の容量素子の一方の電極は、第 $2N+2$ の回路の第4のトランジスタのソース及びドレインの一方に電気的に接続され、第 $2N+1$ の回路の前記第1のトランジスタの第2のゲートと、第 $2N+2$ の回路の前記第4のトランジスタの第2のゲートと、第 $2N+2$ の回路の前記第5のトランジスタの第1のゲートは、前記第1の配線に電気的に接続され、第 $2N+1$ の回路の前記第1のトランジスタの第1のゲートと、第 $2N+1$ の回路の前記第2のトランジスタの第2のゲートと、第 $2N+2$ の回路の前記第6のトランジスタの第1のゲートは、前記第2の配線に電気的に接続され、第 $2N+1$ の回路の前記第3のトランジスタの第2のゲートと、第 $2N+2$ の回路の前記第6のトランジスタの第1のゲートは、前記第3の配線に電気的に接続され、前記第8のトランジスタのソース及びドレインの一方は前記高電位電源線に電気的に接続され、前記第9のトランジスタのソース及びドレインの一方は前記低電位電源線に電気的に接続され、前記第3の容量素子の他方の電極と、前記第7のトランジスタのソース及びドレインの他方は、前記第8のトランジスタの第1のゲートに電気的に接続され、前記第7のトランジスタの第2のゲートは、前記第1の配線に電気的に接続され、前記第7のトランジスタの第1のゲートと、前記第8のトランジスタの第2のゲートは、前記第2の配線に電気的に接続され、前記第9のトランジスタの第2のゲートは、前記第3の配線に電気的に接続されている半導体装置である。ただし、Nは2以上の自然数であり、nは2以上かつN以

下の自然数であり、mは1以上かつN+1以下の自然数である。

**【0058】**

図4(A)～(F)には、回路100を有する半導体装置の一態様における、各層を説明する上面図を示す。ここで、図4(A)～(F)には、第1の回路102と第2の回路104が示されている。図4(A)～(F)には、各層の上面図を示しており、図4(A)が第1の層、図4(B)が第2の層、図4(C)が第3の層、図4(D)が第4の層、図4(E)が第5の層、図4(F)が第6の層である。第1の層は第2の層上に設けられており、第2の層は第3の層上に設けられており、第3の層は第4の層上に設けられており、第4の層は第5の層上に設けられており、第5の層は第6の層上に設けられている。

**【0059】**

図4に示すように、本発明の一態様である半導体装置では、例えば、トランジスタが重畳している場合のように電極を共有できるときには、可能な限り共有することが好ましい。このように電極を共有すると、回路100の各部分の占有面積を小さくすることができる。

**【0060】**

第1の容量素子120の他方の電極と、第2のトランジスタ124の第1のゲートが共有する電極を第1の共有電極181と呼ぶ(図3を参照)。

**【0061】**

第5のトランジスタ134の第2のゲートと、第2の容量素子130の一方の電極が共有する電極を第2の共有電極182と呼ぶ(図3を参照)。

**【0062】**

第1のトランジスタ122の第2のゲートと、第4のトランジスタ132の第1のゲートが共有する電極を第3の共有電極183と呼ぶ(図3を参照)。

**【0063】**

第1のトランジスタ122の第1のゲートと、第2のトランジスタ124の第2のゲートが共有する電極を第4の共有電極184と呼ぶ(図3を参照)。

**【0064】**

第4のトランジスタ132の第2のゲートと、第5のトランジスタ134の第1のゲートが共有する電極を第5の共有電極185と呼ぶ(図3を参照)。

**【0065】**

第3のトランジスタ126の第2のゲートと、第6のトランジスタ136の第1のゲートが共有する電極を第6の共有電極186と呼ぶ(図3を参照)。

**【0066】**

コンタクトホール200は、第3のトランジスタ126の第1のゲートと、第1の層の上の層の導電層と、を電気的に接続している。第1の層の上の層の導電層は、第4の回路108及び最終段の回路110に電気的に接続されている。

**【0067】**

コンタクトホール202は、第1の容量素子120の一方の電極と、第2のトランジスタ124のソース及びドレインの他方と、第3のトランジスタ126のソース及びドレインの他方と、第1の層の上の層の導電層と、を電気的に接続している。ここで、第1の層の上の層の導電層は、第4の回路108及び最終段の回路110の一方または双方に電気的に接続されている。

**【0068】**

コンタクトホール204は、第1のトランジスタ122のソース及びドレインの他方と、第1の層の上の層の導電層と、を電気的に接続している。ここで、第1の層の上の層の導電層は、第4の回路108及び最終段の回路110などに電気的に接続されている。

**【0069】**

コンタクトホール206は、第1のトランジスタ122のソース及びドレインの一方と、第2のトランジスタ124の第1のゲートにコンタクトホール208を介して電気的に接続される導電層と、を電気的に接続している。

10

20

30

40

50

**【0070】**

コンタクトホール208は、前述の通りである。

**【0071】**

コンタクトホール210は、第1のトランジスタ122の第1のゲートと、第2の配線114に電気的に接続される導電層を電気的に接続している。

**【0072】**

コンタクトホール212は、コンタクトホール202が電気的に接続される導電層と、コンタクトホール230及びコンタクトホール232が電気的に接続される導電層を電気的に接続している。

**【0073】**

コンタクトホール214は、コンタクトホール200が電気的に接続される導電層と、第3のトランジスタ126の第1のゲートを電気的に接続している。

**【0074】**

コンタクトホール216は、第3のトランジスタ126の第1のゲートと、コンタクトホール218が電気的に接続される導電層と電気的に接続している。

**【0075】**

コンタクトホール218は、コンタクトホール216が電気的に接続される導電層と、第4のトランジスタ132のソース及びドレインの他方に電気的に接続している。

**【0076】**

コンタクトホール220は、第4のトランジスタ132のソース及びドレインの一方と、コンタクトホール234が電気的に接続される導電層に電気的に接続している。

**【0077】**

コンタクトホール222は、第4のトランジスタ132の第1のゲートと、第1の配線112に電気的に接続される導電層を電気的に接続している。

**【0078】**

コンタクトホール224は、第6のトランジスタ136のソース及びドレインの他方と、第5のトランジスタ134のソース及びドレインの他方と、第2の容量素子130の他方の電極に電気的に接続している。

**【0079】**

コンタクトホール226は、第6のトランジスタ136の第1のゲートと、第3の配線116に電気的に接続される導電層を電気的に接続している。

**【0080】**

コンタクトホール228は、第5のトランジスタ134の第1のゲートと、第2の配線114に電気的に接続される導電層を電気的に接続している。

**【0081】**

コンタクトホール230は、コンタクトホール212及びコンタクトホール232が電気的に接続される導電層を電気的に接続している。

**【0082】**

コンタクトホール232は、第6のトランジスタ136の第2のゲートと、コンタクトホール212及びコンタクトホール230が電気的に接続される導電層を電気的に接続している。

**【0083】**

コンタクトホール234は、第2の容量素子130の一方の電極と、コンタクトホール220が電気的に接続される導電層を電気的に接続している。

**【0084】**

コンタクトホール236は、第2の容量素子130の他方の電極及びコンタクトホール224が電気的に接続される導電層と、第6の層の下の層の導電層と、を電気的に接続している。ここで、第6の層の下の層の導電層は、第3の回路106及び第4の回路108に電気的に接続されている。

**【0085】**

10

20

30

40

50

なお、前記各層の配線となる前記導電層は、原則として、前記各層のトランジスタのソース及びドレインと同一の層である。すなわち、前記各層の配線は、原則として、前記各層のトランジスタのソース及びドレインと同一の層により形成する。これは、後に説明するように、前記各層の第1のゲートと重畳するゲート（第2のゲート）の間には、トランジスタのゲート絶縁膜となる薄い絶縁膜しか介在せず、前記各層のゲートと重畳するゲートの間に寄生容量を生じてしまうからである。なお、このような寄生容量は、第1の容量素子120と第2の容量素子130が設けられる部分以外の部分において問題となるものである。

#### 【0086】

図4（A）～（F）において、第1のトランジスタ122、第2のトランジスタ124、第4のトランジスタ132及び第5のトランジスタ134はすべて重畳している。また、これらと、第1の容量素子120と第2の容量素子130も重畳している。そして、第3のトランジスタ126と第6のトランジスタ136が重畳している。

#### 【0087】

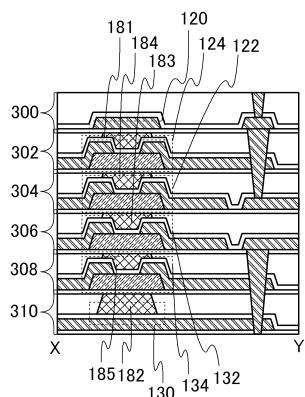

図5には、図4（A）～（F）のX-Yにおける断面図を示す。図5において、第1の層300の下には第2の層302が設けられており、第2の層302の下には第3の層304が設けられており、第3の層304の下には第4の層306が設けられており、第4の層306の下には第5の層308が設けられており、第5の層308の下には第6の層310が設けられている。

#### 【0088】

なお、図5において、上面図と同様に、ゲートとなる層は格子ハッチングにて表し、ソース及びドレインとなる層は二重ラインハッチングにて表し、半導体層は点線ハッチングにて表している。そして、絶縁膜にはハッチングを施していない。

#### 【0089】

図5に示すように、すべてのトランジスタはトップゲートトップコンタクト型であり、すべてのトランジスタは絶縁膜で覆われている。なお、図5では図示していないが、最上層の配線と電気的に接続する配線が設けられていてもよい。同様に、最下層の配線と電気的に接続する配線が設けられていてもよい。すなわち、図5における最上層の上及び最下層の下には更に層が設けられていてもよい。また、図5に示すように、絶縁膜とゲートの表面が一の面上に存在するように平坦化されているとよい。そして、半導体層は、ゲートと重畳するように、ゲート絶縁膜として機能する絶縁膜を介して設けられている。ただし、これに限定されず、すべてのトランジスタはトップゲートボトムコンタクト型であってもよいし、すべてのトランジスタはボトムゲートボトムコンタクト型であってもよいし、すべてのトランジスタはボトムゲートトップコンタクト型であってもよい。

#### 【0090】

なお、図5には、第1のトランジスタ122、第2のトランジスタ124、第4のトランジスタ132及び第5のトランジスタ134が重畳している。また、これらと、第1の容量素子120と第2の容量素子130も重畳している。図5には、第1の共有電極181、第2の共有電極182、第3の共有電極183、第4の共有電極184及び第5の共有電極185が示されている。

#### 【0091】

このように、同電位となる電極を共用することで、複数のトランジスタによって設けられたリングオシレータの占有面積を小さくすることができる。また、容量素子による占有面積の増大もない。

#### 【0092】

上記説明したように、本発明の一態様は、リングオシレータである。ただし、これに限定されず、インバータチェーンとすることもできる。インバータチェーンとする場合には、図4の（A）～（C）と（D）～（F）を繰り返し設ければよい。

#### 【0093】

図4（A）～（C）がインバータの最初の段であるときには、コンタクトホール200

10

20

30

40

50

がインバータの入力となり、コンタクトホール 204 がブートストラップトランジスタの入力となり、図 4 (A) ~ (C) がインバータの最終の段であるときには、コンタクトホール 212 がインバータの出力となり、コンタクトホール 218 がブートストラップトランジスタの出力となる。

#### 【0094】

図 4 (D) ~ (F) がインバータの最初の段であるときには、コンタクトホール 212 がインバータの入力となり、コンタクトホール 218 がブートストラップトランジスタの入力となり、図 4 (D) ~ (F) がインバータの最終の段であるときには、コンタクトホール 236 がインバータの出力となり、コンタクトホール 230 がブートストラップトランジスタの出力となる。

10

#### 【0095】

なお、図 1 に示すように、回路 100において、第 1 乃至第 15 のトランジスタは、同一の極性とすることが好ましい。同一の極性とすると、作製工程が簡略化するからである。より好ましくは、第 1 乃至第 15 のトランジスタのチャネル形成領域を酸化物半導体層とする。リーク電流が小さいトランジスタを作製しやすいためである。

#### 【0096】

ここで、図 5 の半導体装置の作製方法について、図 6 及び図 7 を参照して説明する。なお、ここでは、第 4 の層 306 の作製方法について説明する。また、以下の説明においては第 5 の層 308 及び第 6 の層 310 を被形成物 400 として説明する。最下層を形成する場合には、被形成物 400 は基板である。第 1 の層 300 乃至第 3 の層 304、第 5 の層 308 及び第 6 の層 310 は、ここで説明する方法を適用して作製すればよい。

20

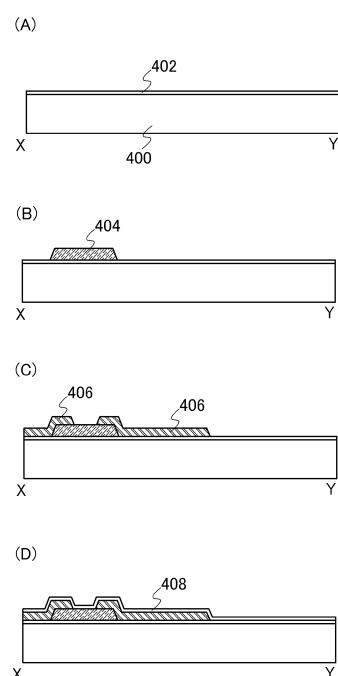

#### 【0097】

まず、被形成物 400 上に下地膜 402 を形成する(図 6 (A))。なお、下地膜 402 が必要でない場合には形成しなくてもよい。

#### 【0098】

被形成物 400 が基板の場合には、ガラス基板(好ましくは無アルカリガラス基板)、石英基板、セラミック基板、プラスチック基板またはシリコン基板などを例示することができる。

#### 【0099】

下地膜 402 は、酸化物半導体層に接する層であるため、化学量論比よりも多くの酸素を含むことが特に好ましい。下地膜 402 が化学量論比よりも多くの酸素を含むことで、酸化物半導体膜に酸素を供給する供給源として機能させることもできる。

30

#### 【0100】

下地膜 402 が化学量論比よりも多くの酸素を含む場合として、例えば、下地膜 402 が  $\text{SiO}_x$  ( $x > 2$ ) で表される酸化シリコンである場合が挙げられる。ただし、これに限定されず、下地膜 402 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化ハフニウムまたは酸化イットリウムなどで形成してもよい。なお、「窒化酸化シリコン」とは、その組成として、酸素よりも窒素の含有量が多いものをいい、「酸化窒化シリコン」とは、その組成として、窒素よりも酸素の含有量が多いものをいう。

40

#### 【0101】

なお、下地膜 402 は、複数の膜が積層された 2 層の積層膜であってもよい。この場合には、少なくとも上層には前記した酸化物半導体膜への酸素の供給源として機能する絶縁膜を配することが好ましい。前記バリア膜としては、窒化シリコン膜または酸化アルミニウム膜を例示することができる。

#### 【0102】

なお、下地膜 402 の形成後には、水素、水、水酸基及び水素化物を除くこと(脱水化または脱水素化と呼ぶ)を目的として熱処理を行い、その後、イオンインプランテーション法などにより酸素を導入することが好ましい。

#### 【0103】

50

次に、下地膜402上に、島状の酸化物半導体膜404を位置選択的に形成する(図6(B))。島状の酸化物半導体膜404は、下地膜402上の全面に形成した酸化物半導体膜を加工することで形成すればよい。島状の酸化物半導体膜404は、水素、水、水酸基及び水素化物などが混入しにくい方法で形成すればよく、例えばスパッタリング法を用いて形成することが好ましい。

#### 【0104】

スパッタリング法は、希ガス雰囲気、酸素ガス雰囲気または希ガスと酸素ガスの混合ガス雰囲気中などで行えばよい。また、酸化物半導体層への水素、水、水酸基及び水素化物などの混入を防ぐために、これらが十分に除去された高純度ガスを用いることが好ましい。

10

#### 【0105】

酸化物半導体膜404の材料としては、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物などを例示することができる。

20

#### 【0106】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、In、Ga及びZnを有する酸化物を意味し、InとGaとZnの比率は問わない。また、In、Ga及びZn以外の金属元素が含まれていてもよい。

30

#### 【0107】

なお、酸化物半導体膜404は、単結晶、多結晶(ポリクリスタル)または非晶質などの状態をとりうるが、好ましくは、C AAC(C Axis Aligned Crystalline)酸化物半導体膜とする。

#### 【0108】

C AAC酸化物半導体膜は、完全な単結晶ではなく、完全な非晶質でもない。C AAC酸化物半導体膜は、非晶質相に結晶部及び非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に收まる大きさであることが多い。また、C AAC酸化物半導体膜の非晶質部と結晶部との境界は、透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって確認されない状態であるとよい。また、C AAC酸化物半導体膜の結晶部には、粒界がTEMによって確認されない状態であるとよい。非晶質部と結晶部の境界が確認できず、結晶部中に粒界が確認できない場合には、電子移動度の低下が抑制される。

40

#### 【0109】

C AAC酸化物半導体膜に含まれる結晶部は、c軸がC AAC酸化物半導体膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつa b面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子が層状に配列している。なお、異なる結晶部間で、それぞれa軸とb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合には、85°以上95°以下の範囲も含まれるものとする。また、単に平行と記載す

50

る場合には、-5°以上5°以下の範囲も含まれるものとする。

**【0110】**

なお、C A A C 酸化物半導体膜において、結晶部の分布は一様でなくともよく、被形成面の近傍よりも表面の近傍において結晶部の占める割合が高くなっていてもよい。例えば、C A A C 酸化物半導体膜の形成において、C A A C 酸化物半導体膜の表面側から結晶を成長させると、被形成面の近傍よりも表面の近傍において結晶部の占める割合が高くなることがある。また、C A A C 酸化物半導体膜へドーピングなどにより添加物が導入されて一部が非晶質化されていてもよい。

**【0111】**

C A A C 酸化物半導体膜に含まれる結晶部のc軸は、C A A C 酸化物半導体膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、C A A C 酸化物半導体膜の形状（被形成面の断面形状または表面の断面形状）によっては、c軸が互いに異なる方向を向いた結晶部が含まれていてもよい。なお、結晶部のc軸の方向は、C A A C 酸化物半導体膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。なお、結晶部は、当該膜の成膜時に形成されていてもよいし、成膜後の結晶化処理（例えば熱処理）により形成されていてもよい。

**【0112】**

C A A C 酸化物半導体膜を用いたトランジスタでは、可視光や紫外光の照射による電気的特性の変動が抑制されるため、信頼性を高くすることができる。

**【0113】**

次に、酸化物半導体膜404に接して、ソース及びドレインとして機能する第1の導電膜406を位置選択的に形成する（図6（C））。第1の導電膜406は、下地膜402及び酸化物半導体膜404上にスパッタリング法またはCVD法などにより導電膜を形成した後に、これを加工することで形成すればよい。

**【0114】**

第1の導電膜406は、導電性材料により形成すればよい。第1の導電膜406に用いることができる導電性材料としては、アルミニウム、銅、チタン、タンタル及びタンゲステンなどの金属材料、並びに導電性を付与する不純物元素が添加された多結晶シリコンを例示することができるが、これらに限定されない。

**【0115】**

次に、少なくとも酸化物半導体膜404の露出された部分を覆って第1のゲート絶縁膜408を形成する（図6（D））。第1のゲート絶縁膜408は、スパッタリング法またはCVD法などにより形成すればよいが、水素、水、水酸基及び水素化物などが混入しにくい方法で形成することが好ましい。

**【0116】**

第1のゲート絶縁膜408は、下地膜402と同様の材料及び同様の方法により形成し、同程度の厚さとすることが好ましい。

**【0117】**

第1のゲート絶縁膜408の形成後には熱処理を行うことが好ましい。特に、第1のゲート絶縁膜408をCVD法により形成する場合には、形成後に熱処理を行うことが好ましい。形成ガスに水素などが含まれていることが多いからである。なお、該熱処理は、基板温度400～800で行えばよく、好ましくは基板温度650近傍で行う。

**【0118】**

なお、本実施の形態の半導体装置の作製方法では、下地膜402及び第1のゲート絶縁膜408の一方または双方が酸素の供給源として機能する。しかし、水素、水、水酸基及び水素化物などを除去する熱処理を行うと、酸素もとともに脱離してしまう。そのため、水素、水、水酸基及び水素化物などを除去する熱処理を行う場合には、第1のゲート絶縁膜408の熱処理後に酸素の添加を行うことが好ましい。酸素の添加は、例えばドーピングにより行えばよい。

**【0119】**

10

20

30

40

50

なお、第1のゲート絶縁膜408は積層膜であってもよい。第1のゲート絶縁膜408が積層膜である場合には、酸化物半導体膜404に接する側に酸素供給源として機能する膜を形成し、その上に酸素原子を脱離させにくい、酸素透過性の低い絶縁膜を形成するといい。このような酸素透過性の低い絶縁膜としては、酸化アルミニウム膜を例示することができる。

#### 【0120】

なお、酸化アルミニウム膜を形成する場合には、まずアルミニウム膜を形成し、該アルミニウム膜に酸素を添加すればよい。酸素の添加は、例えばドーピングにより行えばよい。このとき、酸素の添加は、第1のゲート絶縁膜408中の水素、水、水酸基及び水素化物などを熱処理により除去した後に行なうことが好ましい。

10

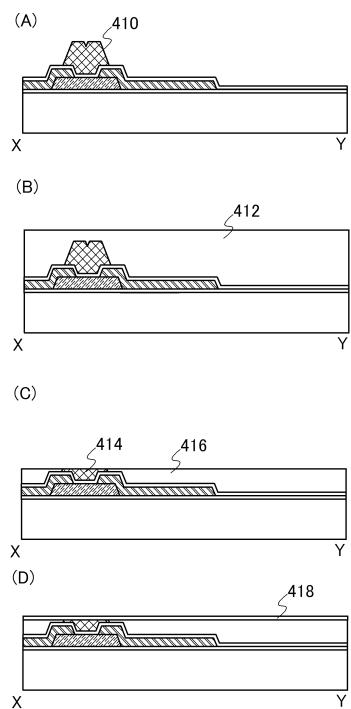

#### 【0121】

次に、酸化物半導体膜404と重畠して第1のゲート絶縁膜408上に、ゲートとして機能する第2の導電膜410を位置選択的に形成する(図7(A))。第2の導電膜410は、下地膜402及び酸化物半導体膜404上にスパッタリング法またはCVD法などにより導電膜を形成した後に、これを加工することで形成すればよい。

#### 【0122】

第2の導電膜410は、導電性材料により形成すればよい。第2の導電膜410に用いることができる導電性材料としては、アルミニウム、銅、チタン、タンタル及びタンゲステンなどの金属材料、並びに導電性を付与する不純物元素が添加された多結晶シリコンを例示することができるが、これらに限定されない。

20

#### 【0123】

次に、上記したように形成した層のすべてを覆って絶縁膜412を形成する(図7(B))。絶縁膜の材料及び形成方法などに特に限定はないが、厚く形成することが可能な材料及び方法を用いて形成する。絶縁膜412は、少なくとも、第2の導電膜410よりも厚く形成する。

#### 【0124】

次に、絶縁膜412をCMP法またはエッチングなどにより、絶縁膜412の表面が平坦となるように加工しつつ(削りつつ)、第2の導電膜410を露出させる。ここで、第2の導電膜410が削られてもよい(図7(C))。削られた第2の導電膜410を第2の導電膜414と呼び、削られた絶縁膜412を絶縁膜416と呼ぶ。

30

#### 【0125】

次に、第2のゲート絶縁膜418を形成する(図7(D))。

#### 【0126】

第2のゲート絶縁膜418は、第3の層304の下地膜でもあり、下地膜402と同様の材料及び同様の方法により形成し、同程度の厚さとすることが好ましい。

#### 【0127】

以上説明したように、第4の層306の第2のゲート絶縁膜418までを形成することができる。その後、同様の工程を経て適宜コンタクトホールを形成することで、図5に示すような積層の半導体装置を形成することができる。

#### 【0128】

本発明の一態様は、多段のインバータを有するものであれば、あらゆる電子機器に適用することができる。

#### 【符号の説明】

#### 【0129】

100 回路

102 第1の回路

104 第2の回路

106 第3の回路

108 第4の回路

110 最終段の回路

40

50

|       |              |    |

|-------|--------------|----|

| 1 1 2 | 第 1 の配線      |    |

| 1 1 4 | 第 2 の配線      |    |

| 1 1 6 | 第 3 の配線      |    |

| 1 2 0 | 第 1 の容量素子    |    |

| 1 2 2 | 第 1 のトランジスタ  |    |

| 1 2 4 | 第 2 のトランジスタ  |    |

| 1 2 6 | 第 3 のトランジスタ  |    |

| 1 3 0 | 第 2 の容量素子    |    |

| 1 3 2 | 第 4 のトランジスタ  | 10 |

| 1 3 4 | 第 5 のトランジスタ  |    |

| 1 3 6 | 第 6 のトランジスタ  |    |

| 1 4 0 | 第 3 の容量素子    |    |

| 1 4 2 | 第 7 のトランジスタ  |    |

| 1 4 4 | 第 8 のトランジスタ  |    |

| 1 4 6 | 第 9 のトランジスタ  |    |

| 1 5 0 | 第 4 の容量素子    |    |

| 1 5 2 | 第 10 のトランジスタ |    |

| 1 5 4 | 第 11 のトランジスタ |    |

| 1 5 6 | 第 12 のトランジスタ |    |

| 1 6 0 | 第 5 の容量素子    | 20 |

| 1 6 2 | 第 13 のトランジスタ |    |

| 1 6 4 | 第 14 のトランジスタ |    |

| 1 6 6 | 第 15 のトランジスタ |    |

| 1 7 1 | 第 1 の同電位部    |    |

| 1 7 2 | 第 2 の同電位部    |    |

| 1 7 3 | 第 3 の同電位部    |    |

| 1 7 4 | 第 4 の同電位部    |    |

| 1 8 1 | 第 1 の共有電極    |    |

| 1 8 2 | 第 2 の共有電極    |    |

| 1 8 3 | 第 3 の共有電極    | 30 |

| 1 8 4 | 第 4 の共有電極    |    |

| 1 8 5 | 第 5 の共有電極    |    |

| 1 8 6 | 第 6 の共有電極    |    |

| 2 0 0 | コンタクトホール     |    |

| 2 0 2 | コンタクトホール     |    |

| 2 0 4 | コンタクトホール     |    |

| 2 0 6 | コンタクトホール     |    |

| 2 0 8 | コンタクトホール     |    |

| 2 1 0 | コンタクトホール     |    |

| 2 1 2 | コンタクトホール     | 40 |

| 2 1 4 | コンタクトホール     |    |

| 2 1 6 | コンタクトホール     |    |

| 2 1 8 | コンタクトホール     |    |

| 2 2 0 | コンタクトホール     |    |

| 2 2 2 | コンタクトホール     |    |

| 2 2 4 | コンタクトホール     |    |

| 2 2 6 | コンタクトホール     |    |

| 2 2 8 | コンタクトホール     |    |

| 2 3 0 | コンタクトホール     |    |

| 2 3 2 | コンタクトホール     | 50 |

|       |           |    |

|-------|-----------|----|

| 2 3 4 | コンタクトホール  |    |

| 2 3 6 | コンタクトホール  |    |

| 3 0 0 | 第1の層      |    |

| 3 0 2 | 第2の層      |    |

| 3 0 4 | 第3の層      |    |

| 3 0 6 | 第4の層      |    |

| 3 0 8 | 第5の層      |    |

| 3 1 0 | 第6の層      |    |

| 4 0 0 | 被形成物      |    |

| 4 0 2 | 下地膜       | 10 |

| 4 0 4 | 酸化物半導体膜   |    |

| 4 0 6 | 第1の導電膜    |    |

| 4 0 8 | 第1のゲート絶縁膜 |    |

| 4 1 0 | 第2の導電膜    |    |

| 4 1 2 | 絶縁膜       |    |

| 4 1 4 | 第2の導電膜    |    |

| 4 1 6 | 絶縁膜       |    |

| 4 1 8 | 第2のゲート絶縁膜 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

| (51)Int.Cl.              | F I           |  |   |

|--------------------------|---------------|--|---|

| H 0 1 L 21/822 (2006.01) | H 0 1 L 27/04 |  | A |

| H 0 1 L 27/04 (2006.01)  | H 0 3 K 3/03  |  |   |

| H 0 3 K 3/03 (2006.01)   |               |  |   |

(56)参考文献 特開平09-036729 (JP, A)

特開2011-119718 (JP, A)

特開2000-132975 (JP, A)

特開平08-083486 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |               |

|---------|---------------|

| H 0 3 K | 3 / 3 5 4     |

| H 0 1 L | 2 1 / 8 2 2   |

| H 0 1 L | 2 1 / 8 2 3 4 |

| H 0 1 L | 2 7 / 0 4     |

| H 0 1 L | 2 7 / 0 8     |

| H 0 1 L | 2 7 / 0 8 8   |

| H 0 1 L | 2 9 / 7 8 6   |

| H 0 3 K | 3 / 0 3       |