# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2012/0267148 A1 LIN et al.

#### Oct. 25, 2012 (43) **Pub. Date:**

## (54) CIRCUIT BOARD

(75) Inventors: YU-HSU LIN, Santa Clara, CA (US); JENG-DA WU, Tu-Cheng

(TW); CHIH-HANG CHAO,

Tu-Cheng (TW)

(73) Assignee: HON HAI PRECISION

INDUSTRY CO., LTD., Tu-Cheng

(21) Appl. No.: 13/536,988

(22) Filed: Jun. 28, 2012

## Related U.S. Application Data

(62) Division of application No. 12/645,303, filed on Dec. 22, 2009, now Pat. No. 8,256,111.

#### (30)Foreign Application Priority Data

Dec. 22, 2006 (CN) ...... 200610157882.8

## **Publication Classification**

(51)Int. Cl. H05K 1/02 (2006.01)

(52)

(57)**ABSTRACT**

A circuit board includes a signal plane and a ground plane. The signal plane is configured to have a plurality of signal traces. Each of the signal traces includes a plurality of straight line segments. Each line segment extends along a path different from the others. The ground plane includes a plurality of tiles connected in an array. Each tile is formed by ground traces. The straight line segments of each signal trace mapped on the ground plane are arranged at an angle relative to any one ground trace of the tiles. The angle is defined within a range determined by one of ground traces of a tile and an adjacent diagonal line of the tile. A method for laying out such a circuit board is also provided.

FIG. 1 (PRIOR ART)

FIG. 2 <PRIOR ART>

FIG. 3 (PRIOR ART)

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

## CIRCUIT BOARD

#### CROSS-REFERENCE

[0001] This is a division case of the U.S. patent application Ser. No. 12/645,303 filed on Dec. 22, 2009 and entitled "CIRCUIT BOARD LAYOUT METHOD".

#### BACKGROUND

[0002] 1. Technical Field

[0003] The disclosure relates to circuit boards and layout methods, particularly to a circuit board with an improved ground plane and a method for laying out such a circuit board.

[0004] 2. Description of Related Art

[0005] Circuit boards such as printed circuit boards (PCBs) are widely used in conventional electronic devices. In design of a contemporary PCB, trace impedance control is very important. The impedance relates to a number of parameters, such as the widths and distances of signal traces, and the thicknesses of media layers of the PCB. For example, in a circuit board including a signal plane for signal traces arranged thereon and a ground plane for ground traces arranged thereon, a media layer is disposed between the signal plane and the ground plane. Often, the media layer is thin enough that the impedance of the signal traces is affected, deteriorating signal quality of the circuit board.

[0006] What is needed, therefore, is a circuit board having sufficient signal trace impedance for improving signal quality.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0007] The disclosure is illustrated by way of example and not by way of limitation in the figures of the accompanying drawings in which like references indicate similar elements. It should be noted that references to "an" or "one" embodiment in this disclosure are not necessarily to the same embodiment, and such references mean at least one.

[0008] FIG. 1 is a top view of one embodiment of a circuit board, according to the prior art, with a conventional ground plane, and with straight line segments of signal traces mapped thereon.

[0009] FIG. 2 is a top view of one embodiment of a circuit board, according to the prior art, with a conventional ground plane, and with straight line segments of signal traces mapped thereon.

[0010] FIG. 3 is a top view of one embodiment of a circuit board, according to the prior art, with a conventional ground plane, and with straight line segments of signal traces mapped thereon.

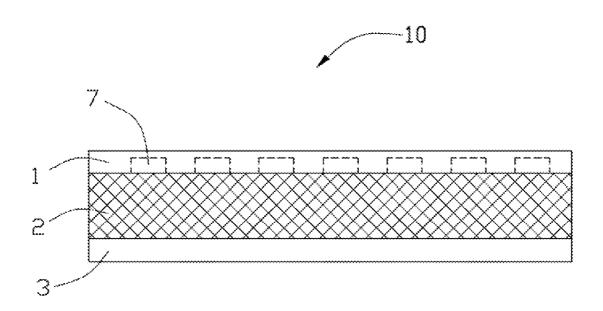

[0011] FIG. 4 is a cutaway view of a circuit board in accordance with one embodiment, including a signal plane with a plurality of signal traces arranged thereon, and a ground plane, and a media layer disposed therebetween.

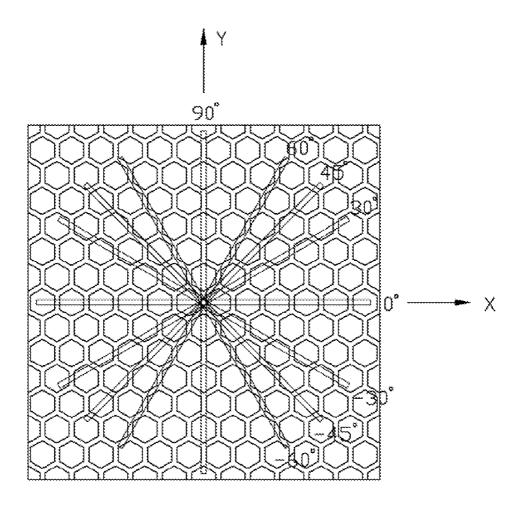

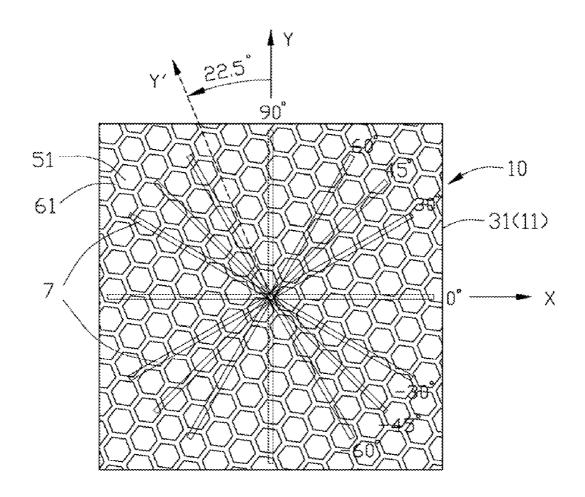

[0012] FIG. 5 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

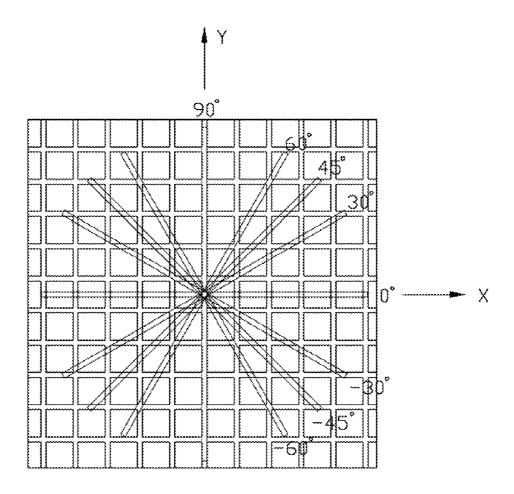

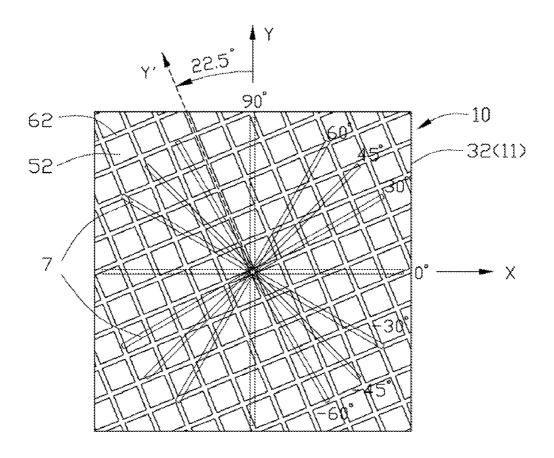

[0013] FIG. 6 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

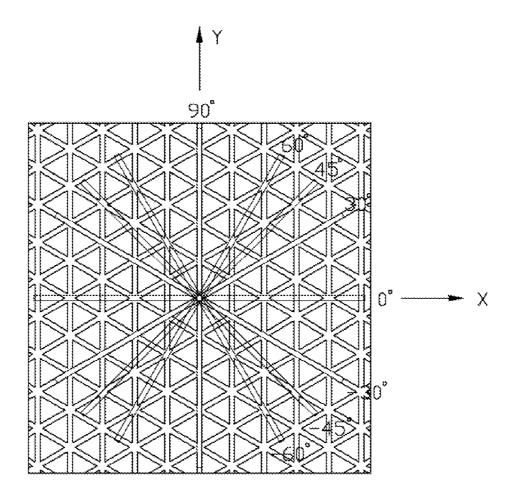

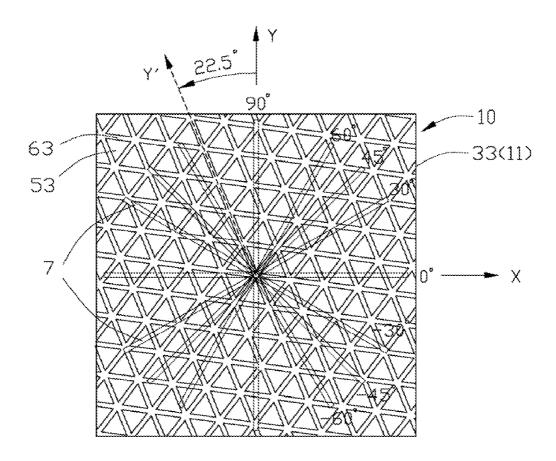

[0014] FIG. 7 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

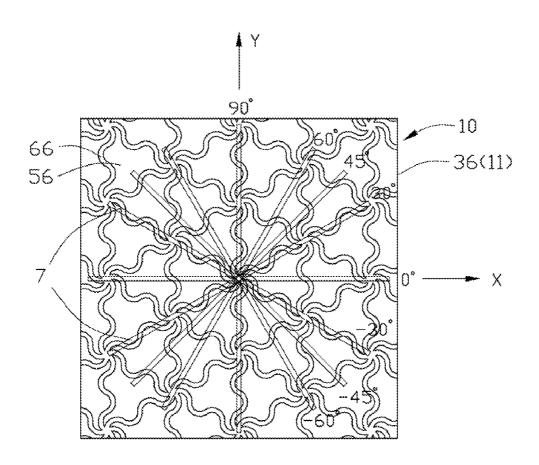

[0015] FIG. 8 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

[0016] FIG. 9 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

[0017] FIG. 10 is a top view of one embodiment of a circuit board with an improved ground plane, and with straight line segments of signal traces mapped thereon.

[0018] FIG. 11 is a top view of a flexible printed circuit (FPC) board with a ground plane in accordance with one embodiment, and with straight line segments of a signal trace mapped on the ground plane.

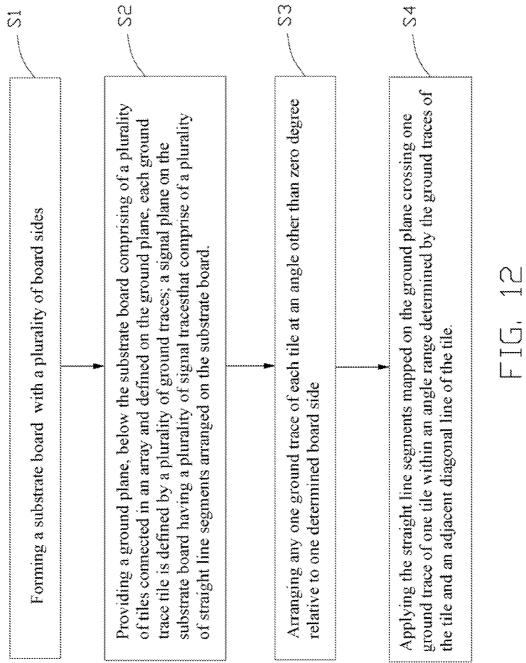

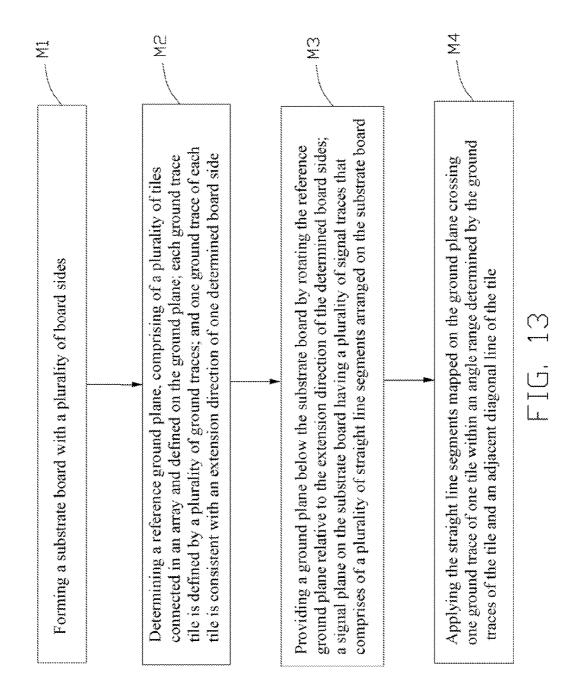

[0019] FIG. 12 and FIG. 13 are flow charts of methods for laying out circuit boards.

## DETAILED DESCRIPTION

[0020] In order to achieve a desired signal impedance of the circuit board, a ground plane formed by an array of samesized equilateral hexagonal, square, or equilateral triangular tiles (as shown in FIGS. 1-3 respectively) is typically adopted. Each tile is formed by ground traces. The ground plane defines an X-axis along which a straight line segment of a signal trace is arranged. Generally, each straight line segment of a signal trace is arranged on the signal plane at an angle of 0, 30, 45, 60, 90, -30, -45 or  $-60^{\circ}$  relative to the X-axis of the ground plane (as shown in FIGS. 1-3). The ground traces are also arranged at angles of 0, 30, 45, 60, 90, -30, -45 or  $-60^{\circ}$ relative to the X-axis of the ground plane. In designing a PCB using the preceding arrangement, some line segments of a signal trace will cross ground traces of the ground plane at an angle causing only slight variation in impedance of the signal trace. However, to the detriment of signal trace performance, some portion or portions of a signal trace line segment will be coincident with a ground trace or traces of the ground plane, causing the impedance of that portion or portions of the signal trace line segment to be greatly reduced. Thus, the impedance of the signal trace will vary unevenly and affect signal quality. [0021] FIG. 4 shows a circuit board 10 with a ground plane 3 for improving signal quality. The circuit board 10 in accordance with one embodiment includes a signal plane 1 with a plurality of signal traces 7 arranged thereon and a ground plane 3 for a plurality of ground traces arranged thereon. Each signal trace 7 includes a plurality of straight line segments. A media layer 2 is disposed between the signal plane 1 and the ground plane 3.

[0022] Referring to FIGS. 5-11, the circuit board 18 includes a plurality of sides 11. Referring to FIG. 5, a ground plane 31 of the circuit board 10 in accordance with one embodiment is shown. The ground plane 31 includes a plurality of same-sized tiles 51 connected in an array. Each tile 51 is a polygon delimited by six equal straight ground traces 61 connected consecutively end-to-end, forming an equilateral hexagonal tile. The ground plane 31 defines an X-axis along which a straight line segment of a signal trace 7 is arranged. A Y-axis of the ground plane 31 is perpendicular to the X-axis and parallel to one side 11 of the circuit board 10. A straight line passing through one straight ground trace 61 of each tile 51 is designated as a Y'-axis of the tile 51. In the present embodiment, the Y'-axis of each tile 51 is rotated 22.5° relative to the Y-axis of the ground plane 31. Thus, the ground traces 61 are oriented on the ground plane 31 at angles of 22.5, 52.5, 67.5, 112.5, -7.5, -22.5, or -37.5° relative to the X-axis of the ground plane 31. Each straight line segment of the signal traces 7 is arranged on the signal plane 1 at an angle of 0, 30, 45, 60, 90, -30, -45 or  $-60^{\circ}$  relative to the X-axis of the ground plane 31. Thus, different portions of each line segment of a signal trace 7 mapped on the ground plane 31 are at an angle of at least 7.5° relative to any given ground trace they cross. With this arrangement, interaction between the ground traces and the signal traces is minimized to reduce impedance differences of the signal traces and cause the impedance of segments of the signal traces to vary evenly, thereby greatly improving signal quality. The ground traces 61 on the ground plane 31 may be oriented at other angles relative to the ground plane 31 to ensure segments of the signal traces 7 are not coincident with the ground traces 61.

[0023] Referring to FIG. 6, a ground plane 32 of the circuit board 10 in accordance with one embodiment is shown. The ground plane 32 of the second embodiment is similar to that of FIG. 5, but each tile of the present embodiment is a polygon delimited by four equal straight ground traces 62 connected consecutively end-to-end, forming a square tile. A Y'-axis of each tile 52 is defined by a straight line passing through one straight ground trace 52 of the square tiles. The Y'-axis of each tile is rotated 22.5° relative to the Y-axis of the ground plane 32

[0024] Referring to FIG. 7, a ground plane 33 of the circuit board 10 in accordance with one embodiment is shown. The ground plane 33 of the third embodiment is similar to that of FIG. 5, but each tile 53 of the present embodiment is a polygon delimited by three equal straight ground traces 63 connected consecutively end-to-end, forming a triangular tile. A Y'-axis of each tile 53 is defined by a straight line passing through one straight ground trace of the triangular tiles. The Y'-axis of each tile is rotated 22.5° relative to the Y-axis of the ground plane 33.

[0025] The tiles of the ground plane can be other polygonal shapes formed by ground traces oriented on the ground plane at angles to ensure segments of the signal traces are not coincident with the ground traces.

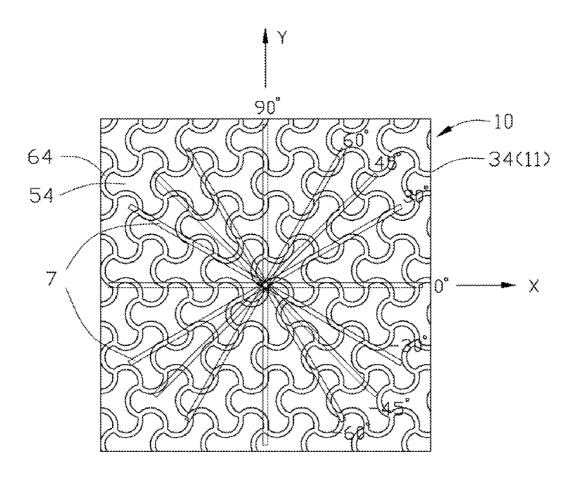

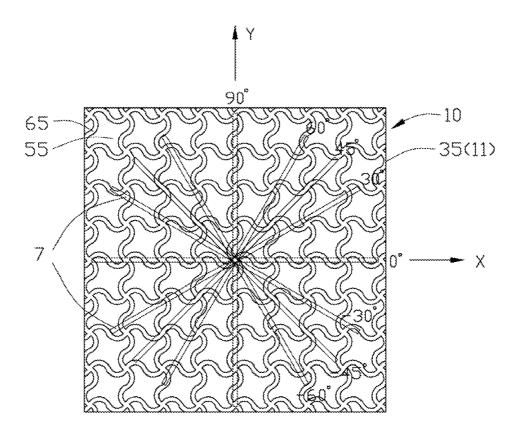

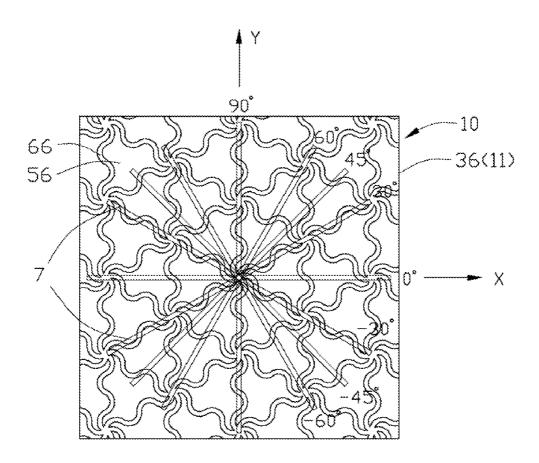

[0026] FIG. 8 shows a ground plane 34 of the circuit board 10 in accordance with one embodiment. In this embodiment, the ground plane 34 includes a plurality of same-sized and generally triangular tiles 54 with rounded convex corners and rounded concave sides. Each tile 54 is formed by curved ground traces 64.

[0027] FIG. 9 shows a ground plane 35 of the circuit board 10 in accordance with one embodiment. In this embodiment, the ground plane 35 includes a plurality of same-sized and

generally square tiles 55 with wavy sides. Each tile 55 is formed by curved ground traces 65.

[0028] Referring to FIG. 10, which shows a ground plane 36 of the circuit board 10 in accordance with one embodiment. In this embodiment, the ground plane 36 includes a plurality of same-sized and generally triangular tiles 56 with wavy sides. Each tile 56 is formed by curved ground traces 66. [0029] Accordingly, different portions of each line segment of a signal trace mapped on the ground plane will cross any given ground trace at a similar angle since the tiles are formed by curved ground traces. With this arrangement, interaction between the ground traces and the signal traces is minimized to reduce impedance differences of the signal traces and cause the impedance of segments of the signal traces to vary evenly, thereby greatly improving signal quality. The tiles of the ground plane may be formed in other shapes by curved ground traces.

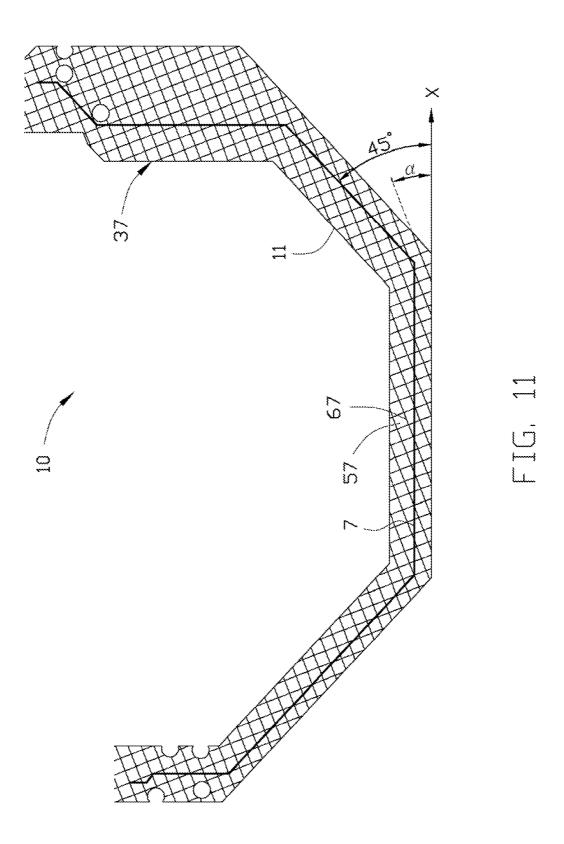

[0030] Referring to FIG. 11, in one embodiment, the circuit board 10 is a flexible printed circuit (FPC) board having a plurality of sides 11. An extending direction of one side 11 of the FPC is determined as the X-axis. The one side 11 of the FPC board 10 is characterized here as the determined side of the circuit board. In some embodiments, the line segments of the signal trace 7 may be arranged on the signal plane of the circuit board at 0, 45, or 90° relative to the X-axis (determined side of the circuit board). One of the ground traces 67 of each ground trace tile 57 is arranged at an angle a relative to the X-axis. In one embodiment, the ground trace tiles 57 are square. In another embodiment, the ground trace tiles 57 may form other polygons with equilateral sides of the same shape and size.

[0031] The following tables show impedance of different signal trace line segments when one of the ground traces of each tile is arranged at 0, 7, 10, 12.5, 17.5, 20, and 22.5° relative to the X-axis. The current embodiment illustrates the signal trace line segments arranged at 0 and 45° relative to the X-axis. That is, the angle between the signal trace line segments and the ground traces are respectively arranged at 0, 7, 10, 12.5, 17.5, 20, 22.5, 25, 27.5, 32.5, 35, 38, and 45°. The results are obtained via 3D electromagnetic software HFSS and a software HSPICE for simulating the impedance of signal traces. A 3D model of signal trace, dielectric material, mesh ground traces is created with specified angles; material properties and boundary conditions of the wave port are assigned. The software HSPICE simulates and obtains the corresponding impedance.

| Signal<br>trace angle          | Signal trace    | Ground trace angle[°] |       |       |       |       |       |       |

|--------------------------------|-----------------|-----------------------|-------|-------|-------|-------|-------|-------|

| [degree]                       | impedance [ohm] | 0                     | 7     | 10    | 12.5  | 17.5  | 20    | 22.5  |

| 0                              | Max             | 42.17                 | 58.92 | 65.74 | 58.58 | 58.20 | 57.53 | 58.11 |

|                                | Min             | 41.51                 | 50.92 | 57.96 | 53.41 | 55.92 | 57.07 | 57.53 |

| 45                             | Max             | 62.11                 | 57.90 | 65.74 | 56.84 | 58.46 | 58.23 | 58.11 |

|                                | Min             | 61.36                 | 55.62 | 57.96 | 55.49 | 57.30 | 56.61 | 57.53 |

| Average impedance [ohm]        |                 | 51.81                 | 54.92 | 61.85 | 56.00 | 57.19 | 57.42 | 57.82 |

| Deviation                      |                 | 19.88%                | 7.29% | 6.29% | 4.61% | 2.22% | 1.41% | 0.50% |

| [(Max - Average/Average)*100%] |                 |                       |       |       |       |       |       |       |

[0032] The table shows that when one of the ground traces of each tile is arranged at  $0^{\circ}$  relative to the X-axis, and the line segments of the signal traces are respectively arranged at 0 and  $45^{\circ}$  to the X-axis, that is, the line segments respectively passing through one of the ground traces of each tile and a diagonal line of the square tile, the impedance between the line segments deviates greatly. When the ground traces of the tile are arranged at an angle other than  $0^{\circ}$ , that is, the line segments of the signal traces avoid overlapping the ground traces of the tile and a diagonal line of the square tile, the impedance difference between the line segments is greatly decreased.

[0033] As shown in the table, when one of the ground traces of each tile is arranged at 22.5° relative to the X-axis (the determined side of the circuit board), the signal trace impedance between the signal trace line segments arranged at  $0^{\circ}$ relative to the X-axis (the determined side of the circuit board) and the signal trace line segments arranged at 45° relative to the X-axis (the determined side of the circuit board) deviates within 0.5%, which shows a most excellent effect to improve the signal quality. That is, when the angle between the ground traces and the signal trace line segments reaches 22.5°, the signal trace will exhibit superior signal quality. In detail, when one of the ground traces of each tile is angled from 12.5 to 22.5° relative to the X-axis (the determined side of the circuit board), the signal trace impedance between the signal trace line segments which are arranged at 0° relative to the X-axis (the determined side of the circuit board) and the signal trace line segments which are arranged at 45° relative to the X-axis (the determined side of the circuit board) deviates within 5%. That is, when the angle between the ground traces and the signal trace line segments are angled from 12.5 to 32.5 (22.5±10)°, the signal trace impedance between the signal trace line segments which are arranged at 0° relative to the X-axis (the determined side of the circuit board) and the signal trace line segments which are arranged at 45° (the determined side of the circuit board) relative to the X-axis deviates within 5%, which may meet a specific requirement for the circuit board. The impedance of the signal trace line segments arranged at different angles relative to the X-axis varies in a slight impedance value range, to ensure that the circuit board has good signal quality.

[0034] Referring to FIG. 12, a method for arranging a circuit board in accordance with one embodiment is illustrated. The method is described as follows.

[0035] In step S1, forming a substrate board with a plurality of board sides.

[0036] In step S2, providing a ground plane, below the substrate board comprising of a plurality of tiles connected in an array and defined on the ground plane, each ground trace tile defined by a plurality of ground traces; a signal plane on the substrate board having a plurality of signal traces that comprise of a plurality of straight line segments arranged on the substrate board. In one embodiment, the tiles are arranged in square or rectangular.

[0037] In step S3, arranging any one ground trace of each tile at an angle other than zero degree relative to one determined board side.

[0038] In step S4, applying the straight line segments mapped on the ground plane crossing one ground trace of one tile within an angle range determined by the ground traces of the tile and an adjacent diagonal line of the tile. In one embodiment, the one ground trace of the tile and the straight line segments of the signal traces are arranged at an angle

range from 12.5 to 32.5°; and the line segments of the signal traces are arranged at about  $0^{\circ}$ ,  $45^{\circ}$ , or  $90^{\circ}$  relative to the determined sides of the circuit board.

[0039] FIG. 13, is a method for arranging a circuit board in accordance with another embodiment. The method is described as follows.

[0040] In step M1, forming a substrate board with a plurality of board sides.

[0041] In step M2, determining a reference ground plane, comprising of a plurality of tiles connected in an array and defined on the ground plane; each ground trace tile is defined by a plurality of ground traces; and one ground trace of each tile is consistent with an extension direction of one determined board side (X-axis). In one embodiment, the tiles are arranged in square or rectangular.

[0042] In step M3, providing a ground plane below the substrate board by rotating the reference ground plane relative to the extension direction of the determined board sides; a signal plane on the substrate board having a plurality of signal traces that comprises of a plurality of straight line segments arranged on the substrate board. The reference ground plane is rotated at an angle value taken from an angle range from 12.5° to 32.5° relative to the determined board side. In one embodiment, the reference ground plane is rotated 22.5° relative to the determined board side.

[0043] In step M4, applying the straight line segments mapped on the ground plane crossing one ground trace of one tile within an angle range determined by the ground traces of the tile and an adjacent diagonal line of the tile. In one embodiment, the one ground trace of the tile and the straight line segments of the signal traces are arranged at an angle range from 12.5 to  $32.5^{\circ}$ ; and the line segments of the signal traces are arranged at about  $0^{\circ}$ ,  $45^{\circ}$ , or  $90^{\circ}$  relative to the determined sides of the circuit board.

[0044] It is to be understood, however, that even though numerous characteristics and advantages of the disclosure have been set forth in the foregoing description, together with details of the structure and function of the disclosure, the disclosure is illustrative only, and changes may be made in detail, especially in matters of shape, size, and arrangement of parts within the principles of the invention to the full extent indicated by the broad general meaning of the terms in which the appended claims are expressed.

[0045] Depending on the embodiment, certain of the method steps described may be removed, others may be added, and the sequence of steps may be altered. It is also to be understood that the description and the claims drawn to a method may include some indication in reference to certain steps. However, the indication used is only to be viewed for identification purposes and not as a suggestion as to an order for the steps.

What is claimed is:

- 1. A circuit board, comprising:

- a signal plane with a plurality of signal traces, each of the plurality of signal traces comprising a plurality of straight line segments; and

- a ground plane comprising a plurality of tiles connected in an array; each tile defined by ground traces, and the plurality of straight line segments mapped on the ground plane crossing one ground trace of one tile at an angle to minimize interaction between the ground traces and the signal traces and reduce impedance differences of the signal traces; the angle is defined within a range deter-

- mined by the ground trace of the tile and an adjacent diagonal line of the tile; and the range is from  $12.5^{\circ}$  to  $32.5^{\circ}$ .

- 2. The circuit board as described in claim 1, wherein the plurality of tiles are equilateral polygons of the same shape and size

- 3. The circuit board as described in claim 2, wherein the tiles of the ground plane are square.

- **4**. The circuit board as described in claim **3**, wherein the plurality of straight line segments are arranged at about 0°, 45°, or 90° relative to determined sides of the circuit board.

- 5. A circuit board, comprising:

- a substrate board having a plurality of board sides;

- a reference ground plane having a plurality of ground trace tiles connected in an array, each of the plurality of ground trace tiles defined by a plurality of ground traces, any one ground trace of each tile consistent with an extension direction of one determined board side;

- a ground plane below the substrate board;

- a signal plane on the substrate board having a plurality of signal traces that comprises of a plurality of straight line segments arranged on the substrate board, the plurality of straight line segments mapped on the ground plane crossing one of the plurality of ground traces within a first angle range determined by one of the plurality of ground traces of one tile and an adjacent diagonal line of the one tile, so as to minimize interaction between the ground traces and the signal traces and reduce impedance differences of the signal traces;

- wherein a second angle range defined between the reference ground plane and the one determined board side is from 12.5° to 32.5°; and an angle defined between the reference ground plane and the one determined board side is 22.5°.

- **6**. The circuit board as described in claim **5**, wherein the first angle range is from 12.5° to 32.5°.

- 7. The circuit board as described in claim 5, wherein the plurality of ground trace tiles of the ground plane in a square array or a rectangular array.

- 8. A circuit board, comprising:

- a substrate board having a plurality of board sides;

- a reference ground plane having a plurality of tiles connected in an array, each ground trace tile defined by a plurality of ground traces, each ground trace being wavy;

- a ground plane below the substrate board;

- a signal plane on the substrate board having a plurality of signal traces that comprises of a plurality of straight line segments arranged on the substrate board, the plurality of straight line segments mapped on the ground plane crossing one of the plurality of ground traces within a first angle range determined by one the plurality of ground traces of one tile and an adjacent diagonal line of the one tile, so as to minimize interaction between the ground traces and the signal traces and reduce impedance differences of the signal traces.

\* \* \* \* \*