(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

3 July 2003 (03.07.2003)

PCT

(10) International Publication Number

WO 03/054966 A1

(51) International Patent Classification<sup>7</sup>: H01L 27/12 (74) Agent: COLLOPY, Daniel, R.; Advanced Micro Devices, Inc., One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(21) International Application Number: PCT/US02/41102 (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(22) International Filing Date: 19 December 2002 (19.12.2002) (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(25) Filing Language: English (30) Priority Data: 10/023,350 20 December 2001 (20.12.2001) US

(26) Publication Language: English (71) Applicant: ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(72) Inventors: CHAN, Darin, A.; 2054 Anthony Drive, Campbell, CA 95008 (US). EN, William, G.; 495 Alexander Way, Milpitas, CA 95035 (US). PELLERIN, John, G.; 6546 Needham Lane, Austin, TX 78739 (US). MICHAEL, Mark, W.; 1805 Dayflower Trace, Austin, TX 78613 (US).

Published:

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: SOI DEVICE WITH DIFFERENT SILICON THICKNESSES

WO 03/054966 A1

(57) Abstract: A method of manufacturing a semiconductor device includes providing a silicon semiconductor layer (14) over an insulating layer (12), and partially removing a first portion of the silicon layer (14). The silicon layer (14) includes the first portion and a second portion, and a thickness of the second portion is greater than a thickness of the first portion. Initially, the first and second portions of the silicon layer (14) initially can have the same thickness. A semiconductor device is also disclosed.

## SOI DEVICE WITH DIFFERENT SILICON THICKNESSES

## FIELD OF THE INVENTION

The present invention relates to the manufacturing of semiconductor devices, and more particularly, to forming silicon on insulator devices having improved characteristics.

## BACKGROUND OF THE INVENTION

5 Over the last few decades, the semiconductor industry has undergone a revolution by the use of semiconductor technology to fabricate small, highly integrated electronic devices, and the most common semiconductor technology presently used is silicon-based. A large variety of semiconductor devices have been manufactured having various applications in numerous disciplines. One silicon-based semiconductor device is a metal-oxide-semiconductor (MOS) 10 transistor. The MOS transistor is one of the basic building blocks of most modern electronic circuits. Importantly, these electronic circuits realize improved performance and lower costs, as the performance of the MOS transistor is increased and as manufacturing costs are reduced.

15 A typical MOS device includes a bulk semiconductor substrate on which a gate electrode is disposed. The gate electrode, which acts as a conductor, receives an input signal to control operation of the device. Source and drain regions are typically formed in regions of the substrate adjacent the gate electrodes by doping the regions with a dopant of a desired conductivity. The conductivity of the doped region depends on the type of impurity used to dope the region. The typical MOS device is symmetrical, in that the source and drain are interchangeable. Whether a 20 region acts as a source or drain typically depends on the respective applied voltages and the type of device being made. The collective term source/drain region is used herein to generally describe an active region used for the formation of either a source or drain.

As an alternative to forming a MOS device on a bulk semiconductor substrate, the semiconductor layer can be formed on an insulating substrate, or over an insulation layer formed in a semiconductor substrate. This technology is referred to as Silicon-on-Insulator (SOI) technology. 25 Silicon on insulator materials offer potential advantages over bulk materials for the fabrication of high performance integrated circuits. For example dielectric isolation and reduction of parasitic capacitance improve circuit performance. Compared to bulk circuits, SOI is more resistant to radiation. For example, silicon-on-sapphire (SOS) technology has been successfully used for years to fabricate radiation-hardened complimentary MOS (CMOS) circuits for military applications. 30 Circuit layout in SOI can also be greatly simplified and packing density greatly increased if the devices are made without body contacts in which the body regions of these devices are "floating".

A disadvantage of many SOI devices is the lack of a bulk silicon or body contact to the MOS transistor. If the channel/body region is left "floating", various hysteresis effects can prevent proper circuit operation. These effects include the so-called "kink" effect and the parasitic lateral bipolar action. Partially-depleted devices are such that the maximum depletion width in the body is 5 smaller than the thickness of the semiconductor Si layer, and a quasi-neutral region results which has a floating potential. These floating body effects may result in undesirable performance in SOI devices.

MOS devices using SOI structure typically fall in one of two groups depending on the type of dopants used to form the source, drain and channel regions. The two groups are often referred to 10 as n-channel and p-channel devices. The type of channel is identified based on the conductivity type of the channel which is developed under the transverse electric field. In an n-channel MOS (NMOS) device, for example, the conductivity of the channel under a transverse electric field is of the conductivity type associated with n-type impurities (e.g., arsenic or phosphorous). Conversely, the channel of a p-channel MOS (PMOS) device under the transverse electric field is associated with 15 p-type impurities (e.g., boron).

One consideration when manufacturing NMOS and PMOS SOI transistors is maintaining a proper channel length. The channel length can be shortened, for example, if the source/drain regions are exposed to excessive temperature and/or time during activation. This causes excess lateral diffusion of the dopants, which causes the channel length to shorten. NMOS and PMOS transistors 20 are formed on a single chip and are therefore exposed to the same temperature/time profile during dopant activation. However, because the NMOS and PMOS transistors are formed using different dopants, which likely have different diffusion characteristics, the temperature/time profile for at least one of the NMOS or PMOS transistors will not be optimized.

Another consideration when forming transistors on a SOI structure is the formation of both 25 fully depleted and partially depleted transistors. In a fully depleted transistor, the source/drain regions extend all the way through the silicon layer to the insulator, and in a partially depleted transistor, the source/drain regions extend partially through the silicon layer. One difference between a partially depleted transistor and fully depleted transistor is that the threshold voltage to obtain a drive or on current through a fully depleted transistor is lower than the threshold voltage for 30 a partially depleted transistor. Accordingly, a need exists for an improved method of forming devices on an SOI structure that allows for improved performance, minimization of floating body effects, and allows for separate optimization of separate transistors formed on the SOI structure.

## SUMMARY OF THE INVENTION

This and other needs are met by embodiments of the present invention which provide a method of manufacturing a semiconductor device that improves performance, minimizes floating body effects, and allows for separate optimization of separate transistors formed on an SOI structure.

5 The method includes providing a silicon semiconductor layer over an insulating layer, and partially removing a first portion of the silicon layer. The silicon layer includes the first portion and a second portion, and a thickness of the second portion is greater than a thickness of the first portion. Initially, the first and second portions of the silicon layer can initially have the same thickness.

In another aspect of the invention, the first portion of the silicon layer is partially removed 10 by etching. The partial removal of the first portion of the silicon layer can also include depositing a resist over the silicon layer and exposing and developing the resist to expose the first portion of the silicon layer. The thickness of the first portion is determined by etching the first portion for a predetermined length of time.

In still another aspect of the invention, the first portion of the silicon layer is partially 15 removed by oxidizing the first portion of the silicon layer and removing the oxidized silicon. The partial removal of the first portion of the silicon layer can also include depositing a mask layer and a resist over the silicon layer and exposing and developing the resist to expose a portion of the mask layer over the first portion of the silicon layer and removing the mask layer over the first portion of the silicon layer. After partially removing the first portion, the mask layer can then be removed.

20 Isolating features can be formed before or after the first portion of the silicon layer is partially removed. Also, a first transistor can be formed in the first portion and a second transistor can be formed in the second portion. The first transistor can be a fully depleted transistor, and the second transistor can be a partially depleted transistor. Also, the first transistor can include source/drain regions formed with a first dopant and the second transistor can include source/drain 25 regions formed with a second dopant, and the diffusivity of the second dopant into silicon is greater than the diffusivity of the first dopant into silicon.

In another embodiment of the present invention, a semiconductor device is provided. The semiconductor device includes an insulating layer and a silicon semiconductor layer over the insulating layer. The silicon layer includes a first portion and a second portion, and a thickness of 30 the second portion is greater than a thickness of the first portion.

Additional advantages of the present invention will become readily apparent to those skilled in this art from the following detailed description, wherein only the preferred embodiment of the present invention is shown and described, simply by way of illustration of the best mode contemplated for carrying out the present invention. As will be realized, the present invention is

capable of other and different embodiments, and its several details are capable of modifications in various obvious respects, all without departing from the invention. Accordingly, the drawings and description are to be regarded as illustrative in nature, and not as restrictive.

#### BRIEF DESCRIPTION OF THE DRAWINGS

5 Reference is made to the attached drawings, wherein elements having the same reference numeral designations represent like elements throughout, and wherein:

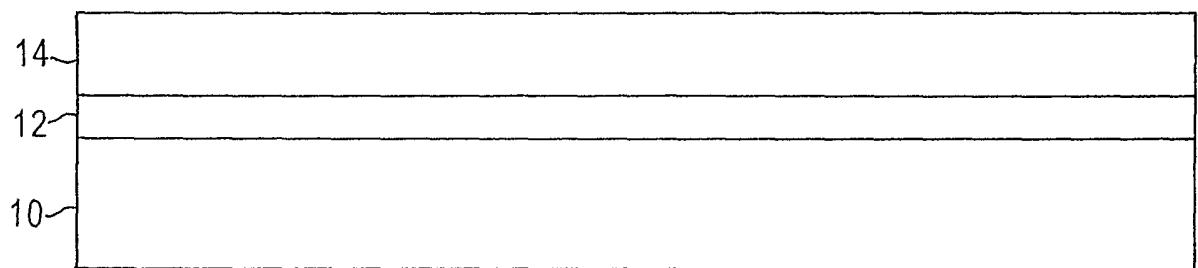

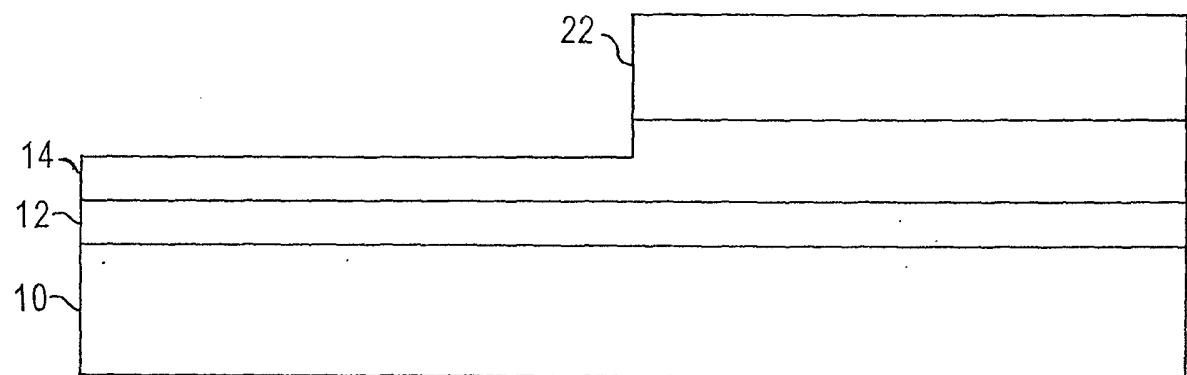

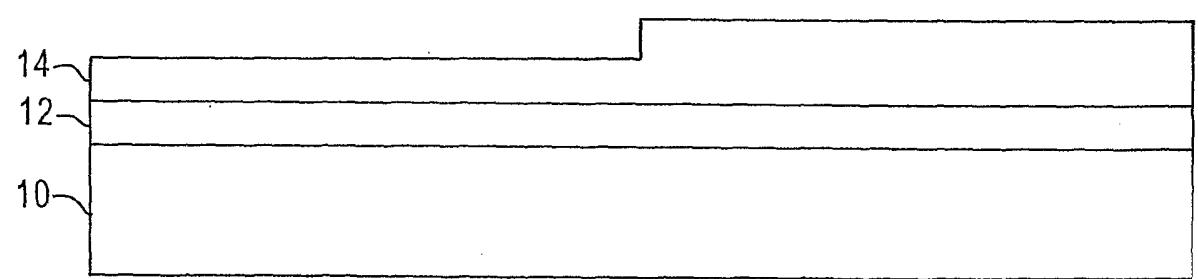

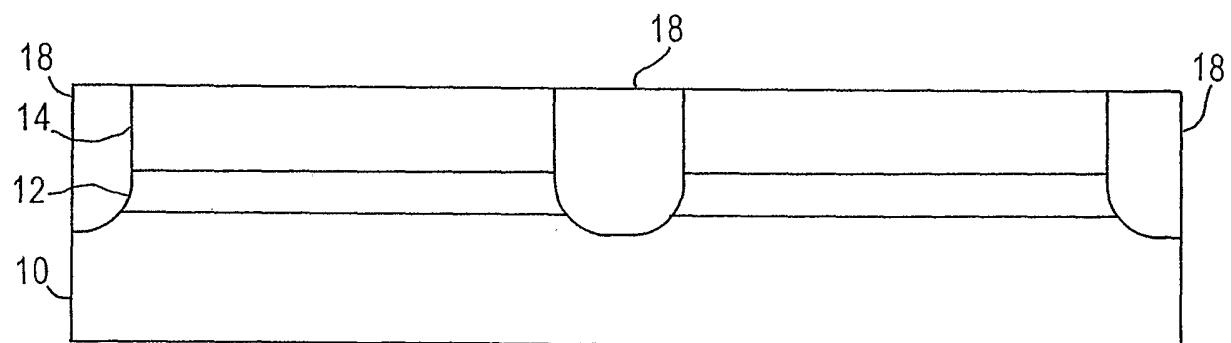

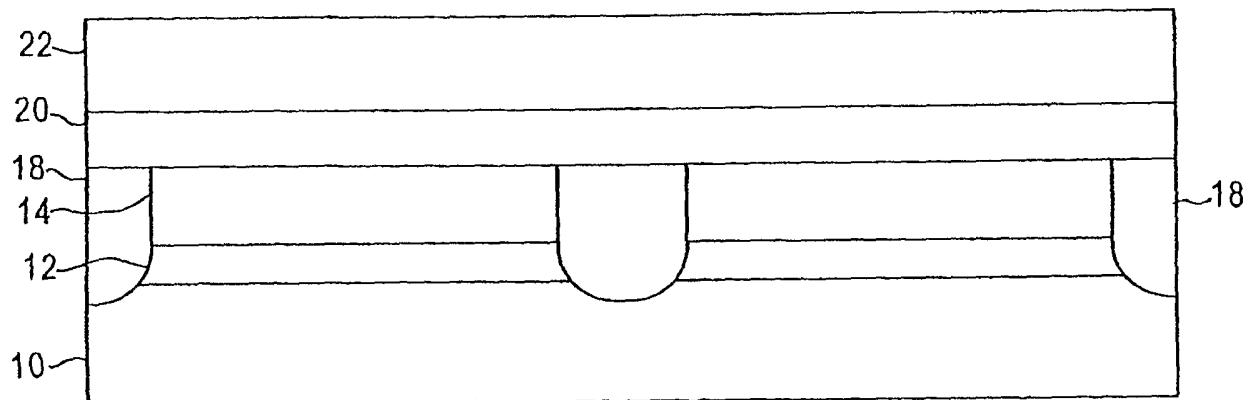

Figures 1A-1D schematically illustrate sequential phases of a SOI fabrication method according to one embodiment of the present invention.

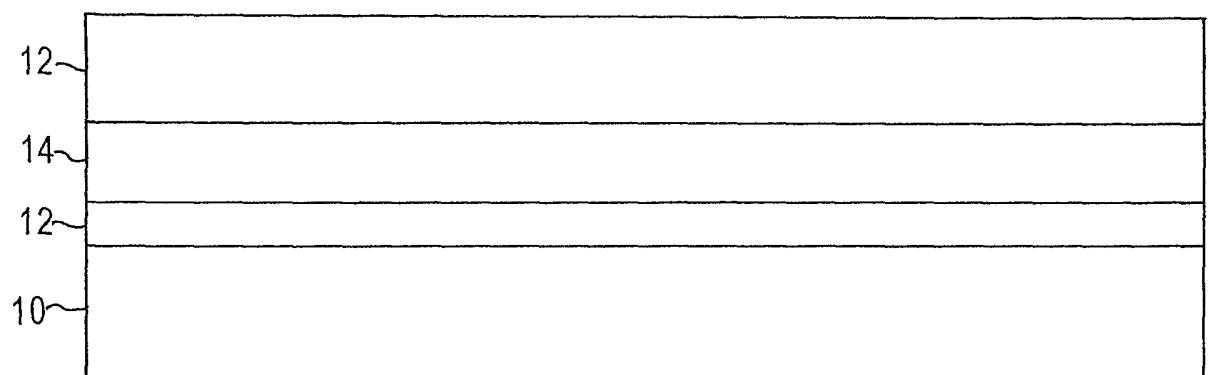

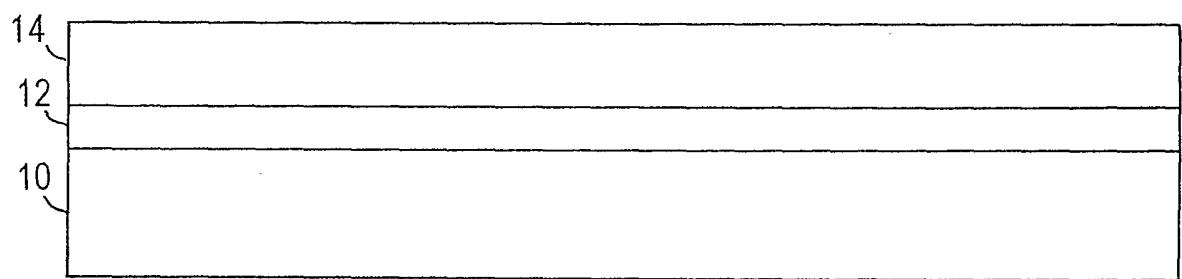

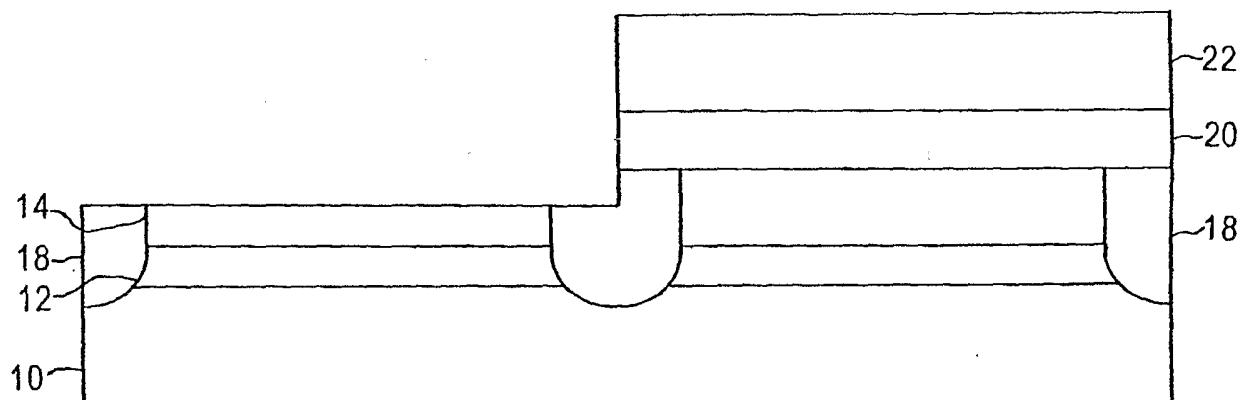

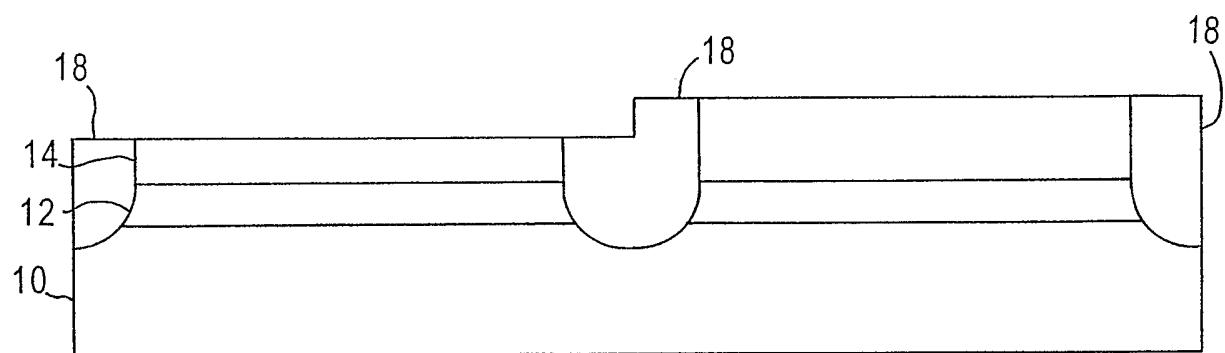

10 Figures 2A-2D schematically illustrate sequential phases of a SOI fabrication method according to another embodiment of the present invention.

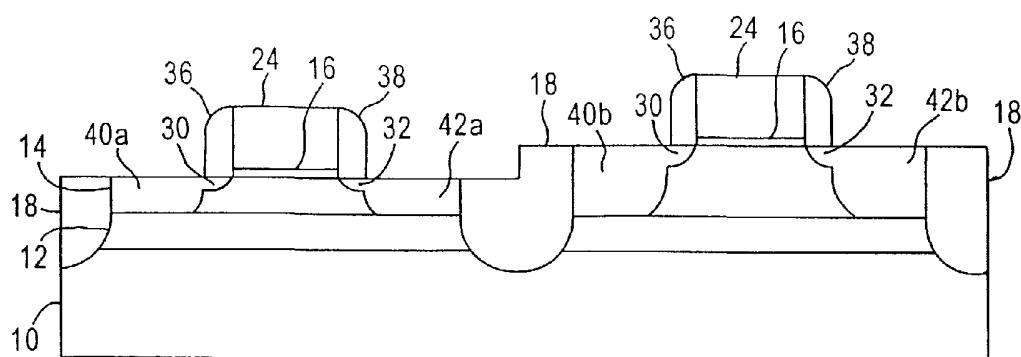

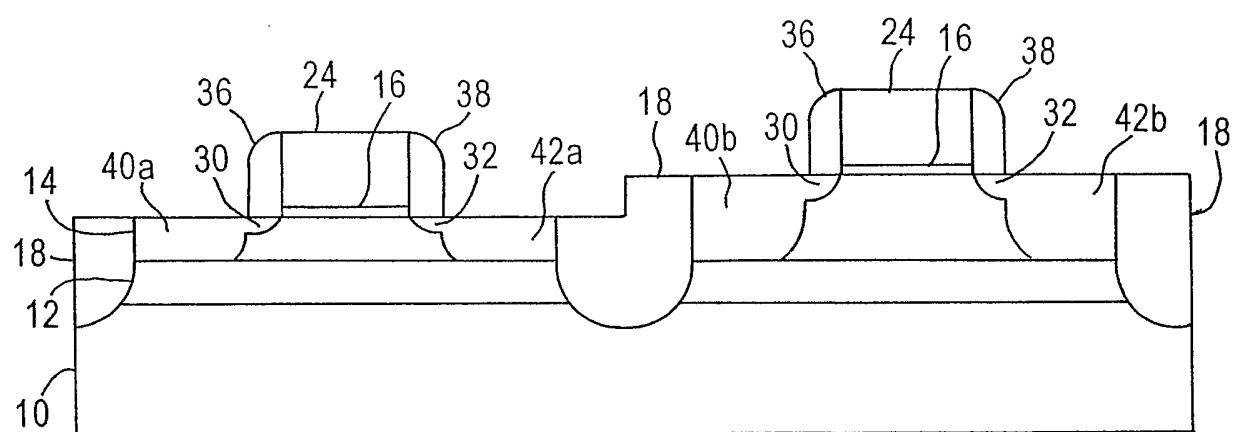

Figure 3 schematically illustrates a SOI semiconductor device having different portions with silicon layers having different thicknesses.

Figure 4 illustrates the semiconductor device of Figure 3 after features are formed on the silicon layers having different thicknesses.

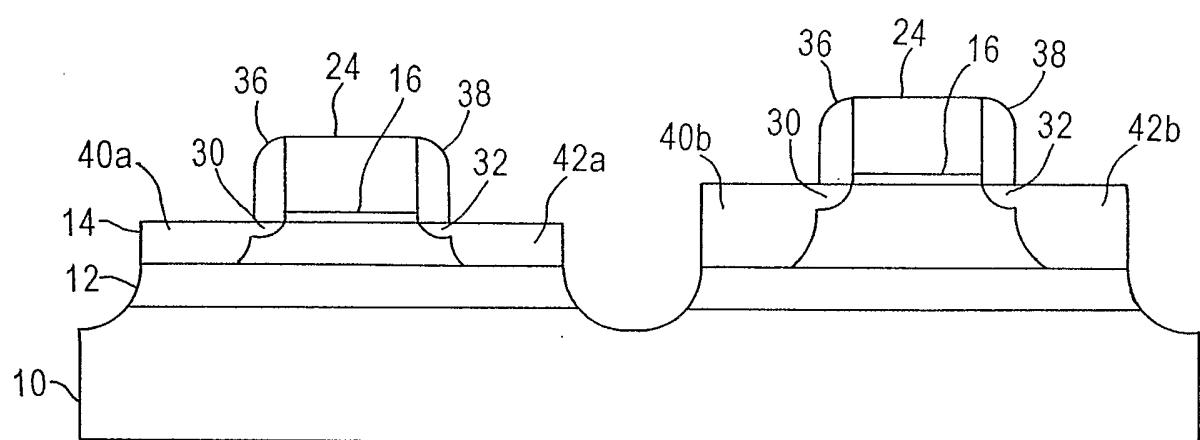

15 Figure 5 schematically illustrates a SOI semiconductor device in which the isolating regions are removed.

#### DETAILED DESCRIPTION OF THE INVENTION

The present invention improves performance, reduces floating body effects, and allows for separate optimization of separate transistors formed on an SOI structure. This is achieved, in part, 20 by providing a semiconductor device having different portions, with each portion having a silicon semiconductor layer of the SOI structure, and a thickness of one portion of the silicon layer differing from another portion of the silicon layer. In so doing, the thickness of each portion of the silicon layer can be optimized depending upon factors, such as whether a transistor formed on the SOI structure is to be partially or fully depleted and the diffusion characteristics of the dopants used to 25 form the transistors.

Embodiments of the present invention are illustrated in Figs. 1-5. Figs. 1A and 2A illustrate a conventional SOI structure. The SOI structure includes a silicon semiconductor layer 14 above an insulator layer 12. The SOI structure is then positioned over a substrate 10. The invention is not limited as to the manner in which the SOI structure is formed. For example, one method of forming 30 an SOI structure involves implanting heavy doses of oxygen into the substrate 10. The substrate 10 is then subjected to an annealing process, which forms a silicon oxide insulator layer 12 and the silicon layer 14 above the insulator layer 12. Another method of forming an SOI structure includes a technique termed wafer bonding in which the SOI structure is bonded onto a substrate 10. The

substrate 10 can be formed from any material suitable for use with an SOI structure, for example, metal substrates have been contemplated. However, in one aspect, the substrate 10 is formed from silicon.

The insulator layer 12 can be formed from any material suitable for use with an SOI structure. For example, sapphire and  $\text{Si}_3\text{N}_4$  are materials known to be acceptable for use with an SOI structure. However, in certain aspects, the insulator layer 12 is formed from  $\text{SiO}_2$ . Although not limited in this manner, the insulator layer 12 can have a thickness from about 100 to 500 nanometers.

The silicon layer 14 is formed above the insulator layer 12, and the silicon layer 14 is not limited as to a particular thickness. However, in a current aspect of the present invention, the thickness of the silicon layer 14 can be optimized for particular individual devices formed on the wafer. In this manner, a semiconductor device can be provided with different portions, each portion having a silicon layer 14 with a thickness that differs from another portion. The invention is also not limited in the manner in which the thickness of the silicon layer 14 of each portion is modified. Two exemplary methods of modifying the thickness of the silicon layer 14 are respectively illustrated in Figs. 1A-D and 2A-D.

In Fig. 1B, a photoresist 22 is formed over the silicon layer 14, and in Fig. 1C, the photoresist 22 is selectively irradiated using a photolithographic system, such as a step and repeat optical projection system, in which ultraviolet light from a mercury-vapor lamp is projected through a first reticle and a focusing lens to obtain a first image pattern. The photoresist 22 is then developed, and the irradiated portions of the photoresist 22 are removed to provide openings in the photoresist 22. The openings expose portions of the silicon layer 14, which will thereby define the portions of the silicon layer 14 having a modified thickness. An etch, typically anisotropic, although not limited in this manner, is then applied to remove a certain thickness of the exposed portions of the silicon layer 14.

In Fig. 1D, the remaining photoresist 22 is removed, and a semiconductor device precursor having different portions with a silicon layer 14 of different respective thicknesses is provided. Once the photoresist 22 is removed, as shown in Fig. 3, isolation features 18 can be provided in the silicon layer 14. The invention, however, is not limited in the manner in which the isolation features 18 are formed. For example, a shallow isolation trench can be formed by etching either isotropically with wet techniques or anisotropically with dry etch techniques. An oxide is thereafter deposited within the trench. As an alternative to the shallow isolation trench, a field oxide can be formed. A field oxide is typically formed via thermal oxidation in an oxygen-steam ambient at temperatures from about 850 to 1050°C. A patterned, oxidation-resistant mask can be used to prevent oxidation

of non-isolation device regions. After formation of the field oxide, the mask is removed using known techniques, for example hot phosphoric acid for a silicon nitride mask or buffered hydrofluoric acid for a pad oxide mask.

Alternatively, as illustrated in Figs. 2A-2D, the isolation features 18 can be formed before the thickness of certain portions of the silicon layer 14 are modified. Furthermore, as also illustrated in Figs. 2A-2D, a hard mask can be formed over the silicon layer 14 to aid in etching of the silicon layer 14. As illustrated in Fig. 2B, the isolation features 18 are formed in the silicon layer 14, and as described above, the invention is not limited in the manner in which the isolation features 18 are formed.

In Fig. 2C, a mask layer 20 is formed over the silicon layer 14, and the invention is not limited as to a particular mask layer 20. For example, the mask layer 20 can be formed from an anti-reflective film, which can be advantageously used during fine line patterning. In a current aspect, the mask layer 20 is formed from silicon nitride.

Upon formation of the mask layer 20, a photoresist 22 is formed over the mask layer 20. In Fig. 2D, the photoresist 22 is selectively irradiated using a photolithographic system, such as a step and repeat optical projection system, in which ultraviolet light from a mercury-vapor lamp is projected through a first reticle and a focusing lens to obtain a first image pattern. The photoresist 22 is then developed, and the irradiated portions of the photoresist 22 are removed to provide openings in the photoresist 22. The openings expose portions of the mask layer 20. A portion of the exposed mask layer 20 below the openings in the photoresist 22 is then removed, which exposes portions of the silicon layer 14 to be modified.

After portions of the mask layer 20 have been removed, the exposed portions of the silicon layer 14 are partially removed, and the invention is not limited in the manner in which the exposed portions of the silicon layer 14 are partially removed. For example, the exposed portions of the silicon layer 14 can be partially removed using an etch, such as an anisotropic etch. The amount of the exposed portions of the silicon layer 14 being removed can be determined, for example, by subjecting the exposed portions of the silicon layer 14 to the etch for a given time, as the removal rate of silicon for a given etchant is known. Another example of partially removing exposed portions of the silicon layer 14 involves oxidizing the exposed portions of the silicon layer 14 to form silicon oxide. The silicon oxide can then be removed leaving only the silicon layer 14. An advantage of using this process is that the consumption of silicon to form silicon oxide can be very closely controlled, and this allows for precise control of the partial removal of the exposed portions of the silicon layer 14.

As illustrated in Fig. 3, after the remaining mask layer 20 and photoresist 22 is removed using techniques known to those skilled in the art, a semiconductor device having different portions, with each portion having a silicon layer 14 with a thickness that differs from another portion, is provided. Once the thickness of certain portions of the silicon layer 14 has been modified, features, 5 such as transistors although not limited in this manner, can be formed in the silicon layer 14, as illustrated in Fig. 4.

The features, for example, can include a gate dielectric 16 and a gate electrode 24 over the gate dielectric 16. Sidewall spacers 36, 38 can be formed on sidewalls 26, 28 of the gate electrode 24, and source/drain extensions 30, 32 can be formed in the silicon layer 14 underneath the sidewall 10 spacers 36, 38. Furthermore, source/drain regions 40, 42 can be formed in the silicon layer 14. As shown, the source/drain regions 40a, 42a in a first portion of the semiconductor device can have different depths than the source/drain regions 40b, 42b in a second portion of the semiconductor device.

In Fig. 5, the isolation features 18 can be removed, and the invention is not limited as to the 15 manner in which the isolation features 18 are removed. For example, the isolation features 18 can be removed using an etchant having a high selectivity to the material with which the isolation features 18 are formed. By removing the isolation features 18, the silicon layer 14 between the isolation features 18 can be relaxed. During formation of the isolation features 18, the silicon layer 14 is stressed, and this stressing of the silicon layer 14 can degrade transistor performance. 20 Furthermore, it is noted that the removal of the relaxing of the silicon layer 14, for example by removing the isolation features between adjacent silicon layers 14, is not limited to semiconductor devices having portions with different depths. For example, the relaxing of the silicon layer 14 can occur for semiconductor devices having a silicon layer 14 with a single depth.

By providing a semiconductor device having different portions, with each portion having a 25 silicon layer with a thickness that differs from another portion, the formation of NMOS and PMOS transistors can be optimized. For example, a transistor with a dopant (e.g., boron) that has a greater diffusion rate in silicon can be formed on a portion of the silicon layer having a greater thickness than a portion of the silicon layer upon which another transistor, with a dopant (e.g., arsenic) with a lower diffusion rate, is formed. Thus, the NMOS and PMOS transistors can both be exposed to an 30 optimal temperature/time profile.

Another advantage of providing a semiconductor device having different portions, with each portion having a silicon layer with a thickness that differs from another portion, is that both fully and partially depleted transistors can be easily formed. For example, a partially depleted transistor can be formed on a portion of the silicon layer having a greater thickness, and a fully depleted transistor

can be formed on a portion of the silicon layer with a lesser thickness. Thus, even if the source/drain regions extend down to the same depth, both partially and fully depleted transistors can be formed. Alternatively, floating body effects can be minimized by eliminating the neutral region between the source/drain region and the insulating layer by making all transistors fully depleted.

5 The present invention can be practiced by employing conventional materials, methodology and equipment. Accordingly, the details of such materials, equipment and methodology are not set forth herein in detail. In the previous descriptions, numerous specific details are set forth, such as specific materials, structures, chemicals, processes, etc., in order to provide a thorough understanding of the present invention. However, it should be recognized that the present invention

10 can be practiced without resorting to the details specifically set forth. In other instances, well-known processing structures have not been described in detail, in order not to unnecessarily obscure the present invention.

Only the preferred embodiment of the present invention and but a few examples of its versatility are shown and described in the present disclosure. It is to be understood that the present

15 invention is capable of use in various other combinations and environments and is capable of changes or modifications within the scope of the inventive concepts as expressed herein.

What is claimed is:

1. A method of manufacturing a semiconductor device, comprising the steps of:

providing a silicon layer 14 over an insulating layer 12, the silicon layer 14 including a first

5 portion and a second portion;

partially removing the first portion of the silicon layer 14, wherein a thickness of the second portion is greater than a thickness of the first portion.

2. The method according to claim 1, wherein the first and second portions of the silicon layer

.0 14 initially have the same thickness.

3. The method according to claim 1, wherein the step of partially removing the first portion of the silicon layer 14 includes etching the first portion.

15 4. The method according to claim 3, wherein the step of partially removing the first portion of the silicon layer 14 includes depositing a resist 22 over the silicon layer 14 and exposing and developing the resist to expose the first portion of the silicon layer 14.

20 5. The method according to claim 1, wherein the step of partially removing the first portion of the silicon layer 14 includes oxidizing the first portion of the silicon layer 14 and removing the oxidized silicon.

25 6. The method according to claim 5, wherein the step of partially removing the first portion of the silicon layer 14 includes depositing a mask layer 20 and a resist 22 over the silicon layer 14 and exposing and developing the resist 22 to expose a portion of the mask layer 20 over the first portion of the silicon layer 14 and removing the mask layer 20 over the first portion of the silicon layer 14.

7. A semiconductor device, comprising:

an insulating layer 12;

30 a silicon layer 14 over the insulating layer 12, the silicon layer 14 including a first portion and a second portion;

wherein a thickness of the second portion is greater than a thickness of the first portion.

35 8. The semiconductor device according to claim 7, wherein a first transistor is formed in the first portion and a second transistor is formed in the second portion.

9. The semiconductor device according to claim 8, wherein the first transistor includes source/drain regions 40a, 42a formed with a first dopant and the second transistor includes source/drain regions 40b, 42b formed with a second dopant, and the diffusivity of the second dopant into silicon is greater than the diffusivity of the first dopant into silicon.

5

10. The semiconductor device according to claim 8, wherein the first transistor includes source/drain regions 40a, 42a formed with a first dopant and the second transistor includes source/drain regions 40b, 42b formed with a second dopant, and the diffusivity of the second dopant into silicon is greater than the diffusivity of the first dopant into silicon.

10

FIG. 1A

FIG. 1B

FIG. 1C

FIG. 1D

FIG. 2A

FIG. 2B

FIG. 3

FIG. 4

FIG. 5

## INTERNATIONAL SEARCH REPORT

|                 |                   |

|-----------------|-------------------|

| Inte            | al Application No |

| PCT/US 02/41102 |                   |

|                                     |

|-------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER |

|-------------------------------------|

|                 |

|-----------------|

| IPC 7 H01L27/12 |

|-----------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                           |

|-------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols) |

|-------------------------------------------------------------------------------------------|

|            |

|------------|

| IPC 7 H01L |

|------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used) |

|----------------------------------------------------------------------------------------------------------------------------|

|                             |

|-----------------------------|

| EPO-Internal, PAJ, WPI Data |

|-----------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                             | Relevant to claim No. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X          | US 5 940 691 A (MANNING H MONTGOMERY)<br>17 August 1999 (1999-08-17)<br>abstract; figures 9,10<br>---                                                                                          | 1-10                  |

| X          | US 6 110 765 A (MANNING H MONTGOMERY)<br>29 August 2000 (2000-08-29)<br>abstract; figures 9,10<br>---                                                                                          | 1-10                  |

| X          | PATENT ABSTRACTS OF JAPAN<br>vol. 1999, no. 12,<br>29 October 1999 (1999-10-29)<br>& JP 11 176925 A (ASAHI KASEI MICRO SYST<br>CO LTD), 2 July 1999 (1999-07-02)<br>abstract; figure 1A<br>--- | 1-10                  |

| X          | US 5 463 238 A (KAMIYA MASAAKI ET AL)<br>31 October 1995 (1995-10-31)<br>abstract; figure 1<br>-----                                                                                           | 1-10                  |

|                                                                                     |

|-------------------------------------------------------------------------------------|

| <input type="checkbox"/> Further documents are listed in the continuation of box C. |

|-------------------------------------------------------------------------------------|

|                                                                                |

|--------------------------------------------------------------------------------|

| <input checked="" type="checkbox"/> Patent family members are listed in annex. |

|--------------------------------------------------------------------------------|

° Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- "&" document member of the same patent family

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|               |

|---------------|

| 24 March 2003 |

|---------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|             |

|-------------|

| 10 APR 2003 |

|-------------|

|                                     |

|-------------------------------------|

| Name and mailing address of the ISA |

|-------------------------------------|

|                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                 |

|-----------------|

| DANIEL MOE/JA A |

|-----------------|

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US 02/41102

| Patent document cited in search report | Publication date | Patent family member(s) |    | Publication date |

|----------------------------------------|------------------|-------------------------|----|------------------|

| US 5940691                             | A 17-08-1999     | US 6110765              | A  | 29-08-2000       |

|                                        |                  | US 6143591              | A  | 07-11-2000       |

|                                        |                  | US 6174755              | B1 | 16-01-2001       |

|                                        |                  | US 6329689              | B1 | 11-12-2001       |

|                                        |                  | US 6277680              | B1 | 21-08-2001       |

|                                        |                  | US 2001000494           | A1 | 26-04-2001       |

| -----                                  |                  |                         |    |                  |

| US 6110765                             | A 29-08-2000     | US 5940691              | A  | 17-08-1999       |

|                                        |                  | US 6329689              | B1 | 11-12-2001       |

|                                        |                  | US 6143591              | A  | 07-11-2000       |

|                                        |                  | US 6174755              | B1 | 16-01-2001       |

|                                        |                  | US 6277680              | B1 | 21-08-2001       |

|                                        |                  | US 2001000494           | A1 | 26-04-2001       |

| -----                                  |                  |                         |    |                  |

| JP 11176925                            | A 02-07-1999     | TW 425606               | B  | 11-03-2001       |

| -----                                  |                  |                         |    |                  |

| US 5463238                             | A 31-10-1995     | JP 3188779              | B2 | 16-07-2001       |

|                                        |                  | JP 6291265              | A  | 18-10-1994       |

|                                        |                  | JP 3350523              | B2 | 25-11-2002       |

|                                        |                  | JP 2001189465           | A  | 10-07-2001       |

| -----                                  |                  |                         |    |                  |