(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5167652号

(P5167652)

(45) 発行日 平成25年3月21日(2013.3.21)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

F 1

**B81B 3/00 (2006.01)**B81B 3/00

B81C 1/00 (2006.01)

B81C 1/00

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2007-35826 (P2007-35826)

(22) 出願日 平成19年2月16日 (2007.2.16)

(65) 公開番号 特開2008-200758 (P2008-200758A)

(43) 公開日 平成20年9月4日 (2008.9.4)

審査請求日 平成22年2月12日 (2010.2.12)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 佐藤 彰

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 山本 健晴

最終頁に続く

(54) 【発明の名称】MEMS素子

## (57) 【特許請求の範囲】

## 【請求項1】

MEMS構造体と、

前記MEMS構造体に設けられた可動電極と、

前記可動電極との間で容量を形成するフローティングゲートと、

前記可動電極との間で容量を形成する駆動電極と、

半導体基板と、

を備えており、

前記フローティングゲートと前記半導体基板との間にゲート領域が設けられ、前記可動電極の一端がアンカー部を介して基部に固定されており、前記基部と前記アンカー部とは幅が異なることを特徴とするMEMS素子。

10

## 【請求項2】

請求項1に記載のMEMS素子において、

前記駆動電極は、前記可動電極の他端に対向して配置され、

前記フローティングゲートは、前記可動電極の一端と前記可動電極の他端との間の前記可動電極に対向して配置されていることを特徴とするMEMS素子。

## 【請求項3】

請求項1に記載のMEMS素子において、

前記フローティングゲートは、前記可動電極の他端に対向して配置されていることを特徴とするMEMS素子。

20

**【請求項 4】**

請求項 2 または請求項 3 に記載の M E M S 素子において、

前記フローティングゲートは、前記半導体基板に形成されたゲート配線とトンネル酸化膜とを介して接続されていることを特徴とする M E M S 素子。

**【請求項 5】**

請求項 4 に記載の M E M S 素子において、

前記フローティングゲートと前記ゲート配線とが前記トンネル酸化膜によって接続されているゲート領域と、前記可動電極が形成される前記半導体基板上の領域とが平面視で異なることを特徴とする M E M S 素子。

**【発明の詳細な説明】**

10

**【技術分野】****【0 0 0 1】**

本発明は、 M E M S 構造体を備えた静電駆動タイプの M E M S 素子およびその製造方法に関する。

**【背景技術】****【0 0 0 2】**

M E M S (Micro Electro Mechanical System) 素子は、加速度センサー、映像デバイス等に利用され、その需要も伸びている。

静電駆動タイプの M E M S 素子では、 M E M S 構造体の構造と寸法によって、駆動に必要な印加電圧、バイアス値、共振特性等の諸特性が決まる。例えば、可変容量素子は、駆動電極と可動電極とで静電容量を形成するが、駆動電極と可動電極とのギャップ距離、駆動電極と可動電極が重なる部分の面積等によって、静電容量と印加電圧との関係が決まる(特許文献 1 参照)。

20

**【0 0 0 3】**

【特許文献 1】特開 2006 - 147995 号公報(11 頁、段落番号 [0032])

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 4】**

したがって、 M E M S 素子の駆動電圧、バイアス値、共振特性等の得たい特性値に応じて、 M E M S 構造体の設計を個々に行う必要がある。言い換えれば、1つの設計によって特性値が固定され、一品一様の設計が必要である。

30

本発明の目的は、1つの設計による M E M S 素子で、特性値を可変可能で、可変後の特性値を維持可能な M E M S 素子およびその製造方法を提供することにある。

**【課題を解決するための手段】****【0 0 0 5】**

本発明の M E M S 素子は、 M E M S 構造体と、前記 M E M S 構造体に設けられた可動電極と、前記可動電極との間で容量を形成するフローティングゲートと、前記可動電極との間で容量を形成する駆動電極と、半導体基板と、を備えており、前記フローティングゲートと前記半導体基板との間にゲート領域が設けられ、前記可動電極の一端がアンカー部を介して基部に固定されており、前記基部と前記アンカー部とは幅が異なることを特徴とする。

40

**【0 0 0 6】**

この発明によれば、フローティングゲートに電荷を注入することによって、可動電極との間に静電気力が生じる。フローティングゲートでは電荷が閉じ込められているので、可動電極には力が加わり続ける。したがって、可動電極は力が加わった状態で、固定または可動し、 M E M S 素子は力が加わった状態に応じた特性値を有する。フローティングゲートに注入する電荷量は調整できるので、注入した電荷量に応じて可動電極に加わる力も可変し、 M E M S 素子の特性値も可変する。フローティングゲートに注入した電荷量が変化しない限り、 M E M S 素子の特性値は維持される。

50

**【 0 0 0 7 】**

本発明では、前記フローティングゲートは、前記可動電極の可動端に対向して配置されているのが好ましい。

この発明では、フローティングゲートと可動電極による静電気力が、可動電極の可動しやすい可動端で働くので、より少ない注入電荷で可動電極に力を加えることができる。

**【 0 0 0 8 】**

本発明では、前記可動電極との間で容量を形成する駆動電極を備えているのが好ましい。

この発明では、フローティングゲートの他に、可動電極を駆動する駆動電極を備えているので、フローティングゲートに電荷を注入し、フローティングゲートと可動電極との間に静電気力を生じさせた状態で可動電極が可動する。したがって、MEMS素子は力が加わった状態で可動状態に応じた特性値を有する。フローティングゲートに注入する電荷量は調整できるので、注入した電荷量に応じて可動電極に加わる力も可変し、MEMS素子の特性値も可変する。フローティングゲートに注入した電荷量が変化しない限り、MEMS素子の特性値は維持される。10

**【 0 0 0 9 】**

本発明では、前記駆動電極は、前記可動電極の可動端に対向して配置され、前記フローティングゲートは、前記可動端と前記可動電極の固定端との間の前記可動電極に対向して配置されているのが好ましい。

この発明では、駆動電極による可動電極の駆動を可動の容易な可動端で行い、フローティングゲートによる可動電極への静電気力は可動端と比較して可動の少ない固定端側で行っているので、駆動電極による可動電極の動きをできるだけ妨げることなく、フローティングゲートによって可動電極に加わる力を調整することができる。20

**【 0 0 1 0 】**

本発明では、前記MEMS素子は、半導体基板上に設けられ、前記フローティングゲートは、前記半導体基板に形成されたゲート配線とトンネル酸化膜を介して接続されているのが好ましい。

この発明では、トンネル酸化膜を介して電荷が注入されるので、フローティングゲートからの電荷の漏れを少なくでき、MEMS素子の特性を維持できる。

**【 0 0 1 1 】**

本発明では、前記フローティングゲートと前記ゲート配線とが前記トンネル酸化膜によって接続されているゲート領域と、前記可動電極が形成される前記半導体基板上の領域とが異なるのが好ましい。30

この発明では、可動電極とゲート領域の位置が異なるので、可動電極の動きによるトンネル酸化膜への影響が少ない。また、ゲート領域形成への影響を考慮せずに可動電極の形成ができる。

**【 0 0 1 2 】**

本発明のMEMS素子の製造方法は、MEMS構造体とフローティングゲートとを備えたMEMS素子の製造方法であって、半導体基板にN型不純物を導入し、ゲート配線およびゲート領域にN<sup>+</sup>拡散層を形成するN<sup>+</sup>拡散層形成工程と、前記N<sup>+</sup>拡散層が形成された前記半導体基板の面にシリコン酸化膜を形成する絶縁膜形成工程と、前記シリコン酸化膜の表面の前記ゲート領域をマスクして、シリコン窒化膜を形成するエッチングストップ膜形成工程と、前記ゲート領域の前記シリコン酸化膜をエッチングし、前記N<sup>+</sup>拡散層を露出させるエッチング工程と、露出した前記N<sup>+</sup>拡散層にトンネル酸化膜を形成するトンネル酸化膜形成工程と、前記MEMS構造体の下部構造体と前記フローティングゲートとを形成するフローティングゲート等形成工程と、前記下部構造体および前記フローティングゲート上に犠牲層を形成する犠牲層形成工程と、前記MEMS構造体の上部構造体を形成する上部構造体形成工程と、前記犠牲層をエッチングして除去する犠牲層除去工程とを含むことを特徴とする。40

**【 0 0 1 3 】**

この発明によれば、MEMS構造体と可動電極とフローティングゲートとを備えた前述の効果を有するMEMS素子が得られる。

【発明を実施するための最良の形態】

【0014】

以下、本発明を具体化した実施形態および変形例について、図面に基づいて説明する。

なお、各実施形態および変形例の図面において、同じ構成要素には同じ符号を付して説明する。

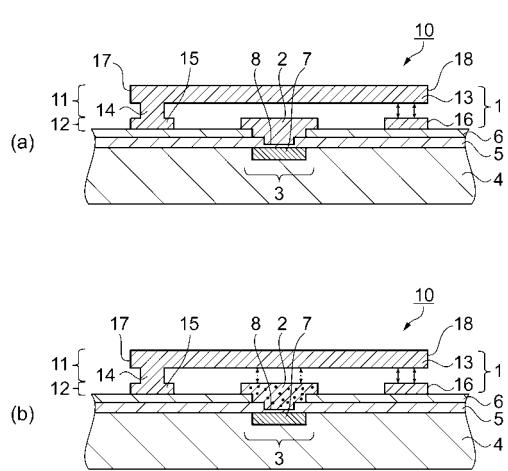

【0015】

(第1実施形態)

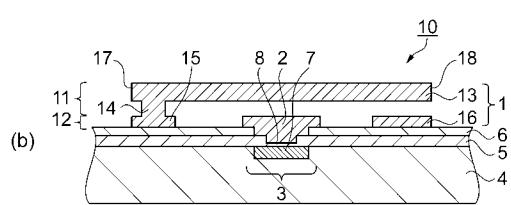

図1は、本発明にかかるMEMS素子10の実施形態を示す概略構成図である。図1(a)はMEMS素子10の概略部分平面図、図1(b)は同図(a)のA-A断線に沿う概略部分断面図である。 10

【0016】

図1(a)および(b)において、MEMS素子10は、MEMS構造体1とフローティングゲート2とゲート領域3とゲート配線9とを備えている。MEMS素子10は、半導体基板4上に形成されている。

半導体基板4の表面には、絶縁膜であるシリコン酸化膜5が形成され、さらにその表面にシリコン窒化膜6が形成されている。

【0017】

MEMS構造体1は、上部構造体11と下部構造体12とを備えている。 20

上部構造体11は可動部13とアンカー部14とを備え、下部構造体12は基部15と駆動電極16とを備えている。

MEMS構造体1は、不純物を含むポリシリコンから形成され、導電性を有している。

【0018】

可動部13は板状の直方体に形成されている。可動部13の端面の1つは固定端17であり、対向する端面は可動端18となっている。固定端17はアンカー部14を介して基部15に固定され、可動部13とアンカー部14とで片持ち梁構造が構成されている。

MEMS構造体1が導電性を有しているため、可動部13は可動電極として機能し、可動部13と基部15とは電気的に接続されている。基部15は図示しない配線によって他の素子、信号線等に接続されている。 30

可動部13の寸法は、例えば、長さが数十 $\mu\text{m}$ 、幅数 $\mu\text{m}$ 、厚み0.数 $\mu\text{m}$ 程度である。これらの値は、MEMS素子10に必要とされる特性値に応じて、設計により自由に選択できる。

なお、可動部13の平面形状については、種々の形状を採用できる。例えば、円盤状、舌状、矢印状等が挙げられる。

【0019】

基部15および駆動電極16はシリコン窒化膜6上に設けられている。駆動電極16は可動端18側に設けられている。駆動電極16は、MEMS素子10から延長して形成され、他の素子、信号線等に接続される。図1(a)においては、図の紙面に向かって上方に向に延長されている。 40

【0020】

フローティングゲート2は、可動部13の略中央に対向する半導体基板4上に設けられている。本実施形態では、フローティングゲート2を平面視した形状は正方形となっている。フローティングゲート2の位置、大きさ、形状等は、設計によって決めることができる。

【0021】

ゲート領域3は、フローティングゲート2と半導体基板4との間に形成されている。ゲート領域3は、N<sup>+</sup>拡散層7とトンネル酸化膜8とを備えている。

N<sup>+</sup>拡散層7は、ゲート領域3のみならず延長して形成され、ゲート配線9を形成している。図1(a)において、ゲート配線9は、図の紙面に向かって上方に向に延長され、他 50

の素子、信号線等に接続されている。

#### 【0022】

以下に、ゲート領域3の構造を詳しく説明する。

シリコン酸化膜5およびシリコン窒化膜6は、N<sup>+</sup>拡散層7上を除いた半導体基板4上に順次積層されている。

N<sup>+</sup>拡散層7の表面にはトンネル酸化膜8が形成され、トンネル酸化膜8の表面にはフローティングゲート2が形成されている。シリコン酸化膜5およびシリコン窒化膜6の厚みは数百nmである。

#### 【0023】

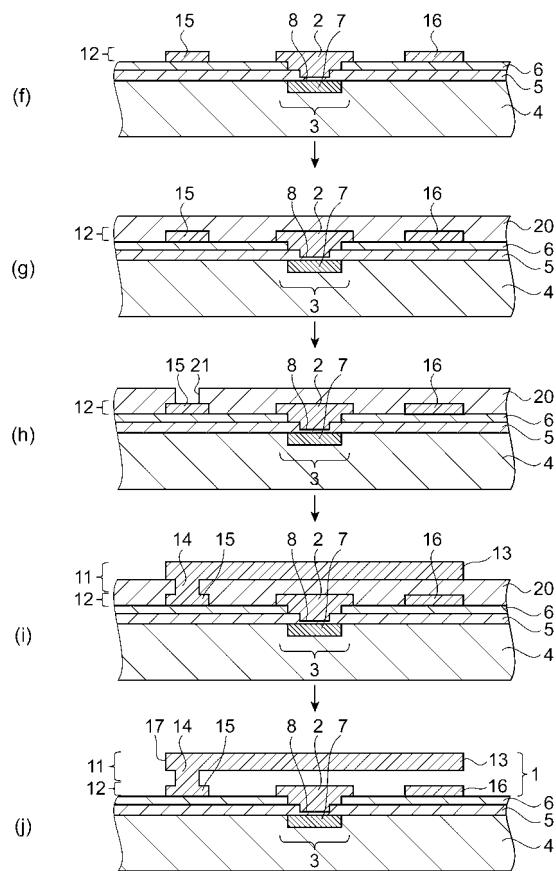

以下に、本実施形態にかかるMEMS素子10の製造方法を図面に基づいて説明する。

10

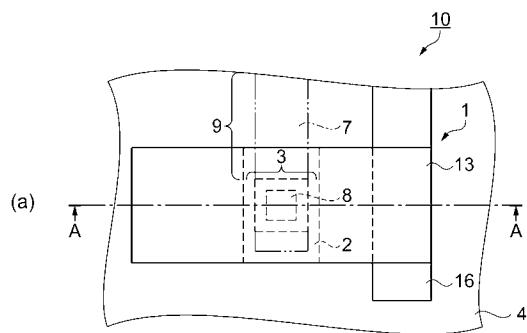

図2には、MEMS素子10の製造方法のフローチャート図が示されている。また、図3および図4には、各工程における概略断面図が示されている。

#### 【0024】

図2において、MEMS素子10の製造方法は、N<sup>+</sup>拡散層形成工程(S1)、絶縁膜形成工程(S2)、エッティングストップ膜形成工程(S3)、エッティング工程(S4)、トンネル酸化膜形成工程(S5)、フローティングゲート等形成工程(S6)、犠牲層形成工程(S7)、犠牲層エッティング工程(S8)、上部構造体形成工程(S9)、犠牲層除去工程(S10)を含んでいる。

#### 【0025】

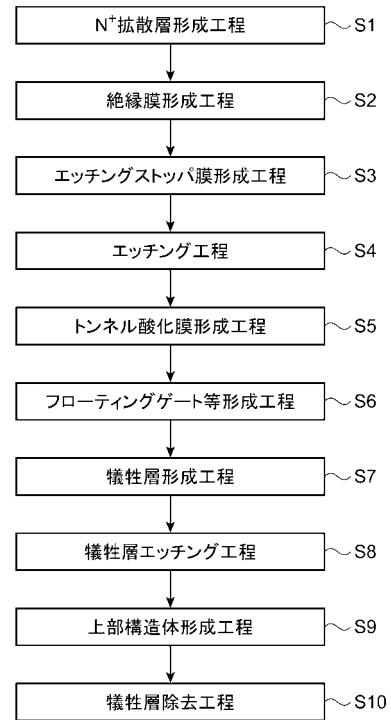

以下、図3および図4に基づいてMEMS素子10の製造方法を詳しく説明する。

20

図3(a)は、N<sup>+</sup>拡散層形成工程(S1)を示している。

N<sup>+</sup>拡散層形成工程(S1)では、イオン打ち込み、熱拡散によって不純物であるリンを半導体基板4に導入し、ゲート領域3にN<sup>+</sup>拡散層7を形成する。図1に示したゲート配線9もN<sup>+</sup>拡散層7と同様に不純物であるリンを導入することによって形成する。したがって、ゲート配線9とN<sup>+</sup>拡散層7とは、同時に形成することができる。注入濃度は、導電性を有する濃度であり、1×10<sup>20</sup>cm<sup>-3</sup>程度が好ましい。

#### 【0026】

図3(b)は、絶縁膜形成工程(S2)を示している。

絶縁膜形成工程(S2)では、半導体基板4のN<sup>+</sup>拡散層7が形成された面にシリコン酸化膜5を形成する。シリコン酸化膜5は、熱酸化法、減圧CVD(Chemical Vapor Deposition)法等を用いて形成する。厚みは100nm程度が好ましい。

30

#### 【0027】

図3(c)は、エッティングストップ膜形成工程(S3)を示している。

エッティングストップ膜形成工程(S3)では、シリコン酸化膜5の表面にシリコン窒化膜6を形成する。シリコン窒化膜6は減圧CVD法等を用いて形成する。このとき、シリコン窒化膜6を全面形成した後、ゲート領域3に相当する部分をドライエッティングして除去する。

#### 【0028】

図3(d)は、エッティング工程(S4)を示している。

エッティング工程(S4)では、ゲート領域3のシリコン酸化膜5を除去し、N<sup>+</sup>拡散層7を露出させる。エッティングには、ドライエッティング法またはウェットエッティング法を用いることができる。

40

#### 【0029】

図3(e)は、トンネル酸化膜形成工程(S5)を示している。

トンネル酸化膜形成工程(S5)では、露出したN<sup>+</sup>拡散層7表面に、トンネル酸化膜8を形成する。トンネル酸化膜8は、熱酸化法、ラジカル酸化法等を用いて形成することができる。トンネル酸化膜8の厚みは、5nm～10nmが好ましい。

#### 【0030】

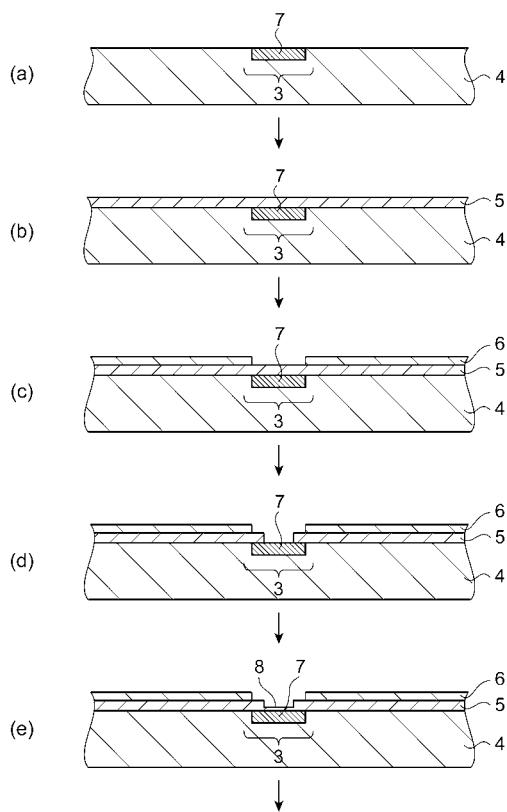

図4(f)は、フローティングゲート等形成工程(S6)を示している。

フローティングゲート等形成工程(S6)では、半導体基板4上にフローティングゲー

50

ト 2、下部構造体 1 2 である基部 1 5 および駆動電極 1 6 を形成する。

フローティングゲート 2 は、ゲート領域 3 に形成する。基部 1 5 および駆動電極 1 6 は、図 1 に示した基部 1 5 および駆動電極 1 6 の位置、形状に形成する。

フローティングゲート 2、基部 1 5 および駆動電極 1 6 は、減圧 C V D 法によりポリシリコン膜を形成することによって得られる。このとき、導電性を得るためにリンを導入する。ポリシリコン膜の膜厚は、1 0 0 n m ~ 5 0 0 n m が好ましい。

フローティングゲート等形成工程 ( S 6 ) は、よく知られたフォトリソ工程によって行うことができる。

#### 【 0 0 3 1 】

図 4 ( g ) は、犠牲層形成工程 ( S 7 ) を示している。

10

犠牲層形成工程 ( S 7 ) では、フローティングゲート 2、基部 1 5 および駆動電極 1 6 上に犠牲層 2 0 を形成する。犠牲層 2 0 は、減圧 C V D 法またはプラズマ C V D 法を用いて、シリコン酸化膜等を形成することによって得られる。犠牲層 2 0 の膜厚は、図 1 に示した可動部 1 3 と半導体基板 4 との間に必要な間隔によって決めることができる。例えば、1 0 0 n m ~ 2 0 0 n m が好ましい。

また、形成された犠牲層 2 0 の表面が平らになるように形成するのが好ましい。犠牲層 2 0 の表面を平らにするには、P S G ( Phospho - Silicate - Glass ) を減圧 C V D 法により形成し、その後 1 0 0 0 °で高温熱処理を行うと、膜の流動化が起こり膜表面が平坦化する。このとき、フローティングゲート等形成工程 ( S 6 ) で形成したポリシリコン膜にリンを拡散し、フローティングゲート 2、基部 1 5 および駆動電極 1 6 を形成することも可能である。

20

その他、C M P ( Chemical Mechanical Polishing ) 法、エッチバック法によって、犠牲層 2 0 の表面を平らにすることも可能である。

#### 【 0 0 3 2 】

図 4 ( h ) は、犠牲層エッティング工程 ( S 8 ) を示している。

犠牲層エッティング工程 ( S 8 ) では、図 1 に示したアンカー部 1 4 に相当する部分をエッティングして穴 2 1 を形成し、基部 1 5 を露出させる工程である。エッティングは、ウェットエッティング法またはドライエッティング法によって行うことができる。または、R I E ( Reactive Ion Etching ) 法によって行ってもよい。

#### 【 0 0 3 3 】

30

図 4 ( i ) は、上部構造体形成工程 ( S 9 ) を示している。

上部構造体形成工程 ( S 9 ) では、犠牲層 2 0 上に上部構造体 1 1 である可動部 1 3 およびアンカー部 1 4 を形成する。上部構造体 1 1 は、減圧 C V D 法によりポリシリコン膜を形成することによって得られる。このとき、導電性を得るためにリンを導入する。

上部構造体形成工程 ( S 9 ) は、よく知られたフォトリソ工程によって行い、上部構造体 1 1 の形状を形成する。

#### 【 0 0 3 4 】

図 4 ( j ) は、犠牲層除去工程 ( S 1 0 ) を示している。

犠牲層除去工程 ( S 1 0 ) では、ウェットエッティング等により犠牲層 2 0 をエッティングし除去する。

40

以上の製造工程を含む製造方法によって、M E M S 素子 1 0 が得られる。

#### 【 0 0 3 5 】

M E M S 素子 1 0 は以下のように作動する。

図 5 は、本実施形態でのM E M S 素子 1 0 の作動状態を示した図である。図 5 ( a ) は、フローティングゲート 2 に電荷 ( 電子 ) が注入されていない時の状態を示す図、図 5 ( b ) は、フローティングゲート 2 に電荷 ( 電子 ) が注入された時の状態を示す図である。電荷は模式的に点で示してある。

#### 【 0 0 3 6 】

図 5 ( a ) において、フローティングゲート 2 に電荷が注入されていない状態では、フローティングゲート 2 と可動部 1 3 との間では、静電気力は働いていない。したがって、

50

可動電極でもある可動部 13 と駆動電極 16 との間の印加電圧のみによって、図中矢印で示した静電気力が働き、可動部 13 が駆動する。

#### 【0037】

一方、図 5 (b)において、フローティングゲート 2 に電荷が注入された状態では、フローティングゲート 2 と可動部 13との間では、図中点線矢印で示したような静電気力も働く。したがって、可動電極でもある可動部 13 と駆動電極 16 との間の印加電圧と静電気力とのバランスで可動部 13 が駆動する。

#### 【0038】

以下、本実施形態の効果を記載する。

(1) フローティングゲート 2 の他に、可動部 13 を駆動する駆動電極 16 を備えているので、フローティングゲート 2 に電荷を注入し、フローティングゲート 2 と可動部 13 との間に静電気力を生じさせた状態で可動部 13 を可動できる。したがって、MEMS 素子 10 は力が加わった状態で可動状態に応じた特性値、例えば、駆動に必要な電圧や共振周波数を有する。フローティングゲート 2 に注入する電荷量は調整できるので、注入した電荷量に応じて可動部 13 に加わる力も可変し、MEMS 素子 10 の特性値を可変できる。例えば、MEMS 素子 10 をスイッチング素子として利用する場合、径時変化によって可動部 13 の弾性係数等が変化することが考えられる。弾性係数等が変化すると、スイッチングに必要な印加電圧も変える必要があるが、フローティングゲート 2 に注入された電荷による静電気力によって、変化させる印加電圧分を補うことができ、印加電圧を変える必要がなくなる。

ここで、フローティングゲート 2 に注入した電荷量が変化しない限り、MEMS 素子 10 の特性値を維持できる。

#### 【0039】

(2) 駆動電極 16 による可動部 13 の駆動を可動の容易な可動端 18 で行い、フローティングゲート 2 による可動部 13 への静電気力は可動端 18 と比較して可動の少ない固定端 17 側で行っているので、駆動電極 16 による可動部 13 の動きをできるだけ妨げることなく、フローティングゲート 2 によって可動部 13 に加わる力を調整することができる。

#### 【0040】

(3) トンネル酸化膜 8 を介して電荷が注入されるので、フローティングゲート 2 からの電荷の漏れを少なくでき、MEMS 素子 10 の特性を維持できる。

#### 【0041】

(4) MEMS 構造体 1 と可動電極である可動部 13 とフローティングゲート 2 とを備えた前述の効果を有するMEMS 素子 10 が得られる。

#### 【0042】

(5) 犠牲層 20 をエッチングによって除去する際に、シリコン窒化膜 6 をエッチングストップとして利用することができ、シリコン酸化膜 5 を保護できる。

#### 【0043】

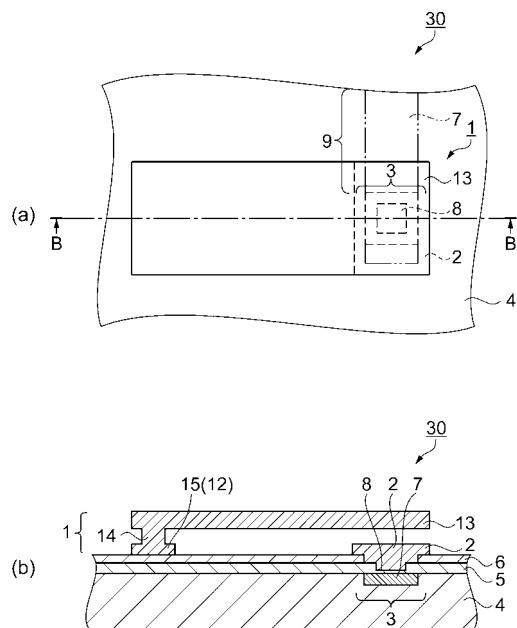

##### (第2実施形態)

図 6 は、本発明にかかるMEMS 素子 30 の実施形態を示す概略構成図である。図 6 (a) は、MEMS 素子 30 の概略部分平面図、図 6 (b) は同図 (a) の B - B 断線に沿う概略部分断面図である。

第1実施形態と本実施形態との異なる点は、本実施形態では、駆動電極 16 を備えておらず、駆動電極 16 の位置に、ゲート領域 3、ゲート配線 9 およびフローティングゲート 2 を設けた点である。その他の構成は、第1実施形態と同様である。

#### 【0044】

以下に、本実施形態の効果を記載する。

(6) フローティングゲート 2 と可動部 13 とによる静電気力が、可動部 13 の可動しやすい可動端で働くので、より少ない注入電荷で可動部 13 に力を加えることができる。

#### 【0045】

10

20

30

40

50

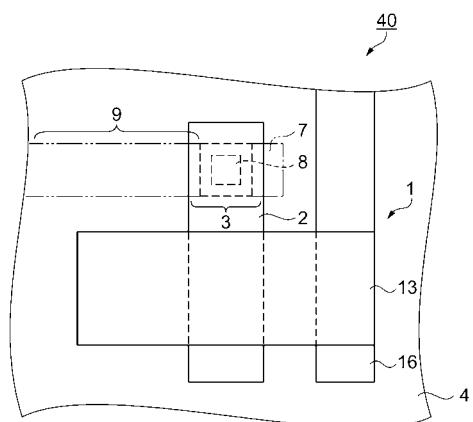

### (変形例)

図7は、本発明にかかるMEMS素子40の変形例を示す概略部分平面図である。

変形例では、ゲート領域3とゲート配線9とを可動部13と半導体基板4との間ではなく、外れた位置に形成した。フローティングゲート2は、可動部13と半導体基板4との間に形成されている。

このように、MEMS構造体の一部である可動部13とゲート領域3とは、平面視した場合の異なる領域に形成してもよい。

### 【0046】

以下に、変形例の効果を記載する。

(7) 可動部13とゲート領域3の位置が異なるので、可動部13の動きによるトンネル酸化膜8への影響を少なくできる。また、ゲート領域3形成への影響を考慮せずに可動電極の形成ができる。10

本発明では、変形例で示した例ならず、色々なレイアウトをとることができる。

### 【0047】

なお、本発明は前述の実施形態および変形例に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

例えば、基板として絶縁体基板に半導体層を形成し、半導体層にN<sup>+</sup>拡散層7を形成してMEMS素子を形成してもよい。

### 【図面の簡単な説明】

### 【0048】

20

【図1】(a)は、本発明の第1実施形態にかかるMEMS素子の概略部分平面図、(b)は同図(a)のA-A断線に沿う概略部分断面図。

【図2】本発明の第1実施形態にかかるMEMS素子の製造方法を示すフローチャート図。。

【図3】本発明の第1実施形態にかかるMEMS素子の製造方法の各工程における概略断面図。

【図4】本発明の第1実施形態にかかるMEMS素子の製造方法の各工程における概略断面図。

【図5】本発明の第1実施形態にかかるMEMS素子の作動状態を示す概略断面図。

【図6】(a)は、本発明の第2実施形態にかかるMEMS素子の概略部分平面図、(b)は同図(a)のB-B断線に沿う概略部分断面図。30

【図7】本発明の変形例の概略部分平面図。

### 【符号の説明】

### 【0049】

1...MEMS構造体、2...フローティングゲート、3...ゲート領域、4...半導体基板、5...シリコン酸化膜、6...シリコン窒化膜、7...N<sup>+</sup>拡散層、8...トンネル酸化膜、9...ゲート配線、10, 30, 40...MEMS素子、11...上部構造体、12...下部構造体、13...可動電極(可動部)、16...駆動電極、17...固定端、18...可動端、20...犠牲層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特表2002-539624(JP,A)

特開平10-115527(JP,A)

特開2006-318670(JP,A)

特開2006-252956(JP,A)

特開2004-243462(JP,A)

特開2006-238265(JP,A)

(58)調査した分野(Int.Cl., DB名)

B81B 3 / 00

B81C 1 / 00