MINISTERO DELLO SVILUPPO ECONOMICO

DIREZIONE GENERALE PER LA TUTELA DELLA PROPRIETÀ INDUSTRIALE

UFFICIO ITALIANO BREVETTI E MARCHI

UIBM

|                           |                        |

|---------------------------|------------------------|

| <b>DOMANDA NUMERO</b>     | <b>101982900001037</b> |

| <b>Data Deposito</b>      | <b>13/12/1982</b>      |

| <b>Data Pubblicazione</b> | <b>13/06/1984</b>      |

|                               |           |

|-------------------------------|-----------|

| <b>Priorità</b>               | 332.387   |

| <b>Nazione Priorità</b>       | US        |

| <b>Data Deposito Priorità</b> | 21-DEC-81 |

Titolo

CIRCUITO COMPARATORE

# **DOCUMENTAZIONE RILEGATA**

DESCRIZIONE dell'invenzione industriale avente per titolo:

"CIRCUITO COMPARATORE".

della GTE LABORATORIES INC. di nazionalità statunitense, con sede a Wilmington Delaware (US.A.)

Inventore designato: Jeffrey R. Fox

Depositata il 13 DIC. 1982

24706A/82

o—o—o—o—o

### RIASSUNTO

Un circuito comparatore differenziale rigenerativo a transistor ad effetto di campo (FET) del tipo a metallo-ossido-silicio (MOS), particolarmente adatto in apparecchiature di modulazione del tipo sigma delta. Il circuito include due stadi amplificatori differenziali seguiti da uno stadio amplificatore di aggancio. Una sezione di aggancio rigenerativa costituita da due FET di aggancio collegati in croce, è collegata allo stadio amplificatore di aggancio. Ciascuno dei FET di aggancio è collegato in serie con un FET di commutazione separato. Un impulso di comando commuta allo stato di accensione i due FET di commutazione, abilitando i FET di aggancio. In dipendenza dalla polarità relativa della tensione differenziale prodotta dallo stadio amplificatore di aggancio, l'azione rigenerativa pilota uno dei due FET di aggancio in forte conduzione, producendo così un'uscita digitale appropriata. I primi due stadi amplificatori differenziali rimangono abilitati durante l'azione rigenerativa, consentendo così un fun-

zionamento ad alta velocità.

TESTO DELLA DESCRIZIONE

La presente invenzione riguarda circuiti comparatori. Più particolarmente, essa riguarda circuiti comparatori impieganti transistor ad effetto di campo (FET) del tipo a metallo-ossido-silicio (MOS).

Un tipo di circuito comparatore che è stato recentemente sviluppato, impiega MOS FET in un circuito comparatore differenziale rigenerativo. Il circuito utilizza stadi amplificatori differenziali ed include una sezione di aggancio rigenerativa che aggancia una versione amplificata di una tensione di ingresso analogica. Una versione perfezionata di un tale circuito comparatore è illustrata e rivendicata nella domanda di brevetto italiana, numero 19955 A/82 depositata il 3 marzo 1982 a nome Micheal Cooperman e William L. Geller, intitolata "Comparator Circuit" (Circuito Comparatore) e ceduta alla richiedente della presente domanda. Per talune applicazioni, specificatamente in convertitori da digitale ad analogico e da analogico a digitale impiegati in apparecchiature di modulazione sigma-delta, è desiderabile fornire un circuito comparatore avente velocità e sensibilità ulteriormente migliorate.

Con circuiti comparatori secondo la presente invenzione si ottengono caratteristiche di velocità e sensibilità migliorate. Questo circuito comparatore comprende mezzi ampli-

ficatori differenziali d'ingresso includenti un primo e secondo transistor ad effetto di campo, con l'ingresso del primo transistor ad effetto di campo collegato ad un terminale d'ingresso di segnale e l'ingresso del secondo transistor ad effetto di campo collegato ad un punto di potenziale di riferimento. I mezzi amplificatori differenziali d'ingresso hanno un primo ed un secondo collegamento d'uscita, su cui sono prodotti segnali d'uscita differenziali. Il circuito comparatore comprende pure mezzi amplificatori differenziali di aggancio includenti un primo e secondo transistor ad effetto di campo, con i loro ingressi collegati al primo e secondo collegamenti di uscita, rispettivamente, dei mezzi amplificatori differenziali di ingresso. I mezzi amplificatori differenziali di aggancio hanno un primo e secondo collegamenti di uscita su cui sono prodotti segnali d'uscita differenziali. Mezzi di aggancio rigenerativi includono un primo e secondo transistor ad effetto di campo di aggancio. L'ingresso del primo transistor ad effetto di campo di aggancio è collegato al secondo transistor ad effetto di campo di aggancio, ed al secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio. L'ingresso del secondo transistor ad effetto di campo di aggancio è collegato al primo transistor ad effetto di campo di aggancio ed al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio.

Un terminale di uscita è collegato ad uno dei transistor ad effetto di campo di aggancio. Il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, operano in un primo insieme di condizioni operative e producono un primo segnale di uscita sul terminale di uscita in risposta a segnali di uscita differenziali di una polarità relativa sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio. Il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, funzionano in un secondo insieme di condizioni operative e producono un secondo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali della polarità relativa opposta sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio. I mezzi di aggancio rigenerativi includono pure un primo e secondo transistor ad effetto di campo di commutazione collegati al primo e secondo transistor ad effetto di campo di aggancio, rispettivamente. I transistor ad effetto di campo di commutazione rispondono ad un segnale di comando per abilitare il primo e secondo transistor ad effetto di campo di aggancio. In tal modo, in risposta ad un segnale di comando, i transistor ad effetto di campo di commutazione abilitano i transistor ad effetto di campo di aggancio. I transistor ad effetto di campo di aggancio sono commutati tramite azione rigenerativa od al primo oppure al secondo insieme di condizioni operative, produ-

cendo od un primo oppure un secondo segnale di uscita sul terminale di uscita, nel modo determinato dalla polarità relativa dei segnali di uscita sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio.

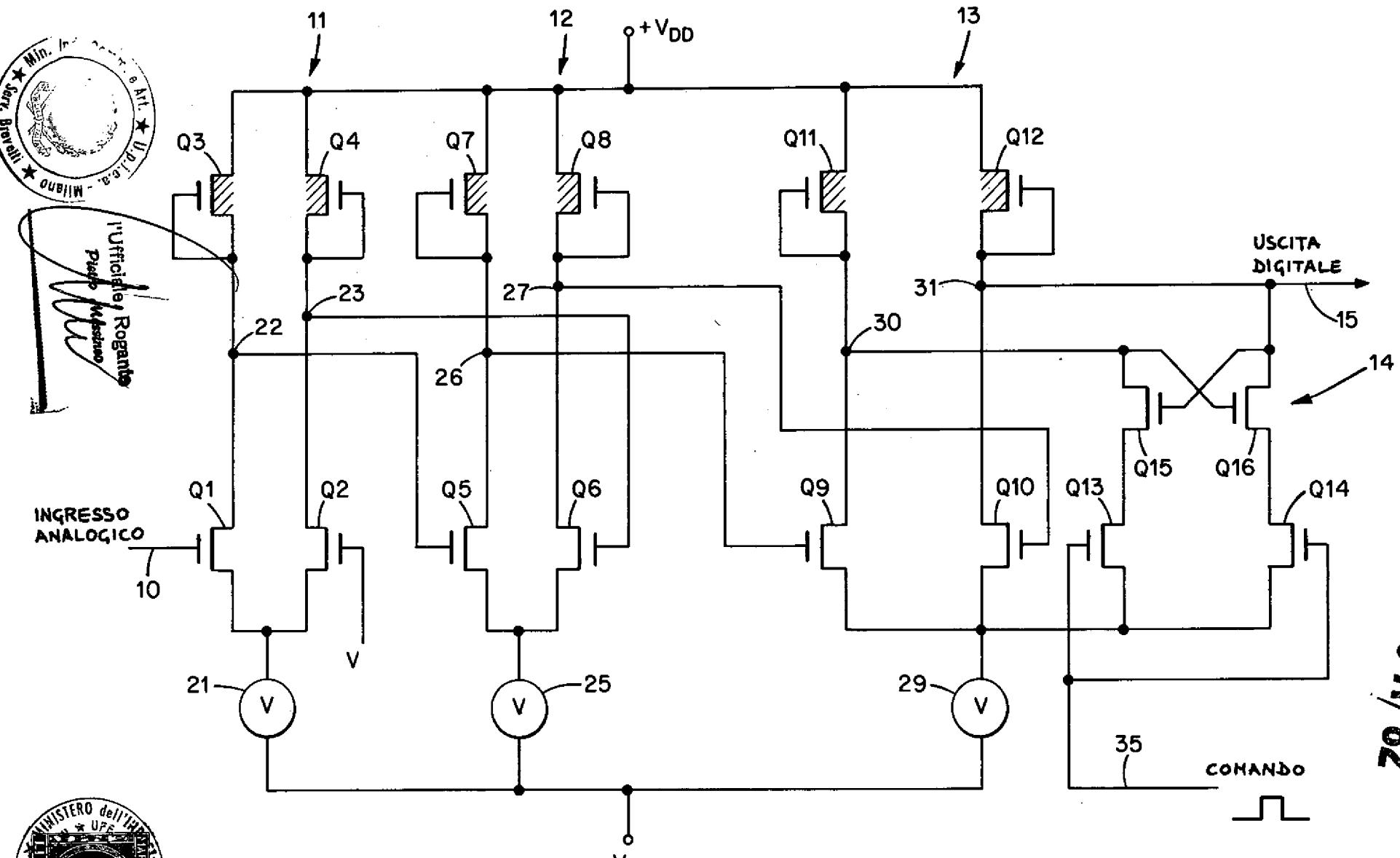

L'unica figura del disegno è uno schema circuittale di massima di un circuito comparatore secondo la presente invenzione.

Per una migliore comprensione della presente invenzione, congiuntamente a suoi altri ed ulteriori scopi, vantaggi e possibilità, viene fatto riferimento alla descrizione che segue ed alle rivendicazioni accluse, in unione con il summenzionato disegno.

L'unica figura del disegno illustra un circuito comparatore a transistor ad effetto di campo (FET), del tipo a metallo-ossido-silicio (MOS) secondo la presente invenzione. Nel circuito illustrato, tutti i FET sono dispositivi del tipo ad arricchimento ed impoverimento a canale N. Come è ben noto, i dispositivi FET del circuito e i loro intercollegamenti illustrati possono essere fabbricati sotto forma di un circuito integrato, in un unico corpo di materiale semiconduttore.

Il circuito comparatore illustrato in figura include un amplificatore differenziale di ingresso 11, un amplificatore differenziale intermedio 12, un amplificatore differenziale d'aggancio 13 ed una sezione d'aggancio rigenera-

tiva 14. Segnali di ingresso analogici sono applicati in corrispondenza di un collegamento d'ingresso 10 e segnali d'uscita digitali sono prelevati su un terminale di uscita 15.

L'amplificatore differenziale d'ingresso 11 include due FET del tipo ad arricchimento Q1 e Q2, ciascuno avente uno dei suoi elettrodi del percorso conduttore (sorgente) collegato a quello dell'altro ed attraverso un generatore di corrente costante 21 ad una sorgente di tensione negativa  $-V_{SS}$ , che è pure collegata al substrato. Il collegamento di ingresso analogico 10 è collegato alla porta del FET Q1, e la porta del FET Q2 è collegata ad un punto di potenziale di riferimento  $V_{REF}$ . L'elettrodo dell'altro percorso conduttivo (pozzo) del FET Q1 è collegato ad un carico resistivo che è costituito da un FET Q3 del tipo a impoverimento avente la sua porta collegata direttamente alla sua sorgente ed il suo pozzo collegato ad una sorgente di tensione positiva  $+V_{DD}$ . Il pozzo del FET Q2 è analogamente collegato attraverso un carico resistivo costituito da un FET Q4 del tipo ad impoverimento avente la sua porta collegata alla sua sorgente ed il suo pozzo collegato ad una sorgente di tensione positiva  $+V_{DD}$ . Un primo ed un secondo collegamenti di uscita 22 e 23 sono prelevati in corrispondenza delle connessioni dei FET Q1 e Q2 con i FET Q3 e Q4, rispettivamente.

L'amplificatore differenziale intermedio 12

è simile all'amplificatore differenziale d'ingresso 11 ed include due FET Q5 e Q6 del tipo ad arricchimento aventi le loro porte collegate al primo e secondo collegamenti di uscita 22 e 23, rispettivamente, dell'amplificatore differenziale d'ingresso 11. Le sorgenti dei FET Q5 e Q6 sono collegate assieme e, attraverso un generatore di corrente costante 25, alla sorgente di tensione negativa  $-V_{SS}$ . I loro pozzi sono collegati attraverso carichi resistivi costituiti da FET Q7 e Q8 del tipo ad impoverimento, rispettivamente, alla sorgente di tensione positiva  $+V_{DD}$ . Un primo e secondo collegamenti d'uscita 26 e 27 sono prelevati in corrispondenza delle connessioni dei FET Q5 e Q6 con il FET Q7 e Q8, rispettivamente.

L'amplificatore differenziale di aggancio 13 include due FET Q9 e Q10 del tipo ad arricchimento aventi le loro porte collegate ai collegamenti di uscita 26 e 27, rispettivamente, dell'amplificatore differenziale intermedio 12. Le sorgenti dei FET Q9 e Q10 sono collegate assieme, e, attraverso un generatore di corrente costante 29, alla sorgente di tensione negativa  $-V_{SS}$ . I pozzi dei FET Q9 e Q10 sono collegati attraverso carichi resistivi formati da FET del tipo ad impoverimento Q11 e Q12, rispettivamente, alla sorgente di tensione positiva  $+V_{DD}$ .

La sezione di aggancio rigenerativa 14 include due FET di aggancio del tipo ad arricchimento Q15 e Q16. Le

porte ed i pozzi dei FET Q15 e Q16 sono collegati in croce. La porta del FET Q16 è pure collegata al collegamento di uscita 30 in corrispondenza della connessione dei FET Q9 e Q11 dell'amplificatore differenziale di aggancio. La porta <sup>31</sup> del FET Q15 è pure collegata al collegamento di uscita/in corrispondenza della connessione dei FET Q10 e Q12 dell'amplificatore differenziale di aggancio. Il terminale di uscita digitale 15 è collegato al collegamento d'uscita 31. La sorgente del FET Q15 è collegata al pozzo di un FET di commutazione del tipo ad arricchimento Q13. La sorgente del FET Q13 è collegata al generatore di corrente costante 29. Analogamente, un FET di commutazione del tipo ad arricchimento Q14 ha il suo pozzo collegato alla sorgente del FET Q16 e la sua sorgente è collegata al generatore di corrente costante 29. Le porte dei FET di commutazione Q13 e Q14 sono collegate assieme ad un collegamento di comando 35 a cui sono applicati impulsi di comando positivi, come sarà illustrato in seguito.

Gli stadi amplificatori differenziali 11, 12 e 13 funzionano, come è ben noto, per produrre segnali di uscita differenziali sui loro collegamenti di uscita. Perciò, la differenza fra la tensione in corrispondenza del collegamento d'ingresso analogico 10 e la tensione di riferimento  $V_{REF}$  viene amplificata attraverso gli stadi a guadagno differenziale per produrre un segnale differenziale amplificato in

corrispondenza dei collegamenti di uscita 30 e 31 dell'amplificatore differenziale di aggancio 13. Mentre il segnale sull'ingresso di comando 35 è basso, entrambi i FET di commutazione Q13 e Q14 sono polarizzati nella condizione di spegnimento (OFF) fornente un'alta impedenza nel percorso di corrente dei FET di aggancio Q15 e Q16 e disabilitando entrambi i FET di aggancio.

In risposta ad un impulso di comando positivo sull'ingresso di comando 35, entrambi i FET di commutazione Q13 e Q14 sono commutati allo stato ON, presentando una bassa impedenza al passaggio di corrente attraverso i FET di aggancio Q15 e Q16 abilitando così entrambi i FET di aggancio. I segnali differenziali fra i collegamenti di uscita 30 e 31 dell'amplificatore differenziale d'aggancio 13 applicati ai FET di aggancio Q15 e Q16 collegati in croce determinano commutazione rigenerativa dei FET di aggancio. In dipendenza dalla polarità relativa dei segnali differenziali sui collegamenti di uscita 30 e 31, uno dei FET di aggancio Q15 e Q16 viene innescato in forte conduzione e l'altro viene effettivamente commutato in spegnimento. I FET Q11 e Q13 dell'amplificatore differenziale di aggancio 13 divengono i carichi resistivi dei FET di aggancio Q15 e Q16. Poichè uno dei FET di aggancio Q15 e Q16 sta funzionando in forte conduzione e l'altro è OFF, una tensione alta predeterminata viene prodotta su uno dei collegamenti 30, 31 ed una tensione

bassa predeterminata viene prodotta sull'altro. Il livello di tensione presente sul collegamento 31 è il segnale di uscita digitale sul terminale d'uscita digitale 15.

Una forma di realizzazione specifica di un circuito comparatore, del tipo descritto, per l'impiego in una apparecchiatura di modulazione sigma-delta impiegava una sorgente di tensione positiva  $+V_{DD}$  di +5 volt, una sorgente di tensione negativa  $-V_{SS}$  di -5 volt, ed una tensione di riferimento  $V_{REF}$  di +2,5 volt. Lo stadio amplificatore differenziale d'ingresso 11 produceva un guadagno di 21, e l'amplificatore differenziale intermedio produceva un guadagno di 10. Lo amplificatore differenziale di aggancio 13 produceva guadagno unitario nel modo di funzionamento non rigenerativo. La tensione di uscita sul terminale d'uscita digitale 15 durante un impulso di comando era 0 volt rappresentante uno 0 logico oppure +5/rappresentante un 1 logico. Il segnale di comando era un'onda quadra ad una frequenza di 2,048 MHz.

La risposta in frequenza di un circuito a MOS FET è fortemente correlata alle capacità parassita associate con i FET. Le capacità parassita principali sono quelle fra porta e sorgente, porta e pozzo, porta e massiccio (il materiale semiconduttore del massiccio), sorgente e massiccio, e pozzo e massiccio. Quando il FET è in stato OFF, predomina la capacità fra porta e massiccio. Nella saturazione, predomina la capacità fra porta e sorgente e nella re-

gione di funzionamento lineare, predominano entrambe le capacità fra porta e sorgente e porta e pozzo ed esse sono approssimativamente uguali. Le capacità fra pozzo e massiccio e sorgente e massiccio dipendono dalla tensione.

Per ottenere un funzionamento ad alta velocità in un circuito MOS FET, devono essere considerati gli effetti delle capacità parassita. Nel circuito comparatore illustrato e descritto precedentemente, i primi due stadi amplificatori differenziali 11 e 12 hanno il guadagno più alto e pure la velocità di commutazione più bassa. E' desiderabile che questi stadi abbiano a rimanere continuamente sensibili a piccole variazioni nel segnale d'ingresso analogico. In molti circuiti comparatori differenziali rigenerativi comandati della tecnica nota, tuttavia, gli stadi di ingresso sono disabilitati quando lo stadio rigenerativo viene agganciato al fine di impedire che un grande segnale di ingresso analogico differenziale abbia a superare l'azione rigenerativa e ad innescare prematuramente l'azione di aggancio rigenerativa. La disabilitazione può essere attuata impiegando ad esempio transistor di commutazione impedenti passaggio di corrente attraverso i FET di una coppia differenziale durante un impulso di comando. La disabilitazione degli stadi di ingresso limita la loro capacità di rispondere a minute variazioni nel segnale d'ingresso analogico, deviando il punto di polarizzazione di guadagno massimo ed introducendo un transitorio

di commutazione in ogni ciclo operativo. Nel circuito comparatore illustrato e descritto, gli stadi di ingresso rimangono attivi. Non vi sono transistor di commutazione collegati in serie con i FET di una coppia differenziale per disabilitarli durante gli impulsi di comando. Nella modulazione sigma-delta, la "tensione d'errore" o variazione di tensione fra campione e campione applicata sul collegamento d'ingresso analogico è relativamente piccola, ad esempio al massimo 3,6 millivolt. Quando amplificata per 210, il guadagno cumulativo dei primi due stadi amplificatori differenziali, allora un segnale massimo di 756 millivolt compare sugli ingressi dello stadio di aggancio. Questa tensione non è sufficiente a superare l'azione di aggancio rigenerativa mentre è presente l'impulso di comando.

Come è stato descritto precedentemente, durante l'aggancio rigenerativo l'uno o l'altro dei FET di aggancio Q15 e Q16 è fortemente conduttore. Nessuno degli altri FET è in forte conduzione. Al fine di ottenere un'elevata velocità di recupero, il guadagno non rigenerativo dell'amplificatore differenziale di aggancio 13 corrisponde all'unità e ad una corrente di riposo relativamente intensa è consentito di passare attraverso i FET di carico resistivi Q11 e Q12. Di conseguenza i FET Q9 e Q10 possono essere costruiti relativamente piccoli, e presentare una bassa capacità di porta per lo stadio precedente ed una bassa capacità fra pozzo e

massiccio per l'uscita dello stadio 13.

I FET di aggancio Q15 e Q16 sono abilitati dallo impulso di comando ai FET di commutazione separati Q13 e Q14. Impiegando FET di commutazione separati, entrambi i FET di aggancio accoppiati in modo incrociato Q15 e Q15 sono polarizzati allo stato OFF in corrispondenza dell'istante in cui l'impulso di comando viene applicato e quindi la capacità parassita fra porta e massiccio predomina. Perciò, quando l'azione rigenerativa inizia, l'accoppiamento capacitivo dall'ingresso di comando al collegamento 30 e al collegamento 31 è piccolo ed uguale, facilitando risposta rigenerativa appropriata quando la tensione differenziale sui collegamenti 30 e 31 è relativamente piccola.

Benchè sia stata illustrata e descritta quella che è considerata essere una forma di realizzazione preferita della presente invenzione, risulterà ovvio agli esperti del ramo che vari cambiamenti e modifiche possono essere apportati in essa senza allontanarsi dall'invenzione, quale definita nelle rivendicazioni accluse.

#### RIVENDICAZIONI

1. Circuito comparatore comprendente:

mezzi amplificatori differenziali di ingresso includenti un primo e secondo transistor ad effetto di campo,

l'ingresso del primo transistor ad effetto di

campo essendo collegato ad un terminale di ingresso di segnale e l'ingresso del secondo transistor ad effetto di campo essendo collegato ad un punto di potenziale di riferimento, ed un primo e secondo collegamenti di uscita per produrre segnali di uscita differenziali su essi;

mezzi amplificatori differenziali di aggancio includenti un primo e secondo transistor ad effetto di campo,

gli ingressi del primo e secondo transistor ad effetto di campo essendo collegati al primo e secondo collegamenti di uscita, rispettivamente, dei mezzi amplificatori differenziali di ingresso, e

un primo e secondo collegamenti di uscita per produrre segnali di uscita differenziali su essi; e

mezzi di aggancio rigenerativi richiedenti un primo ed un secondo transistor ad effetto di campo di aggancio,

l'ingresso del primo transistor ad effetto di campo d'aggancio essendo collegato al secondo transistoror ad effetto di campo d'aggancio e al secondo collegamento di uscita dei mezzi amplificatori differenziali d'aggancio,

l'ingresso del secondo transistor ad effetto di campo di aggancio essendo collegato al primo transistoror ad effetto di campo di aggancio ed al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio,

un terminale di uscita collegato ad uno dei transistor ad effetto di campo di aggancio,

il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, essendo atti ad essere fatti funzionare in un primo insieme di condizioni operative e a produrre un primo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali di una polarità relativa sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio, e essendo atti ad essere fatti funzionare in un secondo insieme di condizioni operative e a produrre un secondo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali di polarità opposta sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio, e

un primo e secondo transistor ad effetto di campo di commutazione collegati al primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, e atti ad essere fatti funzionare in risposta ad un segnale di comando applicato ad essi per abilitare il primo e secondo transistor ad effetto di campo di aggancio,

per cui, in risposta ad un segnale di comando, i transistor ad effetto di campo di commutazione abilitano i transistor ad effetto di campo di aggancio facendo in modo che i transistor ad effetto di campo di aggancio abbiano ad essere commutati mediante azione rigenerativa al primo e

secondo insieme di condizioni operative, producendo il primo e secondo segnale di uscita sul terminale di uscita, come determinato dalla polarità relativa dei segnali di uscita sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio.

2. Circuito comparatore secondo la rivendicazione

1, includente:

mezzi generatori di corrente;

il primo ed il secondo transistor ad effetto di campo di commutazione essendo collegati in serie tra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, ed i mezzi a generatore di corrente;

il primo e secondo transistor ad effetto di campo di commutazione fornendo un'alta impedenza fra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, e i mezzi generatori di corrente in assenza di un segnale di comando ad essi impedendo il passaggio di corrente attraverso i transistor ad effetto di campo di aggancio; e

il primo ed il secondo transistor ad effetto di campo di commutazione fornendo una bassa impedenza fra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, ed i mezzi generatori di corrente durante un segnale di comando ad essi consentendo il passaggio di corrente attraverso i transistor ad effetto di campo di ag-

gancio.

3. Circuito comparatore secondo la rivendicazione

2, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio sono collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, ed i mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato al primo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso, e l'elettrodo di porta del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali di ingresso;

il primo e secondo collegamenti di uscita dei mezzi amplificatori differenziali di aggancio sono collegati alle connessioni del primo e secondo transistor ad effetto di campo e del primo e secondo carichi resistivi, rispettivamente;

il primo transistor ad effetto di campo di aggancio ed il primo transistor ad effetto di campo di commutazione sono collegati in serie fra il primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio ed i mezzi generatori di corrente; ed il secondo transistor

ad effetto di campo di aggancio ed il secondo transistor ad effetto di campo di commutazione sono collegati in serie tra il secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio ed i mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo di aggancio è collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio, e l'elettrodo di porta del secondo transistor ad effetto di campo di aggancio è collegato al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio; e

gli elettrodi di porta del primo e secondo transistor ad effetto di campo di commutazione sono collegati assieme per ricevere su essi segnali di comando.

#### 4. Circuito comparatore secondo la rivendicazione 3, in cui:

il primo carico resistivo dei mezzi amplificatori differenziali di aggancio è collegato fra una sorgente di potenziale operativo ed uno degli elettrodi del percorso conduttivo del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

l'elettrodo dell'altro percorso conduttivo del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato direttamente ai mezzi generatori di corrente;

il secondo carico resistivo dei mezzi amplificatori differenziali di aggancio è collegato fra la sorgente di potenziale operativo ed uno degli elettrodi dei percorsi conduttivi del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

l'altro elettrodo del percorso conduttivo del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato direttamente ai mezzi generatori di corrente;

per cui il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio rimangono sensibili a variazioni nel segnale di uscita differenziale dai mezzi amplificatori differenziali d'ingresso applicato ad essi mentre i transistor ad effetto di campo di aggancio dei mezzi di aggancio rigenrativi sono abilitati e funzionano nel primo o secondo insieme di condizioni operative.

#### 5. Circuito comparatore secondo la rivendicazione 4, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali d'ingresso sono collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, e mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo è collegato al terminale d'ingresso del

segnalet;

l'elettrodo di porta del secondo transistor ad effetto di campo è collegato al punto di potenziale di riferimento; e

il primo e secondo collegamenti di uscita dei mezzi amplificatori differenziali di ingresso sono collegati alle connessioni del primo e secondo transistor ad effetto di campo e, al primo e secondo carichi resistivi, rispettivamente.

6. Circuito comparatore secondo la rivendicazione 5, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali d'ingresso, il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio, i transistor ad effetto di campo di aggancio ed i transistor ad effetto di campo di commutazione sono ciascuno costituito da un transistor ad effetto di campo ad arricchimento;

il primo e secondo carichi resistivi dei mezzi amplificatori differenziali di ingresso ed il primo e secondo carichi resistivi dei mezzi amplificatori differenziali di aggancio sono ciascuno costituito da un transistor ad effetto di campo del tipo ad impoverimento.

7. Circuito comparatore secondo la rivendicazione 6, includente mezzi amplificatori differenziali inter-

medi aventi

UFFICIO TECNICO INTERNAZIONALE BREVETTI

ING. ALESSANDRO ZINI

un primo ed un secondo transistor ad effetto di campo collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, e mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo essendo collegato al primo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso e l'elettrodo di porta del secondo transistor ad effetto di campo essendo collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso;

il punto di connessione del primo transistor ad effetto di campo e del primo carico resistivo essendo collegato all'elettrodo di porta del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio, e la connessione del secondo transistor ad effetto di campo e del secondo carico resistivo essendo collegata all'elettrodo di porta del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

il primo e secondo transistor ad effetto di campo essendo ciascuno costituiti da un transistor ad effetto di campo del tipo ad arricchimento;

il primo ed il secondo carichi resistivi essendo ciascuno costituito da un transistor ad effetto di campo del tipo ad impoverimento.

p.GTE LABORATORIES INC.

UFFICIO TECNICO INTERNAZIONALE BREVETTI

ING. ALESSANDRO ZINI

CIRCUITO COMPARATOREPreliminari dell'invenzione

La presente invenzione riguarda circuiti comparatori. Più particolarmente, essa riguarda circuiti comparatori impieganti transistor ad effetto di campo (FET) del tipo a metallo-ossido-silicio (MOS).

Un tipo di circuito comparatore che è stato recentemente sviluppato, impiega MOS FET in un circuito comparatore differenziale rigenerativo. Il circuito utilizza stadi amplificatori differenziali ed include una sezione di aggancio rigenerativa che aggancia una versione amplificata di una tensione di ingresso analogica. Una versione perfezionata di un tale circuito comparatore è illustrata e rivendicata nella domanda di brevetto italiana, numero 19955 A/82 depositata il 3 marzo 1982 a nome Micheal Cooperman e William L. Geller, intitolata "Comparator Circuit" (Circuito Comparatore) e ceduta alla richiedente della presente domanda. Per talune applicazioni, specificatamente in convertitori da digitale ad analogico e da analogico a digitale impiegati in apparecchiature di modulazione sigma-delta, è desiderabile fornire un circuito comparatore avente velocità e sensibilità ulteriormente migliorate.

Riassunto dell'invenzione

Con circuiti comparatori secondo la presente invenzione si ottengono caratteristiche di velocità e sensibilità migliorate. Questo circuito comparatore comprende mezzi ampli-

ficatori differenziali d'ingresso includenti un primo e secondo transistor ad effetto di campo, con l'ingresso del primo transistor ad effetto di campo collegato ad un terminale d'ingresso di segnale e l'ingresso del secondo transistor ad effetto di campo collegato ad un punto di potenziale di riferimento. I mezzi amplificatori differenziali d'ingresso hanno un primo ed un secondo collegamento d'uscita, su cui sono prodotti segnali d'uscita differenziali. Il circuito comparatore comprende pure mezzi amplificatori differenziali di aggancio includenti un primo e secondo transistor ad effetto di campo, con i loro ingressi collegati al primo e secondo collegamenti di uscita, rispettivamente, dei mezzi amplificatori differenziali di ingresso. I mezzi amplificatori differenziali di aggancio hanno un primo e secondo collegamenti di uscita su cui sono prodotti segnali d'uscita differenziali. Mezzi di aggancio rigenerativi includono un primo e secondo transistor ad effetto di campo di aggancio. L'ingresso del primo transistor ad effetto di campo di aggancio è collegato al secondo transistor ad effetto di campo di aggancio, ed al secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio. L'ingresso del secondo transistor ad effetto di campo di aggancio è collegato al primo transistor ad effetto di campo di aggancio ed al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio.

Un terminale di uscita è collegato ad uno dei transistor ad effetto di campo di aggancio. Il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, operano in un primo insieme di condizioni operative e producono un primo segnale di uscita sul terminale di uscita in risposta a segnali di uscita differenziali di una polarità relativa sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio. Il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, funzionano in un secondo insieme di condizioni operative e producono un secondo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali della polarità relativa opposta sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio. I mezzi di aggancio rigenerativi includono pure un primo e secondo transistor ad effetto di campo di commutazione collegati al primo e secondo transistor ad effetto di campo di aggancio, rispettivamente. I transistor ad effetto di campo di commutazione rispondono ad un segnale di comando per abilitare il primo e secondo transistor ad effetto di campo di aggancio. In tal modo, in risposta ad un segnale di comando, i transistor ad effetto di campo di commutazione abilitano i transistor ad effetto di campo di aggancio. I transistor ad effetto di campo di aggancio sono commutati tramite azione rigenerativa od al primo oppure al secondo insieme di condizioni operative, produ-

cendo od un primo oppure un secondo segnale di uscita sul terminale di uscita, nel modo determinato dalla polarità relativa dei segnali di uscita sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio.

Breve descrizione del disegno

L'unica figura del disegno è uno schema circuittale di massima di un circuito comparatore secondo la presente invenzione.

Per una migliore comprensione della presente invenzione, congiuntamente a suoi altri ed ulteriori scopi, vantaggi e possibilità, viene fatto riferimento alla descrizione che segue ed alle rivendicazioni accluse, in unione con il summenzionato disegno.

Descrizione dettagliata dell'invenzione

L'unica figura del disegno illustra un circuito comparatore a transistor ad effetto di campo (FET), del tipo a metallo-ossido-silicio (MOS) secondo la presente invenzione. Nel circuito illustrato, tutti i FET sono dispositivi del tipo ad arricchimento ed impoverimento a canale N. Come è ben noto, i dispositivi FET del circuito e i loro intercollegamenti illustrati possono essere fabbricati sotto forma di un circuito integrato, in un unico corpo di materiale semiconduttore.

Il circuito comparatore illustrato in figura include un amplificatore differenziale di ingresso 11, un amplificatore differenziale intermedio 12, un amplificatore differenziale d'aggancio 13 ed una sezione d'aggancio rigenera-

tiva 14. Segnali di ingresso analogici sono applicati in corrispondenza di un collegamento d'ingresso 10 e segnali d'uscita digitali sono prelevati su un terminale di uscita 15.

L'amplificatore differenziale d'ingresso 11 include due FET del tipo ad arricchimento Q1 e Q2, ciascuno avente uno dei suoi elettrodi del percorso conduttore (sorgente) collegato a quello dell'altro ed attraverso un generatore di corrente costante 21 ad una sorgente di tensione negativa  $-V_{SS}$ , che è pure collegata al substrato. Il collegamento di ingresso analogico 10 è collegato alla porta del FET Q1, e la porta del FET Q2 è collegata ad un punto di potenziale di riferimento  $V_{REF}$ . L'elettrodo dell'altro percorso conduttivo (pozzo) del FET Q1 è collegato ad un carico resistivo che è costituito da un FET Q3 del tipo a impoverimento avente la sua porta collegata direttamente alla sua sorgente ed il suo pozzo collegato ad una sorgente di tensione positiva  $+V_{DD}$ . Il pozzo del FET Q2 è analogamente collegato attraverso un carico resistivo costituito da un FET Q4 del tipo ad impoverimento avente la sua porta collegata alla sua sorgente ed il suo pozzo collegato ad una sorgente di tensione positiva  $+V_{DD}$ . Un primo ed un secondo collegamenti di uscita 22 e 23 sono prelevati in corrispondenza delle connessioni dei FET Q1 e Q2 con i FET Q3 e Q4, rispettivamente.

L'amplificatore differenziale intermedio 12

è simile all'amplificatore differenziale d'ingresso 11 ed include due FET Q5 e Q6 del tipo ad arricchimento aventi le loro porte collegate al primo e secondo collegamenti di uscita 22 e 23, rispettivamente, dell'amplificatore differenziale d'ingresso 11. Le sorgenti dei FET Q5 e Q6 sono collegate assieme e, attraverso un generatore di corrente costante 25, alla sorgente di tensione negativa  $-V_{SS}$ . I loro pozzi sono collegati attraverso carichi resistivi costituiti da FET Q7 e Q8 del tipo ad impoverimento, rispettivamente, alla sorgente di tensione positiva  $+V_{DD}$ . Un primo e secondo collegamenti d'uscita 26 e 27 sono prelevati in corrispondenza delle connessioni dei FET Q5 e Q6 con il FET Q7 e Q8, rispettivamente.

L'amplificatore differenziale di aggancio 13 include due FET Q9 e Q10 del tipo ad arricchimento aventi le loro porte collegate ai collegamenti di uscita 26 e 27, rispettivamente, dell'amplificatore differenziale intermedio 12. Le sorgenti dei FET Q9 e Q10 sono collegate assieme, e, attraverso un generatore di corrente costante 29, alla sorgente di tensione negativa  $-V_{SS}$ . I pozzi dei FET Q9 e Q10 sono collegati attraverso carichi resistivi formati da FET del tipo ad impoverimento Q11 e Q12, rispettivamente, alla sorgente di tensione positiva  $+V_{DD}$ .

La sezione di aggancio rigenerativa 14 include due FET di aggancio del tipo ad arricchimento Q15 e Q16. Le

porte ed i pozzi dei FET Q15 e Q16 sono collegati in croce. La porta del FET Q16 è pure collegata al collegamento di uscita 30 in corrispondenza della connessione dei FET Q9 e Q11 dell'amplificatore differenziale di aggancio. La porta <sup>31</sup> del FET Q15 è pure collegata al collegamento di uscita/in corrispondenza della connessione dei FET Q10 e Q12 dell'amplificatore differenziale di aggancio. Il terminale di uscita digitale 15 è collegato al collegamento d'uscita 31. La sorgente del FET Q15 è collegata al pozzo di un FET di commutazione del tipo ad arricchimento Q13. La sorgente del FET Q13 è collegata al generatore di corrente costante 29. Analogamente, un FET di commutazione del tipo ad arricchimento Q14 ha il suo pozzo collegato alla sorgente del FET Q16 e la sua sorgente è collegata al generatore di corrente costante 29. Le porte dei FET di commutazione Q13 e Q14 sono collegate assieme ad un collegamento di comando 35 a cui sono applicati impulsi di comando positivi, come sarà illustrato in seguito.

Gli stadi amplificatori differenziali 11, 12 e 13 funzionano, come è ben noto, per produrre segnali di uscita differenziali sui loro collegamenti di uscita. Perciò, la differenza fra la tensione in corrispondenza del collegamento d'ingresso analogico 10 e la tensione di riferimento  $V_{REF}$  viene amplificata attraverso gli stadi a guadagno differenziale per produrre un segnale differenziale amplificato in

corrispondenza dei collegamenti di uscita 30 e 31 dell'amplificatore differenziale di aggancio 13. Mentre il segnale sull'ingresso di comando 35 è basso, entrambi i FET di commutazione Q13 e Q14 sono polarizzati nella condizione di spegnimento (OFF) fornente un'alta impedenza nel percorso di corrente dei FET di aggancio Q15 e Q16 e disabilitando entrambi i FET di aggancio.

In risposta ad un impulso di comando positivo sull'ingresso di comando 35, entrambi i FET di commutazione Q13 e Q14 sono commutati allo stato ON, presentando una bassa impedenza al passaggio di corrente attraverso i FET di aggancio Q15 e Q16 abilitando così entrambi i FET di aggancio. I segnali differenziali fra i collegamenti di uscita 30 e 31 dell'amplificatore differenziale d'aggancio 13 applicati ai FET di aggancio Q15 e Q16 collegati in croce determinano commutazione rigenerativa dei FET di aggancio. In dipendenza dalla polarità relativa dei segnali differenziali sui collegamenti di uscita 30 e 31, uno dei FET di aggancio Q15 e Q16 viene innescato in forte conduzione e l'altro viene effettivamente commutato in spegnimento. I FET Q11 e Q13 dell'amplificatore differenziale di aggancio 13 divengono i carichi resistivi dei FET di aggancio Q15 e Q16. Poichè uno dei FET di aggancio Q15 e Q16 sta funzionando in forte conduzione e l'altro è OFF, una tensione alta predeterminata viene prodotta su uno dei collegamenti 30, 31 ed una tensione

bassa predeterminata viene prodotta sull'altro. Il livello di tensione presente sul collegamento 31 è il segnale di uscita digitale sul terminale d'uscita digitale 15.

Una forma di realizzazione specifica di un circuito comparatore, del tipo descritto, per l'impiego in una apparecchiatura di modulazione sigma-delta impiegava una sorgente di tensione positiva  $+V_{DD}$  di +5 volt, una sorgente di tensione negativa  $-V_{SS}$  di -5 volt, ed una tensione di riferimento  $V_{REF}$  di +2,5 volt. Lo stadio amplificatore differenziale d'ingresso 11 produceva un guadagno di 21, e l'amplificatore differenziale intermedio produceva un guadagno di 10. Lo amplificatore differenziale di aggancio 13 produceva guadagno unitario nel modo di funzionamento non rigenerativo. La tensione di uscita sul terminale d'uscita digitale 15 durante un impulso di comando era 0 volt rappresentante uno 0 logico oppure +5/rappresentante un 1 logico. Il segnale di comando era un'onda quadra ad una frequenza di 2,048 MHz.

La risposta in frequenza di un circuito a MOS FET è fortemente correlata alle capacità parassita associate con i FET. Le capacità parassita principali sono quelle fra porta e sorgente, porta e pozzo, porta e massiccio (il materiale semiconduttore del massiccio), sorgente e massiccio, e pozzo e massiccio. Quando il FET è in stato OFF, predomina la capacità fra porta e massiccio. Nella saturazione, predomina la capacità fra porta e sorgente e nella re-

gione di funzionamento lineare, predominano entrambe le capacità fra porta e sorgente e porta e pozzi ed esse sono approssimativamente uguali. Le capacità fra pozzi e massiccio e sorgente e massiccio dipendono dalla tensione.

Per ottenere un funzionamento ad alta velocità in un circuito MOS FET, devono essere considerati gli effetti delle capacità parassita. Nel circuito comparatore illustrato e descritto precedentemente, i primi due stadi amplificatori differenziali 11 e 12 hanno il guadagno più alto e pure la velocità di commutazione più bassa. E' desiderabile che questi stadi abbiano a rimanere continuamente sensibili a piccole variazioni nel segnale d'ingresso analogico. In molti circuiti comparatori differenziali rigenerativi comandati dalla tecnica nota, tuttavia, gli stadi di ingresso sono disabilitati quando lo stadio rigenerativo viene agganciato al fine di impedire che un grande segnale di ingresso analogico differenziale abbia a superare l'azione rigenerativa e ad innescare prematuramente l'azione di aggancio rigenerativa. La disabilitazione può essere attuata impiegando ad esempio transistor di commutazione impedenti passaggio di corrente attraverso i FET di una coppia differenziale durante un impulso di comando. La disabilitazione degli stadi di ingresso limita la loro capacità di rispondere a minute variazioni nel segnale d'ingresso analogico, deviando il punto di polarizzazione di guadagno massimo ed introducendo un transitorio

di commutazione in ogni ciclo operativo. Nel circuito comparatore illustrato e descritto, gli stadi di ingresso rimangono attivi. Non vi sono transistor di commutazione collegati in serie con i FET di una coppia differenziale per disabilitarli durante gli impulsi di comando. Nella modulazione sigma-delta, la "tensione d'errore" o variazione di tensione fra campione e campione applicata sul collegamento d'ingresso analogico è relativamente piccola, ad esempio al massimo 3,6 millivolt. Quando amplificata per 210, il guadagno cumulativo dei primi due stadi amplificatori differenziali, allora un segnale massimo di 756 millivolt compare sugli ingressi dello stadio di aggancio. Questa tensione non è sufficiente a superare l'azione di aggancio rigenerativa mentre è presente l'impulso di comando.

Come è stato descritto precedentemente, durante l'aggancio rigenerativo l'uno o l'altro dei FET di aggancio Q15 e Q16 è fortemente conduttore. Nessuno degli altri FET è in forte conduzione. Al fine di ottenere un'elevata velocità di recupero, il guadagno non rigenerativo dell'amplificatore differenziale di aggancio 13 corrisponde all'unità e ad una corrente di riposo relativamente intensa è consentito di passare attraverso i FET di carico resistivi Q11 e Q12. Di conseguenza i FET Q9 e Q10 possono essere costruiti relativamente piccoli, e presentare una bassa capacità di porta per lo stadio precedente ed una bassa capacità fra pozzo e

massiccio per l'uscita dello stadio 13.

I FET di aggancio Q15 e Q16 sono abilitati dallo impulso di comando ai FET di commutazione separati Q13 e Q14. Impiegando FET di commutazione separati, entrambi i FET di aggancio accoppiati in modo incrociato Q15 e Q15 sono polarizzati allo stato OFF in corrispondenza dell'istante in cui l'impulso di comando viene applicato e quindi la capacità parassita fra porta e massiccio predomina. Perciò, quando l'azione rigenerativa inizia, l'accoppiamento capacitivo dall'ingresso di comando al collegamento 30 e al collegamento 31 è piccolo ed uguale, facilitando risposta rigenerativa appropriata quand'è la tensione differenziale sui collegamenti 30 e 31 è relativamente piccola.

Benchè sia stata illustrata e descritta quella che è considerata essere una forma di realizzazione preferita della presente invenzione, risulterà ovvio agli esperti del ramo che vari cambiamenti e modifiche possono essere apportati in essa senza allontanarsi dall'invenzione, quale definita nelle rivendicazioni accluse.

#### RIVENDICAZIONI

##### 1. Circuito comparatore comprendente:

mezzi amplificatori differenziali di ingresso includenti un primo e secondo transistor ad effetto di campo,

l'ingresso del primo transistor ad effetto di

campo essendo collegato ad un terminale di ingresso di segnale e l'ingresso del secondo transistor ad effetto di campo essendo collegato ad un punto di potenziale di riferimento, ed un primo e secondo collegamenti di uscita per produrre segnali di uscita differenziali su essi;

mezzi amplificatori differenziali di aggancio includenti un primo e secondo transistor ad effetto di campo,

gli ingressi del primo e secondo transistor ad effetto di campo essendo collegati al primo e secondo collegamenti di uscita, rispettivamente, dei mezzi amplificatori differenziali di ingresso, e

un primo e secondo collegamenti di uscita per produrre segnali di uscita differenziali su essi; e

mezzi di aggancio rigenerativi richiedenti un primo ed un secondo transistor ad effetto di campo di aggancio,

l'ingresso del primo transistor ad effetto di campo d'aggancio essendo collegato al secondo transistoror ad effetto di campo d'aggancio e al secondo collegamento di uscita dei mezzi amplificatori differenziali d'aggancio,

l'ingresso del secondo transistor ad effetto di campo di aggancio essendo collegato al primo transistoror ad effetto di campo di aggancio ed al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio,

un terminale di uscita collegato ad uno dei transistor ad effetto di campo di aggancio,

il primo e secondo transistor ad effetto di campo di aggancio, quando abilitati, essendo atti ad essere fatti funzionare in un primo insieme di condizioni operative e a produrre un primo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali di una polarità relativa sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio, e essendo atti ad essere fatti funzionare in un secondo insieme di condizioni operative e a produrre un secondo segnale di uscita sul terminale di uscita in risposta a segnali d'uscita differenziali di polarità opposta sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio, e

un primo e secondo transistor ad effetto di campo di commutazione collegati al primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, e atti ad essere fatti funzionare in risposta ad un segnale di comando applicato ad essi per abilitare il primo e secondo transistor ad effetto di campo di aggancio,

per cui, in risposta ad un segnale di comando, i transistor ad effetto di campo di commutazione abilitano i transistor ad effetto di campo di aggancio facendo in modo che i transistor ad effetto di campo di aggancio abbiano ad essere commutati mediante azione rigenerativa al primo e

secondo insieme di condizioni operative, producendo il primo e secondo segnale di uscita sul terminale di uscita, come determinato dalla polarità relativa dei segnali di uscita sui collegamenti di uscita dei mezzi amplificatori differenziali di aggancio.

2. Circuito comparatore secondo la rivendicazione 1, includente:

mezzi generatori di corrente;

il primo ed il secondo transistor ad effetto di campo di commutazione essendo collegati in serie tra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, ed i mezzi a generatore di corrente;

il primo e secondo transistor ad effetto di campo di commutazione fornendo un'alta impedenza fra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, e i mezzi generatori di corrente in assenza di un segnale di comando ad essi impedendo il passaggio di corrente attraverso i transisitor ad effetto di campo di aggancio; e

il primo ed il secondo transistor ad effetto di campo di commutazione fornendo una bassa impedenza fra il primo e secondo transistor ad effetto di campo di aggancio, rispettivamente, ed i mezzi generatori di corrente durante un segnale di comando ad essi consentendo il passaggio di corrente attraverso i transistor ad effetto di campo di ag-

gancio.

3. Circuito comparatore secondo la rivendicazione

2, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio sono collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, ed i mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato al primo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso, e l'elettrodo di porta del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali di ingresso;

il primo e secondo collegamenti di uscita dei mezzi amplificatori differenziali di aggancio sono collegati alle connessioni del primo e secondo transistor ad effetto di campo e del primo e secondo carichi resistivi, rispettivamente;

il primo transistor ad effetto di campo di aggancio ed il primo transistor ad effetto di campo di commutazione sono collegati in serie fra il primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio ed i mezzi generatori di corrente, ed il secondo transistor

ad effetto di campo di aggancio ed il secondo transistor ad effetto di campo di commutazione sono collegati in serie tra il secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio ed i mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo di aggancio è collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali di aggancio, e l'elettrodo di porta del secondo transistor ad effetto di campo di aggancio è collegato al primo collegamento di uscita dei mezzi amplificatori differenziali di aggancio; e

gli elettrodi di porta del primo e secondo transistor ad effetto di campo di commutazione sono collegati assieme per ricevere su essi segnali di comando.

#### 4. Circuito comparatore secondo la rivendicazione 3, in cui:

il primo carico resistivo dei mezzi amplificatori differenziali di aggancio è collegato fra una sorgente di potenziale operativo ed uno degli elettrodi del percorso conduttivo del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

l'elettrodo dell'altro percorso conduttivo del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato direttamente ai mezzi generatori di corrente;

il secondo carico resistivo dei mezzi amplificatori differenziali di aggancio è collegato fra la sorgente di potenziale operativo ed uno degli elettrodi dei percorsi conduttivi del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

l'altro elettrodo del percorso conduttivo del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio è collegato direttamente ai mezzi generatori di corrente;

per cui il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio rimangono sensibili a variazioni nel segnale di uscita differenziale dai mezzi amplificatori differenziali d'ingresso applicato ad essi mentre i transistor ad effetto di campo di aggancio dei mezzi di aggancio rigenrativi sono abilitati e funzionano nel primo o secondo insieme di condizioni operative.

#### 5. Circuito comparatore secondo la rivendicazione 4, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali d'ingresso sono collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, e mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo è collegato al terminale d'ingresso del

segnale;

l'elettrodo di porta del secondo transistor ad effetto di campo è collegato al punto di potenziale di riferimento; e

il primo e secondo collegamenti di uscita dei mezzi amplificatori differenziali di ingresso sono collegati alle connessioni del primo e secondo transistor ad effetto di campo e al primo e secondo carichi resistivi, rispettivamente.

6. Circuito comparatore secondo la rivendicazione 5, in cui:

il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali d'ingresso, il primo e secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio, i transistor ad effetto di campo di aggancio ed i transistor ad effetto di campo di commutazione sono ciascuno costituito da un transistor ad effetto di campo ad arricchimento;

il primo e secondo carichi resistivi dei mezzi amplificatori differenziali di ingresso ed il primo e secondo carichi resistivi dei mezzi amplificatori differenziali di aggancio sono ciascuno costituito da un transistor ad effetto di campo del tipo ad impoverimento.

7. Circuito comparatore secondo la rivendicazione 6, includente mezzi amplificatori differenziali inter-

medi aventi

un primo ed un secondo transistor ad effetto di campo collegati in serie fra un primo e secondo carichi resistivi, rispettivamente, e mezzi generatori di corrente;

l'elettrodo di porta del primo transistor ad effetto di campo essendo collegato al primo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso e l'elettrodo di porta del secondo transistor ad effetto di campo essendo collegato al secondo collegamento di uscita dei mezzi amplificatori differenziali d'ingresso;

il punto di connessione del primo transistor ad effetto di campo e del primo carico resistivo essendo collegato all'elettrodo di porta del primo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio, e la connessione del secondo transistor ad effetto di campo e del secondo carico resistivo essendo collegata all'elettrodo di porta del secondo transistor ad effetto di campo dei mezzi amplificatori differenziali di aggancio;

il primo e secondo transistor ad effetto di campo essendo ciascuno costituiti da un transistor ad effetto di campo del tipo ad arricchimento;

il primo ed il secondo carichi resistivi essendo ciascuno costituito da un transistor ad effetto di campo del tipo ad impoverimento.

TAV. 1-I

UFFICIO TECNICO INTERNAZIONALE BREVETTI

ING. ALESSANDRO ZINI

24706A/82

I l'Ufficio dei Brevetti

Pavia - Rogante