## (19) **日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)特許出願公開番号

特開2017-117905 (P2017-117905A)

(43) 公開日 平成29年6月29日(2017.6.29)

| (51) Int.Cl. |         |           | F 1     |        |           | テーマコート    | ド (参考) |

|--------------|---------|-----------|---------|--------|-----------|-----------|--------|

| HO1L         | 21/60   | (2006.01) | HO1L    | 21/92  | 603G      | 5F033     |        |

| HO1L         | 23/522  | (2006.01) | HO1L    | 21/88  | T         | 5F057     |        |

| HO1L         | 21/768  | (2006.01) | HO1L    | 21/304 | 622J      | 5 F 1 3 1 |        |

| HO1L         | 21/3205 | (2006.01) | HO1L    | 21/92  | 602K      |           |        |

| HO1L         | 21/304  | (2006.01) | HO1L    | 21/68  | N         |           |        |

|              |         |           | 審査請求 未請 | 求 請求」  | 頁の数 20 OL | (全 26 頁)  | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2015-250866 (P2015-250866)

平成27年12月24日(2015.12.24)

(71) 出願人 302062931

ルネサスエレクトロニクス株式会社 東京都江東区豊洲三丁目2番24号

(74)代理人 110002066

特許業務法人筒井国際特許事務所

(72) 発明者 太田 祐一

群馬県高崎市西横手町111 ルネサスセミコンダクタパッケージ&テストソリュー

ションズ株式会社内

(72) 発明者 喜多 賢太郎

茨城県ひたちなか市堀口751番地 ルネ サスセミコンダクタマニュファクチュアリ

ング株式会社内

最終頁に続く

# (54) 【発明の名称】半導体装置の製造方法および半導体ウェハ

# (57)【要約】

【課題】半導体装置の製造歩留りを向上する。

【解決手段】複数のボンディングパッドBPを覆う絶縁膜PSNと、絶縁膜PSN上に形成された第1保護膜RF1と、第1保護膜RF1上に形成された第2保護膜RF2と、を備える。製品チップSC1では、絶縁膜PSNに形成された第1開口部C1および第1保護膜RF1に形成された第2開口部C2を介して、複数の電極層MLが複数のボンディングパッドBPとそれぞれ電気的に接続し、第2保護膜RF2に形成された第3開口部C3を介して、複数のバンプ電極BEが複数の電極層MLとそれぞれ電気的に接続する。擬似チップSC2では、第1保護膜RF1に形成された第2開口部C2と、第2保護膜RF2に形成された第2開口部C2と、第2保護関RF2に形成された第3開口部C2と、第3開口部C3が重なる第2開口部C2の底面に絶縁膜PSNが露出する。そして、複数のバンプ電極BEを覆うように主面上に保護テープが貼り付けられる。

【選択図】図3

#### 【特許請求の範囲】

## 【請求項1】

以下の工程を含む半導体装置の製造方法:

- (a)主面と、前記主面を取り囲む周縁と、前記主面に形成された半導体素子を備える複数の第1チップと、複数の前記第1チップを取り囲み、前記周縁に接する複数の第2チップと、を有し、複数の前記第1チップのそれぞれに複数のボンディングパッドが形成された半導体ウェハを準備する工程;

- (b)前記主面上に絶縁膜を形成する工程;

- (c)前記第1チップの前記絶縁膜に、複数の第1開口部を形成して、前記第1開口部の底面に前記ボンディングパッドを露出させる工程;

- ( d ) 前記主面上に第1保護膜を形成する工程;

- (e)前記第1チップおよび前記第2チップの前記第1保護膜に、複数の第2開口部をそれぞれ形成して、前記第1チップでは、平面視において前記第2開口部と重なる前記第1開口部の底面に前記ボンディングパッドを露出させ、前記第2チップでは、前記第2開口部の底面に前記絶縁膜を露出させる工程;

- (f)前記第1開口部および前記第2開口部を介して、複数の前記ボンディングパッドとそれぞれ電気的に接続する複数の電極層を形成する工程;

- ( g ) 前記主面上に第2保護膜を形成する工程;

- (h)前記第1チップおよび前記第2チップの前記第2保護膜に、複数の第3開口部をそれぞれ形成して、前記第1チップでは、前記第3開口部の底面に前記電極層を露出させ、前記第2チップでは、平面視において前記第3開口部と重なる前記第2開口部の底面に前記絶縁膜を露出させる工程;

- (i) 複数の前記電極層とそれぞれ電気的に接続する複数の外部電極を形成する工程;

- ( i ) 前記主面上に、複数の前記外部電極を覆う保護テープを貼り付ける工程。

#### 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第2チップの前記周縁に最も近い位置にある前記第3開口部の開口面積は、前記第1チップの前記第3開口部の開口面積よりも小さい、半導体装置の製造方法。

#### 【請求項3】

請求項1記載の半導体装置の製造方法において、

前記第2チップの前記第3開口部のピッチは、前記第1チップの前記第3開口部のピッチと同じである、半導体装置の製造方法。

#### 【請求項4】

請求項1記載の半導体装置の製造方法において、

前記第2チップには、前記外部電極を形成しない、半導体装置の製造方法。

## 【請求項5】

請求項1記載の半導体装置の製造方法において、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、前記スクライブ領域には、前記第1保護膜および前記第2保護膜は形成されていない、

#### 【請求項6】

半導体装置の製造方法。

以下の工程を含む半導体装置の製造方法:

- (a)主面と、前記主面を取り囲む周縁と、前記主面に形成された半導体素子を備える複数の第1チップと、複数の前記第1チップを取り囲み、前記周縁に接する複数の第2チップと、を有し、複数の前記第1チップのそれぞれに複数のボンディングパッドが形成された半導体ウェハを準備する工程;

- ( b ) 前記主面上に絶縁膜を形成する工程;

- (c)前記第1チップの前記絶縁膜に、複数の第1開口部を形成して、前記第1開口部の底面に前記ボンディングパッドを露出させる工程;

10

20

30

40

- (d)前記主面上に第1保護膜を形成する工程;

- ( e )前記第1チップの前記第1保護膜に、複数の第2開口部を形成して、平面視にお いて前記第2開口部と重なる前記第1開口部の底面に前記ボンディングパッドを露出させ る工程;

- ( f ) 前記第 1 開口部および前記第 2 開口部を介して、複数の前記ボンディングパッド とそれぞれ電気的に接続する複数の電極層を形成する工程;

- (g)前記主面上に第2保護膜を形成する工程;

- ( h ) 前記第1チップの前記第2保護膜に、複数の第3開口部を形成して、前記第3開 口部の底面に前記電極層を露出させ、前記第2チップの前記第1保護膜および前記第2保 護膜に、複数の第4開口部を形成して、前記第4開口部の底面に前記絶縁膜を露出させる 工程;

- ( i ) 複数の前記電極層とそれぞれ電気的に接続する複数の外部電極を形成する工程: ( j )前記主面上に、複数の前記外部電極を覆う保護テープを貼り付ける工程。

# 【請求項7】

請求項6記載の半導体装置の製造方法において、

前記第4開口部の平面視における形状は、円形状、楕円形状、四角形状またはストライ プ形状である、半導体装置の製造方法。

#### 【請求項8】

請求項6記載の半導体装置の製造方法において、

前記第2チップには、前記外部電極を形成しない、半導体装置の製造方法。

#### 【請求項9】

請求項6記載の半導体装置の製造方法において、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り 合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、 前記スクライブ領域には、前記第1保護膜および前記第2保護膜は形成されていない、 半導体装置の製造方法。

# 【請求項10】

主面と、

前記主面を取り囲む周縁と、

前記主面に形成された半導体素子を備える複数の第1チップと、

複数の前記第 1 チップを取り囲み、前記周縁に接する複数の第 2 チップと、

複数の前記第1チップにそれぞれ形成された複数のボンディングパッドと、

前記複数のボンディングパッドを覆い、前記主面上に形成された絶縁膜と、

前 記 第 1 チ ッ プ の 前 記 絶 縁 膜 に 形 成 さ れ 、 前 記 複 数 の ボ ン デ ィ ン グ パ ッ ド の 上 面 の 一 部 をそれぞれ露出する複数の第1開口部と、

前記絶縁膜上に形成された第1保護膜と、

前記第1チップの前記第1保護膜に形成され、平面視において複数の前記第1開口部と それぞれ重なり、前記複数のボンディングパッドの上面の一部をそれぞれ露出する複数の 第2開口部と、

前記第2チップの前記第1保護膜に形成され、前記絶縁膜を露出する複数の第3開口部 と、

前 記 第 1 開 口 部 お よ び 前 記 第 2 開 口 部 を 介 し て 、 前 記 複 数 の ボ ン デ ィ ン グ パ ッ ド と そ れ ぞれ電気的に接続する複数の電極層と、

前記複数の電極層を覆い、前記主面上に形成された第2保護膜と、

前記第1チップの前記第2保護膜に形成され、前記複数の電極層の上面の一部をそれぞ れ露出する複数の第4開口部と、

前記第2チップの前記第2保護膜に形成され、平面視において複数の前記第3開口部と それぞれ重なり、前記絶縁膜を露出する複数の第5開口部と、

前記第4開口部を介して、前記複数の電極層とそれぞれ電気的に接続する複数の外部電 極と、

10

20

30

40

複数の前記外部電極を覆い、前記主面上に貼り付けられた保護テープと、 を有する、半導体ウェハ。

## 【請求項11】

請求項10記載の半導体ウェハにおいて、

前記第2チップの前記周辺に最も近い位置にある前記第5開口部の開口面積は、前記第1チップの前記第4開口部の開口面積よりも小さい、半導体ウェハ。

#### 【請求項12】

請求項10記載の半導体ウェハにおいて、

前記第2チップの前記第5開口部のピッチと、前記第1チップの前記第4開口部のピッチとは同じである、半導体ウェハ。

## 【請求項13】

請求項10記載の半導体ウェハにおいて、

前記第5開口部の平面視における形状は、円形状、楕円形状、四角形状またはストライプ形状である、半導体ウェハ。

## 【請求項14】

請求項10記載の半導体ウェハにおいて、

前記第2チップには、前記外部電極を有しない、半導体ウェハ。

#### 【請求項15】

請求項10記載の半導体ウェハにおいて、

前記第2チップでは、前記保護テープは、前記第1保護膜、前記第2保護膜および複数の前記第3開口部の底面にそれぞれ露出する前記絶縁膜と接する、半導体ウェハ。

#### 【請求項16】

請求項10記載の半導体ウェハにおいて、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、前記スクライブ領域では、前記第1保護膜および前記第2保護膜が形成されておらず、前記保護テープとは、前記絶縁膜と接する、半導体ウェハ。

#### 【請求項17】

請求項10記載の半導体ウェハにおいて、

前記保護テープと前記絶縁膜との接着力が、前記保護テープと前記第1保護膜および前記第2保護膜との接着力よりも弱い、半導ウェハ。

# 【請求項18】

請求項10記載の半導体ウェハにおいて、

前記保護テープは、糊層と、ベース層と、前記糊層と前記ベース層との間に設けられた中間層とから構成され、

前記糊層および前記中間層は、前記ベース層よりも柔らかく、

前記糊層と前記中間層の合計の厚さが、前記外部電極の高さよりも厚い、半導体ウェハ

# 【請求項19】

請求項10記載の半導体ウェハにおいて、

前記絶縁膜は、窒化シリコン膜、酸化シリコン膜、または窒化シリコン膜と酸化シリコン膜との積層膜であり、前記第 1 保護膜および前記第 2 保護膜はポリイミド膜である、半導体ウェハ。

# 【請求項20】

請求項10記載の半導体ウェハにおいて、

平面視における前記第3開口部の開口面積と、前記第5開口部の開口面積とが同じである、半導体ウェハ。

## 【発明の詳細な説明】

# 【技術分野】

[0001]

20

10

30

40

本発明は半導体装置の製造方法および半導体ウェハに関し、例えば半導体ウェハの主面に複数のバンプ電極を備える半導体装置の製造に好適に利用できるものである。

#### 【背景技術】

[0002]

ウェハの外周部から数mmの領域にパッシベーション膜を残しつつ、スクライブライン上のパッシベーション膜を除去することにより、スクライブラインと保護テープの隙間をウェハの外周部に達するまでに閉じる技術が特開 2 0 0 7 - 3 6 1 2 9 号公報 (特許文献 1)に記載されている。

[0003]

また、製品にはならない不完全な擬似チップが形成される擬似チップ領域に、製品チップ領域に形成される部材のパターンと同一のパターンの部材を形成することにより、CMP (Chemical Mechanical Polishing)工程における研磨膜の残膜厚の均一性を向上する技術が特開平11-45868号公報(特許文献2)に記載されている。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2007-36129号公報

【特許文献2】特開平11-45868号公報

【発明の概要】

【発明が解決しようとする課題】

[00005]

現在、半導体ウェハに形成された複数の半導体チップのそれぞれに、半導体集積回路の最上層配線と電気的に接続する複数のバンプ電極を形成した後、半導体ウェハの裏面を研削する方法が採用されている。しかし、この研削工程では、複数のバンプ電極を覆うように半導体ウェハの主面上に保護テープを貼り付ける必要がある。このため、研削工程において水の侵入を防止するために半導体ウェハの主面の外周部に形成された感光性ポリイミドからなる壁(例えば前記特許文献 1 参照)に、保護テープが強く貼り付いて剥がし難くなる、または保護テープを剥離した後に、保護テープの糊がバンプ電極の表面に残り、導通不良の原因になる、などの問題がある。

[0006]

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0007]

10

20

30

40

[00008]

また、一実施の形態による半導体ウェハは、主面と、主面を取り囲む周縁と、主面に形 成された半導体素子を備える複数の製品チップと、複数の製品チップを取り囲み、周縁に 接 す る 複 数 の 擬 似 チ ッ プ と 、 複 数 の 製 品 チ ッ プ に そ れ ぞ れ 形 成 さ れ た 複 数 の ボ ン デ ィ ン グ パッドと、を有する。さらに、複数のボンディングパッドを覆い、主面上に形成された絶 縁膜と、製品チップの絶縁膜に形成され、複数のボンディングパッドの上面の一部をそれ ぞれ露出する複数の第1開口部と、絶縁膜上に形成された第1保護膜と、を有する。さら に、製品チップの第1保護膜に形成され、平面視において複数の第1開口部とそれぞれ重 なり、複数のボンディングパッドの上面の一部をそれぞれ露出する複数の第2開口部と、 擬似チップの第1保護膜に形成され、絶縁膜を露出する複数の第3開口部と、を有する。 さらに、第1開口部および第2開口部を介して、複数のボンディングパッドとそれぞれ電 気的に接続する複数の電極層と、複数の電極層を覆い、主面上に形成された第2保護膜と 、 を 有 す る 。 さ ら に 、 製 品 チ ッ プ の 第 2 保 護 膜 に 形 成 さ れ 、 複 数 の 電 極 層 の 上 面 の 一 部 を それぞれ露出する複数の第4開口部と、擬似チップの第2保護膜に形成され、平面視にお いて複数の第3開口部とそれぞれ重なり、絶縁膜を露出する複数の第5開口部と、を有す る。さらに、第4開口部を介して、複数の電極層とそれぞれ電気的に接続する複数の外部 電極と、複数の外部電極を覆い、主面上に貼り付けられた保護テープと、を有する。

【発明の効果】

[0009]

一実施の形態によれば、半導体装置の製造歩留りを向上することができる。

【図面の簡単な説明】

[0010]

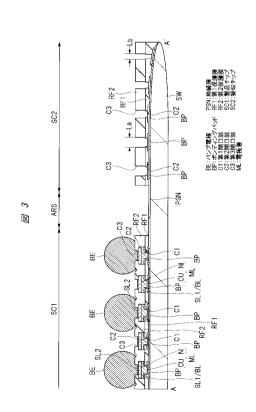

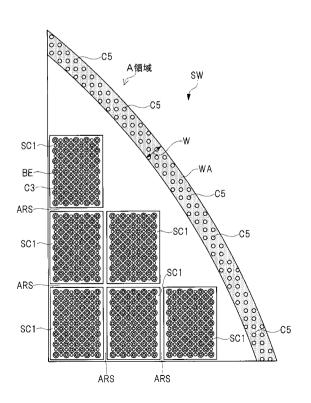

【図1】一実施の形態による複数の半導体チップが形成された半導体ウェハの主面上の状 態を示す上面図である。

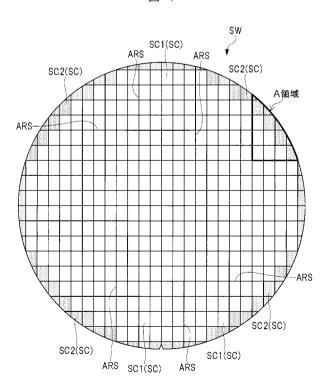

- 【図2】図1のA領域を拡大して示す上面図である。

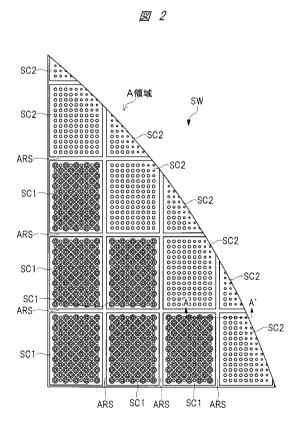

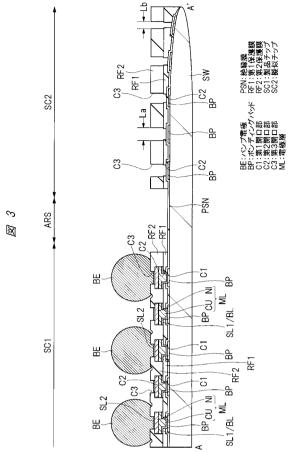

- 【図3】図2のA-A´線に沿った断面図である。

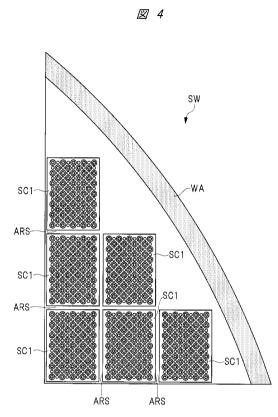

- 【 図 4 】 本 発 明 者 ら が 比 較 検 討 し た 複 数 の 半 導 体 チ ッ プ が 形 成 さ れ た 半 導 体 ウ ェ 八 の 一 部 の主面上の状態を拡大して示す上面図である。

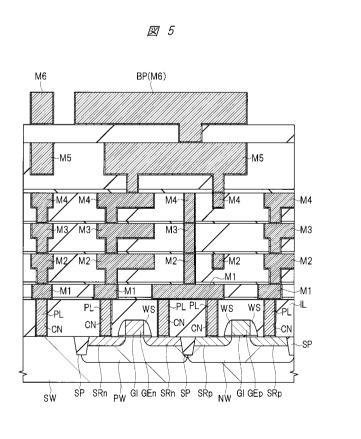

- 【図5】一実施の形態による半導体装置の製造工程を示す断面図である。

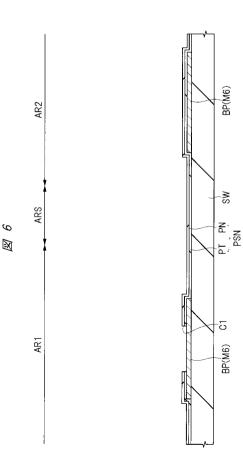

- 【図6】図5に続く、半導体装置の製造工程を示す断面図である。

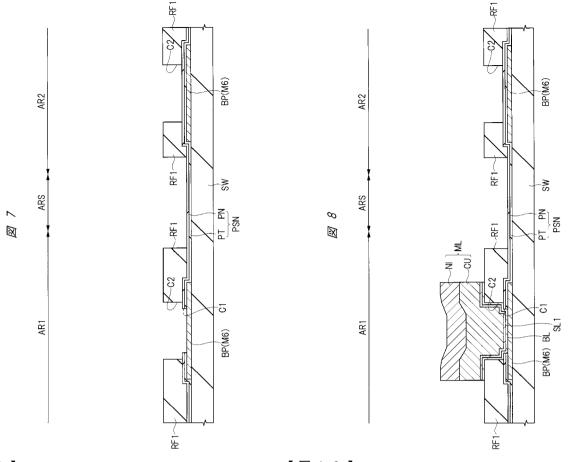

- 【図7】図6に続く、半導体装置の製造工程を示す断面図である。

- 【図8】図7に続く、半導体装置の製造工程を示す断面図である。

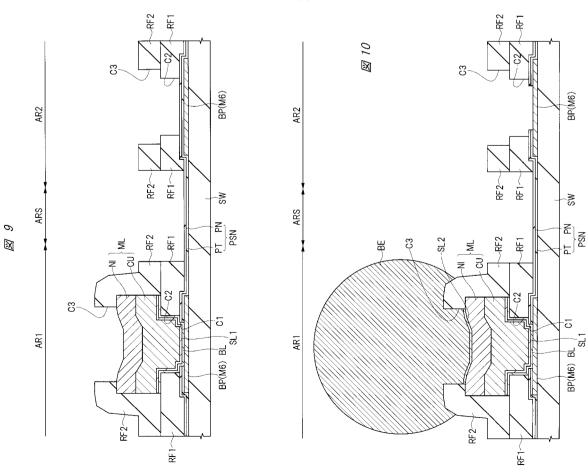

- 【図9】図8に続く、半導体装置の製造工程を示す断面図である。

- 【図10】図9に続く、半導体装置の製造工程を示す断面図である。

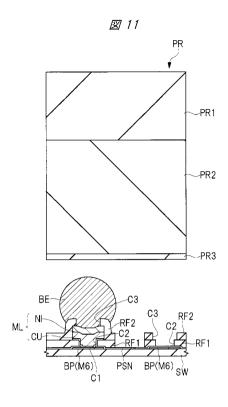

- 【図11】図10に続く、半導体装置の製造工程を示す断面図である。

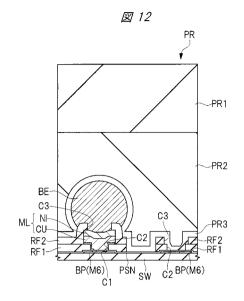

- 【図12】図11に続く、半導体装置の製造工程を示す断面図である。

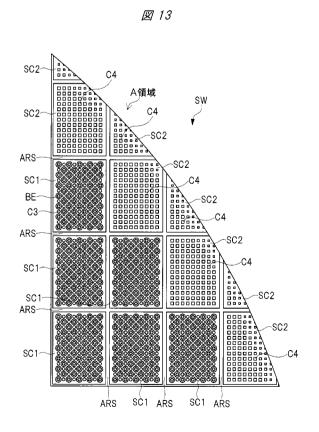

- 【 図 1 3 】 一 実 施 の 形 態 の 第 1 変 形 例 に よ る 複 数 の 半 導 体 チ ッ プ が 形 成 さ れ た 半 導 体 ウ ェ ハの一部の主面上の状態を拡大して示す上面図である。

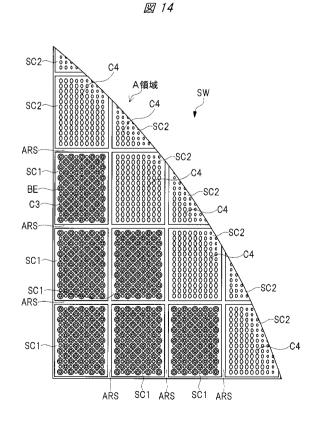

- 【 図 1 4 】 一 実 施 の 形 態 の 第 2 変 形 例 に よ る 複 数 の 半 導 体 チ ッ プ が 形 成 さ れ た 半 導 体 ウ ェ ハの一部の主面上の状態を拡大して示す上面図である。

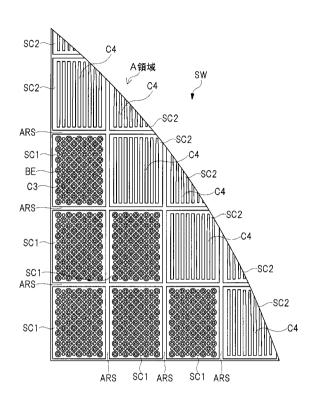

- 【図15】一実施の形態の第3変形例による複数の半導体チップが形成された半導体ウェ ハの一部の主面上の状態を拡大して示す上面図である。

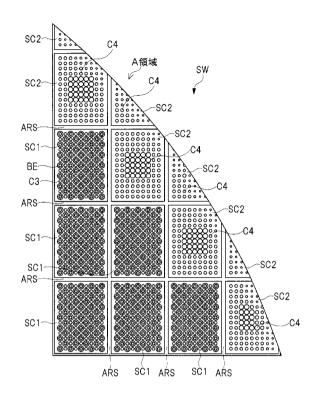

- 【 図 1 6 】 一 実 施 の 形 態 の 第 4 変 形 例 に よ る 複 数 の 半 導 体 チ ッ プ が 形 成 さ れ た 半 導 体 ウ ェ ハの一部の主面上の状態を拡大して示す上面図である。

- 【 図 1 7 】 一 実 施 の 形 態 の 第 5 変 形 例 に よ る 複 数 の 半 導 体 チ ッ プ が 形 成 さ れ た 半 導 体 ウ ェ ハの一部の主面上の状態を拡大して示す上面図である。

【発明を実施するための形態】

[ 0 0 1 1 ]

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実 施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なも 10

20

30

40

のではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

#### [0012]

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

# [0013]

また、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

## [0014]

また、「Aからなる」、「Aよりなる」、「Aを有する」、「Aを含む」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

## [0015]

また、以下の実施の形態を説明するための図面において、各部位の大きさは実デバイスと対応するものではなく、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。また、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。

### [0016]

以下、本実施の形態を図面に基づいて詳細に説明する。

#### [ 0 0 1 7 ]

## (実施の形態)

複数の半導体チップが形成された半導体ウェハ

本実施の形態による複数の半導体チップが形成された半導体ウェハについて、図1~図4を用いて説明する。図1は、本実施の形態による複数の半導体チップが形成された半導体ウェハの主面上の状態を示す上面図である。図2は、図1のA領域を拡大して示す上面図である。図3は、図2のA-A´線に沿った断面図である。図4は、本発明者らが比較検討した複数の半導体チップが形成された半導体ウェハの一部の主面上の状態を拡大して示す上面図である。

#### [0018]

図1および図2に示すように、半導体ウェハSWの主面(第1主面、表面)には、格子状のスクライブ領域(スクライブライン、スペーシング)ARSによって区画された複数の半導体チップSCが形成されている。スクライブ領域ARSの幅は、例えば90~110μm程度である。そして、半導体チップSCには、半導体集積回路装置が形成された製品チップSC1と、半導体ウェハSWの外周領域に半導体ウェハSWの周縁と接して位置し、製品チップSC1にはならない不完全な擬似チップ(図1では、網掛けのハッチングで示す半導体チップSC)SC2とが形成されている。

# [0019]

図3に示すように、製品チップSC1および擬似チップSC2には、半導体集積回路装置の最上層配線からなるボンディングパッドBPが形成されている。ボンディングパッドBPは絶縁膜PSNにより覆われているが、製品チップSC1には、ボンディングパッドBPの上面が露出する第1開口部C1が、第1のピッチで絶縁膜PSNに形成されている。絶縁膜PSNは、例えば窒化シリコン膜、酸化シリコン膜、または窒化シリコン膜と酸化シリコン膜との積層膜からなる。

# [0020]

一方、擬似チップSC2では、ボンディングパッド B P が絶縁膜 P S N によって覆われている。

10

20

30

40

10

20

30

40

50

#### [0021]

さらに、絶縁膜 P S N の上層に感光性ポリイミドからなる第 1 保護膜 R F 1 が形成されている。製品チップ S C 1 には、平面視において第 1 開口部 C 1 と重なる第 2 開口部 C 2 が、第 1 のピッチで第 1 保護膜 R F 1 に形成されている。従って、この第 2 開口部 C 2 が 重なる第 1 開口部 C 1 の底面において、ボンディングパッド B P の上面が露出する。同様に、擬似チップ S C 2 にも、第 2 開口部 C 2 が、第 1 のピッチで第 1 保護膜 R F 1 に形成されている。

# [0022]

但し、擬似チップSC2に形成された第2開口部C2の開口面積は、製品チップSC1に形成された第2開口部C2の開口面積よりも小さくなる場合がある。特に、半導体ウェハSWの周縁に近づくに従って、擬似チップSC2に形成された第2開口部C2の開口面積は小さくなる傾向があり、周縁に最も近い位置にある第2開口部C2の開口面積が最も小さくなる。

# [0023]

さらに、製品チップSC1には、第1開口部C1および第2開口部C2を通じて、電極層(UBM(Under Bump Metal))MLがボンディングパッドBPと電気的に接続されている。電極層MLは、例えば下層をCu(銅)めっき膜からなる第1金属膜CUとし、上層をNi(ニッケル)めっき膜からなる第2金属膜NIとする積層膜からなる。ボンディングパッドBPと電極層MLとの間には、例えば下層をTiN(窒化チタン)からなるバリア層BLとし、上層をCu(銅)からなるシード層SL1とする積層膜が形成されている。

### [0024]

一方、擬似チップSC2には、第2開口部C2は形成されてはいるが、バリア層BL、 シード層SL1および電極層MLは形成されていない。

#### [0025]

さらに、電極層MLの上層に感光性ポリイミドからなる第2保護膜RF2が形成されている。製品チップSC1には、平面視において第2開口部C2と重なる第3開口部C3が、第1のピッチで第2保護膜RF2に形成されている。従って、この第3開口部C3によって、電極層MLの上面が露出する。同様に、擬似チップSC2にも、平面視において第2開口部C2と重なる第3開口部C3が、第1のピッチで第2保護膜RF2に形成されている。従って、この第3開口部C3が重なる第2開口部C2の底面において、絶縁膜PSNが露出する。

### [0026]

但し、擬似チップSC2に形成された第3開口部C3の開口面積は、製品チップSC1に形成された第3開口部C3の開口面積よりも小さくなる場合がある。特に、半導体ウェハSWの周縁に近づくに従って、擬似チップSC2に形成された第3開口部C3の開口面積は小さくなる傾向があり、周縁に最も近い位置にある第3開口部C3の開口面積が最も小さくなる。例えば第3開口部C3が円柱形状であれば、周縁に最も近い位置にある第3開口部C3の径(Lb)は、他の第3開口部C3の径(La)よりも小さくなる。

#### [0027]

また、スクライブ領域ARSでは、第1保護膜RF1および第2保護膜RF2が除去されて、絶縁膜PSNが露出している。

## [0028]

さらに、製品チップSC1には、第3開口部C3を通じて、バンプ電極BEが電極層MLと電気的に接続されている。バンプ電極BEは外部接続用電極であり、例えばPb(鉛)フリー半田などが用いられる。バンプ電極BEの直径は、例えば60~100μm程度である。電極層MLとバンプ電極BEとの間には、例えばAu(金)から成るシード層SL2が形成されている。

## [0029]

一方、擬似チップSC2には、第3開口部C3は形成されているが、シード層SL2お

よびバンプ電極 B E は形成されていない。従って、擬似チップ S C 2 では、第 1 保護膜 R F 1 と第 2 保護膜 R F 2 とが積層された領域と、第 1 保護膜 R F 1 および第 2 保護膜 R F 2 が形成されずに、絶縁膜 P S N が露出した領域とが存在することになる。

### [0030]

後述する半導体装置の製造方法において詳細に説明するが、半導体ウェハSWの裏面(第2主面)を研削する際には、半導体ウェハSWの主面上に保護テープを貼り付ける。保護テープを構成する糊層は感光性ポリイミドからなる第2保護膜RF2との密着力は強いが、絶縁膜PSNとの密着力は弱いという性質を有している。

# [0031]

このため、図4に示すように、半導体ウェハSWの外周の全領域に感光性ポリイミドからなる壁WAを形成した場合は、保護テープと感光性ポリイミドとの密着力が強いため、 保護テープが半導体ウェハSWの主面上から剥がし難いという問題がある。

#### [0032]

しかし、本実施の形態では、半導体ウェハSWの外周領域に位置する擬似チップSC2に、感光性ポリイミドからなる第1保護膜RF1と第2保護膜RF2とが積層された領域と、この積層膜を形成せずに絶縁膜PSNが露出した領域とを設けている。これにより、半導体ウェハSWの外周の全領域に感光性ポリイミドからなる壁WAを形成した場合と比べると、半導体ウェハSWの主面上に貼り付けた保護テープは剥がし易くなる。

#### [0033]

さらに、前述したように、半導体ウェハSWの周縁に近づくに従って、擬似チップSC2に形成された第3開口部C3の開口面積は小さくなる傾向があり、周縁に最も近い位置にある第3開口部C3の開口面積が最も小さくなる。開口面積の小さい第3開口部C3が配置された領域より、保護テープと半導体ウェハSWとの密着性が高くなることから、保護テープを貼り付けた半導体ウェハSWを搬送するときに、半導体ウェハSWの外周部の保護テープの剥がれを防止することができる。一方、保護テープを剥離するときには、密着性が高いのは半導体ウェハSWの外周部のみであるため、保護テープを容易に剥離することができる。

#### [0034]

なお、半導体ウェハSWの外周領域まで、スクライブ領域ARSを形成するため、半導体ウェハSWの裏面を研削する際に供給される研削水が、半導体ウェハSWの主面上に侵入することが懸念される。しかし、後述する半導体装置の製造方法において詳細に説明するが、例えば200μm程度の厚さの柔らかい層を有する保護テープを用いることにより、スクライブ領域ARSの段差にも保護テープを埋め込むことができるので、半導体ウェハSWの主面上への研削水の侵入を防止することができる。

# [0035]

半導体装置の製造方法

本実施の形態による半導体装置の製造方法について、図 5 ~ 図 1 2 を用いて工程順に説明する。図 5 ~ 図 1 2 は、本実施の形態による半導体装置の製造工程を示す断面図である

#### [0036]

図5は、半導体ウェハの製品チップ領域の半導体チップに形成される半導体デバイスおよび多層配線を示す断面図であり、半導体デバイスとしてCMOSFET (Complementary Metal Oxide Semiconductor Field Effect Transistor)を例示する。CMOSFETを構成するpチャネル型MOSFETをpMOSと略し、nチャネル型MOSFETをnMOSと略す。

# [0037]

図6~図10は、半導体デバイスおよび多層配線を省略し、多層配線の最上配線より上層の構造を示す断面図である。図11および図12は、半導体ウェハの主面上への保護テープの貼り付けを説明する断面図である。また、図6~図10に示す符号AR1は、製品チップが形成される製品チップ領域、符号AR2は、擬似チップが形成される擬似チップ

10

20

30

40

10

20

30

40

50

領域、符号ARSは、スクライブ領域である。

## [0038]

まず、図5に示すように、シリコン単結晶からなる半導体ウェハ(円形の薄い板状)SWを準備する。続いて、半導体ウェハSWの素子分離領域に絶縁膜からなる分離部SPを形成した後、半導体ウェハSWにp型の導電性を示す不純物をイオン注入してp型ウェルPWを形成し、同様に、n型の導電性を示す不純物をイオン注入してn型ウェルNWを形成する。

# [0039]

次に、半導体ウェハSWの主面にゲート絶縁膜GIを形成した後、nMOSのゲート電極GEnおよびpMOSのゲート電極GEpを形成し、さらにゲート電極GEn,GEpの側壁にサイドウォールWSを形成する。

[0040]

続いて、ゲート電極GEnの両側のp型ウェルPWにn型の導電性を示す不純物をイオン注入し、nMOSのソース・ドレインとして機能するn型半導体領域SRnをゲート電極GEnおよびサイドウォールWSに対して自己整合的に形成する。同様に、ゲート電極GEpの両側のn型ウェルNWにp型の導電性を示す不純物をイオン注入し、pMOSのソース・ドレインとして機能するp型半導体領域SRpをゲート電極GEpおよびサイドウォールWSに対して自己整合的に形成する。

[0041]

次に、半導体ウェハSWの第1主面上に絶縁膜ILを形成した後、レジストパターンをマスクとしたエッチングにより絶縁膜ILを加工して接続孔CNを形成する。この接続孔CNはn型半導体領域SRp上などの必要部分に形成する。続いて、接続孔CNの内部に、例えばW(タングステン)を主導体とするプラグPLを形成した後、プラグPLに接続する第1層目の配線M1を形成する。第1層目の配線M1は、例えばCu(銅)を主導体とし、例えばシングルダマシン法により形成される。

[0042]

さらに、上層の第2層目の配線M2から第6層目の配線M6を形成する。第6層目の配線M6は、製品チップ領域AR1および擬似チップ領域AR2に形成され、ボンディングパッドBPとして機能する配線層である。

[ 0 0 4 3 ]

第2層目の配線M2から第5層目の配線M5は、例えばCu(銅)を主導体とし、例えばデュエルダマシン法により形成される。第6層目の配線M6は、例えばA1(アルミニウム)を主導体とし、半導体ウェハSW上に堆積されたA1(アルミニウム)膜を、レジストパターンをマスクとしたエッチングにより加工することにより形成される。第6層目の配線M6の厚さは、例えば1μm程度である。なお、本実施の形態では、第6層目の配線M6はA1(アルミニウム)を主導体とするとしたが、Cu(銅)を主導体とすることもできる。また、配線の層数を6層としたが、層数はこれに限定されるものではない。

[0044]

次に、図6に示すように、第6層目の配線M6を覆うように、TEOS(Tetra Ethyl Ortho Silicate; Si(OC $_2$ H $_5$ ) $_4$ )とオゾン(O $_3$ )とをソースガスに用いたプラズマ C V D (Chemical Vapor Deposition)法によりTEOS膜PTを形成する。続いて、TEOS膜PT上にプラズマC V D 法により窒化シリコン膜PNを形成する。これらTEOS膜PTおよび窒化シリコン膜PNは、外部からの水分や不純物の侵入防止および 線の透過の抑制を行う絶縁膜PSNとして機能する。

[0045]

次に、レジストパターンをマスクとしたエッチングにより、窒化シリコン膜 P N および T E O S 膜 P T を順次加工して、製品チップ領域 A R 1 に形成された第 6 層目の配線 M 6 からなるボンディングパッド B P の上面を露出させる第 1 開口部 C 1 を形成する。

[0046]

次に、図7に示すように、半導体ウェハSWの主面上に第1保護膜RF1、例えばポジ

型の感光性ポリイミドを塗布する。続いて、製品チップ領域 A R 1 および擬似チップ領域 A R 2 の第 1 保護膜 R F 1 を露光し、現像することによって、製品チップ領域 A R 1 の半導体チップ毎に、同一のピッチで複数の第 2 開口部 C 2 を第 1 保護膜 R F 1 に形成する。第 2 開口部 C 2 が第 1 開口部 C 1 と重なることにより、第 1 開口部 C 1 の底面にボンディングパッド B P の上面が露出する。

# [0047]

さらに、同工程で、擬似チップ領域AR2の半導体チップ毎に、同一のピッチで複数の第2開口部C2を第1保護膜RF1に形成する。

## [0048]

ここで、製品チップ領域AR1に形成される第2開口部C2と、擬似チップ領域AR2に形成される第2開口部C2とは、同じ露光マスクを用いて形成されることから、製品チップ領域AR1の第2開口部C2のピッチと、擬似チップ領域AR2の第2開口部C2のピッチとは同じになる。

# [0049]

但し、半導体ウェハSWの外周領域では、半導体ウェハSWの厚さが半導体ウェハSWの周縁に向かうに従って漸減するので(前述の図3参照)、露光マスクと半導体ウェハSWの外周領域に塗布された第1絶縁膜RF1の上面との距離が、露光マスクと製品チップ領域AR1に塗布された第1絶縁膜RF1の上面との距離よりも遠くなる。

## [0050]

このため、擬似チップ領域 A R 2 に形成された第 2 開口部 C 2 の開口面積は、製品チップ領域 A R 1 に形成された第 2 開口部 C 2 の開口面積よりも小さくなる。特に、半導体ウェハ S W の周縁に近づくに従って、擬似チップ領域 A R 2 に形成された第 2 開口部 C 2 の開口面積は小さくなる傾向があり、周縁に最も近い位置にある第 2 開口部 C 2 の開口面積が最も小さくなる。

#### [0051]

次に、図8に示すように、第1開口部C1および第2開口部C2の内壁を含む第1保護膜RF1上に、例えばTiN(窒化チタン)からなるバリア層BLを形成した後、CVD法またはスパッタリング法によりバリア層BL上にCu(銅)のシード層SL1を形成する。

# [0052]

次に、製品チップ領域AR1において第2開口部C2に重なり、第2開口部C2より大きめの開口を有するレジストパターン(図示は省略)を形成した後、シード層SL1上に第1金属膜CUを形成する。第1金属膜CUは、例えば電解めっき法により形成されるCu(銅)めっき膜であり、半田の拡散を抑制するバリアメタルとして機能する他に、接触電気抵抗が低い、シート抵抗が低いなどの性質を有し、その厚さは、例えば5μm程度である。さらに、第1金属膜CU上に第2金属膜NIを形成する。第2金属膜NIは、例えば電解めっき法により形成されるNi(ニッケル)めっき膜であり、半田の拡散を抑制するバリアメタルとして機能する他に、半田の濡れ性が良いなどの性質を有し、その厚さは、例えば3μm程度である。

## [0053]

続いて、上記レジストパターンを除去した後、露出しているシード層SL1およびバリア層BLを除去する。これにより、製品チップ領域AR1に、第1開口部C1および第2開口部C2を通じて、ボンディングパッドBPと電気的に接続する、第1金属膜CUと第2金属膜NIとの積層膜からなる電極層MLを形成する。

#### [0054]

次に、図9に示すように、電極層MLを覆うように、半導体ウェハSWの主面上に第2保護膜RF2、例えばポジ型の感光性ポリイミドを塗布する。第1保護膜RF1および第2保護膜RF2の合計の厚さは、例えば8~10μm程度である。続いて、製品チップ領域AR1および擬似チップ領域AR2の第2保護膜RF2を露光し、現像することによって、製品チップ領域AR1の半導体チップ毎に、同一のピッチで複数の第3開口部C3を

10

20

30

40

10

20

30

40

50

第2保護膜RF2に形成する。これにより、第3開口部C3の底面に電極層MLの上面が露出する。

# [0055]

さらに、同工程で、擬似チップ領域AR2の半導体チップ毎に、同一のピッチで複数の第3開口部C3を第2保護膜RF2に形成する。擬似チップ領域AR2では、第3開口部C3が第2開口部C2と重なることにより、第2開口部C2の底面に絶縁膜PSN(窒化シリコン膜PN)が露出する。

## [0056]

さらに、同工程で、スクライブ領域ARSの第1保護膜RF1および第2保護膜RF2を除去することにより、スクライブ領域ARSの絶縁膜PSN(窒化シリコン膜PN)が露出する。

#### [0057]

ここで、製品チップ領域AR1に形成される第3開口部C3と、擬似チップ領域AR2に形成される第3開口部C3とは、同じ露光マスクを用いて形成されることから、製品チップ領域AR1の第3開口部C3のピッチと、擬似チップ領域AR2の第3開口部C3のピッチとは同じになる。

## [0058]

但し、前述の第2開口部C2と同様に、半導体ウェハSWの外周領域では、半導体ウェハSWの厚さが半導体ウェハSWの周縁に向かうに従って漸減するので(前述の図3参照)、露光マスクと半導体ウェハSWの外周領域に塗布された第2絶縁膜RF2の上面との距離が、露光マスクと製品チップ領域AR1に塗布された第2絶縁膜RF2の上面との距離よりも遠くなる。

## [0059]

このため、擬似チップ領域 A R 2 に形成された第 3 開口部 C 3 の開口面積は、製品チップ領域 A R 1 に形成された第 3 開口部 C 3 の開口面積よりも小さくなる。特に、半導体ウェハ S W の周縁に近づくに従って、擬似チップ領域 A R 2 に形成された第 3 開口部 C 3 の開口面積は小さくなる傾向があり、周縁に最も近い位置にある第 3 開口部 C 3 の開口面積が最も小さくなる。

# [0060]

次に、図10に示すように、露出した電極層ML上にAu(金)のシード層SL2を形成した後、電極層ML上にシード層SL2を介してバンプ電極BEを形成する。バンプ電極BEは外部接続用電極であり、例えばPb(鉛)フリー半田などが用いられる。バンプ電極BEの直径は、例えば60~100μm程度である。

# [0061]

バンプ電極BEは、例えば印刷法、めっき法またはボール法などにより形成することができる。印刷法では、電極層ML上にシード層SL2を介して半田ペーストをマスク印刷した後、リフロー処理により半田ペーストを球形に成形して、電極層MLと電気的に接続させる。めっき法では、電極層ML上にシード層SL2を介してめっきにより半田層を形成した後、フラックスを塗布し、続いてリフロー処理およびフラックス残渣の除去洗浄により半田層を球形に成形して、電極層MLと電気的に接続させる。ボール法では、電極層ML上にフラックスをマスク印刷した後、フラックス上に半田ボールを搭載し、続いてリフロー処理およびフラックス残渣の除去洗浄により半田ボールを電極層MLと電気的に接続させる。

# [0062]

次に、図11に示すように、半導体ウェハSWの裏面を研削する際に、複数のバンプ電極BEを覆うように半導体ウェハSWの主面上に貼り付ける保護テープPRを準備する。保護テープPRは、ベース層PR1と、糊層PR3と、ベース層PR1と糊層PR3との間に設けられた中間層PR2とから構成される。中間層PR2および糊層PR3は、ベース層PR1よりも柔らかく、バンプ電極BEを包み込み、半導体ウェハSWの主面上の段差への埋め込み性がよい。ベース層PR1の厚さは、例えば120μm程度であり、中間

# [0063]

また、糊層 P R 3 の粘着力は、例えば 9 . 8 N / 2 5 m m 程度であり、糊層 P R 3 は、感光性ポリイミドからなる第 2 保護膜 R F 2 との密着力は強いが、酸化シリコンまたは窒化シリコンからなる絶縁膜 P S N との密着力は弱いという性質を有している。

#### [0064]

次に、図12に示すように、半導体ウェハSWの主面上に保護テープPRを貼り付ける。中間層PR2および糊層PR3は、半導体ウェハSWの主面上の段差への埋め込み性が良いことから、バンプ電極BEを中間層PR2および糊層PR3によって包み込むことができる。さらに、擬似チップ領域AR2の第1保護膜RF1に形成された第2開口部C2および第2保護膜RF2に形成された第3開口部C3の内部、並びにスクライブ領域ARSを中間層PR2および糊層PR3によって埋め込むことができる。

# [0065]

次に、半導体ウェハSWに研削水を供給しながら、半導体ウェハSWの裏面を研削する。前述したように、擬似チップ領域AR2の第1保護膜RF1に形成された第2開口部C2および第2保護膜RF2に形成された第3開口部C3の内部、並びにスクライブ領域ARSを保護テープPRによって埋め込むことができるので、製品チップ領域AR1への研削水の侵入を防止することができる。

# [0066]

次に、半導体ウェハSWの主面上から保護テープPRを剥がす。前述したように、糊層PR3は、感光性ポリイミドからなる第2保護膜RF2との密着力は強いが、酸化シリコンまたは窒化シリコンからなる絶縁膜PSNとの密着力は弱いという性質を有している。従って、本実施の形態では、擬似チップ領域AR2の全領域に第2保護膜RF2を形成せず、一部領域に絶縁膜PSNの露出面を形成したことにより、半導体ウェハSWの外周領域に感光性ポリイミドからなる壁を形成した場合(前述の図4参照)に比べて、半導体ウェハSWの主面上に貼り付けた保護テープPRは剥がし易くなる。

#### [0067]

その後、スクライブ領域ARSを切断して、半導体ウェハSWから半導体チップに個々に切り分けられ、半導体装置が完成するが、その説明は省略する。

### [0068]

变形例

本実施の形態の変形例による複数の半導体チップが形成された半導体ウェハについて図13~図16を用いて説明する。図13、図14、図15および図16はそれぞれ、本実施の形態の第1、第2、第3および第4変形例による複数の半導体チップが形成された半導体ウェハの一部の主面上の状態を拡大して示す上面図である。

# [0069]

前述の図2に示した擬似チップSC2では、第1保護膜RF1および第2保護膜RF2にそれぞれ形成された第2開口部C2および第3開口部C3の平面視における形状を円形状としたが、これに限定されるものではない。

# [ 0 0 7 0 ]

例えば図13に示す第1変形例のように、擬似チップSC2の第1保護膜および第2保護膜に形成される複数の第4開口部C4の平面視における形状は四角形状であってもよい

## [0071]

また、例えば図14に示す第2変形例のように、擬似チップSC2の第1保護膜および第2保護膜に形成される複数の第4開口部C4の平面視における形状は楕円形状であってもよい。

## [0072]

また、例えば図15に示す第3変形例のように、擬似チップSC2の第1保護膜および

20

10

30

40

第 2 保護膜に形成される複数の第 4 開口部 C 4 の平面視における形状はストライプ形状であってもよい。

# [0073]

また、例えば図16に示す第4変形例のように、擬似チップSC2の第1保護膜および第2保護膜に形成される複数の第4開口部C4の平面視における形状は互いに直径の異なる円形状であってもよい。なお、図16に示す第4変形例では、擬似チップSC2の中央領域に位置する第4開口部C4の径を他の領域に位置する第4開口部C4の径よりも大きくしたが、これに限定されるものではない。例えば中央部に第1径の第4開口部を配置し、その外側に第1径の第4開口部を配置し、さらに、その外側に第1径の第4開口部を配置し、さらに、その外側に第1

[0074]

第4開口部C4の底面には、窒化シリコン、酸化シリコン、または窒化シリコンと酸化シリコンとの積層膜からなる絶縁膜が露出している。

### [0075]

前述したように、感光性ポリイミドと保護テープとの接着力は強いが、窒化シリコンまたは酸化シリコンからなる絶縁膜と保護テープとの接着力は弱い。従って、所望する絶縁膜の露出面積が得られることができれば、第4開口部C4の平面視における形状は、いかなる形状であってもよい。

[0076]

また、前述の図2に示した擬似チップSC2では、第1保護膜RF1に第2開口部C2を形成する露光、現像と、第2保護膜RF2に第3開口部C3を形成する露光、現像とを互いに異なる工程において行ったが、第1、第2、第3および第4変形例では、一度の露光、現像により、擬似チップSC2の第1保護膜と第2保護膜との積層膜に第4開口部C4を形成することができる。

[0077]

なお、第1、第2、第3および第4変形例では、製品チップ領域SC1の第2保護膜に第3開口部C3を形成する際に用いる露光マスクと、擬似チップ領域SC2の第1保護膜および第2保護膜に第4開口部C4を形成する際に用いる露光マスクの2枚の露光マスクが必要となる。しかし、露光マスクを別々とすることによって、擬似チップ領域SC2に形成される第4開口部C4の数および形状などを、製品チップ領域SC1に形成される第3開口部C3の数および形状などに係わらず、任意に決めることができるので、保護テープの接着力および剥がし易さの調整がより容易となる。

[0078]

本実施の形態の他の変形例による複数の半導体チップが形成された半導体ウェハについて図 1 7 を用いて説明する。図 1 7 は、本実施の形態の第 5 変形例による複数の半導体チップが形成された半導体ウェハの一部の主面上の状態を拡大して示す上面図である。

[0079]

前述の図1に示した半導体ウェハSWでは、半導体ウェハSWの外周領域に、製品チップSC1にはならない不完全な擬似チップSC2を形成した。

[ 0 0 8 0 ]

第5変形例では、図17に示すように、擬似チップSC2が形成されておらず、半導体ウェハSWの外周領域に第1保護膜と第2保護膜との積層膜からなる壁WAが形成されている。壁WAはの幅(W)は、例えば半導体ウェハSWの周縁から2mm程度である。そして、この外周領域に形成された壁WAを構成する第1保護膜および第2保護膜にそれぞれ、第5開口部C5が形成されている。

[0081]

第 5 開口部 C 5 の底面に、窒化シリコン、酸化シリコン、または窒化シリコンと酸化シリコンとの積層膜からなる絶縁膜が露出している。

[0082]

10

20

30

40

前述したように、感光性ポリイミドと保護テープとの密着力は強いが、窒化シリコンまたは酸化シリコンからなる絶縁膜と保護テープとの密着力は弱い。従って、半導体ウェハSWの外周領域に、複数の第5開口部を有する感光性ポリイミドからなる壁WAを形成することにより、感光性ポリイミドと保護テープとの貼り付けの強さを弱くすることができるので、半導体ウェハSWの主面上から保護テープを剥がし易くなる。

#### [0083]

また、前述の図2に示した擬似チップSC2では、第1保護膜RF1に第2開口部C2を形成する露光、現像と、第2保護膜RF2に第3開口部C3を形成する露光、現像とを互いに異なる工程において行ったが、第5変形例では、一度の露光、現像により、壁WAを構成する第1保護膜と第2保護膜との積層膜に第5開口部C5を形成することができる

10

20

### [0084]

なお、第5変形例では、製品チップ領域SC1の第2保護膜に第3開口部C3を形成する際に用いる露光マスクと、外周領域の第1保護膜および第2保護膜に第5開口部C5を形成する際に用いる露光マスクの2枚の露光マスクが必要となる。しかし、露光マスクを別々とすることによって、外周領域に形成される第5開口部C5の数および形状などを、製品チップ領域SC1に形成される第3開口部C3の数および形状などに係わらず、任意に決めることができるので、保護テープの接着力および剥がし易さの調整がより容易となる。

# [0085]

このように、本実施の形態によれば、半導体ウェハSWの裏面を研削する際に、半導体ウェハSWの主面上に貼り付けられる保護テープPRの剥離が容易となるので、半導体装置の製造歩留りを向上することができる。

#### [0086]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

## 【符号の説明】

## [0087]

- AR1 製品チップ領域

- AR2 擬似チップ領域

- ARS スクライブ領域(スクライブライン、スペーシング)

- BE バンプ電極

- BL バリア層

- BP ボンディングパッド

- C 1 第 1 開 口 部

- C 2 第 2 開 口 部

- C 3 第 3 開 口 部

- C 4 第4開口部

- C 5 第 5 開 口 部

- CN 接続孔

- C U 第 1 金 属 膜

- GEn,GEp ゲート電極

- G I ゲート絶縁膜

- IL 絶縁膜

- M 1 , M 2 , M 3 , M 4 , M 5 , M 6 配線

- M L 電極層

- NI 第2金属膜

- NW n型ウェル

- PL プラグ

30

50

PN 窒化シリコン膜

PR 保護テープ

P R 1 ベース層

P R 2 中間層

P R 3 糊層

PSN 絶縁膜

PTTEOS膜

PW p型ウェル

R F 1 第 1 保 護 膜

R F 2 第 2 保 護 膜

SC 半導体チップ

SC1 製品チップ

SC2 擬似チップ

S L 1 , S L 2 シード層

SP 分離部

SRn n型半導体領域

S R p p型半導体領域

SW 半導体ウェハ

W A 壁

WS サイドウォール

20

10

# 【図1】

# **2** 1

# 【図2】

【図5】

【図7】

【図9】 【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

図 15

図 16

【図17】

図 17

#### 【手続補正書】

【提出日】平成29年2月10日(2017.2.10)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

以下の工程を含む半導体装置の製造方法:

- (a)主面と、前記主面を取り囲む周縁と、前記主面に形成された半導体素子を備える複数の第1チップと、複数の前記第1チップを取り囲み、前記周縁に接する複数の第2チップと、を有し、複数の前記第1チップのそれぞれに複数のボンディングパッドが形成された半導体ウェハを準備する工程;

- (b)前記主面上に絶縁膜を形成する工程:

- (c)前記第1チップの前記絶縁膜に、複数の第1開口部を形成して、前記第1開口部の底面に前記ボンディングパッドを露出させる工程;

- (d) 前記主面上に第1保護膜を形成する工程;

- (e)前記第1チップおよび前記第2チップの前記第1保護膜に、複数の第2開口部を それぞれ形成して、前記第1チップでは、平面視において前記第2開口部と重なる前記第 1開口部の底面に前記ボンディングパッドを露出させ、前記第2チップでは、前記第2開 口部の底面に前記絶縁膜を露出させる工程;

- (f)前記第1開口部および前記第2開口部を介して、複数の前記ボンディングパッドとそれぞれ電気的に接続する複数の電極層を形成する工程;

- ( g ) 前記主面上に第2保護膜を形成する工程;

- (h)前記第1チップおよび前記第2チップの前記第2保護膜に、複数の第3開口部を それぞれ形成して、前記第1チップでは、前記第3開口部の底面に前記電極層を露出させ 、前記第2チップでは、平面視において前記第3開口部と重なる前記第2開口部の底面に 前記絶縁膜を露出させる工程;

- (i)複数の前記電極層とそれぞれ電気的に接続する複数の外部電極を形成する工程;

- ( j ) 前記主面上に、複数の前記外部電極を覆う保護テープを貼り付ける工程。

# 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第2チップの前記周縁に最も近い位置にある前記第3開口部の開口面積は、前記第1チップの前記第3開口部の開口面積よりも小さい、半導体装置の製造方法。

#### 【請求項3】

請求項1記載の半導体装置の製造方法において、

前記第2チップの前記第3開口部のピッチは、前記第1チップの前記第3開口部のピッチと同じである、半導体装置の製造方法。

# 【請求項4】

請求項1記載の半導体装置の製造方法において、

前記第2チップには、前記外部電極を形成しない、半導体装置の製造方法。

## 【請求項5】

請求項1記載の半導体装置の製造方法において、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、前記スクライブ領域には、前記第1保護膜および前記第2保護膜は形成されていない、半導体装置の製造方法。

## 【請求項6】

以下の工程を含む半導体装置の製造方法:

- (a)主面と、前記主面を取り囲む周縁と、前記主面に形成された半導体素子を備える複数の第1チップと、複数の前記第1チップを取り囲み、前記周縁に接する複数の第2チップと、を有し、複数の前記第1チップのそれぞれに複数のボンディングパッドが形成された半導体ウェハを準備する工程;

- (b)前記主面上に絶縁膜を形成する工程;

- (c)前記第1チップの前記絶縁膜に、複数の第1開口部を形成して、前記第1開口部の底面に前記ボンディングパッドを露出させる工程;

- ( d ) 前記主面上に第1保護膜を形成する工程;

- (e)前記第1チップの前記第1保護膜に、複数の第2開口部を形成して、平面視において前記第2開口部と重なる前記第1開口部の底面に前記ボンディングパッドを露出させる工程:

- (f)前記第1開口部および前記第2開口部を介して、複数の前記ボンディングパッドとそれぞれ電気的に接続する複数の電極層を形成する工程;

- ( g ) 前記主面上に第2保護膜を形成する工程;

- (h)前記第1チップの前記第2保護膜に、複数の第3開口部を形成して、前記第3開口部の底面に前記電極層を露出させ、前記第2チップの前記第1保護膜および前記第2保護膜に、複数の第4開口部を形成して、前記第4開口部の底面に前記絶縁膜を露出させる工程;

- ( i ) 複数の前記電極層とそれぞれ電気的に接続する複数の外部電極を形成する工程;

- ( j )前記主面上に、複数の前記外部電極を覆う保護テープを貼り付ける工程。

#### 【請求項7】

請求項6記載の半導体装置の製造方法において、

前記第4開口部の平面視における形状は、円形状、楕円形状、四角形状またはストライプ形状である、半導体装置の製造方法。

# 【請求項8】

請求項6記載の半導体装置の製造方法において、

前記第2チップには、前記外部電極を形成しない、半導体装置の製造方法。

# 【請求項9】

請求項6記載の半導体装置の製造方法において、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、前記スクライブ領域には、前記第1保護膜および前記第2保護膜は形成されていない、 半導体装置の製造方法。

# 【請求項10】

主面と、

前記主面を取り囲む周縁と、

前記主面に形成された半導体素子を備える複数の第1チップと、

複数の前記第1チップを取り囲み、前記周縁に接する複数の第2チップと、

複数の前記第1チップにそれぞれ形成された複数のボンディングパッドと、

前記複数のボンディングパッドを覆い、前記主面上に形成された絶縁膜と、

前記第1チップの前記絶縁膜に形成され、前記複数のボンディングパッドの上面の一部をそれぞれ露出する複数の第1開口部と、

前記絶縁膜上に形成された第1保護膜と、

前記第1チップの前記第1保護膜に形成され、平面視において複数の前記第1開口部と それぞれ重なり、前記複数のボンディングパッドの上面の一部をそれぞれ露出する複数の 第2開口部と、

前記第2チップの前記第1保護膜に形成され、前記絶縁膜を露出する複数の第3開口部と、

前記第1開口部および前記第2開口部を介して、前記複数のボンディングパッドとそれぞれ電気的に接続する複数の電極層と、

前記複数の電極層を覆い、前記主面上に形成された第2保護膜と、

前記第1チップの前記第2保護膜に形成され、前記複数の電極層の上面の一部をそれぞれ露出する複数の第4開口部と、

前記第2チップの前記第2保護膜に形成され、平面視において複数の前記第3開口部とそれぞれ重なり、前記絶縁膜を露出する複数の第5開口部と、

前記第4開口部を介して、前記複数の電極層とそれぞれ電気的に接続する複数の外部電極と、

複数の前記外部電極を覆い、前記主面上に貼り付けられた保護テープと、

を有する、半導体ウェハ。

#### 【請求項11】

請求項10記載の半導体ウェハにおいて、

前記第2チップの前記周<u>縁に</u>最も近い位置にある前記第5開口部の開口面積は、前記第1チップの前記第4開口部の開口面積よりも小さい、半導体ウェハ。

# 【請求項12】

請求項10記載の半導体ウェハにおいて、

前記第2チップの前記第5開口部のピッチと、前記第1チップの前記第4開口部のピッチとは同じである、半導体ウェハ。

#### 【請求項13】

請求項10記載の半導体ウェハにおいて、

前記第5開口部の平面視における形状は、円形状、楕円形状、四角形状またはストライプ形状である、半導体ウェハ。

#### 【請求項14】

請求項10記載の半導体ウェハにおいて、

前記第2チップには、前記外部電極を有しない、半導体ウェハ。

#### 【請求項15】

請求項10記載の半導体ウェハにおいて、

前記第2チップでは、前記保護テープは、前記第1保護膜、前記第2保護膜および複数の前記第3開口部の底面にそれぞれ露出する前記絶縁膜と接する、半導体ウェハ。

## 【請求項16】

請求項10記載の半導体ウェハにおいて、

互いに隣り合う前記第1チップ間、互いに隣り合う前記第2チップ間および互いに隣り合う前記第1チップと前記第2チップとの間は、スクライブ領域により隔てられており、前記スクライブ領域では、前記第1保護膜および前記第2保護膜が形成されておらず、

前記保護テープとは、前記絶縁膜と接する、半導体ウェハ。

## 【請求項17】

請求項10記載の半導体ウェハにおいて、

前記保護テープと前記絶縁膜との接着力が、前記保護テープと前記第1保護膜および前記第2保護膜との接着力よりも弱い、半導ウェハ。

## 【請求項18】

請求項10記載の半導体ウェハにおいて、

前記保護テープは、糊層と、ベース層と、前記糊層と前記ベース層との間に設けられた中間層とから構成され、

前記糊層および前記中間層は、前記ベース層よりも柔らかく、

前記糊層と前記中間層の合計の厚さが、前記外部電極の高さよりも厚い、半導体ウェハ

# 【請求項19】

請求項10記載の半導体ウェハにおいて、

前記絶縁膜は、窒化シリコン膜、酸化シリコン膜、または窒化シリコン膜と酸化シリコン膜との積層膜であり、前記第 1 保護膜および前記第 2 保護膜はポリイミド膜である、半導体ウェハ。

## 【請求項20】

請求項10記載の半導体ウェハにおいて、

平面視における前記第3開口部の開口面積と、前記第5開口部の開口面積とが同じである、半導体ウェハ。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0043

【補正方法】変更

【補正の内容】

[0043]

第2層目の配線M2から第5層目の配線M5は、例えばCu(銅)を主導体とし、例えばデュアルダマシン法により形成される。第6層目の配線M6は、例えばA1(アルミニウム)を主導体とし、半導体ウェハSW上に堆積されたA1(アルミニウム)膜を、レジストパターンをマスクとしたエッチングにより加工することにより形成される。第6層目の配線M6の厚さは、例えば1 $\mu$ m程度である。なお、本実施の形態では、第6層目の配線M6はA1(アルミニウム)を主導体とするとしたが、Cu(銅)を主導体とすることもできる。また、配線の層数を6層としたが、層数はこれに限定されるものではない。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0049

【補正方法】変更

【補正の内容】

[0049]

但し、半導体ウェハSWの外周領域では、半導体ウェハSWの厚さが半導体ウェハSWの周縁に向かうに従って漸減するので(前述の図3参照)、露光マスクと半導体ウェハSWの外周領域に塗布された第1<u>保護膜</u>RF1の上面との距離が、露光マスクと製品チップ領域AR1に塗布された第1保護膜RF1の上面との距離よりも遠くなる。

【 手 続 補 正 4 】

【補正対象書類名】明細書

【補正対象項目名】0058

【補正方法】変更

【補正の内容】

[0058]

但し、前述の第2開口部C2と同様に、半導体ウェハSWの外周領域では、半導体ウェハSWの厚さが半導体ウェハSWの周縁に向かうに従って漸減するので(前述の図3参照)、露光マスクと半導体ウェハSWの外周領域に塗布された第2<u>保護膜RF2の上面との距離が、露光マスクと製品チップ領域AR1に塗布された第2保護膜RF2の上面との距離よりも遠くなる。</u>

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0077

【補正方法】変更

【補正の内容】

[0077]

なお、第1、第2、第3および第4変形例では、製品チップ領域<u>AR1</u>の第2保護膜に第3開口部C3を形成する際に用いる露光マスクと、擬似チップ領域<u>AR2</u>の第1保護膜および第2保護膜に第4開口部C4を形成する際に用いる露光マスクの2枚の露光マスクが必要となる。しかし、露光マスクを別々とすることによって、擬似チップ領域<u>AR2</u>に形成される第4開口部C4の数および形状などを、製品チップ領域<u>AR1</u>に形成される第3開口部C3の数および形状などに係わらず、任意に決めることができるので、保護テー

プの接着力および剥がし易さの調整がより容易となる。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0084

【補正方法】変更

【補正の内容】

[0084]

なお、第5変形例では、製品チップ領域<u>AR1</u>の第2保護膜に第3開口部C3を形成する際に用いる露光マスクと、外周領域の第1保護膜および第2保護膜に第5開口部C5を形成する際に用いる露光マスクの2枚の露光マスクが必要となる。しかし、露光マスクを別々とすることによって、外周領域に形成される第5開口部C5の数および形状などを、製品チップ領域<u>AR1</u>に形成される第3開口部C3の数および形状などに係わらず、任意に決めることができるので、保護テープの接着力および剥がし易さの調整がより容易となる。

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 21/683 (2006.01)

(72)発明者 大浦 雄大

群馬県高崎市西横手町 1 1 1 ルネサスセミコンダクタパッケージ&テストソリューションズ株式 会社内

(72)発明者 吉田 宏平

群馬県高崎市西横手町 1 1 1 ルネサスセミコンダクタパッケージ&テストソリューションズ株式会社内

Fターム(参考) 5F033 HH07 HH08 HH11 HH13 HH33 JJ01 JJ11 JJ19 JJ33 KK01

KK11 MM01 MM02 MM13 NN06 NN07 PP06 PP15 PP27 PP28 QQ01 QQ47 RR04 RR06 RR22 RR27 SS04 SS15 SS21 TT04

VV07 XX00

5F057 AA11 AA21 BA21 BB03 CA14 DA11 EC05 FA28

5F131 AA02 AA04 BA33 BA53 CA15 CA49 DA14 EA06 EA07 EC34

EC62 EC73