(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3884810号

(P3884810)

(45) 発行日 平成19年2月21日(2007.2.21)

(24) 登録日 平成18年11月24日(2006.11.24)

(51) Int.C1.

F 1

G 1 1 C 16/06 (2006.01)

G 1 1 C 17/00 6 3 2 A

請求項の数 10 (全 15 頁)

(21) 出願番号 特願平9-8542

(22) 出願日 平成9年1月21日(1997.1.21)

(65) 公開番号 特開平10-208489

(43) 公開日 平成10年8月7日(1998.8.7)

審査請求日 平成16年1月19日(2004.1.19)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】高電圧発生装置

## (57) 【特許請求の範囲】

## 【請求項1】

電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、

前記負荷の大きさを見積もる負荷見積り手段と、

前記負荷見積り手段によって見積もられた前記負荷の大きさに応じて前記高電圧生成手段の昇圧能力を制御する昇圧能力制御手段とを備え、

前記負荷見積り手段は、

前記高電圧生成手段が起動した後で予め設定された所定時間経過後にサンプル信号を出力するタイマと、

前記サンプル信号を受取ったときの前記高電圧生成手段の出力電圧の大きさを検知する電圧検知手段とを含む、高電圧発生装置。 10

## 【請求項2】

電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、

前記負荷の大きさを見積もる負荷見積り手段と、

前記負荷見積り手段によって見積もられた前記負荷の大きさに応じて前記高電圧生成手段の昇圧能力を制御する昇圧能力制御手段とを備え、

前記負荷見積り手段は、

前記高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、

前記高電圧生成手段が起動した後前記出力電圧検出手段で予め設定された所定電圧に到達したことが検出されるまでの時間を測るカウント手段とを含む、高電圧発生装置。 20

**【請求項 3】**

前記昇圧能力制御手段は、電源から前記高電圧生成手段に供給される電流の大きさを変化させる、請求項 1 または請求項 2 に記載の高電圧発生装置。

**【請求項 4】**

前記昇圧能力制御手段は、前記電源と前記高電圧生成手段が前記電源から前記電源電圧を受けるためのノードとの間に並列に接続され、前記負荷見積り手段によって制御される複数のトランジスタを含む、請求項 3 に記載の高電圧発生装置。

**【請求項 5】**

前記昇圧能力制御手段は、前記高電圧生成手段から出力される電流の大きさを変化させる、請求項 1 または請求項 2 に記載の高電圧発生装置。 10

**【請求項 6】**

前記昇圧能力制御手段は、接地ノードと前記高電圧生成手段の出力ノードとの間に並列に接続され、前記負荷見積り手段によって制御される複数のトランジスタを含む、請求項 5 に記載の高電圧発生装置。

**【請求項 7】**

電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、前記高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、

前記出力電圧検出手段によって検出された出力電圧の大きさに応じて前記高電圧生成手段の昇圧能力を制御する昇圧能力制御手段と、

前記出力電圧検出手段における検出結果に基づき生成されるアナログ信号を、前記高電圧生成手段に与えられるクロック信号が活性化するたびに更新して、前記アナログ信号を前記昇圧能力制御手段に与えるフィルタ回路とを備え、 20

前記昇圧能力制御手段は、前記アナログ信号に応じて、電源から前記高電圧生成手段に供給される電流の大きさをアナログ的に変化させる、高電圧発生装置。

**【請求項 8】**

電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、前記高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、

前記出力電圧検出手段によって検出された出力電圧の大きさに応じて前記高電圧生成手段の昇圧能力を制御する昇圧能力制御手段と、

前記出力電圧検出手段における検出結果に基づき生成されるアナログ信号を、前記高電圧生成手段に与えられるクロック信号が活性化するたびに更新して、前記アナログ信号を前記昇圧能力制御手段に与えるフィルタ回路とを備え、 30

前記昇圧能力制御手段は、前記アナログ信号に応じて、前記高電圧生成手段から出力される電流の大きさをアナログ的に変化させる、高電圧発生装置。

**【請求項 9】**

前記出力電圧検出手段は、

前記高電圧生成手段の出力電圧と第 1 の基準電圧とを比較し第 1 の信号を生成する第 1 の出力電圧検出手段と、

前記高電圧生成手段の出力電圧と前記第 1 の基準電圧より小さい第 2 の基準信号とを比較し第 2 の信号を生成する第 2 の出力電圧検出手段とを含み、 40

前記フィルタ回路は、前記第 1 の信号および前記第 2 の信号に基づいて前記アナログ信号を生成する、請求項 7 または請求項 8 に記載の高電圧発生回路。

**【請求項 10】**

前記フィルタ回路は、

前記第 1 の信号を受ける第 1 の入力部と、

前記第 2 の信号を受ける第 2 の入力部と、

前記昇圧能力制御手段と接続されるノードとを含み、

前記フィルタ回路は、前記第 1 の信号および前記第 2 の信号に基づき前記ノードの電圧レベルをアナログ的に変動させることにより前記アナログ信号を生成する、請求項 9 に記載の高電圧発生回路。 50

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体記憶装置に関し、特にチャージポンプ技術を利用して高電圧を発生させる高電圧発生装置に関するものである。

**【0002】****【従来の技術】**

図11は、従来の高電圧発生装置の構成を示す図である。図11に示されるように、この高電圧発生装置は、負荷9に接続され、チャージポンプ1と、オシレータ3と、チャージポンプ制御回路5と、検出回路7とを備える。

10

**【0003】**

ここで、チャージポンプ1は、オシレータ3から発生するクロックパルス $/$ を受け、高電圧VPPを発生させる。具体的には、たとえば、クロックパルス $/$ がハイ(H)レベルのときに、ノードN0からノードN1、ノードN2からノードN3、ノードN4からノードN5へ電流が流れ、ノードN(2m)がノードN(2m+1)より約しきい値電圧分高い電位になる。

**【0004】**

次に、クロックパルス $/$ がロー(L)レベルに下がると、ノードN0からノードN5は、キャパシタンスカップリングにより下がろうとするが、左側から電流が供給されて、前にクロックパルス $/$ がLレベルであったときより電位が上がる。すなわちこのとき、クロックパルス $/$ はHレベルになり、ノードN1からノードN2、ノードN3からノードN4へ電流が供給される。

20

**【0005】**

そして、クロックパルス $/$ がLレベルに戻ると、再びノードN0からノードN1、ノードN2からノードN3、ノードN4からノードN5へ電流が供給され、それぞれノードN1、N3、N5の電位が前のサイクルより上昇する。このようにして、左から右へ電流が流れ、容量C1、C2、…などのカップリング比を $/$ 、クロックの振幅をVoscとし、しきい値電圧をV<sub>TN</sub>とすると、1段当たりおよそV<sub>osc</sub>-V<sub>TN</sub>上昇することになる。

**【0006】**

また、検出回路7は、チャージポンプ1の出力電圧VPPを検出する。

30

具体的には、出力電圧VPPを抵抗R1と抵抗R2で抵抗分割し、中間ノードの電位をV<sub>dev</sub>とする。そして、比較器71で電位V<sub>dev</sub>と基準電圧V<sub>ref</sub>とを比較し、電位V<sub>dev</sub>>基準電圧V<sub>ref</sub>のときHレベルの検出信号V<sub>det</sub>を出力し電位V<sub>dev</sub><基準電圧V<sub>ref</sub>のときLレベルの検出信号V<sub>det</sub>を出力する。

**【0007】**

なお、ここでチャージポンプ1の出力電圧VPPの所望値は、(R1+R2)·V<sub>ref</sub>/R2である。

**【0008】**

次に、チャージポンプ制御回路5は、検出回路7からのHレベルの検出信号を受けてオシレータ3を停止状態にし、検出回路7からのLレベルの検出信号を受けてオシレータ3を動作状態にする。

40

**【0009】****【発明が解決しようとする課題】**

たとえばフラッシュメモリにおいては、チャージポンプで発生した高電圧を直接メモリセルに印加するモードがある。ここで高電圧を印加するメモリセルの数は書き込みパターンや消去パターンによって変化する。したがって、チャージポンプの負荷がパターンによって異なる。ここで、チャージポンプの性能はあらゆる動作モードの中で負荷が最も重くなる場合に対して十分なパフォーマンスが得られるように決定しなければならない。

**【0010】**

しかしながら、上記のように動作モードによっては負荷が非常に軽くなる場合がある。こ

50

の場合オーバーパワーとなり、リップル現象が顕著になるという問題が起きる。

【0011】

本発明は、このような問題を解消するためになされたもので、負荷の大きさに応じて昇圧能力を変化させることができる高電圧発生装置を提供することを目的とする。

【0012】

【課題を解決するための手段】

請求項1に係る高電圧発生装置は、電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、負荷の大きさを見積もる負荷見積り手段と、負荷見積り手段によって見積もられた負荷の大きさに応じて高電圧生成手段の昇圧能力を制御する昇圧能力制御手段とを備え、負荷見積り手段は、高電圧生成手段が起動した後で予め設定された所定時間経過後にサンプル信号を出力するタイマと、サンプル信号を受取ったときの高電圧生成手段の出力電圧の大きさを検知する電圧検知手段とを含む。10

【0013】

請求項2に係る高電圧発生装置は、電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、負荷の大きさを見積もる負荷見積り手段と、負荷見積り手段によって見積もられた負荷の大きさに応じて高電圧生成手段の昇圧能力を制御する昇圧能力制御手段とを備え、負荷見積り手段は、高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、高電圧生成手段が起動した後出力電圧検出手段で予め設定された所定電圧に到達したことが検出されるまでの時間を測るカウント手段とを含む。

【0015】

請求項3に係る高電圧発生装置は、請求項1または請求項2に記載の高電圧発生装置であって、昇圧能力制御手段は、電源から高電圧生成手段に供給される電流の大きさを変化させる。

【0016】

請求項4に係る高電圧発生装置は、請求項3に記載の高電圧発生装置であって、昇圧能力制御手段は、電源と高電圧生成手段が電源から電源電圧を受けるためのノードとの間に並列に接続され、負荷見積り手段によって制御される複数のトランジスタを含む。

【0017】

請求項5に係る高電圧発生装置は、請求項1または請求項2に記載の高電圧発生装置であって、昇圧能力制御手段は、高電圧生成手段から出力される電流の大きさを変化させる。30

【0018】

請求項6に係る高電圧発生装置は、請求項5に記載の高電圧発生装置であって、昇圧能力制御手段は、接地ノードと高電圧生成手段の出力ノードとの間に並列に接続され、負荷見積り手段によって制御される複数のトランジスタを含む。

【0019】

請求項7に係る高電圧発生装置は、電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、出力電圧検出手段によって検出された出力電圧の大きさに応じて高電圧生成手段の昇圧能力を制御する昇圧能力制御手段と、出力電圧検出手段における検出結果に基づき生成されるアナログ信号を、高電圧生成手段に与えられるクロック信号が活性化するたびに更新して、アナログ信号を昇圧能力制御手段に与えるフィルタ回路とを備え、昇圧能力制御手段は、アナログ信号に応じて、電源から高電圧生成手段に供給される電流の大きさをアナログ的に変化させる。40

【0020】

請求項8に係る高電圧発生装置は、電源電圧を昇圧することにより高電圧を生成し、負荷に供給する高電圧生成手段と、高電圧生成手段の出力電圧の大きさを検出する出力電圧検出手段と、出力電圧検出手段によって検出された出力電圧の大きさに応じて高電圧生成手段の昇圧能力を制御する昇圧能力制御手段と、出力電圧検出手段における検出結果に基づき生成されるアナログ信号を、高電圧生成手段に与えられるクロック信号が活性化する50

たびに更新して、アナログ信号を昇圧能力制御手段に与えるフィルタ回路とを備え、昇圧能力制御手段は、アナログ信号に応じて、高電圧生成手段から出力される電流の大きさをアナログ的に変化させる。

請求項 9 に係る高電圧発生装置は、請求項 7 または請求項 8 に記載の高電圧発生装置であって、出力電圧検出手段は、高電圧生成手段の出力電圧と第 1 の基準電圧とを比較し第 1 の信号を生成する第 1 の出力電圧検出手段と、高電圧生成手段の出力電圧と第 1 の基準電圧より小さい第 2 の基準信号とを比較し第 2 の信号を生成する第 2 の出力電圧検出手段とを含み、フィルタ回路は、第 1 の信号および第 2 の信号に基づいてアナログ信号を生成する。

請求項 10 に係る高電圧発生装置は、請求項 9 に記載の高電圧発生装置であって、フィルタ回路は、第 1 の信号を受ける第 1 の入力部と、第 2 の信号を受ける第 2 の入力部と、昇圧能力制御手段と接続されるノードとを含み、フィルタ回路は、第 1 の信号および第 2 の信号に基づきノードの電圧レベルをアナログ的に変動させることによりアナログ信号を生成する。

#### 【0022】

#### 【発明の実施の形態】

以下、本発明の実施の形態を図面を参照して詳しく説明する。なお、図中同一符号は同一または相当部分を示す。

#### 【0023】

#### [実施の形態 1]

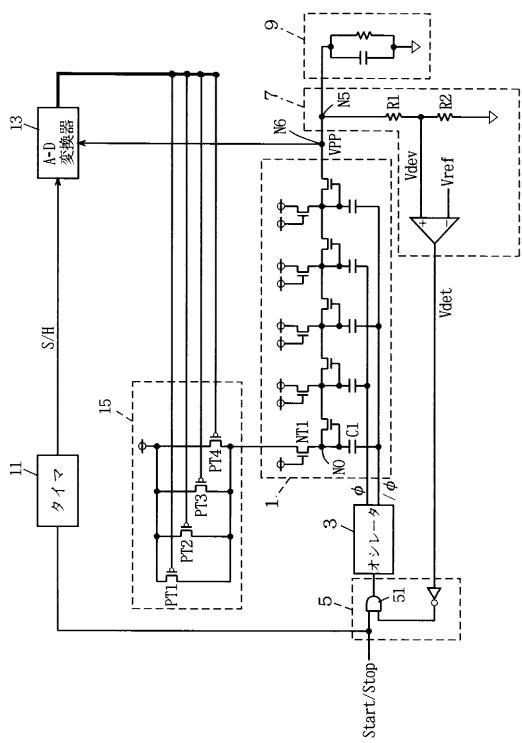

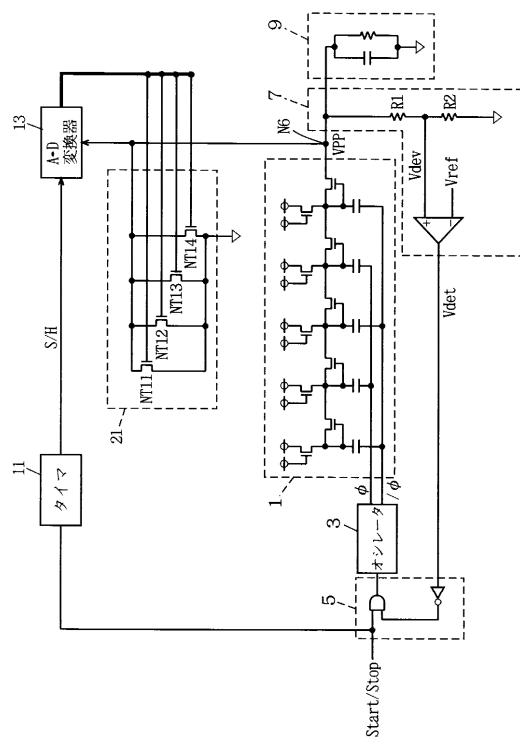

図 1 は、本発明の実施の形態 1 に係る高電圧発生装置の構成を示す図である。図 1 に示されるように、この高電圧発生装置は、負荷 9 に接続され、チャージポンプ 1 と、オシレータ 3 と、チャージポンプ制御回路 5 と、検出回路 7 と、タイマ 11 と、A - D 変換器 13 と、電流制限回路 15 とを備える。

#### 【0024】

ここで、チャージポンプ 1 と、オシレータ 3 、チャージポンプ制御回路 5 、検出回路 7 の構成は上記従来の高電圧発生装置のものと同様である。

#### 【0025】

タイマ 11 は、チャージポンプ制御回路 5 に入力されるチャージポンプ活性化信号 S<sub>t a r t / S t o p</sub> に同期して動作し、チャージポンプの動作開始後予め設定された所定時間を計測する。

#### 【0026】

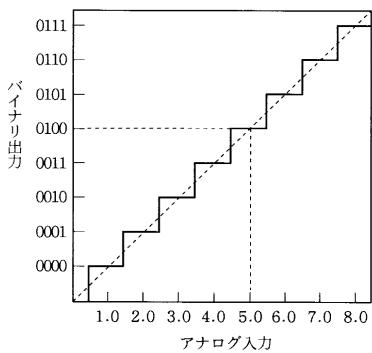

また、A - D 変換器 13 は、タイマ 11 から出力されるサンプルホールド信号 S / H を受取ってチャージポンプ 1 の出力ノード N 6 から出力電圧を入力し、その大きさをデジタル信号に変換する。図 2 は、この A - D 変換器 13 の特性を示す図である。図 2 に示されるように、たとえば、アナログ入力として 5 . 0 V が入力されたとき、A - D 変換器 13 は 4 ビットのデジタル値 (0100) を出力する。

#### 【0027】

また、電流制限回路 15 は、電源ノードとチャージポンプ 1 の初段の N チャネル M O S トランジスタ N T 1 のドレンとの間に並列接続された P チャネル M O S トランジスタ P T 1 ~ P T 4 を含む。そして、それぞれの P チャネル M O S トランジスタ P T 1 ~ P T 4 のゲートには、A - D 変換器 13 からの 4 ビットの出力信号 (デジタル値) V<sub>c c / G N D</sub> の各ビットに対応した電圧が供給される。

#### 【0028】

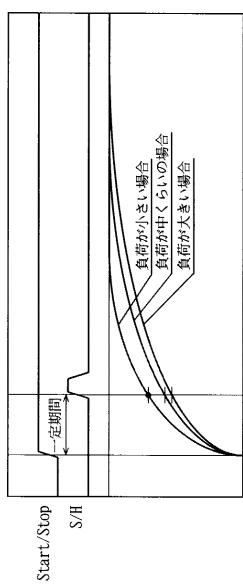

次に、本発明の実施の形態 1 に係る高電圧発生装置の動作を図 3 を参照しつつ説明する。

#### 【0029】

ハイレベルのチャージポンプ活性化信号 S<sub>t a r t / S t o p</sub> がチャージポンプ制御回路 5 に入力することによって、チャージポンプ 1 はポンプ動作を開始し、それと同時にタイマ 11 が時間の計測を開始する。

#### 【0030】

10

20

30

40

50

そして、図3に示されるように予め定められた一定時間経過後にタイマ11はサンプルホールド信号S/HをA-D変換器13に出力する。A-D変換器13はこのサンプルホールド信号S/Hを受けて、チャージポンプ1の出力ノードN6より出力電圧VPPをサンプリングし、その電位に応じたバイナリデータを決定する。なお、決定後は、A-D変換器13の出力データが保持される。

#### 【0031】

ここで、外部接続される負荷9が大きいとチャージポンプ1の出力電圧VPPの立上がりが緩やかなので、図3に示されるように、チャージポンプ1の動作開始後一定時間が経過したときに到達する出力電圧のレベルは低いものとなる。したがってこの場合は、小さなディジタル値が出力される。

10

#### 【0032】

一方、外部接続される負荷9が小さいと、チャージポンプ1の出力電圧VPPの立上がりが急なので、チャージポンプ1の動作開始後一定時間経過後に出力電圧が到達するレベルは高いものとなる。したがって、この場合は大きなディジタル値が出力される。

#### 【0033】

このようにして、チャージポンプ1の動作開始時は、A-D変換器13から(0000)のディジタル値が出力されるため電流制限回路15に含まれるPチャネルMOSトランジスタPT1～PT4はすべてオンし、チャージポンプ1へ電源ノードより最大の電流が供給される。しかし、その後A-D変換器13で外部接続された負荷9が小さいと見積もられれば、出力されるディジタル値が大きいため、オンするPチャネルMOSトランジスタPT1～PT4の数が少ないものとされチャージポンプ1へ供給される電流の大きさが小さくなる。これによりチャージポンプ1の昇圧能力が減少される。

20

#### 【0034】

一方、負荷9が大きいと見積もられた場合には、出力されるディジタル値が小さいため、オンするPチャネルMOSトランジスタPT1～PT4の数は多くなり、チャージポンプ1へ供給される電流の大きさが大きくなる。これによりチャージポンプ1の昇圧能力が高められる。

#### 【0035】

以上より、外部に接続された負荷9の大きさに応じてチャージポンプ1の昇圧能力が調整されるため、リップルが抑制される。

30

#### 【0036】

##### [実施の形態2]

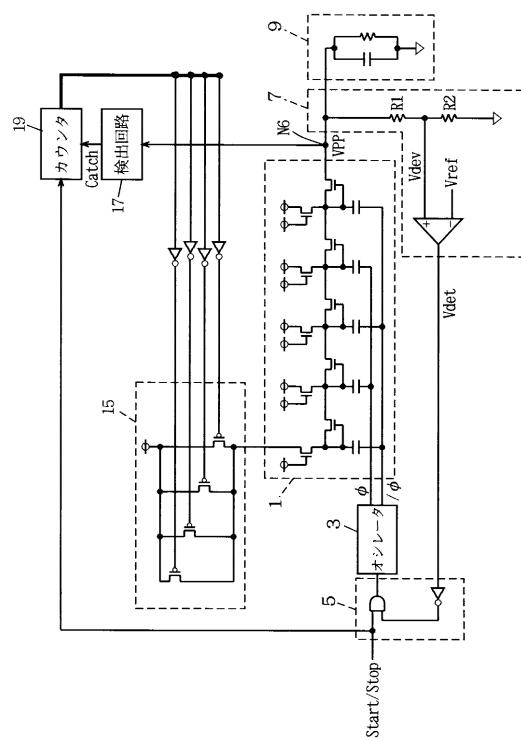

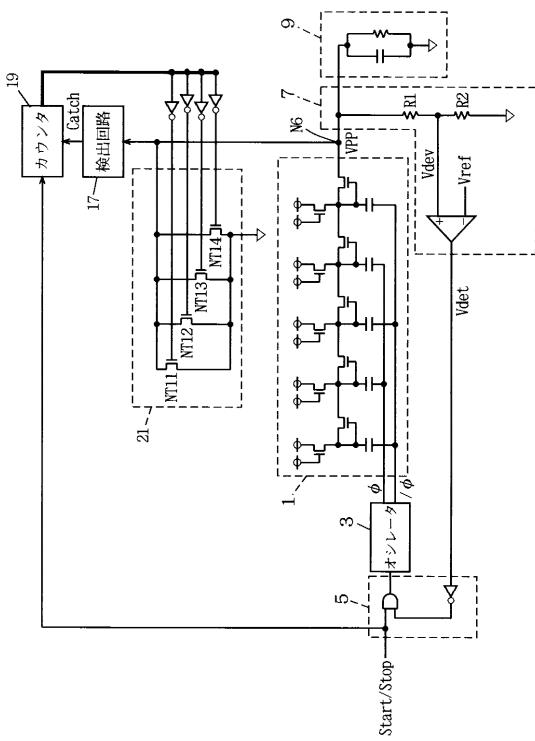

図4は、本発明の実施の形態2に係る高電圧発生装置の構成を示す図である。

#### 【0037】

図4に示されるように、本実施の形態2に係る高電圧発生装置は、上記実施の形態1に係る高電圧発生装置と同様な構成を有するが、外部接続される負荷9の大きさを見積る手段として、チャージポンプ1の出力ノードN6に接続される検出回路17と、検出回路17に接続されチャージポンプ活性化信号Start/Stopと同期して動作し、チャージポンプ1の動作開始後の時間をカウントするカウンタ19とを備える点で相違する。

#### 【0038】

40

ここで、検出回路17の構成は、検出回路7と同様であるが設定される基準電圧は、所望の出力電圧より低いものとされる。

#### 【0039】

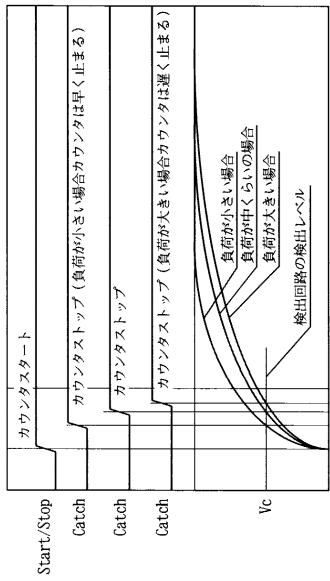

以下において、本発明の実施の形態2に係る高電圧発生装置の動作を図5を参照しつつ説明する。

#### 【0040】

ハイレベルのチャージポンプ活性化信号Start/Stopによってチャージポンプ1はその動作を開始し、それと同時に検出回路17がチャージポンプ1の出力電圧の計測を開始する。また、同時にカウンタ19もチャージポンプ1の動作開始後の時間をカウントする。

50

**【0041】**

ここで、検出回路17は、チャージポンプ1の出力電圧が予め決められた設定電圧 $V_c$ に到達したとき、ハイレベルの信号Catchをカウンタ19に出力する。この信号を受けてカウンタ19は時間の計測を終了し、その値を保持する。図5に示されるように、外部に接続される負荷9が小さいと、チャージポンプ1の出力電圧が設定電圧 $V_c$ に到達するまでの時間が短いので、カウンタ19は信号Catchにより早く止まり、保持した値は小さいものとなる。これにより、カウンタ19から電流制限回路15へ出力される4ビットのデジタル値は小さくその値はインバータで反転されるため、オンするPチャネルMOSトランジスタPT1～PT4の数は少なくなりチャージポンプ1に供給される電流の大きさは小さくなる。したがって、負荷9が小さいときはチャージポンプ1の昇圧能力が低減される。10

**【0042】**

一方、負荷9が大きいと、チャージポンプ1の出力電圧が設定電圧 $V_c$ に到達するまでの時間が長いのでカウンタ19は信号Catchにより遅く止まり、保持する値は大きなものとなる。これにより、カウンタ19から電流制限回路15へ出力される4ビットのデジタル値は大きくその値はインバータで反転されるため、オンするPチャネルMOSトランジスタPT1～PT4の数は多くなりチャージポンプ1に供給される電流の大きさは大きくなる。したがって、負荷9が大きいときはチャージポンプ1の昇圧能力が増大される。20

**【0043】**

以上より、本実施の形態2に係る高電圧発生装置によっても外部に接続された負荷9の大きさに応じてチャージポンプ1の昇圧能力が調整され、リップルが抑制される。20

**【0044】****[実施の形態3]**

図6は、本発明の実施の形態3に係る高電圧発生装置の構成を示す図である。

**【0045】**

図6に示されるように、本実施の形態3に係る高電圧発生装置は、上記実施の形態1に係る高電圧発生装置と同様な構成を有するが、電流制限回路15の代わりにクリップ回路21が備えられる点で相違する。30

**【0046】**

このクリップ回路21は、接地ノードとチャージポンプ1の出力ノードN6との間に並列に接続された4つのNチャネルMOSトランジスタNT11～NT14を含む。

**【0047】**

次に、本実施の形態3に係る高電圧発生装置の動作を説明する。

ハイレベルのチャージポンプ活性化信号Start/Stopがチャージポンプ制御回路5へ入力すると、オシレータ3が活性化しチャージポンプ1が動作を開始する。ここで、タイマ11は、ハイレベルのチャージポンプ活性化信号Start/Stopを受取って動作を開始し、予め設定された所定時間経過後にサンプルホールド信号S/Hを出力する。40

**【0048】**

ここで、A-D変換器13は、タイマ11から出力されるサンプルホールド信号S/Hを受取ってチャージポンプ1の出力ノードN6から出力電圧を入力し、その大きさをデジタル信号に変換する。このデジタル信号は4ビットのバイナリデータであって、各ビットに対応する信号( $V_{cc}/GND$ )がそれぞれ4つのNチャネルMOSトランジスタNT11～NT14のゲートに入力する。

**【0049】**

したがって、チャージポンプ1の出力ノードN6からのリーク電流量はオン状態になるこのNチャネルMOSトランジスタNT11～NT14の数により可変とされる。

**【0050】**

たとえば、A-D変換器13は、負荷9が小さいとき大きなデジタル値を出力し、クリ50

ップ回路 21 に含まれる N チャネルMOS トランジスタ NT11 ~ NT14 がより多くオン状態となる。このため、チャージポンプ 1 から出力される電流がクリップ回路 21 でより多くリークされ、チャージポンプ 1 の昇圧能力が低減される。

#### 【0051】

また、逆に負荷 9 が大きいとき、A - D 変換器 13 は小さなディジタル値を出力するため、クリップ回路 21 に含まれる N チャネルMOS トランジスタ NT11 ~ NT14 の数は少なく、チャージポンプ 1 の昇圧能力が増大される。

#### 【0052】

このような動作により、チャージポンプ 1 の駆動力は変化せずとも、出力電流量が変わるために見かけ上チャージポンプ 1 の昇圧能力が増減され、リップルが抑制される。

10

#### 【0053】

##### [実施の形態 4]

図 7 は、本発明の実施の形態 4 に係る高電圧発生装置の構成を示す図である。

#### 【0054】

図 7 に示されるように、本実施の形態 4 に係る高電圧発生装置は、上記実施の形態 3 に係る高電圧発生装置と同様な構成を有するが、負荷 9 の大きさを見積る手段として、タイマ 11 および A - D 変換器 13 の代わりに、上記実施の形態 2 で説明したカウンタ 19 および検出回路 17 を備える点で相違する。

#### 【0055】

この実施の形態 4 に係る高電圧発生装置は、負荷 9 が小さいときには、図 5 に示されるように、検出回路 17 は信号 Catch を早くカウンタ 19 に出力するため、カウンタ 19 はチャージポンプ 1 動作開始後早く止まり、計測時間に対応する小さなディジタル値を出力する。このため、クリップ回路 21 に含まれる N チャネルMOS トランジスタ NT11 ~ NT14 は、より多くオン状態となりチャージポンプ 1 の出力電流量が減少される。したがって、この場合には見かけ上チャージポンプ 1 の昇圧能力が低減される。

20

#### 【0056】

また逆に、負荷 9 が大きいときには、カウンタ 19 は大きなディジタル値を出力するため、N チャネルMOS トランジスタ NT11 ~ NT14 は、より多くオン状態となり、見かけ上チャージポンプ 1 の昇圧能力が増大される。

#### 【0057】

以上により、本実施の形態 4 に係る高電圧発生装置においても、負荷 9 の大きさに応じてチャージポンプ 1 の昇圧能力を調整するため、リップルを抑制することができる。

30

#### 【0058】

##### [実施の形態 5]

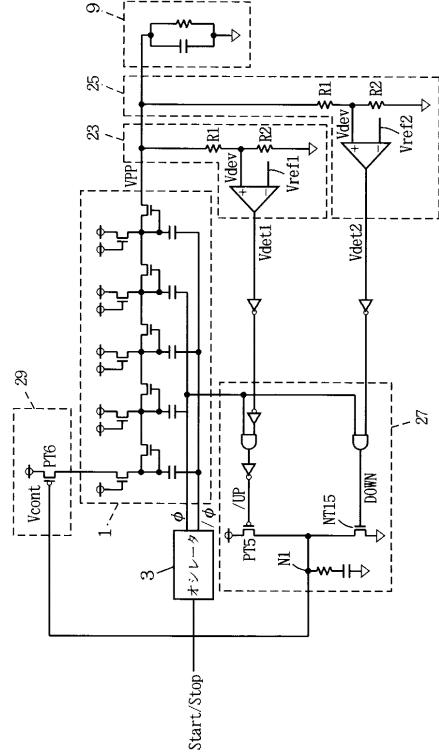

図 8 は、本発明の実施の形態 5 に係る高電圧発生装置の構成を示す図である。

#### 【0059】

図 8 に示されるように、本実施の形態 5 に係る高電圧発生装置は、オシレータ 3 と、チャージポンプ 1 と、チャージポンプ 1 の出力電圧をそれぞれ基準電圧 Vref1 , Vref2 を比較する検出回路 23 , 25 と、チャージポンプ 1 に電流を供給する電流制限回路 29 と、電流制限回路 29 を制御するフィルタ回路 27 とを備える。

40

#### 【0060】

ここで、検出回路 23 , 25 は、それぞれ、従来の高電圧発生装置の検出回路 7 と同様の構成を有するが、基準電圧 Vref1 は基準電圧 Vref2 より小さい電圧とされる。

#### 【0061】

また、電流制限回路 29 は、ソースが電源ノードに接続された P チャネルMOS トランジスタ PT6 を含む。

#### 【0062】

次に、フィルタ回路 27 の構成および動作を図 9 を参照して説明する。

図 9 に示されるように、フィルタ回路 27 は信号 / Vdet1 を反転させるインバータ 273 と、信号 T とインバータ 273 の出力信号を入力する AND 回路 271 と、信号 T と

50

信号 / V<sub>d e t</sub> 2 を入力する AND 回路 272 と、AND 回路 271 の出力信号を反転させるインバータ 274 と、インバータ 274 の出力信号 / UP をゲートに受けソースには電源ノードが接続される P チャネル MOS トランジスタ PT5 と、AND 回路 272 の出力信号 DOWN をゲートに受けソースには接地ノードが接続される N チャネル MOS トランジスタ NT15 と、抵抗 R と、容量 C とを含む。

#### 【0063】

このフィルタ回路 27において、信号 / UP が活性状態（ローレベル）になると、P チャネル MOS トランジスタ PT5 がオンし、ノード N1 を充電する。

#### 【0064】

一方、信号 DOWN が活性状態（ハイレベル）になると、N チャネル MOS トランジスタ NT15 がオンし、ノード N1 を放電する。ここで、信号 / UP と信号 DOWN はクロック信号 T がハイレベルのとき生成されるパルス信号である。したがって、クロック信号 T を活性化するたびに信号 / V<sub>d e t</sub> 1 と信号 / V<sub>d e t</sub> 2 の状態とによりノード N1 を充電したり放電したりする。つまり、信号 / V<sub>d e t</sub> 1 と信号 / V<sub>d e t</sub> 2 との活性頻度に応じてノード N1 の電圧レベルがアナログ的に変動する。10

#### 【0065】

具体的には、クロック信号 T がハイレベルのとき、信号 / UP と信号 / V<sub>d e t</sub> 1 、信号 DOWN と信号 / V<sub>d e t</sub> 2 の論理値はそれぞれ一致し、クロック信号 T がローレベルのとき信号 / UP はハイレベル、信号 DOWN はローレベルとなる。したがって、クロック信号 T がローレベルのとき P チャネル MOS トランジスタ PT5 および N チャネル MOS トランジスタ NT15 はともにオフする一方、クロック信号 T がハイレベルであって、信号 / V<sub>d e t</sub> 1 の活性頻度が多い場合は、ノード N1 の電位を上昇し、信号 / V<sub>d e t</sub> 2 の活性頻度が多い場合にはノード N1 の電位が下降する。20

#### 【0066】

また、信号 / UP と信号 DOWN が同時に活性化した場合は、ノード N1 の電位は一定に保たれるように P チャネル MOS トランジスタ PT5 と N チャネル MOS トランジスタ NT15 のサイズが決められる。

#### 【0067】

次に、本発明の実施の形態 5 に係る高電圧発生装置の動作を説明する。

フィルタ回路 27 には、オシレータ 3 から出力されるクロック信号 が入力される。また、検出回路 23 の出力信号 V<sub>d e t</sub> 1 は、チャージポンプ 1 の出力電圧 V<sub>P P</sub> > (R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 1 / R<sub>2</sub> のときハイレベルになる。一方、検出回路 25 の出力信号 V<sub>d e t</sub> 2 は出力電圧 V<sub>P P</sub> > (R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 2 / R<sub>2</sub> のときハイレベルになる。30

#### 【0068】

ここで、チャージポンプ 1 の出力電圧 V<sub>P P</sub> が (R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 1 / R<sub>2</sub> より低く信号 V<sub>d e t</sub> 1 , V<sub>d e t</sub> 2 がともにローレベルのとき、フィルタ回路 27 に含まれる N チャネル MOS トランジスタ NT15 はオンし、ノード N1 の電位 V<sub>c o n t</sub> が下がる。これにより、電流制限回路 29 に含まれる P チャネル MOS トランジスタ PT6 がオンする。

#### 【0069】

また、チャージポンプ 1 の出力電圧 V<sub>P P</sub> が (R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 1 / R<sub>2</sub> より大きく (R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 2 / R<sub>2</sub> より小さければ信号 V<sub>d e t</sub> 1 がハイレベル、信号 V<sub>d e t</sub> 2 がローレベルとなり、フィルタ回路 27 によりノード N1 の電位 V<sub>c o n t</sub> は一定レベルに保持される。この場合には、ノード N1 の電位 V<sub>c o n t</sub> が一定レベルとされるため、チャージポンプ 1 に供給される電流量は一定とされ、チャージポンプ 1 の昇圧能力は一定に保たれる。40

#### 【0070】

次に、チャージポンプ 1 の出力電圧 V<sub>P P</sub> が、(R<sub>1</sub> + R<sub>2</sub>) · V<sub>r e f</sub> 2 / R<sub>2</sub> より高く信号 V<sub>d e t</sub> 1 , V<sub>d e t</sub> 2 がともにハイレベルのとき、フィルタ回路 27 に含まれる P チャネル MOS トランジスタ PT5 がオンするため、ノード N1 の電位 V<sub>c o n t</sub> が上50

昇する。これにより、PチャネルMOSトランジスタPT6を通してチャージポンプ1に供給される電流量は減少する。したがって、この場合はチャージポンプ1の昇圧能力が低減される。

#### 【0071】

以上より、チャージポンプ1の出力電圧VPPのレベルを一定にするよう昇圧能力が調整され、リップルが抑制される。

#### 【0072】

##### [実施の形態6]

図10は、本発明の実施の形態6に係る高電圧発生装置の構成を示す図である。

#### 【0073】

図10に示されるように、本実施の形態6に係る高電圧発生装置は、上記実施の形態5に係る高電圧発生装置と同様な構成を有するが、電流制限回路29の代わりにクリップ回路31が備えられる点で相違する。

#### 【0074】

このクリップ回路31は、ソースが接地ノードに、ドレインがチャージポンプ1の出力ノードに、ゲートがフィルタ回路27に含まれるノードN1に接続されるNチャネルMOSトランジスタNT16を含む。

#### 【0075】

以下に、本実施の形態6に係る高電圧発生装置の動作を説明する。

チャージポンプ1の出力電圧VPPが( $R_1 + R_2$ )・ $V_{ref1}/R_2$ より低いときは、検出回路23, 25からそれぞれ出力される信号Vdet1, Vdet2がともにローレベルとなり、フィルタ回路27に含まれるNチャネルMOSトランジスタNT15がオンするため、ノードN1の電位Vcontが下がる。

#### 【0076】

これにより、クリップ回路31に含まれるNチャネルMOSトランジスタNT16を介してリークする電流量は減少する。

#### 【0077】

また、チャージポンプ1の出力電圧VPPが( $R_1 + R_2$ )・ $V_{ref1}/R_2$ より高く( $R_1 + R_2$ )・ $V_{ref2}/R_2$ より低いときは、信号Vdet1がハイレベル、信号Vdet2がローレベルとなり、ノードN1の電位Vcontは一定レベルに保持される。この場合には、クリップ回路31での電流リーク量が一定に保たれる。

#### 【0078】

一方、チャージポンプ1の出力電圧VPPが( $R_1 + R_2$ )・ $V_{ref2}/R_2$ より高いときは、信号Vdet1, Vdet2がともにハイレベルとなり、フィルタ回路27に含まれるPチャネルMOSトランジスタPT5がオンするため、ノードN1の電位Vcontが上昇する。これにより、クリップ回路31に含まれるNチャネルMOSトランジスタNT16を介してリークする電流量が増加する。

#### 【0079】

したがってこの場合には、チャージポンプ1の昇圧能力が低減される。

以上のように、チャージポンプ1の出力電圧VPPが一定となるようクリップ回路31での電流リーク量を調整することによって、リップルが抑制される。

#### 【0080】

##### 【発明の効果】

本発明に係る高電圧発生装置によれば、負荷の大きさに応じて高電圧生成手段の昇圧能力が制御されるため、リップルを抑制することができる。

#### 【0081】

本発明に係る高電圧発生装置によれば、高電圧生成手段における起動の所定時間経過後の出力電圧の大きさを検知する電圧検知手段を含むため、外部接続された負荷の大きさを見積もることができ、負荷の大きさに応じて昇圧能力を制御することができる。

#### 【0082】

本発明に係る高電圧発生装置によれば、高電圧生成手段において起動後の出力電圧が所定電圧に到達したことが検出されるまでの時間を測るカウント手段を含むため、外部接続された負荷の大きさを見積もることができ、負荷の大きさに応じて昇圧能力を制御することができる。

【0083】

本発明に係る高電圧発生装置によれば、昇圧能力制御手段が高電圧生成手段に供給する電流の大きさを変化させるため、高電圧生成手段の昇圧能力を変化させることができる。

【0084】

本発明に係る高電圧発生装置によれば、高電圧生成手段に供給される電流量をデジタル的に変化させることができる。 10

【0085】

本発明に係る高電圧発生装置によれば、昇圧能力制御手段は高電圧生成手段から出力される電流の大きさを変化させるため、高電圧生成手段の昇圧能力を変化させることができる。

【0086】

本発明に係る高電圧発生装置によれば、高電圧生成手段から出力される電流量をデジタル的に変化させることができる。

【0087】

本発明に係る高電圧発生装置によれば、高電圧生成手段の昇圧能力がその出力電圧の大きさに応じて制御されるため、リップルが抑制される。 20

【0088】

本発明に係る高電圧発生装置によれば、高電圧生成手段はその出力電圧の大きさに応じて電流が供給されるため、高電圧生成手段の昇圧能力がアナログ的に制御される。

【0089】

本発明に係る高電圧発生装置によれば、高電圧生成手段はその出力電圧の大きさに応じて出力電流の大きさが変化されるため、高電圧生成手段の昇圧能力がアナログ的に制御される。

【図面の簡単な説明】

【図1】 本発明の実施の形態1に係る高電圧発生装置の全体構成を示す図である。

【図2】 図1に示されるA-D変換器の特性を示す図である。 30

【図3】 図1に示されるA-D変換器の動作を説明するための図である。

【図4】 本発明の実施の形態2に係る高電圧発生装置の全体構成を示す図である。

【図5】 図4に示されるカウンタの動作を説明するための図である。

【図6】 本発明の実施の形態3に係る高電圧発生装置の全体構成を示す図である。

【図7】 本発明の実施の形態4に係る高電圧発生装置の全体構成を示す図である。

【図8】 本発明の実施の形態5に係る高電圧発生装置の全体構成を示す図である。

【図9】 図8に示されるフィルタ回路の構成を示す回路図である。

【図10】 本発明の実施の形態6に係る高電圧発生装置の全体構成を示す図である。

【図11】 従来の高電圧発生装置の構成を示す図である。

【符号の説明】

1 チャージポンプ、3 オシレータ、11 タイマ、13 A-D変換器、15, 29

電流制限回路、17, 23, 25 検出回路、19 カウンタ、21, 31 クリップ

回路、27 フィルタ回路。 40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 三原 雅章

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 宮脇 好和

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 高野 芳徳

(56)参考文献 特開平07-231647(JP,A)

特開平06-284705(JP,A)

米国特許第05589793(US,A)

特開平06-259979(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C