(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3909741号 (P3909741)

最終頁に続く

(45) 発行日 平成19年4月25日(2007.4.25)

(24) 登録日 平成19年2月2日 (2007.2.2)

| (51) Int.C1. | F 1                           |                                       |                     |

|--------------|-------------------------------|---------------------------------------|---------------------|

| HO1L 21/822  | ( <b>2006.01)</b> HO1L        | 27/04                                 | Н                   |

| HO1L 27/04   | (2006.01) HO1L                | 29/74                                 | G                   |

| HO1L 29/74   | ( <b>2006.01)</b> HO1L        | 27/06                                 | 3 1 1 Z             |

| HO1L 27/06   | <b>(2006.01)</b> HO1L         | 27/06                                 | I O 1 B             |

| HO1L 21/822  | 2 (2006.01)                   |                                       |                     |

|              |                               |                                       | 請求項の数 10 (全 18 頁)   |

| (21) 出願番号    | 特願2001-53223 (P2001-53223)    | (73) 特許権                              | <b>省</b> 000005049  |

| (22) 出願日     | 平成13年2月27日 (2001.2.27)        |                                       | シャープ株式会社            |

| (65) 公開番号    | 特開2002-261238 (P2002-261238A) |                                       | 大阪府大阪市阿倍野区長池町22番22号 |

| (43) 公開日     | 平成14年9月13日 (2002.9.13)        | (74)代理人                               | 100078282           |

| 審査請求日        | 平成15年1月31日 (2003.1.31)        |                                       | 弁理士 山本 秀策           |

|              |                               | (72)発明者                               | 川添 豪哉               |

|              |                               |                                       | 大阪府大阪市阿倍野区長池町22番22号 |

|              |                               | (70) <b>7</b> 8 <b>1</b> 8 <b>±</b> 4 | シャープ株式会社内           |

|              |                               | (72) 発明者                              | 青木 英治               |

|              |                               |                                       | 大阪府大阪市阿倍野区長池町22番22号 |

|              |                               |                                       | シャープ株式会社内           |

|              |                               | 審査官                                   | 棚田 一也               |

|              |                               |                                       |                     |

|              |                               |                                       |                     |

(54) 【発明の名称】半導体集積回路の静電気保護装置およびそれを用いた静電気保護回路ならびにその製造方法

# (57)【特許請求の範囲】

#### 【請求項1】

第1導電型半導体基板内に形成された第1導電型ウェル層と、

該第1導電型ウェル層に隣接して、第1導電型半導体基板内に形成された第2導電型ウェル層と、

該第1導電型ウェル層上に形成されている第1導電型カソードゲート高濃度不純物領域と、

該第1導電型カソードゲート高濃度不純物領域と第1素子分離絶縁体によって分離されて、該第1導電型カソードゲート高濃度不純物領域よりも該第2導電型ウェル層側に形成され、該第1導電型ウェル層上に設けられた第2素子分離絶縁体および第1素子分離絶縁体の間に形成された第2導電型カソード高濃度不純物領域と、

該第2導電型ウェル層上に形成されている第2導電型アノードゲート高濃度不純物領域と、

該第2導電型アノードゲート高濃度不純物領域と第4素子分離絶縁体によって分離されて、該第2導電型アノードゲート高濃度不純物領域よりも第1導電型ウェル層側に形成され、該第2導電型ウェル層上に設けられた第3素子分離絶縁体および第4素子分離絶縁体の間に形成された第1導電型アノード高濃度不純物領域とを有し、

該第1導電型ウェル層は、その下部に第1導電型高濃度不純物領域が形成されている半 導体集積回路の静電気保護装置。

【請求項2】

20

前記第1導電型カソードゲート高濃度不純物領域と、第2導電型アノードゲート高濃度 不純物領域との間にサイリスタが形成されている請求項1に記載の半導体集積回路の静電 気保護装置。

#### 【請求項3】

前記第1素子分離絶縁体~前記第4素子分離絶縁体のいずれかの幅は、ホールディング電圧が電源電圧以上になるように調整されている請求項1に記載の半導体集積回路の静電気保護装置。

# 【請求項4】

前記第2導電型ウェル層は、その下部に第2導電型高濃度不純物領域が形成されている 請求項1乃至3のいずれかに記載の半導体集積回路の静電気保護装置。

#### 【請求項5】

請求項1に記載の半導体集積回路の静電気保護装置に、電流を双方向に流すことのできる回路素子が、直列接続されていることを特徴とする静電気保護回路。

#### 【請求項6】

前記回路素子がダイオード回路である請求項5に記載の静電気保護回路。

#### 【請求頃7】

前記回路素子がMOSトランジスタである請求項5に記載の静電気保護回路。

#### 【請求項8】

前記回路素子が抵抗である請求項5に記載の静電気保護回路。

#### 【請求項9】

請求項1に記載の半導体集積回路の静電保護装置の製造方法であって、

前記第1導電型半導体基板内に第1導電型不純物を注入して、前記第1導電型ウェル層を形成する工程と、

該第1導電型ウェル層に連続して第1導電型不純物を注入することによって、該第1導電型ウェル層の下部に、前記第1導電型高濃度不純物領域を形成する工程と、

を包含することを特徴とする半導体集積回路の静電保護装置の製造方法。

# 【請求項10】

前記第1導電型ウェル層に隣接した前記第1導電型半導体基板内に第2導電型不純物を 注入して、前記第2導電型ウェル層を形成する工程と、

該第2導電型ウェル層に連続して第2導電型不純物を注入することによって、該第2導電型ウェル層の下部に、第2導電型高濃度不純物領域を形成する工程と、

を包含することを特徴とする請求項<u>9</u>に記載の半導体集積回路の静電保護装置の製造方法。

# 【発明の詳細な説明】

# [0001]

## 【発明の属する技術分野】

本発明は、外部から半導体集積回路への静電気流入現象または帯電した半導体集積回路から外部への静電気放出現象によって、半導体集積回路が破壊されることを防止する半導体集積回路の静電気保護装置およびそれを用いた静電気保護回路ならびにその製造方法に関する。

# [0002]

#### 【従来の技術】

半導体集積回路は、取り扱いに際して、帯電した人体、製造装置等から静電気が半導体集積回路に流入するおそれがある。また、半導体集積回路の搬送工程において、摩擦によって帯電した半導体集積回路が、外部の導体に接触した際に静電気を放出するおそれもある。このように半導体集積回路に対する静電気の流入および流出によって、瞬時に過電流が半導体集積回路内を流れると、半導体集積回路の内部では、過電流によるジュール熱が生じて、配線溶断、接合破壊、絶縁膜破壊等が発生し、半導体集積回路が破壊されるおそれがある。

# [0003]

40

10

20

このような静電気放電による半導体集積回路の破壊を防止するためには、通常、半導体集積回路の外部端子と内部回路との間に、静電気の迂回回路を形成する静電気保護装置が設けられる。

## [0004]

静電気保護装置は、通常、電流制限素子、および、電圧クランプ素子を組み合わせて構成される。電流制限素子は、半導体集積回路の内部を瞬時に流れる過電流を制限するものであり、拡散抵抗、ポリシリコン抵抗等が使用される。電圧クランプ素子は、半導体集積回路の内部に印加される過電圧を抑制するものであり、ダイオード、サイリスタ、MOS型トランジスタ、バイポーラトランジスタ等が使用される。

#### [0005]

電圧クランプ素子としてのサイリスタは、単位素子幅当たりに対して大きな電流を流すことができるために、半導体集積回路内における静電気保護素子の占有面積を小さくできる利点がある。

# [0006]

サイリスタを用いた静電気保護回路の例としては、特開2000-138295号公報に開示されている。その概略構成を図16に示す。

#### [0007]

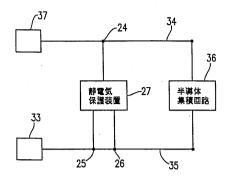

図16は、その公報に開示された静電気保護回路の構成例を示す模式図である。この静電気保護回路は、電圧供給線と基準電圧線との間に、静電気保護装置27が設けられている。静電気保護装置27のアノード端子24は、電源供給線34に接続されており、静電気保護装置27のカソード端子25およびカソードゲート端子26は、基準電圧線35に接続されている。静電気保護装置27によって静電気から保護される半導体集積回路36は、静電気保護装置27と並列になるように、電源供給線34と基準電圧線35との間に接続されている。

#### [0008]

図16に示す静電気保護回路において、電源供給端子37を通して電源供給線34に静電気放電による過電圧が印加された場合には、静電気保護装置27内のサイリスタがON状態となり、電源供給線34と基準電圧線35との間に、静電気保護装置27を介した低抵抗の迂回回路が形成される。これにより、静電気放電による過電圧が静電気保護装置27によって抑制され、半導体集積回路36の破壊が防止される。

#### [0009]

図17は、静電気保護回路を構成するサイリスタを使用した静電気保護装置27の構造図である。この静電気保護装置27は、p型基板1内に設けられたn型ウェル層8を有している。n型ウェル層8上には、p型アノード高濃度不純物領域11およびn型アノードが、また、n型ウェル層8上には、トリガーダイオードEを構成するカソードであるによって分離された状態で積層されている。トリガーダイオードEは、サイリスタの内であるによって分離された状態で積層されている。トリガーダイオードEは、サイリスタの内での内が、カーでの内が、カードの内がであるに設けられており、サイリスタの動作開始電圧を抑制するために設けられており、サイリスタの動作開始電圧であるほり、カー電圧を低減する。n型ウェル層8から離れてp型カソードが一ト高濃度不純物領域6とが素子分離絶縁体3によって分離された状態で積層されている。p型高濃度不純物領域9と、素子分離絶縁体3によって分離されている。p型高濃度不純物領域9は、p型基板1内に設けられたn型ウェル層8の上面およびp型基板1の上面間にわたって積層されている。

# [0010]

p型アノード高濃度不純物領域 1 1、 n型アノードゲート高濃度不純物領域 1 2、 p型カソードゲート高濃度不純物領域 1 8 および n型カソード高濃度不純物領域 6 の表面上には、それぞれシリサイド層 1 3 が素子分離絶縁体 3 によってそれぞれ相互に分離された状態で積層されている。各シリサイド層 1 3 および各素子分離絶縁体 3 上には、全面にわたっ

10

20

30

40

30

40

50

て層間絶縁体20が積層されている。

[0011]

p型アノード高濃度不純物領域11およびn型アノードゲート高濃度不純物領域12上に、それぞれ積層された各シリサイド層13は、層間絶縁体20上に設けられたメタル21と、各シリサイド層13上の層間絶縁体20内に、それぞれ設けられたコンタクト部19を介して、接続されている。n型カソード高濃度不純物領域6上に設けられたシリサイド層13は、層間絶縁体20上に設けられたメタル22と、シリサイド層13上の層間絶縁体20内に設けられたコンタクト部19を介して接続されている。p型カソードゲート高濃度不純物領域18上に設けられたシリサイド層13は、層間絶縁体20上に設けられたメタル23と、シリサイド層13上の層間絶縁体20内に設けられたコンタクト部19を介して接続されている。

[0012]

トリガーダイオード E は、 n 型ウェル層 8 上面と p 型基板 1 の上面間にわたって形成されたアノードである p 型高濃度不純物領域 9 と、 n 型ウェル層 8 の上部に形成されているカソードである n 型高濃度不純物領域 1 0 とを有しており、アノードである p 型高濃度不純物領域 9 およびカソードである n 型高濃度不純物領域 1 0 の間に n 型ウェル層 8 が設けられている。 n 型ウェル層 8 上と、 n 型ウェル層 8 に隣接した p 型高濃度不純物領域 9 および n 型高濃度不純物領域 1 0 の一部の領域上には、半導体集積回路のMOSトランジスタのゲート部分を構成するゲート酸化膜 1 7、ポリシリコン層 1 6、シリサイド層 1 4 が、順番に、層間絶縁体 2 0 内にて積層されており、それらの各側面を覆うようにゲート側壁絶縁体 1 5 が形成されている。

[0013]

半導体集積回路のMOSトランジスタのゲート部分が形成されていないp型高濃度不純物領域9およびn型高濃度不純物領域10のそれぞれの上部には、シリサイド層13が形成されている。トリガーダイオードEは、ゲート側壁絶縁体15の表面には、シリサイド層が形成されていないので、アノードであるp型高濃度不純物領域9とカソードであるn型高濃度不純物領域10とがシリサイド層によって電気的に短絡しない構造となっている。

[0014]

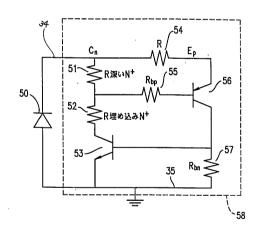

また、サイリスタを用いた静電気保護回路の他の例としては、特開平9-266284号公報に開示されており、その回路図を図18に示す。

[0015]

図18は、バイポーラ/BiCMOS装置のための静電気保護回路であり、サイリスタのトリガー電圧を低減するために、ツェナーダイオード50を用いている。

[0016]

ツェナーダイオード50は、カソード端子が電源供給線34に接続され、アノード端子が基準電圧線35に接続されており、ツェナーダイオード50と並列にサイリスタ58が接続されている。

[0017]

サイリスタ58は、pnpトランジスタ56およびnpnトランジスタ53を有しており、npnトランジスタ53のコレクタ端子(Cn)は、抵抗52と抵抗51とを介して電源供給線34に接続されている。npnトランジスタ53のエミッタ端子は、基準電圧線35に接続され、npnトランジスタ53のベース端子は、pnpトランジスタ56のコレクタ端子に接続されている。npnトランジスタ53のベース端子と基準電圧線35との間には、npnトランジスタ53のベース電圧を与えるベース抵抗57が接続されている。pnpトランジスタ56のエミッタ端子(Ep)は、電源供給線34に接続されている。pnpトランジスタ56のベース端子は、ベース抵抗55を介して抵抗52と抵抗51との接続部に接続されている。pnpトランジスタ56のエミッタ端子(Ep)と、抵抗51と電源供給線34との接続部との間には、抵抗54が接続されている。

[0018]

図18に示す静電気保護回路は、ツェナーダイオード50に印加される電圧がブレークダ

ウン電圧を越えると、抵抗54に電流が流れて、pnpトランジスタ56のエミッタ端子(Ep)に電圧が印加され、同時に、抵抗51および抵抗55を介してpnpトランジスタ56のベース端子に電圧が印加されることによって、pnpトランジスタ56がon状態になる。pnpトランジスタ56がon状態になると、ベース抵抗57に電流が流れて、npnトランジスタ53がon状態となり、サイリスタ58が駆動される。

#### [0019]

一般に、サイリスタを用いた静電気保護回路では、バイポーラ / Bi CMOS装置の通常動作時において、バイポーラ / Bi CMOS装置の入力端子、出力端子、または、電源端子に大電圧の雑音信号が印加されると、サイリスタには、サイリスタが off 状態から on 状態になるトリガー電圧が印加され、雑音信号は、サイリスタを通してバイポーラ / Bi CMOS装置の外部に流れる。バイポーラ / Bi CMOS装置の電源電圧より静電気保護回路のホールディング電圧(保持電圧)が低い場合には、雑音信号が通過した後も、サイリスタに電流が流れ続け、回路パターンにおいてジュール熱が発生して、その発熱によってバイポーラ / Bi CMOS装置が破壊されるラッチアップが生じる。

#### [0020]

ラッチアップを回避するには、静電気保護回路のホールディング電圧がバイポーラ / Bi C M O S 装置の電源電圧より高くなるように調整すれば良い。この結果、バイポーラ / Bi i C M O S 装置の電源電圧より高い雑音信号が印加され、サイリスタに o f f 状態から o n 状態になるトリガー電圧が印加されても、雑音信号の通過した後は、サイリスタには、静電気保護回路のホールディング電圧以下の電圧しか印加されないために、サイリスタの o n 状態が保持されることはない。

#### [0021]

図18に示す静電気保護回路では、サイリスタ58を構成するnpnトランジスタ53のコレクタ端子(Cn)とpnpトランジスタ56のエミッタ端子(Ep)との間に接続された抵抗54の抵抗値を変化させることによって、静電気保護回路のホールディング電圧が調整される。

#### [0022]

# 【発明が解決しようとする課題】

特開2000-138295号公報に開示されているサイリスタを用いた静電気保護装置では、静電気保護装置のホールディング電圧が半導体集積回路の電源電圧より低い場合、半導体集積回路が動作中であって、しかも、静電気保護装置のアノード端子に半導体集積回路の電源電圧が印加されている状態において、静電気保護装置のアノード端子に何らかの雑音信号が印加されることによって、静電気保護装置のサイリスタがon状態になると、静電気保護装置のアノード端子とカソード端子との間には電流が流れ続け、回路パターンにおいてジュール熱が発生して、その発熱によって半導体集積回路が破壊されるラッチアップが生じる。このため、静電気保護装置において、静電気保護装置のホールディング電圧が半導体集積回路の電源電圧より高くなるように調整する必要がある。この場合、静電気保護装置のホールディング電圧の調整は、半導体集積回路の製造コストが増加する新たなフォトマスクおよび工程の追加をせずに行うことが望ましい。

# [0023]

本発明は、このような課題を解決するものであり、その目的は、静電気保護装置において、半導体集積回路の製造工程に、特別な工程およびフォトマスクを追加することなく、静電気保護装置のホールディング電圧を半導体集積回路の電源電圧以上に調整することができ、外部雑音信号によって静電気保護装置を構成するサイリスタが on 状態を保持するラッチアップが生じるおそれがない半導体集積回路の静電気保護装置およびそれを用いた静電気保護回路ならびにその製造方法を提供することにある。

#### [0024]

#### 【課題を解決するための手段】

本発明の半導体集積回路の静電気保護装置は、第1導電型半導体基板内に形成された第

. .

20

30

40

1 導電型ウェル層と、該第1 導電型ウェル層に隣接して、第1 導電型半導体基板内に形成された第2 導電型ウェル層と、該第1 導電型カソードゲート高濃度不純物領域と、該第1 導電型カソードゲート高濃度不純物領域と第1素子分離絶縁体によって分離されて、該第1 導電型カソードゲート高濃度不純物領域よりも該第2 導電型ウェル層側に形成され、該第1 導電型ウェル層上に設けられた第2 素子分離絶縁体および第1素子分離絶縁体の間に形成された第2 導電型カソード高濃度不純物領域と、該第2 導電型アノードゲート高濃度不純物領域と、該第2 導電型アノードゲート高濃度不純物領域と第4素子分離絶縁体によって分離されて、該第2 導電型アノードゲート高濃度不純物領域よりも第1 導電型ウェル層側に形成され、該第2 導電型アノードゲート高濃度不純物領域よりも第1 導電型ウェル層側に形成され、第2 導電型アノードが一ト高濃度不純物領域とを有し、該第1 導電型ウェル層は、その下部に第1 導電型高濃度不純物領域が形成されていることを特徴とする。

[0025]

前記第1導電型カソードゲート高濃度不純物領域と、第2導電型アノードゲート高濃度不純物領域との間にサイリスタが形成されている。

[0026]

前記<u>第1素子分離絶縁体~前記第4素子分離絶縁体のいずれかの幅は、ホールディング</u> 電圧が電源電圧以上になるように調整されている。

[0027]

前記第2導電型ウェル層は、その下部に第2導電型高濃度不純物領域が形成されている。

[0032]

本発明の静電気保護回路は、請求項1に記載の半導体集積回路の静電気保護装置に、電流 を双方向に流すことのできる回路素子が、直列接続されていることを特徴とする。

[0033]

前記回路素子がダイオード回路である。

[0034]

前記回路素子がMOSトランジスタである。

[0035]

前記回路素子が抵抗である。

[0036]

本発明の半導体集積回路の静電気保護装置の製造方法は、請求項1に記載の半導体集積 回路の静電保護装置の製造方法であって、第1導電型半導体基板内に第1導電型不純物を 注入して、第1導電型ウェル層を形成する工程と、該第1導電型ウェル層に連続して第1 導電型不純物を注入することによって、該第1導電型ウェル層の下部に、第1導電型高濃 度不純物領域を形成する工程と、第1導電型ウェル層に隣接した第1導電型半導体基板内 に第2導電型不純物を注入して、第2導電型ウェル層を形成する工程と、該第2導電型ウ ェル層に連続して第2導電型不純物を注入することによって、該第2導電型ウェル層の下 部に、第2導電型高濃度不純物領域を形成する工程と、を包含することを特徴とする。ま た、本発明の半導体集積回路の静電気保護装置の製造方法は、請求項1に記載の半導体集 積回路の静電保護装置の製造方法であって、前記第1導電型半導体基板内に第1導電型不 <u>純物を注入して、前記第1導電型ウェル層を形成する工程と、該第1導電型ウェル層に連</u> 続して第1導電型不純物を注入することによって、該第1導電型ウェル層の下部に、前記 第1導電型高濃度不純物領域を形成する工程と、を包含していてよい。また、本発明の半 導体集積回路の静電気保護装置の製造方法は、前記第1導電型ウェル層に隣接した前記第 1導電型半導体基板内に第2導電型不純物を注入して、前記第2導電型ウェル層を形成す る工程と、該第2導電型ウェル層に連続して第2導電型不純物を注入することによって、 該第2導電型ウェル層の下部に、第2導電型高濃度不純物領域を形成する工程と、を包含 していてもよい。

[0037]

【発明の実施の形態】

10

20

30

40

以下、図面を参照しながら本発明の実施の形態を説明する。

#### [0038]

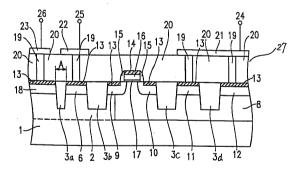

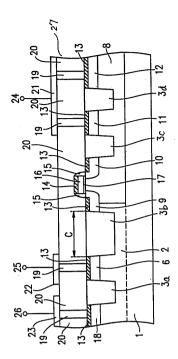

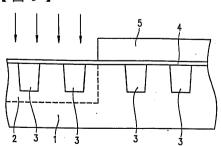

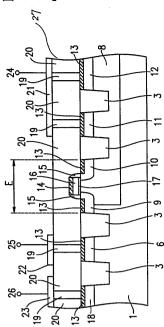

図1は、本発明の第1の実施形態である半導体集積回路の静電気保護装置の構造図である。この静電気保護装置27は、p型基板1内に設けられたn型ウェル層8と、n型ウェル層8と隣接するようにp型基板1内に設けられたp型ウェル層2とを有している。p型中ェル層2上には、n型カソード高濃度不純物領域6およびp型カソードゲート高濃度不純物領域18が第1素子分離絶縁体3aによって分離された状態で積層されている。p型高濃度不純物領域9と第2素子分離絶縁体3bによって分離されている。p型高濃度不純物領域9と第2素子分離絶縁体3bによって分離されている。p型ウェル層2の上面およびp型ウェル層2の上のたって積層されている。p型ウェル層2に隣接するn型ウェル層8上には、p型アノードが一ト高濃度不純物領域11およびn型アノードゲート高濃度不純物領域11が第4素子分離絶縁体3dによって分離された状態で積層されており、また、n型ウェル層8上には下りガーダイオードを構成するカソードであるn型高濃度不純物領域10がp型アノード高濃度不純物領域11と第3素子分離絶縁体3cによって分離された状態で積層されている。その他の構成は、図17に示す静電気保護装置と同様である。

#### [0039]

図1に示す半導体集積回路の静電気保護装置27のサイリスタを構成するnpnトランジスタは、n型アノードゲート高濃度不純物領域12、n型ウェル層8等からコレクタ領域が形成され、p型カソードゲート高濃度不純物領域18、p型ウェル層2、p型基板1等からベース領域が形成され、n型カソード高濃度不純物領域6より、エミッタ領域が形成されている。このnpnトランジスタでは、npnトランジスタのベース領域のp型カソードゲート高濃度不純物領域18と、npnトランジスタのエミッタ領域のn型カソード高濃度不純物領域6との間に設けられている第1素子分離絶縁体3aの間隔Aが、通常より短く設定されている。

## [0040]

この結果、本発明の静電気保護装置 2 7 に使用されているサイリスタを構成するnpnトランジスタは、npnトランジスタのベース / エミッタ間の抵抗値が低くなることによって、npnトランジスタを駆動させる電圧が高くなり、静電気保護装置 2 7 のホールディング電圧も高くなる。

#### [0041]

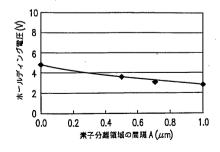

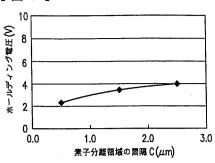

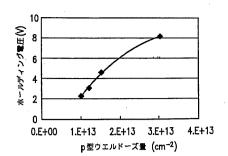

図2は、npnトランジスタのベース領域のp型カソードゲート高濃度不純物領域18とnpnトランジスタのエミッタ領域のn型カソード高濃度不純物領域6との間に設けられている第1素子分離絶縁体3aの間隔Aと、静電気保護装置のホールディング電圧との関係をシミュレーションした結果を示すグラフである。図2より、半導体集積回路の電源電圧が3.3 Vの場合であれば、第1素子分離絶縁体3aの間隔Aを0.5 μm以下にすると、静電気保護装置のホールディング電圧が約3.8 V以上となり、半導体集積回路の電源電圧3.3 V以上に調整可能である。第1素子分離絶縁体3aの間隔Aをx(変数)とし、半導体集積回路の電源電圧をVddとすると次の関係式(1)が成立する。

#### [0042]

- 2 . 0 x + 4 . 8 > V d d · · · · (1)

この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタが on 状態になり、サイリスタを通して雑音信号が半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタは of f 状態となり、静電気保護装置がon 状態を継続するラッチアップ現象を回避することができる。

#### [0043]

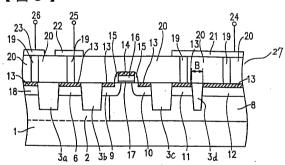

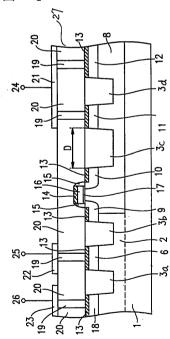

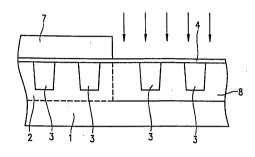

図3は、本発明の第2の実施形態である半導体集積回路の静電気保護装置の構造図である。図3において、本発明の第2の実施形態である半導体集積回路の静電気保護装置のサイリスタを構成するpnpトランジスタは、p型カソードゲート高濃度不純物領域18、p

IU

20

30

40

20

30

40

50

型ウェル層 2 、 p型基板 1 等からコレクタ領域が形成され、 n型アノードゲート高濃度不純物領域 1 2 、 n型ウェル層 8 等からベース領域が形成され、 p型アノード高濃度不純物領域 1 1 より、エミッタ領域が形成されている。この p n p トランジスタでは、 p n p トランジスタのベース領域の n 型アノードゲート高濃度不純物領域 1 2 と、 p n p トランジスタのエミッタ領域の p 型アノード高濃度不純物領域 1 1 との間に設けられている第 4 素子分離絶縁体 3 d の間隔 B が、通常より短く設定されている。その他の構成は、図 1 に示す第 1 の実施形態である半導体集積回路の静電気保護装置と同様である。

### [0044]

この結果、静電気保護装置に使用されているサイリスタを構成するpnpトランジスタは、pnpトランジスタのベース / エミッタ間の抵抗値が低くなることによって、pnpトランジスタを駆動させる電圧が高くなり、静電気保護装置のホールディング電圧も高くなる。

#### [0045]

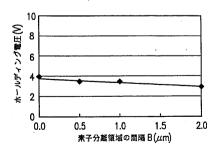

図4は、pnpトランジスタのベース領域のn型アノードゲート高濃度不純物領域12とpnpトランジスタのエミッタ領域のp型アノード高濃度不純物領域11との間に設けられた第4素子分離絶縁体3dの間隔Bと、静電気保護装置のホールディング電圧との関係をシミュレーションした結果を示すグラフである。図4より、半導体集積回路の電源電圧が3.3Vの場合であれば、第4素子分離絶縁体3dの間隔Bを0μmにすると、静電気保護装置のホールディング電圧が約3.8Vとなり、半導体集積回路の電源電圧3.3V以上に調整可能である。第4素子分離絶縁体3dの間隔Bを×(変数)とし、半導体集積回路の電源電圧をVddとすると次の関係式(2)が成立する。

#### [0046]

- 0 . 4 x + 3 . 8 > V d d · · · · · (2)

この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタが on 状態になり、サイリスタを通して雑音信号が半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタは of f 状態となり、静電気保護装置がon 状態を継続するラッチアップ現象を回避することができる。

# [0047]

図5は、本発明の第3の実施形態である半導体集積回路の静電気保護装置の構造図である。図5において、本発明の第3の実施形態である半導体集積回路の静電気保護装置のサイリスタを構成するpnpトランジスタは、p型カソードゲート高濃度不純物領域18、p型ウェル層2、p型基板1等からコレクタ領域が形成され、n型アノードゲート高濃度不純物領域12、n型ウェル層8等からベース領域が形成され、p型アノード高濃度不純物領域11より、エミッタ領域が形成されている。このpnpトランジスタでは、n型カソード高濃度不純物領域6とn型ウェル層8との距離を制御する第2素子分離絶縁体3bの間隔Cが、通常より長く設定されている。その他の構成は、図1に示す第1の実施形態である半導体集積回路の静電気保護装置と同様である。

## [0048]

この結果、静電気保護装置に使用されているサイリスタを構成する p n p トランジスタは、 p n p トランジスタのコレクタ領域の p 型ウェル層 2 が長くなることによって、コレクタ抵抗が増加し、コレクタ電流が減少するとともに、エミッタ電流も減少するために、ベース / エミッタ間の電位差が小さくなることによって、 p n p トランジスタを駆動させる電圧が高くなり、静電気保護装置のホールディング電圧も高くなる。

#### [0049]

図 6 は、 n 型カソード高濃度不純物領域 6 と n 型ウェル層 8 との距離を制御する第 2 素子分離絶縁体 3 b の間隔 C と、静電気保護装置のホールディング電圧との関係をシミュレーションした結果を示すグラフである。図 6 より、半導体集積回路の電源電圧が 3 . 3 V の場合であれば、第 2 素子分離絶縁体 3 b の間隔 C を 1 . 5 μ m以上にすると、静電気保護装置のホールディング電圧が約 3 . 8 V 以上となり、半導体集積回路の電源電圧 3 . 3 V

以上に調整可能である。第2素子分離絶縁体3bの間隔Cを×(変数)とし、半導体集積回路の電源電圧をVddとすると次の関係式(3)が成立する。

#### [0050]

$0.5x + 3.0 > V d d \cdot \cdot \cdot \cdot (3)$

この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタが on 状態になり、サイリスタを通して雑音信号が半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタは of f 状態となり、静電気保護装置がon 状態を継続するラッチアップ現象を回避することができる。

#### [0051]

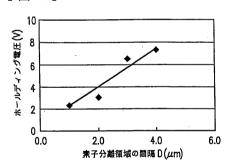

図7は、本発明の第4の実施形態である半導体集積回路の静電気保護装置の構造図である。 図7において、本発明の第4の実施形態である半導体集積回路の静電気保護装置のサイリスタを構成するnpnトランジスタは、n型アノードゲート高濃度不純物領域12、n型ウェル層8等からコレクタ領域が形成され、p型カソードゲート高濃度不純物領域18、p型ウェル層2、p型基板1等からベース領域が形成され、n型カソード高濃度不純物領域6より、エミッタ領域が形成されている。このnpnトランジスタでは、p型アノード高濃度不純物領域11とp型ウェル層2との距離を制御する第3素子分離絶縁体3cの間隔Dが、通常より長く設定されている。その他の構成は、図1に示す第1の実施形態である半導体集積回路の静電気保護装置と同様である。

#### [0052]

この結果、静電気保護装置に使用されているサイリスタを構成するnpnトランジスタは、npnトランジスタのコレクタ領域のn型ウェル層 8 が長くなることによって、コレクタ抵抗が増加し、コレクタ電流が減少するとともに、エミッタ電流も減少するために、ベース / エミッタ間の電位差が小さくなることによって、npnトランジスタを駆動させる電圧が高くなり、静電気保護装置のホールディング電圧も高くなる。

#### [0053]

図8は、p型アノード高濃度不純物領域11とp型ウェル層2との距離を制御する第3素子分離絶縁体3cの間隔Dと、静電気保護装置のホールディング電圧との関係をシミュレーションした結果を示すグラフである。図8より、半導体集積回路の電源電圧が3.3Vの場合であれば、第3素子分離絶縁体3cの間隔Dを2.5μm以上にすると、静電気保護装置のホールディング電圧が約4.5V以上となり、半導体集積回路の電源電圧3.3V以上に調整可能である。第3素子分離絶縁体3cの間隔Dをx(変数)とし、半導体集積回路の電源電圧をVddとすると次の関係式(4)が成立する。

# [0054]

1 .  $6 \times + 0$  .  $8 > V d d \cdot \cdot \cdot \cdot \cdot (4)$

この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタが on 状態になり、サイリスタを通して雑音信号が半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタは of f 状態となり、静電気保護装置がon 状態を継続するラッチアップ現象を回避することができる。

# [0055]

図9は、図1に示す半導体集積回路における静電気保護装置の製造工程において、p型基板1より高濃度の不純物濃度を有するp型ウェル層2を形成する工程の一例を示す断面図である。まず、p型基板1の上部内に複数の素子分離絶縁体3を形成し、p型基板1の表面全体を薄い酸化膜4で覆う。次に、薄い酸化膜4上の全体にフォトレジストを塗布し、p型ウェル層2を形成するためのフォトマスクを用いて、フォトリソグラフィーによって、p型ウェル層2を形成用のフォトレジスト5をパターニングする。その後、薄い酸化膜4上のフォトレジスト5によってパターニングされていない領域に、イオン注入によってp型ウェル層2を形成するp型不純物を注入する。イオン注入後、フォトレジスト5を除去し、熱処理を行い、p型不純物をp型基板1内に拡散させてp型ウェル層2を形成する。

10

20

30

40

30

40

50

#### [0056]

p型ウェル層 2 を形成する p 型不純物をイオン注入する場合には、 p 型ウェル層 2 形成用のフォトレジスト 5 をマスクとして、再度、高エネルギーでイオン注入を行うことにより、 p 型ウェル層 2 の表面から深い領域の不純物濃度を高濃度にすることができるとともに、 p 型ウェル層 2 内に形成される n p n トランジスタ領域の電流電圧特性に影響を与える p 型ウェル層 2 上(エミッタ領域)の不純物濃度を変化させずに、 p 型ウェル層 2 を低抵抗領域にすることができる。

#### [0057]

この結果、前述のnpnトランジスタのベース領域であるp型ウェル層 2 を低抵抗領域にすることができ、静電気保護装置に使用されているサイリスタを構成するnpnトランジスタのベース / エミッタ間の抵抗値が低くなり、npnトランジスタを駆動させる電圧が高くなるために、静電気保護装置のホールディング電圧も高くなる。

#### [0058]

図 1 0 は、 p 型ウェル層 2 の形成において、 2 5 0 k e V の注入エネルギーでボロン( B )をイオン注入した場合のボロンのドーズ量(注入量)と、静電気保護装置のホールディング電圧との関係をシミュレーションした結果を示すグラフである。図 1 0 より、半導体集積回路の電源電圧が 3 . 3 V の場合であれば、ボロンのドーズ量を 1 . 4 × 1 0  $^{13}$  / c  $m^2$ 以上すると、静電気保護装置のホールディング電圧が 4 . 0 V 以上となり、半導体集積回路の電源電圧 3 . 3 V 以上に調整可能である。

#### [0059]

この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタには、サイリスタが o f f 状態から o n 状態になるトリガー電圧が印加され、サイリスタを通して雑音信号は、半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタは o f f 状態となり、静電気保護装置が o n 状態を継続するラッチアップ現象を回避することができる。

#### [0060]

図11は、図9の半導体集積回路における静電気保護装置の製造工程において、 p型ウェル層 2 が形成されると、次に n型ウェル層 8 を形成することを示す。この場合、 p型ウェル層 2 を形成後、薄い酸化膜 4 上の全体にフォトレジストを塗布し、 n型ウェル層 8 を形成するためのフォトマスクを用いて、フォトリソグラフィーによって、 n型ウェル層 8 形成用のフォトレジスト 7 をパターニングする。その後、薄い酸化膜 4 上のフォトレジスト 7 によってパターニングされていない領域に、イオン注入によって n型ウェル層 8 を形成する n型不純物を注入する。イオン注入後、フォトレジスト 7 を除去し、熱処理を行い、 n型不純物を p型基板 1 内に拡散させて n型ウェル層 8 を形成する。 p型ウェル層 2 の形成は、図 9 に示す場合と同様である。

# [0061]

p型基板1の上部にpnpトランジスタが設けられるn型ウェル層8を形成するn型不純物をイオン注入する場合には、n型ウェル層8形成用のフォトレジスト7をマスクとして、再度、高エネルギーでイオン注入を行うことにより、n型ウェル層8の表面から深い領域の不純物濃度を高濃度にすることができるとともに、n型ウェル層8内に形成されるpnpトランジスタ領域の電流電圧特性に影響を与えるn型ウェル層8上(エミッタ領域)の不純物濃度を変化させずに、n型ウェル層8を低抵抗領域にすることができる。pnpトランジスタのベース領域であるn型ウェル層8を低抵抗領域にすることによって、静電気保護装置に使用されているサイリスタを構成するpnpトランジスタのベース/エミッタ間の抵抗値が低くなり、pnpトランジスタを駆動させる電圧が高くなるために、静電気保護装置のホールディング電圧も高くなる。

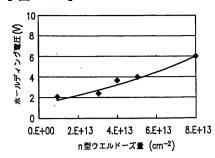

# [0062]

図12は、n型ウェル層8の形成において、600keVの注入エネルギーでリン(P)をイオン注入した場合のリンのドーズ量(注入量)と、静電気保護装置のホールディング

電圧との関係をシミュレーションした結果のグラフである。図12より、半導体集積回路の電源電圧が3.3Vの場合であれば、リンのドーズ量を4.0×10<sup>13</sup> / c m²以上すると、静電気保護装置のホールディング電圧が約3.8V以上となり、半導体集積回路の電源電圧3.3V以上に調整可能である。この結果、半導体集積回路の通常動作時において、大電圧の雑音信号が印加されると、サイリスタがon状態になり、サイリスタを通して雑音信号が半導体集積回路の外部に流れ、雑音信号が通過した後は、半導体集積回路の電源電圧より静電気保護装置のホールディング電圧(保持電圧)が高いために、サイリスタはoff状態となり、静電気保護装置がon状態を継続するラッチアップ現象を回避することができる。

# [0063]

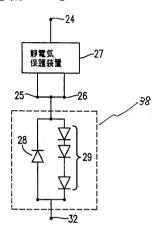

図13は、本発明の静電気保護装置を用いた静電気保護回路である。この静電気保護回路は、静電気保護装置27がダイオード回路38とが直列接続されているために、双方向の電流が流せる。静電気保護装置27には、静電気保護装置27のカソード端子25およびカソードゲート端子26に、順方向が逆になるように並列接続されたダイオード回路が接続されている。ダイオード回路38は、順方向を揃えて直列接続されたダイオード列29とダイオード28とが互いに順方向が逆になるように並列接続されている。ダイオード列29のアノード端子は、ダイオード28のカソード端子と接続され、ダイオード列29のカソード端子は、ダイオード28のカソード端子と接続されている。そして、ダイオード列29のカソード端子とダイオード28のカソード端子の接続部分が静電気保護装置27のカソード端子25とカソードゲート端子26とに接続され、ダイオード列29のカソード端子とダイオード28のアノード端子の接続部分が静電気保護回路のカソード端子とダイオード32

#### [0064]

ダイオード列29のように、ダイオードの順方向を揃えて直列に多段接続することによって、ダイオードー段当たりのpn接合間の電圧0.6 Vの整数倍の電圧分だけ図13の静電気保護回路のホールディング電圧を増加させることができる。この結果、ダイオード列29の多段接続の段数を最適化することによって、図13の静電気保護回路のホールディング電圧を半導体集積回路の電源電圧以上に調整することが可能である。

## [0065]

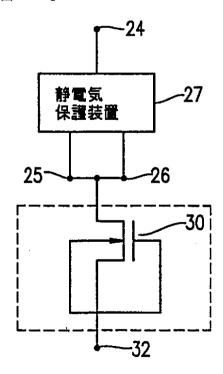

図14は、本発明の静電気保護装置を用いた静電気保護回路の他の例を示している。この静電気保護回路には、静電気保護装置27にn型MOSトランジスタ30が直列接続されている。n型MOSトランジスタ30のドレイン端子は、静電気保護装置27のカソード端子25とカソードゲート端子26とに接続され、n型MOSトランジスタ30のゲート端子およびソース端子は、短絡されており静電気保護回路のカソード端子32となっている。これにより、n型MOSトランジスタ30のホールディング電圧分だけ、図14の静電気保護回路のホールディング電圧を増加させることができることができ、図14の静電気保護回路のホールディング電圧は、半導体集積回路の電源電圧以上に調整することが可能である。

## [0066]

尚、n型MOSトランジスタ30は、ウェル層とドレイン領域との間に寄生ダイオードを 40 形成するために、双方向に電流を流すことが可能である。

#### [0067]

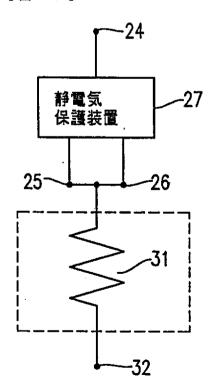

図15は、本発明の静電気保護装置を用いた静電気保護回路さらに他を示している。この静電気保護回路には、静電気保護装置27に抵抗31が直列接続されている。静電気保護装置27のカソード端子25とカソードゲート端子26とに抵抗31が直列接続されており、静電気保護装置27のホールディング電流をIhとし、抵抗31の抵抗値をR31とすると、IhxR31の電圧値分だけ、図15の静電気保護回路のホールディング電圧を増加させることができ、抵抗31の抵抗値を最適化することによって、図15の静電気保護回路のホールディング電圧を、半導体集積回路の電源電圧以上に調整することが可能である。

10

20

[0068]

尚、抵抗31は、ポリシリコン、拡散抵抗、シリサイド抵抗、コンタクト・ビア抵抗、ウ ェル抵抗によって形成することができる。

[0069]

【発明の効果】

本発明の半導体集積回路の静電気保護装置は、第1導電型半導体基板内に形成された第1 導電型ウェル層と、第1導電型ウェル層に隣接して、第1導電型半導体基板内に形成され た第2導電型ウェル層と、第1導電型ウェル層上に形成されている第1導電型カソードゲ ート高濃度不純物領域と、第1導電型カソードゲート高濃度不純物領域と第1素子分離絶 縁体によって分離されて、該第1導電型ウェル層上に設けられた第2素子分離絶縁体およ び第1素子分離絶縁体の間に形成された第2導電型カソード高濃度不純物領域と、第2導 電型ウェル層上に形成されている第2導電型アノードゲート高濃度不純物領域と、第2導 電型アノードゲート高濃度不純物領域と第4素子分離絶縁体によって分離されて、該第2 導電型ウェル層上に設けられた第3素子分離絶縁体および第4素子分離絶縁体の間に形成 された第1導電型アノード高濃度不純物領域と、を有していることによって、半導体集積 回路の製造工程に特別な工程およびフォトマスクを追加することなく、静電気保護装置の ホールディング電圧が半導体集積回路の電源電圧以上に調整でき、外部雑音信号によって 静電気保護装置を構成するサイリスタが on 状態を保持するラッチアップを防止できる。

【図面の簡単な説明】

【図1】本発明の第1の実施形態である半導体集積回路の静電気保護装置の構造図である

20

30

40

【 図 2 】 そ の 静 電 気 保 護 装 置 の 素 子 分 離 絶 縁 体 の 間 隔 A と 静 電 気 保 護 装 置 の ホ ー ル デ ィ ン グ電圧との関係をシミュレーションした結果を示すグラフである。

【図3】本発明の第2の実施形態である半導体集積回路の静電気保護装置の構造図である

【図4】その静電気保護装置の素子分離絶縁体の間隔Bと静電気保護装置のホールディン グ電圧との関係をシミュレーションした結果を示すグラフである。

【図5】本発明の第3の実施形態である半導体集積回路の静電気保護装置の構造図である

【図6】その静電気保護装置の素子分離絶縁体の間隔Cと静電気保護装置のホールディン グ電圧との関係をシミュレーションした結果を示すグラフである。

【図7】本発明の第4の実施形態である半導体集積回路の静電気保護装置の構造図である

【図8】その静電気保護装置の素子分離絶縁体の間隔Dと静電気保護装置のホールディン グ電圧との関係をシミュレーションした結果を示すグラフである。

【図9】本発明の半導体集積回路の静電気保護装置の製造工程におけるpウェル層を形成 する工程を示す断面図である。

【図10】p型ウェル層の形成において、ボロン(B)をイオン注入した場合のボロンの ドーズ量(注入量)と静電気保護装置のホールディング電圧との関係をシミュレーション した結果を示すグラフである。

【図11】本発明の半導体集積回路の静電気保護装置の製造工程におけるnウェル層を形 成する工程を示す断面図である。

【図12】n型ウェル層8の形成において、リン(P)をイオン注入した場合のリンのド ーズ量(注入量)と静電気保護装置のホールディング電圧との関係をシミュレーションし た結果のグラフである。

【図13】本発明の半導体集積回路の静電気保護装置を用いた静電気保護回路である。

【図14】本発明の半導体集積回路の静電気保護装置を用いた他の静電気保護回路である

【図15】本発明の半導体集積回路の静電気保護装置を用いたさらに他の静電気保護回路 である。

【図16】従来の静電気保護装置を設けた静電気保護回路の構成例を示す模式図である。 【図17】従来の静電気保護装置の断面図である。 【図18】従来の静電気保護回路の概略回路図である。 【符号の説明】 p型基板 2 p型ウェル層 3 素子分離絶縁体 3 a 第 1 素子分離 絶縁体 3 b 第 2 素子分離 絶 縁 体 3 c 第 3 素子分離 絶 縁体 10 3 d 第 4 素子分離 絶 縁体 4 薄い酸化膜 5 フォトレジスト n型カソード高濃度不純物領域 6 7 フォトレジスト 8 n型ウェル層 9 p型高濃度不純物領域 10 n型高濃度不純物領域 1 1 p型アノード高濃度不純物領域 12 n型アノードゲート高濃度不純物領域 20 13 シリサイド層 14 シリサイド層 ゲート側壁絶縁体 1 5 16 ポリシリコン 17 ゲート酸化膜 1 8 p型カソードゲート高濃度不純物領域 19 コンタクト部 20 層間絶緣体 21 メタル 22 メタル 30 23 メタル 2.4 アノード端子 2 5 カソード端子 26 カソードゲート端子 27 静電気保護装置 28 ダイオード 29 ダイオード列 3 0 n型MOSトランジスタ 3 1 抵抗 32 静電気保護回路のカソード端子 40 3 3 基準電圧端子 3 4 電源供給線 3 5 基準電圧線 36 半導体集積回路 3 7 電源供給端子 38 ダイオード回路 50 ツェナーダイオード 5 1 抵抗

5 2 抵抗

53 npnトランジスタ

- 5 4 抵抗

- 5 5 ベース抵抗

- 56 pnpトランジスタ

- 5 7 ベース抵抗

- 58 サイリスタ

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

# フロントページの続き

# (56)参考文献 特開平09-293881(JP,A)

特開昭61-032566(JP,A)

特開2000-138295(JP,A)

特開平09-008147(JP,A)

特開2001-035933(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/822

H01L 21/8222

H01L 27/04

H01L 27/06

H01L 29/74