(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6580302号 (P6580302)

(45) 発行日 令和1年9月25日 (2019.9.25)

(24) 登録日 令和1年9月6日(2019.9.6)

FI(51) Int. CL.

G 1 1 C 16/26 (2006, 01) G11C 100 16/26 G 1 1 C 16/08 (2006, 01)G11C 16/08 120

> 請求項の数 30 (全 50 頁)

(21) 出願番号 特願2014-49854 (P2014-49854) (22) 出願日 平成26年3月13日 (2014.3.13) (65) 公開番号 特開2014-182864 (P2014-182864A) (43) 公開日 平成26年9月29日(2014.9.29) 審査請求日 平成29年2月2日(2017.2.2)

(31) 優先権主張番号 10-2013-0027722

平成25年3月15日(2013.3.15) (32) 優先日

(33) 優先権主張国・地域又は機関

韓国(KR)

|(73)特許権者 390019839

三星電子株式会社

Samsung Electronics Co., Ltd.

大韓民国京畿道水原市霊通区三星路129 129, Samsung-ro, Yeon gtong-gu, Suwon-si, G yeonggi-do, Republic

of Korea

(74)代理人 100110364

弁理士 実広 信哉

(72) 発明者 金 經綸

大韓民国大田廣域市儒城区場垈路71番ギ ル34(場垈洞場垈プルジオアパートメン ト107棟1001号)

最終頁に続く

(54) 【発明の名称】不揮発性メモリ装置のデータ読み出し方法及び不揮発性メモリ装置、メモリシステムの駆動方法

## (57)【特許請求の範囲】

## 【請求項1】

メモリ装置のメモリセルに連結された第1ワードラインに第1読み出し電圧(VREF )を印加し前記メモリセルからデータを読み出す読み出し動作を行う段階と、

前記第1ワードラインに対応する第1ページに対する前記読み出し動作において、読み 出された前記データが誤り訂正符号によって誤り訂正可能であるかどうかとは関係なく前 記読み出し動作に応答して、前記メモリセルから前記データを読み出す再読み出し動作を 行う段階と、

前記再読み出し動作に応答して、前記第1読み出し電圧(VREF)とは異なり且つ最 適読み出しレベルを有する読み出し電圧(VOPT)を決める段階を含み、

前記第1ページとは異なるページに対する後続読み出し動作では、前記第1読み出し電 圧(VREF)を用いずに、前記最適読み出しレベルを有する前記読み出し電圧(VOP T)を用いる

ことを特徴とする不揮発性メモリ装置の駆動方法。

### 【請求項2】

前記読み出し動作において、読み出された前記データが前記誤り訂正符号によって誤り 訂正可能であるかどうかを判断する段階をさらに含み、前記再読み出し動作は前記データ が前記誤り訂正符号によって誤り訂正可能であるかどうかの判断に応答して、実行される ことを特徴とする請求項1に記載の不揮発性メモリ装置の駆動方法。

### 【請求項3】

前記第1ワードラインが連結された前記メモリセルはメモリブロックの第1ページに対応して、前記メモリブロックの第2ページに対応するメモリセルに連結された第2ワードラインに前記最適読み出しレベルを有する前記読み出し電圧(VOPT)を印加し前記第2ページに対応するメモリセルからデータを読み出す後続読み出し動作を行う段階をさらに含む

ことを特徴とする請求項1に記載の不揮発性メモリ装置の駆動方法。

### 【請求項4】

前記後続読み出し動作において、読み出された前記データが前記誤り訂正符号によって誤り訂正可能な確率は前記再読み出し動作の実行に応答して増加する

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

## 【請求項5】

前記後続読み出し動作において、読み出された前記データが前記誤り訂正符号によって 誤り訂正可能であるかどうかにより前記第2ページに対する後続再読み出し動作を選択的 に実行または省略する段階をさらに含み、

前記後続再読み出し動作の再読み出し電圧は<u>、前記第1ページに対する</u>前記読み出し動作の<u>前記第1読み出し電圧(VREF)と前記最適読み出しレベルを有する前記読み出し</u>電圧(VOPT)との関係に基づく

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

## 【請求項6】

前記第1ページに対する前記読み出し動作は、前記第1ページに対する硬判定読み出し 動作で読み出された前記データの信頼性を示す軟判定読み出し動作であり、前記後続読み 出し動作は前記第2ページに対する硬判定読み出し動作である

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

#### 【請求項7】

前記読み出し動作は以前に読み出されたページに対し連続した前記第1ページに対する順次読み出し動作を含み、

前記後続読み出し動作は前記第1ページに対<u>し連続していない</u>前記第2ページ<u>に対する</u> ランダム読み出し動作を含む

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

# 【請求項8】

前記読み出し動作は前記メモリブロックの消去後における最初の読み出し動作を含むことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

### 【請求項9】

<u>前記最適読み出しレベル</u>は前記メモリブロックに対応して<u>おり</u>、複数のメモリブロック それぞれに対するそれぞれの最適読み出しレベルを保存する段階をさらに含む

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

# 【請求項10】

前記第 1 および第 2 ワードラインは前記メモリブロックの端から離隔されたそれぞれのメモリセルに連結される

ことを特徴とする請求項3に記載の不揮発性メモリ装置の駆動方法。

# 【請求項11】

前記メモリセルを含むメモリブロックで以前に実行されたプログラム / 消去動作の数を 決める段階をさらに含み、前記再読み出し動作は前記プログラム / 消去動作の数に基づき 、選択的に実行される

ことを特徴とする請求項1に記載の不揮発性メモリ装置の駆動方法。

## 【請求項12】

前記再読み出し動作の間<u>において</u>前記第1ワードラインに印加される再読み出し電圧の数、および / または、これらの間のそれぞれの範囲は<u></u>前記読み出し動作<u>において読み</u>出された前記データが前記誤り訂正符号によって誤り訂正可能であるかどうかにより変更される

10

20

30

50

40

ことを特徴とする請求項1に記載の不揮発性メモリ装置の駆動方法。

## 【請求項13】

「第1ワードラインに第1読み出し電圧を印加し前記第1ワードラインに連結されたメモリセルに対する第1読み出し動作を行う段階と、

\_\_前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは 関係なく、最適読み出しレベルを検出するように第1再読み出しを行う段階と、

前記第1読み出し電圧を用いず、検出した前記最適読み出しレベルを有する読み出し電圧を用いて前記第1ワードラインとは異なる第2ワードラインに連結されたメモリセルに対する後続の第2読み出し動作を行うために、検出した前記最適読み出しレベルを保存する段階を含む不揮発性メモリ装置のデータ読み出し方法。

### 【請求項14】

前記第2ワードラインに前記最適読み出しレベルを有する第2読み出し電圧を印加し前記第2ワードラインに連結されたメモリセルに対する前記第2読み出し動作を行う段階と

前記第 2 読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより第 2 再読み出しを選択的に行う段階をさらに含む

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

### 【請求項15】

前記第2読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかを判断する段階をさらに含み、前記第2再読み出しを選択的に行う段階は、前記第2読み出し動作により読み出されたデータの誤り訂正が可能であると判断された場合、前記第2再読み出しを行わず、前記第2読み出し動作を完了する段階と、

前記第2読み出し動作により読み出されたデータの誤り訂正が可能ではないと判断された場合、前記第2再読み出しを行う段階を含む

ことを特徴とする請求項14に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項16】

前記第2再読み出しは前記第1再読み出しの結果を用い、実行される ことを特徴とする請求項15に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項17】

前記第1再読み出しの結果として前記第1読み出し電圧の電圧レベルより低い前記最適読み出しレベルが検出された場合、前記第2再読み出しは前記第2ワードラインに前記第1読み出し電圧の電圧レベルより低い電圧レベルを有する再読み出し電圧を印加し実行され、前記第1再読み出しの結果として前記第1読み出し電圧の電圧レベルより高い前記最適読み出しレベルが検出された場合、前記第2再読み出しは前記第2ワードラインに前記第1読み出し電圧の電圧レベルより高い電圧レベルを有する再読み出し電圧を印加し実行される

ことを特徴とする請求項16に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項18】

前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかを判断する段階をさらに含み、前記第1再読み出しを行う段階は、前記第1読み出し動作により読み出されたデータの誤り訂正が可能ではないと判断された場合、第1範囲を有する第1再読み出し電圧を用い、前記第1再読み出しを行う段階と、

前記第1読み出し動作により読み出されたデータの誤り訂正が可能であると判断された場合、前記第1範囲より狭い第2範囲を有する第2再読み出し電圧を用い、前記第1再読み出しを行う段階を含む

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

### 【請求項19】

前記第2再読み出し電圧の数は前記第1再読み出し電圧の数より少ない ことを特徴とする請求項18に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項20】

10

20

30

40

BCH(Bose-Chaudhuri-Hocquenghem)符号を用い、前記第1読み出し動作により読み出されたデータに対する誤り訂正を行う段階をさらに含むことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項21】

LDPC(Low DenSity Parity Check)符号を用い、前記第1 読み出し動作により読み出されたデータに対する誤り訂正を行う段階をさらに含む ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項22】

前記第1読み出し動作を行う段階は、前記第1ワードラインに前記第1読み出し電圧を 印加し前記第1ワードラインに連結されたメモリセルから第1硬判定データを読み出す第 1硬判定読み出し動作を行う段階と、

前記第1硬判定読み出し動作により読み出された前記第1硬判定データの誤り訂正が可能であるかどうかを判断する段階と、

前記第1硬判定データの誤り訂正が可能ではないと判断された場合、前記第1ワードラインに連結されたメモリセルから前記第1硬判定データに対する信頼性情報を有する第1 軟判定データを読み出す第1軟判定読み出し動作を行う段階を含む

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項23】

前記第1読み出し動作が複数の隣接したページから次々とデータを読み出す順次読み出し動作のうちの一つなのか否かを判断する段階をさらに含み、前記第1読み出し動作が前記順次読み出し動作のうちの一つではないと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより前記第1再読み出しが選択的に実行され、前記第1読み出し動作が前記順次読み出し動作のうちの一つだと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行され、

複数の隣接したページから次々とデータを読み出す前記順次読み出し動作では、複数の 隣接したページの各ページに対する第1読み出し動作毎に、前記第1読み出し動作により 読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出し が実行される

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項24】

前記第1読み出し動作が前記第1ワードラインに連結されたメモリセルを含むメモリブロックが消去された後最初に実行される読み出し動作なのか否かを判断する段階をさらに含み、前記第1読み出し動作が前記メモリブロックが消去された後最初に実行される読み出し動作ではないと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより前記第1再読み出しが選択的に実行され、前記第1読み出し動作が前記メモリブロックが消去された後最初に実行される読み出し動作だと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行される

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

# 【請求項25】

前記最適読み出しレベルは前記不揮発性メモリ装置に含まれたメモリブロック別に保存される

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項26】

前記第1ワードラインが前記第1ワードラインに連結されたメモリセルを含むメモリブロックの端の領域に位置するのか否かを判断する段階をさらに含み、前記第1ワードラインが前記メモリブロックの端の領域に位置したと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより前記第1再読み出しが選択的に実行され、前記第1ワードラインが前記メモリブロックの端の領域に位置されて

10

20

30

40

ないと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行される

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項27】

前記第1ワードラインに連結されたメモリセルを含むメモリブロックの消去回数をカウントする段階と、

前記カウントされた消去回数を所定の値と比較する段階をさらに含み、前記カウントされた消去回数が前記所定の値のうちの一つと一致しない場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより前記第1再読み出しが選択的に実行され、前記カウントされた消去回数が前記所定の値のうちの一つと一致する場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行される

ことを特徴とする請求項13に記載の不揮発性メモリ装置のデータ読み出し方法。

## 【請求項28】

複数のメモリセルを含むメモリセルアレイと、

第1 ワードラインに読み出し電圧を印加し、前記複数のメモリセルのうち、前記<u>第1</u>ワードラインに連結されたメモリセルに対する第1読み出し動作を行い、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出するように再読み出しを行い、検出した前記最適読み出しレベルを有する読み出し電圧を用いて前記第1ワードラインとは異なる第2ワードラインに連結されたメモリセルに対する後続の第2読み出し動作を行うために、検出した前記最適読み出しレベルを保存するように不揮発性メモリ装置を制御する制御回路を含む不揮発性メモリ装置

## 【請求項29】

不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの駆動方法において、

前記メモリコントローラーが前記不揮発性メモリ装置に読み出しコマンドを転送する段階と、

前記不揮発性メモリ装置が前記読み出しコマンドに応答して<u>第1ワードラインに連結されたメモリセルに対する</u>第1読み出し動作を行うことによって前記メモリコントローラーに前記第1読み出し動作により読み出されたデータを転送する段階と、

前記メモリコントローラーが前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記不揮発性メモリ装置に再読み出しコマンドを転送する段階と、

前記不揮発性メモリ装置が、前記再読み出しコマンドに応答して再読み出しを行うことによって、最適読み出しレベルを検出し、検出した前記最適読み出しレベルを有する読み出し電圧を用いて前記第1ワードラインとは異なる第2ワードラインに連結されたメモリセルに対する後続の第2読み出し動作を行うために、検出した前記最適読み出しレベルを保存する段階を含むメモリシステムの駆動方法。

### 【請求項30】

不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの駆動方法にお いて

前記メモリコントローラーが前記不揮発性メモリ装置に読み出しおよび再読み出しコマンドを転送する段階と、

前記不揮発性メモリ装置が前記読み出しおよび再読み出しコマンドに応答して<u>第1ワードラインに連結されたメモリセルに対する</u>第1読み出し動作を行うことによって前記メモリコントローラーに前記第1読み出し動作により読み出されたデータを転送する段階と、

前記不揮発性メモリ装置が、前記読み出しおよび再読み出しコマンドに応答して前記第 1 読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく 、再読み出しを行うことによって、最適読み出しレベルを検出し、検出した前記最適読み 10

20

30

40

出しレベルを有する読み出し電圧を用いて前記第1ワードラインとは異なる第2ワードラインに連結されたメモリセルに対する後続の第2読み出し動作を行うために、 検出した前記最適読み出しレベルを保存する段階を含むメモリシステムの駆動方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は半導体メモリ装置に関することとして、より詳細には不揮発性メモリ装置のデータ読み出し方法、不揮発性メモリ装置、およびメモリシステムの駆動方法に関する。

【背景技術】

[0002]

フラッシュメモリ装置のような不揮発性メモリ装置のメモリセルはそれぞれ異なる論理状態を示すスレッショルド電圧分布を有するようにプログラムされたことでデータを保存することができる。また、前記所定のスレッショルド電圧を有するメモリセルに所定の読み出し電圧を印加し前記メモリセルがターン・オンするのかまたは、ターン・オフするかどうかを確認することによって前記メモリセルに保存された前記データが読み出しできる。一方、前記メモリセルが前記スレッショルド電圧分布を有するようにプログラムされる。一方、前記メモリセルが前記スレッショルド電圧分布の幅が増加することができる。前記スレッショルド電圧分布の幅が増加することができる。前記スレッショルド電圧分布が広くなれば、前記データが不正確に読み出しされるリードフェール(Read Fail)が発生する可能性がある。前記リードフェールが発生した場合、従来の不揮発性メモリ装置は再読み出し(Read Retry)を行う。前記再読み出しはリードフェールが発生しない時まで予め決まった読み出し電圧レベルを次々と変更しながら読み出し動作を繰り返し行うため、前記再読み出しによって読み出し時

【先行技術文献】

間が増加する問題がある。

【特許文献】

[0003]

【特許文献1】米国特許第7941590号公報

【特許文献 2 】米国特許第 7 8 9 0 8 1 8 号公報

【特許文献3】米国特許第7684255号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

本発明の一目的は平均読み出し時間および/または、平均読み出しレイテンシを減少させることのできる不揮発性メモリ装置のデータ読み出し方法を提供することである。

[0005]

本発明の他の目的は平均読み出し時間および/または、平均読み出しレイテンシを減少させることができる不揮発性メモリ装置を提供することである。

本発明の他の目的は平均読み出し時間および/または、平均読み出しレイテンシを減少させることのできるメモリシステムの駆動方法を提供することである。

[0006]

ただし、本発明における、解決しようとする課題は前記言及された課題に限定されることはなく、本発明の思想および領域から抜け出さない範囲で多様に拡張されてもよい。

【課題を解決するための手段】

[0007]

前記一目的を達成するために、本発明の実施形態による不揮発性メモリ装置の駆動方法において、メモリ装置のメモリセルに連結された第1ワードラインに第1読み出し電圧を印加し、前記メモリセルからデータを読み出す読み出し動作が実行され、前記読み出し動作において、読み出された前記データが誤り訂正符号によって読み出し可能であるかどうかとは別に前記読み出し動作に応答して、前記メモリセルから前記データを読み出す再読

10

20

30

40

み出し動作が実行され、前記再読み出し動作に応答して、前記第1読み出し電圧と異なった誤り訂正可能読み出し電圧が決められる。

### [0008]

一実施形態において、前記読み出し動作において読み出された前記データが前記誤り訂正符号によって読み出し可能であるかどうかが判断され、前記再読み出し動作は前記データが前記誤り訂正符号によって読み出し可能であるかどうかの判断に応答して実行されることができる。

## [0009]

一実施形態において、前記メモリセルはメモリブロックの第1ページに対応して、前記メモリブロックの第2ページに対応するメモリセルに連結された第2ワードラインに前記誤り訂正可能読み出し電圧を印加し前記第2ページに対応するメモリセルからデータを読み出す後続読み出し動作が実行されることができる。

#### [0010]

一実施形態において、前記後続読み出し動作において、読み出された前記データが前記 誤り訂正符号によって誤り訂正可能な確率は前記再読み出し動作の実行に応答して増加す ることができる。

#### [0011]

一実施形態において、前記後続読み出し動作において、読み出された前記データが前記 誤り訂正符号によって誤り訂正可能であるかどうかにより前記第2ページに対する後続再 読み出し動作が選択的に実行または省略され、前記後続再読み出し動作の再読み出し電圧 は前記再読み出し動作の再読み出し電圧と前記誤り訂正可能読み出し電圧の関係に基づく ことができる。

## [0012]

一実施形態において、前記読み出し動作は以前の読み出し動作において読み出された前記データの信頼性を示す軟判定読み出し動作であり、前記後続読み出し動作は前記第2ページに対応する前記メモリセルの第1または第2状態のうちの一つを示す硬判定読み出し動作でもよい。

### [0013]

一実施形態において、前記読み出し動作は以前に読み出されたページに対し、連続した前記第1ページに対する順次読み出し動作を含み、前記後続読み出し動作は前記第1ページに対し連続されない前記第2ページに対するランダム読み出し動作を含むことができる

### [0014]

一実施形態において、前記読み出し動作は前記メモリブロックの消去後、最初の読み出し動作を含むことができる。

### [0015]

一実施形態において、前記誤り訂正可能読み出し電圧は前記メモリブロックに対応し、 複数のメモリブロックのそれぞれに対するそれぞれの誤り訂正可能読み出し電圧が保存さ れることができる。

## [0016]

一実施形態において、前記第1および第2ワードラインは前記メモリブロックの端から離隔されたそれぞれのメモリセルに連結されることができる。

### [0017]

一実施形態において、前記メモリセルを含むメモリブロックにおいて、以前に、実行されたプログラム/消去動作の数が決められ、前記再読み出し動作は前記プログラム/消去動作の数に基づき、選択的に実行されることができる。

### [0018]

一実施形態において、前記再読み出し動作の間、前記第1ワードラインに印加される再読み出し電圧の数、および/または、これらの間のそれぞれの範囲は前記読み出し動作において、読み出された前記データが前記誤り訂正符号によって、誤り訂正可能であるかど

10

20

30

40

うかにより変更されることができる。

# [0019]

前記一目的を達成するために、本発明の実施形態による不揮発性メモリ装置のデータ読み出し方法において、第1ワードラインに第1読み出し電圧を印加し、前記第1ワードラインに連結されたメモリセルに対する第1読み出し動作が実行され、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出するように第1再読み出しが実行され、前記最適読み出しレベルを用い、後続の第2読み出し動作を行うように前記最適読み出しレベルが保存される。

## [0020]

一実施形態において、第2ワードラインに前記最適読み出しレベルを有する第2読み出し電圧を印加し前記第2ワードラインに連結されたメモリセルに対する前記第2読み出し動作が実行され、前記第2読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかにより第2再読み出しが選択的に実行されることができる。

## [0021]

一実施形態において、前記第2読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかが判断され、前記第2読み出し動作により読み出されたデータの誤り訂正が可能であると判断された場合、前記第2再読み出しを行わず、前記第2読み出し動作が完了し、前記第2読み出し動作により読み出されたデータの誤り訂正が可能ではないと判断された場合、前記第2再読み出しが実行されることができる。

## [0022]

一実施形態において、前記第2再読み出しは前記第1再読み出しの結果を用い、実行されることができる。

## [0023]

一実施形態において、前記第1再読み出しの結果として前記第1読み出し電圧の電圧レベルより低い前記最適読み出しレベルが検出された場合、前記第2再読み出しは前記第2ワードラインに前記第1読み出し電圧の電圧レベルより低い電圧レベルを有する再読み出し電圧を印加し実行され、前記第1再読み出しの結果として前記第1読み出し電圧の電圧レベルより高い前記最適読み出しレベルが検出された場合、前記第2再読み出しは前記第2ワードラインに前記第1読み出し電圧の電圧レベルより高い電圧レベルを有する再読み出し電圧を印加し実行されることができる。

### [0024]

一実施形態において、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかが判断され、前記第1読み出し動作により読み出されたデータの誤り訂正が可能ではないと判断された場合、第1範囲を有する第1再読み出し電圧を用い、前記第1再読み出しが実行され、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であると判断された場合、前記第1範囲より狭い第2範囲を有する第2再読み出し電圧を用い、前記第1再読み出しが実行されることができる。

## [0025]

一実施形態において、前記第2再読み出し電圧の数は前記第1再読み出し電圧の数より 少ないこともある。

# [0026]

一実施形態において、BCH(Bose-Chaudhuri-Hocquenghem)符号を用い、前記第1読み出し動作により読み出されたデータに対する誤り訂正が実行されることができる。

### [0027]

一実施形態において、LDPC (Low DenSity Parity Check)符号を用い、前記第1読み出し動作により読み出されたデータに対する誤り訂正が実行されることができる。

## [0028]

一実施形態において、前記第1読み出し動作を行うように、前記第1ワードラインに前

10

20

30

40

記第1読み出し電圧を印加し前記第1ワードラインに連結されたメモリセルから第1硬判定データを読み出す第1硬判定読み出し動作が実行され、前記第1硬判定読み出し動作により読み出された前記第1硬判定データの誤り訂正が可能であるかどうかを判断され、前記第1硬判定データの誤り訂正が可能ではないと判断された場合、前記第1ワードラインに連結されたメモリセルから前記第1硬判定データに対する信頼性情報を有する第1軟判定データを読み出す第1軟判定読み出し動作が実行されることができる。

#### [0029]

一実施形態において、前記第1硬判定データが前記信頼性情報なしで誤り訂正が可能であるか、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能である場合でも、前記第1再読み出しが実行されることができる。

## [0030]

一実施形態において、前記第1軟判定読み出し動作が実行された場合、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかを判断することができ、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能ではないと判断された場合、第1範囲を有する第1再読み出し電圧を用い、前記第1再読み出しが実行され、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であると判断された場合、前記第1の説に要別を有する第2再読み出し電圧を用い、前記第1再読み出しが実行され、前記第1硬判定データが前記信頼性情報なしで誤り訂正が可能であると判断された場合、前記第2範囲より狭い第3範囲を有する第3再読み出し電圧を用い、前記第1再読み出しが実行されることができる。

#### [0031]

一実施形態において、前記第3再読み出し電圧の数は前記第2再読み出し電圧の数より少なく、前記第2再読み出し電圧の数は前記第1再読み出し電圧の数より少ないこともある。

## [0032]

一実施形態において、前記第1硬判定データが前記信頼性情報なしで誤り訂正が可能である場合、前記第1再読み出しが実行されないで、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能である場合でも、前記第1再読み出しが実行されることができる。

## [0033]

一実施形態において、前記第1軟判定読み出し動作が実行された場合、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかを判断することができ、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能ではないと判断された場合、第1範囲を有する第1再読み出し電圧を用い、前記第1再読み出しが実行され、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であると判断された場合、前記第1範囲より狭い第2範囲を有する第2再読み出し電圧を用い、前記第1再読み出しが実行されることができる。

## [0034]

一実施形態において、第2ワードラインに前記最適読み出しレベルを有する第2読み出し電圧を印加し、前記第2ワードラインに連結されたメモリセルから第2硬判定データを読み出す第2硬判定読み出し動作が実行され、前記第2硬判定読み出し動作により読み出された前記第2硬判定データの誤り訂正が可能であるかどうかが判断され、前記第2硬判定データの誤り訂正が可能ではないと判断された場合、前記第2ワードラインに連結されたメモリセルから前記第2硬判定データに対する信頼性情報を有する第2軟判定データを読み出す第2軟判定読み出し動作が実行され、前記第2硬判定データが前記第2軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかにより第2再読み出しが選択的に実行されることができる。

## [0035]

10

20

30

20

30

40

50

一実施形態において、前記第1読み出し動作が複数の隣接したページから次々とデータを読み出す順次読み出し動作のうちの一つであるかどうかが判断され、前記第1読み出し動作が前記順次読み出し動作のうちの一つだと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行されることができる。

### [0036]

一実施形態において、前記第1読み出し動作が前記第1ワードラインに連結されたメモリセルを含むメモリブロックが消去された後最初に実行される読み出し動作なのかどうかが判断され、前記第1読み出し動作が前記メモリブロックが消去された後最初に実行される読み出し動作だと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行されることができる。

### [0037]

一実施形態において、前記最適読み出しレベルは前記不揮発性メモリ装置に含まれたメ モリブロック別に保存されることができる。

#### [0038]

一実施形態において、前記第1ワードラインが前記第1ワードラインに連結されたメモリセルを含むメモリブロックの端の領域に位置するのかどうかが判断され、前記第1ワードラインが前記メモリブロックの端の領域に位置されてないと判断された場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行されることができる。

#### [0039]

一実施形態において、前記第1ワードラインに連結されたメモリセルを含むメモリブロックの消去回数がカウントされ、前記カウントされた消去回数が所定の値と比較され、前記カウントされた消去回数が前記所定の値のうちの一つと一致する場合、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記第1再読み出しが実行されることができる。

### [0040]

前記他の目的を達成するために、本発明の実施形態による不揮発性メモリ装置は複数のメモリセルを含むメモリセルアレイ、およびワードラインに読み出し電圧を印加し前記複数のメモリセルのうち、前記ワードラインに連結されたメモリセルに対する第1読み出し動作を行い、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出するように再読み出しを行い、前記最適読み出しレベルを用い、後続の第2読み出し動作を行うように前記最適読み出しレベルを保存するように前記不揮発性メモリ装置を制御する制御回路を含む。

## [0041]

前記または他の目的を達成するために、本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの駆動方法において、前記メモリコントローラーが前記不揮発性メモリ装置に読み出しコマンドを転送し、前記不揮発性メモリ装置が前記読み出しコマンドに応答して、第1読み出し動作を行うことによって前記メモリコントローラーに前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記不揮発性メモリ装置に再読み出しコマンドを転送し、前記不揮発性メモリ装置が、最適読み出しレベルを用い、後続の第2読み出し動作を行うように、前記再読み出しコマンドに応答して再読み出しを行うことによって前記最適読み出しレベルを保存する。

### [0042]

前記または他の目的を達成するために、本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの駆動方法において、前記メモリコントローラーが前記不揮発性メモリ装置に読み出しおよび再読み出しコマンドを転送し、前記

20

30

40

50

不揮発性メモリ装置が前記読み出しおよび再読み出しコマンドに応答して、第1読み出し動作を行うことによって前記メモリコントローラーに前記第1読み出し動作により読み出されたデータを転送し、前記不揮発性メモリ装置が、最適読み出しレベルを用い、後続の第2読み出し動作を行うように、前記読み出しおよび再読み出しコマンドに応答して前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、再読み出しを行うことによって前記最適読み出しレベルを保存する。

### 【発明の効果】

## [0043]

前記のような本発明の実施形態による不揮発性メモリ装置のデータ読み出し方法、不揮発性メモリ装置、およびメモリシステムの駆動方法は、第1読み出し動作実行後前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出して前記最適読み出しレベルを後続の第2読み出し動作に利用することによって、不揮発性メモリ装置の平均読み出し時間および/または、平均読み出しレイテンシを減少させることができる。

### [0044]

ただし、本発明の効果は前記言及した効果に限定されることはなく、本発明の思想および領域から抜け出さない範囲で多様に拡張されるはずである。

### 【図面の簡単な説明】

[0045]

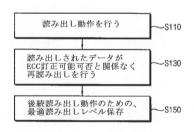

- 【図1】本発明の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフロー チャートである。

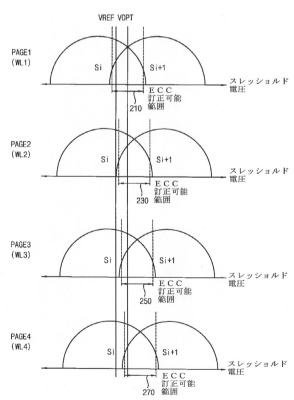

- 【図2】不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を 示す図面である。

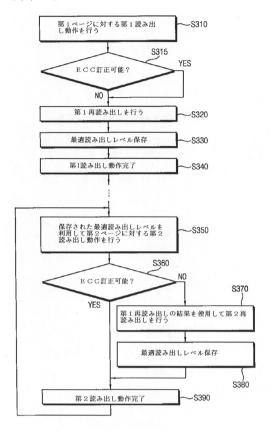

- 【図3】本発明の一実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートである。

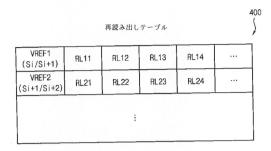

- 【図4】再読み出しの一例を説明するための図面である。

- 【図5】再読み出しの一例を説明するための図面である。

- 【図6】再読み出しの他の例を説明するための図面である。

- 【図7】図3のデータ読み出し方法で実行される第1再読み出しの一例を説明するための図面である。

- 【図8】図3のデータ読み出し方法で実行される第1再読み出しの一例を説明するための図面である。

- 【図9】図3のデータ読み出し方法で実行される第2再読み出しの一例を説明するための図面である。

- 【図10】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

- 【図11】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

- 【図12】2・ビット軟判定読み出し動作の一例を説明するための図面である。

- 【図13】3-ビット軟判定読み出し動作の一例を説明するための図面である。

- 【図14】3ビットマルチレベルセルを含む不揮発性メモリ装置で実行される軟判定読み出し動作の一例を説明するための図面である。

- 【図 1 5 】 3 ビットマルチレベルセルを含む不揮発性メモリ装置で実行される軟判定読み出し動作の一例を説明するための図面である。

- 【図16】3ビットマルチレベルセルを含む不揮発性メモリ装置で実行される軟判定読み出し動作の一例を説明するための図面である。

- 【図17】不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を示す図面である。

- 【図18】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

30

50

- 【図19】不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を示す図面である。

- 【図 2 0 】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートである。

- 【図21】順次読み出し動作およびランダム読み出し動作を説明するための図面である。

- 【図22】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートである。

- 【図23】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

- 【図24】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す 10 フローチャートである。

- 【図 2 5 】メモリブロック別に最適読み出しレベルを保存する不揮発性メモリ装置を説明するための図面である。

- 【図26】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

- 【図27】ワードラインの位置により最適読み出しレベルを保存する不揮発性メモリ装置を説明するための図面である。

- 【図28】本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

- 【図29】プログラムおよび消去回数によるスレッショルド電圧移動を示す図面である。

- 【図30】本発明の実施形態による不揮発性メモリ装置を示すブロック図である。

- 【図31】図30の不揮発性メモリ装置に含まれるメモリセルアレイの例を示す図面である。

- 【図32】図30の不揮発性メモリ装置に含まれるメモリセルアレイの例を示す図面である。

- 【図33】図30の不揮発性メモリ装置に含まれるメモリセルアレイの例を示す図面である。

- 【図34】本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの一例を示すブロック図である。

- 【図35】本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの他の例を示すブロック図である。

- 【図36】本発明の一実施形態によるメモリシステムの駆動方法を示すフローチャートである。

- 【図37】本発明の他の実施形態によるメモリシステムの駆動方法を示すフローチャートである。

- 【図38】本発明の実施形態によるメモリシステムがメモリカードに応用された例を示す 図面である。

- 【図39】本発明の実施形態によるメモリシステムがソリッドステートドライブに応用された例を示す図面である。

- 【図40】本発明の実施形態によるコンピューティングシステムを示すブロック図である 40

【発明を実施するための形態】

## [0046]

本文に記載されている本発明の実施形態に対して、特定の構造的乃至機能的説明は単に本発明の実施形態を説明するための目的で例示されているだけで、本発明の実施形態は多様な形態で実施され、また本文に説明された実施形態に限定されると解釈されてはならない。

## [0047]

本発明は多様な変更を加えることができ、多様な形態を有することができるところ、特定実施形態を図面に例示し、本文に詳細に説明している。しかし、これは本発明を特定の

開始形態に対して限定しようとするのではなく、本発明の思想および技術範囲に含まれる すべての変更、均等物乃至代替物を含むことで理解されなければならない。

## [0048]

第1、第2等の用語は多様な構成要素を説明する際に使われることができるが、前記構成要素は前記用語によって限定されてはならない。前記用語は一つの構成要素を異なる構成要素から区別する目的で使われることができる。例えば、本発明の権利範囲から離脱せずに第1構成要素は第2構成要素と命名されることができ、同様に第2構成要素も第1構成要素と命名されることができる。

#### [0049]

ある構成要素が異なる構成要素に「連結されて」あるとか「接続されて」あると言及された際には、その異なる構成要素に直接的に連結されているかまたは、接続されていることもできるが、間に異なる構成要素が存在することもできると理解されなければならないだろう。反面、ある構成要素が異なる構成要素に「直接連結されて」あるとか「直接接続されて」あると言及された際には、間に異なる構成要素が存在しないことで理解されなければならないだろう。構成要素の間の関係を説明する他の表現、すなわち「~間に」と「すぐに~間に」または「~に隣り合わせる」と「~に直接隣り合う」等も同じように解釈されなければならない。

### [0050]

本出願で使われた用語は単に特定の実施形態を説明するために使われ、本発明を限定しようとする意図ではない。単数の表現は文脈上明白に異なるように意味しない限り、複数の表現を含む。本出願で、「含む」または「有する」等の用語は説示された特徴、数字、段階、動作、構成要素、部分品または、これらを組み合わせたものが存在することを指定しようとすることであって、一つまたは、それ以上の他の特徴や数字、段階、動作、構成要素、部分品または、これらを組み合わせたものなどの存在または、付加の可能性を予め排除しないことで理解されなければならない。

## [0051]

別の方法で定義されていない限り、技術的や科学的な用語を含んでここで使われるすべての用語は本発明が属する技術分野で通常の知識を持った者によって一般的に理解されることと同じ意味である。一般的に使われる事前に定義されているような用語は関連技術の文脈上、有する意味と一致する意味だと解釈されるべきで、本出願で明白に定義しない限り、理想的や過度に形式的な意味と解釈されない。

## [0052]

一方、ある実施形態が異なる方法で実現可能である場合に特定ブロック内に明記された機能または、動作がフローチャートに明記された順序と異なるように起きることもある。 例えば、連続する二つのブロックが実際には実質的に同時に実行される事もでき、関連した機能または、動作により、は前記ブロックが逆に実行されることもできる。

# [0053]

以下、添付した図面を参照し、本発明の望ましい実施形態をより詳細に説明したい。図面上の同じ構成要素に対しては同じ参照符号を使って同じ構成要素に対して重複した説明は省略する。

# [0054]

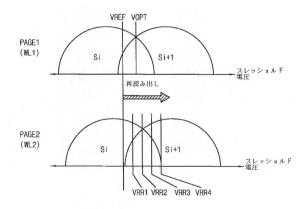

図 1 は本発明の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図 2 は不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を示す図面である。

### [0055]

図1および図2を参照すれば、不揮発性メモリ装置は第1ワードラインWL1に第1読み出し電圧VREFを印加し、第1ワードラインWL1に対応する第1ページPAGE1に対する第1読み出し動作を行う(S110)。すなわち、前記不揮発性メモリ装置は第1ワードラインWL1に所定の基準レベルを有する第1読み出し電圧VREFを印加することによって第1ワードラインWL1に連結されたメモリセルからデータを読み出すこと

10

20

30

40

ができる。

## [0056]

前記不揮発性メモリ装置は前記第1読み出し動作により読み出されたデータが誤り訂正符号ECC(Error Correction Code)による誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベル(誤り訂正可能読み出しレベルまたは、電圧)を検出するように再読み出しを行う(S130)。ここで、読み出されたデータの誤り訂正が可能である場合は、前記読み出されたデータがECCによって訂正可能で小さくても、一つの誤りを含む場合、および前記読み出されたデータが誤りを含まない場合を含む。一方、読み出されたデータの誤り訂正が可能である場合、前記再読み出しを遂行しない従来の不揮発性メモリ装置とは異なり、本発明の実施形態による前記不揮発性メモリ装置は、前記第1読み出し動作により読み出されたデータの誤り訂正が可能である場合でも、前記再読み出しを行い、前記最適読み出しレベルを検出することができる。

### [0057]

前記不揮発性メモリ装置は後続の第2読み出し動作のために前記再読み出しによって検出された前記最適読み出しレベルを保存することができる(S150)。すなわち、前記不揮発性メモリ装置は前記再読み出しによって検出された前記最適読み出しレベルを保存し、前記最適読み出しレベルを有する第2読み出し電圧VOPTを用い、後続の前記第2読み出し動作を行う。このように、後続の前記第2読み出し動作が前記最適読み出しレベルを有する第2読み出し電圧VOPTを用い、実行されるため、後続の前記第2読み出し動作の読み出し時間が減少することができる。

### [0058]

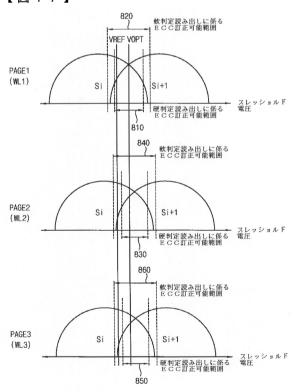

例えば、図2に示されているように、第1ワードラインWLに所定の基準レベルを有する第1読み出し電圧VREFを印加し第1ワードラインWLに連結されたメモリセルの二つの隣接した(例えば、第1および第2)状態Si及びSi+1を区分することによって、第1ワードラインWLに対応する第1ページPAGE1のデータを読み出す前記第1読み出し動作が実行されることができる。一方、第1読み出し電圧VREFの前記基準レベルが誤り訂正可能範囲210のうちにある場合、前記再読み出しが実行されなくても第1読み出し電圧VREFを用い、読み出された第1ページPAGE1のデータに誤り訂正(すなわち、ECCデコーディング)を行い、原本データが復元されることができる。しかし、本発明の実施形態によるデータ読み出し方法において、第1読み出し電圧VREFを用い、読み出された第1ページPAGE1のデータの誤り訂正が可能である場合でも、前記最適読み出しレベルを検出および保存するように前記再読み出しが実行されることができる。

## [0059]

例えば、第2ワードラインWL2に前記最適読み出しレベルを有する第2読み出し電圧 VOPTを印加し第2ワードラインWL2に対応する第2ページPAGE2に対する後続 の前記第2読み出し動作が実行されることができる。

## [0060]

この際、第1読み出し電圧VREFの前記基準レベルが第2ページPAGE2に対する誤り訂正可能範囲230から抜け出して、第2読み出し電圧VOPTの前記最適読み出しレベルは第2ページPAGE2に対する誤り訂正可能範囲230のうちでもよい。この場合、従来の不揮発性メモリ装置では、第1読み出し電圧VREFを用い、読み出された第1ページPAGE1のデータの誤り訂正が可能である場合、前記再読み出しが実行されないため、第2ページPAGE2に対する後続の前記第2読み出し動作もまた、第1読み出し電圧VREFを用い、実行され、前記第2読み出し動作により読み出された第2ページPAGE2のデータは誤り訂正が可能ではないこともある。しかし、本発明の実施形態による不揮発性メモリ装置では、第2ページPAGE2に対する前記第2読み出し動作が前記最適読み出しレベルを有する第2読み出し電圧VOPTを用い、実行されるため、前記第2読み出し動作により読み出された第2ページPAGE2のデータは誤り訂正ができる

10

20

30

40

20

30

40

50

可能性がある。それに伴い、本発明の実施形態による不揮発性メモリ装置で後続の前記第2読み出し動作の読み出し時間、および読み出しコマンドの印加時点からデータが出力される時点までの読み出しレイテンシ(Read Latency)が減少することができる。

## [0061]

また、第3および第4ワードラインWL3及びWL4に前記最適読み出しレベルを有する第2読み出し電圧VOPTを印加し第3および第4ワードラインWL3及びWL4に対応する第3および第4ページPAGE3及びPAGE4に対する後続の読み出し動作がそれぞれ実行されることができる。この際、第1読み出し電圧VREFの前記基準レベルが第3および第4ページPAGE3及びPAGE4に対する誤り訂正可能範囲250及び270から抜け出して、第2読み出し電圧VOPTの前記最適読み出しレベルは第3および第4ページPAGE3及びPAGE4に対する誤り訂正可能範囲250及び270のうちでもよい。この場合、前記後続の読み出し動作により読み出された第3および第4ページPAGE3及びPAGE4のデータは誤り訂正ができる可能性がある。それに伴い、本発明の実施形態による不揮発性メモリ装置で前記後続の読み出し動作の読み出し時間および読み出しレイテンシ(Read Latency)が減少することができる。

## [0062]

上述したように、本発明の実施形態による不揮発性メモリ装置のデータ読み出し方法において、読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、(別に)前記最適読み出しレベル(または、誤り訂正可能読み出しレベル)を検出することによって、前記最適または、誤り訂正可能読み出しレベルを用い、後続の読み出し動作が実行されることができる。それに伴い、前記後続の読み出し動作により読み出されたデータは誤り訂正が可能であり、前記後続の読み出し動作の読み出し時間および読み出しレイテンシが減少することによって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0063]

一方、図 2 には前記メモリセルの状態 S i 及び S i + 1 として二つの状態 S i 及び S i + 1 が図示されているが、本発明の実施形態による前記不揮発性メモリ装置の前記メモリセルは二つまたは、それ以上の状態を有することができる。一実施形態において、前記メモリセルはそれぞれ一つのデータビットを保存するように二つの状態のうちの一つを有するシングルレベルメモリセル S L C (Single Level memory Cell)でもよい。他の実施形態で、前記メモリセルはそれぞれ複数のデータビットを保存するように3つ以上の状態を有するマルチレベルメモリセルMLC (Multi Level memory Cell)でもよい。

## [0064]

図3は本発明の一実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図4および図5は再読み出しの一例を説明するための図面などで、図6は再読み出しの他の例を説明するための図面で、図7および図8は図3のデータ読み出し方法で実行される第1再読み出しの一例を説明するための図面で、図9は図3のデータ読み出し方法で実行される第2再読み出しの一例を説明するための図面である。

# [0065]

図3を参照すれば、不揮発性メモリ装置は第1ページに対する第1読み出し動作を行う(S310)。例えば、前記不揮発性メモリ装置は第1ワードラインに所定の基準レベルを有する第1読み出し電圧を印加し、前記第1ワードラインに対応する前記第1ページに対する前記第1読み出し動作を行う。前記不揮発性メモリ装置は前記第1読み出し動作により読み出された前記第1ページのデータがリコントローラーは前記第1読み出し動作により読み出された前記第1ページのデータがECCによって誤り訂正が可能であるかどうかを判断することができる(S315)。

### [0066]

前記不揮発性メモリ装置は前記第1読み出し動作により読み出された前記第1ページの

20

30

40

50

データがECCによって誤り訂正が可能であるかどうかとは関係なく、(別に)最適読み出しレベルを検出する第1再読み出しを行う(S320)。すなわち、前記不揮発性メモリ装置は、前記第1読み出し動作により読み出された前記第1ページのデータがECCによって誤り訂正が可能でなくても前記第1再読み出しを行い、(S315(No)及びS320)、前記第1読み出し動作により読み出された前記第1ページのデータがECCによって誤り訂正が可能である場合でも前記第1再読み出しを行う(S315(Yes)及びS320)。

## [0067]

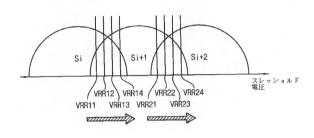

例えば、前記不揮発性メモリ装置は、図4および図5に示されているように、再読み出 しテーブル400に保存された読み出しレベルRL11~RL14及びRL21~RL2 4 を有する再読み出し電圧 V R R 1 1 ~ V R R 1 4 、 V R R 2 1 ~ V R R 2 4 を次々と利 用することによって、前記第1再読み出しを行う。例えば、再読み出しテーブル400に はメモリセルの第1状態Siと第2状態Si+1の区分のための第1基準読み出し電圧V REF1の第1読み出しレベルRL11及びRL14、およびメモリセルの第2状態Si + 1 と第 3 状態 S i + 2 の区分のための第 2 基準読み出し電圧 V R E F 2 の第 2 読み出し レベルRL21~RL24が保存されることができる。前記不揮発性メモリ装置は、読み 出されたデータがECCによって誤り訂正可能な時まで、前記第1ワードラインに第1読 み出しレベルRL11及びRL14を有する再読み出し電圧VRR11~VRR14を次 々と印加し第1状態Siと第2状態Si + 1 の区分のための第1基準読み出し電圧VRE F1の前記最適読み出しレベルを検出することができる。すなわち、前記不揮発性メモリ 装置は第1読み出しレベルRL11及びRL14のうちECCによって誤り訂正可能なデ ータが読み出しなる時印加された再読み出し電圧の読み出しレベルを第1基準読み出し電 圧VREF1の前記最適読み出しレベルで決めることができる。また、前記不揮発性メモ リ装置は、読み出されたデータがECCによって誤り訂正可能な時まで、前記第1ワード ラインに第2読み出しレベルRL21~RL24を有する再読み出し電圧VRR21~V RR24を次々と印加し第2状態Si+1と第3状態Si+2の区分のための第2基準読 み出し電圧VREF2の前記最適読み出しレベルを検出することができる。

### [0068]

一方、図4および図5には再読み出し電圧VRR11~VRR14の第1読み出しレベルRL11及びRL14が次々と増加して、再読み出し電圧VRR21~VRR24の第2読み出しレベルRL21~RL24が次々と増加する例が図示されているが、再読み出しテーブル400に保存された第1読み出しレベルRL11及びRL14および第2読み出しレベルRL21~RL24は次々と増加または、減少しない任意の電圧レベルでもよい。例えば、第1読み出しレベルRL11及びRL14のうち2番目に印加される再読み出し電圧VRR12の読み出しレベルRL11及びRL14のうち、最初に印加される再読み出し電圧VRR11の読み出しレベルRL11なびRL11の方ちの3番目に印加される再読み出し電圧VRR13の読み出しレベルRL13は第1読み出しレベルRL11及びRL11の方ちの3番目に印加される再読み出し電圧VRR12の読み出しレベルRL11とり増加または、減少することができる。

# [0069]

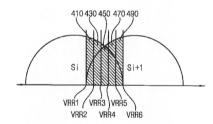

他の例で、前記不揮発性メモリ装置は、図6に示されているように、一定の間隔を有する複数の再読み出し電圧VRR1~VRR6の間のスレッショルド電圧を有するメモリセル410、430、450、470、490の数をカウントして前記最適検出レベルを検出する前記第1再読み出しを行う。例えば、第2再読み出し電圧VRR2の印加時のオン・セルの数で第1再読み出し電圧VRR1の印加時のオン・セルの数を減算し、第1再読み出し電圧VRR1と第2再読み出し電圧VRR2の間のスレッショルド電圧を有するメモリセル410の数をカウントし、第3再読み出し電圧VRR3の印加時のオン・セルの数で第2再読み出し電圧VRR2の印加時のオン・セルの数を減算し、第2再読み出し電圧VRR2と第3再読み出し電圧VRR3の間のスレッショルド電圧を有するメモリセル

430の数をカウントし、第4再読み出し電圧VRR4の印加時のオン・セルの数で第3再読み出し電圧VRR3の印加時のオン・セルの数を減算し、第3再読み出し電圧VRR3の印加時のオン・セルの数で第4再読み出し電圧VRR4の間のスレッショルド電圧を有するメモリセル450の数をカウントし、第5再読み出し電圧VRR5の印加時のオン・セルの数で第4再読み出し電圧VRR4と第5再読み出し電圧VRR5の間のスレッショルド電圧を有するメモリセル470の数をカウントし、第6再読み出し電圧VRR6の印加時のオン・セルの数を減算し、第5再読み出し電圧VRR5と第6再読み出し電圧VRR5の印加時のオン・セルの数を減算し、第5再読み出し電圧VRR5と第6再読み出し電圧VRR6の間のスレッショルド電圧を有するメモリセル490の数をカウントすることができる。前記不揮発性メモリ装置はカウントされたメモリセル410、430、450、470、490の数のうち、最小個数のメモリセル450のスレッショルド電圧レベルを前記最適読み出しレベルで決めることができる。

[0070]

一方、図4および図5には再読み出しテーブル400を利用する再読み出しを行う例が図示されていて、図6には再読み出し電圧の間のスレッショルド電圧を有するメモリセルの数をカウントする再読み出しを行う例が図示されているが、本発明の実施形態によるデータ読み出し方法で実行される再読み出しはこれに対しは限定されず、多様な方式で実行されることができる。例えば、一実施形態において、前記不揮発性メモリ装置はモニタリングセルを用い、メモリセルのスレッショルド電圧分布を検出して、前記検出されたスレッショルド電圧分布を用い、前記再読み出しを行う。

[0071]

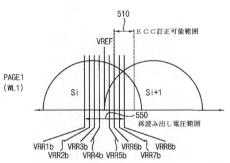

一実施形態において、前記不揮発性メモリ装置は前記第1読み出し動作により読み出さ れた前記第1ページのデータがECCによって誤り訂正が可能であるかどうかによりそれ ぞれ異なる範囲の再読み出し電圧を用い、前記第1再読み出しを行う。例えば、図8に示 されているように、第1読み出し電圧VREFの前記基準レベルが誤り訂正可能範囲51 0 を抜け出した場合、前記第 1 読み出し動作により読み出されたデータの誤り訂正が可能 ではないこともある。この場合、前記不揮発性メモリ装置は第1範囲550を有する再読 み出し電圧VRR1b~VRR8bを用い、前記第1再読み出しを行う。例えば、前記不 揮発性メモリ装置は、図4および図5に示されているように読み出されたデータが誤り訂 正可能な時まで第1ワードラインWL1に再読み出し電圧VRR1b~VRR8bを次々 と印加し前記第1再読み出しを行うかまたは、図6に示されているように再読み出し電圧 VRR1b~VRR8bの間のスレッショルド電圧を有するメモリセルの数をカウントす ることによって前記第1再読み出しを行う。また、図7に示されているように、第1読み 出し電圧VREFの前記基準レベルが誤り訂正可能範囲510のうちにある場合、前記第 1 読み出し動作により読み出されたデータの誤り訂正ができる可能性がある。一方、前記 第1読み出し動作により読み出されたデータの誤り訂正が可能である場合、前記第1読み 出し動作により読み出されたデータの誤り訂正が可能ではない場合と比べ、第1読み出し 電圧VREFの前記基準レベルが前記最適読み出しレベルに相対的に周辺でもよい。それ に伴い、前記不揮発性メモリ装置は第1範囲550より狭い第2範囲530を有する再読 み出し電圧VRR1a~VRR4aを用いて前記第1再読み出しを行う。例えば、前記不 揮発性メモリ装置は、図4および図5に図示された方式、図6に図示された方式、または 、他の方式で前記第1再読み出しを行う。一方、一実施形態において、前記第1読み出し 動作により読み出されたデータの誤り訂正が可能である場合、前記不揮発性メモリ装置は 前記第1読み出し動作により読み出されたデータの誤り訂正が可能ではない場合の再読み 出し電圧VRR1b~VRR8bの数より少ない数の再読み出し電圧VRR1a~VRR 4 a を用い、前記第1再読み出しを行うことによって、前記第1再読み出し時間を減少さ せることができる。他の実施形態で、前記第1読み出し動作により読み出されたデータの 誤り訂正が可能である場合の再読み出し電圧VRR1a~VRR4aは前記第1読み出し 動作により読み出されたデータの誤り訂正が可能ではない場合の再読み出し電圧VRR1 b~VRR8bより狭い間隔を有することができる。

20

10

30

40

20

30

40

50

### [0072]

これに対し、他の実施形態で、前記不揮発性メモリ装置は、前記第1読み出し動作により読み出された前記第1ページのデータがECCによって誤り訂正が可能である場合、および誤り訂正が可能ではない場合で、同じ範囲の再読み出し電圧を用い、前記第1再読み出しを行う。

## [0073]

前記不揮発性メモリ装置は前記最適読み出しレベルを用い、後続の第2読み出し動作を 行うように前記第1再読み出しによって検出された前記最適読み出しレベルを保存するこ とができる(S330)。一方、前記メモリコントローラーは、前記第1読み出し動作に より読み出された前記第1ページのデータが誤り訂正可能である場合、前記第1ページの データに誤り訂正(すなわち、ECCデコーディング)を行い、原本データを復元でき、 前記第1読み出し動作により読み出された前記第1ページのデータが誤り訂正可能ではな い場合、前記第1再読み出しによって読み出された前記第1ページのデータに誤り訂正を 行い、原本データを復元することができる。一実施形態において、前記メモリコントロー ラーはBCH(Bose-Chaudhuri-Hocguenghem)符号を用い、 前記第1読み出し動作または、前記第1再読み出しによって読み出された前記第1ページ のデータに対する前記誤り訂正を行う。他の実施形態で、前記メモリコントローラーはタ ーボ符号(Turbo code)、リード・ソロモン符号(read-Solomon Code)、コンボルリューション符号(Convolution Code)、RSC (RecurSive Systematic Code)、TCM(Trellis-C oded Modulation)、BCM(Block Coded Modulati on)等の符号化された変調(Coded Modulation)、または、異なる誤 り訂正符号を用い、前記誤り訂正を行う。それに伴い、前記第1ページのデータを読み出 す前記第1読み出し動作が完了することができる(S340)。

### [0074]

前記第1読み出し動作が完了した後、ホストは前記メモリコントローラーに第2ページのデータを求めることができ、前記メモリコントローラーは前記不揮発性メモリ装置に前記第2ページのデータの読み出しを求めるコマンドを転送することができる。前記不揮発性メモリ装置は前記保存された最適読み出しレベルを用い、前記第2ページに対する第2読み出し動作を行う(S350)。例えば、前記不揮発性メモリ装置は第2ワードラインに連結されたメモリセルを含む前記第2ページに対する前記第2読み出し動作を行う。

## [0075]

前記第2読み出し動作により読み出された前記第2ページのデータの誤り訂正が可能で あるかどうかを判断することができて(S360)、前記第2読み出し動作により読み出 された前記第2ページのデータの誤り訂正が可能であるかどうかにより第2再読み出しを 選択的に行う(S360及びS370)。すなわち、前記不揮発性メモリ装置は、前記第 2 読み出し動作により読み出された前記第 2 ページのデータの誤り訂正が可能であると判 断された場合(S360(Yes))、前記第2再読み出しを行わず、前記第2読み出し 動作を完了でき(S390)、前記第2読み出し動作により読み出された前記第2ページ のデータの誤り訂正が可能ではないと判断された場合(S360(No)、前記第2再読 み出しを行う( S 3 7 0 )。例えば、前記不揮発性メモリ装置は、図 4 および図 5 に図示 された方式、図6に図示された方式、または、他の方式で前記第2再読み出しを行う。一 方、前記第2再読み出しが実行された場合、前記不揮発性メモリ装置は後続読み出し動作 に利用するように前記第2再読み出しによって検出された新しい最適読み出しレベルを保 存することができる(S380)。一方、本発明の一実施形態によるデータ読み出し方法 において、前記第2読み出し動作が前記第1再読み出しによって検出された前記最適検出 レベルを用い、実行されるため、従来のデータ読み出し方法に比べて前記第2読み出し動 作により読み出された前記第2ページのデータの誤り訂正が可能である場合が発生する確 率が増加することができ、それに伴い、前記第2再読み出しが実行されないことによって

前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0076]

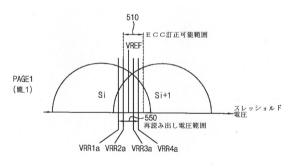

一実施形態において、前記不揮発性メモリ装置は前記第1再読み出しの結果を用い、前 記第2再読み出しを行う。例えば、前記第2再読み出しは第1読み出し電圧VREFの電 圧レベルと前記第1再読み出しによって検出された前記最適読み出しレベルの関係に基づ き、実行されることができる。一実施形態において、図9に示されているように、前記第 1 再読み出しの結果として前記第 1 読み出し動作時印加された第 1 読み出し電圧VREF の電圧レベルより高い前記最適読み出しレベルが検出された場合、前記第2再読み出しは 第2ワードラインWL2に第1読み出し電圧VREFの電圧レベルより高い電圧レベルを 有する再読み出し電圧VRR1~VRR4を印加し実行されることができる。また、前記 第1再読み出しの結果として前記第1読み出し動作時印加された第1読み出し電圧VRE Fの電圧レベルより低い前記最適読み出しレベルが検出された場合、前記第 2 再読み出し は第2ワードラインWL2に第1読み出し電圧VREFの電圧レベルより低い電圧レベル を有する再読み出し電圧を印加し実行されることができる。他の実施形態で、第1読み出 し電圧VREFの電圧レベルより高い前記最適読み出しレベルが検出された場合、前記第 2 再読み出しは第 2 ワードラインWL 2 に前記最適読み出しレベルより高い電圧レベルを 有する再読み出し電圧を印加し実行されることができ、第1読み出し電圧VREFの電圧 レベルより低い前記最適読み出しレベルが検出された場合、前記第2再読み出しは第2ワ ードラインWL2に前記最適読み出しレベルより低い電圧レベルを有する再読み出し電圧 を印加し実行されることができる。このように、前記第1再読み出しの結果を用い、前記 第2再読み出しが実行されることによって、前記第2再読み出し時間が減少することがで きる。

#### [0077]

一方、前記メモリコントローラーは、前記第2読み出し動作により読み出された前記第2ページのデータが誤り訂正可能である場合、前記第2ページのデータに誤り訂正(すなわち、ECCデコーディング)を行い、原本データを復元でき、前記第2読み出し動作により読み出された前記第2ページのデータが誤り訂正可能ではない場合、前記第2再読み出しによって読み出された前記第2ページのデータに誤り訂正を行い、原本データを復元することができる。それに伴い、前記第2ページのデータを読み出す前記第2読み出し動作が完了することができる(S390)。また、前記不揮発性メモリ装置は前記第1再読み出しまたは、前記第2再読み出しによって検出された前記最適読み出しレベルを用い、後続の読み出し動作をより一層行う(S350)。

## [0078]

上述したように、本発明の一実施形態による不揮発性メモリ装置のデータ読み出し方法において、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記最適読み出しレベルを検出することによって、前記最適読み出しレベルを用い、少なくとも一つの後続の第2読み出し動作が実行されることができる。それに伴い、後続の読み出し動作により読み出されたデータは誤り訂正が可能であり、前記後続の読み出し動作の読み出し時間および読み出しレイテンシが減少することによって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

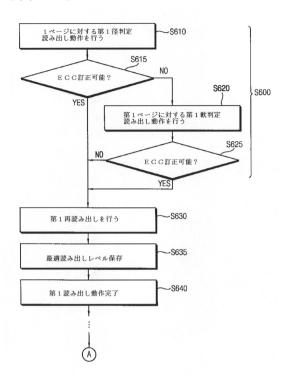

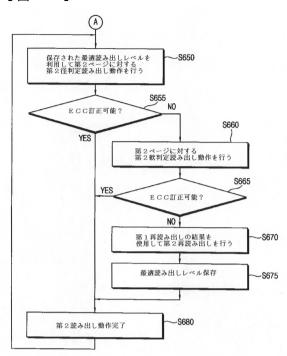

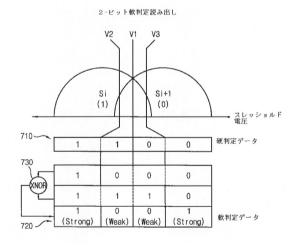

## [0079]

図10および図11は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図12は2・ビット軟判定読み出し動作の一例を説明するための図面であり、図13は3・ビット軟判定読み出し動作の一例を説明するための図面で、図14乃至図16は3ビットマルチレベルセルを含む不揮発性メモリ装置で実行される軟判定読み出し動作の一例を説明するための図面などで、図17は不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を示す図面である。

## [0800]

10

20

30

20

30

40

50

図10および図11を参照すれば、不揮発性メモリ装置は第1ページに対する第1読み出し動作を行う(S600)。一実施形態において、前記不揮発性メモリ装置によって実行される読み出し動作は硬判定(Hard Decision)読み出し動作および/または、軟判定(Soft DeciSion)読み出し動作を含むことができる。前記硬判定読み出し動作はワードラインに所定の基準レベルを有する読み出し電圧を印加し前記ワードラインに連結されたメモリセルの(例えば、論理「0」または、論理「1」を示す)オン/オフ状態により前記メモリセルから硬判定データを読み出す動作として、メモリコントローラーは前記硬判定データと誤り訂正符号(例えば、LDPC(Low DenSity Parity Check)符号)のみを用い、硬判定方式の誤り訂正を行う。また、前記軟判定読み出し動作は前記ワードラインに一定の間隔を有する複数の読み出し生を印加し前記ワードラインに連結されたメモリセルから前記硬判定データに対する信頼性情報を有する(例えば、検出されたビットが「0」または「1」である確率を示す)軟判定データを読み出す動作として、前記メモリコントローラーは前記硬判定データおよび前記誤り訂正符号(例えば、LDPC符号)とともに前記硬判定データに対する信頼性情報を用い、軟判定方式の誤り訂正を行う。

#### [0081]

例えば、前記不揮発性メモリ装置は前記第1ページに対する第1読み出し動作を行うように、前記第1ページの第1硬判定データを読み出す第1硬判定読み出し動作を行う(S610)。前記不揮発性メモリ装置は第1ワードラインに所定の基準レベルを有する第1読み出し電圧を印加し前記第1ワードラインに連結されたメモリセルを含む前記第1ページから前記第1硬判定データを読み出す前記第1硬判定読み出し動作を行う。前記不揮発性メモリ装置は前記第1硬判定読み出し動作により読み出された前記第1ページの前記第1硬判定データを前記メモリコントローラーに出力でき、前記メモリコントローラーは前記第1硬判定読み出し動作により読み出された前記第1ページの前記第1硬判定データがECCによって誤り訂正が可能であるかどうかを判断することができる(S615)。

## [0082]

前記第1ページの前記第1硬判定データがECCによって誤り訂正が可能ではない場合(S615(No))、前記不揮発性メモリ装置は前記第1硬判定データに対する信頼性情報を有する前記第1ページの第1軟判定データを読み出す第1軟判定読み出し動作を行う(S620)。前記不揮発性メモリ装置は前記第1ワードラインに一定の間隔を有する複数の電圧を印加し前記第1ワードラインに連結されたメモリセルを含む前記第1ページから前記第1硬判定データに対する信頼性情報を有する前記第1軟判定データを読み出すことができる。

## [0083]

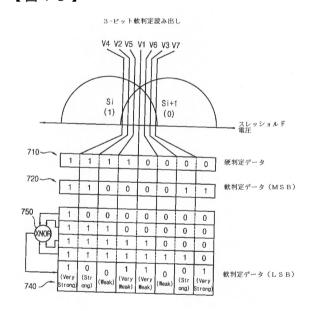

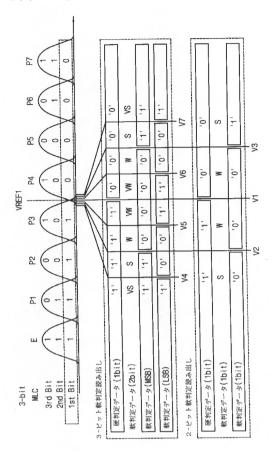

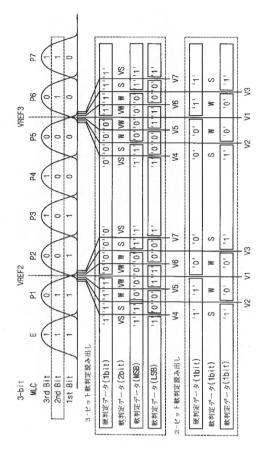

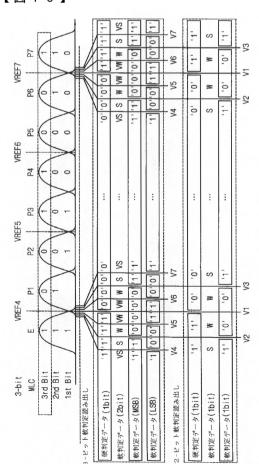

例えば、図12に示されているように、前記不揮発性メモリ装置は2-ビット軟判定読 み出し動作を行う。前記2・ビット軟判定読み出し動作は一定の間隔を有する3つの電圧 V1~V3を利用する3つの読み出し動作を含むことができる。例えば、3つの電圧V1 ~ V 3 はデータ「 1 」に対応する第 1 状態 S i とデータ「 0 」に対応する第 2 状態 S i + 1の区分のための所定の基準レベルを有する第1電圧V1、第1電圧V1より所定のレベ ルぐらい低い第2電圧V2、および第1電圧V1より前記所定のレベルぐらい高い第3電 圧 V 3 を含むことができる。一つ、前記基準レベルを有する第1電圧 V 1 を用い、読み出 しされるデータ710は硬判定読み出し動作により読み出された硬判定データ710であ って、前記2-ビット軟判定読み出し動作は前記基準レベルを有する第1電圧V1の印加 なしで前記硬判定読み出し動作により読み出された硬判定データ710を活用することが できる。前記2-ビット軟判定読み出し動作は第2電圧V2を用い、読み出されたデータ および第3電圧V3を用い、読み出されたデータに所定の論理演算(例えば、XNOR演 算730)(または、エンコーディング(Encoding))を行い、硬判定データ7 10に対する信頼性情報を有する軟判定データ720を生成することができる。軟判定デ ータ720の各ビットは硬判定データ710の対応するビットの信頼性の程度を示すこと ができ、例えば、値が「1」である軟判定データ720のビットは硬判定データ710の 対応するビットが高い(Strong(S))信頼性を有することを示し、値が「0」である軟判定データ720のビットは硬判定データ710の対応するビットが低い(Weak(W))信頼性を有することを示すことができる。

## [0084]

他の例で、図13に示されているように、前記不揮発性メモリ装置は3‐ビット軟判定 読み出し動作を行う。前記3-ビット軟判定読み出し動作は一定の間隔を有する七個の電 圧V1~V7を利用する七個の読み出し動作を含むことができる。例えば、7個の電圧V 1~V7は前記2・ビット軟判定読み出し動作において、使われる3つの電圧V1~V3 と共に第2電圧 V 2 より低い第4電圧 V 4、第2電圧 V 2 と第1電圧 V 1 の間の第5電圧 V 5 、第 1 電圧 V 1 と第 3 電圧 V 3 の間の第 6 電圧 V 6 、および第 3 電圧 V 3 より高い第 7電圧Vフを含むことができる。第1電圧V1を用い、読み出しされるデータ710は前 記硬判定読み出し動作により読み出された硬判定データ710でもよい。また、第2およ び第3電圧V2及びV3を用い、読み出しされるデータ720は上位ビットMSB軟判定 データ 7 2 0 として前記 2 - ビット軟判定読み出し動作により、読み出しされる軟判定デ ータ720に対応することができる。前記3-ビット軟判定読み出し動作は第4電圧V4 、第5電圧V5、第6電圧V6および第7電圧V7を用い、読み出されたデータに所定の 論理演算(例えば、XNOR演算750)(または、エンコーディング(Encodin g))を行い、下位ビットLSB軟判定データ740を生成することができる。二つのビ ットを有する各軟判定データ720及び740は対応する硬判定データ710の信頼性の 程度を示すことができ、例えば、値が「11」である各軟判定データ720及び740は 対応する硬判定データ710が非常に高い(Verv Strong(VS))信頼性を 有することを示し、値が「10」である各軟判定データ720及び740は対応する硬判 定データ710が高い(Strong(S))信頼性を有することを示し、値が「00」 である各軟判定データフ20及び740は対応する硬判定データフ10が低い(Weak (W))信頼性を有することを示し、値が「01」である各軟判定データ720及び74 0は対応する硬判定データ710が非常に低い(Very Weak (VW))信頼性を 有することを示すことができる。

### [0085]

一方、図12および図13には二つの隣接した状態Si及びSi+1が図示されている が、図12および図13に図示された2-ビット軟判定読み出し動作および3-ビット軟 判定読み出し動作は複数の状態のうち、二つに隣接した状態を区分するように実行される ことができる。例えば、前記メモリセルがセル当り3ビットのデータを保存するように8 個の状態E及びP1~P7を有する3-ビットMLCである場合、前記不揮発性メモリ装 置は図14乃至図16に図示された方式で2-ビット軟判定読み出し動作または、3-ビ ット軟判定読み出し動作を行う。図14には第1基準読み出し電圧VREF1を用い、3 - ビットMLCに保存された第1ビット(例えば、LSB)のデータを読み出す際、実行 される2-ビット軟判定読み出し動作の例および3-ビット軟判定読み出し動作の例が図 示されていて、図15には第2および第3基準読み出し電圧VREF2及びVREF3を 用い、3-ビットMLCに保存された第2ビット(例えば、CSB)のデータを読み出す 際、実行される2-ビット軟判定読み出し動作の例および3-ビット軟判定読み出し動作 の例が図示されていて、図16には第4乃至第7基準読み出し電圧VREF4及びREF 7を用い、3‐ビットMLCに保存された第3ビット(例えば、MSB)のデータを読み 出す際、実行される2-ビット軟判定読み出し動作の例および3-ビット軟判定読み出し 動作の例が図示されている。

### [0086]

前記不揮発性メモリ装置は前記第1軟判定読み出し動作により読み出された前記第1ページの前記第1軟判定データを前記メモリコントローラーに出力でき、前記メモリコントローラーは前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかを判断することができる(S625)。

# [ 0 0 8 7 ]

10

20

30

20

30

40

50

前記不揮発性メモリ装置は前記第1硬判定データが(前記信頼性情報なまたは、前記第1 軟判定データの前記信頼性情報に基づき)誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出する第1再読み出しを行う(S630)。すなわち、前記不揮発性メモリ装置は前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能ではない場合だけでなく(S625(No))、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかまたは(S615(Yes))、前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能である場合でも(S625(Yes))、前記第1再読み出しを行う(S630)。一実施形態において、前記第1再読み出しで使われる再読み出し電圧のうち少なくとも一部は第1軟判定読み出し動作において、使われる一定の間隔を有する複数の電圧のうち少なくとも一部に対応でき、前記第1再読み出しは前記第1軟判定データの少なくとも一部をくとも一部に対応できる。

## [0088]

一実施形態において、前記不揮発性メモリ装置は前記第1硬判定データが前記信頼性情 報なしで誤り訂正が可能であるかどうかおよび前記第1硬判定データが前記第1軟判定デ ータの前記信頼性情報に基づき、誤り訂正が可能であるかどうかによりそれぞれ異なる範 囲の再読み出し電圧を用い、前記第1再読み出しを行う。例えば、前記不揮発性メモリ装 置は前記第1硬判定データが前記第1軟判定データの前記信頼性情報に基づき、誤り訂正 が可能ではないと判断された場合(S625(No))、第1範囲を有する第1再読み出 し電圧を用い、前記第1再読み出しを行う。一方、前記第1硬判定データが前記第1軟判 定データの前記信頼性情報に基づき、誤り訂正が可能である場合、前記第1硬判定データ が前記第1軟判定データの前記信頼性情報に基づき、誤り訂正が可能ではない場合と比べ 、前記第1読み出し電圧の前記基準レベルが前記最適読み出しレベルに相対的に周辺でも よい。それに伴い、前記不揮発性メモリ装置は前記第1硬判定データが前記第1軟判定デ ータの前記信頼性情報に基づき、誤り訂正が可能であると判断された場合( S 6 2 5 ( Y es))、前記第1範囲より狭い第2範囲を有する第2再読み出し電圧を用い、前記第1 再読み出しを行う。また、前記第1硬判定データが前記信頼性情報なしで誤り訂正が可能 である場合、前記第1硬判定データが前記信頼性情報なしで誤り訂正が可能ではない場合 と比べ、前記第1読み出し電圧の前記基準レベルが前記最適読み出しレベルに相対的に周 辺でもよい。それに伴い、前記不揮発性メモリ装置は前記第1硬判定データが前記信頼性 情報なしで誤り訂正が可能であると判断された場合(S615(Yes))、前記第2範 囲より狭い第3範囲を有する第3再読み出し電圧を用い、前記第1再読み出しを行う。ま た、一実施形態において、前記第3再読み出し電圧の数は前記第2再読み出し電圧の数よ り少なく、前記第2再読み出し電圧の数は前記第1再読み出し電圧の数より少ないことも ある。

### [0089]

前記不揮発性メモリ装置は前記最適読み出しレベルを用い、後続の第2読み出し動作を行うように前記第1再読み出しによって検出された前記最適読み出しレベルを保存することができる(S635)。一方、前記メモリコントローラーは誤り訂正符号、前記第1 軟判定データを用い、硬判定方式または、軟判定方式の誤り訂正を行う。例えば、前記メモリコントローラーは、前記第1 硬判定データを開い、前記第1 硬判定データを用い、前記第1 である場合(S615 (Yes))、前記誤り訂正が可能である場合(S615 (Yes))、前記誤り可で表示できるによって原本データを行うことによって原本データで記憶が可能である場合(S625 (Yes))、前記誤り訂正符号、前記第1 硬判定データが前記第1 軟判定データが前記第1 できることができるし、前記第1 できることができるし、前記第1 できることができるし、前記第1 でまりでである場合(S625 (No))、第1 再読み出しによって読み出された前記第1 ページの硬判定

データおよび/または、軟判定データに硬判定方式または、軟判定方式の誤り訂正を行うことによって原本データを復元することができる。それに伴い、前記第1ページのデータを読み出す前記第1読み出し動作が完了することができる(S640)。一実施形態において、前記硬判定方式または、前記軟判定方式の誤り訂正で使われる前記誤り訂正符号はLDPC(Low DenSity Parity Check)符号でもよい。

### [0090]

前記第1読み出し動作が完了した後、ホストは前記メモリコントローラーに第2ページのデータを求めることができ、前記メモリコントローラーは前記不揮発性メモリ装置に前記第2ページのデータの読み出しを求めるコマンドを転送することができる。前記不揮発性メモリ装置は前記コマンドに応答して前記第2ページに対する第2読み出し動作を行う(S650、S655、S660、S665、S670、S675、S680)。前記第2読み出し動作は第2硬判定読み出し動作および/または、第2軟判定読み出し動作を含むことができる。

## [0091]

例えば、前記不揮発性メモリ装置は前記第2ページに対する前記第2読み出し動作を行うように、前記保存された最適読み出しレベルを用い、前記第2ページの第2硬判定データを読み出す第2硬判定読み出し動作を行う(S650)。例えば、前記不揮発性メモリ装置は第2ワードラインに前記最適読み出しレベルを有する第2読み出し電圧を印加し前記第2ワードラインに連結されたメモリセルを含む前記第2ページに対する前記第2硬判定読み出し動作を行う。

## [0092]

前記第2硬判定読み出し動作により読み出された前記第2硬判定データが信頼性情報なしで誤り訂正が可能であるかどうかが判断されることができる(S655)。前記不揮発性メモリ装置は前記第2硬判定データの誤り訂正が可能ではないと判断された場合(S655(No))、前記第2ワードラインに連結されたメモリセルを含む前記第2ページから前記第2硬判定データに対する信頼性情報を有する第2軟判定データを読み出す第2軟判定読み出し動作を行う(S660)。前記第2硬判定データが前記信頼性情報なしで誤り訂正が可能であると判断された場合(S655(Yes))、前記不揮発性メモリ装置は前記第2軟判定読み出し動作を行うことができないことがある。

# [0093]

### [0094]

このように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、後続の前記第2読み出し動作時、前記第2ページのデータ(すなわち、前記第2硬判定データ)が前記第2硬判定読み出し動作のみで訂正可能ではない場合にだけ(S65(No))、前記第2軟判定読み出し動作が実行される。また、後続の前記第2読み出し動作時、前記第2ページのデータが前記第2硬判定読み出し動作のみでは訂正ができ

10

20

30

40

ず、また、前記第2軟判定読み出し動作により、も訂正可能ではない場合にだけ(S655(No)及びS665(No))、前記第2再読み出しが実行される。一方、前記第2硬判定読み出し動作は前記第1ページのデータ(すなわち、前記第1硬判定データ)の訂正可能であるかどうかとは関係なく、実行された前記第1再読み出しによって検出された前記最適読み出しレベルを用い、実行されるため、前記第2硬判定読み出し動作のみで前記第2ページのデータの誤り訂正が可能である場合が発生する確率が増加することができ、それに伴い、前記第2軟判定読み出し動作および/または、前記第2再読み出しが実行されないことによって前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0095]

例えば、図17に示されているように、第1ワードラインWLに所定の基準レベルを有 する第1読み出し電圧VREFを印加し第1ページPAGE1に対する前記第1読み出し 動作が実行されることができる。この際、第1読み出し電圧VREFの前記基準レベルが 前記第1軟判定読み出し動作による誤り訂正可能範囲820のうちのみではなく前記第1 硬判定読み出し動作による誤り訂正可能範囲810のうちにある場合、従来のデータ読み 出し方法では前記第1再読み出しが実行されないが、本発明の実施形態によるデータ読み 出し方法では前記第1再読み出しが実行されて前記最適読み出しレベルが検出されること ができる。それに伴い、従来のデータ読み出し方法では、第2および第3ページPAGE 2 及び P A G E 3 に対する後続の硬判定読み出し動作において、第 1 読み出し電圧 V R E Fが利用され、第1読み出し電圧VREFが第2および第3ページPAGE2及びPAG E3に対する硬判定読み出し動作による誤り訂正可能範囲830及び850を抜け出すの で第2および第3ページPAGE2及びPAGE3に対する軟判定読み出し動作が実行さ れることができる。また、従来のデータ読み出し方法では、第1読み出し電圧VREFが 第2および第3ページPAGE2及びPAGE3に対する軟判定読み出し動作による誤り 訂正可能範囲840及び860また抜け出す場合、第2および第3ページPAGE2及び PAGE3に対する軟判定読み出し動作のみでなく第2および第3ページPAGE2及び PAGE3に対する再読み出しがさらに行うことができる。しかし、本発明の実施形態に よるデータ読み出し方法では、第1ページPAGE1に対する前記第1再読み出しが実行 されて前記最適読み出しレベルが検出され、第2および第3ページPAGE2及びPAG E3に対する後続の硬判定読み出し動作において、前記最適読み出しレベルを有する第2 読み出し電圧VOPTが使われるため、第2読み出し電圧VOPTは第2および第3ペー ジPAGE2及びPAGE3に対する硬判定読み出し動作による誤り訂正可能範囲830 及び850のうちにあることもあり、第2および第3ページPAGE2及びPAGE3に 対する軟判定読み出し動作および再読み出しが実行されないこともある。それに伴い、後 続の読み出し動作において、軟判定読み出し動作および再読み出しが実行されないことに よって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減 少することができる。

## [0096]

一方、前記メモリコントローラーは誤り訂正符号、前記第2硬判定データおよび/または、前記第2軟判定データを用い、前記第2ページのデータに対し硬判定方式または、軟判定方式の誤り訂正を行うことによって原本データを復元することができる。それに伴い、前記第2ページのデータを読み出す前記第2読み出し動作が完了することができる(S680)。また、前記不揮発性メモリ装置は前記第1再読み出しまたは、前記第2再読み出しによって検出された前記最適読み出しレベルを用い、後続の読み出し動作をより一層行う(S650)。

# [0097]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、前記最適読み出しレベルを検出することによって、前記最適読み出しレベルを用い、少なくとも一つの後続の第2読み出し動作が実行されることができる。

10

20

30

40

20

30

40

50

それに伴い、後続の読み出し動作により読み出されたデータが軟判定読み出し動作および/または再読み出しの実行なしで硬判定読み出し動作のみで誤り訂正が可能であり、前記後続の読み出し動作の読み出し時間および読み出しレイテンシが減少することによって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

### [0098]

図18は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図19は不揮発性メモリ装置に含まれた複数のページのスレッショルド電圧分布の一例を示す図面である。

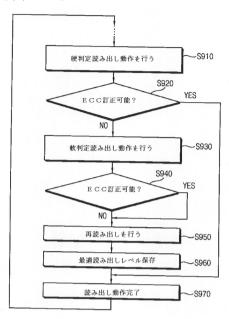

### [0099]

図18を参照すれば、不揮発性メモリ装置は硬判定データを読み出す硬判定読み出し動作を行い(S910)、メモリコントローラーは前記硬判定データが信頼性情報なしで誤り訂正が可能であるかどうかを判断することができる(S920)。前記硬判定データが信頼性情報なしで誤り訂正が可能である場合(S920(Yes))、前記不揮発性メモリ装置および前記メモリコントローラーは軟判定読み出し動作および再読み出しを行わず、原本データを復元することによって読み出し動作を完了することができる(S970)

### [0100]

前記硬判定データが信頼性情報なしで誤り訂正が可能ではない場合(S920(No))、前記不揮発性メモリ装置は前記硬判定データに対する信頼性情報を有する軟判定データを読み出す軟判定読み出し動作を行う(S930)。前記メモリコントローラーは前記硬判定データが前記軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかととができる(S940)。前記不揮発性メモリ装置は前記硬判定データが前記軟判定データの前記信頼性情報に基づき、誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出する再読み出しを行い(S950)、後続読み出し動作において、利用するように前記最適読み出しレベルを保存することができる(S960)。すなわち、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し動作において、前記硬判定データが前記信頼性情報なしで誤り訂正が可能である場合(S920(Yes))、前記再読み出しが実行されることができる。

## [0101]

一実施形態において、前記不揮発性メモリ装置は前記硬判定データが軟判定データの信頼性情報に基づき、誤り訂正が可能なことで可否によりそれぞれ異なる範囲を有する再読み出し電圧を用い、前記再読み出しを行う。例えば、前記硬判定データが前記軟判定データの信頼性情報に基づき、誤り訂正が可能ではないと判断された場合、前記不揮発性メモリ装置は第1範囲を有する第1再読み出し電圧を用い、前記再読み出しを行い、前記硬判定データが前記軟判定データの信頼性情報に基づき、誤り訂正が可能であると判断された場合、前記第1範囲より狭い第2範囲を有する第2再読み出し電圧を用い、前記再読み出しを行う。また、前記メモリコントローラーは誤り訂正符号、前記硬判定データおよび/または、前記軟判定データを用い、原本データを復元でき、それに伴い読み出し動作が完了することができる(S970)。一方、後続読み出し動作、すなわち後続硬判定読み出し動作は前記保存された最適読み出しレベルを用い、実行されることができる(S910)。

# [0102]

このように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、前記軟判定読み出し動作が実行された場合、前記硬判定データが前記軟判定読み出し動作により、誤り訂正が可能であるかどうかとは関係なく、前記最適読み出しレベルを検出する前記再読み出しが実行されることができる。また、後続読み出し動作時、硬判

20

30

40

50

定読み出し動作が前記最適読み出しレベルを用い、実行されることによって、前記硬判定読み出し動作のみで読み出されたデータの誤り訂正が可能である場合が発生する確率が増加することができる。それに伴い、前記後続読み出し動作時、軟判定読み出し動作および/または、前記再読み出しが実行されないことによって前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

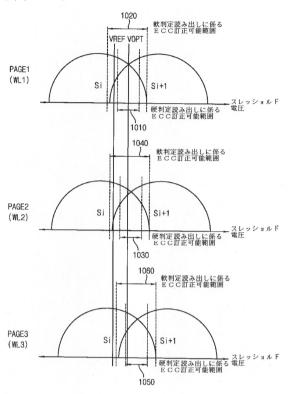

### [0103]

例えば、図19に示されているように、第1ワードラインWLに所定の基準レベルを有 する第1読み出し電圧VREFを印加し、第1ページPAGE1に対する硬判定読み出し 動作が実行されることができる。この際、第1読み出し電圧VREFが硬判定読み出し動 作による誤り訂正可能範囲1010を抜け出す場合、第1ページPAGE1に対する軟判 定読み出し動作が実行されることができる。第1読み出し電圧VREFが軟判定読み出し 動作による誤り訂正可能範囲1020のうちにある場合、従来のデータ読み出し方法では 再読み出しが実行されないが、本発明の実施形態によるデータ読み出し方法では前記再読 み出しが実行されて最適読み出しレベルが検出されることができる。それに伴い、従来の データ読み出し方法では、第2および第3ページPAGE2及びPAGE3に対する後続 の硬判定読み出し動作において、第1読み出し電圧VREFが利用され、第1読み出し電 圧VREFが第2および第3ページPAGE2及びPAGE3に対する硬判定読み出し動 作による誤り訂正可能範囲 1 0 3 0 及び 1 0 5 0 を抜け出すので第 2 および第 3 ページ P AGE2及びPAGE3に対する軟判定読み出し動作が実行されることができる。また、 従来のデータ読み出し方法では、第1読み出し電圧VREFが第2ページPAGE2に対 する軟判定読み出し動作による誤り訂正可能範囲1040のうちにある場合、第2ページ PAGE2に対する再読み出しが実行されないが、第1読み出し電圧VREFが第3ペー ジ P A G E 3 に対する軟判定読み出し動作による誤り訂正可能範囲 1 0 6 0 また抜け出す 場合、第3ページPAGE3に対する再読み出しがよりさらに行うことができる。しかし 本発明の実施形態によるデータ読み出し方法では、第1ページPAGE1に対する前記 再読み出しが実行されて前記最適読み出しレベルが検出され、第2および第3ページPA GE2及びPAGE3に対する後続の硬判定読み出し動作において、前記最適読み出しレ ベルを有する第2読み出し電圧VOPTが使われるため、第2読み出し電圧VOPTは第 2 および第 3 ページPAGE 2 及びPAGE 3 に対する硬判定読み出し動作による誤り訂 正可能範囲830及び850のうちにあることもあり、第2および第3ページPAGE2 及びPAGE3に対する軟判定読み出し動作および再読み出しが実行されないこともある 。それに伴い、後続の読み出し動作において、軟判定読み出し動作および再読み出しが実 行されないことによって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出 しレイテンシが減少することができる。

## [0104]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、読み出されたデータが前記軟判定読み出し動作により、訂正可能である場合でも、前記最適読み出しレベルを検出されることによって、前記最適読み出しレベルを用い、少なくとも一つの後続の読み出し動作が実行されることができる。それに伴い、後続の読み出し動作により読み出されたデータが軟判定読み出し動作および/または再読み出しの実行なしで硬判定読み出し動作のみで誤り訂正が可能であり、前記後続の読み出し動作の読み出し時間および読み出しレイテンシが減少することによって、前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

# [0105]

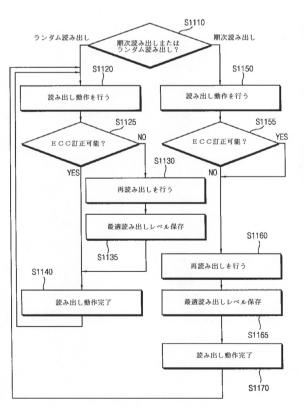

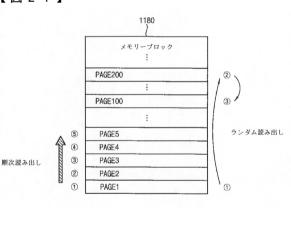

図 2 0 は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図 2 1 は順次読み出し動作およびランダム読み出し動作を説明するための図面である。

## [0106]

図 2 0 を参照すれば、不揮発性メモリ装置は読み出し動作が順次読み出し動作のうちの 一つであるかまたは、ランダム読み出し動作のうちの一つのいずれかによって誤り訂正可

20

30

40

50

能であるかどうかとは関係なく、再読み出しを行うかまたは、誤り訂正可能であるかどう かにより再読み出しを選択的に行う。すなわち、前記読み出し動作が順次読み出し動作の うちの一つであるかまたは、ランダム読み出し動作のうちの一つであるかどうかが判断さ れることができる(S1110)。例えば、図21に示されているように、前記読み出し 動作が複数の隣接したページPAGE1及びPAGE5から次々とデータを読み出す読み 出し動作のうちの一つである場合、前記読み出し動作が前記順次読み出し動作のうちの一 つだと判断されることができ、前記読み出し動作が複数の隣接しなかったページPAGE 1、PAGE100、PAGE200からデータを読み出す読み出し動作のうちの一つで ある場合、前記読み出し動作が前記ランダム読み出し動作のうちの一つだと判断されるこ とができる。一方、図21には前記ランダム読み出し動作の例として一つのメモリブロッ ク1180に含まれた隣接しなかったページPAGE1、PAGE100、PAGE20 0に対する読み出し動作が図示されているが、前記ランダム読み出し動作はそれぞれ異な るメモリブロックのページに対し実行される読み出し動作を含むことができる。実施形態 により、前記読み出し動作が前記順次読み出し動作のうちの一つであるかまたは、前記ラ ンダム読み出し動作のうちの一つなのかに対する判断はメモリコントローラーで実行され たり、ホストで実行されることができる。

## [0107]

前記読み出し動作が前記ランダム読み出し動作のうちの一つである場合(S 1 1 1 0 (r a n d o m R e a d ))、前記不揮発性メモリ装置は前記読み出し動作を行い(S 1 1 2 0)、読み出されたデータの誤り訂正が可能である場合(S 1 1 2 5 (Y e S))、再読み出しを行わず、読み出されたデータの誤り訂正が可能ではない場合にだけ(S 1 1 2 5 (X o ))、前記再読み出しを行い(X 1 1 3 0)最適読み出しレベルを保存することができる(X 1 1 3 5)。前記読み出し動作により読み出されたデータまたは、前記再読み出しによって読み出されたデータに誤り訂正が実行されることによって原本データが復元され、前記読み出し動作が完了することができる(X 1 1 4 0)。

## [0108]

前記読み出し動作が前記順次読み出し動作のうちの一つである場合(S1110(Se quential Read))、前記不揮発性メモリ装置は前記読み出し動作を行い( S1150)、読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、再読 み出しを行う(S1155及びS1160)。すなわち、前記不揮発性メモリ装置は、読 み出されたデータの誤り訂正が可能ではないかまたは(S1155(No))、読み出さ れたデータの誤り訂正が可能である場合でも(S1155(Yes))、前記再読み出し を行い、最適読み出しレベルを検出して、前記順次読み出し動作のうち後続読み出し動作 において、使われるように前記最適読み出しレベルを保存することができる(S1165 )。前記読み出し動作により読み出されたデータまたは、前記再読み出しによって読み出 されたデータに誤り訂正が実行されることによって原本データが復元され、前記読み出し 動作が完了することができる(S1170)。前記順次読み出し動作中後続読み出し動作 は前記保存された最適読み出しレベルを用い、実行されることができて(S1120)、 後続読み出し動作により読み出されたデータが誤り訂正可能なことで可否により再読み出 しが選択的に実行されることができる(S1125及びS1130)。一方、隣接したペ ージは互いに類似のスレッショルド電圧分布特性を有することができ、それに伴い、前記 順次読み出し動作のうちの一つで検出された前記最適読み出しレベルを用い、前記順次読 み出し動作中後続読み出し動作が実行されれば、前記後続読み出し動作により読み出され たデータの誤り訂正が可能である場合が発生する確率が増加することができる。したがっ て、前記後続読み出し動作において、再読み出しが実行されないことによって前記不揮発 性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる

## [0109]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、読み出し動作が順次読み出し動作のうちの一つである場合、読み出されたデ

20

30

40

50

ータの誤り訂正が可能であるかどうかとは関係なく、再読み出しが実行されることができる。それに伴い、前記順次読み出し動作中後続読み出し動作において、再読み出しが実行されないことによって、不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0110]

図 2 2 は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示す フローチャートである。

## [0111]

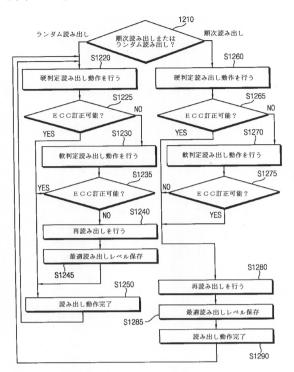

図22を参照すれば、不揮発性メモリ装置は読み出し動作が順次読み出し動作のうちの一つであるかまたは、ランダム読み出し動作のうちの一つのいずれかによって誤り訂正可能であるかどうかとは関係なく、再読み出しを行うかまたは、誤り訂正可能であるかどうかにより再読み出しを選択的に行う。前記読み出し動作が順次読み出し動作のうちの一つであるかまたは、ランダム読み出し動作のうちの一つであるかどうかが判断されることができる(S1210)。

### [0112]

前記読み出し動作が前記ランダム読み出し動作のうちの一つである場合S1210( r and om Read)、前記不揮発性メモリ装置は硬判定データを読み出す硬判定読み出し動作を行い(S1220)、前記硬判定データが信頼性情報なしで誤り訂正が可能である場合S1225(Yes))、軟判定読み出し動作および再読み出しを行わず、前記読み出し動作を完了することができる(S1250)。前記硬判定データが信頼性情報なして誤り訂正が可能ではない場合(S1225(No))、前記不揮発性メモリ装置は前記硬判定データに対する信頼性情報を有する軟判定データを読み出す軟判定読み出し動作を行い、(S1230)、前記硬判定データが前記信頼性情報に基づき、誤り訂正が可能である場合(S1235(Yes))、再読み出しを行わず、前記読み出し動作を完了できて(S1250)、前記硬判定データが前記信頼性情報に基づき、誤り訂正が可能ない場合(S1235(No))、再読み出しを行い(S1240)、前記再読み出したない場合(S1235(No))、再読み出しを行い(S1245)、前記読み出ししていたのできる(S1250)。

## [0113]

前記読み出し動作が前記順次読み出し動作のうちの一つである場合(S1210(Se quential Read))、前記不揮発性メモリ装置は読み出されたデータの誤り 訂正が可能であるかどうかとは関係なく、再読み出しを行う。すなわち、前記不揮発性メ モリ装置は硬判定データを読み出す硬判定読み出し動作を行い(S1260)、前記硬判 定データが信頼性情報なしで誤り訂正が可能である場合(S1265(Yes))、再読 み出しを行う(S1280)。前記硬判定データが信頼性情報なしで誤り訂正が可能では ない場合(S1265(No))、前記不揮発性メモリ装置は前記硬判定データに対する 信頼性情報を有する軟判定データを読み出す軟判定読み出し動作を行う(S1270)。 また、前記不揮発性メモリ装置は、前記硬判定データが前記信頼性情報に基づき、誤り訂 正が可能ではないかまたは(S1275(No))、前記硬判定データが前記信頼性情報 に基づき、誤り訂正が可能である場合でも(S1275(Yes))、最適読み出しレベ ルを検出する再読み出しを行う(S1280)。前記不揮発性メモリ装置は前記順次読み 出し動作中後続読み出し動作において、使われるように前記最適読み出しレベルを保存し (S1285)、前記読み出し動作を完了することができる(S1290)。前記順次読 み出し動作中後続読み出し動作において、後続硬判定読み出し動作は前記保存された最適 読み出しレベルを用い、実行されることができて(S1220)、読み出されたデータが 誤り訂正可能なことで可否により再読み出しが選択的に実行されることができる(S12 25、S1230、S1235、S1240)。一方、隣接したページは互いに類似のス レッショルド電圧分布特性を有することができ、それに伴い、前記順次読み出し動作のう ちの一つで検出された前記最適読み出しレベルを用い、前記順次読み出し動作中後続読み 出し動作の硬判定読み出し動作が実行されれば、前記硬判定読み出し動作により読み出さ

20

30

40

50

れた硬判定データが信頼性情報なしで誤り訂正が可能である場合が発生する確率が増加することができる。したがって、前記後続読み出し動作において、軟判定読み出し動作および再読み出しが実行されないことによって前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0114]

図23は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートである。

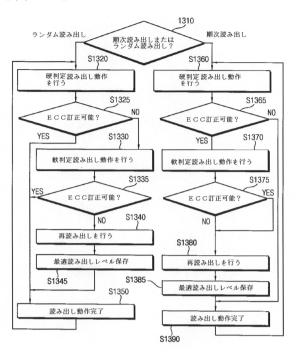

## [0115]

図23を参照すれば、不揮発性メモリ装置は読み出し動作が順次読み出し動作のうちの一つであるかまたは、ランダム読み出し動作のうちの一つのいずれかによって誤り訂正可能であるかどうかとは関係なく、再読み出しを行うかまたは、誤り訂正可能であるかどうかにより再読み出しを選択的に行う。前記読み出し動作が順次読み出し動作のうちの一つであるかまたは、ランダム読み出し動作のうちの一つであるかどうかが判断されることができる(S1310。

### [0116]

前記読み出し動作が前記ランダム読み出し動作のうちの一つである場合(S1310(Random Read))、前記不揮発性メモリ装置は硬判定データを読み出す硬判定読み出し動作を行い、(S1320)、前記硬判定データが信頼性情報なしで誤り訂正が可能である場合(S1325(Yes))、軟判定読み出し動作および再読み出しを行わず、前記読み出し動作を完了することができる(S1350)。前記硬判定データが信頼性情報なしで誤り訂正が可能ではない場合(S1325(No))、前記不揮発性メモリ装置は前記硬判定データに対する信頼性情報を有する軟判定データを読み出す軟判定読み出し動作を行い(S1330)、前記硬判定データが前記信頼性情報に基づき、誤り訂正が可能である場合(S13350)、両読み出しを行わず、前記読み出し動作を完了でき(S1350)、前記硬判定データが前記信頼性情報に基づき、誤り訂正が可能ではない場合(S13350)、再読み出しを行い、((S1340、前記再読み出しによって検出された最適読み出しレベルを保存し(S1345、前記読み出し動作を完了することができる(S1350)。

## [0117]

前記読み出し動作が前記順次読み出し動作のうちの一つである場合(S1310(Se quential Read))、前記不揮発性メモリ装置は読み出されたデータが軟判 定読み出し動作により、誤り訂正が可能である場合でも再読み出しを行う。すなわち、前 記不揮発性メモリ装置は硬判定データを読み出す硬判定読み出し動作を行い、(S136 り、前記硬判定データが信頼性情報なしで誤り訂正が可能である場合(S1365(Ye s))、軟判定読み出し動作および再読み出しを行わず、前記読み出し動作を完了するこ とができる(S1390)。前記硬判定データが信頼性情報なしで誤り訂正が可能ではな い場合(S1365(No))、前記不揮発性メモリ装置は前記硬判定データに対する信 頼性情報を有する軟判定データを読み出す軟判定読み出し動作を行う(S1370)。ま た、前記不揮発性メモリ装置は、前記硬判定データが前記信頼性情報に基づき、誤り訂正 が可能ではないかまたは(S1375(No))、前記硬判定データが前記信頼性情報に 基づき、誤り訂正が可能である場合でも(S1375(Yes))、最適読み出しレベル を検出する再読み出しを行う(S1380。前記不揮発性メモリ装置は前記順次読み出し 動作中後続読み出し動作において、使われるように前記最適読み出しレベルを保存してS 1385、前記読み出し動作を完了することができる(S1390)。前記順次読み出し 動作中後続読み出し動作において、後続硬判定読み出し動作は前記保存された最適読み出 しレベルを用い、実行されることができる(S1360)。一方、隣接したページは互い に類似のスレッショルド電圧分布特性を有することができ、それに伴い、前記順次読み出 し動作のうちの一つで検出された前記最適読み出しレベルを用い、前記順次読み出し動作 中後続読み出し動作の硬判定読み出し動作が実行されれば、前記硬判定読み出し動作によ り読み出された硬判定データが信頼性情報なしで誤り訂正が可能である場合が発生する確

20

30

40

50

率が増加することができる。したがって、前記後続読み出し動作において、軟判定読み出し動作および再読み出しが実行されないことによって前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

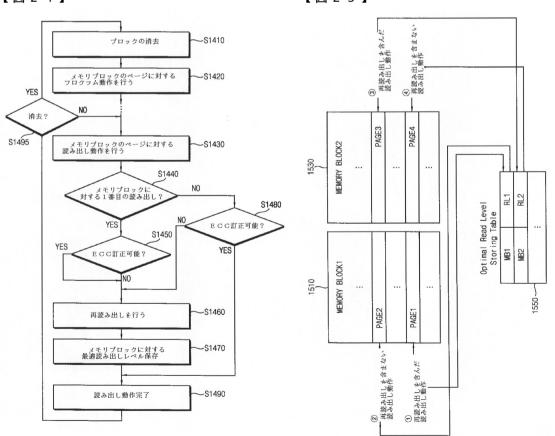

### [0118]

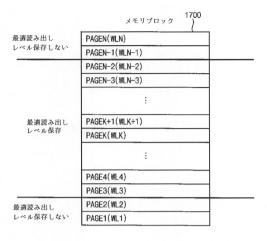

図 2 4 は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図 2 5 はメモリブロック別に最適読み出しレベルを保存する不揮発性メモリ装置を説明するための図面である。

図 2 4 を参照すれば、不揮発性メモリ装置は各メモリブロックが消去されてプログラムされた後、最初の実行される読み出し動作において、誤り訂正可能であるかどうかとは関係なく、再読み出しを行う。また、前記再読み出しによって検出された最適読み出しレベルはメモリブロック別に保存されることができる。

### [0119]

例えば、前記不揮発性メモリ装置はメモリブロックを消去して(S1410)、前記メモリブロックのページにデータを記入するプログラム動作を行う(S1420)。この後、前記不揮発性メモリ装置は前記メモリブロックの前記ページからデータを読み出す読み出し動作を行う(S1430)。この際、前記不揮発性メモリ装置は前記読み出し動作が前記メモリブロックが消去およびプログラムされた後、前記メモリブロックに対し最初に実行される読み出し動作なのか可否を判断することができる(S1440)。前記読み出し動作が前記メモリブロックに対し最初に実行される読み出し動作において、ない場合(S1440(No))、前記不揮発性メモリ装置は、前記データが誤り訂正可能ではない場合にだけ(S1480(No))、再読み出しを行い、前記データが誤り訂正可能である場合(S1480(Yes))、再読み出しを行わず、読み出し動作を完了することができる(S1490)。

#### [ 0 1 2 0 ]

また、前記読み出し動作が前記メモリブロックに対し最初に実行される読み出し動作において、ある場合(S1440(Yes))、前記不揮発性メモリ装置は、前記データが誤り訂正可能であるかどうかとは関係なく、前記再読み出しを行う(S1450及びS1460)。すなわち、前記不揮発性メモリ装置は、前記データが誤り訂正可能ではないかまたは(S1450(No))、前記データが誤り訂正可能である場合でも(S1450(Yes))、前記再読み出しを行い、最適読み出しレベルを検出して(S1460)、後続読み出し動作のために前記メモリブロックに対する前記最適読み出しレベルを保存して(S1470)、読み出し動作を完了することができる(S1490)。

### [0121]

一実施形態において、前記最適読み出しレベルはメモリブロック別に保存されることが できる。例えば、図25に示されているように、第1ページPAGE1に対する読み出し 動作が第1メモリブロック1510及びMB1が消去およびプログラムされた後、第1メ モリブロック1510及びMB1に対し最初に実行される読み出し動作において、ある場 合、読み出されたデータが誤り訂正可能であるかどうかとは関係なく、最適読み出しレベ ルRL1を検出する再読み出しが実行されることができる。最適読み出しレベルRL1は 最適読み出しレベル保存テーブル1550に第1メモリブロック1510及びMB1に対 し、保存されることができる。以後、第2ページPAGE2に対する読み出し動作が実行 される場合、第2ページPAGE2に対する読み出し動作は最適読み出しレベル保存テー ブル1550に保存された第1メモリブロック1510及びMB1に対する最適読み出し レベルRL1を用い、実行されることができ、読み出されたデータが誤り訂正可能である かどうかにより再読み出しが選択的に実行されることができる。また、第3ページPAG E 3 に対する読み出し動作が第 2 メモリブロック 1 5 3 0 及び M B 2 が消去およびプログ ラムされた後、第2メモリブロック1530及びMB2に対し最初に実行される読み出し 動作において、ある場合、読み出されたデータが誤り訂正可能であるかどうかとは関係な く、最適読み出しレベルRL2を検出する再読み出しが実行されることができる。最適読 み出しレベルRL2は最適読み出しレベル保存テーブル1550に第2メモリブロック1

20

30

40

50

5 3 0 及びM B 2 に対し、保存されることができる。以後、第 4 ページ P A G E 4 に対する読み出し動作が実行される場合、第 4 ページ P A G E 4 に対する読み出し動作は最適読み出しレベル保存テーブル 1 5 5 0 に保存された第 2 メモリブロック 1 5 3 0 及び M B 2 に対する最適読み出しレベル R L 2 を用い、実行されることができ、読み出されたデータが誤り訂正可能であるかどうかにより再読み出しが選択的に実行されることができる。

## [0122]

一方、同じメモリブロックに属したページは互いに類似のスレッショルド電圧分布特性を有することができ、それに伴い、メモリブロックが消去およびプログラムされた後、最初に実行された読み出し動作において、検出された前記最適読み出しレベルを用い、前記メモリブロックの他のページに対する後続読み出し動作が実行されれば、前記後続読み出し動作により読み出されたデータの誤り訂正が可能である場合が発生する確率が増加することができる。したがって、前記後続読み出し動作において、再読み出しが実行されないことによって前記不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

### [0123]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、メモリブロックが消去およびプログラムされた後、最初に実行された読み出し動作において、読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出する再読み出しが実行されることができる。また、前記最適読み出しレベルはメモリブロック別で保存されることができる。それに伴い、メモリブロック別で保存された前記最適読み出しレベルを用い、後続読み出し動作が実行されることによって、前記後続読み出し動作において、再読み出しが実行されないことによって、不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる

## [0124]

図 2 6 は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図 2 7 はワードラインの位置により最適読み出しレベルを保存する不揮発性メモリ装置を説明するための図面である。

## [0125]

図 2 6 を参照すれば、不揮発性メモリ装置は読み出し動作が実行されるページのワード ラインがメモリブロックの端の領域に位置するのかまたは、端の領域に位置しないのかど うかにより誤り訂正可能であるかどうかにより再読み出しを選択的に行うかまたは、誤り 訂正可能であるかどうかとは関係なく、再読み出しを行う。

## [0126]

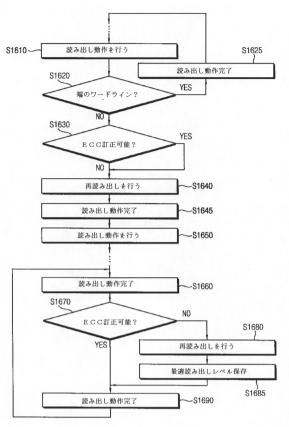

例えば、前記不揮発性メモリ装置は一つのワードラインに対応するページに対する読み出し動作を行い(S1610)、前記ワードラインが前記ワードラインに連結されたメモリセルを含むメモリブロックの端の領域に位置するのか可否を判断することができる(S1620)。前記ワードラインが前記メモリブロックの端の領域に位置したワードラインである場合(S1620(Yes))、前記不揮発性メモリ装置は誤り訂正可能であるかどうかにより再読み出しを選択的に行い、前記再読み出しが実行されても最適読み出しレベルを保存しないで読み出し動作を完了することができる(S1625)。一方、前記ワードラインが前記メモリブロックの端の領域に位置しなかったワードラインである場合(S1620(No))、前記不揮発性メモリ装置は誤り訂正可能であるかどうかに関係なく、再読み出しを行い、最適読み出しレベルを保存して読み出し動作を完了することができる(S1640、S1645、S1650)。

# [0127]

例えば、図27に示されているように、メモリブロック1700の少なくとも片方の端の領域に位置した少なくとも一つのワードラインWL1、WL2、WLN-1、WLNに連結されたページPAGE1、PAGE2、PAGEN-1、PAGENに対する読み出し動作において、誤り訂正可能であるかどうかにより再読み出しが選択的に実行され、前

20

30

40

50

記再読み出しが実行されても最適読み出しレベルが保存されないことがある。一方、メモリブロック1700の中心領域(すなわち、端の領域を除いた領域)に位置したワードラインWL3、WL4、WLK、WLK+1、WLN-3、WLN-2に連結されたページPAGE3、PAGE4、PAGEK、PAGEK+1、PAGEN-3、PAGEN-2に対する読み出し動作のうちの一つの読み出し動作において、誤り訂正可能であるかどうかに関係なく、再読み出しが実行され、最適読み出しレベルが保存されることができる

## [0128]

後続読み出し動作において、前記後続読み出し動作は前記保存された最適読み出しレベルを用い、実行されて(S1660)、誤り訂正可能であるかどうかにより再読み出しおよび最適読み出しレベルの保存が選択的に実行されて前記後続読み出し動作が完了することができる(S1670、S1680、S1685、S1690)。

# [0129]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、各メモリブロックでスレッショルド電圧分布特性が異なるページと相異なった最も端の領域に位置したページの読み出し動作時、最適読み出しレベルを保存しないで、スレッショルド電圧分布特性が異なるページと類似の中心領域に位置したページの読み出し動作時誤り訂正可能であるかどうかとは関係なく、最適読み出しレベルを検出および保存することによって、後続読み出し動作において、再読み出しが実行されないことがあって、不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

#### [ 0 1 3 0 ]

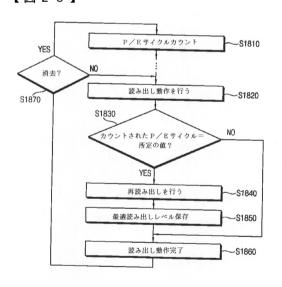

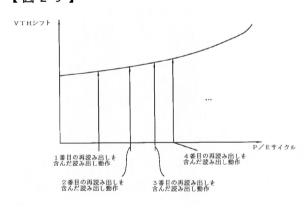

図 2 8 は本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法を示すフローチャートで、図 2 9 はプログラムおよび消去回数によるスレッショルド電圧移動を示す図面である。

## [0131]

図 2 8 を参照すれば、不揮発性メモリ装置はメモリブロックのプログラムおよび消去回数(Program & Erase Cycle、P/E Cycle)(または、消去回数)が所定の値のうちの一つである時、誤り訂正可能であるかどうかとは関係なく、再読み出しを行う。

## [0132]

例えば、前記不揮発性メモリ装置は前記不揮発性メモリ装置の消去回数または、各メモリブロックの消去回数をカウントすることができる(S1810)。すなわち、前記不揮発性メモリ装置は前記メモリブロックが消去されるたびに(S1870(Yes))前記メモリブロックに対する消去回数を増加させることができる。前記不揮発性メモリ装置は前記メモリブロックに含まれたページに対する読み出し動作を行い(S1820)、前記メモリブロックの消去回数を所定の値と比較することができる(S1830)。前記メモリブロックの消去回数が前記所定の値と一致しない場合(または、一実施形態において、かどうかにより再読み出しを選択的に行い、前記読み出し動作を完了することができる(S1860)。また、前記メモリブロックの消去回数が前記所定の値のうちの一つと一致する場合(または、一実施形態において、大きい場合)(S1830(Yes))、前記不揮発性メモリ装置は誤り訂正可能であるかどうかとは関係なく、再読み出しを行い(S1840)、最適読み出しレベルを保存して(S1850)前記読み出し動作を完了することができる(S1860)。

# [0133]

実施形態により、誤り訂正可能であるかどうかとは関係なく、再読み出しが実行される前記所定の値は一定の間隔を有するか、徐々に小さくなる間隔を有することができる。例えば、図29に示されているように、各メモリブロックの消去回数が増加するにつれ、前記メモリブロックに含まれたメモリセルの劣化程度が増加することができ、各ページのス

レッショルド電圧移動の程度が増加することができる。それに伴い、各メモリブロックの消去回数が増加するにつれ誤り訂正可能であるかどうかとは関係なく、実行される再読み出しがより頻繁に実行されるように、前記所定の値は徐々に小さくなる間隔を有することができる。

## [0134]

上述したように、本発明の他の実施形態による不揮発性メモリ装置のデータ読み出し方法において、所定の消去回数で誤り訂正可能であるかどうかとは関係なく、最適読み出しレベルを検出および保存することによって、後続読み出し動作において、再読み出しが実行されないことがあって、不揮発性メモリ装置の平均読み出し時間および平均読み出しレイテンシが減少することができる。

[0135]

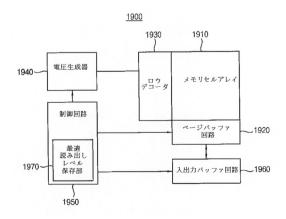

図30は本発明の実施形態による不揮発性メモリ装置を示すブロック図である。

#### [0136]

図30を参照すれば、不揮発性メモリ装置1900はメモリセルアレイ1910、ページバッファ回路1920、ロウデコーダ1930、電圧生成器1940、入出力バッファ回路1960、および制御回路1950を含む。一実施形態において、不揮発性メモリ装置1900はフラッシュメモリ装置でもよい。他の実施形態で、不揮発性メモリ装置1900はPRAM(Phase ChangeRandom Access Memory)、RRAM(登録商標)(ReSistance random Access Memory)、RRAM(Magnetic random Access Memory)、PRAM(Ferroelectirc random access memory)等と同じ任意の不揮発性メモリ装置でもよい。

[0137]

メモリセルアレイ1910は複数のワードラインおよび複数のビットラインにそれぞれ連結される複数のメモリセルを含む。図31乃至図33を参照し、後述するように、前記複数のメモリセルはそれぞれNANDまたはNORフラッシュメモリセルであることもあり、2次元アレイ(array)構造または、3次元垂直アレイ構造で配列されることができる。

## [0138]

一実施形態において、前記複数のメモリセルはそれぞれ一つのデータビットを保存するシングルレベルメモリセルSLC(Single Level memory Cell)または、複数のデータビットを保存するマルチレベルメモリセルMLC(Multi Level memory Cell)でもよい。マルチレベルメモリセルの場合に記入モードでのプログラム方式はシャドウプログラム方式、リプログラム方式または、オンチップバッファドプログラム方式と同じ多様なプログラム方式が適用されることができる。

[0139]

ページバッファ回路1920は前記複数のビットラインに連結され、メモリセルアレイ1910にプログラムされる記入データを保存したりあるいはメモリセルアレイ1910から感知された読み出しデータを保存する。すなわち、ページバッファ回路1920はフラッシュメモリ装置1900の動作モードにより記入ドライバーとしてまたは、感知増幅器として動作することができる。例えば、ページバッファ回路1920は記入モードで記入ドライバーとして動作して、読み出しモードで感知増幅器として動作することができる。入出力バッファ回路1960は外部のメモリコントローラーからメモリセルアレイ1910に記入されたデータを受信して、メモリセルアレイ1910から読み出されたデータを前記メモリコントローラーで転送することができる。

## [0140]

ロウデコーダ1930は前記複数のワードラインに連結され、ロウアドレスに応答して前記複数のワードラインのうち少なくとも一つを選択することができる。電圧生成器1940は制御回路1950の制御によりプログラム電圧、パス電圧、検証電圧、消去電圧および読み出し電圧と同じワードライン電圧を生成することができる。制御回路1950は

10

20

30

40

20

30

40

50

メモリセルアレイ1910に対するデータ保存、消去および読み出し動作を行うようにページバッファ回路1920、ロウデコーダ1930、電圧生成器1940および入出力バッファ回路1960を制御することができる。

## [0141]

一実施形態において、不揮発性メモリ装置1900は最適読み出しレベル保存部1970を含むことができる。最適読み出しレベル保存部1970は制御回路1950の内部または、外部に位置することができる。制御回路1950はワードラインに読み出し電圧を印加し前記複数のメモリセルのうち、前記ワードラインに連結されたメモリセルに対する第1読み出し動作を行い、前記第1読み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、最適読み出しレベルを検出するように再読み出しを行い、前記最適読み出しレベルを保存するように不揮発性メモリも置1900を制御することができる。すなわち、不揮発性メモリ装置1900は誤り訂正可能であるかどうかとは関係なく、再読み出しを行い、検出された最適読み出しレベルを用い、後続読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置1900の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0142]

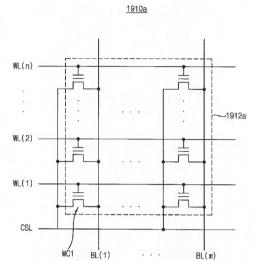

図31、図32および図33は図30の不揮発性メモリ装置に含まれるメモリセルアレイの例を示す図面である。

## [0143]

図31はNOR型フラッシュメモリ装置に含まれるメモリセルアレイの一例を示す回路図で、図32はNAND型フラッシュメモリ装置に含まれるメモリセルアレイの一例を示す回路図であり、図33は垂直型フラッシュメモリ装置に含まれるメモリセルアレイの一例を示す回路図である。

図31を参照すれば、メモリセルアレイ1910aは複数のメモリセルMC1を含むことができる。同じ列に配列されたメモリセルMC1はビットラインBL1、…、BLmのうちの一つと共通ソースラインCSLの間に並列に配置され、同様の行に配列されたメモリセルMC1はワードラインWL1、WL2、…、WLnのうちの一つに共通に連結されることができる。例えば、第1列に配列されたメモリセルは第1ビットラインWL1と共通ソースラインCSLの間に並列に配置されることができる。第1行に配列されたメモリセルのゲート電極は第1ワードラインWL1に共通に連結されることができる。メモリセルのゲート電極は第1ワードラインWL1に共通に連結されることができる。メモリセルとができる。メモリセルアレイ1910aを含むNOR型フラッシュメモリ装置はバイト(byte)単位または、ワード(word)単位で記入動作および読み出し動作を行い、ブロックblock、1912a単位で消去動作を行う。

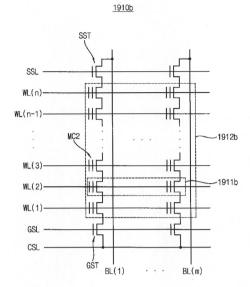

## [0144]

図32を参照すれば、メモリセルアレイ1910bはストリング選択トランジスターSST、接地選択トランジスターGSTおよびメモリセルMC2を含むことができる。ストリング選択トランジスターSSTはビットラインBL1、…、BLmに連結され、接地選択トランジスターGSTは共通ソースラインCSLに連結されることができる。同じ列に配列されたメモリセルMC2はビットラインBL1、…、BLmのうちの一つと共通ソースラインCSLの間に直列に配置され、同様の行に配列されたメモリセルMC2はワードラインWL1、WL2、WL3、…、WLn・1、WLnのうちの一つに共通に連結されることができる。すなわち、ストリング選択トランジスターSSTと接地選択トランジスターGSTの間にメモリセルMC2が直列に連結され、ストリング選択ラインSSLと接地選択ラインGSLの間には16個、32個または、64個の複数のワードラインが配列されることができる。

## [0145]

ストリング選択トランジスターSSTはストリング選択ラインSSLに連結され、ストリング選択ラインSSLから印加される電圧のレベルにより制御されることができ、接地選択トランジスターGSTは接地選択ラインGSLに連結され、接地選択ラインGSLから印加される電圧のレベルにより制御されることができる。メモリセルMC2はワードラインWL1、…、WLnに印加される電圧のレベルにより制御されることができる。

### [0146]

メモリセルアレイ1910bを含むNAND型フラッシュメモリ装置はページPAGE及び1911b単位で記入動作および読み出し動作を行い、ブロック1912b単位で消去動作を行う。一方、実施形態にしたがって、ページバッファはそれぞれ偶数ビットラインと奇数ビットラインが一つずつ連結されることができる。この場合、偶数ビットラインは偶数ページを形成して、メモリセルMC2に対する記入動作は偶数ページと奇数ページが交替して次々と実行されることができる。

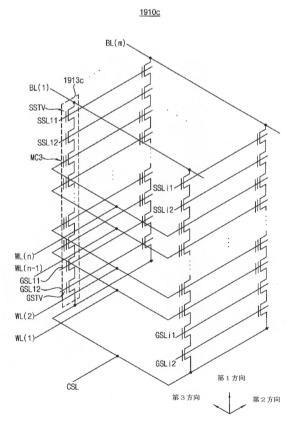

図33を参照すれば、メモリセルアレイ1910cは垂直構造を有する複数のストリング1913cを含むことができる。ストリング1913cは第2方向について複数個で形成されてストリング列を形成することができるし、前記ストリング列は第3方向について複数個で形成されてストリングアレイを形成することができる。複数のストリング1913cはビットラインBL1、…、BLmと共通ソースラインCSLの間に第1方向について直列に配置される接地選択トランジスターGSTV、メモリセルMC3およびストリング選択トランジスターSSTVをそれぞれ含むことができる。

#### [0148]

接地選択トランジスターGSTVは接地選択ラインGSL11、GSL12、…、GSLi1、GSLi2にそれぞれ連結され、ストリング選択トランジスターSSTVはストリング選択ラインSSL11、SSL12、…、SSLi1、SSLi2にそれぞれ連結されることができる。同じ層に配列されるメモリセルMC3はワードラインWL1、WL2、…、WLn・1、WLnのうちの一つに共通に連結されることができる。接地選択ラインGSL11、…、GSLi2およびストリング選択ラインSSL11、…、SSLi2は前記第2方向で延び、前記第3方向について複数個で形成されることができる。ワードラインWL1、…、WLnは前記第2方向で延びて前記第1方向および前記第3方向について複数個で形成されることができる。メモリセルMC3はワードラインWL1、…、WLnに印加される電圧のレベルにより制御されることができる。

## [0149]

メモリセルアレイ1910cを含む垂直型フラッシュメモリ装置はNANDフラッシュメモリセルを含むことで、NAND型フラッシュメモリ装置と同じようにページ単位で記入動作および読み出し動作を行い、ブロック単位で消去動作を行う。

## [ 0 1 5 0 ]

実施形態にしたがって、一つのストリング1913cに含まれる二つのストリング選択トランジスターは一つのストリング選択ラインに連結されて一つのストリングに含まれる二つの接地選択トランジスターは一つの接地選択ラインに連結されるように具現されることもできる。また、実施形態にしたがって、一つのストリングは一つのストリング選択トランジスターおよび一つの接地選択トランジスターを含んで具現されることもできる。

### [0151]

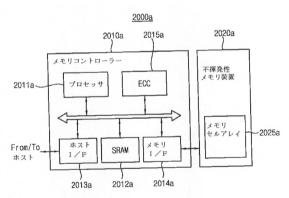

図34は本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの一例を示すブロック図である。

### [0152]

図 3 4 を参照すれば、メモリシステム 2 0 0 0 a はメモリコントローラー 2 0 1 0 a および不揮発性メモリ装置 2 0 2 0 a を含む。

10

20

30

40

### [0153]

不揮発性メモリ装置 2 0 2 0 a はデータを保存する複数のメモリセルを有するメモリセルアレイ 2 0 2 5 a を含むことができる。不揮発性メモリ装置 2 0 2 0 a は読み出し動作を行い、前記読み出し動作により読み出されたデータが誤り訂正可能であるかどうかとは関係なく、再読み出しを行い、最適読み出しレベルを検出および保存することができる。また、不揮発性メモリ装置 2 0 2 0 a は前記保存された最適読み出しレベルを用い、後続読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しなしで誤り訂正可能になることができ、軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置 2 0 2 0 a の平均読み出し時間および平均読み出しレイテンシが減少することができる

10

### [0154]

メモリコントローラー 2 0 1 0 a は不揮発性メモリ装置 2 0 2 0 a を制御する。メモリコントローラー 2 0 1 0 a は外部のホストと不揮発性メモリ装置 2 0 2 0 a の間のデータ交換を制御することができる。メモリコントローラー 2 0 1 0 a は中央処理装置 C P U のようなプロセッサ 2 0 1 1 a、バッファメモリ 2 0 1 2 a、ホストインターフェース 2 0 1 3 a、メモリインターフェース 2 0 1 4 a および E C C プロック 2 0 1 5 a を含むことができる。プロセッサ 2 0 1 1 a は前記データ交換のための動作を行う。一実施形態において、バッファメモリ 2 0 1 2 a は S R A M (S t a t i c r a n d o m a c c e s s m e m o r y )で具現されることができる。他の実施形態で、バッファメモリ 2 0 1 2 a は D R A M (D y n a m i c r a n d o m A c c e s s M e m o r y )、P R A M 、P R A M 、R R A M (登録商標)、M R A M などで具現されることができる。実施形態にしたがって、バッファメモリ 2 0 1 2 a はメモリコントローラー 2 0 1 0 a の内部または、外部に位置することができる。

20

## [0155]

ホストインターフェース 2 0 1 3 a は前記ホストと連結され、メモリインターフェース 2014aは不揮発性メモリ装置2020aと連結される。プロセッサ2011aはホス トインターフェース2013aを通じて前記ホストと通信することができる。例えば、ホ ストインターフェース 2 0 1 3 a は U S B ( U n i v e r s a l S e r i a l B u s ) 、MMC(Multi-Media Card)、PCI-E(Peripheral C omponent Interconnect-Express)、SAS(Seria l-attached SCSI)、SATA(Serial Advanced Tec hnology Attachment)、PATA(Parallel Advance d Technology Attachment)、SCSI(small compu ter System Interface), ESDI (Enhanced small Disk Interface)、IDE(Integrated Drive Elec tronics)等と同じ多様なインターフェースプロトコルのうち少なくとも一つを通 じてホストと通信するように構成されることができる。また、プロセッサ2011aはメ モリインターフェース2014aを通じて不揮発性メモリ装置2020aと通信すること ができる。ECCブロック2015aは前記ホストから提供されたデータをECCエンコ ーディングして不揮発性メモリ装置2020aに提供して、不揮発性メモリ装置2020 aから読み出されたデータをECCデコーディング下で前記ホストに提供することができ る。一実施形態において、ECCブロック2015aはBCH(Bose‐Chaudh uri-Hocquenghem)符号を用い、ECCエンコーディングおよびECCデ コーディングを行う。他の実施形態で、ECCブロック2015aはLDPC(Low DenSity Parity Check)符号を用い、ECCエンコーディングおよび ECCデコーディングを行う。または他の実施形態で、ECCブロック2015aはター ボ符号(Turbo Code)、リード・ソロモン符号(read-Solomon Code)、コンボルリューション符号(Convolution Code)、RSC

(RecurSive Systematic Code)、TCM(Trellis-C

30

40

20

30

40

50

oded Modulation)、BCM(Block Coded Modulation)等の符号化された変調(Coded Modulation)、または、異なる誤り訂正符号を用い、ECCエンコーディングおよびECCデコーディングを行う。実施形態により、メモリコントローラー 2010 aが不揮発性メモリ装置 2020 aにビルトイン(built-in)されて具現されたり、メモリコントローラー 2010 aおよび不揮発性メモリ装置 2020 aがそれぞれ別途のチップで具現されることができる。

メモリシステム2000aはメモリカード (memory card)、ソリッドステ ートドライブ(solid state drive)等と同じ形態で具現されることがで きる。 不揮発性メモリ装置2020a、メモリコントローラー2010a、および/また は、メモリシステム2000aは多様な形態のパッケージを用い、具現されるのに、例え ば、PoP(Package on Package)、Ball grid arrays (BGAs)、Chip scale Packages(CSPs)、Plastic Leaded Chip Carrier (PLCC), Plastic Dual In-Line Package (PDIP), Die in Waffle Pack, Die in Wafer Form、Chip On Board (COB)、Ceramic D ual In-Line Package (CERDIP), Plastic Metri c Quad Flat Pack (MQFP), Thin Quad Flatpac k(TQFP)、smallOutline(SOIC)、Shrink small Outline Package (SSOP), Thin small Outline ( TSOP)、Thin Quad Flatpack(TQFP)、System In P ackage(SIP)、Multi Chip Package(MCP)、Wafer -level Fabricated Package (WFP), Wafer-Leve 1 Processed Stack Packagee(WSP)等と同じパッケージを 用い、具現されることができる。

[0157]

[ 0 1 5 6 ]

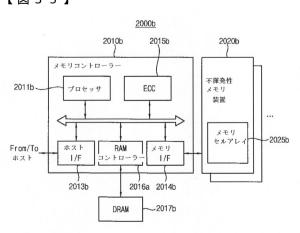

図35は本発明の実施形態による不揮発性メモリ装置およびメモリコントローラーを含むメモリシステムの他の例を示すブロック図である。

[0158]

図35を参照すれば、メモリシステム2000bはメモリコントローラー2010b、少なくとも一つの不揮発性メモリ装置2020bおよびバッファメモリ2017bを含む。一実施形態において、バッファメモリ2017bはDRAM(Dynamic random Access Memory)で具現されることができ、メモリコントローラー2010bの外部に位置することができる。不揮発性メモリ装置2020bはメモリセルアレイ2025bを含み、メモリコントローラー2010bはプロセッサ2011b、ホストインターフェース2013b、メモリインターフェース2011b、ホストインターフェース2013b、メモリインターフェース2011b、まストインターフェース2013b、メモリインターフェース2011b、まるとできる。図35のメモリシステム2000bは、バッファメモリ2017bがメモリコントローラー2010bの外部に位置したことの他に、図34のメモリシステム2000aと実質的に類似の構成および動作を有することができる。

[0159]

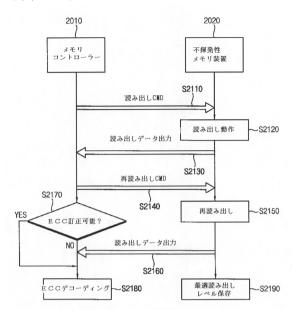

図36は本発明の一実施形態によるメモリシステムの駆動方法を示すフローチャートである。

[0160]

図36を参照すれば、メモリコントローラー2010および不揮発性メモリ装置2020を含むメモリシステムの駆動方法において、メモリコントローラー2010が不揮発性メモリ装置2020に読み出しコマンドを転送して(S2110)、不揮発性メモリ装置2020は前記読み出しコマンドに応答して第1読み出し動作を行うことによってメモリコントローラー2010に前記第1読み出し動作により読み出されたデータを転送するこ

20

30

40

50

とができる(S2120及びS2130)。メモリコントローラー2010は前記第1読 み出し動作により読み出されたデータの誤り訂正が可能であるかどうかとは関係なく、不 揮発性メモリ装置2020に再読み出しコマンドを転送することができる(S2140) 。すなわち、メモリコントローラー2010は前記データの誤り訂正可能可否を判断(S 2 1 7 0 ) する前、または、前記データの誤り訂正可能可否が判断された後でも前記判断 の結果と関係なく、不揮発性メモリ装置2020に再読み出しコマンドを転送することが できる。不揮発性メモリ装置2020は前記再読み出しコマンドに応答して、再読み出し を行い、前記再読み出しによって読み出されたデータをメモリコントローラー2010に 転送することができる(S2150及びS2160)。メモリコントローラー2010は 前記第1読み出し動作により読み出されたデータの誤り訂正可能である場合(S2170 (Yes))、前記再読み出しによって読み出されたデータを無視して、前記第 1 読み出 し動作により読み出されたデータにECCデコーディングを行い、原本データを復元する ことができる(S2180)。また、前記第1読み出し動作により読み出されたデータの 誤り訂正が可能ではない場合(S2170(No))、メモリコントローラー2010は 前記再読み出しによって読み出されたデータにECCデコーディングを行い、原本データ を復元することができる(S2180)。また、不揮発性メモリ装置2020は、前記最 適読み出しレベルを用い、後続の第2読み出し動作を行うように、前記再読み出しによっ て検出された前記最適読み出しレベルを保存することができる(S2190)。

#### [0161]

上述したように、本発明の一実施形態によるメモリシステムの駆動方法において、不揮発性メモリ装置2020が前記第1読み出し動作において、検出された前記最適読み出しレベルを用い、少なくとも一つの後続の第2読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しなしで誤り訂正可能になることができ、軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置2020の平均読み出し時間および平均読み出しレイテンシが減少することができる。

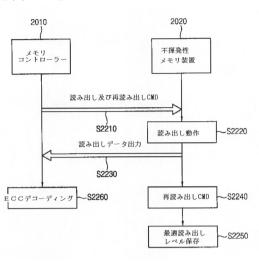

#### [0162]

図37は本発明の他の実施形態によるメモリシステムの駆動方法を示すフローチャートである。

## [0163]

図37を参照すれば、メモリコントローラー2010は不揮発性メモリ装置2020に一つのコマンド(例えば、読み出しおよび再読み出しコマンド(Read w/ ReadRetry CMD))を転送し、不揮発性メモリ装置2020が読み出し動作実行後誤り校正可能の有無と関係なく、再読み出しを行うようにすることができる。例えば、メモリコントローラー2010は不揮発性メモリ装置2020に読み出しおよび再読み出しコマンドを転送することができる(S2210)。不揮発性メモリ装置2020は前記読み出しおよび再読み出しコマンドに応答して第1読み出し動作を行い、メモリコントローラー2010に前記第1読み出し動作により読み出されたデータを転送することができる(S2220及びS2230)。メモリコントローラー2010は前記読み出し動作により読み出されたデータにECCデコーディングを行い、原本データを復元することができる(S2260)。不揮発性メモリ装置2020は、追加的なコマンドを受信しなくても、前記読み出しおよび再読み出しコマンドに応答して前記第1読み出し動作により読み出たデータの誤り訂正が可能であるかどうかとは関係なく、再読み出しを行う(S2240)。また、不揮発性メモリ装置2020は、最適読み出しレベルを用い、後続の第2読み出し動作を行うように、前記最適読み出しレベルを保存することができる(S2250)

### [0164]

上述したように、本発明の他の実施形態によるメモリシステムの駆動方法において、不揮発性メモリ装置 2 0 2 0 が前記第 1 読み出し動作において、検出された前記最適読み出していたのでは、少なくとも一つの後続の第 2 読み出し動作を行う。それに伴い、後続読

20

30

40

50

み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しなしで誤り訂正可能になることができ、軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置 2 0 2 0 の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0165]

図38は本発明の実施形態によるメモリシステムがメモリカードに応用された例を示す図面である。

### [0166]

図38を参照すれば、メモリカード2300は複数の接続ピン2310、メモリコントローラー2320および不揮発性メモリ装置2330を含む。

### [0167]

ホストとメモリカード 2 3 0 0 の間の信号が送受信されるように複数の接続ピン 2 3 1 0 は前記ホストに連結されることができる。複数の接続ピン 2 3 1 0 はクロックピン、コマンドピン、データピンおよび/または、リセットピンを含むことができる。

### [0168]

メモリコントローラー 2 3 2 0 は、前記ホストからデータを受信して、前記受信された データを不揮発性メモリ装置 2 3 3 0 に保存することができる。

#### [0169]

不揮発性メモリ装置 2 3 3 0 は読み出し動作を行い、前記読み出し動作により読み出されたデータが誤り訂正可能であるかどうかとは関係なく、再読み出しを行い、最適読み出しレベルを検出および保存することができる。また、不揮発性メモリ装置 2 3 3 0 は前記保存された最適読み出しレベルを用い、後続読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しなしで誤り訂正可能になることができ、軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置 2 3 3 0 の平均読み出し時間および平均読み出しレイテンシが減少することができる。

## [0170]

例えば、メモリカード2300はマルチメディアカード(MultiMedia Card:MMC)、エンベデッドマルチメディアカード(embedded MultiMedia Card:eMMC)、ハイブリッドエンベデッドマルチメディアカード(hybrid embedded MultiMedia Card;hybrid eMMC)、SD(Secure Digital)カード、マイクロSDカード、メモリスティック(Memory Stick)、IDカード、PCMCIA(Personal computer Memory Card International Association)カード、チップカード(Chip Card)、USBカード、スマートカード(Smart Card)、CFカード(Compact Flash Card)等と同じメモリカードでもよい。

### [0171]

実施形態にしたがって、メモリカード(2300)はコンピュータ(computer)、ノートブック(laptop)、携帯電話(cellular)、スマートフォン(Smart phone)、MP3プレーヤー、PDA(Personal Digital AsSistants)、P.M.P(Portable Multimedia Player)、デジタルTV、デジタルカメラ、ポータブルゲームコンソール(portable game consol)等と同じホストに装着されることができる。

#### [0172]

図39は本発明の実施形態によるメモリシステムがソリッドステートドライブに応用された例を示す図面である。

## [0173]

図 3 9 を参照すれば、ソリッドステートドライブ S S D 2 4 0 0 ( s o l i d s t a t e d r i v e ) はメモリコントローラー 2 4 1 0、バッファメモリ 2 4 2 0 および複

20

30

40

50

数の不揮発性メモリ装置2450を含む。

### [0174]

メモリコントローラー 2 4 1 0 は、ホスト(未図示)からデータを受信して、前記受信されたデータを複数の不揮発性メモリ装置 2 4 5 0 に保存することができる。バッファメモリ 2 4 2 0 は前記ホストと複数の不揮発性メモリ装置 2 4 5 0 の間で交換されるデータを一時保存することができ、メモリコントローラー 2 4 1 0 の外部に位置する D R A M で具現されることができる。

### [0175]

各不揮発性メモリ装置 2 4 5 0 は読み出し動作を行い、前記読み出し動作により読み出されたデータが誤り訂正可能であるかどうかとは関係なく、再読み出しを行い、最適読み出しレベルを検出および保存することができる。また、不揮発性メモリ装置 2 4 5 0 は前記保存された最適読み出しレベルを用い、後続読み出し動作を行う。それに伴い、後続読み出し動作において、読み出されたデータが軟判定読み出し動作および/または再読み出しなしで誤り訂正可能になることができ、軟判定読み出し動作および/または再読み出しが実行されないことによって不揮発性メモリ装置 2 4 5 0 の平均読み出し時間および平均読み出しレイテンシが減少することができる。

#### [0176]

実施形態にしたがって、ソリッドステートドライブ 2 4 0 0 はコンピュータ、ノートブック、携帯電話、スマートフォン、MP3 プレーヤー、PDA、P.M.P、デジタルTV、デジタルカメラ、ポータブルゲームコンソールなどと同じホストに装着されることができる。

## [0177]

図40は本発明の実施形態によるコンピューティングシステムを示すブロック図である

### [0178]

図40を参照すれば、コンピューティングシステム2500はプロセッサ2510、メモリ装置2520、ユーザインタフェース2530、バス2550およびメモリシステム2560を含む。実施形態により、コンピューティングシステム2500はベースバンドチップセット(baseband Chipset)と同じモデム2540をさらに含むことができる。

## [0179]

プロセッサ2510は特定計算または、タスクを実行することができる。例えば、プロ セッサ2510はマイクロプロセッサーまたは、中央処理装置CPUでもよい。プロセッ サ 2 5 1 0 はアドレスバス、制御バスおよび/または、データバスのようなバス 2 5 5 0 を通じてメモリ装置1120に連結されることができる。例えば、メモリ装置2520は DRAM、モバイルDRAM、SRAM、PRAM、PRAM、RRAM(登録商標)お よび/またはMRAMで具現されることができる。また、プロセッサ2510は周辺構成 要素相互連結PCI(peripheral component interconne c t ) バスのような拡張バスに連結されることができる。それに伴い、プロセッサ251 0 はキーボードまたは、マウスのような一つ以上の入力装置、プリンタまたは、ディスプ レイ装置のような一つ以上の出力装置を含むユーザインタフェース2530を制御するこ とができる。モデム2540は外部装置と無線でデータを送受信することができる。メモ リシステム2560の不揮発性メモリ装置2580にはプロセッサ2510により処理さ れたデータまたは、モデム2540を通じて受信されたデータなどがメモリコントローラ ー2570を通じて保存されることができる。コンピューティングシステム2500は動 作電圧を供給するためのパワーサプライをさらに含むことができる。また、コンピューテ ィングシステム2510は、実施形態にしたがって、応用チップセット(applica tion Chipset)、カメライメージプロセッサCIS(camera ima ge processor)等をさらに含むことができる。

### 【産業上の利用可能性】

### [0180]

本発明はフラッシュメモリのような不揮発性メモリ装置、およびこれを含む多様な装置およびシステムに適用されることができる。したがって、本発明は不揮発性メモリ装置を備えるメモリカード、ソリッドステートドライブ(solidstate drive:SSD)、コンピュータ(computer)、ノートブック(laptop)、携帯電話(cellular)、スマートフォン(Smart phone)、MP3プレーヤー、PDA(Personal Digital Assistants)、ポータブルメディアプレイヤー(Portable Multimedia Player:PMP)、デジタルTV、デジタルカメラ、ポータブルゲームコンソール(portable game consol)等と同じ電子機器に拡大適用されてもよい。

## [0181]

上記において本発明の実施形態を参照して説明したが、当該技術分野当業者は下記の特許請求の範囲に記載された本発明の思想および領域から抜け出さない範囲内で本発明を多様に修正および変更させる可能性があることを理解されたい。

### 【符号の説明】

### [0182]

1910 メモリセルアレイ

1950 制御回路

1900 不揮発性メモリ装置

## 【図1】

## 【図2】

# 【図3】

# 【図4】

# 【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

# 【図26】

# 【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図40】

【図39】

## フロントページの続き

# (72)発明者 尹 翔 ヨン

大韓民国ソウル特別市中浪区ドンイル路 7 5 2 (中和洞中和ハンシンアパートメント 1 0 1 棟 1 8 0 2 号 )

## 審査官 酒井 恭信

# (56)参考文献 特表2009-515281(JP,A)

米国特許出願公開第2007/0091677(US,A1)

米国特許出願公開第2012/0236656(US,A1)

特開2012-203957(JP,A)

特開2009-070542(JP,A)

米国特許出願公開第2009/0067257(US,A1)

特開2012-113809(JP,A)

米国特許出願公開第2008/0320346(US,A1)

米国特許出願公開第2013/0080858(US,A1)

特開2013-073669(JP,A)

# (58)調査した分野(Int.CI., DB名)

G11C 16/02 - 16/34