(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6165502号

(P6165502)

(45) 発行日 平成29年7月19日(2017.7.19)

(24) 登録日 平成29年6月30日(2017.6.30)

(51) Int.Cl.

F 1

**GO 1 R 19/00 (2006.01)**

**HO 1 L 29/786 (2006.01)**

**HO 1 L 21/336 (2006.01)**

**HO 1 L 21/8234 (2006.01)**

**HO 1 L 27/088 (2006.01)**

GO 1 R 19/00 H

HO 1 L 29/78 E

HO 1 L 21/336 6 1 8 B

HO 1 L 29/78 6 2 3

HO 1 L 29/78 6 1 8 Z

請求項の数 4 (全 28 頁) 最終頁に続く

(21) 出願番号 特願2013-104618 (P2013-104618)

(22) 出願日 平成25年5月17日 (2013.5.17)

(65) 公開番号 特開2014-2133 (P2014-2133A)

(43) 公開日 平成26年1月9日 (2014.1.9)

審査請求日 平成28年5月10日 (2016.5.10)

(31) 優先権主張番号 特願2012-117197 (P2012-117197)

(32) 優先日 平成24年5月23日 (2012.5.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 高橋 圭

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 井上 昇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 荒井 誠

最終頁に続く

(54) 【発明の名称】測定装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プローブ針と、第1乃至第3のFETと、高電位側の電源線と、出力端子と、を有し、前記第1のFETのゲートは、前記プローブ針と、前記第2のFETのゲート及びドレインと、前記第3のFETのソースと、に電気的に接続され、

前記第1のFETのドレインは、前記電源線と電気的に接続され、

前記第1のFETのソースは、前記出力端子と、前記第3のFETのゲート及びドレンとに直接接続され、

前記第2のFETのソースは、前記電源線と電気的に接続され、

前記第2のFET及び前記第3のFETは、チャネル形成領域に酸化物半導体膜が用いられていることを特徴とする測定装置。 10

## 【請求項 2】

プローブ針と、第1乃至第3のFETと、低電位側の電源線と、出力端子と、を有し、前記第1のFETのゲートは、前記プローブ針と、前記第2のFETのゲート及びドレインと、前記第3のFETのソースと、に電気的に接続され、

前記第1のFETのドレインは、前記電源線と電気的に接続され、

前記第1のFETのソースは、前記出力端子と、前記第2のFETのソースに直接接続され、

前記第3のFETのゲート及びドレインは、前記電源線と電気的に接続され、

前記第2のFET及び前記第3のFETは、チャネル形成領域に酸化物半導体膜が用い 20

られていることを特徴とする測定装置。

**【請求項 3】**

請求項 1 または請求項 2 において、

前記第 2 の F E T 及び前記第 3 の F E T のオフ時の漏れ電流は、それぞれ  $10^{-2} \text{ A}$  以下であることを特徴とする測定装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一項において、

前記第 1 の F E T と、前記第 2 の F E T 及び前記第 3 の F E T とは、同一の素子基板に積層して設けられていることを特徴とする測定装置。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、測定装置に関する。特に、電気回路の電気的な測定、検査に用いる測定装置に関する。

**【背景技術】**

**【0002】**

動作検証テストや故障解析のため、L S I 、L C D やO L E D に代表される表示装置等の集積回路における内部電圧の計測にアクティブプローブが用いられている。アクティブプローブとして代表的なF E T プローブは、能動素子であるF E T ( F i e l d E f f e c t T r a n s i s t o r ) と受動素子とを有し、また電源が用いられている。これにより、C ( 容量 ) とR ( 抵抗 ) とで構成されるパッシブプローブよりも高い入力インピーダンス ( 例えば  $1 \text{ M}$  以上 ) と低い入力容量 ( 例えば  $1 \text{ pF}$  以下 ) が実現され、被測定物 ( D U T : D e v i c e U n d e r T e s t ) に影響を極力与えずに波形観測を行うことができる。

20

**【0003】**

アクティブプローブは、漏れ電流が小さく、例えば  $10^{-1} \text{ A}$  程度のものが一般に用いられている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

30

【特許文献 1】米国特許第 4 6 4 6 0 0 2 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

このような高入力インピーダンス、低入力容量のプローブを実現するために、例えば特許文献 1 では、入力信号の検出用素子にバイポーラトランジスタや接合形トランジスタを用いた回路を形成している。しかし、これらの素子は入力から出力に電流を流すことで制御するものであるため、動作原理上、漏れ電流が不可避的に発生する。検出用素子における漏れ電流の発生は、被測定物の電位の測定精度を損なう結果となる。

**【0006】**

40

特に、漏れ電流が極めて小さい、酸化物半導体膜をチャネル形成領域に用いた電界効果トランジスタ ( 以下、O S - F E T という。 ) が被測定物である電気回路に用いられている場合、従来のプローブでは漏れ電流が大きすぎて、電圧に変動が生じる。従って、正確な電圧データの推移を観測することはできない。

**【0007】**

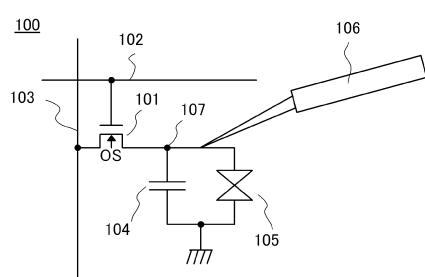

図 1 ( A ) は、画像データを保持するためのスイッチとして O S - F E T 1 0 1 を使用した画素回路 1 0 0 である。O S - F E T 1 0 1 のゲートはゲート信号線 1 0 2 に、ソース又はドレインの一方はソース信号線 1 0 3 に電気的に接続されている。また、O S - F E T 1 0 1 のソース又はドレインの他方は、容量素子 1 0 4 が有する一対の電極のうち一方と、また液晶素子 1 0 5 が有する対向する電極の一方 ( 画素電極 ) と電気的に接続されて

50

いる。画像データはOS-FET101を介してソース信号線103から、ノード107に書き込まれる。ここで、例えば、容量素子104の容量を80fF(フェムトファラッド)とし、液晶素子105の容量を20fFとする。よって、容量素子104と液晶素子105の容量の総和は100fFである。

#### 【0008】

ここで、漏れ電流が $10^{-14}$ Aと微小な従来のプローブ106を用いて、ノード107に書き込まれた画像データを長時間連続的に測定する場合を、図1(B)に示す。図1(B)のように、ホールド期間にプローブ106で測定を1秒間行うと、容量100fFではホールド電圧が実際の画像データの電圧より0.1Vも変動してしまう。例えば1画素に最大5Vの電圧の画像データが保持された場合、画像データが256階調ではホールド電圧は1階調につき約20mVであるから、1階調分の電圧よりも大きい変動が生じるという結果となってしまう。

10

#### 【0009】

このような漏れ電流が生じる原因として、以下のことが挙げられる。電圧検出用FETには、検出の際のESD(Electrostatic Discharge: 静電気放電)による過電圧から保護するために、MOS(Metal-Oxide-Semiconductor)型のFET(以下、MOSFETという。)により構成される保護回路が設けられている。このMOSFETは一般にゲートリークが生じるため、これが微小な漏れ電流となる。

20

#### 【0010】

また、漏れ電流を完全に無くして電圧を検出する方法として、電圧検出用FETにゲートリークの無いMOSFETを用い、検出の際の過電圧保護回路を設けない方法が考えられる。しかし、この場合、MOSFETのゲートは電荷を逃がす経路を有さないため、電荷の蓄積により容易にゲート絶縁破壊を引き起こしてしまう。

#### 【0011】

そこで、本発明の課題の一は、所定のESD耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたって正確な電圧の測定を可能とする測定装置を提供することである。

#### 【0012】

また、検出用FETと過電圧からの保護回路とを異なる素子基板上に形成した場合、素子基板どうしの接続部においてESDが発生するリスクや、漏れ電流の発生要因が加わるリスクがある。

30

#### 【0013】

そこで、本発明の課題の一は、所定のESD耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたって正確な電圧の測定を可能とともに、上記のリスクを極力低減した測定装置を提供することである。

#### 【課題を解決するための手段】

#### 【0014】

上記課題に鑑み本発明の一態様は、被測定物の電圧検出用FETにMOSFETを用い、該MOSFETのゲートに、オフ時の漏れ電流が極めて小さいOS-FETを電気的に接続させる。これにより、ESD耐性を確保しつつ、被測定物に影響を与えずに長時間の電圧測定を可能にする。

40

#### 【0015】

OS-FETのチャネル形成領域に用いる酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料である。このような特性を有する半導体材料をチャネル形成領域に含むことで、オフ電流が極めて低いトランジスタを実現することができる。このような半導体材料としては、例えば、シリコンの約3倍程度の大きなバンドギャップを有する、酸化物半導体の他、炭化シリコン、窒化ガリウムなどが挙げられる。上記半導体材料を有するFETは、通常のシリコンやゲルマニウムなどの半導体材料で形成されたFETに比べて、オフ電流を極めて低くすることができる。

50

**【0016】**

本発明の一態様は、被測定物と接触するためのプローブ針と、被測定物の電圧を検出するための第1のFETと、第1のFETを静電気から保護するための保護回路と、を有し、保護回路は、チャネル形成領域に酸化物半導体膜を用いた第2のFETを有する測定装置である。

**【0017】**

また本発明の一態様において、より具体的な構成としては、例えば、プローブ針と、第1乃至第4のFETと、高電位側の第1の電源線と、低電位側の第2の電源線と、バイアス電位を印加する配線と、を有し、第1のFETのゲートは、プローブ針と、第2のFETのゲート及びドレインと、第3のFETのソースと、に電気的に接続され、第1のFETのドレインは、第1の電源線と電気的に接続され、第1のFETのソースは、第4のFETのドレインに電気的に接続され、第2のFETのソースは、第1の電源線と電気的に接続され、第3のFETのゲート及びドレインは、第2の電源線と電気的に接続され、第4のFETのゲートは、配線と電気的に接続され、第4のFETのソースは、第2の電源線と電気的に接続され、第2のFET及び第3のFETは、チャネル形成領域に酸化物半導体膜が用いられている測定装置である。 10

**【0018】**

また本発明の一態様において、より具体的な他の構成としては、プローブ針と、第1乃至第3のFETと、高電位側の電源線と、を有し、第1のFETのゲートは、プローブ針と、第2のFETのゲート及びドレインと、第3のFETのソースと、に電気的に接続され、第1のFETのドレインは、電源線と電気的に接続され、第1のFETのソースは、第3のFETのゲート及びドレインに電気的に接続され、第2のFETのソースは、電源線と電気的に接続され、第2のFET及び第3のFETは、チャネル形成領域に酸化物半導体膜が用いられている測定装置である。 20

**【0019】**

また本発明の一態様において、より具体的な他の構成としては、プローブ針と、第1乃至第4のFETと、高電位側の第1の電源線と、低電位側の第2の電源線と、バイアス電位を印加する配線と、を有し、第1のFETのゲートは、プローブ針と、第2のFETのゲート及びドレインと、第3のFETのソースと、に電気的に接続され、第1のFETのドレインは、第2の電源線と電気的に接続され、第1のFETのソースは、第4のFETのドレインに電気的に接続され、第2のFETのソースは、第1の電源線と電気的に接続され、第3のFETのゲート及びドレインは、第2の電源線と電気的に接続され、第4のFETのゲートは、配線と電気的に接続され、第4のFETのソースは、第1の電源線と電気的に接続され、第2のFET及び前記第3のFETは、チャネル形成領域に酸化物半導体膜が用いられている測定装置である。 30

**【0020】**

また本発明の一態様において、より具体的な他の構成としては、プローブ針と、第1乃至第3のFETと、低電位側の電源線と、を有し、第1のFETのゲートは、プローブ針と、第2のFETのゲート及びドレインと、第3のFETのソースと、に電気的に接続され、第1のFETのドレインは、電源線と電気的に接続され、第1のFETのソースは、第2のFETのソースに電気的に接続され、第3のFETのドレインは、電源線と電気的に接続され、第2のFET及び第3のFETは、チャネル形成領域に酸化物半導体膜が用いられている測定装置である。 40

**【0021】**

ここで、保護回路に用いる第2のFET及び/または第3のFETは、オフ時の漏れ電流は、それぞれ $10^{-2} \sim 4 A$ 以下であることが好ましい。

**【0022】**

また、電圧検出のための第1のFETと、保護回路に用いる第2のFET及び/または第3のFETとは、同一の素子基板に積層して形成することが好ましい。

**【発明の効果】**

**【 0 0 2 3 】**

本発明の一態様により、所定の E S D 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたって正確な電圧の測定を可能とする測定装置を提供することができる。

**【 0 0 2 4 】**

また、本発明の一態様により、所定の E S D 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたって正確な電圧の測定を可能とするとともに、電圧検出用 F E T と保護回路との間で E S D が発生するリスクや、漏れ電流の発生要因が加わるリスクを極力低減した測定装置を提供することができる。

**【図面の簡単な説明】**

10

**【 0 0 2 5 】**

【図 1】従来のプローブによる測定の例と、ホールド時間とホールド電圧の関係を示す図。

【図 2】測定装置の一形態を説明する回路図。

【図 3】測定装置の一形態を説明する回路図。

【図 4】測定装置の一形態を説明する回路図。

【図 5】測定装置の一形態を説明する回路図。

【図 6】半導体装置の一形態を示す断面図。

【図 7】半導体装置の一形態を示す断面図。

**【発明を実施するための形態】**

20

**【 0 0 2 6 】**

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

**【 0 0 2 7 】**

なお、第 1、第 2 として付される序数詞は便宜上用いるものであり、本明細書において発明を特定するための事項として固有の名称を示すものではない。

**【 0 0 2 8 】**

30

「電気的に接続」や「電気的接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限はない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

**【 0 0 2 9 】**

(実施の形態 1)

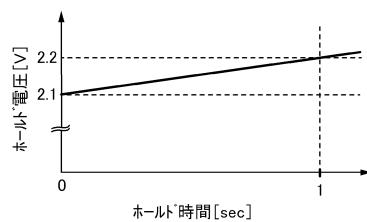

本実施の形態では、測定装置の一形態を、図 2 を用いて説明する。

**【 0 0 3 0 】**

40

図 2 ( A ) は、測定装置、より詳細にはアクティブプローブの入力端の回路構成を示す図である。本実施の形態において、アクティブプローブは、プローブ針 2 0 1 と、保護回路部 2 1 0 と、検出部 2 1 1 とを有する。本実施の形態における検出部 2 1 1 は、高電位側の電位 ( V D D ) を与える電源線 2 0 7 と、低電位側の電位 ( V S S : 接地電位 ) を与える電源線 2 0 8 と、出力端子 2 0 6 とを有するため、3 端子出力の回路である。

**【 0 0 3 1 】**

プローブ針 2 0 1 は、物理的に被測定物に接触することで、被測定物の接触部分の電圧を測定装置に入力するためのインターフェースとして機能する。従って、プローブ針 2 0 1 は被測定物との電気的な接触性の良い材料が望ましく、また測定時に付加される外部応力に対する強度 ( 剛性や機械的弾性等 ) が求められる。このため、プローブ針 2 0 1 の材料として、例えばタンクスチタン、鋼鉄、炭化タンクスチタン、パラジウム、ベリリウム、オス

50

ミウム、銅、又はこれらを二種以上組み合わせた合金、あるいはこれらに金等を被覆した材料等を用いることができる。また、プローブ針201の径は、強度等種々の要求特性を充足する上で被測定物の接触部位（金属パッド等）の形状に応じた種々の径とすることが可能であり、例えば0.1μm以上100μm以下とすることができます。プローブ針201は保護回路部210を介して、検出部211と電気的に接続する。

#### 【0032】

検出部211は、二つのトランジスタ、すなわちMOSFET202とMOSFET205とを有する。本実施の形態において、MOSFET202とMOSFET205は、ともにn型のトランジスタである。MOSFET202は、電圧検出用のトランジスタとして機能する。MOSFET202は、ゲートがプローブ針201と電気的に接続され、ドレインが高電位側の電位（VDD）を与える電源線207と電気的に接続され、ソースがMOSFET205のドレイン及び出力端子206と電気的に接続される。一方MOSFET205は、検出部において定電流源として機能し、ゲートはバイアス電位（VB）を印加する配線209と電気的に接続され、ソースは低電位側の電位（VSS：接地電位）を与える電源線208と電気的に接続される。

#### 【0033】

このようなFETの接続により、検出部211はソースフォロワ回路を構成する。プローブ針201より入力された微小な信号は、MOSFET202を介して出力端子206に出力される。ここでソースフォロワ回路の動作について、図2(B)を用いて説明する。

#### 【0034】

ソースフォロワ回路を構成する検出部211において、電圧検出用のトランジスタであるMOSFET202のゲートは入力端子となっており、MOSFET202のゲートには入力電位Vinが入力される。また、電圧検出用のMOSFET202のソースが出力端子206と電気的に接続しており、MOSFET202のソースの電位が、出力電位Voutとなる。一方、MOSFET205のゲートにはバイアス電位VBが印加されており、MOSFET205が飽和領域で動作するときには、MOSFET205に電流Ibが流れるとする。このとき、MOSFET202及びMOSFET205は直列に接続されているため、MOSFET202及びMOSFET205には同量の電流が流れる。つまり、MOSFET205に電流Ibが流れるときには、MOSFET202にも電流Ibが流れる。

#### 【0035】

ソースフォロワ回路における出力電位Voutは、入力電位VinよりもMOSFET202のゲート・ソース間電圧Vgsの分だけ低い値となる。このとき、入力電位Vin、出力電位Vout、ゲート・ソース間電圧Vgsの関係は、以下の式(1)を満たす。

#### 【0036】

$$V_{out} = V_{in} - V_{gs} \quad \text{式(1)}$$

#### 【0037】

従って、MOSFET202から出力端子206に出力される電圧Voutは、MOSFET202のゲートに入力された電圧Vinからオフセット電位となるVgsを差し引いた値となる。このオフセット電位Vgsは、一般にMOSFET202の閾値電圧や移動度等の関数で表されるため、MOSFET202として、閾値電圧に特性ばらつきの少ないトランジスタ、例えば単結晶シリコンをチャネル形成領域に用いたトランジスタを用いると、出力電位Voutは入力電位Vinに比例した値となる。

#### 【0038】

以上のことから、ソースフォロア回路を出力バッファとして用いることができる。これにより、出力端子206が高インピーダンスの機器に接続された場合であっても、プローブ針201により入力された信号を検出することができる。

#### 【0039】

なお、検出部211はソースフォロア回路の構成に限らず、他の回路構成とすることができる。例えばオペアンプを用いた回路構成としてもよい。

10

20

30

40

50

**【0040】**

保護回路部210は、例えば図2(A)に示すように、二つのOS-FET203、204により構成される。これらOS-FET203、204はいずれもn型のトランジスタである。OS-FET203のソースは、高電位側の電位(VDD)を供給する電源線207に電気的に接続され、ドレインはゲートに電気的に接続(いわゆるダイオード接続)される。また、OS-FET204のドレインは、低電位側の電位(VSS:接地電位)を供給する電源線208に電気的に接続され、ゲートに電気的に接続(いわゆるダイオード接続)される。OS-FET203とOS-FET204とは、電気的に直列に接続される。具体的には、OS-FET203のドレインとOS-FET204のソースとが電気的に接続される。プローブ針201と、電圧検出用のMOSFET202のゲートは、このOS-FET203とOS-FET204の接続点と電気的に接続される。

10

**【0041】**

次に、保護回路部210の動作について説明する。

**【0042】**

保護回路部210は、検出部211における電圧検出用のMOSFET202に、ESD等による過大な電圧が印加されるのを防止するものである。過大な電圧(過電圧)がプローブ針201に入力された場合、電圧検出用のMOSFET202に直接過電圧が印加されることがないようにするため、保護回路部に電気的に接続された別の配線(電源線207、208)に電圧を逃がし、瞬時に電圧を低減させる機能を有する。

20

**【0043】**

OS-FET203は、プローブ針201と電圧検出用のMOSFET202のゲートとを結ぶ配線と電源線207との間に設けられ、高電位側の電位を与える電源線207と電気的に接続している。OS-FET203は、ゲートとドレインとを接続させた2端子素子であり、ドレインにOS-FET203の閾値電圧Vth以上の正の電圧が印加された場合、ゲートにも同一の電圧が印加されるため、OS-FET203のソースドレイン間が導通状態(オン)となる。

**【0044】**

このため、通常時においてはOS-FET203のソースドレイン間は非導通状態(オフ)であるが、ESDの発生等により、プローブ針201に正の過電圧が印加された場合には、正の過電圧はOS-FET203の閾値電圧Vthよりも十分大きい電圧であるから、この過電圧がOS-FET203のゲートに印加されることで、OS-FET203のソースドレイン間は導通状態となる。よって、OS-FET203を通じて高電位側の電位を与える電源線207に電流が瞬時に流れ、電圧検出用のMOSFET202のゲートに印加される電圧は大きく下がる。以上のようにして、電圧検出用のMOSFET202が保護される。なお、プローブ針201に正の過電圧が印加された場合には、OS-FET204は、非導通状態である。

30

**【0045】**

同様に、OS-FET204もゲートとドレインとを接続させた2端子素子であり、ドレインにOS-FET204の閾値電圧Vth以上の正の電圧が印加された場合、ゲートにも同一の電圧が印加されるため、OS-FET204のソースドレイン間が導通状態(オン)となる。

40

**【0046】**

通常時においてはOS-FET204のソースドレイン間は非導通状態(オフ)であるが、ESDの発生等により、プローブ針201に負の過電圧が印加された場合には、OS-FET204のソースに負の過電圧が印加される。すると、OS-FET204のゲート及びドレインには、閾値電圧Vthよりも十分大きい電圧が相対的に印加されたことになるから、OS-FET204のソースドレイン間は導通状態となる。よって、OS-FET204を通じて低電位側の電位(接地電位)を与える電源線208から、プローブ針201に電流が瞬時に流れ、電圧検出用のMOSFET202のゲートに印加される電圧は大きく上がる。以上のようにして、電圧検出用のMOSFET202が保護される。なお

50

、プローブ針 201 に負の過電圧が印加された場合には、OS-FET 203 は、非導通状態である。

#### 【0047】

このように、保護回路部 210 にそれぞれがダイオード接続した OS-FET 203、204 を用いることで、過電圧に対して電圧検出用の MOSFET 202 を保護することができる。

#### 【0048】

ここで、上述したように、OS-FET 203、204 は、測定装置の通常の動作時においては、非導通状態（オフ）を維持している。ここで、オフ時において大きな漏れ電流がある場合には、プローブ針 201 からの入力電圧に変動を生じる。従って、正確な電圧データの推移を観測することはできない。しかし、本発明に係る OS-FET 203、204 には、チャネル形成領域に酸化物半導体を用いているため、オフ時の漏れ電流は極めて小さく、例えば  $10^{-24}$  A 以下である。

#### 【0049】

以上のことから、所定の ESD 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたっての正確な電圧の測定が可能となる。

#### 【0050】

なお、本実施の形態においては、保護回路部 210 にダイオード接続した OS-FET を二つのみ用いたがこれに限らず、例えば OS-FET 203 と電源線 207 との間に、さらにダイオード接続した OS-FET を複数直列に挿入してもよい。同様に、OS-FET 204 と電源線 208 との間に、さらにダイオード接続した OS-FET を複数直列に挿入してもよい。このようにダイオード接続した OS-FET の設置数を増やすことで、過電圧に対する閾値を上げることができる他、保護回路部 210 における漏れ電流をさらに低減することができる。

#### 【0051】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0052】

##### (実施の形態 2)

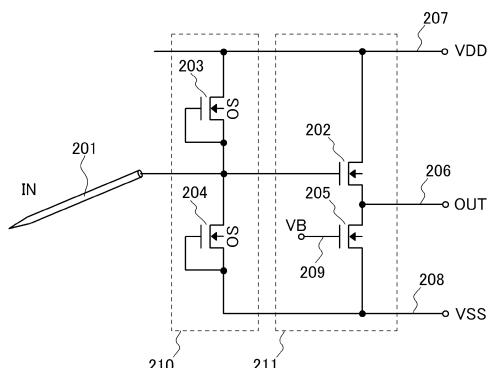

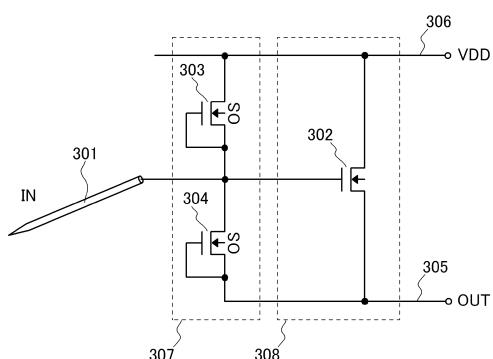

実施の形態 1 では、3 端子出力の検出部を有する測定装置について示したが、本実施の形態では、2 端子出力の検出部を有する測定装置について、図 3 を用いて説明する。

#### 【0053】

図 3 は、測定装置、より詳細にはアクティブプローブの入力端の回路構成を示す図である。本実施の形態において、アクティブプローブは、プローブ針 301 と、保護回路部 307 と、検出部 308 とを有する。本実施の形態における検出部 308 は、高電位側の電位 (VDD) を与える電源線 306 と、出力端子 305 とを有するため、2 端子出力の回路である。

#### 【0054】

プローブ針 301 は保護回路部 307 を介して、検出部 308 と電気的に接続する。

#### 【0055】

検出部 308 は、MOSFET 302 を有する。本実施の形態において、MOSFET 302 は、n 型のトランジスタである。MOSFET 302 は、電圧検出用のトランジスタとして機能する。MOSFET 302 は、ゲートがプローブ針 301 と電気的に接続され、ドレインが高電位側の電位 (VDD) を与える電源線 306 と電気的に接続され、ソースが出力端子 305 と電気的に接続される。

#### 【0056】

保護回路部 307 は、実施の形態 1 で示した保護回路部 210 とほぼ同様の構成であり、二つの OS-FET 303、304 により構成される。これら OS-FET 303、304 はいずれも n 型のトランジスタである。OS-FET 303 のソースは、高電位側の電位 (VDD) を供給する電源線 306 に電気的に接続され、ドレインはゲートに電気的に接続（いわゆるダイオード接続）される。また、OS-FET 304 のドレインは、出力

10

20

30

40

50

端子 305 に電気的に接続され、ゲートに電気的に接続（いわゆるダイオード接続）される。OS-FET 303 と OS-FET 304 とは、電気的に直列に接続される。具体的には、OS-FET 303 のドレインと OS-FET 304 のソースとが電気的に接続される。プローブ針 301 と、電圧検出用の MOSFET 302 のゲートは、この OS-FET 303 と OS-FET 304 の接続点と電気的に接続される。

#### 【0057】

本実施の形態における検出部 308 は 2 端子出力の構成であるが、出力端子 305 は検出部 308 の外部に設けられた定電流源と電気的に接続され、検出部 308 を含めてソースフォロワ回路を形成することができる。

#### 【0058】

本実施の形態における検出部 308 は 2 端子出力であり、実施の形態 1 で説明した検出部 211 と比べて少ない端子数で機能することができる。一方、実施の形態 1 で説明した測定装置に比べ、プローブ針 301（入力端子）と出力端子 305との間で、OS-FET 304 が寄生容量として働く場合がある。そこで、実施の形態 1 で示した測定装置と、本実施の形態で示した測定装置とを、被測定物や測定条件等に合わせて適宜使い分ければよい。

#### 【0059】

以上の構成により、所定の ESD 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたっての正確な電圧の測定が可能となる。

#### 【0060】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0061】

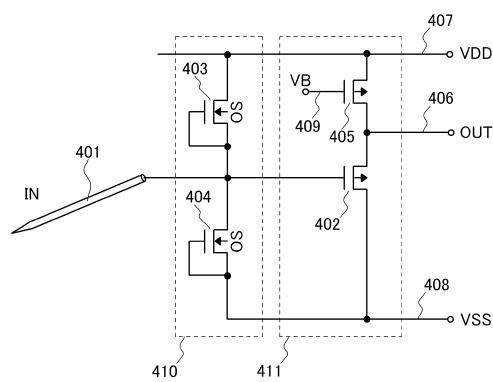

##### （実施の形態 3）

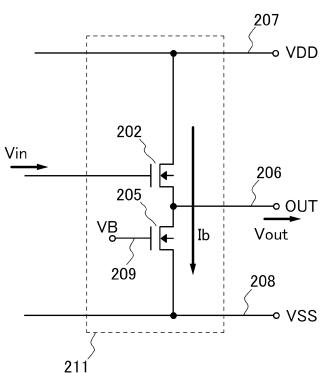

実施の形態 1 では、3 端子出力の検出部を有する測定装置について検出部に n 型の MOSFET を用いた場合を示したが、本実施の形態では、p 型の MOSFET を用いた場合について、図 4 を用いて説明する。

#### 【0062】

図 4 は、測定装置、より詳細にはアクティブプローブの入力端の回路構成を示す図である。本実施の形態において、アクティブプローブは、プローブ針 401 と、保護回路部 410 と、検出部 411 とを有する。本実施の形態における検出部 411 は、高電位側の電位（VDD）を与える電源線 407 と、低電位側の電位（VSS：接地電位）を与える電源線 408 と、出力端子 406 とを有するため、3 端子出力の回路である。

#### 【0063】

プローブ針 401 は保護回路部 410 を介して、検出部 411 と電気的に接続する。

#### 【0064】

検出部 411 は、二つのトランジスタ、すなわち MOSFET 402 と MOSFET 405 とを有する。本実施の形態において、MOSFET 402 と MOSFET 405 は、ともに p 型のトランジスタである。MOSFET 402 は、電圧検出用のトランジスタとして機能する。MOSFET 402 は、ゲートがプローブ針 401 と電気的に接続され、ソースが MOSFET 405 のドレイン及び出力端子 406 と電気的に接続され、ドレインが低電位側の電位（VSS：接地電位）を与える電源線 407 と電気的に接続される。一方 MOSFET 405 は、検出部において定電流源として機能し、ゲートはバイアス電位（VB）を印加する配線 409 と電気的に接続され、ソースは高電位側の電位（VDD）を与える電源線 407 と電気的に接続される。

#### 【0065】

保護回路部 410 は、実施の形態 1 で示した保護回路部 210 と同様の構成であり、二つの OS-FET 403、404 により構成される。これら OS-FET 403、404 はいずれも n 型のトランジスタである。OS-FET 403 のソースは、高電位側の電位（VDD）を供給する電源線 407 に電気的に接続され、ドレインはゲートに電気的に接続（いわゆるダイオード接続）される。また、OS-FET 404 のドレインは、低電位側

10

20

30

40

50

の電位 (VSS : 接地電位) を供給する電源線 408 に電気的に接続され、ゲートに電気的に接続 (いわゆるダイオード接続) される。OS-FET 403 と OS-FET 404 とは、電気的に直列に接続される。具体的には、OS-FET 403 のドレインと OS-FET 404 のソースとが電気的に接続される。プローブ針 401 と、電圧検出用のMOSFET 402 のゲートは、このOS-FET 403 と OS-FET 404 の接続点と電気的に接続される。

#### 【0066】

検出部 411 のMOSFET を p 型とすることで、実施の形態 1 で示した n 型のMOSFET に比べ、ノイズを低減することができる。一方で、n 型のMOSFET の方が、電界効果移動度が高い。そこで、実施の形態 1 で示した測定装置と、本実施の形態で示した測定装置とを、被測定物や測定条件等に合わせて適宜使い分ければよい。

10

#### 【0067】

以上の構成により、所定のESD 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたっての正確な電圧の測定が可能となる。

#### 【0068】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0069】

##### (実施の形態 4 )

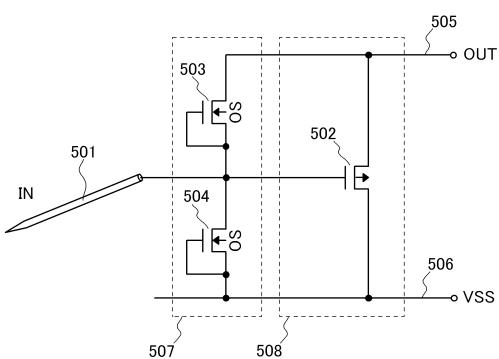

実施の形態 2 では、2 端子出力の検出部を有する測定装置について検出部に n 型のMOSFET を用いた場合を示したが、本実施の形態では、p 型のMOSFET を用いた場合について、図 5 を用いて説明する。

20

#### 【0070】

図 5 は、測定装置、より詳細にはアクティブプローブの入力端の回路構成を示す図である。本実施の形態において、アクティブプローブは、プローブ針 501 と、保護回路部 507 と、検出部 508 とを有する。本実施の形態における検出部 508 は、低電位側の電位 (VSS : 接地電位) を与える電源線 506 と、出力端子 505 とを有するため、2 端子出力の回路である。

#### 【0071】

プローブ針 501 は保護回路部 507 を介して、検出部 508 と電気的に接続する。

#### 【0072】

検出部 508 は、MOSFET 502 を有する。本実施の形態において、MOSFET 502 は、p 型のトランジスタである。MOSFET 502 は、電圧検出用のトランジスタとして機能する。MOSFET 502 は、ゲートがプローブ針 501 と電気的に接続され、ドレインが低電位側の電位 (VSS : 接地電位) を与える電源線 506 と電気的に接続され、ソースが出力端子 505 と電気的に接続される。

30

#### 【0073】

保護回路部 507 は、実施の形態 1 で示した保護回路部 210 とほぼ同様の構成であり、二つのOS-FET 503、504 により構成される。これらOS-FET 503、504 はいずれも n 型のトランジスタである。OS-FET 503 のソースは、出力端子 505 に電気的に接続され、ドレインはゲートに電気的に接続 (いわゆるダイオード接続) される。また、OS-FET 504 のドレインはゲートに電気的に接続 (いわゆるダイオード接続) されるとともに、低電位側の電位 (VSS : 接地電位) を供給する電源線 506 に電気的に接続される。OS-FET 503 と OS-FET 504 とは、電気的に直列に接続される。具体的には、OS-FET 503 のドレインと OS-FET 504 のソースとが電気的に接続される。プローブ針 501 と、電圧検出用のMOSFET 502 のゲートは、このOS-FET 503 と OS-FET 504 の接続点と電気的に接続される。

40

#### 【0074】

本実施の形態における検出部 508 は 2 端子出力の構成であるが、出力端子 505 は検出部 508 の外部に設けられた定電流源と電気的に接続され、検出部 508 を含めてソースフォロワ回路を形成することができる。

50

**【 0 0 7 5 】**

本実施の形態における検出部 508 は 2 端子出力であり、実施の形態 3 で説明した検出部 411 と比べて少ない端子数で機能することができる。一方、実施の形態 3 で説明した測定装置に比べ、プローブ針 501（入力端子）と出力端子 505との間で、OS-FET 503 が寄生容量として働く場合がある。そこで、実施の形態 3 で示した測定装置と、本実施の形態で示した測定装置とを、被測定物や測定条件等に合わせて適宜使い分ければよい。

**【 0 0 7 6 】**

以上の構成により、所定の ESD 耐性を確保し、また漏れ電流を小さくすることで、被測定物に影響を与えることなく、長時間にわたっての正確な電圧の測定が可能となる。

10

**【 0 0 7 7 】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

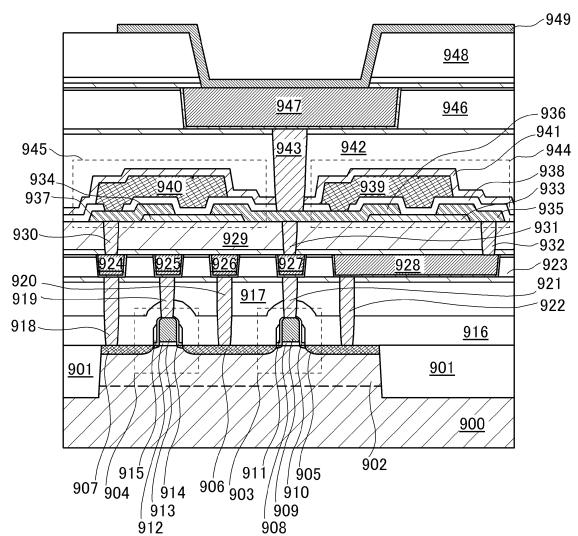

**【 0 0 7 8 】****( 実施の形態 5 )**

本実施の形態では、実施の形態 1 で説明した FET に、MOSFET 202 及び MOSFET 205 としてチャネル形成領域に単結晶シリコンウェハを用い、OS-FET 203、OS-FET 204 としてチャネル形成領域に酸化物半導体を用いた場合の断面構造の例、及びその作製方法の例について、図 6 を用いて説明する。

**【 0 0 7 9 】**

ただし、MOSFET 202 及び MOSFET 205 のチャネル形成領域には、シリコンの他、ゲルマニウム、シリコングルマニウム、単結晶炭化シリコンなどの半導体材料を用いていてもよい。また、例えば、シリコンを用いたトランジスタは、SOI 法により作製されたシリコン薄膜、気相成長法により作製されたシリコン薄膜などを用いて形成することができる。この場合、基板にはフュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のものを用いるとよい。さらに、MOSFET 202 及び MOSFET 205 に、保護回路に用いる酸化物半導体を用いててもよい。

20

**【 0 0 8 0 】**

図 6 は、実施の形態 1 で説明した測定装置における保護回路部 210 及び検出部 211 の回路構成を断面構造として具現したものを見せる図である。この場合、単結晶シリコンウェハを用いた MOSFET 903、MOSFET 904 が、実施の形態 1 における MOSFET 202、MOSFET 205 に相当し、その上階層に酸化物半導体を用いた OS-FET 944、OS-FET 945 が、実施の形態 1 における OS-FET 203、OS-FET 204 に相当する。すなわち、本実施の形態で示す測定装置は、シリコンウェハを基板として、その上層に酸化物半導体膜が設けられた三次元の積層構造を有する測定装置であり、また、シリコンをチャネル形成領域に用いたトランジスタと酸化物半導体をチャネル形成領域に用いたトランジスタとを有するハイブリッド型の測定装置である。

30

**【 0 0 8 1 】**

なお、本実施の形態においては、測定装置の保護回路部及び検出部の構造についてのみ断面を示すが、この積層構造を用いて検出部から出力された信号が入力される他の回路構成を作製することができる。このような構成とすることで、保護回路部及び検出部の全体を一つの積層構造体として作製することができる。従って、検出部に設けられた電圧検出用の MOSFET 202 と、保護回路とを極めて近接して設けることができるため、これらを異なる素子基板に設けた場合に生じる基板間の接続部における ESD の発生や、漏れ電流の発生を抑制することができる。

40

**【 0 0 8 2 】**

半導体材料を含む基板 900 を用いて作製された MOSFET 903、MOSFET 904 は、n チャネル型トランジスタ（NMOSFET）、p チャネル型トランジスタ（PMOSFET）のいずれも用いることができる。本実施の形態においては、実施の形態 1 に

50

基づいて、MOSFET 903、MOSFET 904はともにNMOSFETである。図6に示す例では、MOSFET 903、MOSFET 904は、STI (Shallow Trench Isolation) 901によって他の素子と絶縁分離されている。STI 901を用いることにより、LOCOSによる素子分離法で発生し得る素子分離部のバーズピークを抑制することができ、素子分離部の縮小等が可能となる。一方で、構造の微細化小型化が要求されない半導体装置においてはSTI 901の形成は必ずしも必要ではなく、LOCOS等の素子分離手段を用いることもできる。MOSFET 903、MOSFET 904が形成される基板900には、ボロンやリン、ヒ素等の導電性を付与する不純物が添加されたウェル902が形成されている。

## 【0083】

10

図6におけるMOSFET 903は、基板900中に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域905、906と、チャネル形成領域上に設けられたゲート絶縁膜908と、ゲート絶縁膜908上にチャネル形成領域と重畠するように設けられたゲート電極層909とを有する。不純物領域905、906のうち、不純物領域905はMOSFET 903のドレイン領域として、不純物領域906はソース領域として機能する。

## 【0084】

同様に、MOSFET 904は、基板900中に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域906、907と、チャネル形成領域上に設けられたゲート絶縁膜912と、ゲート絶縁膜912上にチャネル形成領域と重畠するように設けられたゲート電極層913とを有する。不純物領域906、907のうち、不純物領域906はMOSFET 904のドレイン領域として、不純物領域907はソース領域として機能する。

20

## 【0085】

図示しないが、ゲート電極層909、913は、加工精度を高めるための第1の材料からなるゲート電極層と、配線として低抵抗化を目的とした第2の材料からなるゲート電極層を積層した構造とすることができる。例えば導電性を付与するリン等の不純物を添加した結晶性シリコンとニッケルシリサイドとの積層構造などが挙げられる。しかし、この構造に限らず、適宜要求される仕様に応じて材料、積層数、形状等を調整することができる。

## 【0086】

30

なお、図6に示すMOSFET 903、MOSFET 904を、フィン型構造のトランジスタとしてもよい。フィン型構造とは、半導体基板の一部を板状の突起形状に加工し、突起形状の長尺方向を交差するようにゲート電極層を設けた構造である。ゲート電極層は、ゲート絶縁膜を介して突起構造の上面及び側面を覆う。MOSFET 903、MOSFET 904をフィン型構造のトランジスタとすることで、チャネル幅を縮小してトランジスタの集積化を図ることができる。また、電流を多く流すことができ、加えて制御効率向上させることができるために、トランジスタのオフ時の電流及び閾値電圧を低減することができる。

## 【0087】

また、基板900中に設けられた不純物領域905、906、907には、それぞれコンタクトプラグ922、920、918が接続されている。また、ゲート電極層909、913には、それぞれコンタクトプラグ921、919が接続されている。ここでコンタクトプラグ922、920、918は、接続するMOSFET 903、MOSFET 904のソース電極やドレイン電極としても機能する。また、不純物領域905、906、907とチャネル領域の間には、不純物領域905、906、907と異なる不純物領域が設けられている。該不純物領域は、導入された不純物の濃度によって、LDD領域やエクステンション領域としてチャネル形成領域近傍の電界分布を制御する機能を果たす。ゲート電極層909、913の側壁にはそれぞれ絶縁膜910、914を介してサイドウォール絶縁膜911、915を有する。この絶縁膜910、914やサイドウォール絶縁膜911、915を用いることで、LDD領域やエクステンション領域を形成することができる

40

50

。

### 【 0 0 8 8 】

また、MOSFET 903、MOSFET 904 は、絶縁膜 916 により被覆されている。絶縁膜 916 には保護膜としての機能を持たせることができ、外部からチャネル形成領域への不純物の侵入を防止することができる。また、絶縁膜 916 を CVD 法による窒化シリコン等の材料とすることで、チャネル形成領域に単結晶シリコンを用いた場合には加熱処理によって水素化を行うことができる。また、絶縁膜 916 に引張応力又は圧縮応力を有する絶縁膜を用いることで、チャネル形成領域を構成する半導体材料に歪みを与えることができる。n チャネル型のトランジスタの場合にはチャネル形成領域となるシリコン材料に引張応力を、p チャネル型のトランジスタの場合にはチャネル形成領域となるシリコン材料に圧縮応力を付加することで、各トランジスタの電界効果移動度を向上させることができる。10

### 【 0 0 8 9 】

さらに、絶縁膜 916 上に絶縁膜 917 が設けられ、その表面は CMP による平坦化処理が施されている。これにより、MOSFET 903、MOSFET 904 を含む階層よりも上の階層に高い精度で素子層を積層していくことができる。

### 【 0 0 9 0 】

MOSFET 903、MOSFET 904 を含む階層よりも上層に、酸化物半導体膜をチャネル形成領域に用いた OS - FET 944、OS - FET 945 を含む階層を形成する。OS - FET 944、OS - FET 945 はトップゲート構造のトランジスタである。20

OS - FET 944 では、ソース電極層 935 及びドレイン電極層 936 が酸化物半導体膜 933 の側面及び上面に接することで、ソース電極層 935 及びドレイン電極層 936 が酸化物半導体膜 933 に電気的に接続されている。また、OS - FET 944 は、これらの上のゲート絶縁膜 938 上にゲート電極層 939 を有している。同様に、OS - FET 945 では、ソース電極層 936 及びドレイン電極層 937 が酸化物半導体膜 934 の側面及び上面に接することで、ソース電極層 936 及びドレイン電極層 937 が酸化物半導体膜 934 に電気的に接続されている。また、OS - FET 945 は、これらの上のゲート絶縁膜 938 上にゲート電極層 940 を有している。ここで、OS - FET 944 が電気的に接続するドレイン電極層 936 は、OS - FET 945 が電気的に接続するソース電極層 936 と同一の配線材料からなり共通する。30

### 【 0 0 9 1 】

OS - FET 944 において、ゲート電極層 939 は、ゲート絶縁膜 938 に設けられた開口を介してドレイン電極層 936 と電気的に接続され、いわゆるダイオード接続されている。また、OS - FET 945 において、ゲート電極層 940 は、ゲート絶縁膜 938 に設けられた開口を介してドレイン電極層 937 と電気的に接続され、いわゆるダイオード接続されている。

### 【 0 0 9 2 】

また、OS - FET 944、OS - FET 945 上には、これら FET を覆うように絶縁膜 941 が形成されている。ここで OS - FET 944、OS - FET 945 の作製方法について、以下に説明する。40

### 【 0 0 9 3 】

絶縁膜 929 上に酸化物半導体膜 933、934 を形成する。絶縁膜 929 は、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。特に、誘電率の低い (10 w - k) 材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁膜 929 に上記材料を用いた多孔性の絶縁膜を適用しても良い。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。本実施の形態では、膜厚 50 nm の酸化アルミニウム膜上に膜厚 300 nm 程度の酸化珪素膜を積層させて、絶縁膜 929 として用いる。50

## 【0094】

酸化物半導体膜933、934は、絶縁膜929上に形成した酸化物半導体膜を所望の形状に加工することで、形成することができる。上記酸化物半導体膜の膜厚は、2nm以上200nm以下、好ましくは3nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

## 【0095】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁膜929の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

10

## 【0096】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。また、上記酸化物半導体は、珪素を含んでいてもよい。

20

## 【0097】

本実施の形態では、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚30nmのIn-Ga-Zn系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、好ましくは、原子数比がIn:Ga:Zn=1:1:1、4:2:3、3:1:2、1:1:2、2:1:3、または3:1:4で示されるターゲットを用いる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

30

## 【0098】

なお、酸化物半導体膜としてIn-Zn系の材料を用いる場合、用いるターゲットの組成は、原子数比で、In:Zn=50:1~1:2(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO=25:1~1:4)、好ましくはIn:Zn=20:1~1:1(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO=10:1~1:2)、さらに好ましくはIn:Zn=1.5:1~1.5:1(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO=3:4~1.5:2)とする。例えば、In-Zn系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。Znの比率を上記範囲に収めることで、移動度の向上を実現することができる。

40

## 【0099】

50

また、酸化物半導体膜として In - Sn - Zn 系酸化物半導体膜をスパッタリング法で成膜する場合、好ましくは、原子数比が In : Sn : Zn = 1 : 1 : 1、2 : 1 : 3、1 : 2 : 2、または 20 : 45 : 35 で示される In - Sn - Zn - O ターゲットを用いる。

#### 【 0100 】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。成膜時に、基板温度を 100 以上 600 以下、好ましくは 200 以上 400 以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。10

#### 【 0101 】

成膜条件の一例としては、基板とターゲットの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電源 0.5 kW、酸素 (酸素流量比率 100%) 雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。20

#### 【 0102 】

また、スパッタリング装置の処理室のリークレートを  $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3 / \text{秒}$  以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として上述した吸着型の真空ポンプを用いることで、排気系からのアルカリ金属、水素原子、水素分子、水、または水素化物等の不純物の逆流を低減することができる。

#### 【 0103 】

また、ターゲットの純度を、99.99% 以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。30

#### 【 0104 】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜 929 までが形成された基板 900 を予備加熱し、基板 900 に吸着した水分又は水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100 以上 400 以下、好ましくは 150 以上 300 以下である。また、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

#### 【 0105 】

なお、酸化物半導体膜 933、934 を形成するためのエッチングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。ドライエッティングに用いるエッティングガスとしては、塩素を含むガス (塩素系ガス、例えば塩素 (Cl<sub>2</sub>)、三塩化硼素 (BCl<sub>3</sub>)、四塩化珪素 (SiCl<sub>4</sub>)、四塩化炭素 (CCl<sub>4</sub>) など) が好ましい。また、フッ素を含むガス (フッ素系ガス、例えば四弗化炭素 (CF<sub>4</sub>)、六弗化硫黄 (SF<sub>6</sub>)、三弗化窒素 (NF<sub>3</sub>)、トリフルオロメタン (CHF<sub>3</sub>) など)、臭化水素 (HBr)、酸素 (O<sub>2</sub>)、これらのガスにヘリウム (He) やアルゴン (Ar) などの希ガスを添加したガス、などを用いることができる。40

#### 【 0106 】

ドライエッティング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductively Coupled Plasma : 誘導

結合型プラズマ)エッティング法を用いることができる。所望の形状にエッティングできるよう、エッティング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

#### 【0107】

ウェットエッティングに用いるエッティング液として、磷酸と酢酸と硝酸を混ぜた溶液、クエン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO-07N(関東化学社製)を用いる。

#### 【0108】

酸化物半導体膜933、934を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。10

#### 【0109】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体膜933、934及び絶縁膜929の表面に付着しているレジスト残渣などを除去することが好ましい。

#### 【0110】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分又は水素(水酸基を含む)が多量に含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分又は水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体膜933、934に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)雰囲気下で、加熱処理を施す。20

#### 【0111】

酸化物半導体膜933、934に加熱処理を施すことで、酸化物半導体膜933、934中の水分又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化又は脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。30

#### 【0112】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

#### 【0113】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。40

#### 【0114】

加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。50

**【0115】**

以上の工程により、酸化物半導体膜933、934中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、オフ電流の著しく低いトランジスタを作製することができる。上記加熱処理は、酸化物半導体膜の成膜以降であれば、いつでも行うことができる。

**【0116】**

なお、酸化物半導体膜は非晶質であっても良いが、結晶性を有していても良い。結晶性を有する酸化物半導体膜としては、c軸配向を有した結晶(CAAC)を含むCAC-O<sub>10</sub>(C Axis Aligned Crystalline Oxide Semiconductor)膜であっても、トランジスタの信頼性を高めるという効果を得ることができるので、好ましい。

**【0117】**

CAC-O<sub>10</sub>膜で構成された酸化物半導体膜は、スパッタリング法によても作製することができる。スパッタリング法によってCAC-O<sub>10</sub>膜を得るには酸化物半導体膜の堆積初期段階において六方晶の結晶が形成されるようにすることと、当該結晶を種として結晶が成長されるようにすることが肝要である。そのためには、ターゲットと基板の距離を広くとり(例えば、150mm~200mm程度)、基板加熱温度を100~500、好適には200~400、さらに好適には250~300にすると好ましい。また、これに加えて、成膜時の基板加熱温度よりも高い温度で、堆積された酸化物半導体膜を熱処理することで膜中に含まれるミクロな欠陥や、積層界面の欠陥を修復することができる。<sub>20</sub>

**【0118】**

次いで、フォトリソグラフィ工程を用いて、ソース電極層及びドレイン電極層935、936、937を形成する。具体的には、これらの電極層は、スパッタ法や真空蒸着法で絶縁膜929上に導電膜を形成した後、当該導電膜を所定の形状に加工(パターニング)することで、形成することができる。

**【0119】**

ソース電極層及びドレイン電極層935、936、937は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側もしくは上側にクロム、タンタル、チタン、モリブデン、タングステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウム又は銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム、イットリウム等を用いることができる。<sub>30</sub>

**【0120】**

また、ソース電極層及びドレイン電極層935、936、937となる導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、更にその上にチタン膜を成膜する3層構造などが挙げられる。また、Cu-Mg-Al合金、Mo-Ti合金、Ti、Mo、は、酸化膜との密着性が高い。よって、下層にCu-Mg-Al合金、Mo-Ti合金、Ti、あるいはMoで構成される導電膜、上層にCuで構成される導電膜を積層し、上記積層された導電膜をソース電極層及びドレイン電極層935、936、937に用いることで、絶縁膜929と、これら電極層との密着性を高めることができる。<sub>40</sub>

**【0121】**

また、ソース電極層及びドレイン電極層935、936、937となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ混合物、酸化インジウム酸化亜鉛混合物又は

10

20

30

40

50

前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

**【0122】**

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

**【0123】**

本実施の形態では、ソース電極層及びドレイン電極層935、936、937として、膜厚100nmのタンゲステン膜を用いる。

**【0124】**

なお、導電膜のエッチングの際に、酸化物半導体膜933、934がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、酸化物半導体膜933、934の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

**【0125】**

本実施の形態では、ソース電極層及びドレイン電極層935、936、937となる導電膜に、タンゲステン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(アンモニア過水)を用いて、選択的に上記導電膜をウェットエッチングすることができる。具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と、水とを、体積比5:2:2で混合したアンモニア過水を用いる。あるいは、四弗化炭素(CF<sub>4</sub>)、塩素(Cl<sub>2</sub>)、酸素を含むガスを用いて、上記導電膜をドライエッチングしても良い。

**【0126】**

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことで更に形状を変形するため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

**【0127】**

また、酸化物半導体膜933、934と、ソース電極層及びドレイン電極層935、936、937との間に、ソース領域及びドレイン領域として機能する酸化物導電膜を設けるようにしてもよい。酸化物導電膜の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを適用することができる。

**【0128】**

例えば、酸化物導電膜を形成する場合、酸化物導電膜を形成するためのパターニングと、ソース電極層及びドレイン電極層935、936、937を形成するためのパターニングとを一括で行うようにしてもよい。

**【0129】**

ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、酸化物半導体膜933、934とソース電極層及びドレイン電極層935、936、937との間の抵抗を下げる所以ができるので、トランジスタの高速動作を実現させることができる。また、ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、トランジスタの耐圧を高めることができる。

**【0130】**

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行うようにしても良い。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

10

20

30

40

50

## 【0131】

なお、プラズマ処理を行った後、ソース電極層及びドレイン電極層935、936、937と、酸化物半導体膜933、934とを覆うように、ゲート絶縁膜938を形成する。そして、ゲート絶縁膜938上において、酸化物半導体膜933、934と重なる位置にゲート電極層939、940をそれぞれ形成する。

## 【0132】

ゲート絶縁膜938は、例えば酸化窒化珪素膜を用いて形成することができる。なお、ゲート絶縁膜938は、水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。ゲート絶縁膜938に水素が含まれると、その水素が酸化物半導体膜933、934へ侵入し、又は水素が酸化物半導体膜933、934中の酸素を引き抜き、酸化物半導体膜933、934が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。よって、ゲート絶縁膜938はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記ゲート絶縁膜938には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いることができる。複数の積層された絶縁膜を用いる場合、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体膜933、934に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、ソース電極層及びドレイン電極層935、936、937及び酸化物半導体膜933、934と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜933、934内、ゲート絶縁膜938内、あるいは、酸化物半導体膜933、934と他の絶縁膜の界面とその近傍に、水分又は水素などの不純物が入り込むのを防ぐことができる。また、酸化物半導体膜933、934に接するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体膜933、934に接するのを防ぐことができる。

## 【0133】

本実施の形態では、スパッタ法で形成された膜厚20nmの酸化窒化珪素膜をゲート絶縁膜938として用いる。成膜時の基板温度は、室温以上400以下とすればよく、本実施の形態では300とする。

## 【0134】

なお、ゲート絶縁膜938を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、又は希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。本実施の形態では、例えば、窒素雰囲気下で250、1時間の加熱処理を行う。あるいは、ソース電極層及びドレイン電極層935、936、937を形成する前に、水分又は水素を低減させるための酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含むゲート絶縁膜938が設けられた後に、加熱処理が施されることによって、酸化物半導体膜933、934に対して行った先の加熱処理により、酸化物半導体膜933、934に酸素欠損が発生していたとしても、ゲート絶縁膜938から酸化物半導体膜933、934に酸素が供与される。そして、酸化物半導体膜933、934に酸素が供与されることで、酸化物半導体膜933、934において、ドナーとなる酸素欠損を低減し、化学量論的組成を満たすことが可能である。その結果、酸化物半導体膜933、934をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この加熱処理を行うタイミングは、ゲート絶縁膜938の形成後であれば特に限定されず、他の工程と兼ねることで、工程数を増やすことなく酸化物半導体膜933、934をi型に近づけることができる。

## 【0135】

10

20

30

40

50

また、酸素雰囲気下で酸化物半導体膜933、934に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体膜933、934中においてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100以上350未満、好ましくは150以上250未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0136】

あるいは、イオン注入法又はイオンドーピング法などを用いて、酸化物半導体膜933、934に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45GHzのマイクロ波でプラズマ化した酸素を酸化物半導体膜933、934に添加すれば良い。

10

#### 【0137】

ゲート電極層939、940は、ゲート絶縁膜938上に導電膜を形成した後、該導電膜をパターニングすることで形成することができる。

#### 【0138】

ゲート電極層939、940は、10nm~400nm、好ましくは100nm~300nmとする。本実施の形態では、スパッタ法により膜厚30nmの窒化タンタル上に膜厚135nmのタンクステンを積層させてゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極層939、940を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

20

#### 【0139】

以上の工程により、OS-FET944、OS-FET945が形成される。

#### 【0140】

なお、上記作製方法では、ソース電極層及びドレイン電極層935、936、937が、酸化物半導体膜933、934の後に形成されている。よって、図6に示すように、上記作製方法によって得られるOS-FET944、OS-FET945は、ソース電極層及びドレイン電極層935、936、937が、酸化物半導体膜933、934の上に形成されている。しかし、OS-FET944、OS-FET945は、ソース電極層及びドレイン電極層935、936、937が、酸化物半導体膜933、934の下、すなわち、酸化物半導体膜933、934と絶縁膜929の間に設けられていても良い。

30

#### 【0141】

また、酸化物半導体膜933、934に接する絶縁膜は、第13族元素及び酸素を含む絶縁材料を用いるようにしても良い。酸化物半導体材料には第13族元素を含むものが多く、第13族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体膜に接する絶縁膜に用いることで、酸化物半導体膜との界面の状態を良好に保つことができる。

40

#### 【0142】

第13族元素を含む絶縁材料とは、絶縁材料に一又は複数の第13族元素を含むことを意味する。第13族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上のものを示す。

#### 【0143】

例えば、ガリウムを含有する酸化物半導体膜に接して絶縁膜を形成する場合に、絶縁膜に酸化ガリウムを含む材料を用いることで酸化物半導体膜と絶縁膜の界面特性を良好に保つ

50

ことができる。例えば、酸化物半導体膜と酸化ガリウムを含む絶縁膜とを接して設けることにより、酸化物半導体膜と絶縁膜の界面における水素のパイアルアップを低減することができる。なお、絶縁膜に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁膜を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体膜への水の侵入防止という点においても好ましい。

#### 【 0 1 4 4 】

また、酸化物半導体膜 9 3 3、9 3 4 に接する絶縁膜は、酸素雰囲気下による熱処理や、酸素ドープなどにより、絶縁材料を化学量論的組成より酸素が多い状態とすることが好ましい。酸素ドープとは、酸素をバルクに添加することをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。また、酸素ドープは、イオン注入法又はイオンドーピング法を用いて行ってもよい。

10

#### 【 0 1 4 5 】

酸素ドープ処理を行うことにより、化学量論的組成より酸素が多い領域を有する絶縁膜を形成することができる。このような領域を備える絶縁膜と酸化物半導体膜が接することにより、絶縁膜中の過剰な酸素が酸化物半導体膜に供給され、酸化物半導体膜中、又は酸化物半導体膜と絶縁膜の界面における酸素欠陥を低減し、酸化物半導体膜を  $i$  型化又は  $i$  型に限りなく近くすることができる。

20

#### 【 0 1 4 6 】

なお、化学量論的組成より酸素が多い領域を有する絶縁膜は、酸化物半導体膜 9 3 3、9 3 4 に接する絶縁膜のうち、上層に位置する絶縁膜又は下層に位置する絶縁膜のうち、どちらか一方のみに用いても良いが、両方の絶縁膜に用いる方が好ましい。化学量論的組成より酸素が多い領域を有する絶縁膜を、酸化物半導体膜 9 3 3、9 3 4 に接する絶縁膜の、上層及び下層に位置する絶縁膜に用い、酸化物半導体膜 9 3 3、9 3 4 を挟む構成とすることで、上記効果をより高めることができる。

#### 【 0 1 4 7 】

また、酸化物半導体膜 9 3 3、9 3 4 の上層又は下層に用いる絶縁膜は、上層と下層で同じ構成元素を有する絶縁膜としても良いし、異なる構成元素を有する絶縁膜としても良い。また、酸化物半導体膜 9 3 3、9 3 4 に接する絶縁膜は、化学量論的組成より酸素が多い領域を有する絶縁膜の積層としても良い。

30

#### 【 0 1 4 8 】

なお、本実施の形態においては、OS - FET 9 4 4、OS - FET 9 4 5 はトップゲート構造としているが、これらにバックゲート電極層（図示せず）を設けることもできる。バックゲート電極層は酸化物半導体膜を挟んでゲート電極層 9 3 9、9 4 0 に対向する位置に設けた電極層であり、該電極層に所定の電位を印加することで、OS - FET 9 4 4、OS - FET 9 4 5 のノーマリオフ化を実現することができる。例えば、バックゲート電極層の電位を GND や固定電位とすることで OS - FET 9 4 4、OS - FET 9 4 5 の閾値電圧をよりプラスとし、さらにノーマリオフのトランジスタとすることができる。

40

#### 【 0 1 4 9 】

以上のような MOSFET 9 0 3、MOSFET 9 0 4、OS - FET 9 4 4、OS - FET 9 4 5 を電気的に接続して保護回路部と検出部とを含む電気回路を形成するために、各階層間及び上層に接続のための配線層を単層又は多層積層する。

#### 【 0 1 5 0 】

図 6においては、実施の形態 1 で示した測定装置を形成するために、MOSFET 9 0 3 の不純物領域 9 0 5（ドレイン領域）は、コンタクトプラグ 9 2 2 を介して配線層 9 2 8 と電気的に接続する。配線層 9 2 8 は、高電位側の電位を付与する電源と電気的に接続し、電源供給線として機能する。MOSFET 9 0 3 の不純物領域 9 0 6（ソース領域）は

50

、MOSFET 904 の不純物領域 906 (ドレイン領域) と共有され、コンタクトプラグ 920 を介して配線層 926 と電気的に接続する。配線層 926 は、検出部の出力として機能する。MOSFET 904 の不純物領域 907 (ソース領域) は、コンタクトプラグ 918 を介して配線層 924 と電気的に接続する。配線層 924 は、低電位側の電位を付与する電源と電気的に接続し、電源供給線として機能する。MOSFET 903 のゲート電極層 909 は、コンタクトプラグ 921 、配線層 927 、コンタクトプラグ 931 を介して、OS-FET 944 と電気的に接続するドレイン電極層 936 と、OS-FET 945 と電気的に接続するソース電極層 936 とに電気的に接続する。また、MOSFET 904 のゲート電極層 913 は、コンタクトプラグ 919 を介して配線層 925 と電気的に接続する。配線層 925 は、MOSFET 904 のゲートに所定の電圧を印加するための配線として機能する。

10

#### 【0151】

OS-FET 944 と電気的に接続するソース電極層 935 は、コンタクトプラグ 932 を介して配線層 928 と電気的に接続する。また、OS-FET 945 と電気的に接続するドレイン電極層 937 は、コンタクトプラグ 930 を介して配線層 924 と電気的に接続する。さらに、OS-FET 944 と電気的に接続するドレイン電極層 936 と、OS-FET 945 と電気的に接続するソース電極層 936 とは、コンタクトプラグ 943 及び配線 947 を介して、プローブ針と電気的に接続する入力端子層 949 と電気的に接続する。

#### 【0152】

入力端子層 949 は、積層構造の最上層に位置し露出しているため、酸化されにくい導電性材料を用いることが好ましい。このため、例えば金等の薄膜を用いるとよい。また、ITO 等の酸化物半導体材料を用いてもよい。

20

#### 【0153】

配線層 924 、925 、926 、927 、928 及び 947 は、絶縁膜中に埋め込まれている。これらの配線層等は、例えば銅、アルミニウム等の低抵抗な導電性材料を用いることが好ましい。また、CVD 法により形成したグラフェンを導電性材料として用いて配線層を形成することもできる。グラフェンとは、 $s p^2$  結合を有する 1 原子層の炭素分子のシートのこと、または 2 乃至 100 層の炭素分子のシートが積み重なっているものをいう。このようなグラフェンを作製する方法として、金属触媒の上にグラフェンを形成する熱 CVD 法や、紫外光を照射して局所的にプラズマを発生させることで触媒を用いずにメタンからグラフェンを形成する plasma CVD 法などがある。

30

#### 【0154】

このような低抵抗な導電性材料を用いることで、配線層を伝播する信号の RC 遅延を低減することができる。配線層に銅を用いる場合には、銅のチャネル形成領域への拡散を防止するため、バリア膜を形成する。バリア膜として、例えば窒化タンタル、窒化タンタルとタンタルとの積層、窒化チタン、窒化チタンとチタンとの積層等による膜を用いることができるが、配線材料の拡散防止機能、及び配線材料や下地膜等との密着性が確保される程度においてこれらの材料からなる膜に限られない。バリア膜は配線層とは別個の層として形成してもよく、バリア膜となる材料を配線材料中に含有させ、加熱処理によって絶縁膜に設けられた開口の内壁に析出させて形成しても良い。

40

#### 【0155】

絶縁膜 917 、923 、942 、946 には、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、BPSG ( Boron Phosphorus Silicate Glass ) 、PSG ( Phosphorus Silicate Glass ) 、炭素を添加した酸化シリコン ( SiOC ) 、フッ素を添加した酸化シリコン ( SiOF ) 、Si(OCH<sub>2</sub>H<sub>5</sub>)<sub>4</sub> を原料とした酸化シリコンである TEOS ( Tetraethyl orthosilicate ) 、HSQ ( Hydrogen Silsesquioxane ) 、MSQ ( Methyl Silsesquioxane ) 、OSG ( Organo Silicate Glass ) 、有機ポリマー系の材料等の絶縁体を用いることができる。

50

特に半導体装置の微細化を進める場合には、配線間の寄生容量が顕著になり信号遅延が増大するため酸化シリコンの比誘電率 ( $k = 4.0 \sim 4.5$ ) では高く、 $k$  が 3.0 以下の材料を用いることが好ましい。また該絶縁膜に配線を埋め込んだ後に C M P 处理を行うため、絶縁膜には機械的強度が要求される。この機械的強度が確保できる限りにおいて、これらを多孔質(ポーラス)化させて低誘電率化することができる。絶縁膜は、スパッタリング法、C V D 法、スピンドルコート法(Spin On Glass: S O G ともいう)を含む塗布法等により形成する。

#### 【 0 1 5 6 】

絶縁膜 9 1 7、9 2 3、9 4 2、9 4 6 には、配線材料をこれら絶縁膜中に埋め込んだ後、C M P 等による平坦化処理を行う際のエッチングストップとして機能させるための絶縁膜を別途設けてもよい。10

#### 【 0 1 5 7 】

配線層 9 2 4、9 2 5、9 2 6、9 2 7、9 2 8 及び 9 4 7 上には、バリア膜が設けられており、バリア膜上に保護膜が設けられている。バリア膜は銅等の配線材料の拡散を防止することを目的とした膜である。バリア膜は、窒化シリコンや S i C、S i B O N 等の絶縁性材料で形成することができる。但し、バリア膜の膜厚が厚い場合には配線間容量を増加させる要因となるため、バリア性を有し、かつ低誘電率の材料を選択することが好ましい。

#### 【 0 1 5 8 】

コントラクトプラグ 9 1 8、9 1 9、9 2 0、9 2 1、9 2 2、9 3 0、9 3 1、9 3 2 及び 9 4 3 は、絶縁膜に高アスペクト比の開口(ビアホール)を形成し、タンゲステン等の導電材料で埋め込むことで作製する。開口は、異方性の高いドライエッチングを行うことが好ましい。特に、反応性イオンエッチング法(R I E 法)を用いることが好ましい。開口の内壁にはチタン膜、窒化チタン膜又はこれらの積層膜等からなるバリア膜(拡散防止膜)が設けられ、バリア膜の内部にタンゲステンやリン等をドープしたポリシリコン等の材料が充填される。例えばプランケット C V D 法により、ビアホール内にタンゲステンを埋め込むことができ、C M P によりコントラクトプラグの上面は平坦化されている。20

#### 【 0 1 5 9 】

また配線 9 4 7 及び絶縁膜 9 4 6 の上層には保護絶縁膜 9 4 8 が設けられ、外部から水分や汚染物が測定装置へ侵入するのを防止する。保護絶縁膜 9 4 8 は、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の材料を用いて形成することができ、単層でも積層でもよい。30

#### 【 0 1 6 0 】

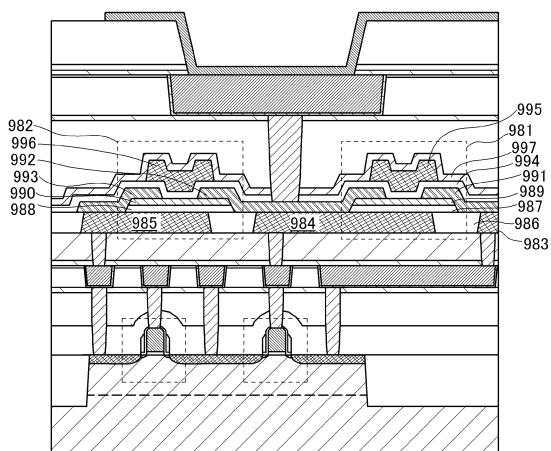

次に、O S - F E T の他の構造の一例として、ボトムゲート構造の O S - F E T を保護回路部に用いた場合の断面構造を、図 7 を用いて説明する。

#### 【 0 1 6 1 】

図 7 は、実施の形態 1 で説明した測定装置における保護回路部 2 1 0 及び検出部 2 1 1 の回路構成を断面構造として具現したものを見せる図である。図 6 で示した断面構造に対して、保護回路部の O S - F E T の構造をボトムゲート構造とした点のみが異なる。酸化物半導体を用いた O S - F E T 9 8 1、O S - F E T 9 8 2 が、実施の形態 1 における O S - F E T 2 0 3、O S - F E T 2 0 4 に相当する。図 7 に示す測定装置も、シリコンウェハを基板として、その上層に酸化物半導体膜が設けられた三次元の積層構造を有する測定装置であり、また、シリコンをチャネル形成領域に用いたトランジスタと酸化物半導体をチャネル形成領域に用いたトランジスタとを有するハイブリッド型の測定装置である。40

#### 【 0 1 6 2 】

O S - F E T 9 8 1 は、ゲート電極層 9 8 4 と、ゲート絶縁膜 9 8 7 を間に挟んでゲート電極層 9 8 4 上に設けられたチャネル形成領域を含む酸化物半導体膜 9 8 9 とを有する。酸化物半導体膜 9 8 9 の上面及び側面の一部に接してソース電極層 9 9 1 及びドレイン電極層 9 9 2 が設けられている。また、酸化物半導体膜 9 8 9 が有するチャネル形成領域の上方には、絶縁膜 9 9 4 を間に挟んでバックゲート電極層 9 9 5 が設けられ、これらは絶50

縁膜 997 に覆われている。

#### 【0163】

同様に、OS-FET982は、ゲート電極層985と、ゲート絶縁膜988を間に挟んでゲート電極層985上に設けられたチャネル形成領域を含む酸化物半導体膜990とを有する。酸化物半導体膜990の上面及び側面の一部に接してソース電極層992及びドレイン電極層993が設けられている。また、酸化物半導体膜990が有するチャネル形成領域の上方には、絶縁膜994を間に挟んでバックゲート電極層996が設けられ、これらは絶縁膜997に覆われている。

#### 【0164】

ゲート電極層984、985及び電極層983は、所望の形状に加工された後、絶縁膜986で被覆され、CMP処理によって平坦化されている。この平坦面上にゲート絶縁膜987、988と酸化物半導体膜989、990が積層され、エッチング処理により島状のパターンに形成されている。従って、ソース電極層及びドレイン電極層991、992、993は酸化物半導体膜989、990及びゲート絶縁膜987、988の側面に接する。

#### 【0165】

OS-FET981において、ドレイン電極層992はゲート電極層984と電気的に接続する。また、OS-FET982において、ドレイン電極層993はゲート電極層985と電気的に接続する。このようにして、ダイオード接続されたボトムゲート構造のOS-FET981、982による保護回路部が積層上層に形成されている。

#### 【0166】

なお、図7においては、各OS-FETにバックゲート電極層を形成している。バックゲート電極層に所定の電位を印加することで、OS-FET981、OS-FET982のノーマリオフ化を実現することができる。例えば、バックゲート電極層の電位をGNDや固定電位とすることでOS-FET981、OS-FET982の閾値電圧をよりプラスとし、さらにノーマリオフのトランジスタとすることができます。

#### 【0167】

測定装置を以上のような構成とすることで、所定のESD耐性が確保され、また漏れ電流を小さくすることができるため、被測定物に影響を与えることなく、長時間にわたって正確な電圧を測定することができる。

#### 【0168】

また、検出部に設けられた電圧検出用のMOSFETと、保護回路とを極めて近接して設けることができるため、これらを異なる素子基板に設けた場合に生じる基板間の接続部におけるESDの発生や、漏れ電流の発生を抑制することができる。

#### 【0169】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【符号の説明】

#### 【0170】

100 画素回路

101 OS-FET

102 ゲート信号線

103 ソース信号線

104 容量素子

105 液晶素子

106 プローブ

107 ノード

201 プローブ針

202 MOSFET

203 OS-FET

204 OS-FET

10

20

30

40

50

|       |             |    |

|-------|-------------|----|

| 2 0 5 | M O S F E T |    |

| 2 0 6 | 出力端子        |    |

| 2 0 7 | 電源線         |    |

| 2 0 8 | 電源線         |    |

| 2 0 9 | 配線          |    |

| 2 1 0 | 保護回路部       |    |

| 2 1 1 | 検出部         |    |

| 3 0 1 | プローブ針       |    |

| 3 0 2 | M O S F E T | 10 |

| 3 0 3 | O S - F E T |    |

| 3 0 4 | O S - F E T |    |

| 3 0 5 | 出力端子        |    |

| 3 0 6 | 電源線         |    |

| 3 0 7 | 保護回路部       |    |

| 3 0 8 | 検出部         |    |

| 4 0 1 | プローブ針       |    |

| 4 0 2 | M O S F E T |    |

| 4 0 3 | O S - F E T |    |

| 4 0 4 | O S - F E T |    |

| 4 0 5 | M O S F E T | 20 |

| 4 0 6 | 出力端子        |    |

| 4 0 7 | 電源線         |    |

| 4 0 8 | 電源線         |    |

| 4 0 9 | 配線          |    |

| 4 1 0 | 保護回路部       |    |

| 4 1 1 | 検出部         |    |

| 5 0 1 | プローブ針       |    |

| 5 0 2 | M O S F E T |    |

| 5 0 3 | O S - F E T |    |

| 5 0 4 | O S - F E T | 30 |

| 5 0 5 | 出力端子        |    |

| 5 0 6 | 電源線         |    |

| 5 0 7 | 保護回路部       |    |

| 5 0 8 | 検出部         |    |

【図1】

(A)

(B)

【図2】

(A)

(B)

【図3】

【図5】

【図4】

【図6】

【図7】

---

フロントページの続き

| (51)Int.Cl.             | F I             |

|-------------------------|-----------------|

| H 01 L 21/822 (2006.01) | H 01 L 27/088 F |

| H 01 L 27/04 (2006.01)  | H 01 L 27/088 E |

|                         | H 01 L 27/04 H  |

(56)参考文献 特開昭56-038853(JP,A)

特開2011-135049(JP,A)

特開2012-053866(JP,A)

特開2011-176294(JP,A)

米国特許出願公開第2003/0184507(US,A1)

(58)調査した分野(Int.Cl., DB名)

|        |                   |

|--------|-------------------|

| G 01 R | 19 / 00 - 19 / 32 |

| H 01 L | 21 / 336          |

| H 01 L | 21 / 822          |

| H 01 L | 21 / 8234         |

| H 01 L | 27 / 04           |

| H 01 L | 27 / 088          |

| H 01 L | 29 / 786          |