【公報種別】特許公報の訂正

【部門区分】第1部門第2区分

【発行日】令和4年6月3日(2022.6.3)

【特許番号】特許第7059258号(P7059258)

【登録日】令和4年4月15日(2022.4.15)

【特許公報発行日】令和4年4月25日(2022.4.25)

【年通号数】登録公報(特許)2022-072

【出願番号】特願2019-511734(P2019-511734)

【訂正要旨】特許権者の住所の誤載により、下記のとおり全文を訂正する。

10

【国際特許分類】

A 6 1 B 8/00(2006.01)

【F I】

A 6 1 B 8/00

【記】別紙のとおり

20

30

40

50

(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7059258号

(P7059258)

(45)発行日 令和4年4月25日(2022.4.25)

(24)登録日 令和4年4月15日(2022.4.15)

(51)国際特許分類

A 6 1 B 8/00 (2006.01)

F I

A 6 1 B

8/00

請求項の数 14 (全19頁)

(21)出願番号 特願2019-511734(P2019-511734)

(86)(22)出願日 平成29年8月17日(2017.8.17)

(65)公表番号 特表2019-526351(P2019-526351)

A)

(43)公表日 令和1年9月19日(2019.9.19)

(86)国際出願番号 PCT/EP2017/070804

(87)国際公開番号 WO2018/041636

(87)国際公開日 平成30年3月8日(2018.3.8)

審査請求日 令和2年8月13日(2020.8.13)

(31)優先権主張番号 16193675.2

(32)優先日 平成28年10月13日(2016.10.13)

(33)優先権主張国・地域又は機関

歐州特許庁(EP)

(31)優先権主張番号 62/382,811

(32)優先日 平成28年9月2日(2016.9.2)

最終頁に続く

(73)特許権者 590000248

コーニンクレッカ フィリップス エヌ

ヴェ

Koninklijke Philips

N. V.

オランダ国 5656 アーヘー アイン

ドーフェン ハイテック キャンパス 5

110001690

(74)代理人 特許業務法人M & S パートナーズ

セイヴォルド ベルナルド ヨセフ

オランダ国 5656 アーヘー アイン

ドーフェン ハイ テック キャンパス 5

(72)発明者 ファン レンズ アントニア コルネリア

オランダ国 5656 アーヘー アイン

ドーフェン ハイ テック キャンパス 5

最終頁に続く

(54)【発明の名称】 マルチラインデジタルマイクロビーム形成器を含む超音波プローブ

## (57)【特許請求の範囲】

## 【請求項1】

デジタルマイクロビーム形成器と、

アレイトランスデューサであって、前記デジタルマイクロビーム形成器の制御下において前記アレイトランスデューサの素子を使用して対象領域をスキャンする、当該アレイトランスデューサと

を備え、

前記デジタルマイクロビーム形成器が、

前記アレイトランスデューサの前記素子に結合され、かつ受信期間中、前記アレイトランスデューサの前記素子からアナログエコー信号を受信する複数の増幅器であって、複数の増幅されたアナログエコー信号を提供する、当該複数の増幅器と、

前記増幅器に結合され、かつ前記増幅されたアナログエコー信号を受信し、かつ前記増幅されたアナログエコー信号をデジタルエコー信号に変換する複数のA D Cと、

前記複数のA D Cの各A D Cについて、当該A D Cに結合され、かつ複数の選択可能に遅延された前記デジタルエコー信号を生成する複数のデジタル遅延回路と、

前記複数のデジタル遅延回路に結合され、かつ前記複数の選択可能に遅延されたデジタルエコー信号を受信する複数のデジタル加算器と

を備える超音波プローブであって、

前記複数の選択可能に遅延されたデジタルエコー信号が、マルチライン信号であり、前記複数のデジタル加算器が、複数のデジタルマルチラインエコー信号を生成し、

前記複数の A D C が、複数の低電力逐次近似型 A D C を備える、

超音波プローブ。

【請求項 2】

前記デジタルマイクロビーム形成器が、前記アレイトランステューサの前記素子に結合され、かつ連続した送信パルス事象を生成する複数の送信器をさらに備え、

前記複数のデジタル加算器が、前記連続した送信パルス事象における単一の送信パルス事象に応答して、前記複数のデジタルマルチラインエコー信号を生成する、

請求項 1 に記載の超音波プローブ。

【請求項 3】

前記デジタル遅延回路のうちの少なくとも 1 つが、書き込みアドレス制御装置と読み出しアドレス制御装置とを含むランダムアクセスメモリを備え、

前記少なくとも 1 つのデジタル遅延回路に対するデジタル遅延が、前記デジタルエコー信号の書き込み及び読み出しがアドレス指定の関数である、

請求項 1 に記載の超音波プローブ。

【請求項 4】

前記読み出しアドレス制御装置が、動的に焦点処理された前記ランダムアクセスメモリからの遅延された前記デジタルエコー信号を読み出す、

請求項 3 に記載の超音波プローブ。

【請求項 5】

前記ランダムアクセスメモリに結合された複数の読み出しアドレス制御装置をさらに備え、

各前記読み出しアドレス制御装置が、前記複数のデジタルマルチラインエコー信号を生成するために、複数の選択可能に遅延された前記デジタルエコー信号の読み取りを制御する、

請求項 3 に記載の超音波プローブ。

【請求項 6】

各前記デジタル遅延回路が、4 つの前記デジタルマルチラインエコー信号を生成するため

に、前記複数のデジタル加算器に結合された、

請求項 1 に記載の超音波プローブ。

【請求項 7】

各前記デジタル遅延回路が、8 つの前記デジタルマルチラインエコー信号を生成するため

に、前記複数のデジタル加算器に結合された、

請求項 1 に記載の超音波プローブ。

【請求項 8】

各前記デジタル遅延回路が、8 つを上回る前記デジタルマルチラインエコー信号を生成す

るために、前記複数のデジタル加算器に結合された、

請求項 1 に記載の超音波プローブ。

【請求項 9】

前記デジタルマイクロビーム形成器が、複数のデジタルチャンネルとしてさらに構成され

、各前記デジタルチャンネルが、前記複数の A D C のうちの 1 つの低電力 A D C と、前記

複数のデジタル遅延回路のうちの 1 つのデジタル遅延回路と、前記複数のデジタル加算器

のうちの少なくともいくつかのデジタル加算器とを備え、各前記デジタルチャンネルが複

数の前記デジタルマルチラインエコー信号を生成する、

請求項 1 に記載の超音波プローブ。

【請求項 10】

前記複数のデジタルチャンネルのうちの少なくともいくつかのデジタルチャンネルの前記

デジタル加算器が、複数の前記デジタルチャンネルからの遅延された前記デジタルエコー

信号を組み合わせるように一緒に結合され、かつ前記複数のデジタルマルチラインエコー

信号を生成する、

請求項 9 に記載の超音波プローブ。

【請求項 11】

10

20

30

40

50

前記複数のデジタルチャンネルのうちの少なくともいくつかのデジタルチャンネルが、同時に前記デジタルマルチラインエコー信号を生成する、

請求項 10 に記載の超音波プローブ。

【請求項 12】

前記複数のデジタルチャンネルのうちの少なくともいくつかのデジタルチャンネルが、並行して前記デジタルマルチラインエコー信号を生成する、

請求項 11 に記載の超音波プローブ。

【請求項 13】

前記デジタル加算器により生成された前記複数のデジタルマルチラインエコー信号を受信するように結合された F P G A をさらに備える、

請求項 12 に記載の超音波プローブ。

10

【請求項 14】

前記 F P G A に結合され、かつ前記デジタルマルチラインエコー信号をディスプレイシステムに通信する、

U S B 制御装置をさらに備える、請求項 13 に記載の超音波プローブ。

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、医療診断超音波システムに関し、特に、マルチラインデジタルマイクロビーム形成器を含む超音波プローブに関する。

**【背景技術】****【0002】**

超音波アレイトランスデューサは、ビーム形成器を使用して、トランスデューサアレイの素子から受信された超音波エコー信号を送信し、適切に遅延させ、かつ加算する。遅延は、ビーム形成器により形成されるビームの方向（操舵）及び焦点深度を考慮して選択される。各素子から受信された信号がビーム形成器のチャンネルにより適切に遅延された後、遅延された信号が組み合わされて、適切に操舵及び合焦されたコヒーレントエコー信号のビームが形成される。超音波ビーム送信中、個々の素子の作動の時点は、送信ビームを操舵し、合焦させる受信遅延の相補的部分である。遅延の選択は、アレイ素子のジオメトリ、及びビームにより検査される像フィールドのジオメトリから決定可能なことが知られている。

10

**【0003】**

従来の超音波システムにおいて、アレイトランスデューサは、像形成中に患者の体に触れて配置されるプローブ内に位置し、調整素子、スイッチ、及び増幅デバイスなどのいくつかの電子コンポーネントを含む。遅延及び信号の組み合わせは、超音波システムメインフレームに含まれるビーム形成器により実行され、プローブはケーブルにより超音波システムメインフレームに接続される。

20

**【0004】**

アレイトランスデューサ及びビーム形成器のための前述のシステムアーキテクチャは、大多数の一次元（1D）トランスデューサアレイに対してまさしく十分でありトランスデューサ素子の数及びビーム形成器チャンネルの数は概ね同じである。トランスデューサ素子の数がビーム形成器チャンネルの数より多いとき、一般的に多重化が使用され、トランスデューサの素子の総数の部分集合のみが、任意の時点でビーム形成器に接続され得る。1Dアレイにおける素子の数は、100未満から数百に及ぶことがあり、一般的なビーム形成器は、128個のビーム形成器チャンネルを有する。このシステムアーキテクチャの解決策は、二次元及び三次元（3D）像形成のための二次元（2D）アレイトランスデューサの出現に伴って支持できなくなった。それは、2Dアレイトランスデューサがボリュメトリック領域にわたり方位角と仰角との両方においてビームを操舵及び合焦させるからである。このビーム形成に必要なトランスデューサ素子の数は、通常、数千である。従って、本問題の最も重要な点は、ビーム形成器が位置するシステムメインフレームにプローブを接続するケーブルとなる。たとえ最良の伝導フィラメントの数千の伝導体のケーブルであっても、厚くて扱い難くなるので、プローブの操作を不可能ではないとしても煩わしいものにする。

30

**【0005】**

この問題に対する解決策は、米国特許第5,229,933号（Larson, III）において説明されているように、プローブ自体におけるビーム形成のうちの少なくともいくつかを実行することである。この特許に示される超音波システムでは、ビーム形成は、プローブとシステムメインフレームとの間で仕切られる。素子のグループの初期ビーム形成は、部分的にビーム形成された加算結果が生成されるマイクロビーム形成器として知られるマイクロ回路によりプローブ内において行われる。トランスデューサ素子の数より少ない数のこれらの部分的にビーム形成された加算結果が、相応の寸法のケーブルを通してシステムメインフレームに結合され、システムメインフレームにおいてビーム形成処理が完了となり、最終的なビームが生成される。プローブ内における部分的ビーム形成は、アレイトランスデューサに装着されたマイクロ電子機器の形態のマイクロビーム形成器において、Larson, IIIがグループ内プロセッサと呼ぶものにより行われる。米国特

40

50

許第5,997,479号(Savordら)、米国特許第6,013,032号(Savord)、米国特許第6,126,602号(Savordら)、及び米国特許第6,375,617号(Fraser)も参照されたい。トランスデューサアレイの何千もの素子とマイクロビーム形成器との間における何千もの接続が、小さな寸法のマイクロ回路及びアレイピッチにおいて実現されるとともに、マイクロビーム形成器とシステムメインフレームのビーム形成器との間における多くのより少ないケーブル接続が、前の従来のケーブル技術により実現される。米国特許第7,821,180号(Kunkel, III)及び米国特許第7,927,280号(Davidson)に示される湾曲したアレイなどの、様々な平面の、及び湾曲したアレイ形式がマイクロビーム形成器とともに使用され得る。マイクロビーム形成器は、また、一次元アレイとともに、及び一次元アレイとして動作するようにされた2Dアレイとともに使用され得る。例えば米国特許第7,037,264号(Poland)を参照されたい。

10

#### 【0006】

現在、長年にわたって超音波システムにおけるビーム形成がデジタルで行われている。受信された信号は、クロックトシフトレジスタにより、又はランダムアクセスメモリでの一時記憶の時間だけ遅延され、遅延された信号はデジタル加算装置により加算される。デジタルビーム形成は、FPGA(フィールドプログラマブル可能ゲートアレイ:field programmable gate array)などの回路において、又はマイクロプロセッサにおけるソフトウェア命令により実行され得る。しかし、デジタルでビーム形成を実行するためには、受信された信号は、まず、アナログ・デジタルコンバータによりデジタル化されなければならない。現在の市販のマイクロビーム形成器を含む超音波プローブでは、部分的加算信号は、マイクロビーム形成器において、受信されたエコー信号に対してそれらの本来のアナログ領域で演算することにより形成される。アナログ部分的加算信号はプローブケーブルを通してシステムメインフレームに結合され、システムメインフレームにおいて、アナログ部分的加算信号がデジタル化され、ビーム形成がデジタルドメインにおいて完了となる。最近、ビーム形成技術は、Philips HealthcareのLumify(商標)超音波製品のL12-4リニア及びC5-2湾曲アレイプローブにおいてさらに統合されている。デジタル化及びデジタルビーム形成は、信号検出及びスキャン変換による像形成と同様に、プローブのハンドル内に位置するマイクロ回路により実行される。しかし、これらのプローブは、3D像形成のための2Dアレイプローブのトランスデューサ素子よりはるかに少ないトランスデューサ素子を含む1D(一次元)アレイトランスデューサを使用する。1Dアレイ(二次元像形成)プローブ及び2Dアレイ(三次元像形成)プローブのいずれの場合にも、ビーム形成回路全体がプローブ内に位置することが望ましい。

20

#### 【0007】

2Dアレイトランスデューサを使用した三次元像形成は、3D像を形成するために多くのスキャンラインが送信及び受信されなければならないというさらなる問題を提起する。リアルタイムの表示フレームレートでこれを実行するために、各送信ビームに応答して複数のスキャンラインを受信することが望ましく、これは、マルチラインスキャニングと呼ばれる技術である。例えば米国特許第5,318,033号(Savord)を参照されたい。米国特許第8,137,272号(Cooleyら)において説明されているように、合成送信焦点像を生成するために高次マルチラインも使用される。米国特許第6,471,652号(Fraserら)は、マイクロビーム形成器においてマルチラインエコー信号を実行することを提案するが、これはアナログ領域において行われ、より高次のマルチラインが超音波システムビーム形成器において実行される。マイクロビーム形成器においてデジタルマルチラインを生成し、完全にマルチラインシステムビーム形成器を不要とすることが望ましい。

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

40

50

ビーム形成回路のすべてをプローブ内に統合するときに解決されなければならない問題は、マイクロ回路による電力消費に起因する。この問題は、回路からの熱放散である。スキヤニング中、プローブは超音波検査技師の手によって保持されるので、プローブの内部回路により生成された熱のすべてが、プローブに触ると温かく感じさせることになる。場合によっては、プローブハンドルは、触ると不快なほど熱く感じることがあり、これは防止されなければならない問題である。米国特許出願公開第2014/0058270号(David senら)及び米国特許出願公開第2015/0099978号(David senら)において説明されているものなど、プローブから熱を伝導・除去し、結果的に熱がユーザから消散する能動的なシステムに加えて、受動的なプローブ冷却装置が考案された。しかし、このような装置は、コストを大幅に上げ、プローブ及びプローブのケーブルの複雑さを増大させる。マイクロ回路による電力消費がより少ないはるかに簡単な手法により、このような装置を避けることが望ましい。

10

【0009】

文献EP0815793は、Bモード及びドップラー像形成のための手持ち式超音波器具を開示する。器具は、アレイトランスデューサ、デジタルビーム形成器、デジタルフィルタ、及び像プロセッサを含む。

【0010】

文献米国特許第6208189号は、像形成システムの動的に遅延されたデジタルサンプルストリームにおけるひずみを低減する方法及び装置を開示する。この装置は、各送信サイクルにおいていくつかの同時受信ビームを生成するマルチビームビーム形成器を含む。

20

【課題を解決するための手段】

【0011】

本発明は、請求項により定義される。

【0012】

本発明の原理により、超音波プローブにおいてデジタルビーム形成を実行するマイクロビーム形成器回路が説明される。本発明は、低電力コンポーネントを備える超音波プローブの完全な超音波像形成機能を可能にする低電力コンポーネントのユニークな組み合わせを提供する。電力消費は、デルタシグマ、逐次近似アナログ・デジタル変換などの低電力デジタル・アナログ変換技術を使用することにより低減される。デジタル変換に続いて、受信されたエコー信号が同じ送信パルス事象のエコーから複数の異なるマルチライン信号を形成するために使用され得るように、デジタル遅延回路が受信されたエコー信号に選択可能に異なる遅延を印加する。マルチラインの次数は、設計者により選択された結果に応じて、4つ、8つ、又はより高次のマルチラインである。

30

【0013】

好ましい実施形態において、デジタルマイクロビーム形成器は、アレイトランスデューサのトランスデューサ素子からの信号を受信及び増幅する。受信されたアナログエコー信号は、低電力逐次近似型ADCなどのADC(アナログ・デジタルコンバータ:analog to digital converter)によりデジタル化され、ランダムアクセスメモリ、シフトレジスタなどのデジタル遅延に印加される。各デジタル遅延は、単一の送信事象に応答して、送信事象に応答した複数のデジタルマルチラインエコー信号を生成するために、デジタル加算器により他の遅延のデジタルエコー信号と組み合わされた複数の選択可能に遅延されたデジタルエコー信号を生成する。複数のマルチラインエコー信号の生成は、表示のためにリアルタイムのフレームレートで3D像が生成されることを可能にし、プローブにより生成されたマルチラインエコー信号は、スマートフォン、タブレット、ラップトップコンピュータなどの共通の処理及びディスプレイデバイスによる即時の使用に適したデジタル形式である。

40

【図面の簡単な説明】

【0014】

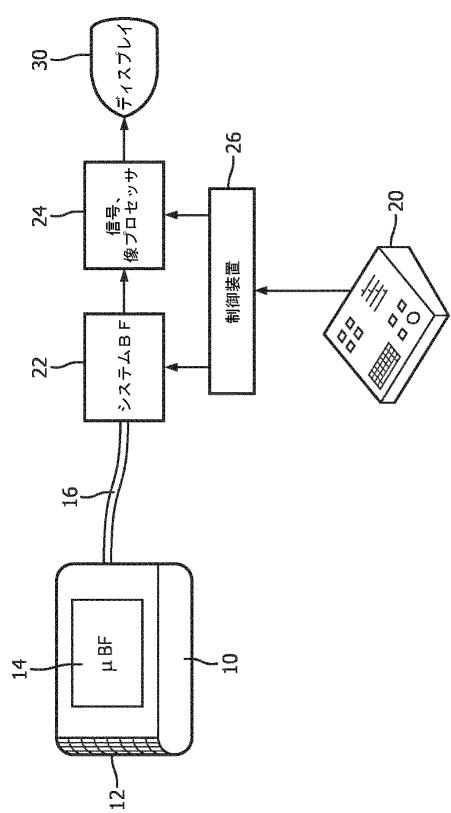

【図1】本発明の原理により構築された超音波像形成システムをブロック図の形態で示す図である。

50

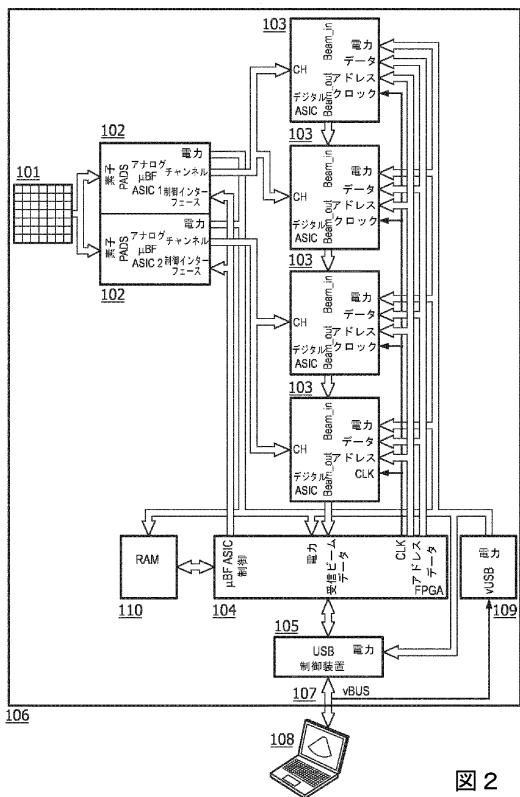

【図2】ディスプレイデバイスとしてのポータブルコンピュータに結合された本発明の超音波プローブのマイクロビーム形成回路及びトランスデューサアレイをブロック図の形態で示す図である。

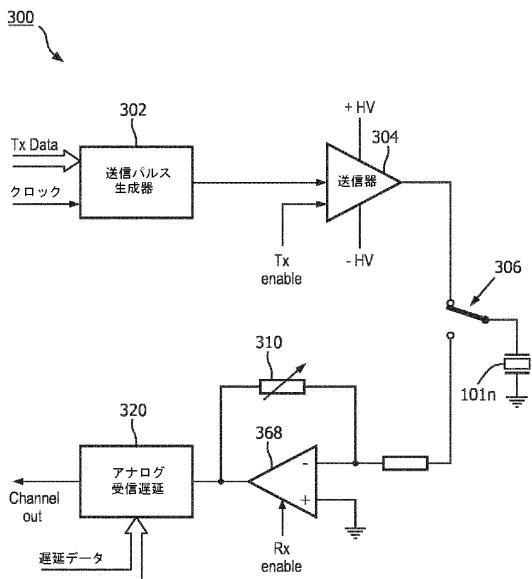

【図3】図2におけるマイクロビーム形成器のアナログASICのコンポーネントをブロック図の形態で示す図である。

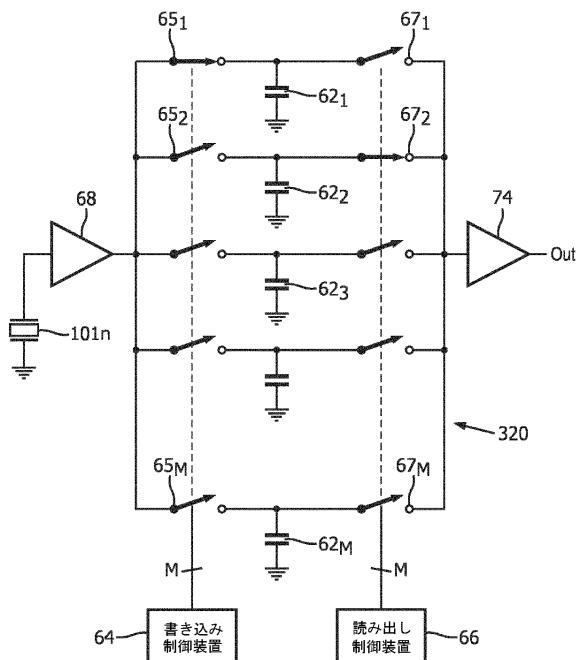

【図4】図3におけるアナログASICのアナログ受信遅延の回路図である。

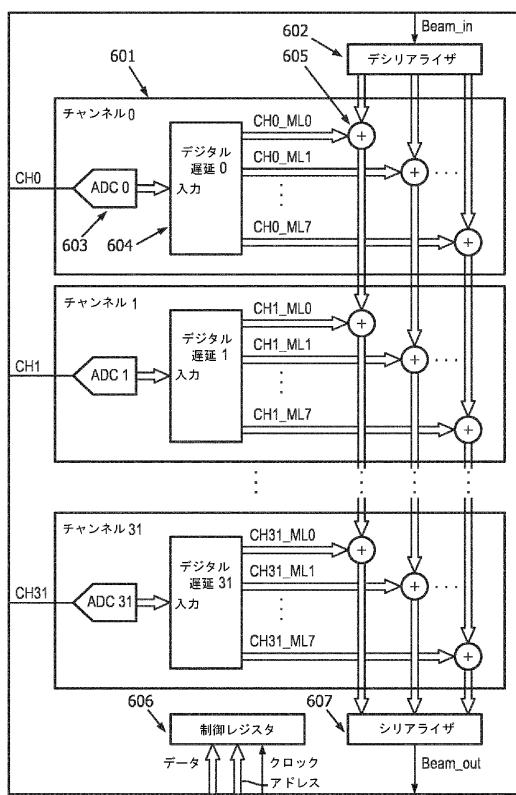

【図5】図3のデジタルADC(アナログ・デジタルコンバータ)及びビーム形成ASICのコンポーネントをブロック図の形態で示す図である。

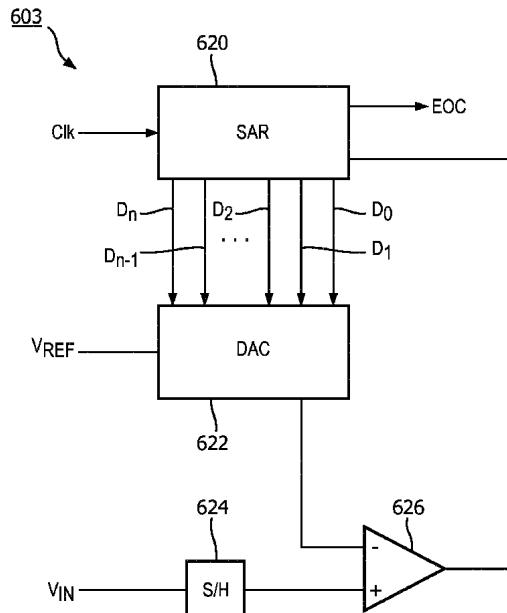

【図5a】図5のデジタルASICにおける使用に適した逐次近似アナログ・デジタルコンバータをブロック図の形態で示す図である。

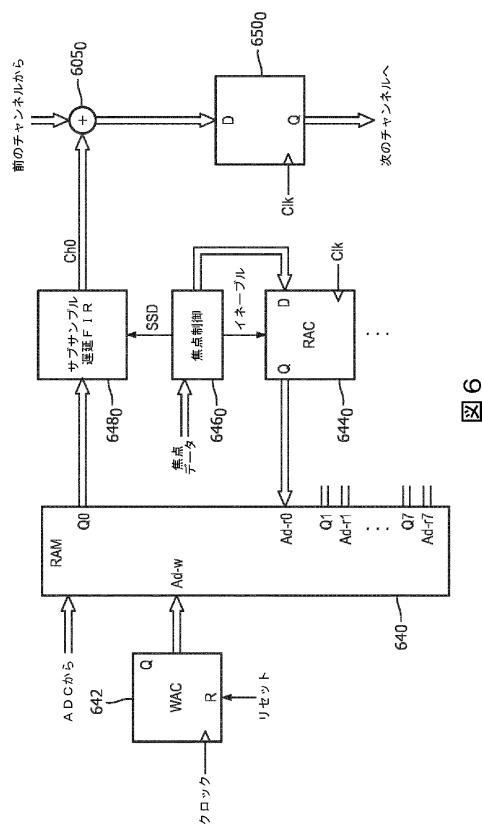

【図6】図5におけるデジタルASICの1つのチャンネルのデジタル遅延、遅延制御、及び加算回路を示す図である。

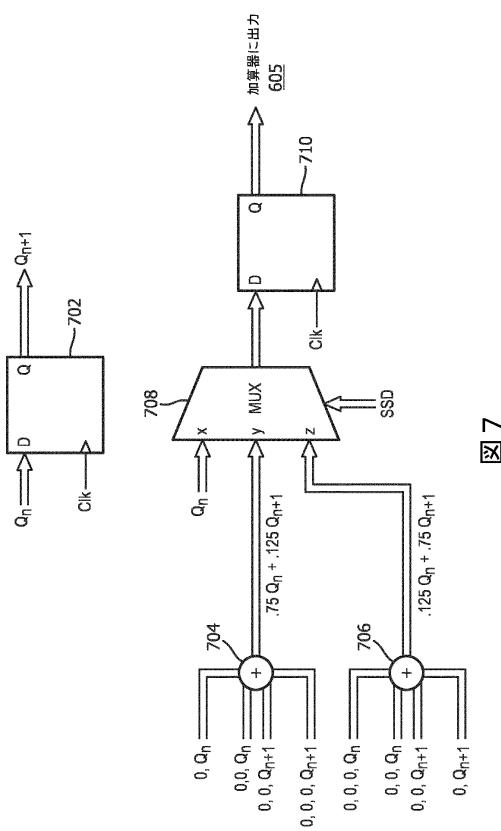

【図7】図5に示すデジタルASICにおけるサブサンプル遅延のために使用されるデジタルFIR(有限インパルス応答)フィルタを示す図である。

【図8】図7に示すサブサンプル遅延FIRにより生成された異なる遅延を伴うエコー信号波形を示す図である。

【発明を実施するための形態】

【0015】

まず図1を参照すると、本発明の原理により構築された超音波システムがブロック図の形態で示される。プローブ10は、平面であるか、又はこの例において示されるように湾曲したものである二次元アレイトランスデューサ12を含む。トランスデューサは、CMUT(マイクロマシニング加工された静電容量型超音波トランスデューサ:capacitive micro-machined ultrasonic transducer)又はPVDFなどのMUTデバイスから形成されるが、好ましくは、PZTなどの圧電セラミック材料から形成される。アレイの素子は、トランスデューサアレイの後方においてプローブ内に位置するデジタルマイクロビーム形成器14に結合される。マイクロビーム形成器は、2Dアレイトランスデューサ12の素子に結合されたビーム形成チャンネルを含むプローブ内に位置する集積回路である。マイクロビーム形成器は、アレイの素子の各グループ(パッチ)の素子にタイミング制御された送信パルスを印加して、所望の方向に、またアレイの前における像フィールド内の所望の焦点にビームを送信する。仰角の次元における送信ビームのプロファイルは、点焦点、平面波、又は任意の中間のビームプロファイルを示し得る。送信されたビームから細胞及び組織により返されたエコーは、アレイ素子により受信され、マイクロビーム形成器14のチャンネルに結合され、マイクロビーム形成器14においてアナログエコー信号が個々に遅延させられる。トランスデューサ素子の隣接したパッチからの遅延された信号は、組み合わされてパッチに対する部分的加算信号を形成する。以下でより完全に説明されるマイクロビーム形成器のアナログセクションでは、組み合わせることが、パッチの素子からの遅延された信号を共通バスに結合することにより行われ、加算回路を不要とする。次に、アナログエコー信号がデジタル化され、デジタルASIC(特定用途向け集積回路:application specific integrated circuit)によりデジタル形式でさらにビーム形成される。各パッチのビーム形成されたデジタル信号は、ケーブル16により超音波システムにおけるシステムビーム形成器22に結合され、システムビーム形成器22においてビーム形成処理が完了となる。代替的に、好ましい実施態様において、ビーム形成のすべてがプローブ内のマイクロビーム形成器により実行され、完全にビーム形成されたデジタル信号がシステムメインフレームに結合される。ビーム形成されたデジタル信号は、ベースバンド検出、高調波分離、フィルタ処理、ドップラー処理、及び像形成のためのスキャン変換などの動作を実行する信号及び像プロセッサ24により、像を形成するために使用される。信号及び像プロセッサ24は、像ディスプレイ30における表示のために2D又は3D像を生成する。信号及び像プロセッサは、電子ハードウェアコンポーネント、ソフトウェアにより制御されるハードウェア、又は像処理アルゴリズムを実行するマイクロプロセッサ

10

20

30

40

50

を備える。信号及び像プロセッサは、通常、スキャンコンバータなど、受信されたエコードを所望の表示形式の像のための像データへと処理する特殊なハードウェア又はソフトウェアをさらに含む。

【0016】

プローブ選択、ビーム操舵及び合焦、並びに信号及び像処理などの超音波システムパラメータの制御は、以下でより完全に説明されるように、システムの様々なモジュール及びプローブ10内のマイクロビーム形成器に結合されたシステム制御装置26の制御下で行われる。システム制御装置は、ASIC回路又はマイクロプロセッサ回路、及び、RAM、ROM、又はディスクドライブなどのソフトウェアデータ記憶デバイスにより形成される。プローブ10の場合、この制御情報のうちのいくつかが、ケーブル16のデータ線を通してシステムメインフレームからマイクロビーム形成器に提供され、特定のスキャニング手順のために必要とされる通り、トランスデューサアレイの動作のためにマイクロビーム形成器を調整する。ユーザは、制御パネル20によりこれらの動作パラメータを制御する。

【0017】

図2は、8×8パッチとして構成された64個の素子の128個のグループにおいて動作するようにされた8192個のトランスデューサ素子を含む2D(二次元)マトリックスアレイトランスデューサ101を動作させる超音波プローブ106におけるデジタルマイクロビーム形成器を示す。図示された実施形態におけるマイクロビーム形成器は、2つのアナログASIC102を備え、各々が、マトリックスアレイ101の素子の半分に結合される。アナログASICは、以下でより完全に説明される通り、送信回路、送信/受信(T/R)スイッチ、前置増幅用増幅器、及びアナログ遅延を含む。アナログASIC102は、低電力アナログ・デジタルコンバータ及びデジタルビーム形成回路を含むマイクロビーム形成器の4つのデジタルASIC103に結合される。FPGA104は、本例においてラップトップコンピュータ108として示される制御及びディスプレイデバイスを動作させるユーザから制御データを受信する。制御及びディスプレイデバイスは、代替的に、カート搭載型超音波システム、タブレットコンピュータ、PDA、スマートフォン、又はディスプレイ及びユーザインターフェースを含む同様のデジタルデバイスであり得る。FPGAは、マイクロビーム形成器ASICに結合されて、超音波送信及び受信ビーム形成のための制御情報を提供し、さらに、RAM(ランダムアクセスメモリ:random access memory)110にデータを記憶し、USB制御装置105及びスイッチング電源109を管理する。RAM110は、プローブの予測されるスキャニングモードの各々に必要な制御データのすべてを記憶する。例えば、RAM110は、RAMにデジタルエコー信号を書き込む書き込みアドレス制御装置に結合されるとともに、複数の読み出しアドレス制御装置に結合され、各々が、異なるデジタルマルチラインエコー信号に対する遅延されたデジタルエコー信号の読み出しを制御するように適用される。これらの回路のすべてが、熱くない手持ち式プローブを維持するために、この例においては3.0ワットである選択された最大供給電力量に従って動作しなければならない。図2に示されるマイクロビーム形成器回路の例示的な最大供給電力量が、次の表1に示される。

10

20

30

40

50

【表 1】

| 表 1: 表示された状態に対する図 2 の回路の消費電力 |                                                           |             |

|------------------------------|-----------------------------------------------------------|-------------|

| コンポーネント                      | 動作                                                        | 電力          |

| アナログ ASIC の送信機能              | 4096 個の素子を使用した送信                                          | 0.75W       |

| アナログ ASIC の前置増幅器及び遅延回路       | 8192 個の素子を使用した受信、128 個の部分的加算信号へのビーム形成                     | 0.5W        |

| USB 3.0 制御装置                 | 3Gb/s データ転送                                               | 0.7W        |

| 制御 FPGA                      | データ管理                                                     | 0.25W       |

| 電源                           | 90%の効率と仮定                                                 | 0.3W        |

| デジタル ASIC                    | 20Mhz における 128 個の ADC サンプリング、及び 8x マルチライン出力を使用したデジタルビーム形成 | 0.5W        |

| <b>合計</b>                    |                                                           | <b>3.0W</b> |

## 【0018】

この最大供給電力量は、マイクロビーム形成器回路全体、マイクロビーム形成器回路の制御 FPGA、電源、及び USB 制御装置が、3.0 ワットの電力割り当て量内で動作することにより、プローブにおいて非常に少量の熱しか生成しないことを示す。アナログ ASIC 102 は、デジタル ASIC における 128 個の ADC に対する 128 個の入力信号である、各 64 個の素子の 128 個のパッチから 128 個の部分的加算アナログ信号を生成する。従って、マイクロビーム形成器は、128 チャンネルデジタルビーム形成器とみなされる。チャンネル数により電力割り当て量を除算することは、マイクロビーム形成器がチャンネル当たり約 2.3 ミリワットしか消費しないことを示す。さらに、好ましい実施形態における各デジタルチャンネルは、高フレームレートデジタル像形成のために 8 個のマルチラインを生成し、これはマルチラインスキャンライン当たりわずか約 3 ミリワットの電力消費である。

## 【0019】

従って、本発明の超音波プローブは、複数のデジタルチャンネルを提供し、単一のマルチラインスキャンライン当たりの電力消費は、3 ミリワットという低いものとなり得る。各デジタルチャンネルが 4 つのマルチラインを生成する別の実施形態では、電力消費はマルチラインスキャンライン当たり約 6 ミリワット以下である。

## 【0020】

図 2 で示される実施形態において、マトリックスアレイトランステューサ 101 の音響素子は、フリップチップ型相互接続体におけるアナログ ASIC 102 の素子パッドに直接接続される。制御及びグループ出力信号は、アナログ ASIC とマイクロビーム形成器の他方のコンポーネントとの間において、可撓性の相互接続体（例えば可撓性回路）を通して他のプローブ回路を含むプリント回路基板まで接続される。積層されたシリコンダイ、セラミック回路、又はマルチチップモジュールなどの他の相互接続技術も使用される。各アナログ ASIC は、デジタル ASIC のうちの 2 つのデジタル ASIC のチャンネル入力 (CH) に素子の 64 個のパッチの部分的にビーム形成されたアナログ信号を伝える 64 個のチャンネルライン出力 (CHANNEL) を含む。従って、各デジタル ASIC は、部分的加算信号の 32 個のチャンネルを処理する。FPGA 104 は、アナログ ASIC に対して、その μBF ASIC 制御バスから、アナログ ASIC 102 の制御インターフェース入力に制御データを供給する。FPGA は、クロック (CLK) 信号に加えて、アドレス及びデータバスを通して、それぞれデジタル ASIC 103 にデジタルアドレスデータ及び制御データを供給する。デジタルビーム形成された出力信号は、完全に加算

10

20

30

40

50

されたデジタルエコー信号が最後の A S I C から F P G A の受信ビームデータ入力に印加されるまで、 A S I C から A S I C へと接続された B E A M \_ I N 及び B E A M \_ O U T バスを使用して、 1 つのデジタル A S I C から次へと伝搬及び加算される。 F P G A は、 U S B 制御装置 1 0 5 に完全にビーム形成された出力信号を印加し、 次に、 U S B 制御装置 1 0 5 が、 U S B ケーブル 1 0 7 を通してユーザ制御及びディスプレイシステム 1 0 8 に対し、 デジタルエコー信号をシリアルデータとして送信する。 H D M I ( 登録商標 ) 又は E t h e r n e t ( 登録商標 ) などの他の高速デジタルインターフェースも使用され得る。 適切な U S B 制御装置は、 S a n J o s e 、 C a l i f o r n i a の C y p r e s s S e m i c o n d u c t o r から入手可能な F X 3 . 0 s 制御装置である。マイクロビーム形成器のすべての I C の電力入力に対し必要な電力を印加するスイッチング電源 1 0 9 が示される。

### 【 0 0 2 1 】

図 3 は、 アナログ A S I C 1 0 2 の 1 つのチャンネル 3 0 0 のコンポーネントを示す。 図示されている実施形態において、 各アナログ A S I C は、 マトリックスアレイ 1 0 1 の 4 0 9 6 個の素子に接続された 4 0 9 6 値のアナログチャンネルのためのコンポーネントを含む。 送信データ ( T x D a t a ) は、 F P G A 1 0 4 から送信パルス生成器 3 0 2 により受信される。 F P G A は、 システム制御装置 2 6 から以前に受信されたコマンドに応答して、 所望の送信 / 受信シーケンスのために R A M メモリ 1 1 0 からこのデータにアクセスし、 システム制御装置 2 6 自体は、 ユーザインターフェース 2 0 においてユーザにより入力された像形成選択に応答して作動する。 T x D a t a は、 パルス幅、 時間マーカーに対する送信遅延、 及びパルスカウントなどの送信パルスのパラメータを制御する。 T x D a t a は、 送信パルス事象の所望のシーケンスを実現することにより応答する送信パルス生成器 3 0 2 にクロックに基づいて入力される。 送信パルスシーケンスは、 送信イネーブル信号 ( T x E n a b l e ) のタイミングで高電圧送信器 3 0 4 の入力に印加される。 送信 / 受信 ( T / R ) スイッチ 3 0 6 が、 図面に示されているように送信器をトランステューサ素子に結合するように設定されたとき、 高電圧送信器 3 0 4 が高電圧送信波形を使用してマトリックスアレイの素子 1 0 1 n を駆動する。 対象者内への波形の送信後、 受信された音響エコーに応答して変換された電気信号が前置増幅器 6 8 ( 前置増幅用増幅器とも呼ばれる ) の入力に結合されるように、 T / R スイッチ 3 0 6 が他方の位置に設定される。 受信イネーブル信号 ( R x E n a b l e ) は、 エコー信号受信の期間中、 前置増幅器を有効化する。 前置増幅器 6 8 の利得は、 エコー受信の期間中、 高められ、 対象者の次第に大きくなる深さから受信された信号に T G C 利得特性を提供する。 利得は、 複数のスイッチング可能な並列インピーダンスとして集積回路形態で実現された制御可能なフィードバックインピーダンス 3 1 0 によりデジタルで調節される。 並列インピーダンスのデジタル制御された、 より多くのスイッチが閉じるにつれて、 より多くのインピーダンスが並列に結合され、 前置増幅器のフィードバックインピーダンス 3 1 0 が減少する。 例えば、 米国仮特許出願第 6 2 / 3 7 0 , 8 4 1 号 ( F r e e m a n ら ) を参照されたい。 増幅されたアナログエコー信号はアナログ受信遅回路 3 2 0 に結合され、 アナログ受信遅回路 3 2 0 は、 アナログビーム形成のためのパッチの他の素子のチャンネルにより他のエコー信号に適用された遅延との関連で、 受信されたエコー信号を遅延させる。 適用された遅延は、 F P G A 1 0 4 から受信された遅延データ ( D e l a y D a t a ) により制御される。 遅延されたエコー信号は、 図に C h a n n e l O u t として示されるように、 パッチの他のアナログ信号とともに加算ノードに印加され、 加算ノードにおいて、 エコー信号がパッチ加算アナログ信号の形態で加算される。 2 D アレイに対する好ましい実施形態では、 各 6 4 個の素子の 1 2 8 個のパッチから部分的加算信号を生成する 1 2 8 個の加算ノードが存在する。 これらの 1 2 8 個の部分的加算信号は、 マルチラインデジタルビーム形成を実行するデジタル A S I C 1 0 3 のための入力信号である。

### 【 0 0 2 2 】

図 4 は、 アナログ受信遅回路 3 2 0 の集積回路の実施形態を示す。 回路 3 2 0 は、 容量性回路であり、 スイッチ 6 5 の閉鎖によりトランステューサ素子 1 0 1 n によって生成さ

10

20

30

40

50

れた信号をサンプリングし、回路のコンデンサ 6 2 にサンプルを記憶させ、次に、意図される遅延を規定する後の時点で、スイッチ 6 2 の閉鎖によりサンプル結果がコンデンサから読み出される。この手法により遅延された信号は、次に、出力バッファ 7 4 によりパッチ加算ノードに結合され、パッチ加算ノードにおいて、遅延された信号がパッチの他の 6 3 個の素子からのアナログ信号と加算される。信号がコンデンサ 6 2 1、6 2 2、…6 2 M に記憶される時点は、書き込み制御装置 6 4 及び読み出し制御装置 6 6 の動作により決定される。書き込み制御装置は、スイッチ 6 5 1、6 5 2、…6 5 M のうちの 1 つの閉鎖を決定するポインター回路であり、スイッチ 6 5 1、6 5 2、…6 5 M のうちの 1 つの一時的な閉鎖が、前置増幅器 6 8 の出力においてトランスデューサ 1 0 1 n の信号をサンプリングし、コンデンサにサンプルを記憶させる。スイッチがコンデンサに 1 つのサンプルを「書き込んだ」後、書き込み制御装置が、別のスイッチ 6 5 を閉じて、別のコンデンサ 6 2 に信号の別のサンプルを記憶させる。従って、書き込み制御装置は、エコー受信の期間中、トランスデューサ素子 1 0 1 n により受信された信号の複数のサンプルを迅速に連続して記憶させる。サンプルが獲得される周波数は、受信周波数帯に対するナイキストレートを上回り、通常、このレートを十分に上回る。読み出し制御装置 6 6 は、所望の遅延期間にわたって信号サンプルがコンデンサに記憶された後に、記憶された信号サンプルを読み出すことと同様の手法で動作するポインター回路である。読み出し制御装置は、スイッチ 6 7 のうちの 1 つを閉じ、記憶された信号サンプルを出力バッファ 7 4 に結合し、出力バッファ 7 4 から信号サンプルがさらなる処理のために利用可能となる。迅速な連続動作において、サンプリングされた信号のシーケンスがコンデンサ 6 2 から読み出され、この時点の遅延されたサンプルがパッチ加算ノードにおける加算のために転送される。

#### 【 0 0 2 3 】

アナログ A S I C 1 0 2 のコンポーネントが、デジタル制御されるアナログコンポーネントとみなされ、送信器 3 0 4 及び T / R スイッチ 3 0 6 は、トランスデューサ素子を駆動するために必要な高電圧で動作することが可能でなければならない。好ましい実施形態において、アナログ A S I C は、高電圧に適した集積回路プロセスにより製造され、0 . 1 8  $\mu$  M などの比較的大きな形状寸法をもつ。

#### 【 0 0 2 4 】

4 つのデジタル A S I C 1 0 3 の回路が図 5 に示される。図示される実施形態において、各デジタル A S I C は、トランスデューサ素子の 3 2 個のパッチから加算されたアナログ信号を処理する 3 2 個のデジタルチャンネル 6 0 1 を含む。各デジタルチャンネルは、アナログパッチ信号をデジタル化し、デジタルエコー信号の各シーケンスである 8 個の受信ビームが同時に形成されるように、8 個のデジタルマルチライン出力信号を形成する。8 個のマルチライン出力信号は、図面において各チャンネルに対して M L 0 から M L 7 として示されている。マルチラインの程度は、回路設計者により決定される通り、4 x であるか、図 5 に示されるように 8 x であるか、1 6 x であるか、又は任意のより多数のマルチラインである。動作時、アナログパッチ信号は、逐次近似型 A D C 又はデルタシグマ A D C などの好ましくは 1 0 ミリワット以下を消費するものである低電力 A D C 6 0 3 により、デジタルエコーサンプルのシーケンスに変換される。各デジタルエコーサンプルは、デジタル遅延回路 6 0 4 により 8 個の選択可能な遅延インクリメントだけ遅延され、8 個のマルチラインに対して遅延されたエコー信号を生成する。8 個のマルチラインサンプル M L 0 ~ M L 7 は、8 個のデジタル加算装置又は加算器（加算回路）6 0 5 に結合され、8 個のデジタル加算装置又は加算器（加算回路）6 0 5 において、サンプルが他のチャンネルにより生成されたデジタルエコーサンプルと加算される。前のデジタル A S I C からの 8 個のマルチラインのデジタルエコーサンプルは、デシリアライザ（非直列化器）6 0 2 により高レートシリアルデータストリームとして受信され、デシリアライザ 6 0 2 が、データストリームのサンプルを 8 個のマルチラインに対する 8 個の並列ラインにソートする。次に、A S I C の 3 2 チャンネルが、それらの部分的加算マルチライン信号を、これらの 8 個の並列ラインのデータにシリアルデータストリームの高レートより低いデータレートで加算する。例えば、シリアルデータストリームが 1 6 0 M H z において動作するのに

10

20

30

40

50

対し、デジタル A S I C におけるすべての他の回路は 2 0 M H z でクロックに基づいて動作する。A S I C の出力（図中の右下）において、8 個の並列ラインのデータがシリアルライザ 6 0 7 により高レートシリアルデータストリームに再構成され、シリアルライザ 6 0 7 は、他のチャンネルからのデジタル部分的加算信号との加算のために次のデジタル A S I C に結合される。デシリアルライザ 6 0 2 と同様に、シリアルライザ 6 0 7 は、より高いデータレートで動作する。チーンにおける最後のデジタル A S I C の出力において、完全にビーム形成されたシリアルデータ（受信ビームデータ）が F P G A 1 0 4 に結合され、F P G A 1 0 4 は受信されたビームデータを、像ディスプレイデバイス 1 0 8 への通信のために U S B 制御装置 1 0 5 に印加する。各デジタル A S I C は、F P G A から制御データを受信し、サンプリング時間及びデジタル遅延回路 6 0 4 のための遅延値などの、デジタル変換及びビーム形成プロセスのパラメータを設定する制御レジスタ 6 0 6 をさらに含む。

#### 【 0 0 2 5 】

図 5 に示されるデジタル A S I C において、使用される集積回路プロセスは、好ましくは、高電圧で動作しなければならないアナログ A S I C の形状寸法より小さな形状寸法に使用するプロセスである。デジタル A S I C のための適切な形状寸法は 6 5 n m 以下であり、このことが、電力をそのままに維持しながら、アナログ A S I C の回路密度より高い回路密度を可能にする。集積回路プロセスが可能にするクロックレートより低いクロックレートでデジタル A S I C の大部分を動作させることにより、電力消費の低減がさらに促進される。上述のように、シリアルライザ及びデシリアルライザは、1 6 0 M H z などの高周波で動作するので、選択された集積回路プロセスは、そのクロック周波数で動作することが可能でなければならない。しかし、デジタル A S I C コア、特に A D C 及びデジタル遅延及び加算器は、2 0 M H z でクロックに基づいて動作する。電力消費はクロック周波数に比例するので、回路が設計されるときに目的とする周波数よりはるかに低いこの低い動作周波数が、デジタル A S I C 1 0 3 により要求される電力をさらに小さくする。さらに、データのより低いクロックレートが、回路間における再同期レジスタの必要性を小さくし、電力消費をさらに低減する。さらに、より低いクロック周波数でデジタル A S I C を動作させることにより、そうでない場合においてより高いクロック周波数で所望の精度を維持するために必要とされる電源電圧よりも低い電源電圧を使用することができる。電力消費は電圧に依存するので、より低い電圧における動作も電力を削減する。好ましい実施形態において、A D C 並びにデジタル A S I C のシリアルライザ及びデシリアルライザは、より高い電圧で動作するようにされ、A S I C コアは、より低い電圧で動作するようにされる。

#### 【 0 0 2 6 】

図 5 a は、低電力逐次近似 A D C 6 0 3 のアーキテクチャを示す。変換されるアナログエコー信号、すなわち図の V I N は、サンプル・ホールド回路 6 2 4 によりサンプリング及びホールドされる。逐次近似レジスタ（S A R : s u c c e s s i v e a p p r o x i m a t i o n r e g i s t e r ）6 2 0 は、その最上位出力ビット D n が値 1 に設定されるように初期化される。デジタル・アナログコンバータ（D A C : d i g i t a l - t o - a n a l o g c o n v e r t e r ）6 2 2 は、デジタルワードの最上位ビット（D n ）が 1 に設定された状態の n + 1 ビットデジタルワードにアナログとして等価な、電圧 V R E F を基準とした比較電圧を生成する。比較器 6 2 6 が、アナログエコー信号を比較電圧と比較して、比較電圧がアナログエコー信号より大きい場合、比較器の出力は、S A R が最上位ビットをゼロに設定することをもたらし、そうでない場合、最上位ビットは値 1 に維持される。S A R の最上位の次のビット D n - 1 が 1 に設定され、D n - 1 ビットの正しい設定を決定するために別の比較が実行される。S A R の出力ビットのすべてが正しく設定されるまで本プロセスが履行され、その結果、出力ビットがアナログエコー信号のデジタル値となる。変換終了信号 E O C が変換のこの完了をデジタル遅延回路 6 0 4 に通知し、次に、デジタル遅延回路 6 0 4 が、S A R のデジタル値をその次のデジタル信号サンプルとして容認する。次に、サンプル・ホールド回路 6 2 4 が新しいエコー信号サンプルを獲得し、S A R 6 2 0 が初期化され、本プロセスが続く。

#### 【 0 0 2 7 】

10

20

30

40

50

図 6において、図 5に示すデジタル遅延回路、遅延制御、及びデジタルA S I Cの1つのチャンネルの加算回路がさらに詳細に示される。低電力A D C 6 0 3がパッチから連続したデジタルエコー信号サンプルを生成するとき、サンプルが書き込みアドレスカウンタ (W A C : w r i t e a d d r e s s c o u n t e r ) 6 4 2のインデックス処理によりマルチポートR A M 6 4 0に記憶される。遅延されたエコー信号は、8個のマルチラインに対する8個の読み出しアドレスカウンタ (R A C : r e a d a d d r e s s c o u n t e r ) 6 4 4 0から6 4 4 7により、R A M 6 4 0の8個の出力ポートQ 0 ~ Q 7から読み出され、8個の読み出しアドレスカウンタ (R A C ) 6 4 4 0から6 4 4 7のうちの1つの回路が図に示される。8個を上回るマルチラインが生成される場合、追加的な読み出しアドレスカウンタが追加され得る。各R A C 6 4 4は、その読み出しアドレスを、R A Mの8個のアドレスポートA d - r 0からA d - r 7のうちの1つに送る。読み出されるサンプルのアドレスとそのタイミングとが、デジタルエコー信号の遅延を決定する。マルチラインのためにR A Mに送られたアドレスは、F P G A 1 0 4により提供される焦点データに応答して、焦点制御回路6 4 6 0により設定され、出力アドレスがR A C 6 4 4 0にクロックに基づいて入力され、動的な焦点処理のために定期的に調節される。R A M 6 4 0のQ出力において生成された遅延されたデジタルエコー信号は、サブサンプル遅延F I R 6 4 8 0により、より細かい遅延にさらに分解され得、サブサンプル遅延F I R 6 4 8 0は、焦点制御回路から要求される通りにデータをさらに受信する。図においてC H 0として示される、マルチラインのための最終的な遅延されたデジタルエコー信号は、加算器6 0 5 0により他のデジタルチャンネルからのそのマルチラインに対する他のサンプルに加算される。その点まで加算されたサンプルは、D型フリップフロップ6 5 0 0にクロックに基づいて入ることにより再同期され、次のチャンネルの加算器に送られる。従って、各チャンネルは、同時に8個のマルチライン (Q 0 ~ Q 7)に対する適切に遅延されたデジタルパッチ信号サンプルを生成する。

#### 【 0 0 2 8 】

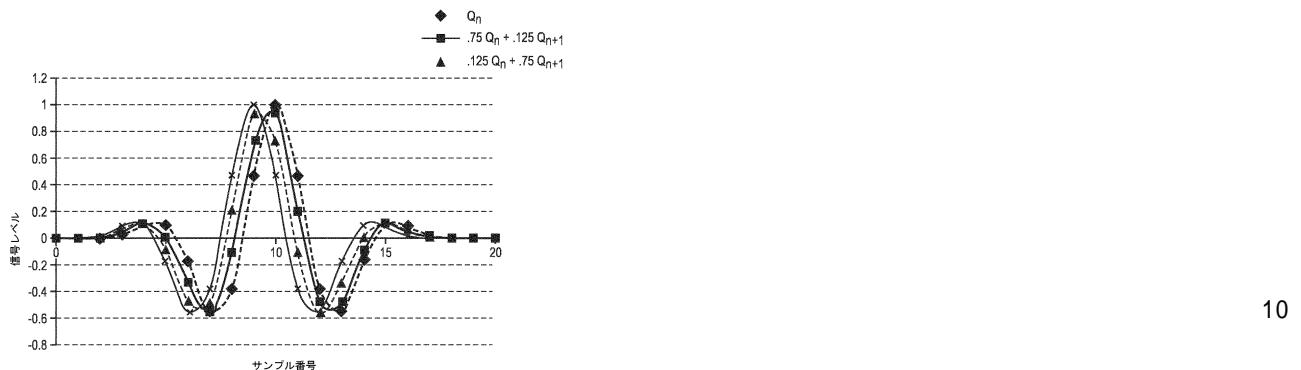

好ましいサブサンプル遅延有限インパルス応答 (F I R : f i n i t e i m p u l s e r e s p o n s e) フィルタが図 7に示される。この好ましいF I Rフィルタは、従来のF I Rフィルタと異なり、乗算器を使用しないことにより、電力をそのままに維持する。R A M 6 4 0からの連続したエコー信号サンプルは、クロックに基づいてレジスタ7 0 2に入力され、従って、現在のサンプルQ<sub>n</sub>をその入力にもち、前のサンプルQ<sub>n+1</sub>をその出力にもつ。2つのサンプルの重み付けされた分画が形成されて、より細かく分解された遅延されたサンプル値を生成する。乗算器を使用して重み付けを行う代わりに、使用される重み付け係数は、2の累乗であり、サンプル値の最上位ビットのうちの1つ又は複数の強制ゼロ充填により形成される。従って、加算器7 0 4は、2回重み付けされたQ<sub>n</sub>サンプルを受信するように結合され、一回目にその最上位ビットがゼロにされ (0, Q<sub>n</sub>)、さらに、その2個の最上位ビットがゼロにされる (0, 0, Q<sub>n</sub>)。同様に、加算器7 0 4は、さらに、2回重み付けされた形態でQ<sub>n+1</sub>サンプルを受信するように結合され、一回目に2個の最上位ビットがゼロにされ、さらに、3個の最上位ビットがゼロにされる。従って、加算器7 0 4は、. 7 5 Q<sub>n+1</sub> . 1 2 5 Q<sub>n+1</sub>の形態の重み付けされたエコー信号を生成する。同様の手法で、加算器7 0 6が、. 1 2 5 Q<sub>n+1</sub> . 7 5 Q<sub>n+1</sub>の形態の重み付けされたエコー信号を生成するように結合される。Q<sub>n</sub>サンプル及びこれらの2回重み付けされたサンプル値が、マルチプレクサ7 0 8の3個の入力に送られ、送られた値のうちの1つが、焦点制御回路6 4 6により提供されるS S D選択信号によりマルチプレクサ出力値として選択される。選択された細かく遅延された値が、再同期のためにレジスタ7 1 0にクロックに基づいて入力され、そのマルチラインに対する加算器6 0 5に送られる。図 8は、図 7に示すサブサンプル遅延F I Rフィルタにより生成され得る典型的な超音波エコー信号の3個の位相シフトを示す。見てわかるように、基本サンプリングクロック周波数の0、1/3、及び2/3の遅延値が、この回路を使用して達成され得る。

#### 【 0 0 2 9 】

10

20

30

40

50

電力消費の低減のための図 5 に示すデジタル A S I C の重要な特徴は、 A D C 6 0 3 及び後述のデジタルビーム形成（デジタル遅延 6 0 4 及び加算器 6 0 5 ）が同じ集積回路パッケージ内に位置することである。これは、介入する I C ピン、 P C B トレース、及び接続パッドを通して 1 つのパッケージから別のパッケージに信号を駆動するために、より多くの電力を必要とする、 1 つのパッケージ内の A D C から別のパッケージ内のデジタルビーム形成器にデータを伝達する必要性を無くす。パッケージ内相互接続のこの用法により電力が削減される。デジタル A S I C パッケージは、積層されたダイ又はマルチチップモジュールを使用し得るが、 A D C はデジタルビーム形成器回路と同じシリコンダイにあることが好ましい。

#### 【 0 0 3 0 】

上述の、及び図 1 及び図 2 の例示的な超音波システムにより示される様々な実施形態は、ハードウェア、ソフトウェア、又はハードウェアとソフトウェアとの組み合わせにより実施されてよいことが留意されなければならない。超音波システムの様々な実施形態及び／又はコンポーネント、例えば、モジュール、又はモジュール内のコンポーネント及び制御装置もまた、 1 つ又は複数のコンピュータ又はマイクロプロセッサの一部として実施されてよい。コンピュータ又はプロセッサは、コンピューティングデバイス、入力デバイス、ディスプレイユニット、及びインターフェース、例えば、インターネットにアクセスするためのインターフェースを含んでよい。コンピュータ又はプロセッサは、マイクロプロセッサを含んでよい。マイクロプロセッサは、通信バスに接続されて、例えば、 P A C S システムにアクセスしてよい。コンピュータ又はプロセッサは、メモリをさらに含んでよい。上述のメモリデバイスは、ランダムアクセスメモリ（ R A M ）、及び読み出し専用メモリ（ R O M : R e a d O n l y M e m o r y ）を含んでよい。コンピュータ又はプロセッサは、ハードディスクドライブ又はリムーバブル記憶ドライブ、例えばフロッピーディスクドライブ、光ディスクドライブ、ソリッドステートサムドライブなどの記憶デバイスをさらに含んでよい。記憶デバイスは、コンピュータ又はプロセッサにコンピュータプログラム又は他の命令をロードするための他の同様の手段であってもよい。

#### 【 0 0 3 1 】

本明細書において使用される場合、「コンピュータ（ c o m p u t e r ）」又は「モジュール（ m o d u l e ）」又は「プロセッサ（ p r o c e s s o r ）」という用語は、マイクロ制御装置、縮小命令セットコンピュータ（ R I S C : r e d u c e d i n s t r u c t i o n s e t c o m p u t e r ）、 A S I C 、論理回路、及び、本明細書において説明される機能を実行することが可能な任意の他の回路又はプロセッサを使用したシステムを含む、任意のプロセッサベースの、又はマイクロプロセッサベースのシステムを含んでよい。上述の例は例示に過ぎず、従って、いかなる形でもこれらの用語の定義及び／又は意味を限定することは意図されない。

#### 【 0 0 3 2 】

コンピュータ又はプロセッサは、入力データを処理するために、 1 つ又は複数の記憶素子に記憶された命令のセットを実行する。記憶素子は、所望により、又は必要に応じてデータ又は他の情報も記憶する。記憶素子は、情報源又は処理マシン内の物理的なメモリ素子の形態であってよい。

#### 【 0 0 3 3 】

マイクロビーム形成器を含む超音波システムの命令のセットは、コンピュータ又はプロセッサに対し、処理マシンとして本発明の様々な実施形態の方法及びプロセスなどの具体的な処理を実行するよう命令する様々なコマンドを含む。命令のセットは、ソフトウェアプログラムの形態であってよい。ソフトウェアは、システムソフトウェア又はアプリケーションソフトウェアなどの、有形かつ非一時的なコンピュータ可読媒体として具現化されている様々な形態であってよい。さらに、ソフトウェアは、独立したプログラム又はモジュールの集合体、より大きなプログラム内のプログラムモジュール、又は、プログラムモジュールの一部分の形態であってよい。ソフトウェアは、オブジェクト指向プログラムの形態のモジュール式プログラムをさらに含んでよい。処理マシンによる入力データの処理は

10

20

30

40

50

、操作者のコマンドに応答して、若しくは以前の処理の結果に応答して、又は別の処理マシンによりなされた要求に応答して行われる。図2に示す超音波システムでは、例えば、ソフトウェア命令は、メインフレーム超音波システムから、マイクロビーム形成器のFPG A 1 0 4により受信される。次に、FPG Aが、アナログA S I C 1 0 2及びデジタルA S I C 1 0 3にソフトウェア命令を送り、ソフトウェア命令によりマイクロビーム形成器の構造上のコンポーネントの動作を制御する。

【0034】

さらに、下記の請求項の限定はミーンズプラスファンクション形式で記載されておらず、そのような請求項の限定が、明示的に「そのための手段」という語句を使用し、続いてさらなる構成を欠いた機能の記述がなされない限り、又はそれがなされるまでは、米国特許法第112条第6項に基づいて解釈されることは意図されない。

10

20

30

40

50

【四面】

【 四 1 】

一

【 図 2 】

图 2

【図3】

义 3

【 図 4 】

图 4

【図 5】

図 5

【図 5 a】

FIG. 5a

【図 6】

図 6

【図 7】

図 7

10

20

30

40

50

【図 8】

図 8

10

20

30

40

50

---

フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

(72)発明者 オウゾウノフ ソティル フィリポフ

オランダ国 5 6 5 6 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 ポーランド マッキー ドゥーン

オランダ国 5 6 5 6 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 レドックス ニック

オランダ国 5 6 5 6 アーエー アインドーフェン ハイ テック キャンパス 5

審査官 富永 昌彦

(56)参考文献 米国特許出願公開第2007/0016023(US, A1)

特開2012-235912(JP, A)

特表2004-516123(JP, A)

(58)調査した分野 (Int.Cl., DB名)

A 61 B 8 / 00 - 8 / 15