(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6058346号

(P6058346)

(45) 発行日 平成29年1月11日(2017.1.11)

(24) 登録日 平成28年12月16日(2016.12.16)

(51) Int.Cl.

F 1

|             |               |                  |      |        |         |

|-------------|---------------|------------------|------|--------|---------|

| <b>G09G</b> | <b>3/3233</b> | <b>(2016.01)</b> | G09G | 3/3233 |         |

| <b>G09G</b> | <b>3/20</b>   | <b>(2006.01)</b> | G09G | 3/20   | 6 2 4 B |

| <b>H01L</b> | <b>51/50</b>  | <b>(2006.01)</b> | G09G | 3/20   | 6 1 1 H |

| <b>H05B</b> | <b>33/14</b>  | <b>(2006.01)</b> | G09G | 3/20   | 6 4 1 C |

|             |               |                  | G09G | 3/20   | 6 4 2 A |

請求項の数 8 (全 109 頁) 最終頁に続く

(21) 出願番号

特願2012-227571 (P2012-227571)

(22) 出願日

平成24年10月15日 (2012.10.15)

(65) 公開番号

特開2013-137509 (P2013-137509A)

(43) 公開日

平成25年7月11日 (2013.7.11)

審査請求日

平成27年9月18日 (2015.9.18)

(31) 優先権主張番号

特願2011-228418 (P2011-228418)

(32) 優先日

平成23年10月18日 (2011.10.18)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2011-261317 (P2011-261317)

(32) 優先日

平成23年11月30日 (2011.11.30)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

(56) 参考文献 特開2009-134110 (JP, A

)特開2005-164891 (JP, A

)特開2004-246204 (JP, A

)

最終頁に続く

(54) 【発明の名称】半導体装置及び表示装置

(57) 【特許請求の範囲】

【請求項 1】

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの一方は、前記第4の配線に電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつ

10

20

て、

第1の期間と、前記第1の期間の後の第2の期間と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第4の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位乃至前記第4の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とする半導体装置。

10

【請求項2】

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの一方は、前記第4の配線に電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつて、

20

第1の期間と、前記第1の期間の後の第2の期間と、前記第2の期間の後の第3の期間と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第4の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位乃至前記第4の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とし、

30

前記第3の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオフ状態、かつ、前記第3のスイッチをオフ状態とすることで、前記第1の容量素子の第1電極に前記第1の配線の電位を供給する半導体装置。

40

【請求項3】

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、負荷と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

50

、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記負荷と電気的に接続され、且つ前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつて、

第1の期間と、前記第1の期間の後の第2の期間と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第3の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位及び前記第3の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とする半導体装置。

【請求項4】

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、負荷と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記負荷と電気的に接続され、且つ前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつて、

第1の期間と、前記第1の期間の後の第2の期間と、前記第2の期間の後の第3の期間と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第3の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位及び前記第3の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とし、

前記第3の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオフ状態、かつ、前記第3のスイッチをオフ状態とすることで、前記第1の容量素子の第1電

10

20

30

40

50

極に前記第1の配線の電位を供給する半導体装置。

**【請求項5】**

請求項1乃至請求項4のいずれか一において、

前記トランジスタが有する半導体膜は、酸化物半導体を有する半導体装置。

**【請求項6】**

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、発光素子と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記発光素子と電気的に接続され、且つ前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつて、

第1の期間と、前記第1の期間の後の第2の期間と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第3の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位及び前記第3の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とする表示装置。

**【請求項7】**

トランジスタと、第1の配線と、第2の配線と、第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、発光素子と、を有し、

前記第1のスイッチは、前記第1の配線と前記第1の容量素子の第1電極との間の導通または非導通を選択する機能を有し、

前記第1の容量素子の第1電極は、前記第2の容量素子の第1電極と電気的に接続され、

前記第1の容量素子の第2電極は、前記トランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2電極は、前記発光素子と電気的に接続され、且つ前記トランジスタのソースまたはドレインの一方と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第2のスイッチは、前記第2の配線と前記トランジスタのゲートとの間の導通または非導通を選択する機能を有し、

前記第3のスイッチは、前記第1の容量素子の第1電極と前記トランジスタのソースまたはドレインの一方との間の導通または非導通を選択する機能を有する半導体装置であつて、

第1の期間と、前記第1の期間の後の第2の期間と、前記第2の期間の後の第3の期間

10

20

30

40

50

と、を有し、

前記第1の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオン状態、かつ、前記第3のスイッチをオン状態とし、かつ、前記トランジスタをオン状態とするように前記第1の配線の電位乃至前記第3の配線の電位を制御し、

前記第2の期間において、前記第1のスイッチをオフ状態、前記第2のスイッチをオン状態、前記第3のスイッチをオン状態とし、かつ、前記第1の容量素子に蓄積されている電荷が前記トランジスタを介して放出されるように前記第2の配線の電位及び前記第3の配線の電位を制御することで、前記トランジスタのゲート電圧を前記トランジスタの閾値電圧に応じた大きさの電圧とし、

前記第3の期間において、前記第1のスイッチをオン状態、前記第2のスイッチをオフ状態、かつ、前記第3のスイッチをオフ状態とすることで、前記第1の容量素子の第1電極に前記第1の配線の電位を供給する表示装置。 10

【請求項8】

請求項6または7において、

前記トランジスタが有する半導体膜は、酸化物半導体を有する表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置、発光装置、または、表示装置に関する。または、それらの駆動方法、または、それらの製造方法に関する。半導体装置としては、例えば、トランジスタなどの能動素子等を有する半導体装置が挙げられる。発光装置としては、例えば、エレクトロルミネッセンス素子（以下、EL素子という）等の発光素子を有する発光装置が挙げられる。表示装置としては、例えば、EL素子等の発光素子、または表示素子を有する表示装置が挙げられる。特に、本発明は、トランジスタの特性のばらつきの影響が低減された半導体装置、発光装置、表示装置、または、それらの駆動方法に関する。 20

【背景技術】

【0002】

発光素子を用いた表示装置は視認性が高く、薄型化に最適であると共に、視野角にも制限が無いため、CRT（cathode ray tube）や液晶表示装置に替わる表示装置として注目されている。発光素子を用いたアクティブマトリクス型の表示装置は、具体的に提案されている構成がメーカーによって異なるが、通常、少なくとも発光素子と、画素へのビデオ信号の入力を制御するトランジスタ（スイッチング用トランジスタ）と、該発光素子に供給する電流値を制御するトランジスタ（駆動用トランジスタ）とが、各画素に設けられている。 30

【0003】

例えば、画素に設ける上記トランジスタをすべて同じ導電型とすることで、トランジスタの作製工程において、半導体膜に一導電性を付与する不純物元素の添加などの工程を、一部省略することができる。下記の特許文献1には、nチャネル型トランジスタのみで画素が構成される表示装置について記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-195810号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、発光装置や表示装置等の半導体装置では、トランジスタのドレイン電流が発光素子に供給されるため、画素においてトランジスタの特性などにばらつきが生じると、発光素子等の表示素子の輝度にもそのばらつきが反映されてしまう。従って、例えば、閾値電圧のばらつきを見越してトランジスタのドレイン電流の電流値を補正することができ 50

る画素構成の提案は、半導体装置の質向上を図る上で、重要な課題である。

#### 【0006】

上述の問題に鑑み、本発明の一態様は、トランジスタの特性のばらつきの影響が抑えられる、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、トランジスタの特性の劣化の影響が抑えられる、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、トランジスタの閾値電圧のばらつきによる輝度のばらつきが抑えられる、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、トランジスタの移動度のばらつきによる輝度のばらつきが抑えられる、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、トランジスタがノーマリオフ型であっても正常に動作する、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、トランジスタがノーマリオフ型であっても、トランジスタのしきい値電圧を取得できる、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、質の良い表示を行う半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、ムラの少ない表示を行う半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、少ないトランジスタ数で、所望の回路を実現できるような、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、少ない配線数で、所望の回路を実現できるような、半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、発光素子の劣化の影響が抑えられる半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。または、本発明の一態様は、少ない工程数で製造される半導体装置、発光装置、または、表示装置を提供することを課題の一つとする。

#### 【0007】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、特許請求の範囲などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0008】

本発明の半導体装置の一態様は、トランジスタと、第1の配線と、第2の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、を少なくとも有する。第1のスイッチは、第1の配線と第1の容量素子の一対の電極のうちの一方との間の導通または非導通を選択する機能を有する。第1の容量素子の一対の電極のうちの一方は、第2の容量素子の一対の電極のうちの一方と電気的に接続される。第1の容量素子の一対の電極のうちの他方は、トランジスタのゲートと電気的に接続される。第2の容量素子の一対の電極のうちの他方は、トランジスタのソース及びドレインの一方と電気的に接続される。第2のスイッチは、第2の配線と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第3のスイッチは、第1の容量素子の一対の電極のうちの一方と、トランジスタのソース及びドレインの一方との間の導通または非導通を選択する機能を有する。

#### 【0009】

上記構成の半導体装置では、閾値電圧のばらつきを見越してトランジスタ（以下、駆動用トランジスタという場合がある）のソースとゲート間に印加される電圧を補正することができる。こうして、トランジスタのドレイン電流を補正することができる。

#### 【0010】

本発明の半導体装置の一態様は、トランジスタと、負荷と、第1の配線と、第2の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、を少なくとも有する。第1のスイッチは、第1の配線と第1の容量素子の一

対の電極のうちの一方との間の導通または非導通を選択する機能を有する。第1の容量素子の一対の電極のうちの一方は、第2の容量素子の一対の電極のうちの一方と電気的に接続される。第1の容量素子の一対の電極のうちの他方は、トランジスタのゲートと電気的に接続される。第2の容量素子の一対の電極のうちの他方は、負荷と、トランジスタのソース及びドレインの一方とに、電気的に接続される。第2のスイッチは、第2の配線と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第3のスイッチは、第1の容量素子の一対の電極のうちの一方と、トランジスタのソース及びドレインの一方との間の導通または非導通を選択する機能を有する。

【0011】

上記構成の半導体装置では、閾値電圧のばらつきを見越してトランジスタ（以下、駆動用トランジスタという場合がある）のソースとゲート間に印加される電圧を補正することができる。こうして、トランジスタのドレン電流を補正することができる。そして、当該ドレン電流を負荷に供給することができる。

10

【0012】

負荷は、任意の素子や回路を用いることができる。例えば、負荷は、EL素子等の発光素子とすることができます。EL素子等の発光素子は、発光素子のアノードとカソード間を流れる電流の電流値に比例した輝度で発光する。

【0013】

負荷として発光素子を用いる場合、一例としては、以下の（タイプA）または（タイプB）の構成とすることができます。

20

【0014】

（タイプA）

上記本発明の一態様に係る半導体装置では、トランジスタ（駆動用トランジスタ）のソース及びドレンの一方は、発光素子のアノードと電気的に接続された構成とすることができます。この場合、当該トランジスタはnチャネル型トランジスタとする。そして、本発明の一態様に係る半導体装置は、第1の配線の電位を制御する機能を有する手段（例えば、駆動回路）を有し、当該手段（駆動回路）は、第1の配線の電位が発光素子のカソードの電位以下となるような期間を有するように、第1の配線の電位を制御する。

【0015】

（タイプB）

30

上記本発明の一態様に係る半導体装置では、トランジスタ（駆動用トランジスタ）のソース及びドレンの一方は、発光素子のカソードと電気的に接続された構成とすることができます。この場合、当該トランジスタはpチャネル型トランジスタとする。そして、本発明の一態様に係る半導体装置は、第1の配線の電位を制御する機能を有する手段（例えば、駆動回路）を有し、当該手段（駆動回路）は、第1の配線の電位が発光素子のアノードの電位以上となるような期間を有するように、第1の配線の電位を制御する。

【0016】

第1のスイッチ乃至第3のスイッチそれぞれは、トランジスタを用いて構成することができる。当該トランジスタは、駆動用トランジスタと同じ導電型のトランジスタとすることができます。

40

【0017】

上記本発明の一態様に係る半導体装置は、チャネル形成領域に酸化物半導体を含むトランジスタを用いて構成することができる。または、チャネル形成領域に単結晶シリコンを含むトランジスタを用いて構成することができる。または、チャネル形成領域に多結晶シリコンを含むトランジスタを用いて構成することができる。または、チャネル形成領域に非晶質シリコンを含むトランジスタを用いて構成することができる。

【0018】

つまり、トランジスタとして、様々な構造のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。トランジスタの一例としては、単結晶シリコンを有するトランジスタ、または、非晶質シリコン、多結晶シリコン、微結晶（マイクロ

50

クリスタル、ナノクリスタル、セミアモルファスとも言う)シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを用いることが出来る。

【0019】

なお、トランジスタの一例としては、化合物半導体(例えば、SiGe、GaAsなど)、又は酸化物半導体(例えば、ZnO、InGaZnO、インジウム亜鉛酸化物、ITO(インジウム錫酸化物)、SnO、TiO、AlZnSnO(AZTO)、InSnZnOなど)などを有するトランジスタ又は、これらの化合物半導体又は酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くできるので、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板又はフィルム基板などに直接トランジスタを形成することが出来る。なお、これらの化合物半導体又は酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体又は酸化物半導体を配線、抵抗素子、画素電極、又は透光性を有する電極などとして用いることができる。それらをトランジスタと同時に成膜又は形成することが可能なため、コストを低減できる。

10

【0020】

なお、トランジスタの一例としては、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。

【0021】

なお、トランジスタの一例としては、ゲート電極が2個以上のマルチゲート構造のトランジスタを用いることができる。マルチゲート構造にすると、チャネル形成領域が直列に接続されるため、複数のトランジスタが直列に接続された構造となる。よって、マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上(信頼性の向上)を図ることができる。または、マルチゲート構造により、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレインとソースとの間の電流があまり変化せず、傾きがフラットである電圧・電流特性を得ることができる。傾きがフラットである電圧・電流特性を利用すると、理想的な電流源回路、又は非常に高い抵抗値をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路又はカレントミラー回路などを実現することが出来る。

20

【0022】

30

なお、トランジスタの一例としては、チャネルの上下にゲート電極が配置されている構造のトランジスタを適用することができる。チャネルの上下にゲート電極が配置される構造にすることにより、複数のトランジスタが並列に接続されたような回路構成となる。よって、チャネル領域が増えるため、電流値の増加を図ることができる。または、チャネルの上下にゲート電極が配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図ることができる。

【0023】

なお、トランジスタの一例としては、チャネル形成領域の上にゲート電極が配置されている構造、チャネル形成領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構造、チャネル形成領域を複数の領域に分けた構造、チャネル形成領域を並列に接続した構造、又はチャネル形成領域が直列に接続する構造などのトランジスタを用いることができる。

40

【0024】

なお、トランジスタの一例としては、LDD領域を設けた構造を適用できる。LDD領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上(信頼性の向上)を図ることができる。または、LDD領域を設けることにより、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレイン電流があまり変化せず、傾きがフラットな電圧・電流特性を得ることができる。

【0025】

なお、明細書の中の図面や文章において規定されていない内容について、その内容を除く

50

ことを規定した発明を構成することが出来る。または、ある値について、上限値と下限値などで示される数値範囲が記載されている場合、その範囲を任意に狭めることで、または、その範囲の中の一点を除くことで、その範囲を一部除いて発明を規定することができる。これらにより、例えば、従来技術が本発明の技術的範囲内に入らないことを規定することができる。

#### 【0026】

具体例としては、ある回路において、第1乃至第5のトランジスタを用いている回路図が記載されているとする。その場合、その回路が、第6のトランジスタを有していないことを発明として規定することが可能である。または、その回路が、容量素子を有していないことを規定することが可能である。さらに、その回路が、ある特定の接続構造を有している第6のトランジスタを有していない、と規定して発明を構成することができる。または、その回路が、ある特定の接続構造を有している容量素子を有していない、と規定して発明を構成することができる。例えば、ゲートが第3のトランジスタのゲートと接続されている第6のトランジスタを有していない、と発明を規定することが可能である。または、例えば、第1の電極が第3のトランジスタのゲートと接続されている容量素子を有していない、と発明を規定することが可能である。

10

#### 【0027】

別の具体例としては、ある値について、例えば、「ある電圧が、3V以上10V以下であることが好適である」と記載されているとする。その場合、例えば、ある電圧が、-2V以上1V以下である場合を除く、と発明を規定することが可能である。または、例えば、ある電圧が、13V以上である場合を除く、と発明を規定することが可能である。なお、例えば、その電圧が、5V以上8V以下であると発明を規定することも可能である。なお、例えば、その電圧が、概略9Vであると発明を規定することも可能である。なお、例えば、その電圧が、3V以上10V以下であるが、9Vである場合を除くと発明を規定することも可能である。

20

#### 【0028】

別の具体例としては、ある値について、例えば、「ある電圧が、10Vであることが好適である」と記載されているとする。その場合、例えば、ある電圧が、-2V以上1V以下である場合を除く、と発明を規定することが可能である。または、例えば、ある電圧が、13V以上である場合を除く、と発明を規定することが可能である。

30

#### 【0029】

別の具体例としては、ある物質の性質について、例えば、「ある膜は、絶縁膜である」と記載されているとする。その場合、例えば、その絶縁膜が、有機絶縁膜である場合を除く、と発明を規定することが可能である。または、例えば、その絶縁膜が、無機絶縁膜である場合を除く、と発明を規定することが可能である。

#### 【0030】

別の具体例としては、ある積層構造について、例えば、「AとBとの間に、ある膜が設けられている」と記載されているとする。その場合、例えば、その膜が、4層以上の積層膜である場合を除く、と発明を規定することが可能である。または、例えば、Aとその膜との間に、導電膜が設けられている場合を除く、と発明を規定することが可能である。

40

#### 【発明の効果】

#### 【0031】

本発明の一態様では、駆動用トランジスタの閾値電圧に応じてソースとゲート間に印加される電圧を定めることができる。こうして、トランジスタの特性のばらつきの影響が抑えられる、半導体装置、発光装置、または、表示装置を提供することができる。または、トランジスタの特性の劣化の影響が抑えられる、半導体装置、発光装置、または、表示装置を提供することができる。または、トランジスタの閾値電圧のばらつきによる輝度のばらつきが抑えられる、半導体装置、発光装置、または、表示装置を提供することができる。または、トランジスタの移動度のばらつきによる輝度のばらつきが抑えられる、半導体装置、発光装置、または、表示装置を提供することができる。または、本発明の一態様は、

50

トランジスタがノーマリオフ型であっても正常に動作する、半導体装置、発光装置、または、表示装置を提供することができる。または、本発明の一態様は、トランジスタがノーマリオフ型であっても、トランジスタのしきい値電圧を取得できる、半導体装置、発光装置、または、表示装置を提供することができる。または、質の良い表示を行う半導体装置、発光装置、または、表示装置を提供することができる。または、ムラの少ない表示を行う半導体装置、発光装置、または、表示装置を提供することができる。または、少ないトランジスタ数で、所望の回路を実現できるような、半導体装置、発光装置、または、表示装置を提供することができる。または、少ない配線数で、所望の回路を実現できるような、半導体装置、発光装置、または、表示装置を提供することができる。または、発光素子の劣化の影響が抑えられる半導体装置、発光装置、または、表示装置を提供することができる。または、少ない工程数で製造される半導体装置、発光装置、または、表示装置を提供することができる。10

【図面の簡単な説明】

【0032】

【図1】半導体装置の構成を示す図。

【図2】半導体装置の構成を示す図。

【図3】半導体装置の構成を示す図。

【図4】半導体装置の構成を示す図。

【図5】タイミングチャートと半導体装置の動作を示す図。

【図6】半導体装置の動作を示す図。

【図7】半導体装置の動作を示す図。

【図8】半導体装置の構成を示す図。

【図9】半導体装置の構成を示す図。

【図10】半導体装置の構成を示す図。

【図11】半導体装置の構成を示す図。

【図12】半導体装置の構成を示す図。

【図13】半導体装置の構成を示す図。

【図14】半導体装置の構成を示す図。

【図15】半導体装置の構成を示す図。

【図16】半導体装置の構成を示す図。

【図17】タイミングチャートと半導体装置の動作を示す図。

【図18】半導体装置の動作を示す図。

【図19】半導体装置の動作を示す図。

【図20】タイミングチャートと半導体装置の動作を示す図。

【図21】半導体装置の構成を示す図。

【図22】半導体装置の構成を示す図。

【図23】半導体装置の構成を示す図。

【図24】半導体装置の構成を示す図。

【図25】半導体装置の構成を示す図。

【図26】半導体装置の構成を示す図。

【図27】半導体装置の構成を示す図。

【図28】半導体装置の構成を示す図。

【図29】半導体装置の構成を示す図。

【図30】半導体装置の構成を示す図。

【図31】半導体装置の構成を示す図。

【図32】半導体装置の構成を示す図。

【図33】半導体装置の構成を示す図。

【図34】半導体装置の構成を示す図。

【図35】半導体装置の動作を示す図。

【図36】半導体装置の動作を示す図。

10

20

30

40

50

- 【図37】半導体装置の構成を示す図。

【図38】半導体装置の構成を示す図。

【図39】半導体装置の構成を示す図。

【図40】半導体装置の構成を示す図。

【図41】半導体装置の構成を示す図。

【図42】半導体装置の構成を示す図。

【図43】半導体装置の構成を示す図。

【図44】半導体装置の構成を示す図。

【図45】半導体装置の構成を示す図。

【図46】半導体装置の構成を示す図。

【図47】半導体装置の構成を示す図。

【図48】半導体装置の構成を示す図。

【図49】半導体装置の構成を示す図。

【図50】半導体装置の構成を示す図。

【図51】半導体装置の構成を示す図。

【図52】半導体装置の構成を示す図。

【図53】半導体装置の構成を示す図。

【図54】半導体装置の構成を示す図。

【図55】半導体装置の構成を示す図。

【図56】半導体装置の構成を示す図。

【図57】半導体装置の構成を示す図。

【図58】半導体装置の構成を示す図。

【図59】半導体装置の構成を示す図。

【図60】半導体装置の構成を示す図。

【図61】半導体装置の構成を示す図。

【図62】半導体装置の構成を示す図。

【図63】半導体装置の構成を示す図。

【図64】半導体装置の構成を示す図。

【図65】半導体装置の構成を示す図。

【図66】半導体装置の構成を示す図。

【図67】半導体装置の構成を示す図。

【図68】半導体装置の構成を示す図。

【図69】半導体装置の構成を示す図。

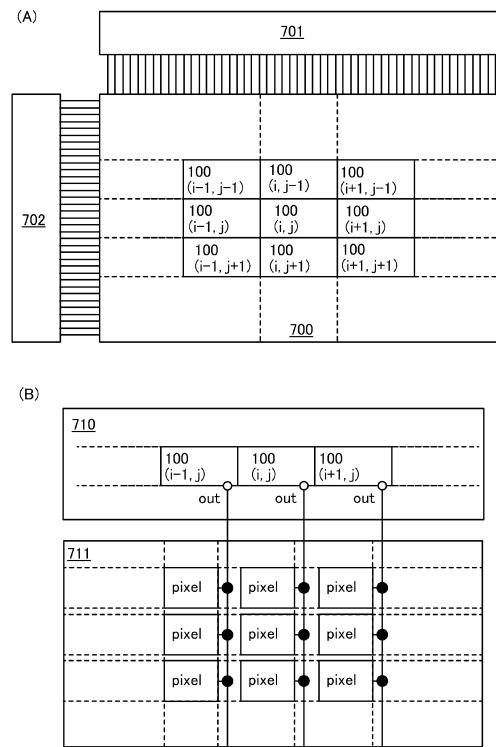

【図70】半導体装置の構成を示す図。

【図71】半導体装置の構成を示す図。

【図72】半導体装置の動作を示す図。

【図73】半導体装置の構成を示す図。

【図74】半導体装置の構成を示す図。

【図75】半導体装置の構成を示す図。

【図76】半導体装置の構成を示す図。

【図77】半導体装置の構成を示す図。

【図78】半導体装置の構成を示す図。

【図79】半導体装置の構成を示す図。

【図80】半導体装置の構成を示す図。

【図81】半導体装置の構成を示す図。

【図82】半導体装置の構成を示す図。

【図83】半導体装置の構成を示す図。

【図84】半導体装置の構成を示す図。

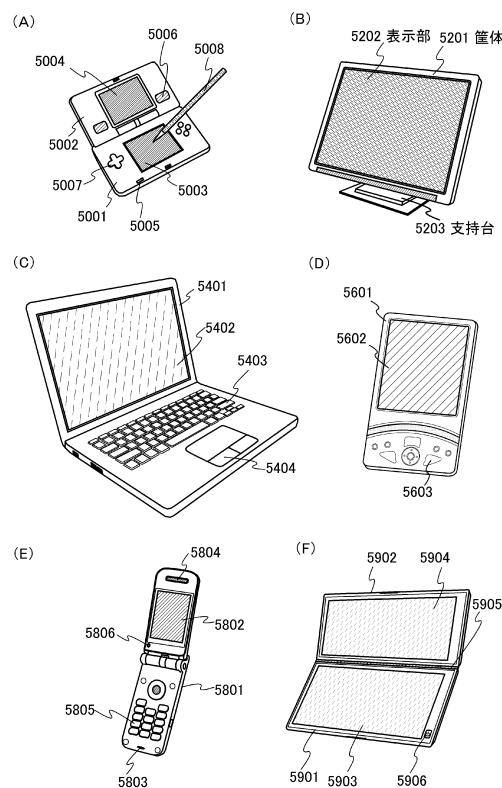

【図85】電子機器の図。

【図86】半導体装置の構成を示す図。

10

20

30

40

50

【図87】半導体装置の構成を示す図。

【図88】半導体装置の構成を示す図とタイミングチャート。

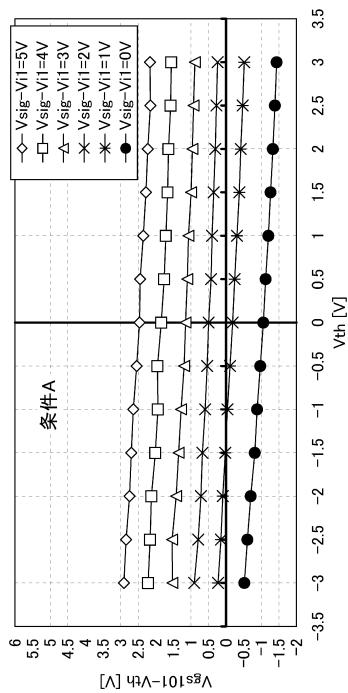

【図89】シミュレーションの結果を示す図。

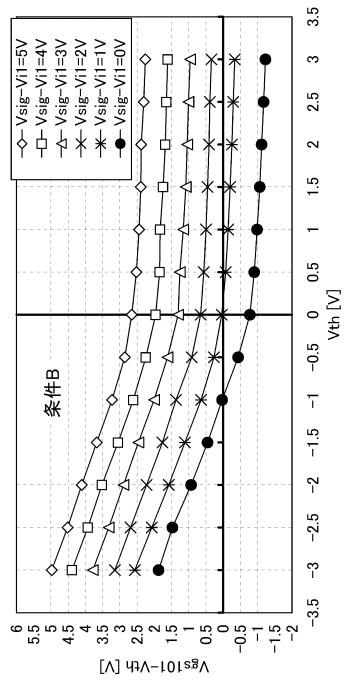

【図90】シミュレーションの結果を示す図。

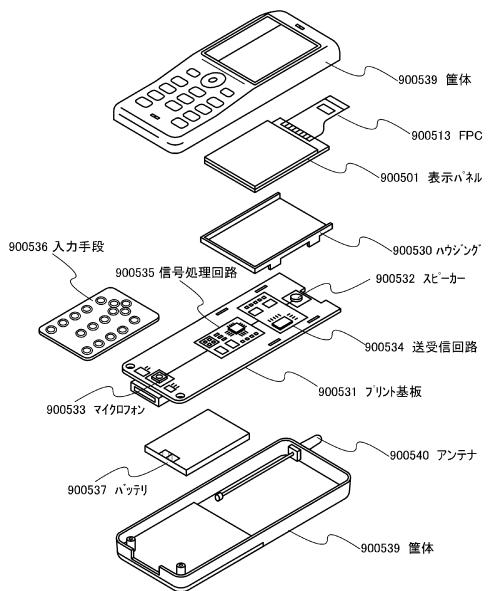

【図91】電子機器の図。

【発明を実施するための形態】

【0033】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一部分または同様な機能を有する部分については同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0034】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、及び／または、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、または置き換えなどを行うことができる。

【0035】

なお、ある一つの実施の形態において述べる図（一部でもよい）の構成は、その図の別の部分の構成、その実施の形態において述べる別の図（一部でもよい）の構成、及び／または、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）の構成と組み合わせることができる。

20

【0036】

なお、図において、大きさ、厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、本発明の実施形態の一態様は、必ずしもそのスケールに限定されない。または、図は、理想的な例を模式的に示したものである。よって、本発明の実施形態の一態様は、図に示す形状などに限定されない。例えば、製造技術による形状のばらつき、誤差による形状のばらつきなどを含むことが可能である。

【0037】

30

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、表示素子、発光素子、負荷など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

【0038】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。

40

【0039】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（D/A変換回路、A/D変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きくできる

50

回路、オペアンプ、差動増幅回路、ソースフォロワ回路、バッファ回路など)、信号生成回路、記憶回路、制御回路など)が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。

【0040】

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

10

【0041】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0042】

なお、能動素子(トランジスタ、ダイオードなど)、受動素子(容量素子、抵抗素子など)などが有するすべての端子について、その接続先を特定しなくても、当業者であれば、発明の一態様を構成することは可能な場合がある。つまり、接続先を特定しなくても、発明の一態様が明確であり、本明細書等に記載されていると判断することが可能な場合がある。特に、端子の接続先が複数のケース考えられる場合には、その端子の接続先を特定の箇所に限定する必要はない。したがって、能動素子(トランジスタ、ダイオードなど)、受動素子(容量素子、抵抗素子など)などが有する一部の端子についてのみ、その接続先を特定することによって、発明の一態様を構成することが可能な場合がある。

20

【0043】

なお、ある回路について、少なくとも接続先を特定すれば、当業者であれば、発明を特定することが可能な場合がある。または、ある回路について、少なくとも機能を特定すれば、当業者であれば、発明を特定することが可能な場合がある。つまり、機能を特定すれば、発明の一態様が明確であり、本明細書等に記載されていると判断することが可能な場合がある。したがって、ある回路について、機能を特定しなくても、接続先を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。または、ある回路について、接続先を特定しなくても、機能を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。

30

【0044】

なお、本発明の実施形態の一態様は、さまざまな人が実施することができる。しかしながら、その実施は、複数の人にまたがって実施される場合がある。例えば、送受信システムの場合において、A社が送信機を製造および販売し、B社が受信機を製造および販売する場合がある。別の例としては、TFTおよび発光素子を有する発光装置の場合において、TFTが形成された半導体装置は、A社が製造および販売する。そして、B社がその半導体装置を購入して、その半導体装置に発光素子を成膜して、発光装置として完成させる、という場合がある。

40

【0045】

このような場合、A社またはB社のいずれに対しても、特許侵害を主張できるような発明の一態様を、構成することができる。従って、A社またはB社に対して、特許侵害を主張できるような発明の一態様は、明確であり、本明細書等に記載されていると判断する事が出来る。例えば、送受信システムの場合において、送信機のみで発明の一態様を構成することができ、受信機のみで発明の一態様を構成することができ、それらの発明の一態様は、明確であり、本明細書等に記載されていると判断する事が出来る。別の例としては、

50

TFT および発光素子を有する発光装置の場合において、TFT が形成された半導体装置のみで発明の一態様を構成することができ、TFT および発光素子を有する発光装置のみで発明の一態様を構成することができ、それらの発明の一態様は、明確であり、本明細書等に記載されていると判断することが出来る。

【0046】

(実施の形態1)

本発明の一態様は、発光素子を有する画素だけでなく、様々な回路として用いることができる。例えば、アナログ回路として用いたり、電流源としての機能を有する回路として用いることが出来る。そこでまず、本実施の形態では、本発明で開示する回路の基本原理の一例について述べる。

10

【0047】

本発明の一態様に係る半導体装置は、例えば、トランジスタと、当該トランジスタにおいて、ゲートの電位を固定した状態で、ゲートとソース間に保持されている電荷を放電する機能を有する構成とを、少なくとも有する。本発明の一態様に係る半導体装置は、上記構成により、トランジスタの閾値電圧や移動度などに起因するドレイン電流のばらつきを補正することができる。

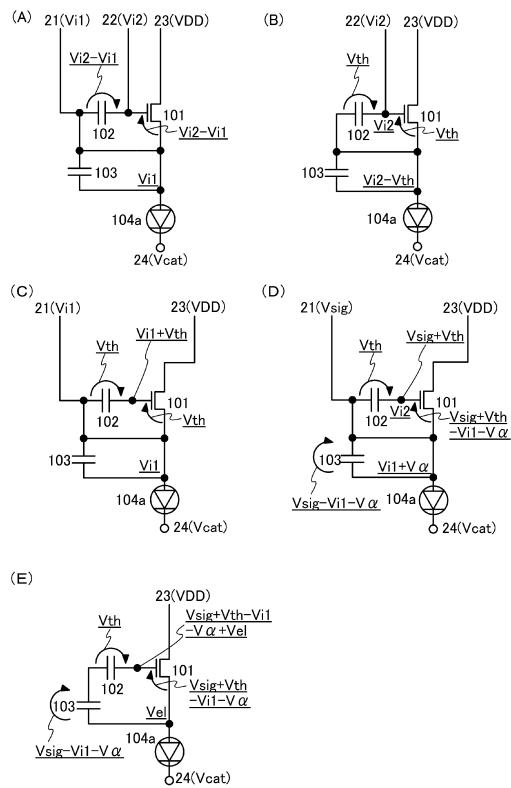

【0048】

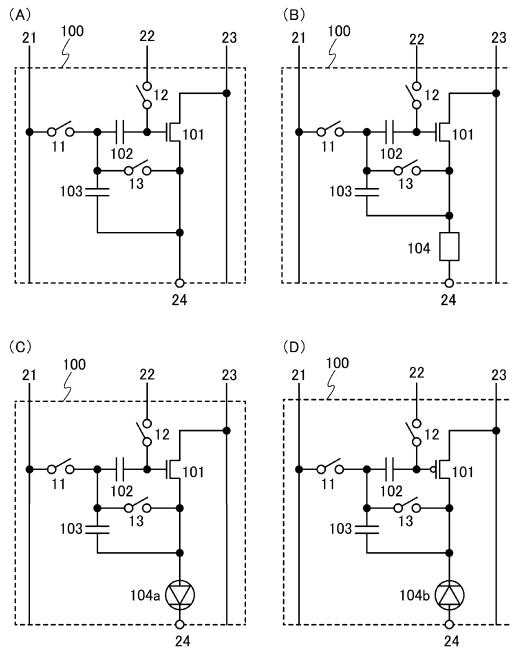

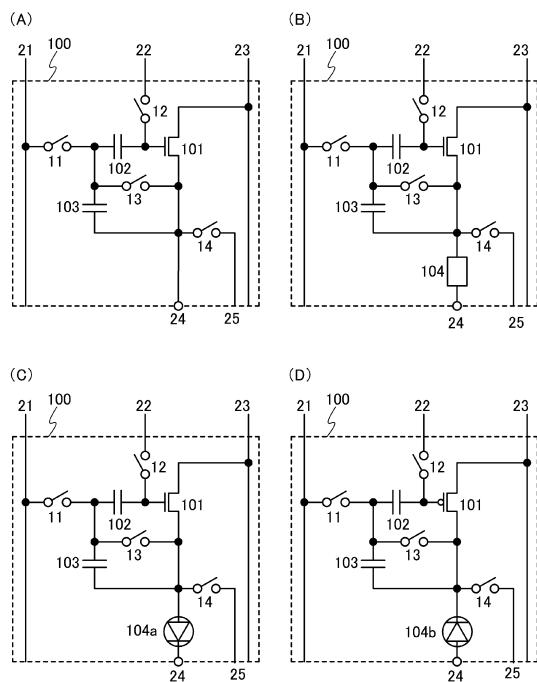

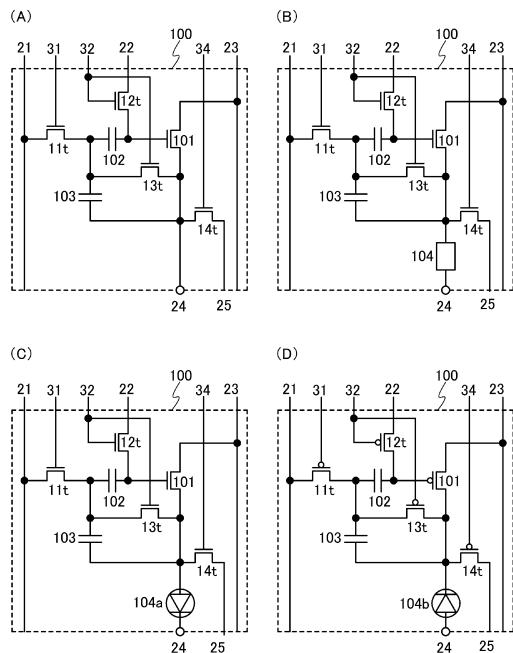

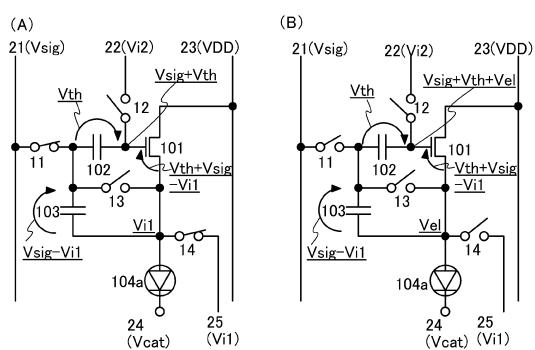

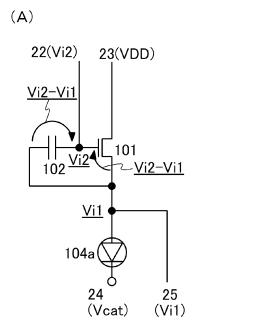

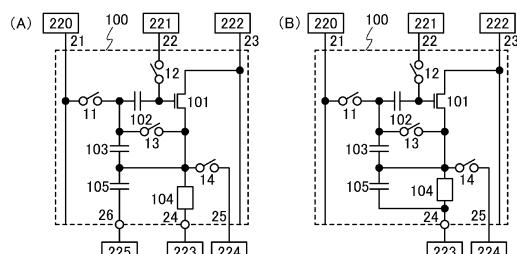

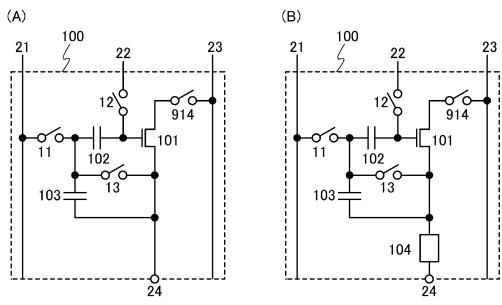

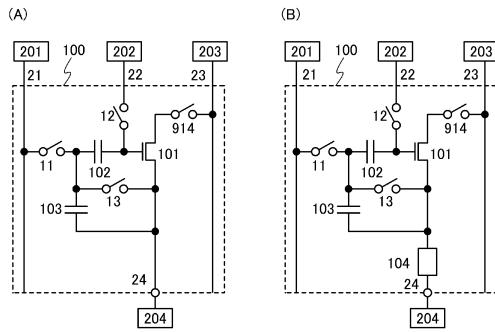

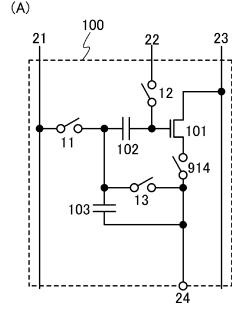

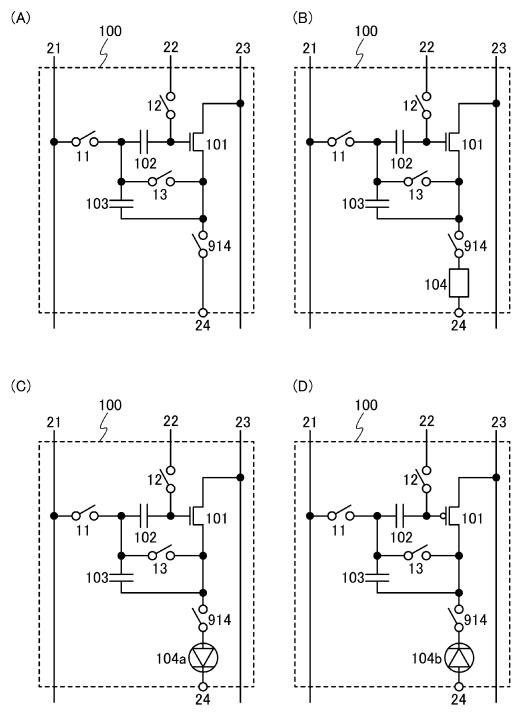

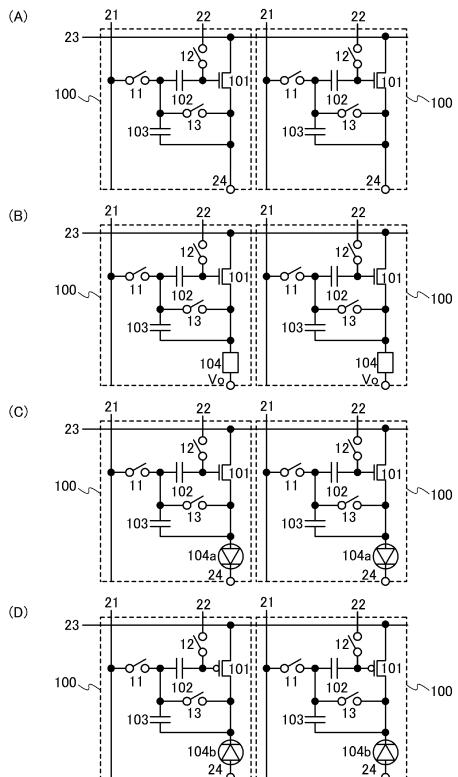

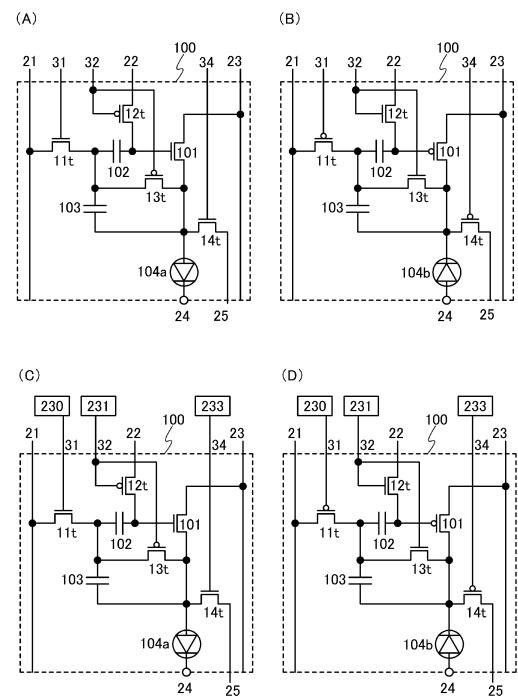

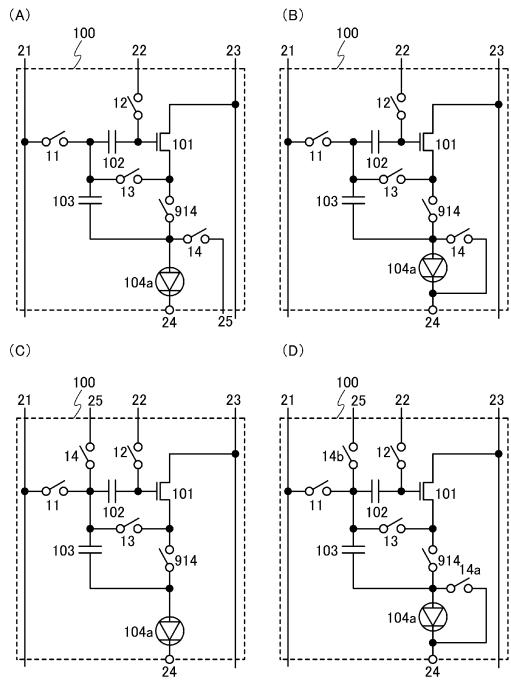

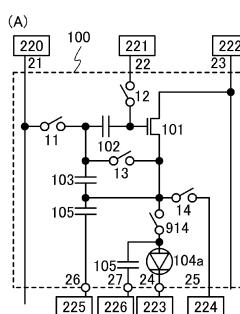

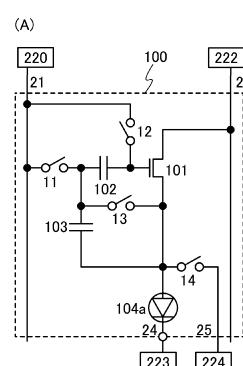

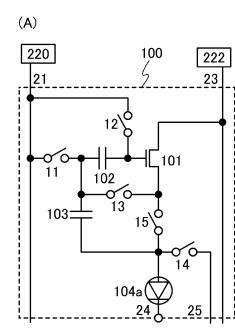

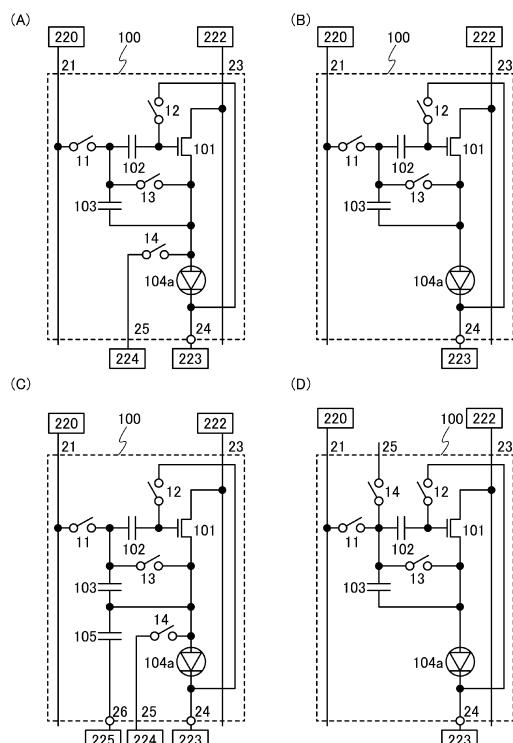

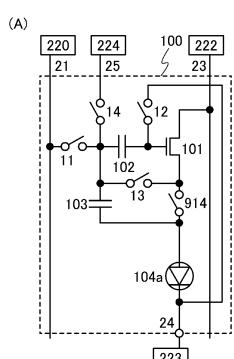

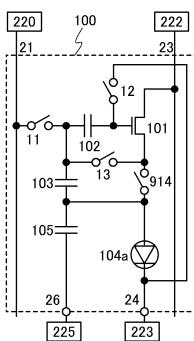

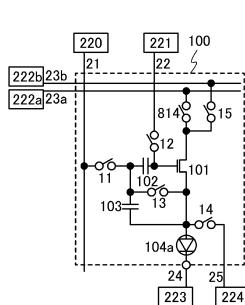

図1(A)に示す回路100は、本発明の一態様に係る半導体装置である。回路100は、スイッチ11、スイッチ12、スイッチ13、トランジスタ101、容量素子102、容量素子103を有する。なお、図1(A)では、トランジスタ101がnチャネル型である場合を一例として示している。

20

【0049】

具体的に、図1(A)では、スイッチ11は、配線21と、容量素子102の一方の電極(端子)又は容量素子103の一方の電極(端子)との間の導通状態を制御する機能を有する。スイッチ12は、配線22と、容量素子102の他方の電極(端子)及びトランジスタ101のゲートとの間の導通状態を制御する機能を有する。スイッチ13は、トランジスタ101のソースまたはドレインの一方、又は、容量素子103の他方の電極(端子)と、容量素子102の一方の電極、又は、容量素子103の一方の電極(端子)との間の導通状態を制御する機能を有する。トランジスタ101のソースまたはドレインの他方は、配線23に接続されている。トランジスタ101のソースまたはドレインの一方、又は、容量素子103の他方の電極(端子)は、配線24に接続されている。

30

【0050】

なお、トランジスタが有するソース(ソース端子、ソース領域またはソース電極)とドレイン(ドレイン端子、ドレイン領域またはドレイン電極)は、トランジスタの極性及びソースとドレインに与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がソースと呼ばれ、高い電位が与えられる方がドレインと呼ばれる。また、pチャネル型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がドレインと呼ばれ、高い電位が与えられる方がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。そこで、ソースとして機能する部分、及びドレインとして機能する部分を、ソース又はドレインと呼ばない場合がある。その場合、一例として、ソースとドレインとの一方を、第1端子、第1電極、又は第1領域と表記し、ソースとドレインとの他方を、第2端子、第2電極、又は第2領域と表記する場合がある。

40

【0051】

なお、スイッチは、端子間の導通状態と非導通状態を切り替えて動作する機能を有しており、電流を流すか流さないかを制御する機能を有している素子である。または、スイッチは、電流を流す経路を選択して切り替える機能を有し、例えば、経路1に電流を流すことが出来るようにするか、経路2に電流を流すことができるようとするかを選択して切り替

50

える機能を有している。例えば、電気的スイッチまたは機械的なスイッチなどを用いることができる。具体的には、トランジスタ、ダイオード、デジタルマイクロミラーデバイス（DMD）のようにMEMS（マイクロ・エレクトロ・メカニカル・システム）技術を用いたスイッチ、などで構成すればよい。また、スイッチはトランジスタを組み合わせた論理回路でもよい。スイッチとしてトランジスタを用いる場合、該トランジスタの極性は特に限定されない。ただし、オフ電流が小さいトランジスタを用いることが望ましく、入力電位に応じて、トランジスタの極性を使い分けることが望ましい。

#### 【0052】

なお、オフ電流が小さいトランジスタとしては、LDD領域を有するトランジスタ、マルチゲート構造を有するトランジスタ、または酸化物半導体をチャネル形成領域に含むトランジスタ等がある。また、トランジスタを組み合わせてスイッチとして動作させる場合、nチャネル型とpチャネル型の両方を用いた相補型のスイッチにしてもよい。相補型のスイッチにすることで、スイッチに入力する電位が、出力電位と比べて相対的に変化しても、適切に動作させることができる。

10

#### 【0053】

なお、スイッチとしてトランジスタを用いる場合、スイッチは、入力端子（ソースまたはドレインの一方）と、出力端子（ソースまたはドレインの他方）と、導通を制御する端子（ゲート）とを有している場合がある。一方、スイッチとしてダイオードを用いる場合、スイッチは、導通を制御する端子を有していない場合がある。したがって、トランジスタよりもダイオードをスイッチとして用いた方が、端子を制御するための配線を少なくすることができる。

20

#### 【0054】

なお、トランジスタの一例としては、チャネル形成領域の上下にゲートが配置されている構造のトランジスタを適用することができる。半導体膜の上下にゲートを配置することにより、複数のトランジスタが並列に接続されたような回路構成となる。よって、チャネル形成領域が増えるため、電流値の増加を図ることができる。または、チャネル形成領域の上下にゲートが配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図ることができる。

#### 【0055】

なお、トランジスタの一例としては、チャネル形成領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造のトランジスタを用いることができる。チャネル形成領域（もしくはその一部）にソース電極やドレイン電極が重なる構造にすることによって、チャネル形成領域の一部に電荷が溜まることにより動作が不安定になることを防ぐことができる。

30

#### 【0056】

なお、容量素子102または容量素子103は、例えば、配線、半導体膜、または電極等で絶縁膜または有機膜を挟んだ構成とすればよい。

#### 【0057】

なお、図1(A)で示した回路100は、図1(B)に示すように負荷104を有しても良い。図1(B)に示す回路100では、負荷104が、トランジスタ101のソースまたはドレインの一方、または、容量素子103の他方の電極と、配線24との間に接続されている。

40

#### 【0058】

なお、本明細書中において負荷とは、例えば、整流性を有するものや、容量性を有するものや、抵抗性を有するもの、スイッチを有する回路、画素回路、電流源回路などがある。例えば、整流性を有するものは、印加するバイアス方向により抵抗値が異なる電流電圧特性を有し、一方向のみにほとんど電流が流れる電気的特性を有するものであるとする。具体的に、負荷104として、表示素子（液晶素子、EL素子など）、発光素子（EL（エレクトロルミネッセンス）素子（有機物及び無機物を含むEL素子、有機EL素子、無機EL素子）、LED（白色LED、赤色LED、緑色LED、青色LEDなど）、トラン

50

ジスタ（電流に応じて発光するトランジスタ）、電子放出素子、または、表示素子や発光素子の一部（例えば、画素電極、アノード、カソード）などが挙げられる。

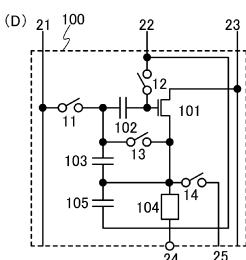

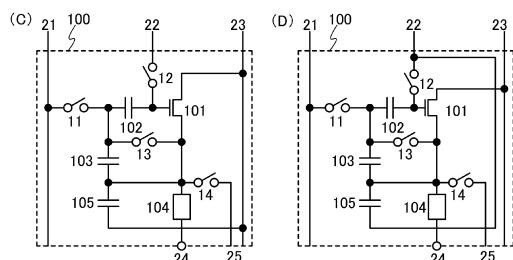

【0059】

図1(C)に、負荷104として、発光素子104aを用いた場合の、回路100の構成を示す。図1(C)では、発光素子104aのアノードが、トランジスタ101のソースまたはドレインの一方、または、容量素子103の他方の電極に接続されており、発光素子104aのカソードが、配線24に接続されている場合を一例として示している。

【0060】

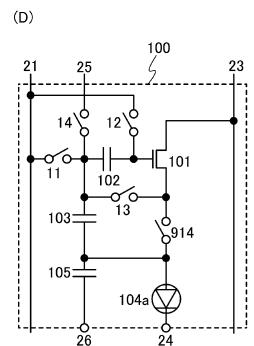

また、図1(D)に、負荷104として、発光素子104bを用いた場合の、回路100の構成を示す。図1(D)では、発光素子104bのカソードが、トランジスタ101のソースまたはドレインの一方、または、容量素子103の他方の電極に接続されており、発光素子104bのアノードが、配線24に接続されている場合を一例として示している。なお、図1(D)では、トランジスタ101がpチャネル型である場合を一例として示している。

【0061】

また、本発明の一態様に係る半導体装置は、例えば、図1(A)乃至図1(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

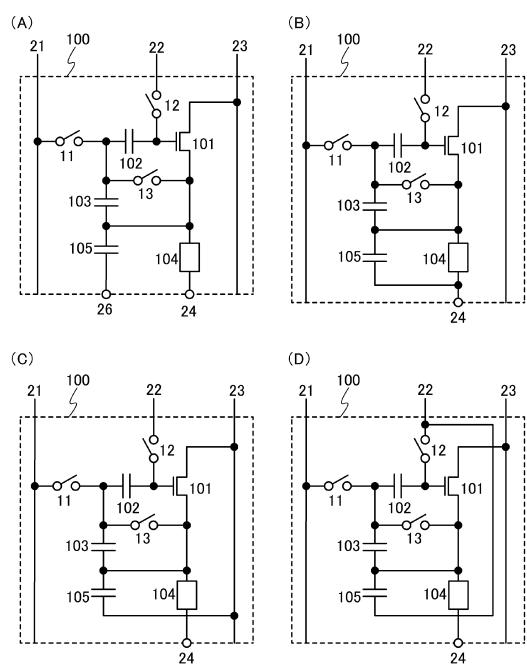

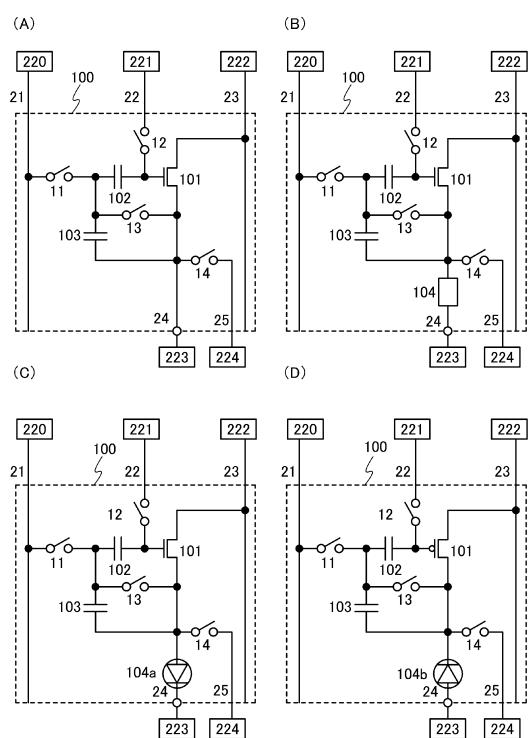

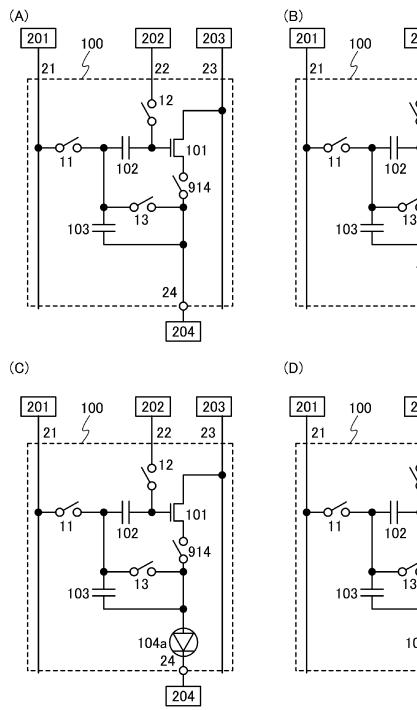

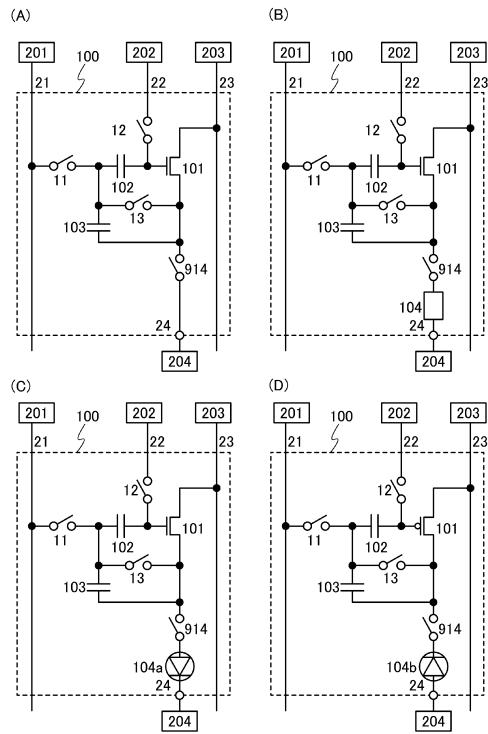

【0062】

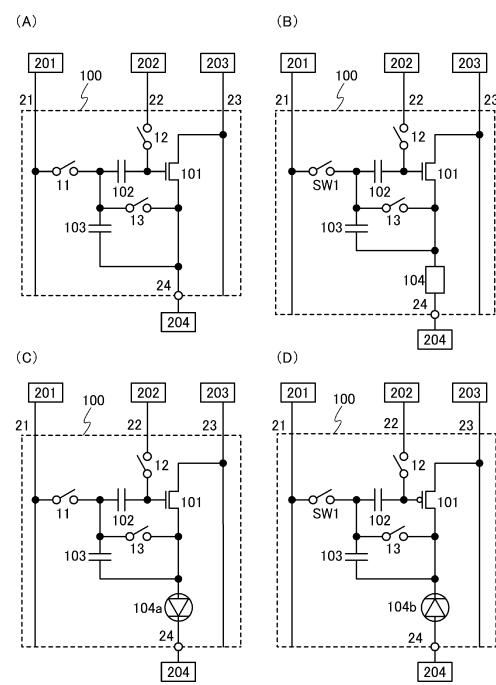

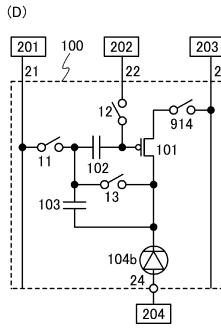

図2(A)乃至図2(D)に示す半導体装置は、図1(A)乃至図1(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路201と、配線22に一定電圧や信号を供給する機能を有する回路202と、配線23に一定電圧や信号を供給する機能を有する回路203と、配線24に一定電圧や信号を供給する機能を有する回路204とを、それぞれ有する。

【0063】

具体的に、回路201は、配線21に、電位Vi1または電位Vsigを供給する機能を有する。回路201の例としては、ソースドライバ（信号線駆動回路）などがある。したがって、配線21は、電位Vi1、及び/又は、電位Vsigを、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線21は、映像信号線としての機能を有している。または、配線21は、初期化用配線としての機能を有している。

【0064】

電位Vi1は、回路100内の各ノードの電位を初期化するための電位である。または、電位Vi1は、一例としては、容量素子102に電荷を供給するための電位である。または、電位Vi1は、一例としては、トランジスタ101をオン状態にするための電位である。なお、電位Vi1は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

【0065】

なお、一例としては、電位Vsigを回路100に供給する前において、電位Vi1が回路100に供給される。

【0066】

電位Vsigは、トランジスタ101のドレイン電流の大きさを制御するための電位である。図2(B)に示した半導体装置の場合は、上記ドレイン電流が負荷104に供給される。図2(C)に示した半導体装置の場合は、上記ドレイン電流が発光素子104aに供給される。図2(D)に示した半導体装置の場合は、上記ドレイン電流が発光素子104bに供給される。例えば、トランジスタ101のドレイン電流を一定値に保つ場合は、電位Vsigの高さを一定とする。また、例えば、トランジスタ101のドレイン電流を一定値としない場合は、電位Vsigの高さを、時間と共に変化させる。一例としては、電位Vsigは映像信号、及び/又は、アナログ信号である。ただし、本発明の実施形態の一態様は、これに限定されず、電位Vsigは、一定の電位でもよい。

10

20

30

40

50

## 【0067】

また、回路202は、配線22に、電位 $V_{i2}$ を供給する機能を有する。回路204の例としては、電源回路などがある。したがって、配線22は、電位 $V_{i2}$ を、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線22は、初期化用配線としての機能を有している。なお、配線22の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

## 【0068】

電位 $V_{i2}$ は、回路100内の各ノード（特にトランジスタ101のゲート）の電位を初期化するための電位である。なお、図2（C）の場合、電位 $V_{i2}$ は、配線24の電位と同じ、または、それよりも低いことが好適である。これにより、発光素子104aに電流が流れることを低減することが出来る。図2（D）の場合、電位 $V_{i2}$ は、配線24の電位と同じ、または、それよりも高いことが好適である。これにより、発光素子104bに電流が流れることを低減することが出来る。ただし、電位 $V_{i2}$ は、これらに限定されない。なお、電位 $V_{i2}$ は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

10

## 【0069】

なお、配線22は、他の配線、または、別の回路100が有する配線と接続させることが可能である。これにより、配線の数を減らすことが出来る。

## 【0070】

20

また、回路203は、配線23に、電源電位（高電源電位または低電源電位）、例えば、電位 $V_{DD}$ 、または、電位 $V_{SS}$ を供給する機能を有する。または、回路203は、配線23に、信号を供給する機能を有する。回路203の例としては、電源回路、パルス出力回路、ゲートドライバ回路などがある。したがって、配線23は、電源電位または信号を伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線23は、トランジスタ101に電流を供給することが出来る機能を有している。または、配線23は、負荷104に電流を供給することが出来る機能を有している。または、配線23は、電源線としての機能を有している。または、配線23は、電流供給線としての機能を有している。なお、配線23の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。例えば、配線23の電位は、負荷104に、順バイアス電圧だけでなく、逆バイアス電圧を加えるような電位であってもよい。

30

## 【0071】

また、回路204は、配線24に、電源電位（低電源電位または高電源電位）、例えば、電位 $V_{cat}$ を供給する機能を有する。回路204の例としては、電源回路などがある。したがって、配線24は、電源電位を伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線24は、負荷104に電流を供給することが出来る機能を有している。または、配線24は、トランジスタ101に電流を供給することが出来る機能を有している。または、配線24は、共通線としての機能を有している。または、配線24は、陰極配線としての機能を有している。または、配線24は、陽極配線としての機能を有している。なお、配線24の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。例えば、配線24の電位は、負荷104に、順バイアス電圧だけでなく、逆バイアス電圧を加えるような電位であってもよい。

40

## 【0072】

電位 $V_{DD}$ と電位 $V_{cat}$ の電位差により、トランジスタ101におけるドレイン電流の向きが決まる。例えば、電位 $V_{DD}$ が電位 $V_{cat}$ より高い場合、配線23から配線24へ電流が流れる。配線23の電位が電位 $V_{SS}$ の場合で、電位 $V_{cat}$ より低い場合、配線24から配線23へ電流が流れる。

## 【0073】

50

なお、図2(A)乃至図2(D)では、半導体装置が、回路100に加えて、回路201、回路202、回路203、及び回路204を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路201、回路202、回路203、及び回路204を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

【0074】

なお、トランジスタ101は、一例としては、少なくとも電流源としての機能を有している。したがって、例えば、トランジスタ101は、トランジスタ101の両端(ソースとドレインの間)に加わる電圧の大きさが変化しても、概ね一定の電流を供給する機能を有している。または、例えば、トランジスタ101は、負荷104の電位が変化しても、負荷104に概ね一定の電流を供給する機能を有している。または、例えば、トランジスタ101は、配線23の電位が変化しても、概ね一定の電流を供給する機能を有している。

10

【0075】

ただし、本発明の実施形態の一態様は、これに限定されず、トランジスタ101は電流源としての機能を有さないことも可能である。例えば、トランジスタ101は、スイッチの機能を有することが可能である。

【0076】

なお、電流源とは別の電源として、電圧源がある。電圧源は、それに接続された回路に流れる電流が変化しても、一定の電圧を供給する機能を有している。したがって、電圧源も電流源も、電圧と電流とを供給する機能を有しているが、何が変化しても、一定の何を供給する機能を有しているのか、という点で、異なった機能を有するものである。電流源は、両端の電圧が変化しても、一定の電流を供給する機能を有し、電圧源は、電流が変化しても、一定の電圧を供給する機能を有している。

20

【0077】

なお、図1などは、回路構成の一例であるため、さらに、トランジスタを追加して設けることが可能である。逆に、図1などの各ノードにおいて、追加してトランジスタ、スイッチ、受動素子などを設けないようにすることも可能である。例えば、各スイッチの端子が接続されたノード、トランジスタの各端子が接続されたノード、またはノード、負荷の各端子が接続されたノードにおいて、直接的に接続されたトランジスタを、これ以上は設けないようにすることが可能である。従って、例えば、負荷104とトランジスタ101と容量素子103とスイッチ13とが接続されているノードにおいて、直接的に接続されているトランジスタはトランジスタ101のみであり、他のトランジスタはそのノードと直接的に接続されていない、というような構成にすることが可能である。

30

【0078】

そのため、トランジスタを追加しない場合には、少ないトランジスタ数で回路を構成することが可能となる。

【0079】

なお、図1及び図2に示した回路100は、スイッチ11、スイッチ12、スイッチ13にトランジスタを用いることができる。

【0080】

40

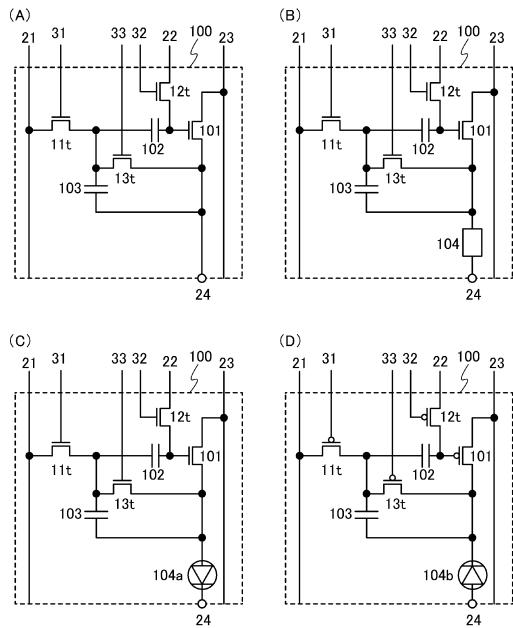

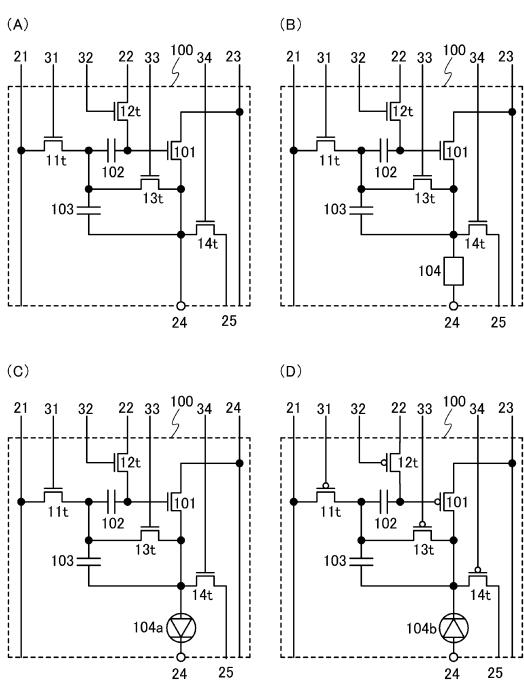

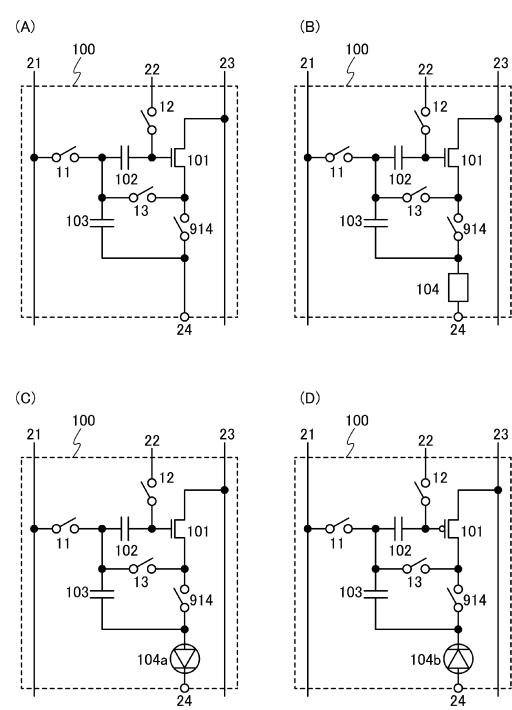

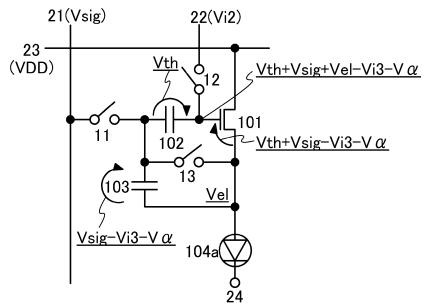

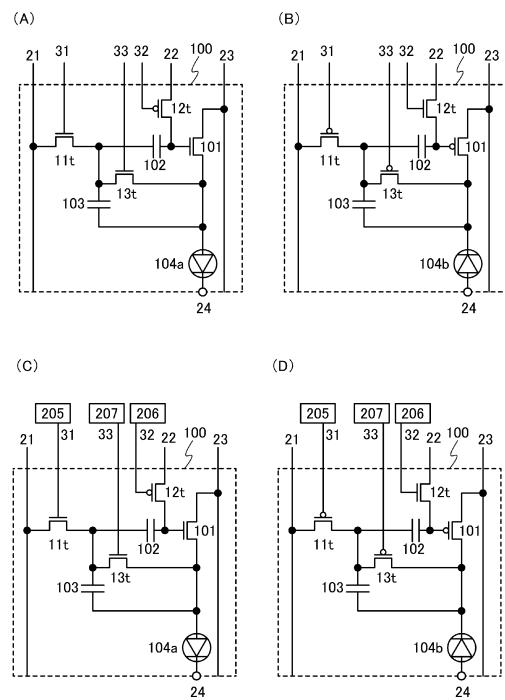

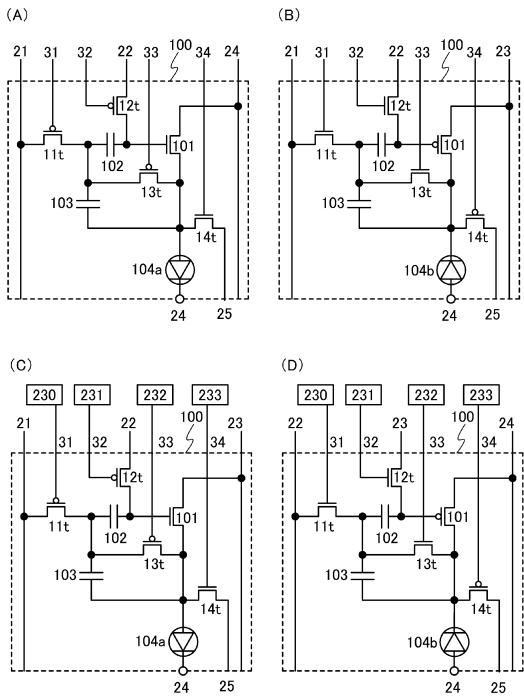

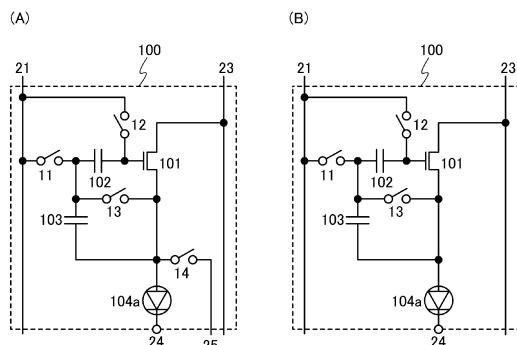

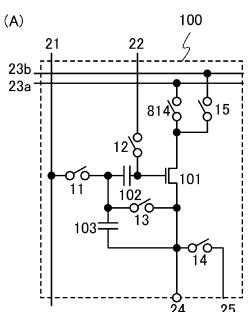

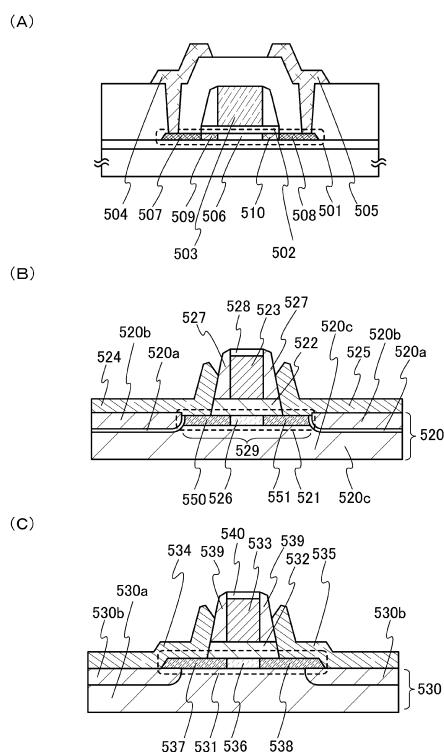

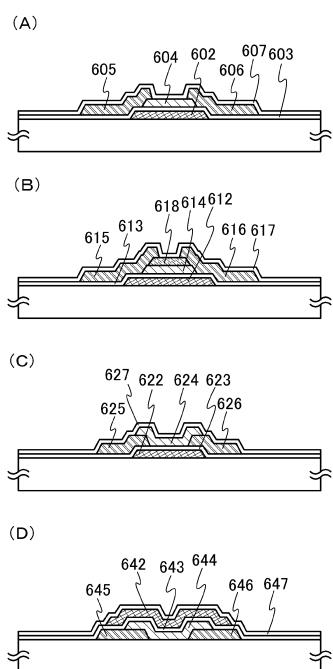

図1(A)乃至図1(D)に示した回路100において、スイッチ11としてトランジスタ11t、スイッチ12としてトランジスタ12t、及びスイッチ13としてトランジスタ13tを用いた場合の回路100の構成を、図3(A)乃至図3(D)に示す。なお、図3(A)乃至図3(C)では、トランジスタ11t、トランジスタ12t、及びトランジスタ13tが全てnチャネル型である場合を一例として示している。また、図3(D)では、トランジスタ11t、トランジスタ12t、及びトランジスタ13tが全てpチャネル型である場合を一例として示している。トランジスタ11t、トランジスタ12t、及びトランジスタ13tを全て同じ極性のトランジスタとすることで、これらのトランジスタを少ない工程数で製造できる。ただし、本発明の実施形態の一態様は、これに限定されず、異なる極性のトランジスタを用いることも可能である。

50

## 【0081】

なお、図3(A)乃至図3(D)において、トランジスタ11tは、ゲートが配線31に接続されている。配線31に供給される電位に従って、トランジスタ11tは導通状態または非導通状態となる。トランジスタ12tは、ゲートが配線32に接続されている。配線32に供給される電位に従って、トランジスタ12tは導通状態または非導通状態となる。トランジスタ13tは、ゲートが配線33に接続されている。配線33に供給される電位に従って、トランジスタ13tは導通状態または非導通状態となる。したがって、配線31乃至配線33の電位は、パルス状であり、一定ではないことが望ましいが、本発明の実施形態の一態様は、これに限定されない。または、配線31乃至配線33は、ゲート信号線(ゲート線)、選択信号線、または、スキャン線(走査線)としての機能を有している。

## 【0082】

なお、配線31乃至配線33において、その中の少なくとも2本の配線は、互いに接続させることが可能である。または、配線31乃至配線33の少なくとも1本は、別の回路100の配線31乃至配線33の少なくとも1本と接続させることが可能である。

## 【0083】

また、本発明の一態様に係る半導体装置は、図3(A)乃至図3(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

## 【0084】

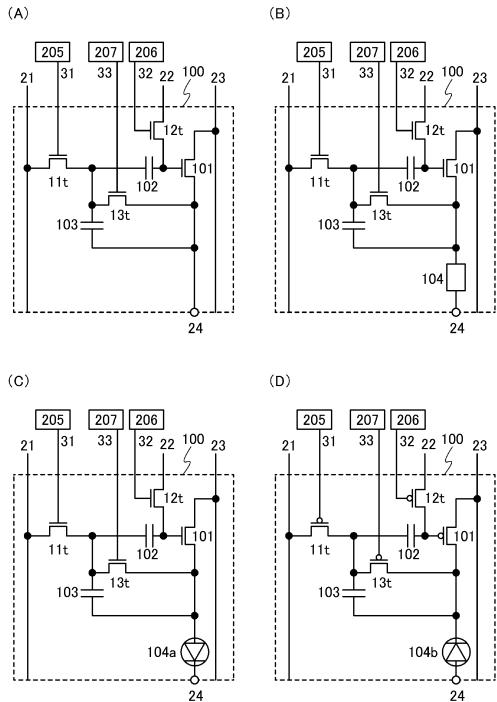

図4(A)乃至図4(D)に示す半導体装置は、図3(A)乃至図3(D)に示す回路100に加えて、配線31に一定電圧や信号を供給する機能を有する回路205と、配線32に一定電圧や信号を供給する機能を有する回路206と、配線33に一定電圧や信号を供給する機能を有する回路207とを、それぞれ有する。回路205、回路206、回路207の例としては、ゲートドライバ(走査線駆動回路)などがある。

## 【0085】

なお、回路201、回路202、回路203、回路204、回路205、回路206、回路207は、一つの同じ回路であってもよいし、別々の回路であってもよい。

## 【0086】

なお、図4(A)乃至図4(D)では、半導体装置が、回路100に加えて、回路205、回路206、及び回路207を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路205、回路206、及び回路207を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

## 【0087】

また、図3(C)に示す回路100において、トランジスタ101、トランジスタ11t、及びトランジスタ13tがnチャネル型、トランジスタ12tがpチャネル型である場合の回路100の構成を図37(A)に示す。また、図3(D)に示す回路100において、トランジスタ101、トランジスタ11t、及びトランジスタ13tがpチャネル型、トランジスタ12tがnチャネル型である場合の回路100の構成を図37(B)に示す。このように、様々な極性のトランジスタを用いることが出来る。

## 【0088】

また、本発明の一態様に係る半導体装置は、図37(A)及び図37(B)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

## 【0089】

図37(C)及び図37(D)に示す半導体装置は、図37(A)及び図37(B)に示す回路100に加えて、配線31に一定電圧や信号を供給する機能を有する回路205と、配線32に一定電圧や信号を供給する機能を有する回路206と、配線33に一定電圧や信号を供給する機能を有する回路207とを、それぞれ有する。

## 【0090】

10

20

30

40

50

なお、図37(C)及び図37(D)では、半導体装置が、回路100に加えて、回路205、回路206、及び回路207を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路205、回路206、及び回路207を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

【0091】

なお、トランジスタ101は、電流を流すときには、飽和領域で動作する場合が多い。よって、図3、図4、及び図37において、トランジスタ101のチャネル長またはゲート長を、トランジスタ11t、トランジスタ12t、及び/または、トランジスタ13tよりも長くすることが望ましい。チャネル長またはゲート長を長くすることにより、飽和領域での特性がフラットになり、キンク効果を低減することができる。好ましくは、5倍以上、より好ましくは10倍以上であることが望ましい。一例としては、トランジスタ101のチャネル長またはゲート長は、 $10\text{ }\mu\text{m}$ 以上、より好ましくは、 $20\text{ }\mu\text{m}$ 以上である。或いは、トランジスタ101のチャネル幅またはゲート幅を、トランジスタ11t、トランジスタ12t、及び/または、トランジスタ13tよりも長くすることにより、トランジスタ101は、飽和領域においても、多くの電流を流すことができる。好ましくは、5倍以上、より好ましくは10倍以上であることが望ましい。トランジスタ101のチャネル幅またはゲート幅は、 $20\text{ }\mu\text{m}$ 以上、より好ましくは、 $30\text{ }\mu\text{m}$ 以上である。ただし、本発明の実施形態の一態様は、これらに限定されない。

10

【0092】

次いで図1(C)に示す回路100を例に挙げて、本発明の一態様の半導体装置の動作について説明する。

20

【0093】

図1(C)に示す回路100の動作は、主に第1の動作、第2の動作、第3の動作、第4の動作、第5の動作に分けることができる。ただし、これに限定されず、新たな動作の追加、或いは、一部の動作の削除も可能である。

【0094】

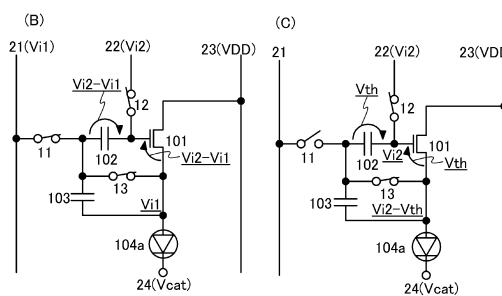

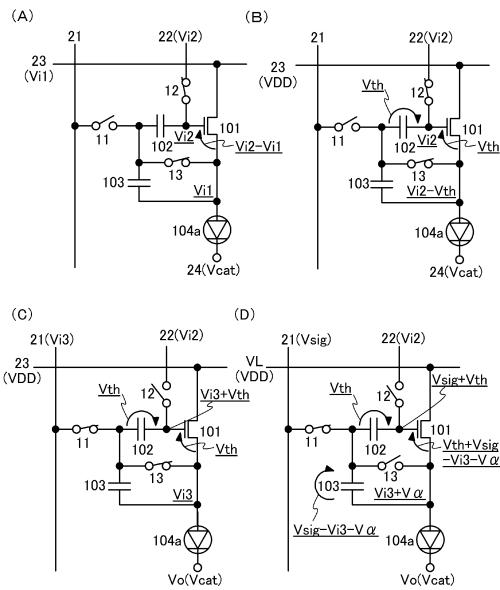

図1(C)に示す回路100における、スイッチ11、スイッチ12、及びスイッチ13の動作と、配線21の電位と、トランジスタ101のゲートソース間電圧( $V_{gs101}$ )とを示すタイミングチャートの一例を、図5(A)に図示する。

30

【0095】

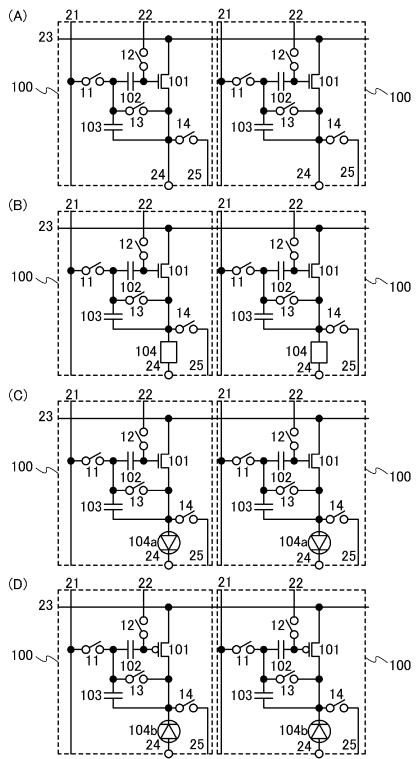

まず、期間T11において行われる第1の動作について説明する。期間T11では、図5(A)に示すように、スイッチ11、スイッチ12、及びスイッチ13が導通状態である。また、配線21には電位 $V_{i1}$ が供給される。よって、期間T11では、図5(B)に示すように、容量素子102に電圧 $V_{i2} - V_{i1}$ が供給され、発光素子104aのアノードは電位 $V_{i1}$ となり、トランジスタ101のゲートソース間電圧( $V_{gs101}$ )は、電圧 $V_{i2} - V_{i1}$ となる。つまり、トランジスタ101、及び、容量素子102を、初期化していることとなる。

【0096】

なお、図1(C)に示す回路100では、電位 $V_{i2}$ は、電位 $V_{i1}$ にトランジスタ101の閾値電圧 $V_{th}$ を加算した電位よりも、高いことが望ましい。つまり、電位 $V_{i2}$ と電位 $V_{i1}$ は、トランジスタ101がオン状態となるような電位であることが望ましい。また、電位 $V_{i1}$ に発光素子104aの閾値電圧 $V_{th}$ (発光素子104aが発光はじめる電圧)を加算した電位は、電位 $V_{cat}$ より低いことが望ましい。例えば、電位 $V_{i1}$ は、電位 $V_{cat}$ と同じ電位か、それよりも低い電位であることが望ましい。電位 $V_{i1}$ が、電位 $V_{cat}$ よりも低い場合には、発光素子104aが逆バイアス状態となるため、発光素子104aの劣化を低減する、或いはショート箇所をリペアすることが可能である。また、電位 $V_{i2}$ から発光素子104aの閾値電圧 $V_{th}$ を差し引いた電位は、電位 $V_{cat}$ より低いことが望ましい。なお、以下、一例として、閾値電圧 $V_{th}$ が0であるものと仮定する。

40

【0097】

50

期間 T 1 2 において行われる第 2 の動作について説明する。期間 T 1 2 では、図 5 ( A ) に示すように、スイッチ 1 1 が非導通状態、スイッチ 1 2 及びスイッチ 1 3 が導通状態である。スイッチ 1 1 が非導通状態となることで、容量素子 1 0 2 に蓄積されている電荷がトランジスタ 1 0 1 を介して放出され、トランジスタ 1 0 1 のソースの電位が上昇する。そして、トランジスタ 1 0 1 がオフ状態となると、容量素子 1 0 2 からの電荷の放出が止まる。最終的には、トランジスタ 1 0 1 の閾値電圧  $V_{th}$  が容量素子 1 0 2 に保持される。よって、期間 T 1 2 では、図 5 ( C ) に示すように、容量素子 1 0 2 に閾値電圧  $V_{th}$  が保持され、発光素子 1 0 4 a のアノードは電位  $V_{i2} - V_{th}$  となり、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) は、閾値電圧  $V_{th}$  となる。つまり、トランジスタ 1 0 1 のしきい値電圧  $V_{th}$  を取得することができる。

10

#### 【 0 0 9 8 】

なお、 $V_{gs101}$  が、トランジスタ 1 0 1 のしきい値電圧  $V_{th}$  に等しくなるまでには、非常に長い時間が必要となる場合がある。したがって、 $V_{gs101}$  は、しきい値電圧  $V_{th}$  まで完全に低下させずに、動作させる場合も多い。つまり、 $V_{gs101}$  は、しきい値電圧  $V_{th}$  よりも、わずかに大きい値となった状態で、期間 T 1 2 が終了する場合も多い。つまり、期間 T 1 2 が終了した時点では、 $V_{gs101}$  は、しきい値電圧に応じた大きさの電圧になっている、ということも出来る。

#### 【 0 0 9 9 】

なお、第 2 の動作において、トランジスタ 1 0 1 のしきい値電圧  $V_{th}$  が正か負かということに関係なく、動作させることができる。これは、トランジスタ 1 0 1 がオフ状態となるまで、トランジスタ 1 0 1 のソース電位が上昇できるからである。つまり、トランジスタ 1 0 1 のゲート電位よりも、トランジスタ 1 0 1 のソース電位の方が高くなつた状態で、ようやくトランジスタ 1 0 1 がオフし、 $V_{gs101}$  が  $V_{th}$  となる、ということが可能であるからである。したがって、トランジスタ 1 0 1 がエンハンスメント型 (ノーマリオフ型) であっても、デブリーション型 (ノーマリオン型) であっても、正常に動作させることができる。

20

#### 【 0 1 0 0 】

なお、発光素子 1 0 4 a のアノードの電位が高くなつたときに、発光素子 1 0 4 a に電流が流れないようにすることが望ましい。そのためには、発光素子 1 0 4 a に電流が流れないように、電位  $V_{i2}$  を低い値とすることが好適である。ただし、発明の実施形態の一様様は、これに限定されない。なお、発光素子 1 0 4 a と直列にスイッチを設けて、それをオフ状態にすることにより、発光素子 1 0 4 a に電流が流れないようにすることが可能であれば、電位  $V_{i2}$  は、高い値でもよい。

30

#### 【 0 1 0 1 】

期間 T 1 3 において行われる第 3 の動作について説明する。期間 T 1 3 では、図 5 ( A ) に示すように、スイッチ 1 1 及びスイッチ 1 3 が導通状態、スイッチ 1 2 が非導通状態である。また、配線 2 1 には、一例として、電位  $V_{i1}$  が供給される。よって、期間 T 1 3 では、図 6 ( A ) に示すように、容量素子 1 0 2 に閾値電圧  $V_{th}$  (または  $V_{th}$  に応じた大きさの電圧) が保持され、発光素子 1 0 4 a のアノードは電位  $V_{i1}$  となり、トランジスタ 1 0 1 のゲートの電位は電位  $V_{i1} + V_{th}$  (または  $V_{th}$  に応じた大きさの電圧) となり、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) は、閾値電圧  $V_{th}$  (または  $V_{th}$  に応じた大きさの電圧) となる。これにより、発光素子 1 0 4 a のアノードの電位、または、トランジスタ 1 0 1 のソースの電位を初期化することができる。

40

#### 【 0 1 0 2 】

なお、上記第 3 の動作は必ずしも行う必要はなく、第 2 の動作の後に、以下に示す第 4 の動作を行うようにしても良い。

#### 【 0 1 0 3 】

なお、期間 T 1 3 における配線 2 1 の電位は、電位  $V_{i1}$  に限定されず、別の大きさの電位 (例えば電位  $V_{i3}$ ) とすることも可能である。ただし、期間 T 1 3 における配線 2 1 の電位を電位  $V_{i1}$  とすることにより、回路 2 0 1 の構成をシンプルにすることができます

50

。または、配線 21 に、複数の回路 100 が接続されている場合において、配線 21 の電位を電位  $V_{i1}$  とすることにより、ある回路 100 では、期間  $T_{11}$  として動作させ、別の回路 100 では、期間  $T_{13}$  として動作させることが出来るため、動作期間を効率的に使用することが出来る。

【0104】

期間  $T_{14}$  において行われる第 4 の動作について説明する。期間  $T_{14}$  では、図 5 (A) に示すように、スイッチ 11 が導通状態、スイッチ 12 及びスイッチ 13 が非導通状態である。また、配線 21 には電位  $V_{sig}$  が供給される。よって、期間  $T_{14}$  では、図 6 (B) に示すように、容量素子 102 に閾値電圧  $V_{th}$  ( または  $V_{th}$  に応じた大きさの電圧である ) が保持され、容量素子 103 に電圧  $V_{sig} - V_{i1} - V$  が保持され、発光素子 104a のアノードは電位  $V_{i1} + V$  となり、トランジスタ 101 のゲートの電位は電位  $V_{sig} + V_{th}$  となり、トランジスタ 101 のゲートソース間電圧 ( $V_{gs101}$ ) は電圧  $V_{sig} + V_{th} - V_{i1} - V$  となる。したがって、電位  $V_{sig}$  を容量素子 103 に入力することが出来る。または、容量素子 102 の電圧と容量素子 103 の電圧との和が、トランジスタ 101 のゲートソース間電圧となるようにすることができる。

【0105】

なお、第 4 の動作で、電位  $V$  は、発光素子 104a のアノードが電気的に浮遊状態 ( フローティング状態 ) となることで変動する電位である。電位  $V$  は、トランジスタ 101 がオフであるならば、発光素子 104a の静電容量と、容量素子 102 及び容量素子 103 の静電容量の比に応じて、その値が定まる。しかし、電位  $V_{sig}$  の高さによっては、トランジスタ 101 がオンするので、トランジスタ 101 を介して発光素子 104a のアノードに電荷が流入してしまう。よって、電位  $V$  は、上記静電容量の比によってのみ決まりず、発光素子 104a のアノードに流入する電荷によっても、その値が変化する。

【0106】

ここで、ゲートソース間電圧  $V_{gs}$  を理想的な値、すなわち電圧  $V_{sig} + V_{th} - V_{i1}$  に近づけるには、電位  $V$  が小さくなるように設計することが好ましい。具体的には、発光素子 104a の静電容量が、容量素子 102 及び容量素子 103 の静電容量よりも十分に大きければ、ゲートソース間電圧  $V_{gs}$  を理想的な値に近づけることができる。

【0107】

したがって、容量素子 103 の容量値は、負荷 104 ( 発光素子 104a ) の寄生容量の容量値よりも、小さいことが望ましく、望ましくは 1 / 2 倍以下、より望ましくは 1 / 5 倍以下が好適である。または、容量素子 103 の電極の面積は、負荷 104 ( 発光素子 104a ) の電極の面積よりも小さいことが望ましく、望ましくは 1 / 2 倍以下、より望ましくは 1 / 5 倍以下が好適である。ただし、本発明の実施形態の一態様は、これらに限定されない。

【0108】

また、ゲートソース間電圧 ( $V_{gs101}$ ) を理想的な値に近づけるには、発光素子 104a のアノードに流入する電荷量  $Q$  を小さくすることが、望ましい。よって、上記電荷量  $Q$  を小さくするために期間  $T_{14}$  はなるべく短い方が良い。なお、上述したように、予め期間  $T_{13}$  において配線 21 に電位  $V_{sig}$  を供給しておくと、期間  $T_{14}$  においてスイッチ 11 を導通状態にしたときに、トランジスタ 101 のゲートの電位を、電位  $V_{sig} + V_{th}$  に素早く近づけることができる。よって、期間  $T_{14}$  を短くできるので、電荷量  $Q$  を小さくする上で望ましい。

【0109】

したがって、期間  $T_{14}$  の長さは、期間  $T_{11}$ 、期間  $T_{12}$ 、及び / 又は、期間  $T_{13}$  の長さよりも、小さいことが望ましく、望ましくは 2 / 3 倍以下、より望ましくは 1 / 2 倍以下が好適である。ただし、本発明の実施形態の一態様は、これらに限定されない。

【0110】

なお、電荷量  $Q$  は、上述したように小さい方が望ましいが、トランジスタ 101 の移動度のばらつきが大きい場合は、電荷量  $Q$  によって移動度のばらつきを抑える効果が期待でき

10

20

30

40

50

る。以下、この理由について説明する。

【0111】

電荷量Qは、期間T14において、トランジスタ101のドレインからソースに流れ込む電荷量に相当する。よって、電荷量Qは、トランジスタ101の移動度が大きいほど、大きくなる。そして、電荷量Qが大きくなると、発光素子104aの発光時における、トランジスタ101のゲートソース間電圧( $V_{g s 101}$ )が、小さくなる。すなわち、電荷量Qにより、トランジスタ101の移動度が大きいほど、発光素子104aに供給される電流値が小さくなるように補正がかかり、また、トランジスタ101の移動度が小さいほど、発光素子104aに供給される電流値があまり小さくならないように補正がかかる。したがって、電荷量Qにより、移動度のばらつきを抑えることができる。

10

【0112】

なお、容量素子102の容量値は、トランジスタ101のゲートの寄生容量の容量値よりも、大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子102の電極の面積は、トランジスタ101のチャネルの面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子102の電極の面積は、トランジスタ101のゲート電極の面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。それにより、電位 $V_{sig}$ が入力されて、容量素子102とトランジスタのゲート容量とで、電圧が容量分割されたときに、容量素子102の電圧の減少を低減することが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

20

【0113】

なお、容量素子102の容量値は、容量素子103の容量値と、同じ程度の大きさであるか、それよりも、大きいことが望ましい。容量素子102の容量値は、容量素子103の容量値と、 $\pm 20\%$ 以下の違い、より好ましくは $\pm 10\%$ 以下の違いであることが好適である。または、容量素子102の電極の面積は、容量素子103の電極の面積と、同じ程度の大きさであるか、それよりも、大きいことが望ましい。これらにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

【0114】

期間T15において行われる第5の動作について説明する。期間T15では、図5(A)に示すように、スイッチ11、スイッチ12及びスイッチ13が非導通状態である。よって、期間T15では、図6(C)に示すように、容量素子102に閾値電圧 $V_{th}$ が保持され、容量素子103に電圧 $V_{sig} - V_{i1} - V$ が保持され、発光素子104aのアノードは電位 $V_{e1}$ となり、トランジスタ101のゲートの電位は電位 $V_{sig} + V_{th} - V_{i1} - V + V_{e1}$ となり、トランジスタ101のゲートソース間電圧( $V_{g s 101}$ )は電圧 $V_{sig} + V_{th} - V_{i1} - V$ となる。したがって、電位 $V_{sig}$ に応じた大きさの電流を発光素子104aに流すことができ、電位 $V_{sig}$ に応じた輝度で発光素子104aを発光させることができる。

30

【0115】

なお、電位 $V_{e1}$ は、トランジスタ101を介して、発光素子104aに電流を流す際に生じる電位である。具体的には、電位VDDと電位Vcatの間の電位になる。

40

【0116】

上記第5の動作では、トランジスタ101のゲートソース間電圧( $V_{g s 101}$ )を、電圧 $V_{sig} + V_{th} - V_{i1} - V$ とし、トランジスタ101の閾値電圧 $V_{th}$ を加味した値に設定することができる。従って、上記構成により、トランジスタ101の閾値電圧 $V_{th}$ のばらつきが、発光素子104aに供給する電流値に影響を及ぼすのを防ぐことができる。または、トランジスタ101が劣化して、閾値電圧 $V_{th}$ が変化しても、上記変化が発光素子104aに供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、質の良い表示を行うことができる。

【0117】

50

同様に、トランジスタ101のゲートソース間電圧( $V_{g s 101}$ )を、電圧 $V_{sig} + V_{th} - V_{i1} - V$ とし、 $V_{e1}$ とは無関係な値に設定することができる。上記構成により、発光素子104aの電圧電流特性のばらつきが、発光素子104aに供給する電流値に影響を及ぼすのを防ぐことができる。または、発光素子104aが劣化して、発光素子104aの電圧電流特性が変化して、 $V_{e1}$ が変化しても、上記変化が発光素子104aに供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、質の良い表示を行うことができる。

#### 【0118】

なお、第5の動作の一部の期間において、強制的にトランジスタ101がオフ状態になるようにして、発光素子104aが発光しないような状況にすることも可能である。つまり、非発光期間を設けることも可能である。例えば、スイッチ12をオンにすることにより、トランジスタ101をオフ状態にすることが可能である。

10

#### 【0119】

なお、本発明の一態様に係る半導体装置では、第2の動作において、トランジスタ101のゲートを電位 $V_{i2}$ に保つ。上記動作により、トランジスタ101がノーマリオンであっても、すなわち閾値電圧 $V_{th}$ がマイナスの値を有していても、トランジスタ101において、ソースの電位がゲートの電位 $V_{i2}$ よりも高くなるまで容量素子102に蓄積されている電荷を放出することができる。よって、本発明の一態様に係る半導体装置では、トランジスタ101がノーマリオンであっても、上記第5の動作において、トランジスタ101の閾値電圧 $V_{th}$ を加味した値になるよう、トランジスタ101のゲートソース間電圧( $V_{g s 101}$ )を設定することができる。

20

#### 【0120】

なお、期間T11乃至期間T15における、回路100の概略図を、図7(A)乃至図7(E)に、それぞれ示す。本発明の一態様に係る半導体装置は、回路100が、上記各期間において図7(A)乃至図7(E)に示す構造を取ることができれば良い。よって、本発明の一態様に係る半導体装置は、図1乃至図4に示した構成を有する回路100に限定されるものではない。本発明の一態様に係る半導体装置は、回路100において、図7(A)乃至図7(E)に示す構造を取りうるように、スイッチの配置や数、各種電位の供給を行う配線の数などを、適宜変更することが可能である。

30

#### 【0121】

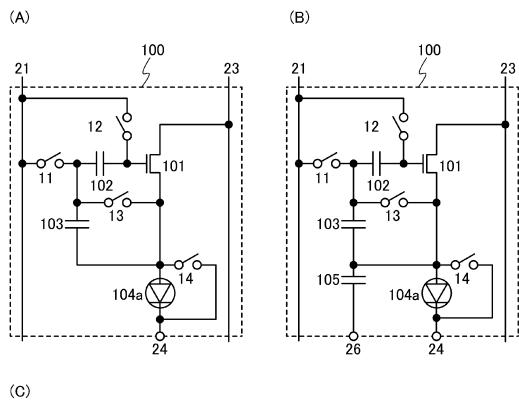

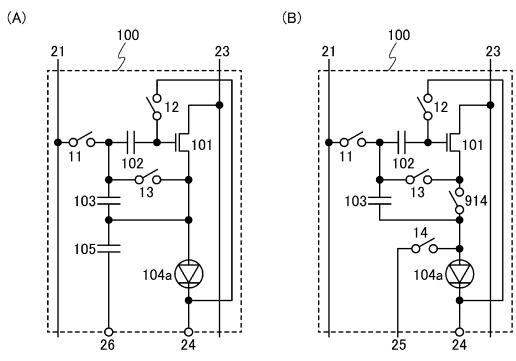

また、本発明の一態様に係る半導体装置は、図1(B)に示した回路100において、負荷104と接続された容量素子105を、さらに有していても良い。同様に、本発明の一態様に係る半導体装置は、図1(C)に示した回路100において、発光素子104aと接続された容量素子105を、さらに有していても良い。同様に、本発明の一態様に係る半導体装置は、図1(D)に示した回路100において、発光素子104bと接続された容量素子105を、さらに有していても良い。

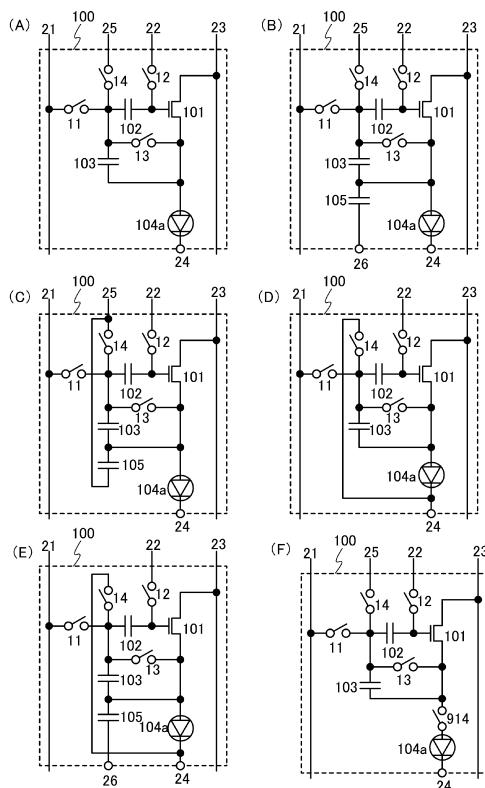

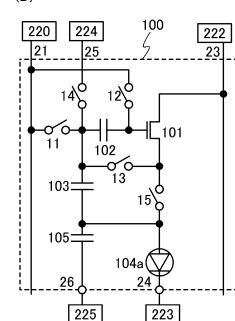

#### 【0122】

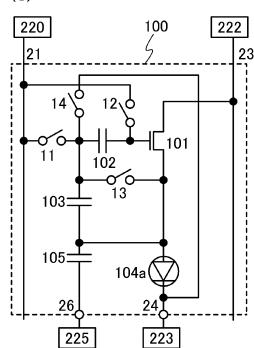

図8(A)に示す半導体装置は、図1(B)に示した回路100において、負荷104と接続された容量素子105を、さらに有している。具体的には、容量素子105の一方の電極が、容量素子103の他方の電極、及びトランジスタ101のソースまたはドレインの一方に、接続されている。容量素子105の他方の電極は、配線26に接続されている。なお、図8(A)では、回路100が負荷104を有する場合を一例として示しているが、図8(A)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられていても良い。

40

#### 【0123】

なお、配線26は、様々な配線と接続させることが可能である。例えば、配線22、配線23、配線24、または、別の回路100の配線、走査線、ゲート線、トランジスタのゲートと接続された配線などに接続させることが出来る。これにより、配線の数を減らすことが出来る。

#### 【0124】

50

図8(B)に示す半導体装置は、図8(A)に示した回路100において、配線26を配線24に接続させた場合の例を示す。なお、図8(B)では、回路100が負荷104を有する場合を一例として示しているが、図8(B)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられていても良い。このように接続することにより、配線26を減らすことが出来る。

【0125】

図8(C)に示す半導体装置は、図8(A)に示した回路100において、配線26を配線23に接続させた場合の例を示す。なお、図8(C)では、回路100が負荷104を有する場合を一例として示しているが、図8(C)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられていても良い。このように接続することにより、配線26を減らすことが出来る。

10

【0126】

図8(D)に示す半導体装置は、図8(A)に示した回路100において、配線26を配線22に接続させた場合の例を示す。なお、図8(D)では、回路100が負荷104を有する場合を一例として示しているが、図8(D)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられていても良い。このように接続することにより、配線26を減らすことが出来る。

【0127】

負荷104、発光素子104aまたは発光素子104bに、接続された容量素子105を、回路100に追加することで、本実施の形態で説明した第3の動作及び第4の動作において、トランジスタ101のソースまたはドレインの一方における電荷の変動を抑えることができるため、電圧 $V_s$ を小さくすることができる。よって、ゲートソース間電圧 $V_{gs}$ を理想的な値、すなわち電圧 $V_{sig} + V_{th} - V_{i1}$ に近づけることができ、負荷104、発光素子104aまたは発光素子104bに供給する電流を、電圧 $V_{sig}$ を正確に反映した値により近づけることができる。

20

【0128】

または、容量素子105の容量値を適宜調整することにより、期間 $T_{14}$ における電荷量 $Q$ による電位の変化量を調整することができる。これにより、移動度のばらつきの低減を、より適切に行うことが出来る。

【0129】

30

なお、容量素子105の電極の面積は、負荷104(発光素子104a)の電極の面積よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。または、容量素子105の容量値は、負荷104(発光素子104a)の容量値よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。それらにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

【0130】

なお、容量素子105の電極の面積と、負荷104(発光素子104a)の電極の面積の合計は、容量素子103の電極の面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子105の容量値と、負荷104(発光素子104a)の容量値の合計は、容量素子103の容量値よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。それらにより、容量素子103と、容量素子105及び負荷104(発光素子104a)とで、電圧が容量分割されたときに、容量素子103により多くの電圧が加わるようにすることができる。ただし、本発明の実施形態の一態様は、これに限定されない。

40

【0131】

なお、容量素子105の電極の面積は、容量素子102または容量素子103の電極の面積よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。または、容量素子105の容量値は、容量素子102または容量素子103の容量値よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/

50

3倍以下が好適である。それにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

#### 【0132】

また、本発明の一態様に係る半導体装置は、図8(A)乃至図8(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

#### 【0133】

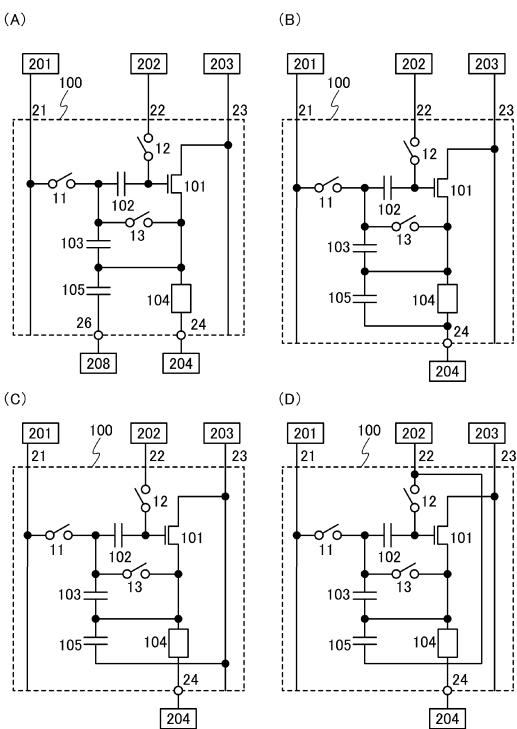

図9(A)乃至図9(D)に示す半導体装置は、図8(A)乃至図8(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路201と、配線22に一定電圧や信号を供給する機能を有する回路202と、配線23に一定電圧や信号を供給する機能を有する回路203と、配線24に一定電圧や信号を供給する機能を有する回路204とを、それぞれ有する。さらに、図9(A)に示す回路100は、配線26に一定電圧や信号を供給する機能を有する回路208を有する。回路208の例としては、電源回路などがある。したがって、配線26は、所定の電位を、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線26は、容量用配線としての機能を有している。なお、配線26の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

#### 【0134】

また、図1(B)乃至図1(D)、図8(B)乃至図8(D)のいずれかの回路100を、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。同様に、画素が有する容量素子105の容量値も、対応する色相によって、異なっていても良い。

#### 【0135】

図10(A)に、図1(B)に示した回路100を、表示装置の画素として用いた場合を一例として示している。図10(A)では、回路100(R)が赤(R)に対応した画素に相当し、回路100(G)が緑(G)に対応した画素に相当し、回路100(B)が青(B)に対応した画素に相当する。本発明の一態様では、回路100(R)が有するトランジスタ101(R)と、回路100(G)が有するトランジスタ101(G)と、回路100(B)が有するトランジスタ101(B)との少なくとも一つにおいて、そのチャネル幅とチャネル長の比が他と異なっていても良い。上記構成により、回路100(R)が有する負荷104(R)、回路100(G)が有する負荷104(G)、回路100(B)が有する負荷104(B)のそれぞれに供給される電流を異なる値に設定することができる。一例としては、第2の色に対応するトランジスタ101のチャネル幅とチャネル長の比は、第1の色に対応するトランジスタ101よりも、好ましくは1.2倍以上、より好ましくは、1.5倍以上であることが好適である。そして、第3の色に対応するトランジスタ101のチャネル幅とチャネル長の比は、第1の色に対応するトランジスタ101よりも、好ましくは1.5倍以上、より好ましくは、2倍以上であることが好適である。ただし、本発明の実施形態の一態様は、これに限定されない。

#### 【0136】

また、図10(B)に、図8(A)に示した回路100を、表示装置の画素として用いた場合を一例として示している。図10(B)の場合も図10(A)と同様に、回路100(R)が有するトランジスタ101(R)と、回路100(G)が有するトランジスタ101(G)と、回路100(B)が有するトランジスタ101(B)との少なくとも一つが、そのチャネル幅とチャネル長の比が他と異なっていても良い。上記構成により、回路100(R)が有する負荷104(R)、回路100(G)が有する負荷104(G)、回路100(B)が有する負荷104(B)のそれぞれに供給される電流を異なる値に設定することができる。

#### 【0137】

10

20

30

40

50

また、図10(B)の場合、回路100(R)が有する容量素子105(R)と、回路100(G)が有する容量素子105(G)と、回路100(B)が有する容量素子105(B)との少なくとも一つにおいて、その容量値が他と異なっていても良い。一例としては、第2の色に対応する容量素子105の容量値は、第1の色に対応する容量素子105よりも、好ましくは1.2倍以上、より好ましくは、1.5倍以上であることが好適である。そして、第3の色に対応する容量素子105の容量値は、第1の色に対応する容量素子105よりも、好ましくは1.5倍以上、より好ましくは、2倍以上であることが好適である。ただし、本発明の実施形態の一態様は、これに限定されない。

【0138】

なお、図10(A)及び図10(B)では、回路100(R)が負荷104(R)を有し、回路100(G)が負荷104(G)を有し、回路100(B)が負荷104(B)を有する場合を一例として示しているが、図10(A)または図10(B)において、負荷104(R)、負荷104(G)、または負荷104(B)の代わりに、各色相に対応した発光素子104aまたは発光素子104bが用いられていても良い。

10

【0139】

また、図10(B)では、図8(A)に示した回路100を、表示装置の画素として用いた場合を一例として示しているが、図8(B)乃至図8(D)に示した回路100を、表示装置の画素として用いても良い。

【0140】

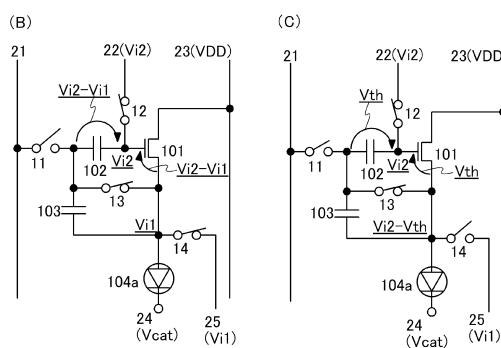

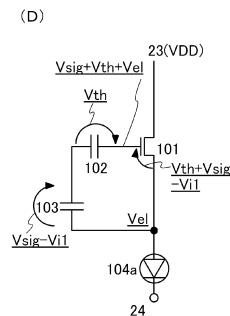

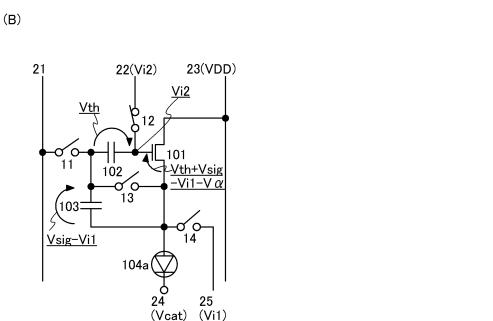

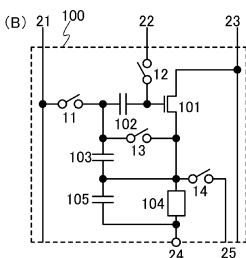

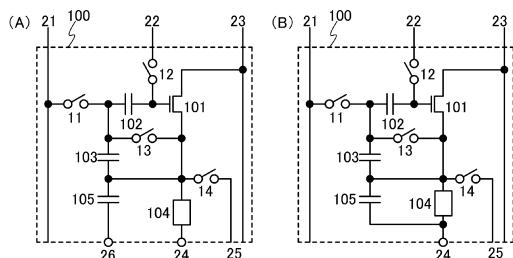

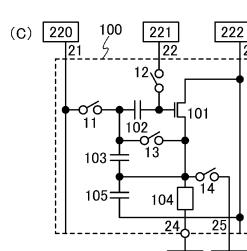

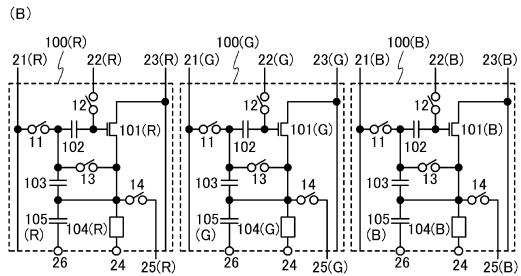

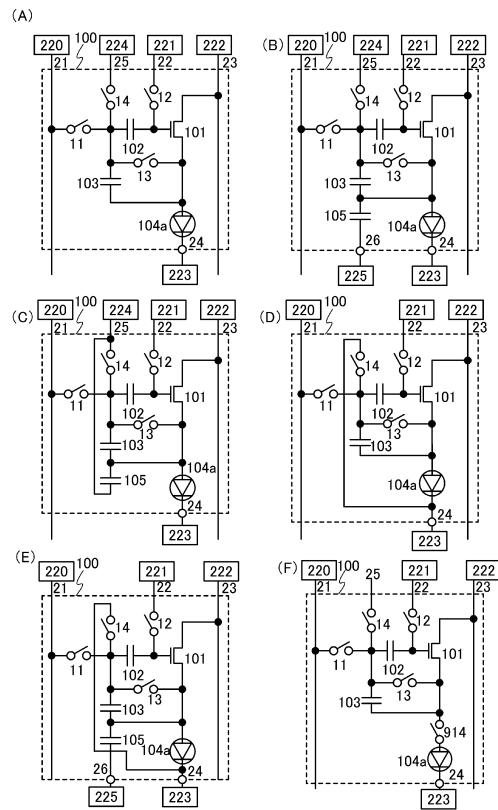

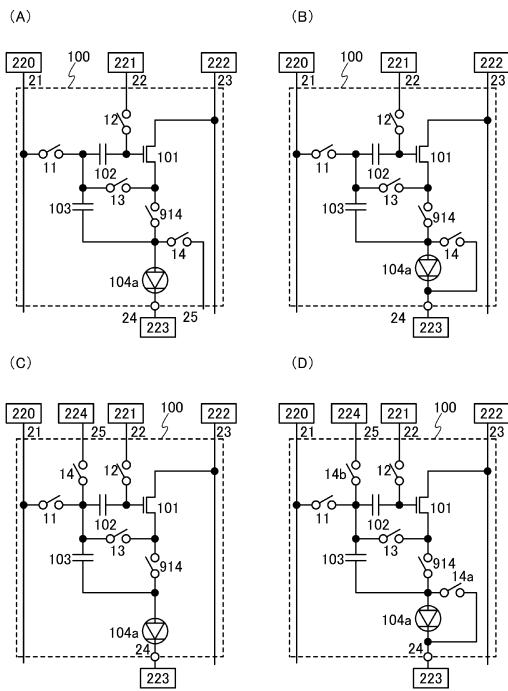

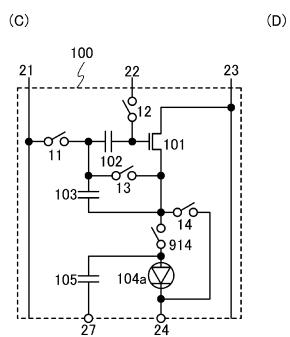

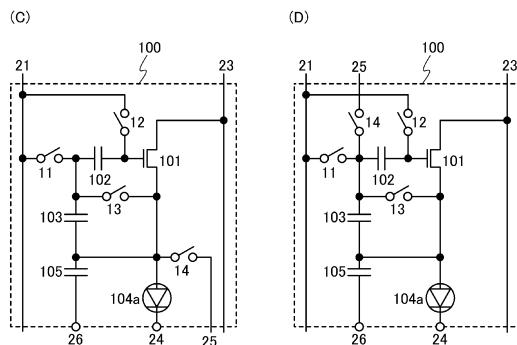

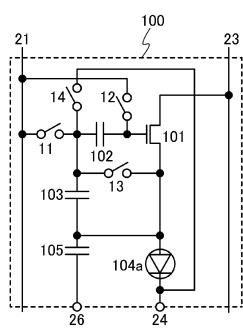

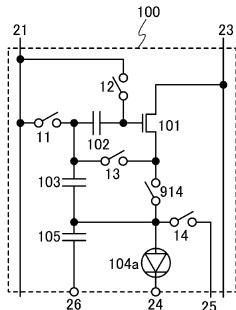

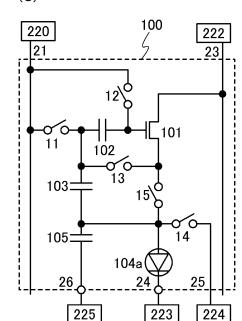

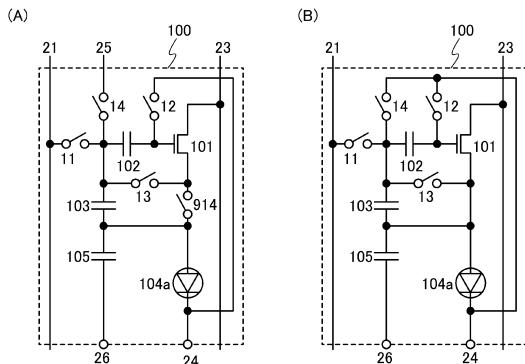

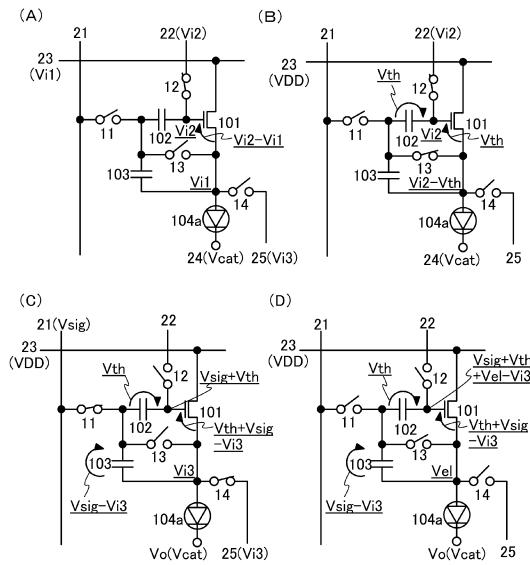

次いで、図11(A)に示す回路100は、本発明の一態様に係る半導体装置である。回路100は、スイッチ11、スイッチ12、スイッチ13、スイッチ14、トランジスタ101、容量素子102、容量素子103を有する。なお、図11(A)では、トランジスタ101がnチャネル型である場合を一例として示している。図11(A)は、図1(A)にスイッチ14を追加した構成に相当する。したがって、図1(A)などで述べた内容は、図11(A)などにも適用することが可能である。

20

【0141】

具体的に、図11(A)では、スイッチ11は、配線21と、容量素子102の一方の電極または容量素子103の一方の電極との間の導通状態を制御する機能を有する。スイッチ12は、配線22と、容量素子102の他方の電極、又は、トランジスタ101のゲートとの間の導通状態を制御する機能を有する。スイッチ13が、トランジスタ101のソースまたはドレインの一方、又は、容量素子103の他方の電極と、容量素子102の一方の電極、又は、容量素子103の一方の電極との間の導通状態を制御する機能を有する。スイッチ14が、トランジスタ101のソースまたはドレインの一方、又は、容量素子103の他方の電極と、配線25との間の導通状態を制御する機能を有する。トランジスタ101のソースまたはドレインの他方は、配線23に接続されている。トランジスタ101のソースまたはドレインの一方及び容量素子103の他方の電極は、配線24に接続されている。

30

【0142】

なお、図11(A)で示した回路100は、図11(B)に示すように負荷104を有していても良い。図11(B)に示す回路100では、負荷104が、トランジスタ101のソースまたはドレインの一方、又は、容量素子103の他方の電極と、配線24との間に接続されている。

40

【0143】

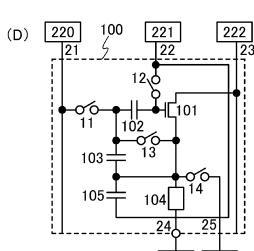

図11(C)に、負荷104として、発光素子104aを用いた場合の、回路100の構成を示す。図11(C)では、発光素子104aのアノードが、トランジスタ101のソースまたはドレインの一方及び容量素子103の他方の電極に接続されており、発光素子104aのカソードが、配線24に接続されている場合を一例として示している。

【0144】

また、図11(D)に、負荷104として、発光素子104bを用いた場合の、回路100の構成を示す。図11(D)では、発光素子104bのカソードが、トランジスタ10

50

1のソースまたはドレインの一方、又は、容量素子103の他方の電極に接続されており、発光素子104bのアノードが、配線24に接続されている場合を一例として示している。なお、図11(D)では、トランジスタ101がpチャネル型である場合を一例として示している。

【0145】

また、本発明の一態様に係る半導体装置は、図11(A)乃至図11(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

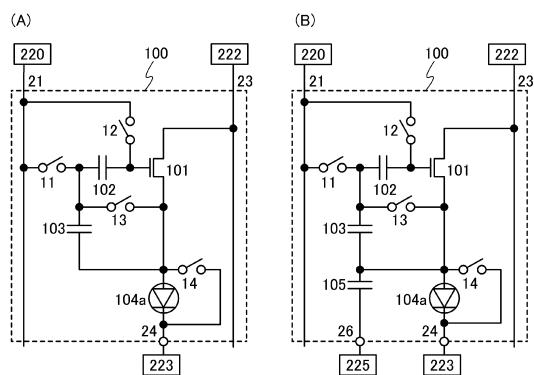

【0146】

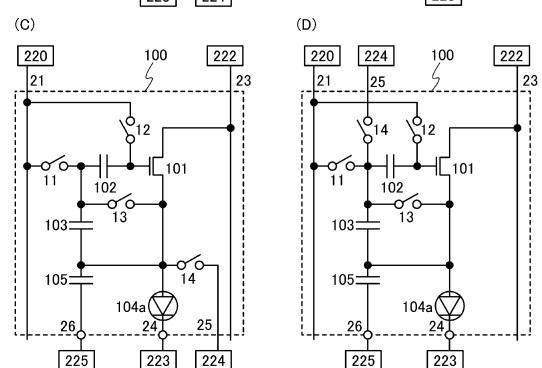

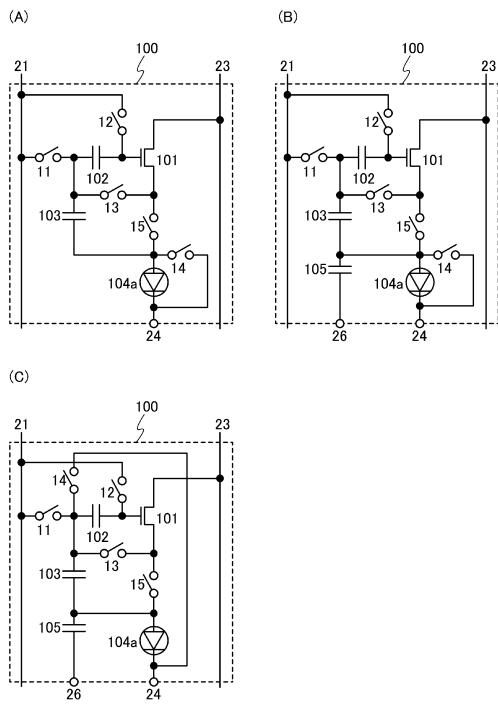

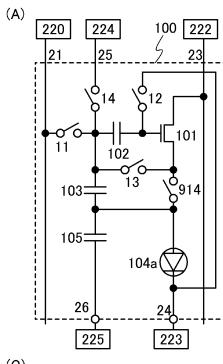

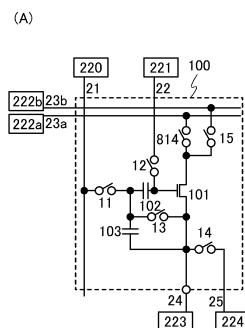

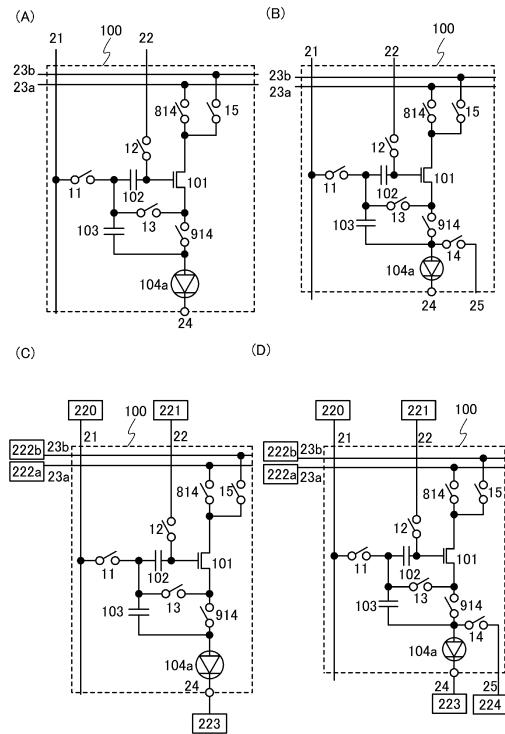

図12(A)乃至図12(D)に示す半導体装置は、図11(A)乃至図11(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路220と、配線22に一定電圧や信号を供給する機能を有する回路221と、配線23に一定電圧や信号を供給する機能を有する回路222と、配線24に一定電圧や信号を供給する機能を有する回路223と、配線25に一定電圧や信号を供給する機能を有する回路224とを、それぞれ有する。

【0147】

具体的に、回路220は、配線21に、電位Vsigを供給する機能を有する。回路220の例としては、ソースドライバ(信号線駆動回路)などがある。したがって、配線21は、電位Vsigを、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線21は、映像信号線としての機能を有している。

【0148】

また、回路221は、配線22に、電位V12を供給する機能を有する。回路221の例としては、電源回路などがある。したがって、配線22は、電位V12を、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線22は、初期化用配線としての機能を有している。なお、配線22の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

【0149】

また、回路222は、配線23に、電源電位(高電源電位または低電源電位)、例えば、電位VDD、または、電位VSSを供給する機能を有する。回路222の例としては、電源回路などがある。したがって、配線23は、電源電位を伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線23は、トランジスタ101に電流を供給することが出来る機能を有している。または、配線23は、負荷104に電流を供給することが出来る機能を有している。または、配線23は、電源線としての機能を有している。または、配線23は、電流供給線としての機能を有している。なお、配線23の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。例えば、配線23の電位は、負荷104に、順バイアス電圧だけでなく、逆バイアス電圧を加えるような電位であってもよい。

【0150】

また、回路223は、配線24に、電源電位(低電源電位または高電源電位)、例えば、電位Vcatを供給する機能を有する。回路223の例としては、電源回路などがある。したがって、配線24は、電源電位を伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線24は、負荷104に電流を供給することが出来る機能を有している。または、配線24は、トランジスタ101に電流を供給することが出来る機能を有している。または、配線24は、共通線としての機能を有している。または、配線24は、陰極配線としての機能を有している。または、配線24は、陽極配線としての機能を有している。なお、配線24の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。例えば、配線24の電位は、負荷104に、順バイアス電圧だけでなく、逆バイアス電

10

20

30

40

50

圧を加えるような電位であってもよい。

【0151】

また、回路224は、配線25に、電位Vi1を供給する機能を有する。回路224の例としては、電源回路などがある。したがって、配線25は、電位Vi1を、伝えることが出来る機能、または、供給することが出来る機能を有している。または、配線25は、初期化用配線としての機能を有している。なお、配線25の電位は、一定の電位であることが望ましいが、本発明の実施形態の一態様は、これに限定されず、パルス信号のように変動してもよい。

【0152】

なお、図12(A)乃至図12(D)では、半導体装置が、回路100に加えて、回路220、回路221、回路222、回路223、及び回路224を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路220、回路221、回路222、回路223、及び回路224を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

【0153】

なお、図11及び図12に示した回路100は、一例として、スイッチ11、スイッチ12、スイッチ13、スイッチ14にトランジスタを用いることができる。

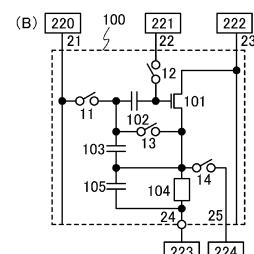

【0154】

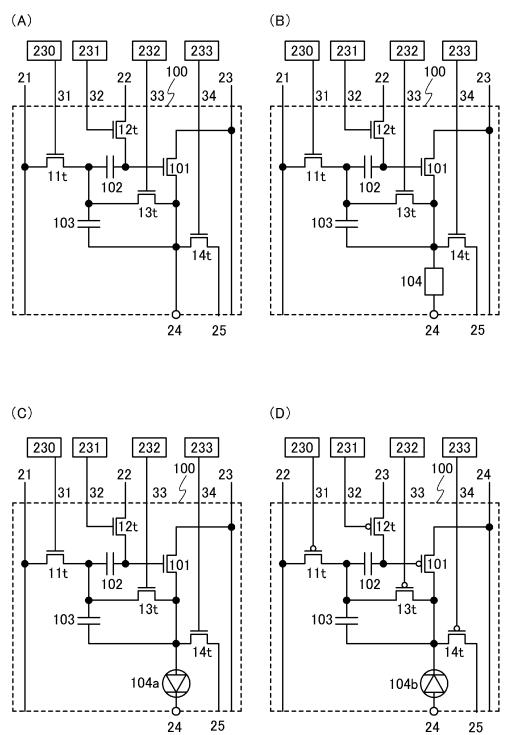

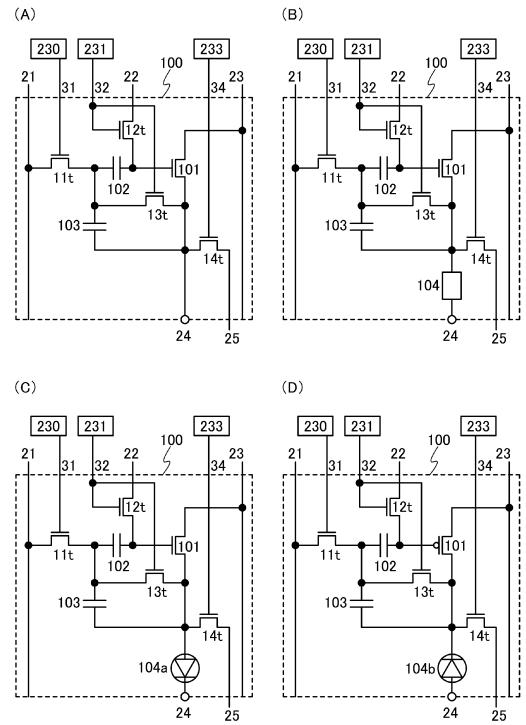

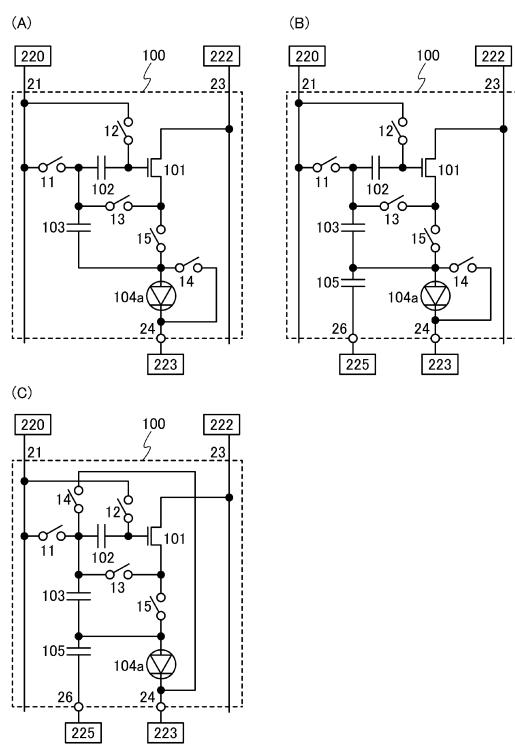

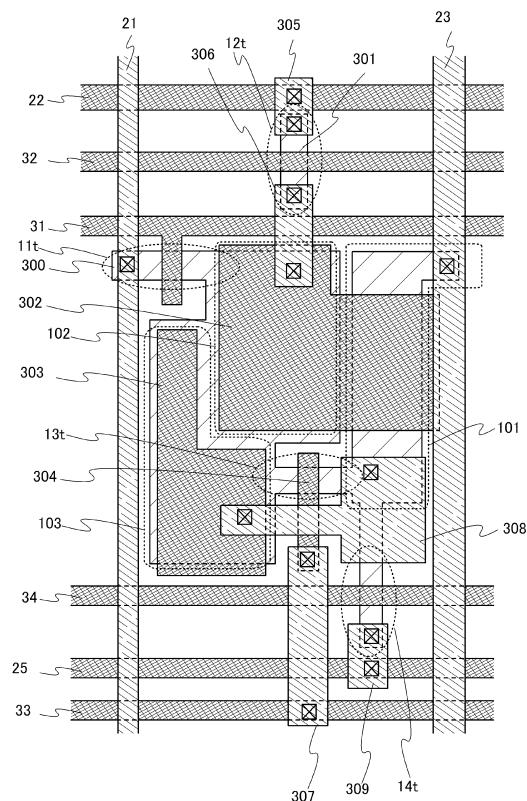

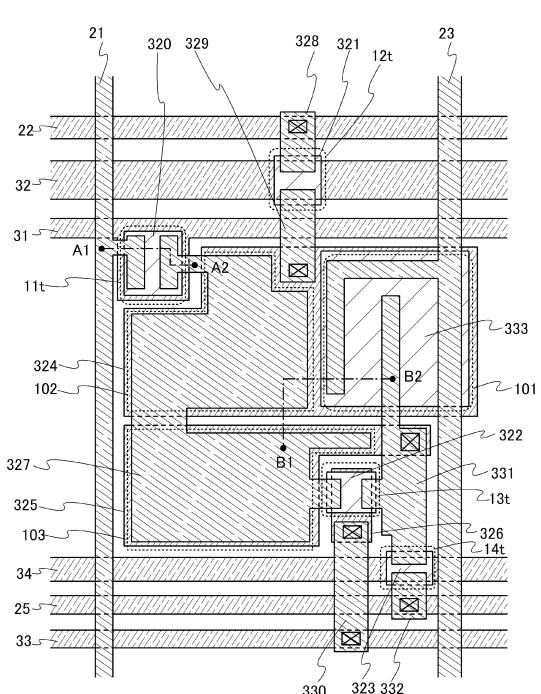

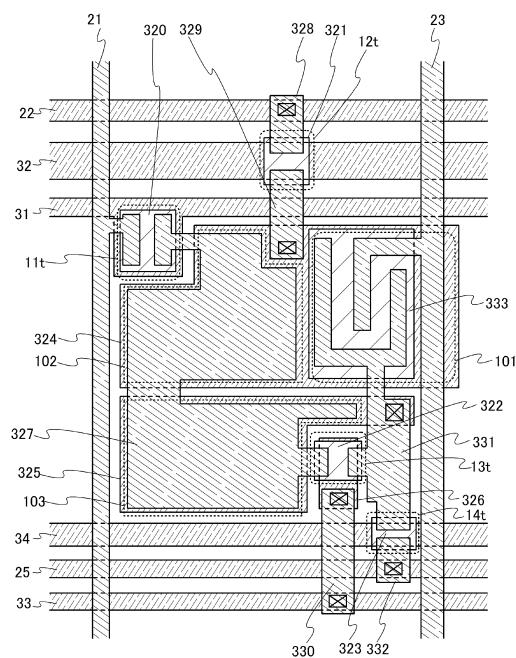

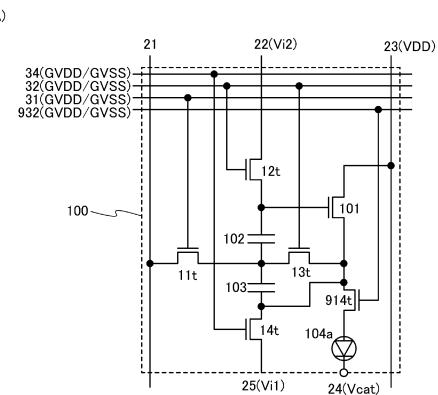

図11(A)乃至図11(D)に示した回路100において、スイッチ11としてトランジスタ11t、スイッチ12としてトランジスタ12t、スイッチ13としてトランジスタ13t、及びスイッチ14としてトランジスタ14tを用いた場合の回路100の構成を、図13(A)乃至図13(D)に示す。なお、図13(A)乃至図13(D)では、トランジスタ11t、トランジスタ12t、トランジスタ13t、及びトランジスタ14tが全てnチャネル型である場合を一例として示している。トランジスタ11t、トランジスタ12t、トランジスタ13t、及びトランジスタ14tを全て同じ極性のトランジスタとすることで、これらのトランジスタを少ない工程数で製造できる。ただし、本発明の実施形態の一態様は、これに限定されず、異なる極性のトランジスタを用いることも可能である。

【0155】

なお、図13(A)乃至図13(D)において、トランジスタ11tは、ゲートが配線31に接続されている。配線31に供給される電位に従って、トランジスタ11tは導通状態または非導通状態となる。トランジスタ12tは、ゲートが配線32に接続されている。配線32に供給される電位に従って、トランジスタ12tは導通状態または非導通状態となる。トランジスタ13tは、ゲートが配線33に接続されている。配線33に供給される電位に従って、トランジスタ13tは導通状態または非導通状態となる。トランジスタ14tは、ゲートが配線34に接続されている。配線34に供給される電位に従って、トランジスタ14tは導通状態または非導通状態となる。したがって、配線31乃至配線34の電位は、パルス状であり、一定ではないことが望ましいが、本発明の実施形態の一態様は、これに限定されない。または、配線31乃至配線34は、ゲート信号線、選択信号線、または、スキャン線としての機能を有している。

【0156】

なお、配線31乃至配線34において、その中の少なくとも2本の配線は、互いに接続させることが可能である。または、配線31乃至配線34の少なくとも1本は、別の回路100の配線31乃至配線34の少なくとも1本と接続させることが可能である。

【0157】

また、本発明の一態様に係る半導体装置は、図13(A)乃至図13(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0158】

図14(A)乃至図14(D)に示す半導体装置は、図13(A)乃至図13(D)に示

10

20

30

40

50

す回路 100 に加えて、配線 31 に一定電圧や信号を供給する機能を有する回路 230 と、配線 32 に一定電圧や信号を供給する機能を有する回路 231 と、配線 33 に一定電圧や信号を供給する機能を有する回路 232 と、配線 34 に一定電圧や信号を供給する機能を有する回路 233 とを、それぞれ有する。回路 230、回路 231、回路 232、回路 233 の例としては、ゲートドライバ（走査線駆動回路）などがある。

#### 【0159】

なお、図 14 (A) 乃至図 14 (D) では、半導体装置が、回路 100 に加えて、回路 230、回路 231、回路 232、及び回路 233 を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路 230、回路 231、回路 232、及び回路 233 を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

10

#### 【0160】

なお、回路 220、回路 221、回路 222、回路 223、回路 224、回路 230、回路 231、回路 232、回路 233 は、一つの同じ回路であってもよいし、別々の回路であってもよい。

#### 【0161】

また、図 13 (C) に示す回路 100 において、トランジスタ 101、及びトランジスタ 14t が n チャネル型、トランジスタ 11t、トランジスタ 12t、及びトランジスタ 13t が p チャネル型である場合の回路 100 の構成を図 38 (A) に示す。また、図 13 (D) に示す回路 100 において、トランジスタ 101、及びトランジスタ 14t が p チャネル型、トランジスタ 11t、トランジスタ 12t、及びトランジスタ 13t が n チャネル型である場合の回路 100 の構成を図 38 (B) に示す。

20

#### 【0162】

また、本発明の一態様に係る半導体装置は、図 38 (A) 及び図 38 (B) に示した回路 100 に加えて、回路 100 に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

#### 【0163】

図 38 (C) 及び図 38 (D) に示す半導体装置は、図 38 (A) 及び図 38 (B) に示す回路 100 に加えて、配線 31 に一定電圧や信号を供給する機能を有する回路 230 と、配線 32 に一定電圧や信号を供給する機能を有する回路 231 と、配線 33 に一定電圧や信号を供給する機能を有する回路 232 と、配線 34 に一定電圧や信号を供給する機能を有する回路 233 とを、それぞれ有する。

30

#### 【0164】

なお、図 38 (C) 及び図 38 (D) では、半導体装置が、回路 100 に加えて、回路 230、回路 231、回路 232、及び回路 233 を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路 230、回路 231、回路 232、及び回路 233 を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

#### 【0165】

なお、トランジスタ 101 は、電流を流すときには、飽和領域で動作する場合が多い。よって、図 13、図 14、及び図 38 において、トランジスタ 101 のチャネル長またはゲート長を、トランジスタ 11t、トランジスタ 12t、トランジスタ 13t、及び / または、トランジスタ 14t よりも長くすることが望ましい。好ましくは、5 倍以上、より好ましくは 10 倍以上であることが望ましい。一例としては、トランジスタ 101 のチャネル長またはゲート長は、10  $\mu\text{m}$  以上、より好ましくは、20  $\mu\text{m}$  以上である。チャネル長またはゲート長を長くすることにより、飽和領域での特性がフラットになり、キンク効果を低減することができる。或いは、トランジスタ 101 のチャネル幅またはゲート幅を、トランジスタ 11t、トランジスタ 12t、トランジスタ 13t、及び / または、トランジスタ 14t よりも長くすることにより、トランジスタ 101 は、飽和領域においても、多くの電流を流すことができる。好ましくは、5 倍以上、より好ましくは 10 倍以上で

40

50

あることが望ましい。トランジスタ 101 のチャネル幅またはゲート幅は、20  $\mu$ m 以上、より好ましくは、30  $\mu$ m 以上である。ただし、本発明の実施形態の一態様は、これに限定されない。

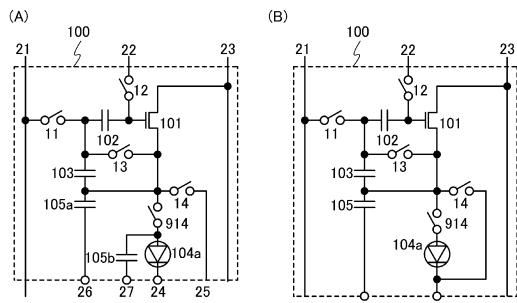

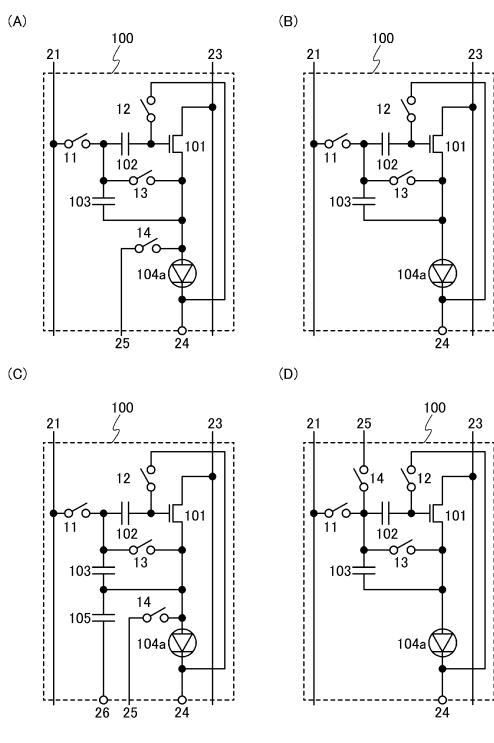

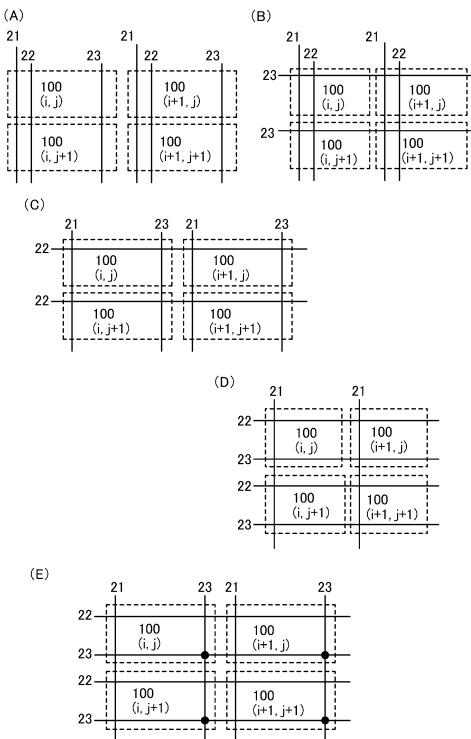

【0166】

なお、図 13 (A) 乃至図 13 (D) と、図 38 (A) 及び図 38 (B) に示す半導体装置において、トランジスタ 12t 及びトランジスタ 13t は、共にそのゲートが一の配線に接続されていても良い。図 15 (A) 乃至図 15 (D) に、図 13 (A) 乃至図 13 (D) に示す半導体装置において、トランジスタ 12t 及びトランジスタ 13t のゲートが、配線 32 に接続されている場合を一例として示す。配線 32 に供給される電位に従って、トランジスタ 12t 及びトランジスタ 13t は導通状態または非導通状態となる。

10

【0167】

また、本発明の一態様に係る半導体装置は、図 15 (A) 乃至図 15 (D) に示した回路 100 に加えて、回路 100 に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0168】

図 16 (A) 乃至図 16 (D) に示す半導体装置は、図 15 (A) 乃至図 15 (D) に示す回路 100 に加えて、配線 31 に一定電圧や信号を供給する機能を有する回路 230 と、配線 32 に一定電圧や信号を供給する機能を有する回路 231 と、配線 34 に一定電圧や信号を供給する機能を有する回路 233 とを、それぞれ有する。

20

【0169】

なお、図 16 (A) 乃至図 16 (D) では、半導体装置が、回路 100 に加えて、回路 230、回路 231、及び回路 233 を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路 230、回路 231、及び回路 233 を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

【0170】

また、図 16 (C) に示す回路 100 において、トランジスタ 101、トランジスタ 11t、及びトランジスタ 14t が n チャネル型、トランジスタ 12t、及びトランジスタ 13t が p チャネル型である場合の回路 100 の構成を図 42 (A) に示す。また、図 16 (D) に示す回路 100 において、トランジスタ 101、トランジスタ 11t、及びトランジスタ 14t が p チャネル型、トランジスタ 12t、及びトランジスタ 13t が n チャネル型である場合の回路 100 の構成を図 42 (B) に示す。

30

【0171】

また、本発明の一態様に係る半導体装置は、図 42 (A) 及び図 42 (B) に示した回路 100 に加えて、回路 100 に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0172】

図 42 (C) 及び図 42 (D) に示す半導体装置は、図 42 (A) 及び図 42 (B) に示す回路 100 に加えて、配線 31 に一定電圧や信号を供給する機能を有する回路 230 と、配線 32 に一定電圧や信号を供給する機能を有する回路 231 と、配線 34 に一定電圧や信号を供給する機能を有する回路 233 とを、それぞれ有する。回路 230、回路 231、回路 233 の例としては、ゲートドライバ (走査線駆動回路) などがある。

40

【0173】

なお、図 42 (C) 及び図 42 (D) では、半導体装置が、回路 100 に加えて、回路 230、回路 231、及び回路 233 を有する場合を一例として示しているが、本発明の一態様に係る半導体装置は、必ずしも回路 230、回路 231、及び回路 233 を全て有する必要はなく、そのいずれか一つまたは複数だけを有していても良い。

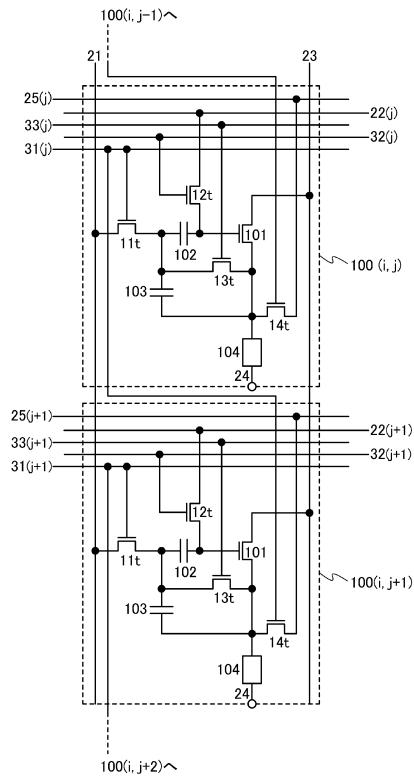

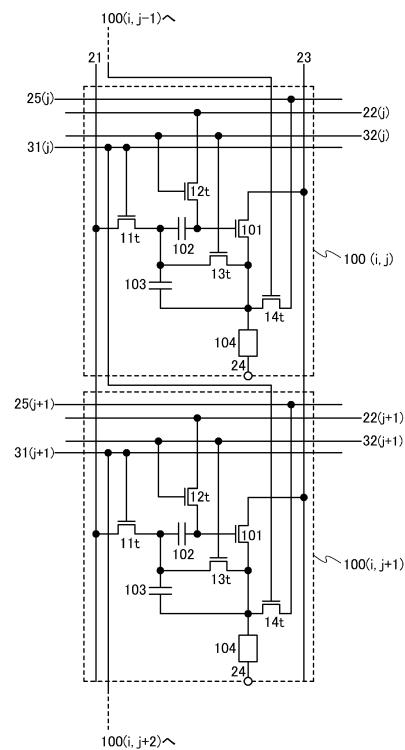

【0174】

また、図 13 (A) 乃至図 13 (D) に示す半導体装置において、隣接する回路 100 間で、あるトランジスタのゲートと別のトランジスタのゲートが接続されていてもよい。例えば、トランジスタ 11t とトランジスタ 14t のゲートが接続されていても良い。図 3

50

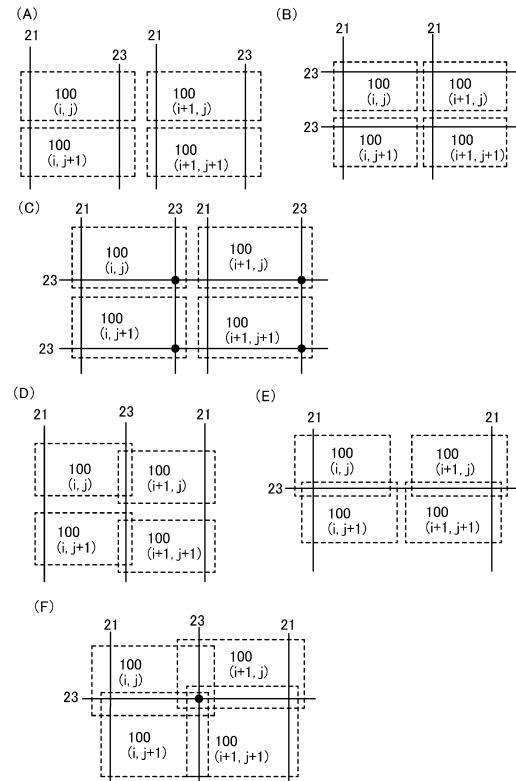

9に、 $i$ 列 $j$ 行目の回路100 ( $i, j$ ) が有するトランジスタ11tのゲートと、 $i$ 列 $j+1$ 行目の回路100 ( $i, j+1$ ) が有するトランジスタ14tのゲートとが、 $j$ 行目の配線31 ( $j$ ) に接続されている場合を一例として示している。

【0175】

また、図15 (A) 乃至図15 (D) に示す半導体装置において、隣接する回路100間で、あるトランジスタのゲートと別のトランジスタのゲートが接続されていてもよい。例えば、トランジスタ11tとトランジスタ14tのゲートが接続されていても良い。図40に、 $i$ 列 $j$ 行目の回路100 ( $i, j$ ) が有するトランジスタ11tのゲートと、 $i$ 列 $j+1$ 行目の回路100 ( $i, j+1$ ) が有するトランジスタ14tのゲートとが、 $j$ 行目の配線31 ( $j$ ) に接続されている場合を一例として示している。

10

【0176】

なお、図39及び図40では、 $j$ 行目の回路100が有するトランジスタ11tのゲートと、 $j+1$ 行目の回路100が有するトランジスタ14tのゲートとが、 $j$ 行目の配線31 ( $j$ ) に接続されている場合を一例として示している。しかし、本発明の一態様はこの構成に限定されず、例えば、図14 (A) 乃至図14 (D) 、図38 (C) 及び図38 (D) に示す半導体装置において、回路230が、 $j$ 行目の配線31 ( $j$ ) と、 $j+1$ 行目の配線34 ( $j+1$ ) とに、電位の供給を行うようにしても良い。

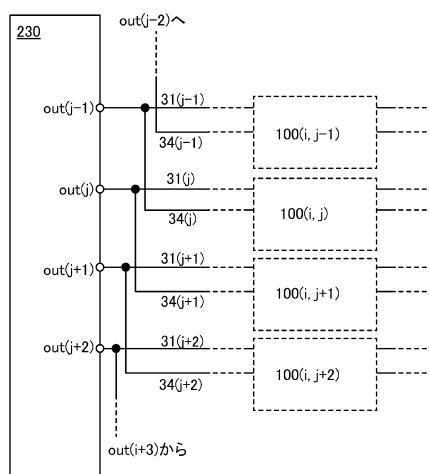

【0177】

図41に、回路230から、配線31及び配線34に電位の供給を行っている様子を示す。具体的に、図41では、回路230が有する $j$ 番目の出力端子out ( $j$ ) から出力される電位が、 $j$ 行目の配線31 ( $j$ ) と、 $j+1$ 行目の配線34 ( $j+1$ ) とに与えられる。つまり、これは、例えば、走査線駆動回路と、画素領域との間で、異なる行の配線を接続させることに相当する。

20

【0178】

次いで図11 (C) に示す回路100を例に挙げて、本発明の半導体装置の一態様の動作について説明する。

【0179】

図11 (C) に示す回路100の動作は、主に第1の動作、第2の動作、第3の動作、第4の動作に分けることができる。ただし、本発明の実施形態の一態様は、これに限定されず、新たな動作の追加、或いは、一部の動作の削除も可能である。

30

【0180】

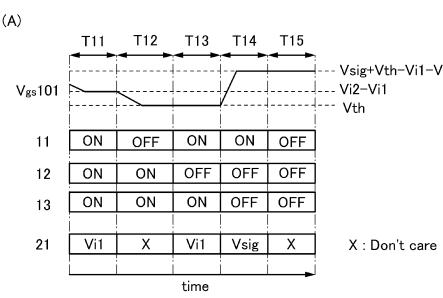

なお、図11 (C) では、図1 (C) の回路に対して、スイッチ14が追加されているため、図6 (A) に示す第3の動作 (期間T13) を削除することが可能である。

【0181】

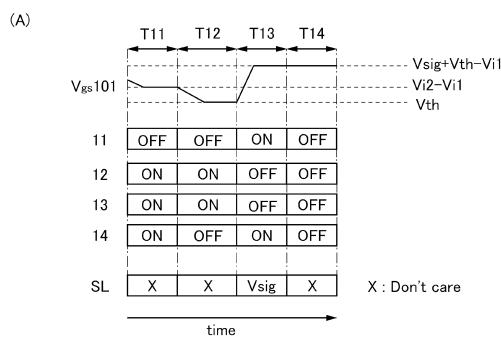

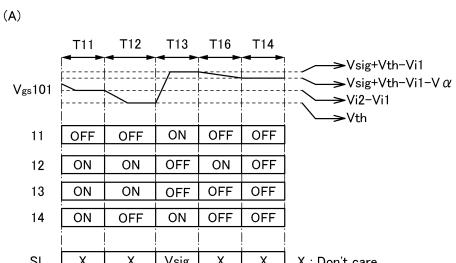

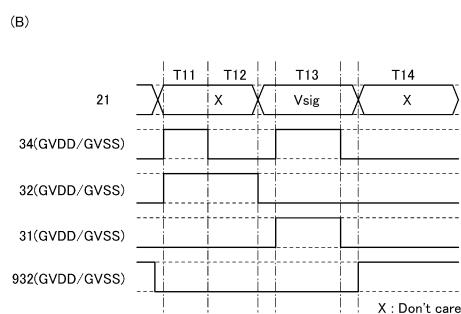

図11 (C) に示す回路100における、スイッチ11、スイッチ12、スイッチ13、及びスイッチ14の動作と、配線21の電位と、トランジスタ101のゲートソース間電圧 ( $V_{gs101}$ ) とを示すタイミングチャートの一例を、図17 (A) に図示する。

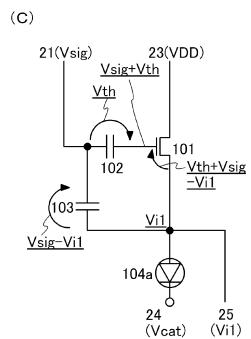

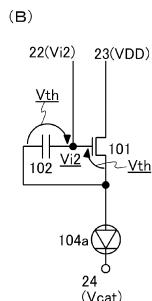

【0182】

まず、期間T11において行われる第1の動作について説明する。期間T11では、図17 (A) に示すように、スイッチ11が非導通状態、スイッチ12、スイッチ13、及びスイッチ14が導通状態である。よって、期間T11では、図17 (B) に示すように、容量素子102に電圧 $V_{i2} - V_{i1}$ が供給され、発光素子104aのアノードは電位 $V_{i1}$ となり、トランジスタ101のゲートソース間電圧 ( $V_{gs101}$ ) は、電圧 $V_{i2} - V_{i1}$ となる。つまり、トランジスタ101、及び、容量素子102を、初期化していることとなる。

40

【0183】

なお、スイッチ11は、配線21の電位が悪影響を及ぼさない場合には、導通状態であってもよい。その場合、スイッチ14は、非導通状態でもよい。

【0184】

なお、スイッチ13は、非導通状態であってもよい。

50

## 【0185】

期間T12において行われる第2の動作について説明する。期間T12では、図17(A)に示すように、スイッチ11及びスイッチ14が非導通状態、スイッチ12及びスイッチ13が導通状態である。スイッチ11及びスイッチ14が非導通状態となることで、容量素子102に蓄積されている電荷がトランジスタ101を介して放出され、トランジスタ101のソースの電位が上昇する。そして、トランジスタ101がオフ状態となると、容量素子102からの電荷の放出が止まる。最終的には、トランジスタ101の閾値電圧Vthが容量素子102に保持される。よって、期間T12では、図17(C)に示すように、容量素子102に閾値電圧Vthが保持され、発光素子104aのアノードは電位Vi2-Vthとなり、トランジスタ101のゲートソース間電圧(Vgs101)は、閾値電圧Vthとなる。つまり、トランジスタ101のしきい値電圧Vthを取得することができる。10

## 【0186】

なお、Vgs101が、トランジスタ101のしきい値電圧Vthに等しくなるまでには、非常に長い時間が必要となる場合がある。したがって、Vgs101は、しきい値電圧Vthまで完全に低下させずに、動作させる場合も多い。つまり、Vgs101は、しきい値電圧Vthよりも、わずかに大きい値となった状態で、期間T12が終了する場合も多い。つまり、期間T12が終了した時点では、Vgs101は、しきい値電圧に応じた大きさの電圧になっている、ということも出来る。

## 【0187】

なお、第2の動作において、トランジスタ101のしきい値電圧Vthが正か負かということに関係なく、動作させることができる。これは、トランジスタ101がオフ状態となるまで、トランジスタ101のソース電位が上昇できるからである。つまり、トランジスタ101のゲート電位よりも、トランジスタ101のソース電位の方が高くなつた状態で、ようやくトランジスタ101がオフし、Vgs101がVthとなる、ということが可能であるからである。したがって、トランジスタ101がエンハンスメント型(ノーマリオフ型)であっても、デブリーション型(ノーマリオン型)であっても、正常に動作させることができる。20

## 【0188】

なお、発光素子104aのアノードの電位が高くなつたときに、発光素子104aに電流が流れないようにすることが望ましい。そのためには、発光素子104aに電流が流れないように、電位Vi2を低い値とすることが好適である。ただし、本発明の実施形態の一様様は、これに限定されない。なお、発光素子104aと直列にスイッチを設けて、それをオフ状態にすることにより、発光素子104aに電流が流れないようにすることが可能であれば、電位Vi2は、高い値でもよい。30

## 【0189】

期間T13において行われる第3の動作について説明する。期間T13では、図17(A)に示すように、スイッチ11及びスイッチ14が導通状態、スイッチ12及びスイッチ13が非導通状態である。また、配線21には電位Vsigが供給される。よって、期間T13では、図18(A)に示すように、容量素子102に閾値電圧Vth(またはVthに応じた大きさの電圧である)が保持され、容量素子103に電圧Vsig-Vi1が保持され、発光素子104aのアノードは電位Vi1となり、トランジスタ101のゲートの電位は電位Vsig+Vthとなり、トランジスタ101のゲートソース間電圧(Vgs101)は電圧Vsig+Vth-Vi1となる。したがって、電位Vsigを容量素子103に入力することが出来る。または、容量素子102の電圧と容量素子103の電圧との和が、トランジスタ101のゲートソース間電圧となるようにすることができる。40

## 【0190】

なお、このとき、スイッチ14を非導通状態とすることも可能である。

## 【0191】

50

期間 T 1 4 において行われる第 4 の動作について説明する。期間 T 1 4 では、図 17 ( A ) に示すように、スイッチ 1 1 、スイッチ 1 2 、スイッチ 1 3 、及びスイッチ 1 4 が非導通状態である。よって、期間 T 1 4 では、図 18 ( B ) に示すように、容量素子 1 0 2 に閾値電圧  $V_{th}$  が保持され、容量素子 1 0 3 に電圧  $V_{sig} - V_{i1}$  が保持され、発光素子 1 0 4 a のアノードは電位  $V_{e1}$  となり、トランジスタ 1 0 1 のゲートの電位は電位  $V_{sig} + V_{th} + V_{e1}$  となり、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) は電圧  $V_{sig} + V_{th} - V_{i1}$  となる。したがって、電位  $V_{sig}$  に応じた大きさの電流を発光素子 1 0 4 a に流すことができ、電位  $V_{sig}$  に応じた輝度で発光素子 1 0 4 a を発光させることができる。

## 【 0 1 9 2 】

10

上記第 4 の動作では、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) を、 $V_{sig} + V_{th} - V_{i1}$  とし、トランジスタ 1 0 1 の閾値電圧  $V_{th}$  を加味した値に設定することができる。従って、上記構成により、トランジスタ 1 0 1 の閾値電圧  $V_{th}$  のばらつきが、発光素子 1 0 4 a に供給する電流値に影響を及ぼすのを防ぐことができる。または、トランジスタ 1 0 1 が劣化して、閾値電圧  $V_{th}$  が変化しても、上記変化が発光素子 1 0 4 a に供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、質の良い表示を行うことができる。

## 【 0 1 9 3 】

同様に、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) を、電圧  $V_{sig} + V_{th} - V_{i1}$  とし、 $V_{e1}$  とは無関係な値に設定することができる。上記構成により、発光素子 1 0 4 a の電圧電流特性のばらつきが、発光素子 1 0 4 a に供給する電流値に影響を及ぼすのを防ぐことができる。または、発光素子 1 0 4 a が劣化して、発光素子 1 0 4 a の電圧電流特性が変化して、 $V_{e1}$  が変化しても、上記変化が発光素子 1 0 4 a に供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、質の良い表示を行うことができる。

20

## 【 0 1 9 4 】

なお、第 4 の動作の一部の期間において、強制的にトランジスタ 1 0 1 がオフ状態になることや、発光素子 1 0 4 a に電流が流れないようにして、発光素子 1 0 4 a が発光しないような状況にすることも可能である。つまり、非発光期間を設けることも可能である。例えば、スイッチ 1 2 をオンにすることにより、トランジスタ 1 0 1 をオフ状態にすることが可能である。または、スイッチ 1 4 をオンにすることにより、発光素子 1 0 4 a に電流が流れないようにすることができる。

30

## 【 0 1 9 5 】

なお、本発明の一態様に係る半導体装置では、第 2 の動作において、トランジスタ 1 0 1 のゲートを電位  $V_{i2}$  に保つ。上記動作により、トランジスタ 1 0 1 がノーマリオンであっても、すなわち閾値電圧  $V_{th}$  がマイナスの値を有していても、トランジスタ 1 0 1 において、ソースの電位がゲートの電位  $V_{i2}$  よりも高くなるまで容量素子 1 0 2 に蓄積されている電荷を放出することができる。よって、本発明の一態様に係る半導体装置では、トランジスタ 1 0 1 がノーマリオンであっても、上記第 4 の動作において、トランジスタ 1 0 1 の閾値電圧  $V_{th}$  を加味した値になるよう、トランジスタ 1 0 1 のゲートソース間電圧 ( $V_{gs101}$ ) を設定することができる。

40

## 【 0 1 9 6 】

なお、容量素子 1 0 3 の容量値は、負荷 1 0 4 ( 発光素子 1 0 4 a ) の寄生容量の容量値よりも、小さいことが望ましく、望ましくは 1 / 2 倍以下、より望ましくは 1 / 5 倍以下が好適である。または、容量素子 1 0 3 の電極の面積は、負荷 1 0 4 ( 発光素子 1 0 4 a ) の電極の面積よりも小さいことが望ましく、望ましくは 1 / 2 倍以下、より望ましくは 1 / 5 倍以下が好適である。ただし、本発明の実施形態の一態様は、これらに限定されない。

## 【 0 1 9 7 】

なお、容量素子 1 0 2 の容量値は、トランジスタ 1 0 1 のゲートの寄生容量の容量値より

50

も、大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子102の電極の面積は、トランジスタ101のチャネルの面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子102の電極の面積は、トランジスタ101のゲート電極の面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。それらにより、電位 $V_{sig}$ が入力されて、容量素子102とトランジスタのゲート容量とで、電圧が容量分割されたときに、容量素子102の電圧の減少を低減することが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

#### 【0198】

なお、容量素子102の容量値は、容量素子103の容量値と、同じ程度の大きさであるか、それよりも、大きいことが望ましい。容量素子102の容量値は、容量素子103の容量値と、±20%以下の違い、より好ましくは±10%以下の違いであることが好適である。または、容量素子102の電極の面積は、容量素子103の電極の面積と、同じ程度の大きさであるか、それよりも、大きいことが望ましい。これらにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

10

#### 【0199】

なお、期間T11乃至期間T14における、回路100の概略図を、図19(A)乃至図19(D)に、それぞれ示す。本発明の一態様に係る半導体装置は、回路100が、上記各期間において図19(A)乃至図19(D)に示す構造を取ることができれば良い。よって、本発明の一態様に係る半導体装置は、図11乃至図16に示した構成を有する回路100に限定されるものではない。本発明の一態様に係る半導体装置は、回路100において、図19(A)乃至図19(D)に示す構造を取りうるように、スイッチの配置や数、各種電位の供給を行う配線の数などを、適宜変更することが可能である。

20

#### 【0200】

なお、上記第3の動作が行われる期間T13の後、上記第4の動作が行われる期間T14の前に、第6の動作が行われる期間T16を設けても良い。

#### 【0201】

図11(C)に示す回路100において、期間T16を設けた場合の、スイッチ11、スイッチ12、スイッチ13、及びスイッチ14の動作と、配線21の電位と、トランジスタ101のゲートソース間電圧( $V_{gss101}$ )とを示すタイミングチャートの一例を、図20(A)に図示する。

30

#### 【0202】

図20(A)に示すタイミングチャートは、期間T13と期間T14の間に、期間T16が設けられている点において、図17(A)に示したタイミングチャートと異なる。

#### 【0203】

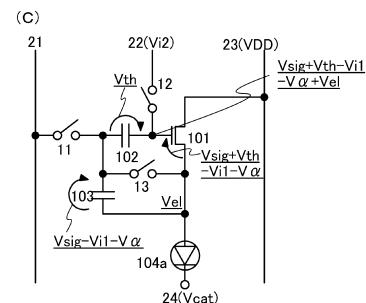

期間T16において行われる第6の動作について説明する。期間T16では、図20(A)に示すように、スイッチ12が導通状態、スイッチ11、スイッチ13、及びスイッチ14が非導通状態である。よって、期間T16では、図20(B)に示すように、トランジスタ101のゲートソース間電圧( $V_{gss101}$ )は、電圧 $V_{sig} + V_{th} - V_{i1} - V$ となる。

40

#### 【0204】

第6の動作で、電位 $V$ は、発光素子104aのアノードが電気的に浮遊状態(フローティング状態)となることで変動する電位である。電位 $V$ は、トランジスタ101がオフであるならば、発光素子104aの容量値と、容量素子102及び容量素子103の容量値の比に応じて、その値が定まる。しかし、電位 $V_{sig}$ の高さによっては、トランジスタ101がオンするので、トランジスタ101を介して発光素子104aのアノードに電荷が流入してしまう。よって、電位 $V$ は、上記静電容量の比によってのみ決まらず、発光素子104aのアノードに流入する電荷によっても、その値が変化する。

#### 【0205】

50

上記電荷量 Q によって移動度のばらつきを抑える効果が期待できる。以下、この理由について説明する。

【 0 2 0 6 】

電荷量 Q は、期間 T 1 6 において、トランジスタ 1 0 1 のドレインからソースに流れ込む電荷量に相当する。よって、電荷量 Q は、トランジスタ 1 0 1 の移動度が大きいほど、大きくなる。そして、電荷量 Q が大きくなると、発光素子 1 0 4 a の発光時における、トランジスタ 1 0 1 のゲートソース間電圧 (V<sub>g s 1 0 1</sub>) が、小さくなる。すなわち、電荷量 Q により、トランジスタ 1 0 1 の移動度が大きいほど、発光素子 1 0 4 a に供給される電流値が小さくなるように補正がかかり、また、トランジスタ 1 0 1 の移動度が小さいほど、発光素子 1 0 4 a に供給される電流値があまり小さくならないように補正がかかる。

10

したがって、電荷量 Q により、移動度のばらつきを抑えることができる。

【 0 2 0 7 】

期間 T 1 6 の後、期間 T 1 4 では、トランジスタ 1 0 1 のゲートソース間電圧 (V<sub>g s 1 0 1</sub>) は電圧 V<sub>s i g</sub> + V<sub>t h</sub> - V<sub>i 1</sub> - V<sub>1</sub> となる。よって、トランジスタ 1 0 1 の閾値電圧 V<sub>t h</sub> と移動度を加味した値に、ゲートソース間電圧を設定することができる。

【 0 2 0 8 】

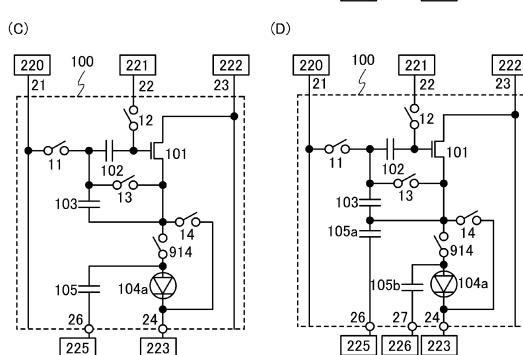

また、本発明の一態様に係る半導体装置は、図 8 と同様に、図 1 1 (B) に示した回路 1 0 0 において、負荷 1 0 4 と接続された容量素子 1 0 5 を、さらに有していても良い。同様に、本発明の一態様に係る半導体装置は、図 1 1 (C) に示した回路 1 0 0 において、発光素子 1 0 4 a と接続された容量素子 1 0 5 を、さらに有していても良い。同様に、本発明の一態様に係る半導体装置は、図 1 1 (D) に示した回路 1 0 0 において、発光素子 1 0 4 b と接続された容量素子 1 0 5 を、さらに有していても良い。

20

【 0 2 0 9 】

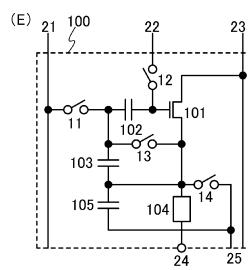

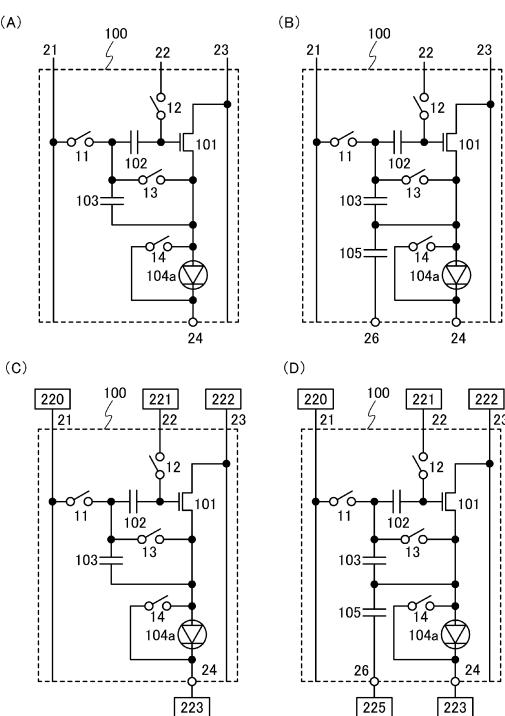

図 2 1 (A) に示す半導体装置は、図 1 1 (B) に示した回路 1 0 0 において、負荷 1 0 4 と接続された容量素子 1 0 5 を、さらに有している。具体的には、容量素子 1 0 5 の一方の電極が、容量素子 1 0 3 の他方の電極、及びトランジスタ 1 0 1 のソースまたはドレインの一方へ、接続されている。容量素子 1 0 5 の他方の電極は、配線 2 6 に接続されている。なお、図 2 1 (A) では、回路 1 0 0 が負荷 1 0 4 を有する場合を一例として示しているが、図 2 1 (A) において、負荷 1 0 4 の代わりに発光素子 1 0 4 a または発光素子 1 0 4 b が用いられていても良い。

30

【 0 2 1 0 】

なお、配線 2 6 は、様々な配線と接続させることが可能である。例えば、配線 2 2 、配線 2 3 、配線 2 4 、配線 2 5 、または、別の回路 1 0 0 の配線、走査線、ゲート線、トランジスタのゲートと接続された配線などに接続させることが出来る。これにより、配線の数を減らすことが出来る。

【 0 2 1 1 】

図 2 1 (B) に示す半導体装置は、図 2 1 (A) に示した回路 1 0 0 において、配線 2 6 を配線 2 4 に接続させた場合の例を示す。なお、図 2 1 (B) では、回路 1 0 0 が負荷 1 0 4 を有する場合を一例として示しているが、図 2 1 (B) において、負荷 1 0 4 の代わりに発光素子 1 0 4 a または発光素子 1 0 4 b が用いられていても良い。このように接続することにより、配線 2 6 を減らすことが出来る。

40

【 0 2 1 2 】

図 2 1 (C) に示す半導体装置は、図 2 1 (A) に示した回路 1 0 0 において、配線 2 6 を配線 2 3 に接続させた場合の例を示す。なお、図 2 1 (C) では、回路 1 0 0 が負荷 1 0 4 を有する場合を一例として示しているが、図 2 1 (C) において、負荷 1 0 4 の代わりに発光素子 1 0 4 a または発光素子 1 0 4 b が用いられていても良い。このように接続することにより、配線 2 6 を減らすことが出来る。

【 0 2 1 3 】

図 2 1 (D) に示す半導体装置は、図 2 1 (A) に示した回路 1 0 0 において、配線 2 6 を配線 2 2 に接続させた場合の例を示す。なお、図 2 1 (D) では、回路 1 0 0 が負荷 1

50

04を有する場合を一例として示しているが、図21(D)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられても良い。このように接続することにより、配線26を減らすことが出来る。

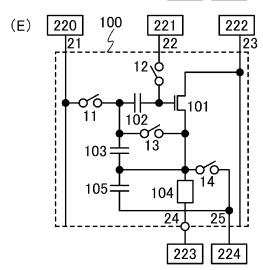

【0214】

図21(E)に示す半導体装置は、図21(A)に示した回路100において、配線26を配線25に接続させた場合の例を示す。なお、図21(E)では、回路100が負荷104を有する場合を一例として示しているが、図21(E)において、負荷104の代わりに発光素子104aまたは発光素子104bが用いられても良い。このように接続することにより、配線26を減らすことが出来る。

【0215】

負荷104、発光素子104aまたは発光素子104bに、並列に接続された容量素子105を、回路100に追加することで、上記実施の形態で説明した第6の動作及び第4の動作において、トランジスタ101のソースまたはドレインの一方における電荷の変動を抑えることができるため、電圧V<sub>g</sub>を小さくすることができる。よって、ゲートソース間電圧V<sub>gs</sub>を理想的な値、すなわち電圧V<sub>sig</sub>+V<sub>th</sub>-V<sub>i1</sub>に近づけることができる、負荷104、発光素子104aまたは発光素子104bに供給する電流を、電圧V<sub>sig</sub>を正確に反映した値により近づけることができる。

【0216】

または、容量素子105の容量値を適宜調整することにより、期間T16における電荷量Qによる電位の変化量を調整することができる。これにより、移動度のばらつきの低減を、より適切に行うことが出来る。

10

20

【0217】

なお、容量素子105の電極の面積は、負荷104(発光素子104a)の電極の面積よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。または、容量素子105の容量値は、負荷104(発光素子104a)の容量値よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。それらにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

【0218】

なお、容量素子105の電極の面積と、負荷104(発光素子104a)の電極の面積の合計は、容量素子103の電極の面積よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。または、容量素子105の容量値と、負荷104(発光素子104a)の容量値の合計は、容量素子103の容量値よりも大きいことが望ましく、望ましくは2倍以上、より望ましくは5倍以上が好適である。それらにより、容量素子103と、容量素子105及び負荷104(発光素子104a)とで、電圧が容量分割されたときに、容量素子103により多くの電圧が加わるようにすることができる。ただし、本発明の実施形態の一態様は、これに限定されない。

30

【0219】

なお、容量素子105の電極の面積は、容量素子102または容量素子103の電極の面積よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。または、容量素子105の容量値は、容量素子102または容量素子103の容量値よりも小さいことが望ましく、望ましくは1/2倍以下、より望ましくは1/3倍以下が好適である。それらにより、同じレイアウト面積のなかで、最適な動作を行うことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

40

【0220】

なお、配線25は、様々な配線と接続させることが可能である。例えば、配線22、配線24、配線26、または、別の回路100の配線、走査線、ゲート線、トランジスタのゲートと接続された配線などに接続させることが出来る。これにより、配線の数を減らすことが出来る。

【0221】

50

また、本発明の一態様に係る半導体装置は、図21(A)乃至図21(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有しても良い。

【0222】

図22(A)乃至図22(D)に示す半導体装置は、図21(A)乃至図21(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路220と、配線22に一定電圧や信号を供給する機能を有する回路221と、配線23に一定電圧や信号を供給する機能を有する回路222と、配線24に一定電圧や信号を供給する機能を有する回路223と、配線25に一定電圧や信号を供給する機能を有する回路224とを、それぞれ有する。さらに、図22(A)に示す回路100は、配線26に一定電圧や信号を供給する機能を有する回路225を有する。

10

【0223】

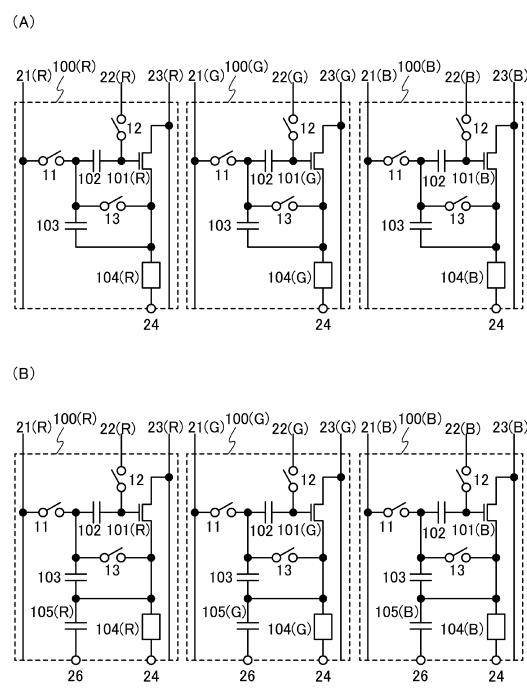

また、図11(B)乃至図11(D)、図21(B)乃至図21(D)のいずれかの回路100を、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。同様に、画素が有する容量素子105の容量値も、対応する色相によって、異なっていても良い。

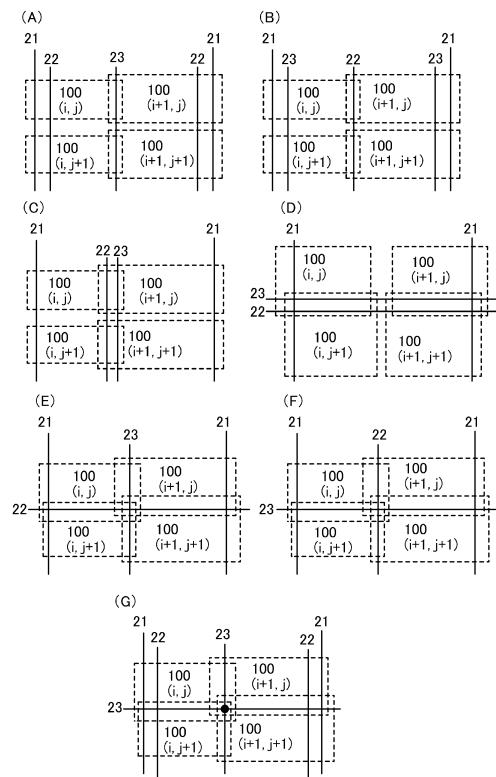

【0224】

図23(A)に、図11(B)に示した回路100を、表示装置の画素として用いた場合を一例として示している。図23(A)では、回路100(R)が赤(R)に対応した画素に相当し、回路100(G)が緑(G)に対応した画素に相当し、回路100(B)が青(B)に対応した画素に相当する。本発明の一態様では、回路100(R)が有するトランジスタ101(R)と、回路100(G)が有するトランジスタ101(G)と、回路100(B)が有するトランジスタ101(B)との少なくとも一つにおいて、そのチャネル幅とチャネル長の比が他と異なっていても良い。上記構成により、回路100(R)が有する負荷104(R)、回路100(G)が有する負荷104(G)、回路100(B)が有する負荷104(B)のそれぞれに供給される電流を異なる値に設定することができる。

20

【0225】

また、図23(B)に、図21(A)に示した回路100を、表示装置の画素として用いた場合を一例として示している。図23(B)の場合も図23(A)と同様に、回路100(R)が有するトランジスタ101(R)と、回路100(G)が有するトランジスタ101(G)と、回路100(B)が有するトランジスタ101(B)との少なくとも一つが、そのチャネル幅とチャネル長の比が他と異なっていても良い。上記構成により、回路100(R)が有する負荷104(R)、回路100(G)が有する負荷104(G)、回路100(B)が有する負荷104(B)のそれぞれに供給される電流を異なる値に設定することができる。

30

【0226】

また、図23(B)の場合、回路100(R)が有する容量素子105(R)と、回路100(G)が有する容量素子105(G)と、回路100(B)が有する容量素子105(B)との少なくとも一つにおいて、その容量値が他と異なっていても良い。

40

【0227】

なお、図23(A)及び図23(B)では、回路100(R)が負荷104(R)を有し、回路100(G)が負荷104(G)を有し、回路100(B)が負荷104(B)を有する場合を一例として示しているが、図23(A)または図23(B)において、負荷104(R)、負荷104(G)、または負荷104(B)の代わりに、各色相に対応した発光素子104aまたは発光素子104bが用いられていても良い。

【0228】

また、図23(B)では、図21(A)に示した回路100を、表示装置の画素として用いた場合を一例として示しているが、図21(B)乃至図21(E)に示した回路100

50

を、表示装置の画素として用いても良い。

【0229】

なお、本実施の形態において、トランジスタ101のしきい値電圧などのばらつきを補正するような動作を行ったが、本発明の実施形態の一態様は、これに限定されない。例えば、しきい値電圧のばらつきを補正するような動作を行わずに、負荷104に電流を供給させて動作させることも可能である。

【0230】

本実施の形態は、基本原理の一例について述べたものである。したがって、本実施の形態の一部または全部について、他の実施の形態の一部または全部と、自由に組み合わせたり、適用することや、置き換えて実施することができる。

10

【0231】

(実施の形態2)

本実施の形態では、本発明の一態様に係る半導体装置である、回路100の構成例について説明する。本実施の形態では、実施の形態1で示した回路に対して、スイッチを追加した構成や、駆動方法の一部を変更した場合などについて述べる。したがって、実施の形態1で述べた内容は、本実施の形態にも適用することが可能である。

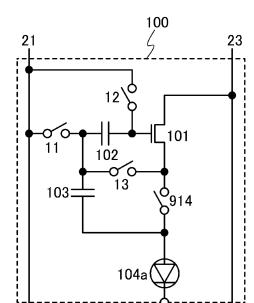

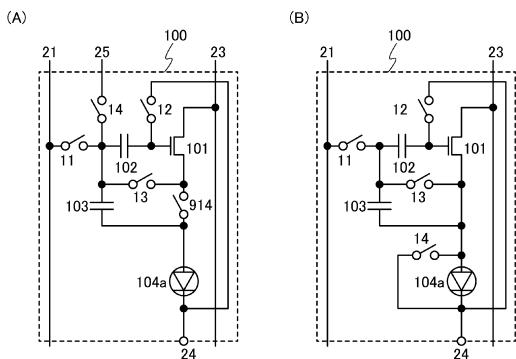

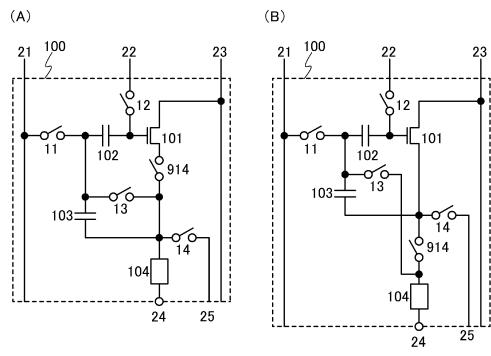

【0232】

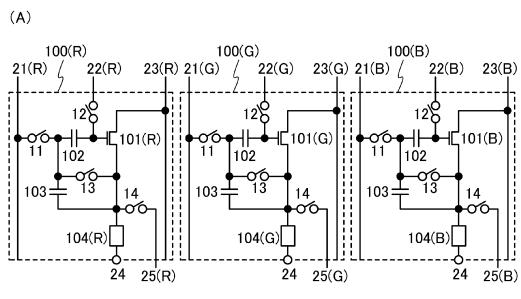

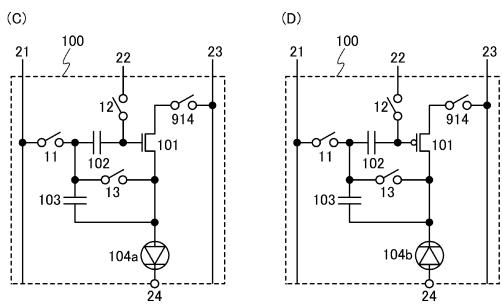

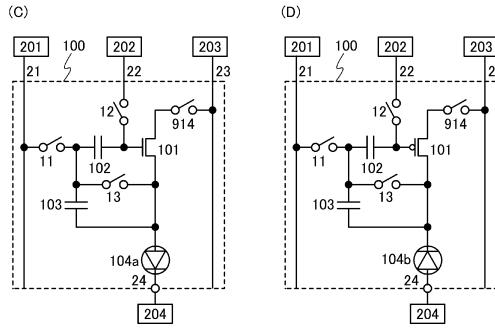

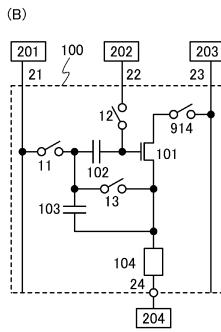

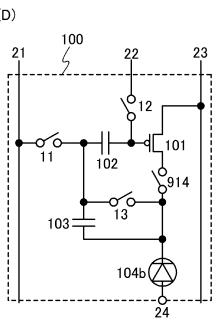

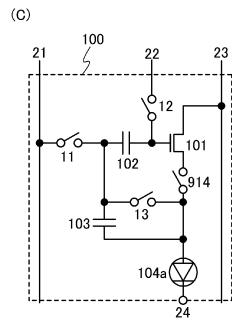

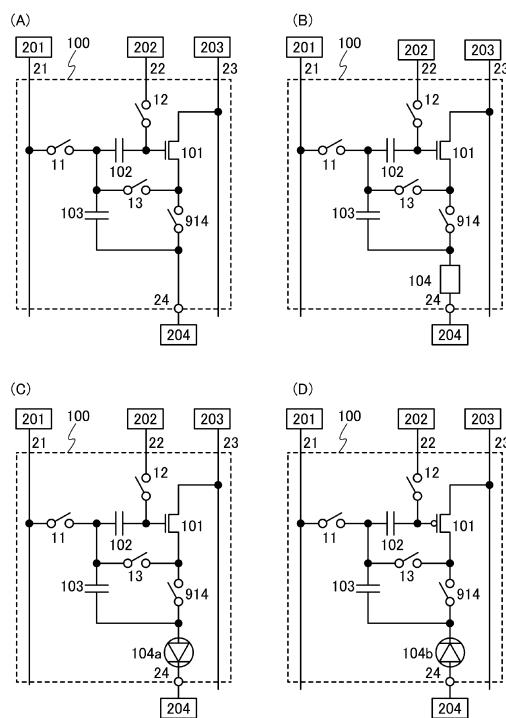

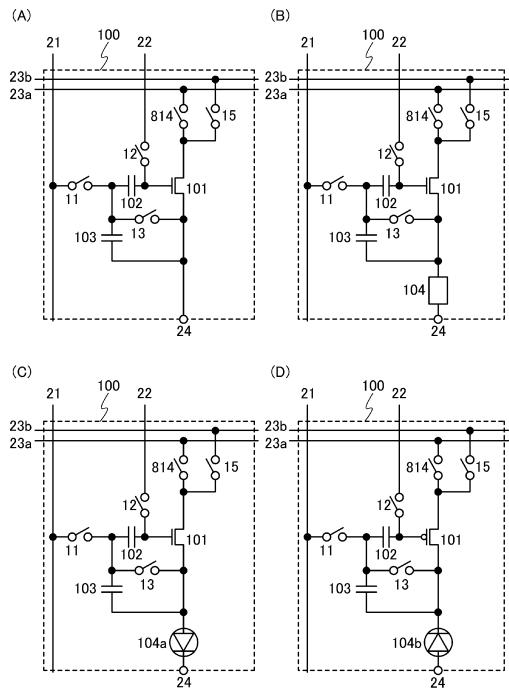

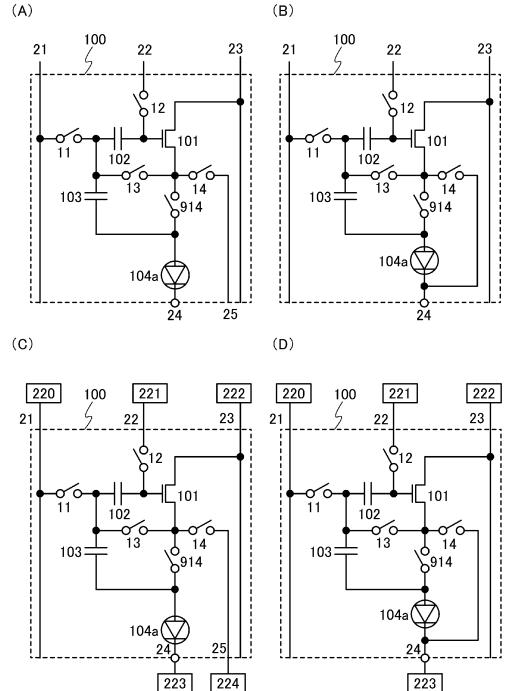

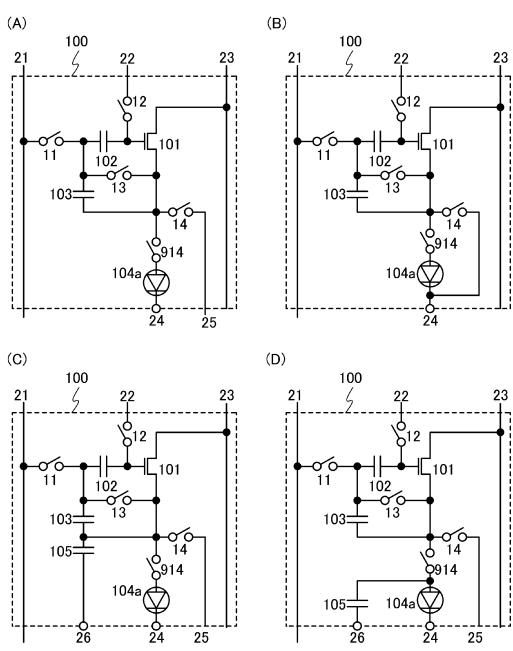

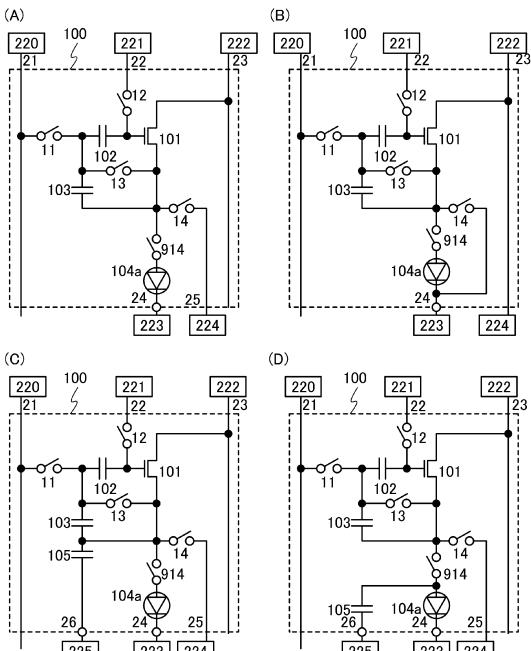

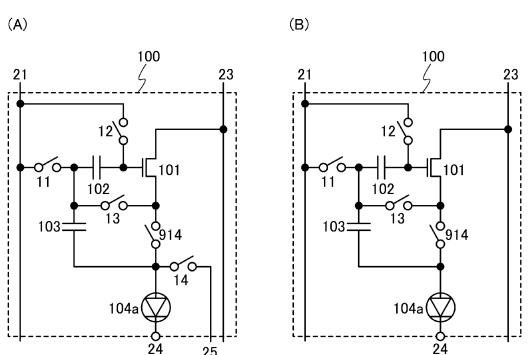

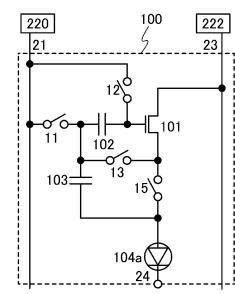

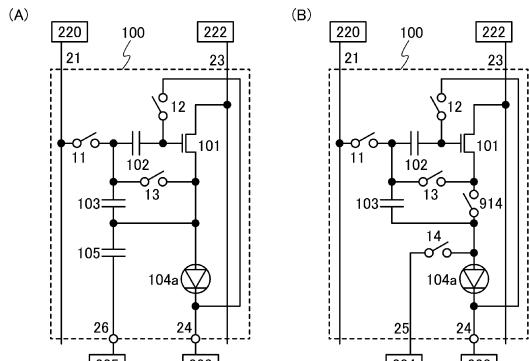

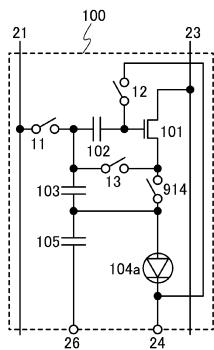

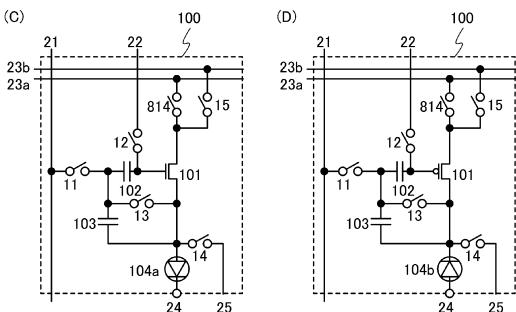

図24(A)乃至図24(D)に、回路100の構成例をそれぞれ示す。図24(A)乃至図24(D)に示す回路100は、図1(A)乃至図1(D)に示した回路100にスイッチ914を追加した構成に、それぞれ相当する。そして、上記スイッチ914は、トランジスタ101のソースまたはドレインの他方と、配線23との間の導通状態を制御する機能を有する。または、配線23から配線24までの間の導通状態を制御する機能を有する。または、スイッチ914は、容量素子103に電流が流れることを防ぐ機能を有する。または、スイッチ914は、容量素子102に電流が流れることを防ぐ機能を有する。または、スイッチ914は、負荷104に電流が流れることを防ぐ機能を有する。

20

【0233】

また、本発明の一態様に係る半導体装置は、図24(A)乃至図24(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

30

【0234】

図25(A)乃至図25(D)に示す半導体装置は、図24(A)乃至図24(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路201と、配線22に一定電圧や信号を供給する機能を有する回路202と、配線23に一定電圧や信号を供給する機能を有する回路203と、配線24に一定電圧や信号を供給する機能を有する回路204とを、それぞれ有する。

【0235】

なお、図24及び図25に示す回路100は、スイッチ11、スイッチ12、スイッチ13、スイッチ914に、トランジスタを用いることができる。

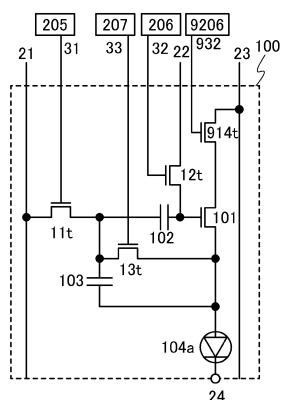

【0236】

なお、一例として図86に示すように、スイッチ914がトランジスタ914tである場合、そのトランジスタ914tのゲートは、配線932と接続されており、その配線932は、一定電圧や信号を供給する機能を有する回路9206と接続されていることが可能である。その回路9206の例としては、ゲートドライバ(走査線駆動回路)などがある。

40

【0237】

なお、配線31乃至配線33、配線932において、その中の少なくとも2本の配線は、互いに接続させることが可能である。または、配線31乃至配線33、配線932の少なくとも1本は、別の回路100の配線31乃至配線33、配線932の少なくとも1本と接続させることが可能である。

【0238】

50

図24及び図25に示す回路100は、図1及び図2に示す回路100と同様の動作を行うことができる。ただし、一例としては、図24及び図25に示す回路100では、図5、図6に示す期間T11乃至期間T13、及び期間T15において、スイッチ914は導通状態であり、期間T14においてスイッチ914は非導通状態であることが好適である。これらにより、期間T14において、トランジスタ101を介して、発光素子104aなどに、電荷が漏れることを防ぐことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

【0239】

または、期間T13において、スイッチ914を非導通状態とすることも可能である。これにより、トランジスタ101に電流が流れないので、トランジスタ101のゲートやソースなどの、回路100内の各ノードにおける電位の制御がしやすくなる。

10

【0240】

または、期間T11において、スイッチ914を非導通状態とすることも可能である。これにより、トランジスタ101に電流が流れないので、トランジスタ101のゲートやソースなどの、回路100内の各ノードにおける電位の制御がしやすくなる。

【0241】

または、期間T15の一部の期間においても、スイッチ914を非導通状態とする。これにより、発光素子104aなどに電流が流れないようにして、非発光期間を設けることが出来る。

【0242】

なお、図24(B)及び図25(B)に示す回路100は、図8、図9、図10(B)と同様に、負荷104と接続された容量素子105を、さらに有していても良い。同様に、図24(C)及び図25(C)に示す回路100は、発光素子104aと接続された容量素子105を、さらに有していても良い。同様に、図24(D)及び図25(D)に示す回路100は、発光素子104bと接続された容量素子105を、さらに有していても良い。具体的に、容量素子105の一方の電極は、容量素子103の他方の電極、及びトランジスタ101のソースまたはドレインの一方に、接続される。容量素子105の他方の電極は、別途設けられた配線26、配線24、配線23、或いは配線22に接続される。

20

【0243】

また、図24(B)乃至図24(D)に示す回路100、及び、図25(B)乃至図25(D)に示す回路100に上記容量素子105を追加した回路の、いずれかを、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。

30

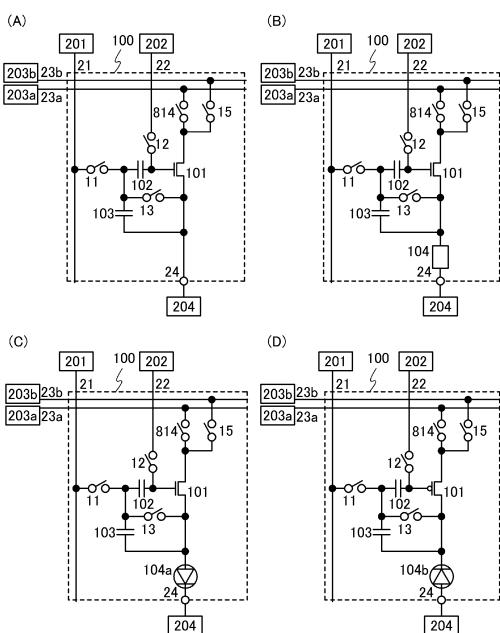

【0244】

なお、図24及び図25とは別の場所に、スイッチ914を設けることも可能である。具体的には、一例としては、配線23から配線24までの間の導通状態を制御することが可能である場所に設けることが出来る。例えば、図26(A)乃至図26(D)に、回路100の構成例をそれぞれ示す。図26(A)乃至図26(D)に示す回路100は、図1(A)乃至図1(D)に示した回路100にスイッチ914を追加した構成に、それぞれ相当する。そして、上記スイッチ914は、トランジスタ101のソースまたはドレインの一方と、容量素子103の他方の電極との間の導通状態を制御する機能を有する。さらに、スイッチ13が導通状態であるならば、上記スイッチ914は、トランジスタ101のソースまたはドレインの一方と、容量素子102の一方の電極及び容量素子103の一方の電極との間の導通状態を制御する機能を有する。

40

【0245】

また、本発明の一態様に係る半導体装置は、図26(A)乃至図26(D)に示した回路100に加えて、回路100に各種一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0246】

50

図27(A)乃至図27(D)に示す半導体装置は、図26(A)乃至図26(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路201と、配線22に一定電圧や信号を供給する機能を有する回路202と、配線23に一定電圧や信号を供給する機能を有する回路203と、配線24に一定電圧や信号を供給する機能を有する回路204とを、それぞれ有する。

【0247】

なお、図26及び図27に示す回路100は、スイッチ11、スイッチ12、スイッチ13、スイッチ914に、トランジスタを用いることができる。

【0248】

図26及び図27に示す回路100は、図1、図2、図24、または、図25に示す回路100と同様の動作を行うことができる。

【0249】

なお、図26(B)及び図27(B)に示す回路100は、図8、図9、図10(B)と同様に、負荷104と接続された容量素子105を、さらに有していても良い。同様に、図26(C)及び図27(C)に示す回路100は、発光素子104aと接続された容量素子105を、さらに有していても良い。同様に、図26(D)及び図27(D)に示す回路100は、発光素子104bと接続された容量素子105を、さらに有していても良い。具体的に、容量素子105の一方の電極は、容量素子103の他方の電極に接続される。なおかつ、スイッチ914は、容量素子105の一方の電極と、トランジスタ101のソースまたはドレインの一方との間の導通状態を制御する。容量素子105の他方の電極は、別途設けられた配線26、配線24、配線23、或いは配線22に接続される。

【0250】

また、図26(B)乃至図26(D)に示す回路100、及び、図27(B)乃至図27(D)に示す回路100に上記容量素子105を追加した回路の、いずれかを、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。

【0251】

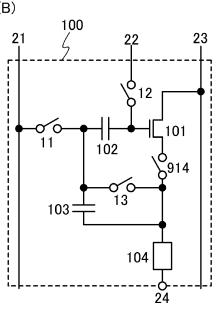

なお、図24、図25、図26、図27とは別の場所に、スイッチ914を設けることも可能である。例えば、図28(A)乃至図28(D)に、回路100の構成例をそれぞれ示す。図28(A)乃至図28(D)に示す回路100は、図1(A)乃至図1(D)に示した回路100にスイッチ914を追加した構成に、それぞれ相当する。そして、上記スイッチ914は、トランジスタ101のソースまたはドレインの一方と、容量素子103の他方の電極との間の導通状態を制御する機能を有する。さらに、スイッチ13が導通状態であるならば、上記スイッチ914は、容量素子102の一方の電極及び容量素子103の一方の電極と、容量素子103の他方の電極との間の導通状態を制御する機能を有する。

【0252】

また、本発明の一態様に係る半導体装置は、図28(A)乃至図28(D)に示した回路100に加えて、回路100に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0253】

図29(A)乃至図29(D)に示す半導体装置は、図28(A)乃至図28(D)に示す回路100に加えて、配線21に一定電圧や信号を供給する機能を有する回路201と、配線22に一定電圧や信号を供給する機能を有する回路202と、配線23に一定電圧や信号を供給する機能を有する回路203と、配線24に一定電圧や信号を供給する機能を有する回路204とを、それぞれ有する。

【0254】

なお、図28及び図29に示す回路100は、スイッチ11、スイッチ12、スイッチ13、スイッチ914に、トランジスタを用いることができる。

10

20

30

40

50

## 【0255】

図28及び図29に示す回路100は、図1、図2、図24、図25、図26、図27に示す回路100と同様の動作を行うことができる。ただし、一例としては、図28及び図29に示す回路100では、図5、図6に示す期間T11乃至期間T13、及び期間T15において、スイッチ914は導通状態であり、期間T14においてスイッチ914は非導通状態であることが好適である。これらにより、期間T14において、トランジスタ101を介して、発光素子104aなどに、電荷が漏れることを防ぐことが出来る。ただし、本発明の実施形態の一態様は、これに限定されない。

## 【0256】

または、期間T11において、スイッチ914を非導通状態とすることも可能である。これにより、トランジスタ101に電流が流れないので、電位の制御がしやすくなる。

10

## 【0257】

または、期間T15の一部の期間においても、スイッチ914を非導通状態とする。これにより、発光素子104aなどに電流が流れないようにして、非発光期間を設けることが出来る。

## 【0258】

なお、期間T12において、スイッチ914を非導通状態とすることも可能である。期間T12において、スイッチ914を非導通状態とすることで、期間T12において発光素子104aのアノードを電位Vi1に保つことができる。よって、期間T13を設けずに、すなわち第3の動作を行わずに、期間T12における第2の動作が終了した後、期間T14における第4の動作を行うことができる。

20

## 【0259】

なお、図28(B)及び図29(B)に示す回路100は、図8、図9、図10(B)などと同様に、負荷104と接続された容量素子105を、さらに有していても良い。同様に、図28(C)及び図29(C)に示す回路100は、発光素子104aと接続された容量素子105を、さらに有していても良い。同様に、図28(D)及び図29(D)に示す回路100は、発光素子104bと接続された容量素子105を、さらに有していても良い。具体的に、容量素子105の一方の電極は、容量素子103の他方の電極に接続される。なおかつ、スイッチ914は、容量素子105の一方の電極と、トランジスタ101のソースまたはドレインの一方との間の導通状態を制御する。容量素子105の他方の電極は、別途設けられた配線26、配線24、配線23、或いは配線22に接続される。

30

## 【0260】

また、図28(B)乃至図28(D)に示す回路100、及び、図29(B)乃至図29(D)に示す回路100に上記容量素子105を追加した回路の、いずれかを、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。

## 【0261】

なお、図24乃至図29とは別の場所に、スイッチ914を設けることも可能である。例えば、図30(A)乃至図30(D)に、回路100の構成例をそれぞれ示す。図30(A)乃至図30(D)に示す回路100は、図1(A)乃至図1(D)に示した回路100にスイッチ914を追加した構成に、それぞれ相当する。そして、図30(A)において上記スイッチ914は、トランジスタ101のソースまたはドレインの一方及び容量素子103の他方の電極と、配線24との間の導通状態を制御する機能を有する。図30(B)において上記スイッチ914は、トランジスタ101のソースまたはドレインの一方及び容量素子103の他方の電極と、負荷104との間の導通状態を制御する機能を有する。図30(C)において上記スイッチ914は、トランジスタ101のソースまたはドレインの一方及び容量素子103の他方の電極と、発光素子104aのアノードとの間の導通状態を制御する機能を有する。図30(D)において上記スイッチ914は、トラン

40

50

ジスタ 101 のソースまたはドレインの一方及び容量素子 103 の他方の電極と、発光素子 104b のカソードとの間の導通状態を制御する機能を有する。

【0262】

また、本発明の一態様に係る半導体装置は、図 30 (A) 乃至図 30 (D) に示した回路 100 に加えて、回路 100 に各種の一定電圧や信号を供給する機能を有する回路を、さらに有していても良い。

【0263】

図 31 (A) 乃至図 31 (D) に示す半導体装置は、図 30 (A) 乃至図 30 (D) に示す回路 100 に加えて、配線 21 に一定電圧や信号を供給する機能を有する回路 201 と、配線 22 に一定電圧や信号を供給する機能を有する回路 202 と、配線 23 に一定電圧や信号を供給する機能を有する回路 203 と、配線 24 に一定電圧や信号を供給する機能を有する回路 204 とを、それぞれ有する。

10

【0264】

なお、図 30 及び図 31 に示す回路 100 は、スイッチ 11、スイッチ 12、スイッチ 13、スイッチ 914 に、トランジスタを用いることができる。

【0265】

図 30 及び図 31 に示す回路 100 は、図 1、図 2、図 24、図 25、図 26、図 27、図 28、図 29 に示す回路 100 と同様の動作を行うことができる。ただし、一例としては、図 30 及び図 31 に示す回路 100 では、図 5、図 6 に示す期間 T11、及び期間 T13 乃至期間 T15 において、スイッチ 914 は導通状態であり、期間 T12 においてスイッチ 914 は非導通状態であることが好適である。ただし、本発明の実施形態の一態様は、これに限定されない。これにより、期間 T12 において、スイッチ 914 を非導通状態とすることで、期間 T12 において発光素子 104a のアノードを電位 Vi1 に保つことができる。よって、期間 T13 を設けずに、すなわち第 3 の動作を行わずに、期間 T12 における第 2 の動作が終了した後、期間 T14 における第 4 の動作を行うことができる。ただし、本発明の実施形態の一態様は、これに限定されない。

20

【0266】

または、期間 T11 において、スイッチ 914 を非導通状態とすることも可能である。これにより、発光素子 104a などに電流が流れないため、配線 22 の電位 Vi2 は、高い値でもよい。

30

【0267】

または、期間 T12 において、スイッチ 914 を非導通状態とすることも可能である。これにより、発光素子 104a などに電流が流れないため、配線 22 の電位 Vi2 は、高い値でもよい。

【0268】

または、期間 T15 の一部の期間においても、スイッチ 914 を非導通状態とする。これにより、発光素子 104a などに電流が流れないようにして、非発光期間を設けることが出来る。

【0269】

なお、図 30 (B) 及び図 31 (B) に示す回路 100 は、図 8、図 9、図 10 (B)、図 21、図 22 などと同様に、負荷 104 と接続された容量素子 105 を、さらに有していても良い。同様に、図 30 (C) 及び図 31 (C) に示す回路 100 は、発光素子 104a と接続された容量素子 105 を、さらに有していても良い。同様に、図 30 (D) 及び図 31 (D) に示す回路 100 は、発光素子 104b と接続された容量素子 105 を、さらに有していても良い。具体的に、容量素子 105 の一方の電極は、容量素子 103 の他方の電極、及びトランジスタ 101 のソースまたはドレインの一方には接続される。容量素子 105 の他方の電極は、別途設けられた配線 26、配線 24、配線 23、或いは配線 22 に接続される。

40

【0270】

また、図 30 (B) 乃至図 30 (D) に示す回路 100、及び、図 31 (B) 乃至図 31

10

20

30

40

50

(D)に示す回路100に上記容量素子105を追加した回路の、いずれかを、表示装置の画素として用いても良い。そして、複数の色相にそれぞれ対応した画素が表示装置に設けられている場合、対応する色相によって、画素が有するトランジスタ101の、チャネル幅とチャネル長の比が、異なっていても良い。

【0271】

なお、図24乃至図31において、図1などに示す回路において、スイッチ914を追加した構成について述べたが、スイッチ914を追加するような回路は、図1などに限定されない。図1以外の他の図面に示す回路においても、図24乃至図31と同様に、スイッチ914を追加する構成を用いることが出来る。例えば、図11の回路のように、スイッチ14が追加された構成において、図24乃至図31と同様に、スイッチ914を追加する回路を構成することが出来る。その場合の一例を、図87に示す。

10

【0272】

次に、図1および図11などの回路において、図5および図17などに示す駆動方法とは異なる駆動方法を用いる場合の一例を示す。なお、このような駆動方法を用いる場合には、配線23を列方向の画素間で接続するよりも、行方向の画素間で接続することが望ましいため、図34(A)乃至図34(D)に、図1(A)乃至図1(D)に示した回路100の配置例をそれぞれ示す。図34(A)乃至図34(D)では、互いに異なる配線21に接続された複数の回路100が、共通の配線23に接続されている場合を一例として示している。つまり、配線23は、配線21と交差して設けられている。

【0273】

20

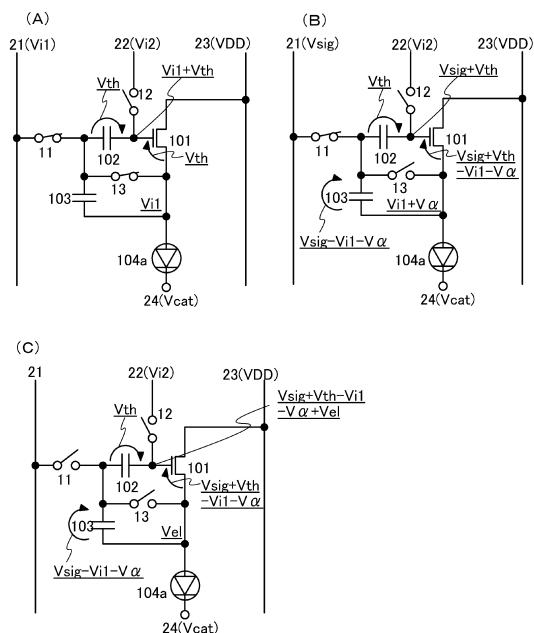

図34(C)に示す回路100を例に挙げて、本発明の半導体装置の一態様の動作の一例について説明する。この動作では、図5(B)や図17(B)における第1の動作において、容量素子102に電圧 $V_{i2} - V_{i1}$ が供給され、トランジスタ101のゲートソース間電圧( $V_{gs101}$ )が電圧 $V_{i2} - V_{i1}$ になるときに、配線21やスイッチ14を介して電位 $V_{i1}$ が供給されるのではなく、配線23を介して供給される。したがって、図5や図17などで述べた内容を、本発明の半導体装置の一態様に適用することが可能である。

【0274】

図34(C)に示す回路100の動作は、主に第1の動作、第2の動作、第3の動作、第4の動作、第5の動作に分けることができる。ただし、これに限定されず、新たな動作の追加、或いは、一部の動作の削除も可能である。

30

【0275】

まず、期間T11において行われる第1の動作について説明する。期間T11では、図35(A)に示すように、スイッチ11が非導通状態、スイッチ12及びスイッチ13が導通状態である。また、配線23には電位 $V_{i1}$ が供給される。よって、期間T11では、発光素子104aのアノードは電位 $V_{i1}$ となり、トランジスタ101のゲートソース間電圧( $V_{gs101}$ )は、電圧 $V_{i2} - V_{i1}$ となる。つまり、トランジスタ101、及び、容量素子102を、初期化していることとなる。

【0276】