(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7101648号

(P7101648)

(45)発行日 令和4年7月15日(2022.7.15)

(24)登録日 令和4年7月7日(2022.7.7)

(51)国際特許分類

A 6 3 F 7/02 (2006.01)

F I

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 2 0

請求項の数 1 (全78頁)

|          |                             |          |                                             |

|----------|-----------------------------|----------|---------------------------------------------|

| (21)出願番号 | 特願2019-164669(P2019-164669) | (73)特許権者 | 391010943<br>株式会社藤商事<br>大阪府大阪市中央区内本町一丁目1番4号 |

| (22)出願日  | 令和1年9月10日(2019.9.10)        | (74)代理人  | 100100376<br>弁理士 野中 誠一                      |

| (65)公開番号 | 特開2021-40890(P2021-40890A)  | (74)代理人  | 100142077<br>弁理士 板谷 真之                      |

| (43)公開日  | 令和3年3月18日(2021.3.18)        | (74)代理人  | 100143199<br>弁理士 磯邊 賀                       |

| 審査請求日    | 令和2年10月26日(2020.10.26)      | (72)発明者  | 柴田 伸美<br>大阪府大阪市中央区内本町一丁目1番4号 株式会社藤商事内       |

|          |                             | 審査官      | 山本 一                                        |

最終頁に続く

(54)【発明の名称】 遊技機

## (57)【特許請求の範囲】

## 【請求項1】

画像演出に必要な画像信号を生成するV D P ( Video Display Processor )、及び、前記V D Pの動作を規定する設定値が設定されるV D Pレジスタを有するV D P回路と、前記画像信号の基礎データを不揮発的に記憶するC G R O Mと、C P U、前記C P Uに制御されて動作する内部回路、及び、前記内部回路の動作を規定する設定値が設定される動作制御レジスタを有するC P U回路と、を有し、前記C P U回路が前記V D P回路に発行するディスプレイリストと、前記C P U回路による前記V D Pレジスタへの設定動作に基づいて所定の画像演出動作が実行される遊技機であって、前記C P U回路の外部に位置して前記C P Uからアクセス可能なC P Uメモリ空間には、前記C P Uのリセット後、最初に実行すべき初期プログラムを格納するメモリデバイスと、前記V D Pレジスタとが、少なくとも位置付けられており、前記メモリデバイスへのアクセス動作を適切化するべく、必要な設定値を前記動作制御レジスタに設定する第1手段と、その後、前記画像演出動作の開始前に前記初期プログラムの動作に基づき機能して、前記C G R O Mへのアクセス動作を適切化するべく、必要な動作パラメータを前記V D Pレジスタに設定する第2手段と、を設けたことを特徴とする遊技機。

## 【発明の詳細な説明】

## 【技術分野】

**【 0 0 0 1 】**

本発明は、遊技動作に起因する抽選処理を行い、その抽選結果に対応する画像演出を実行する遊技機に関し、特に、迫力ある画像演出を安定して実行できる遊技機に関する。

**【背景技術】****【 0 0 0 2 】**

パチンコ機などの弾球遊技機は、遊技盤に設けた図柄始動口と、複数の表示図柄による一連の図柄変動態様を表示する図柄表示部と、開閉板が開閉される大入賞口などを備えて構成されている。そして、図柄始動口に設けられた検出スイッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示図柄が所定時間変動される。その後、7・7・7などの所定の態様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な遊技状態を発生させている。

10

**【 0 0 0 3 】**

このような遊技状態を発生させるか否かは、図柄始動口に遊技球が入賞したことを条件に実行される大当たり抽選で決定されており、上記の図柄変動動作は、この抽選結果を踏まえたものとなっている。例えば、抽選結果が当選状態である場合には、リーチアクションなどと称される演出動作を20秒前後実行し、その後、特別図柄を整列させている。一方、ハズレ状態の場合にも、同様のリーチアクションが実行されることがあり、この場合には、遊技者は、大当たり状態になることを強く念じつつ演出動作の推移を注視することになる。そして、図柄変動動作の終了時に、停止ラインに所定図柄が揃えば、大当たり状態であることが遊技者に保証されたことになる。

20

**【先行技術文献】****【特許文献】****【 0 0 0 4 】**

【文献】特開2017-093633号公報

特開2017-093632号公報

特開2016-159030号公報

特開2016-159029号公報

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 5 】**

この種の遊技機では、各種の演出を複雑化かつ豊富化したいところ、特に、画像演出については、その要請が高い。そこで、出願人は、各種の提案をしているが（引用文献1～引用文献4）、画像演出の更なる高度化や、画像演出制御を中心とした各種の演出制御動作の更なる改善が望まれるところである。

30

**【 0 0 0 6 】**

本発明は、上記の課題に鑑みてなされたものであり、画像演出制御を中心とした各種の演出制御動作が更に改善された遊技機を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 7 】**

上記の目的を達成するため、本発明は、画像演出に必要な画像信号を生成するVDP (Video Display Processor)、及び、前記VDPの動作を規定する設定値が設定されるVDPレジスタを有するVDP回路と、前記画像信号の基礎データを不揮発的に記憶するROMと、CPU、前記CPUに制御されて動作する内部回路、及び、前記内部回路の動作を規定する設定値が設定される動作制御レジスタを有するCPU回路と、を有し、前記CPU回路が前記VDP回路に発行するディスプレイリストと、前記CPU回路による前記VDPレジスタへの設定動作に基づいて所定の画像演出動作が実行される遊技機であつて、前記CPU回路の外部に位置して前記CPUからアクセス可能なCPUメモリ空間には、前記CPUのリセット後、最初に実行すべき初期プログラムを格納するメモリデバイスと、前記VDPレジスタとが、少なくとも位置付けられており、前記メモリデバイスへのアクセス動作を適切化するべく、必要な設定値を前記動作制御レジスタに設定する第

40

50

1手段と、その後、前記画像演出動作の開始前に前記初期プログラムの動作に基づき機能して、前記C G R O Mへのアクセス動作を適切化するべく、必要な動作パラメータを前記V D Pレジスタに設定する第2手段と、を設けてある。なお、実施例では、V D P (Video Display Processor)の動作は、V D P回路52を構成する各種の内部回路(72～77など)によって実現される。

【発明の効果】

【0008】

上記した本発明によれば、第1手段の設定動作に基づいて、その後の初期プログラムが動作するので、第2手段、及びそれ以降の処理を最適化することができる。また、C G R O Mのアクセスを最適化することもできる。

10

【図面の簡単な説明】

【0009】

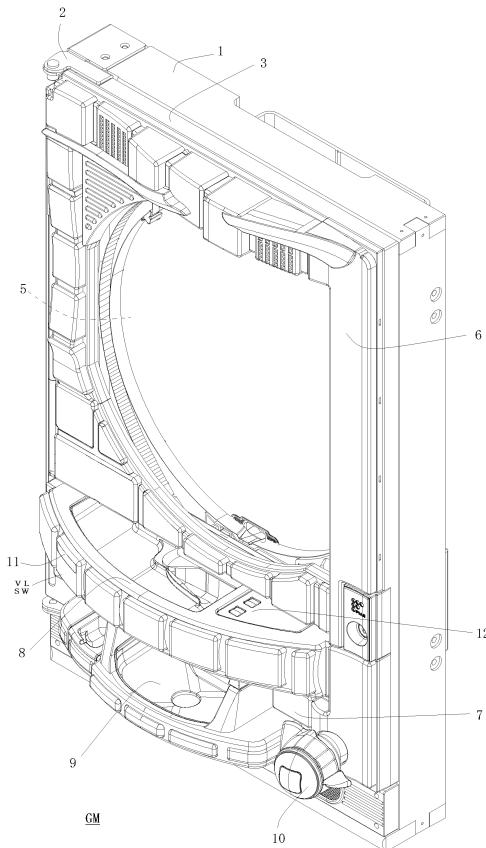

【図1】本実施例のパチンコ機を示す斜視図である。

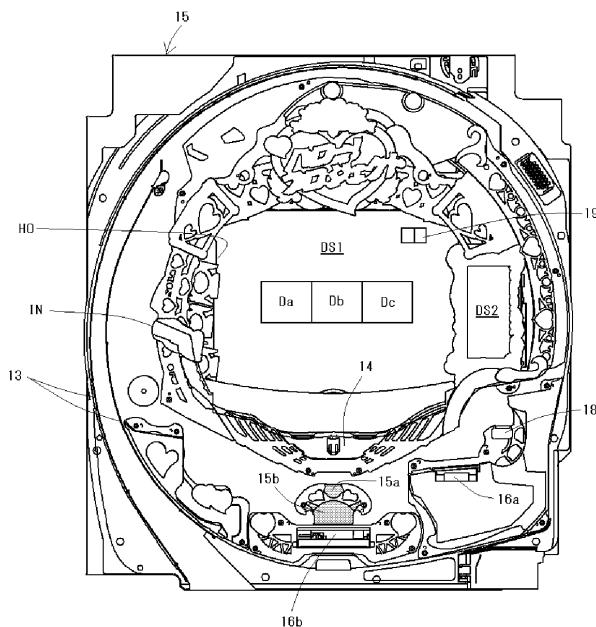

【図2】図1の遊技機の遊技領域を示す正面図である。

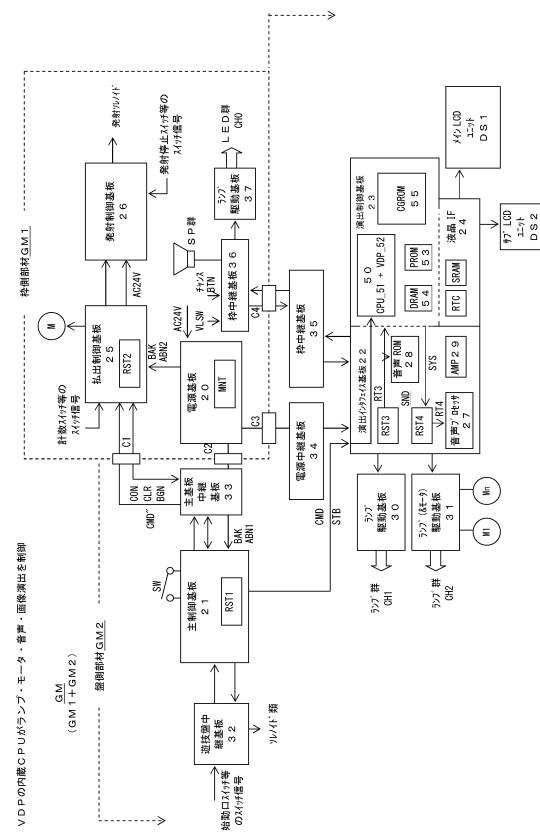

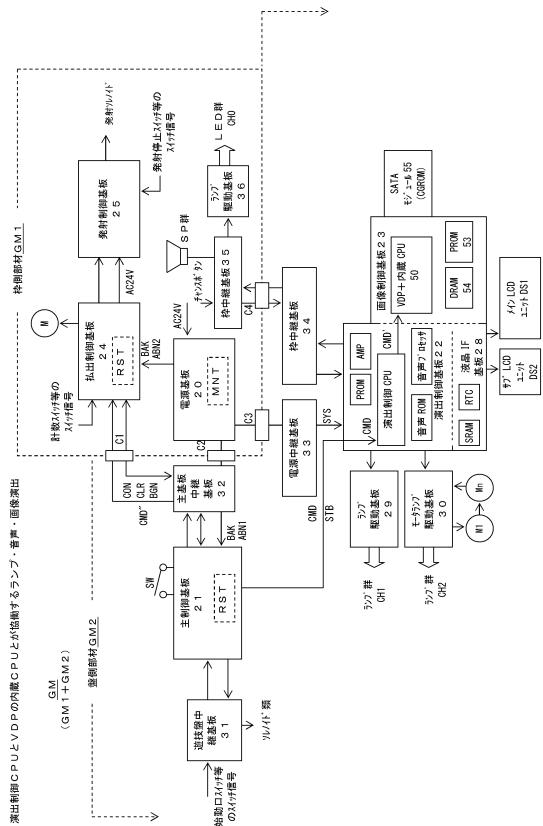

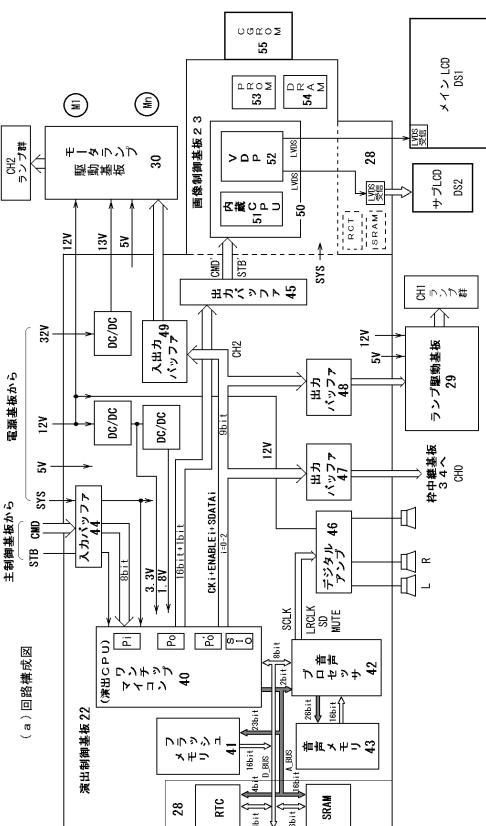

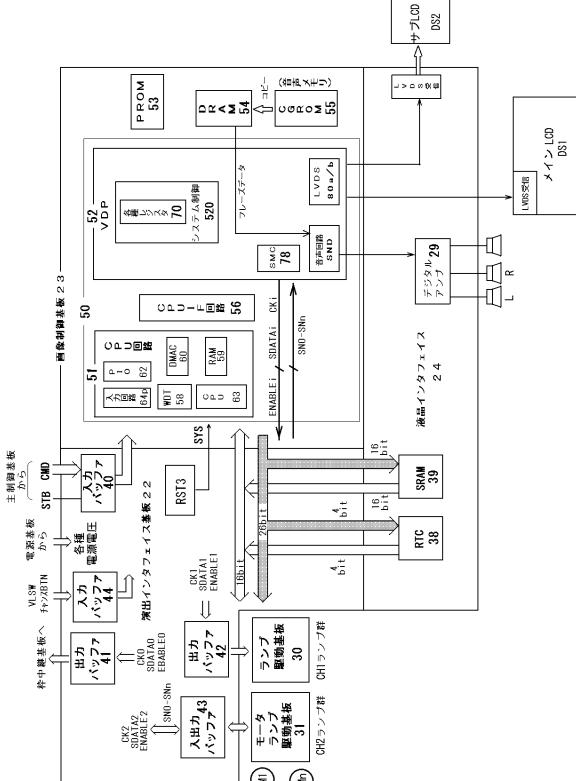

【図3】図1の遊技機の全体回路構成を示すブロック図である。

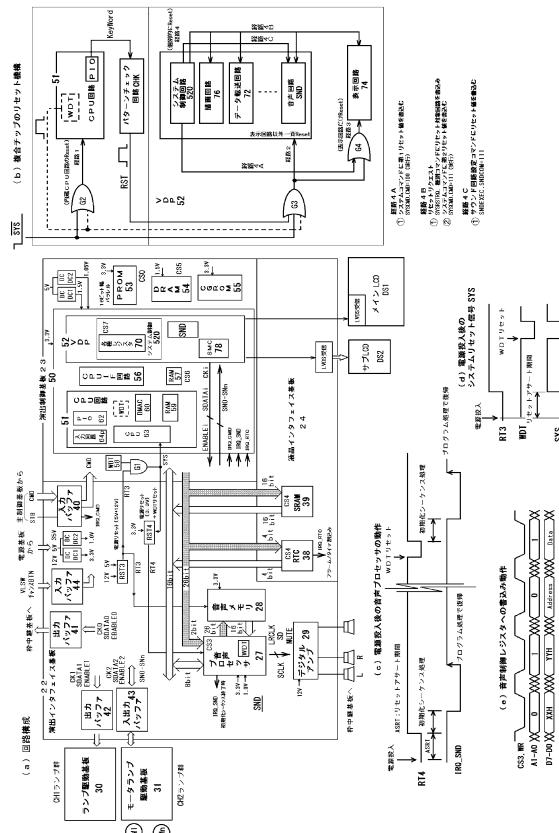

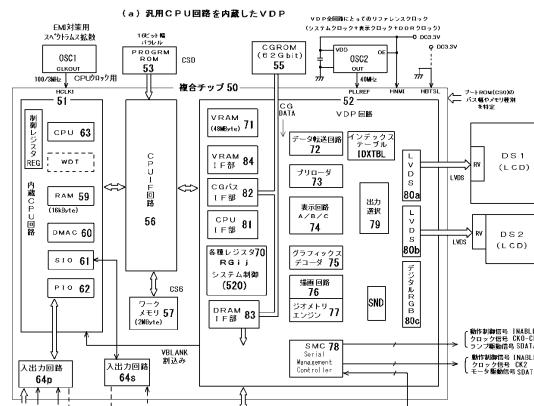

【図4】図1の遊技機について、演出制御部の回路構成をやや詳細に示すブロック図である。

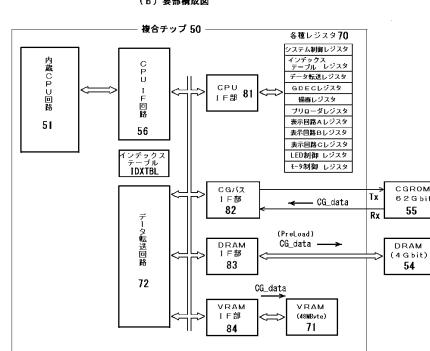

【図5】演出制御部を構成する複合チップを説明する図面である。

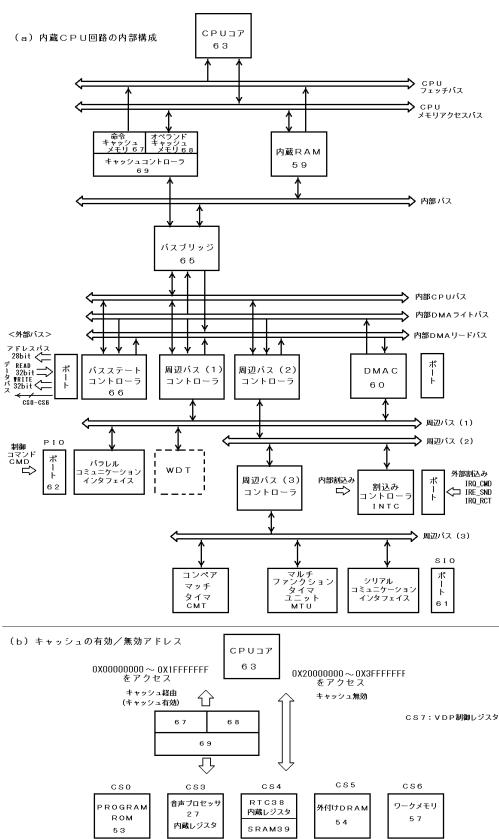

【図6】図4に示すC P U回路の内部構成を示すブロック図である。

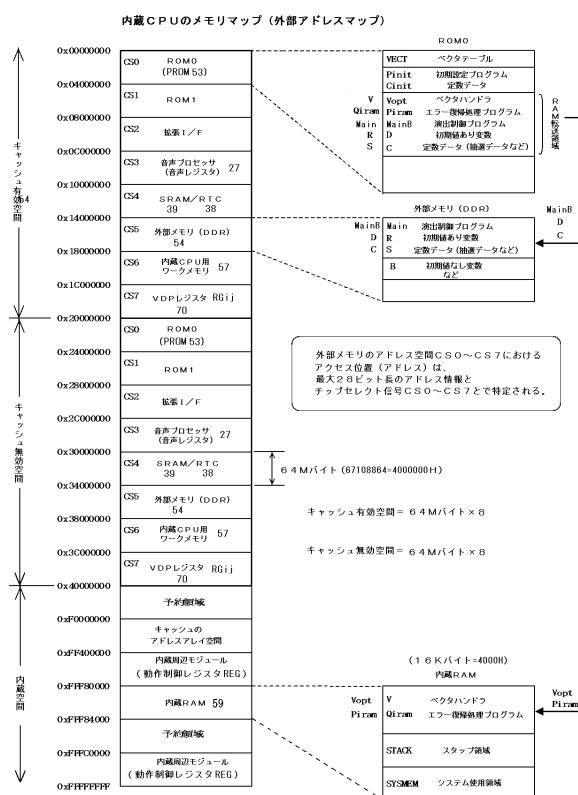

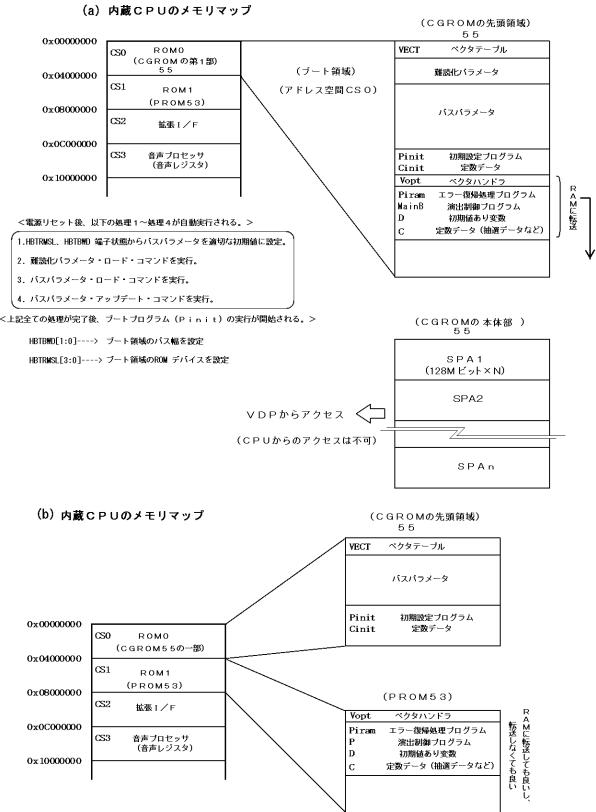

【図7】C P U回路の内蔵C P U(演出制御C P U)のメモリマップを図示したものである。

20

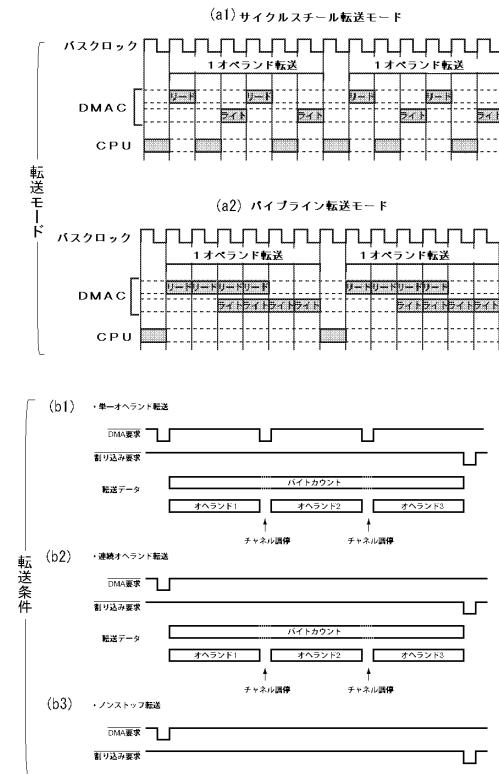

【図8】D M A Cについて、各種の転送動作モード(a)～(b)と、転送動作手順(c)～(e)を説明する図面である。

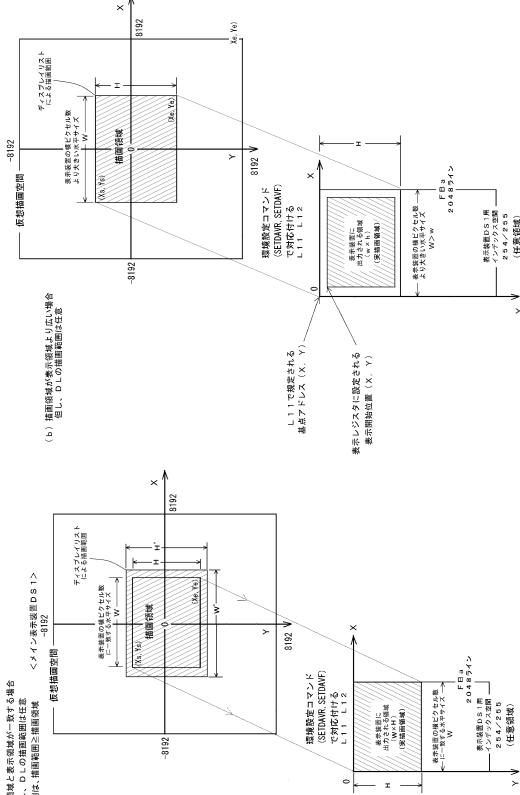

【図9】インデックス空間、インデックステーブル、仮想描画空間、及び、描画領域について説明する図面である。

【図10】データ転送回路の内部構成を、関連する回路構成と共に記載したブロック図である。

【図11】表示回路の内部構成を、関連する回路構成と共に記載したブロック図である。

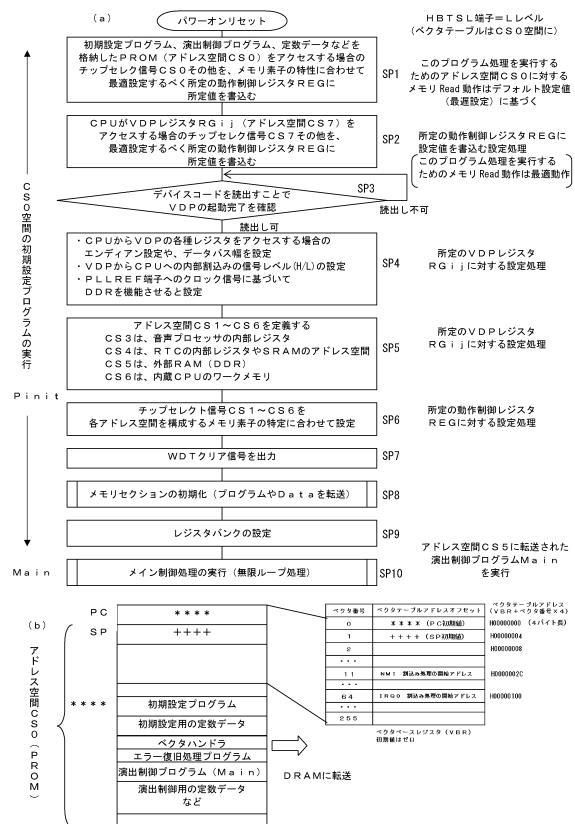

【図12】C P Uリセット後のパワーリセット動作を説明するフローチャートである。

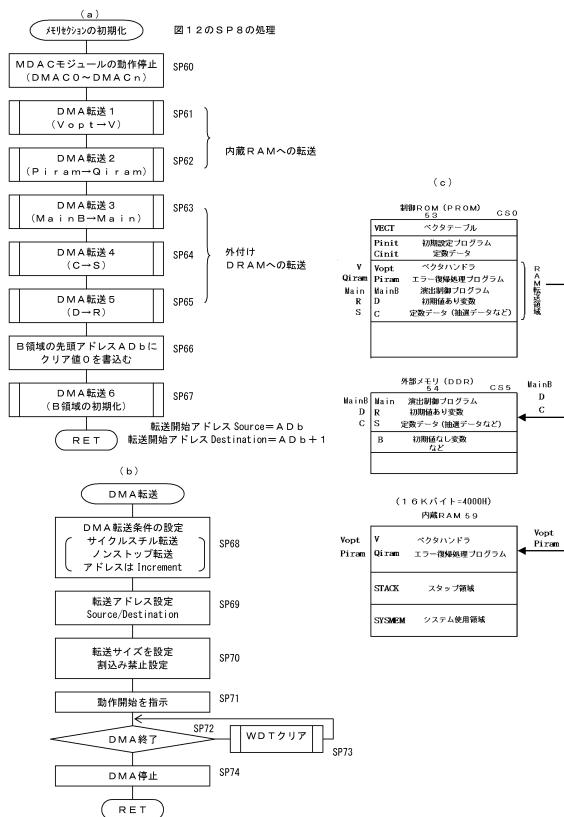

【図13】図12の一部であるメモリセクション初期化処理を説明するフローチャートである。

30

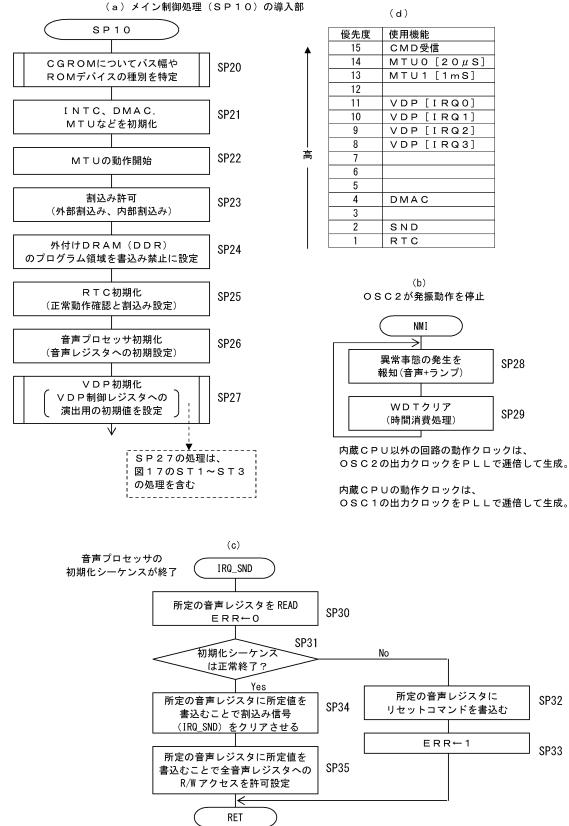

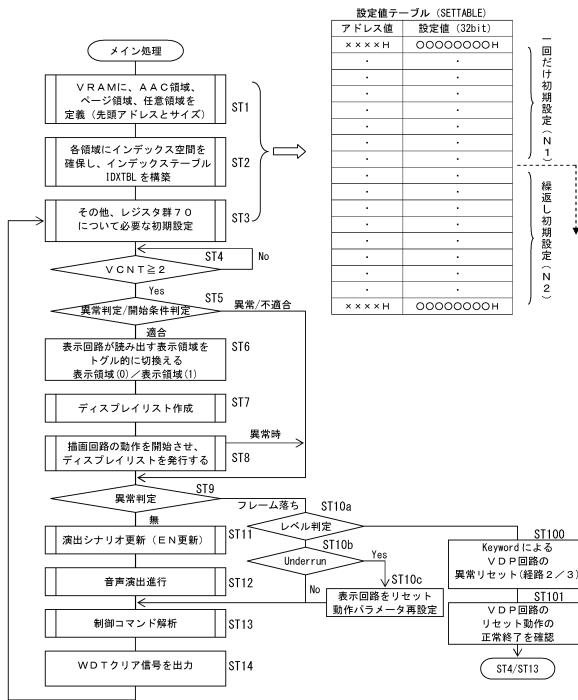

【図14】図12の一部であるメイン制御処理と、割込み処理を説明するフローチャートである。

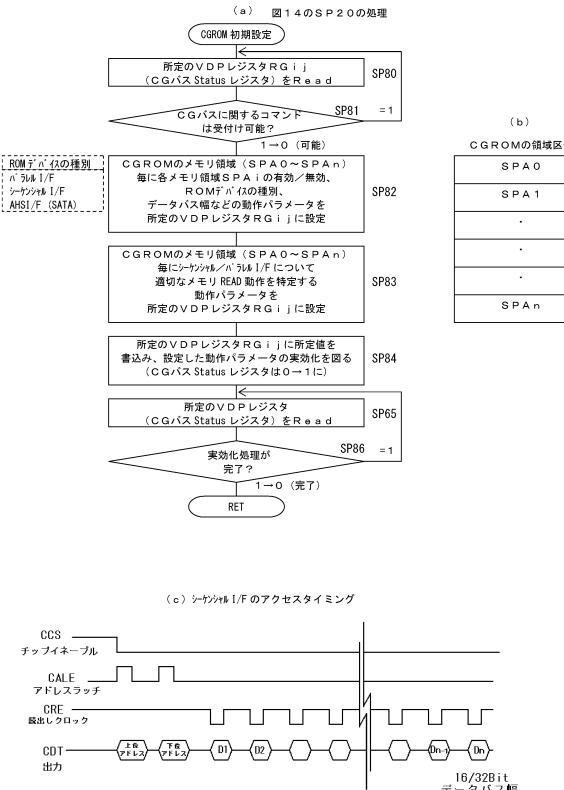

【図15】メイン制御処理の一部であるC G R O Mの初期化処理を説明するフローチャートである。

【図16】別の割込み処理について、処理内容の一部を説明するフローチャートである。

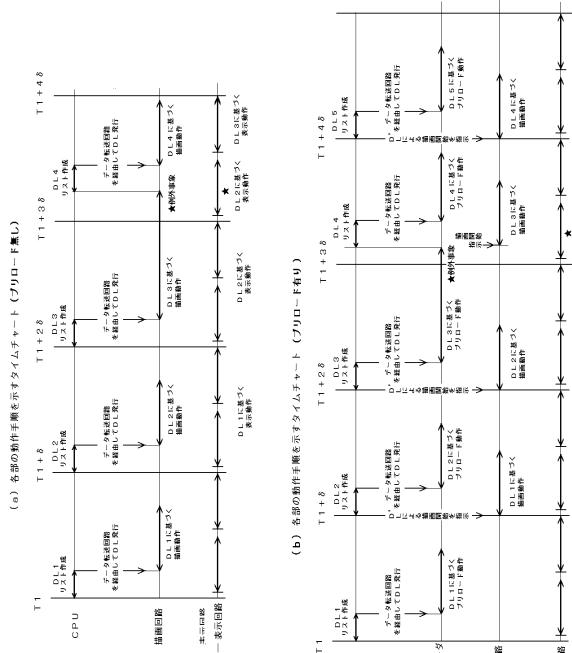

【図17】プリローダを使用しない場合について、演出制御C P U 63の制御動作を説明するフローチャートである。

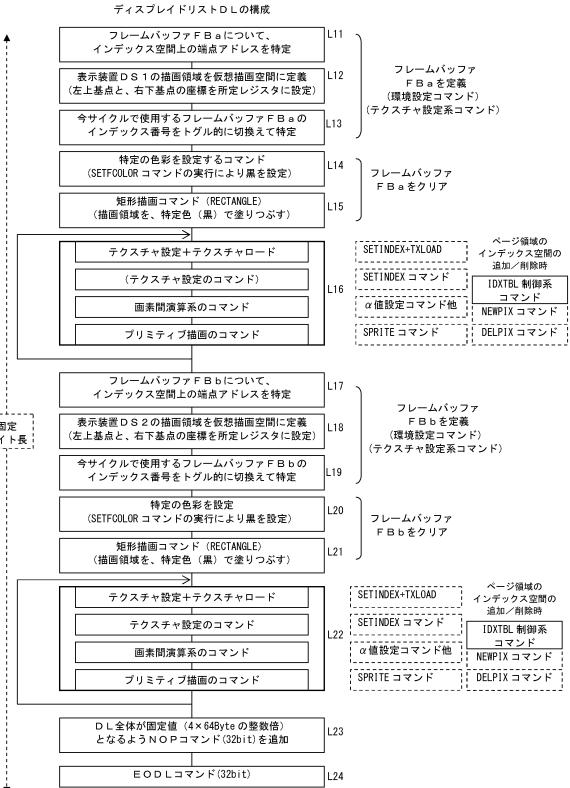

【図18】ディスプレイリストの構成を説明する図面である。

【図19】ディスプレイリストD Lを発行するD L発行処理を示すフローチャートである。

40

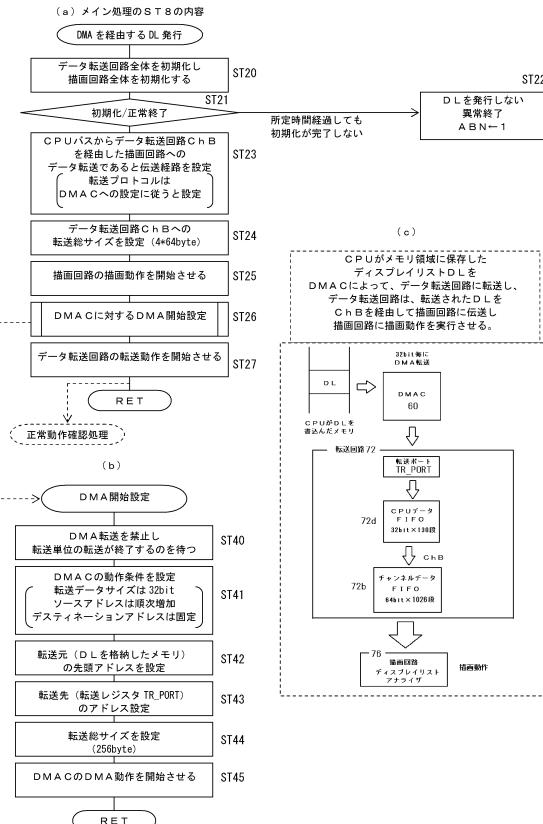

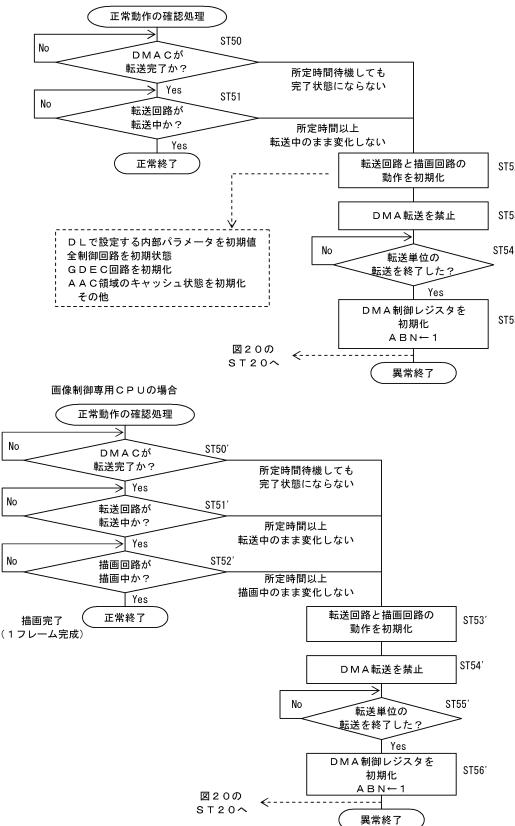

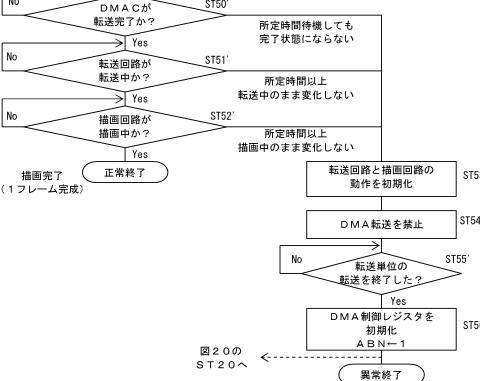

【図20】図19の動作にD M A Cが関与する場合の動作を説明するフローチャートである。

【図21】図20の処理に続く動作を説明するフローチャートである。

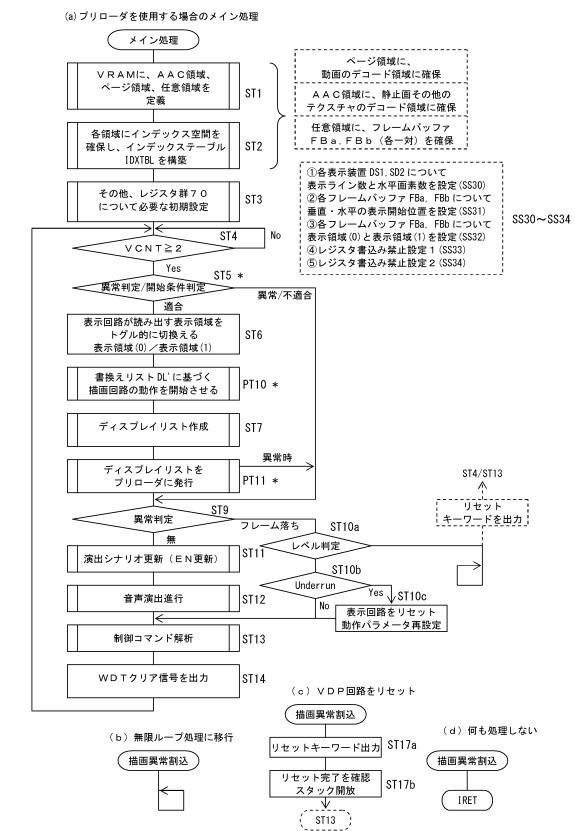

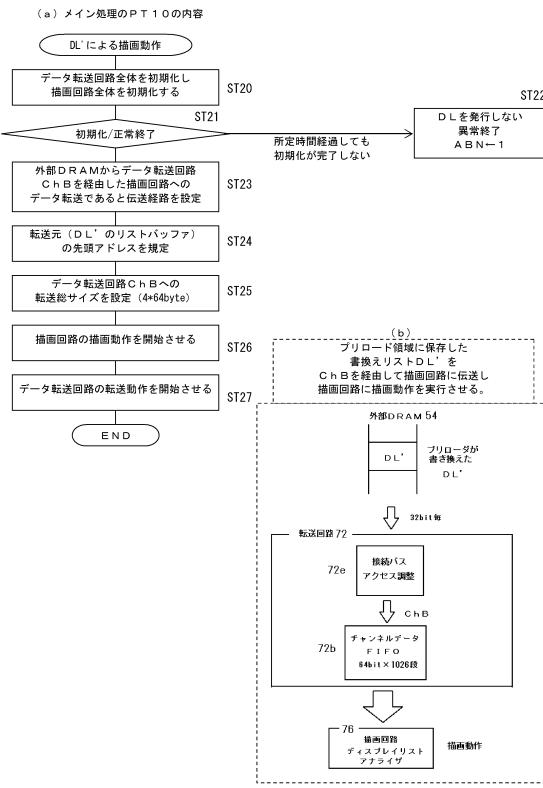

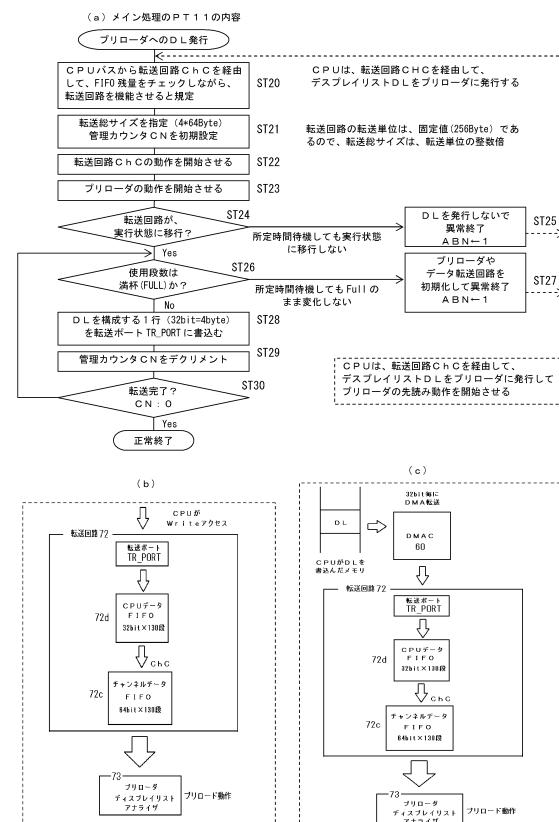

【図22】プリローダを使用する場合について、演出制御C P U 63の制御動作を説明するフローチャートである。

【図23】図22の一部を説明するフローチャートである。

【図24】図22の別の一部を説明するフローチャートである。

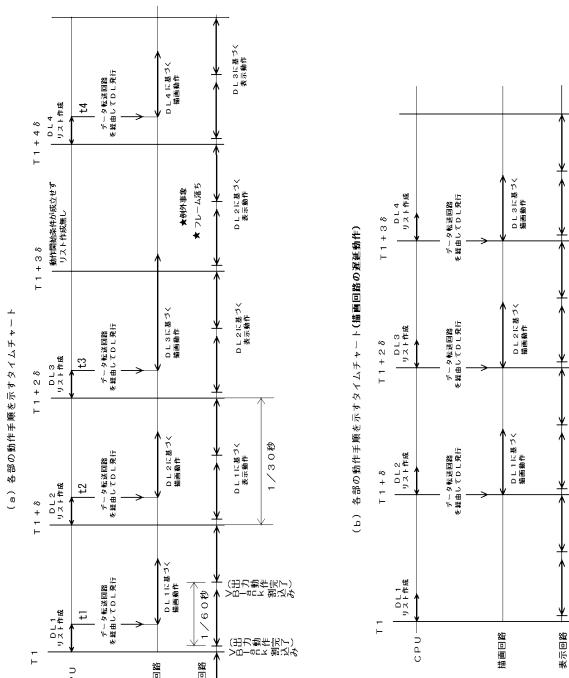

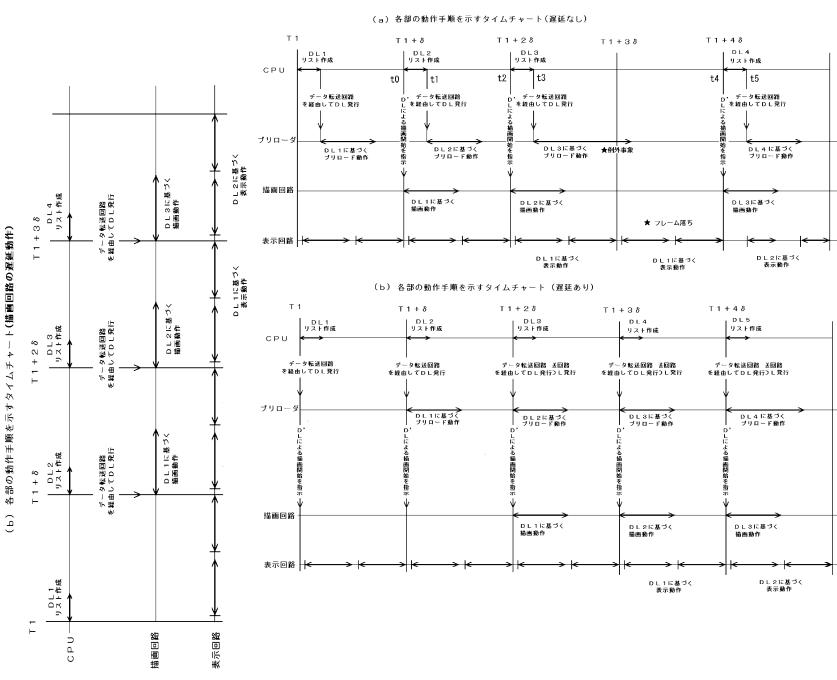

【図25】プリローダを使用しない実施例について、V D P各部の動作を示すタイムチャートである。

【図26】プリローダを使用する実施例について、V D P各部の動作を示すタイムチャートである。

50

トである。

【図27】別の実施例について全体回路構成を示すブロック図である。

【図28】図27の一部をやや詳細に示すブロック図である。

【図29】別の実施例について、動作内容を説明するフローチャートである。

【図30】更に別の実施例を説明する図面である。

【図31】設定値を繰り返し設定する実施例を説明する図面である。

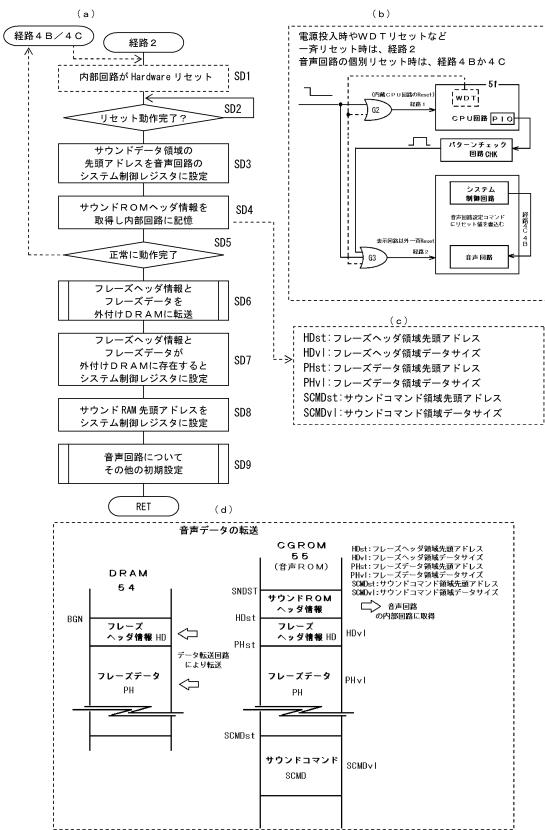

【図32】内蔵された音声回路を使用する実施例の回路構成を説明する図面である。

【図33】音声回路の初期設定動作を説明するフローチャートである。

【図34】CPUリセット後のパワーリセット動作について別の実施例を説明する図面である。

10

【図35】メモリREAD動作とメモリWRITE動作の一例を示すタイムチャートである。

【発明を実施するための形態】

【0010】

以下、実施例に基づいて本発明を詳細に説明する。図1は、本実施例のパチンコ機GMを示す斜視図である。このパチンコ機GMは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく、表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。

【0011】

ガラス扉6の外周には、LEDランプなどによる電飾ランプが、略C字状に配置されている。一方、ガラス扉6の上部左右位置と下側には、全3個のスピーカが配置されている。上部に配置された2個のスピーカは、各々、左右チャンネルR,Lの音声を出力し、下側のスピーカは低音を出力するよう構成されている。

20

【0012】

前面板7には、発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。

【0013】

上皿8の外周面には、チャンスボタン11が設けられている。このチャンスボタン11は、遊技者の左手で操作できる位置に設けられており、遊技者は、発射ハンドル10から右手を離すことなくチャンスボタン11を操作できる。このチャンスボタン11は、通常時には機能していないが、ゲーム状態がボタンチャンス状態となると内蔵ランプが点灯されて操作可能となる。なお、ボタンチャンス状態は、必要に応じて設けられるゲーム状態である。

30

【0014】

また、チャンスボタン11の下方には、ロータリースイッチ型の音量スイッチVLSWが配置されており、遊技者が音量スイッチVLSWを操作することで、無音レベル(=0)から最高レベル(=7)まで、スピーカ音量を8段階に調整できるようになっている。なお、スピーカの音量は、係員だけが操作可能な設定スイッチ(不図示)によって初期設定されており、遊技者が音量スイッチVLSWを操作しない限り、初期設定音量が維持される。また、異常事態が発生したことを報知する異常報知音は、係員による初期設定音量や、遊技者の設定音量に拘らず最高音量で放音される。

40

【0015】

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設けられている。

【0016】

図2に示すように、遊技盤5の表面には、金属製の外レールと内レールとからなるガイド

50

レール 1 3 が環状に設けられ、その略中央には、中央開口 H O が設けられている。そして、中央開口 H O の下方には、不図示の可動演出体が隠蔽状態で収納されており、可動予告演出時には、その可動演出体が上昇して露出状態となることで、所定の信頼度の予告演出を実現している。ここで、予告演出とは、遊技者に有利な大当たり状態が招来することを不確定に報知する演出であり、予告演出の信頼度とは、大当たり状態が招来する確率を意味している。

#### 【 0 0 1 7 】

中央開口 H O には、大型（例えば、横 1 2 8 0 × 縦 1 0 2 4 ピクセル）の液晶カラーディスプレイ（LCD）で構成されたメイン表示装置 D S 1 が配置され、メイン表示装置 D S 1 の右側には、小型（例えば、横 4 8 0 × 縦 8 0 0 ピクセル）の液晶カラーディスプレイで構成された可動式のサブ表示装置 D S 2 が配置されている。メイン表示装置 D S 1 は、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に表示する装置である。この表示装置 D S 1 は、中央部に特別図柄表示部 D a ~ D c と右上部に普通図柄表示部 1 9 とを有している。そして、特別図柄表示部 D a ~ D c では、大当たり状態の招来を期待させるリーチ演出が実行されることがあり、特別図柄表示部 D a ~ D c 及びその周りでは、適宜な予告演出などが実行される。

10

#### 【 0 0 1 8 】

サブ表示装置 D S 2 は、通常時には、その表示画面が遊技者に見やすい角度に傾斜した静止状態で画像情報を表示している。但し、所定の予告演出時には、遊技者に見やすい角度に傾斜角度を変えながら、図示の左側に移動する共に、所定の予告画像を表示するようになっている。

20

#### 【 0 0 1 9 】

すなわち、実施例のサブ表示装置 D S 2 は、単なる表示装置ではなく、予告演出を実行する可動演出体としても機能している。ここで、サブ表示装置 D S 2 による予告演出は、その信頼度が高く設定されており、遊技者は、大きな期待感をもってサブ表示装置 D S 2 の移動動作に注目することになる。

#### 【 0 0 2 0 】

ところで、遊技球が落下移動する遊技領域には、第 1 図柄始動口 1 5 a、第 2 図柄始動口 1 5 b、第 1 大入賞口 1 6 a、第 2 大入賞口 1 6 b、普通入賞口 1 7、及び、ゲート 1 8 が配設されている。これらの入賞口 1 5 ~ 1 8 は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。

30

#### 【 0 0 2 1 】

第 1 図柄始動口 1 5 a の上部には、導入口 I N から進入した遊技球がシーソー状又はルーレット状に移動した後に、第 1 図柄始動口 1 5 に入賞可能に構成された演出ステージ 1 4 が配置されている。そして、第 1 図柄始動口 1 5 に遊技球が入賞すると、特別図柄表示部 D a ~ D c の変動動作が開始されるよう構成されている。

#### 【 0 0 2 2 】

第 2 図柄始動口 1 5 b は、左右一対の開閉爪を備えた電動式チューリップで開閉されるよう構成され、普通図柄表示部 1 9 の変動後の停止図柄が当り図柄を表示した場合には、所定時間だけ、若しくは、所定個数の遊技球を検出するまで、開閉爪が開放されるようになっている。

40

#### 【 0 0 2 3 】

なお、普通図柄表示部 1 9 は、普通図柄を表示するものであり、ゲート 1 8 を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート 1 8 の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止する。

#### 【 0 0 2 4 】

第 1 大入賞口 1 6 a は、前後方向に進退するスライド盤を有して構成され、第 2 大入賞口 1 6 b は、下端が軸支されて前方に開放する開閉板を有して構成されている。第 1 大入賞口 1 6 a や第 2 大入賞口 1 6 b の動作は、特に限定されないが、この実施例では、第 1 大入賞口 1 6 a は、第 1 図柄始動口 1 5 a に対応し、第 2 大入賞口 1 6 b は、第 1 図柄始動

50

□ 15 b に対応するよう構成されている。

【 0 0 2 5 】

すなわち、第1図柄始動□15 a に遊技球が入賞すると、特別図柄表示部 D a ~ D c の変動動作が開始され、その後、所定の大当り図柄が特別図柄表示部 D a ~ D c に整列すると、第1大当りたる特別遊技が開始され、第1大入賞□16 a のスライド盤が、前方に開放されて遊技球の入賞が容易化される。

【 0 0 2 6 】

一方、第2図柄始動□15 b への遊技球の入賞によって開始された変動動作の結果、所定の大当り図柄が特別図柄表示部 D a ~ D c に整列すると、第2大当りたる特別遊技が開始され、第2大入賞□16 b の開閉板が開放されて遊技球の入賞が容易化される。特別遊技（大当り状態）の遊技価値は、整列する大当り図柄などに対応して種々相違するが、何れの遊技価値が付与されるかは、遊技球の入賞タイミングに応じた抽選結果に基づいて予め決定される。

10

【 0 0 2 7 】

典型的な大当り状態では、大入賞□16 の開閉板が開放された後、所定時間が経過し、又は所定数（例えば10個）の遊技球が入賞すると開閉板が閉じる。このような動作は、最大で例えば15回まで継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部 D a ~ D c の変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別遊技の終了後のゲームが高確率状態（確変状態）となるという特典が付与される。

【 0 0 2 8 】

20

図3は、上記した各動作を実現するパチンコ機GMの全体回路構成を示すブロック図であり、図4(a)はその一部を詳細に図示したものである。

【 0 0 2 9 】

図3に示す通り、このパチンコ機GMは、AC24Vを受けて各種の直流電圧や、電源異常信号ABN1、ABN2を出力する電源基板20と、遊技制御動作を中心統括的に担う主制御基板21と、音声演出用の回路素子 SND を搭載した演出インタフェイス基板22と、主制御基板21から受けた制御コマンドCMDに基づいてランプ演出、音声演出、及び画像演出を統一的に実行する演出制御基板23と、演出制御基板23と表示装置DS1, DS2の間に位置する液晶インタフェイス基板24と、主制御基板21から受けた制御コマンドCMD'に基づいて払出モータMを制御して遊技球を払い出す払出制御基板25と、遊技者の操作に応答して遊技球を発射させる発射制御基板26と、を中心に構成されている。

30

【 0 0 3 0 】

本実施例の場合、演出インタフェイス基板22と、演出制御基板23と、液晶インタフェイス基板24とは、配線ケーブルを経由することなく、雄型コネクタと雌型コネクタとを直結されている。そのため、各電子回路の回路構成を複雑高度化しても基板全体の収納空間を最小化できると共に、接続ラインを最短化することで耐ノイズ性を高めることができる。

【 0 0 3 1 】

40

図示の通り、主制御基板21が出力する制御コマンドCMD'は、主基板中継基板33を経由して、払出制御基板25に伝送される。一方、主制御基板21が出力する制御コマンドCMDは、演出インタフェイス基板22を経由して演出制御基板23に伝送される。制御コマンドCMD, CMD'は、何れも16bit長であるが、8bit長毎に2回に分けてパラレル送信される。

【 0 0 3 2 】

主制御基板21と払出制御基板25には、ワンチップマイコンを含むコンピュータ回路が搭載されている。また、演出制御基板23には、VDP回路（Video Display Processor）52や内蔵CPU回路51などのコンピュータ回路が内蔵された複合チップ50が搭載されている。そこで、これらの制御基板21, 25, 23と、演出インタフェイス基板22や液晶インタフェイス基板24に搭載された回路、及びその回路によって実現される動

50

作を機能的に総称して、本明細書では、主制御部21、演出制御部23、及び払出制御部25と言うことがある。なお、主制御部21に対して、演出制御部23と、払出制御部25がサブ制御部となる。

#### 【0033】

また、このパチンコ機GMは、図3の破線で囲む枠側部材GM1と、遊技盤5の背面に固定された盤側部材GM2とに大別されている。枠側部材GM1には、ガラス扉6や前面板7が枢着された前枠3と、その外側の木製外枠1とが含まれており、機種の変更に拘わらず、長期間にわたって遊技ホールに固定的に設置される。一方、盤側部材GM2は、機種変更に対応して交換され、新たな盤側部材GM2が、元の盤側部材の代わりに枠側部材GM1に取り付けられる。なお、枠側部材1を除く全てが、盤側部材GM2である。

10

#### 【0034】

図3の破線枠に示す通り、枠側部材GM1には、電源基板20と、払出制御基板25と、発射制御基板26と、枠中継基板36とが含まれており、これらの回路基板が、前枠3の適所に各々固定されている。一方、遊技盤5の背面には、主制御基板21、演出制御基板23が、表示装置DS1, DS2やその他の回路基板と共に固定されている。そして、枠側部材GM1と盤側部材GM2とは、一箇所に集中配置された接続コネクタC1~C4によって電気的に接続されている。

#### 【0035】

電源基板20は、接続コネクタC2を通して、主基板中継基板33に接続され、接続コネクタC3を通して、電源中継基板34に接続されている。そして、電源基板20には、交流電源の投入と遮断とを監視する電源監視部MNTが設けられている。電源監視部MNTは、交流電源の遮断を検知すると、電源異常信号ABN1, ABN2を、直ちにLレベルに遷移させる。なお、電源異常信号ABN1, ABN2は、電源投入後に速やかにHレベルとなる。

20

#### 【0036】

主基板中継基板33は、電源基板20から出力される電源異常信号ABN1、バックアップ電源BAK、及びDC5V, DC12V, DC35Vを、そのまま主制御部21に出力している。また、電源中継基板34は、電源基板20から受けた交流及び直流の電源電圧DC5V, DC12V, DC35Vを、そのまま演出インターフェイス基板22に出力している。

30

#### 【0037】

図示の通り、演出インターフェイス基板22には、音声プロセッサ27などの音声回路SN-Dが搭載され、演出制御基板23には、VDP回路52や内蔵CPU回路51などのコンピュータ回路が内蔵された複合チップ50が搭載されている。以下、内蔵CPU回路をCPU回路と略称することがある。

#### 【0038】

演出インターフェイス基板22には、電源投入時に、電源電圧の上昇を検知して各種のリセット信号RT3, RT4を生成するリセット回路RST3, RST4が搭載されている。先ず、リセット回路RST3は、電源基板20から配電された直流電圧12Vと5Vに基づいて、リセット信号RT3を生成している。そして、リセット信号RT3は、音声メモリ28だけを電源リセットして、そのまま演出制御基板23に伝送される。

40

#### 【0039】

演出制御基板23に伝送されたリセット信号RT3は、図4(a)に示す通り、ANDゲートG1において、WDT(Watch Dog Timer)回路58の出力とAND演算され、システムリセット信号SYSとして、CPU回路51やVDP回路52を電源リセットしている(図4(a)及び図4(d)参照)。

#### 【0040】

リセット回路RST3が生成するリセット信号RT3は、電源投入後、電源リセット信号として所定時間Lレベルを維持した後、Hレベルに上昇する。しかし、その後、直流電圧12V又は直流電圧5Vの何れか一以上が降下した場合(通常は電源遮断時)には、リセ

50

ット信号 R T 3 のレベル降下に対応して、システムリセット信号 S Y S も L レベルに降下するので、演出制御基板 2 3 の C P U 回路 5 1 と V D P 回路 5 2 は動作停止状態となる。

【 0 0 4 1 】

このシステムリセット信号 S Y S は、W D T 回路 5 8 の出力（正常時には H レベル）に基づいても変化するので、リセット信号 R T 3 = H の状態で、プログラム暴走時などに起因して、W D T 回路 5 8 の出力が L レベルに降下することに対応して、システムリセット信号 S Y S も L レベルに変化して、C P U 回路 5 1 や V D P 回路 5 2 を異常リセットする（図 4 ( d ) 参照）。

【 0 0 4 2 】

一方、リセット回路 R S T 4 は、電源基板 2 0 から配電された 5 V を降下して生成された 3 . 3 V に基づいて、リセット信号 R T 4 を生成している。このリセット信号 R T 4 は、電源投入時の電源リセット信号として、音声プロセッサ 2 7 を電源リセットしている。

10

【 0 0 4 3 】

図示の通り、リセット回路 R S T 4 には、演出制御基板 2 3 から返送されたシステムリセット信号 S Y S も供給されているので、C P U 回路 5 1 や V D P 回路 5 2 の異常リセット時には、これらの回路の異常リセットに同期して、音声プロセッサ 2 7 も異常リセットされる。この結果、音声演出は、画像演出やランプ演出と共に初期状態に戻ることになり、不自然な音声演出が継続するおそれがない。

【 0 0 4 4 】

次に、枠側部材 G M 1 たる払出制御基板 2 5 は、中継基板を介することなく、電源基板 2 0 に直結されて、主制御部 2 1 が受けると同様の電源異常信号 A B N 2 や、バックアップ電源 B A K を、その他の電源電圧と共に受けている。また、主制御部 2 1 と払出制御部 2 5 には、各々、リセット回路 R S T 1 , R S T 2 が搭載されており、電源投入時に電源リセット信号が生成され、各コンピュータ回路が電源リセットされるよう構成されている。

20

【 0 0 4 5 】

このように、本実施例では、主制御部 2 1 と、払出制御部 2 5 と、演出インターフェイス基板 2 2 に、各々、リセット回路 R S T 1 ~ R S T 4 を配置しており、システムリセット信号 S Y S が回路基板間で伝送されることがない。すなわち、システムリセット信号 S Y S を伝送する配線ケーブルが存在しないので、配線ケーブルに重畳するノイズによって、コンピュータ回路が異常リセットされるおそれが解消される。

30

【 0 0 4 6 】

但し、主制御部 2 1 や払出制御部 2 5 に設けられたリセット回路 R S T 1 , R S T 2 は、各々ウォッチドッグタイマを内蔵しており、各制御部 2 1 , 2 5 の C P U から、定時的なクリアパルスを受けない場合には、各 C P U は強制的にリセットされる。

【 0 0 4 7 】

また、主制御部 2 1 には、係員が操作可能な初期化スイッチ S W が配置されており、電源投入時、初期化スイッチ S W が O N 操作されたか否かを示す R A M クリア信号 C L R が出力されるよう構成されている。この R A M クリア信号 C L R は、主制御部 2 1 と払出制御部 2 5 のワンチップマイコンに伝送され、各制御部 2 1 , 2 5 のワンチップマイコンの内蔵 R A M の全領域を初期設定するか否かを決定している。

40

【 0 0 4 8 】

また、主制御部 2 1 及び払出制御部 2 5 は、電源基板 2 0 から電源異常信号 A B N 1 , A B N 2 を受けることによって、停電や営業終了に先立って、必要な終了処理を開始するようになっている。また、バックアップ電源 B A K は、営業終了や停電により交流電源 2 4 V が遮断された後も、主制御部 2 1 と払出制御部 2 5 のワンチップマイコンの内蔵 R A M のデータを保持する D C 5 V の直流電源である。したがって、主制御部 2 1 と払出制御部 2 5 は、電源遮断前の遊技動作を電源投入後に再開できることになる（電源バックアップ機能）。このパチンコ機では少なくとも数日は、各ワンチップマイコンの R A M の記憶内容が保持されるよう設計されている。

【 0 0 4 9 】

50

図3に示す通り、主制御部21は、払出制御部25から、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号CONや、動作開始信号BGNを受信している。ステータス信号CONには、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。動作開始信号BGNは、電源投入後、払出制御部25の初期動作が完了したことを主制御部21に通知する信号である。

#### 【0050】

また、主制御部21は、遊技盤中継基板32を経由して、遊技盤5の各遊技部品に接続されている。そして、遊技盤上の各入賞口16～18に内蔵された検出スイッチのスイッチ信号を受ける一方、電動式チューリップなどのソレノイド類を駆動している。ソレノイド類や検出スイッチは、主制御部21から配電された電源電圧VB(12V)で動作するよう構成されている。また、図柄始動口15への入賞状態などを示す各スイッチ信号は、電源電圧VB(12V)と電源電圧Vcc(5V)とで動作するインタフェイスICで、TTLレベル又はCMOSレベルのスイッチ信号に変換された上で、主制御部21に伝送される。

10

#### 【0051】

先に説明した通り、演出インタフェイス基板22と演出制御基板23と液晶インタフェイス基板24とはコネクタ連結によって一体化されており、演出インタフェイス基板22は、電源中継基板34を経由して、電源基板20から各レベルの直流電圧(5V, 12V, 35V)を受けている(図3及び図4(a)参照)。直流電圧12Vは、デジタルアンプ29の電源電圧であると共に、LEDランプなどの駆動電圧として使用される。また、直流電圧35Vは、モータの駆動電圧として使用される。

20

#### 【0052】

一方、直流電圧5Vは、演出インタフェイス基板22各所の回路素子の電源電圧として供給されると共に、2つのDC/DCコンバータDC1, DC2に供給されて3.3Vと1.0Vが生成される(図4(a)参照)。生成された直流電圧3.3Vと1.0Vは、各自、I/O(入出力)用と、チップコア用の電源電圧として音声プロセッサ27に供給される。また、直流電圧3.3Vは、リセット回路\_RST4が生成する電源リセット信号RT4の基礎電圧となる。

#### 【0053】

演出インタフェイス基板22に配電された直流電圧5Vは、DC/DCコンバータDC1で生成された3.3Vと共に、演出制御基板23に配電される。そして、演出制御基板23に配電された直流電圧3.3Vは、電源電圧として、複合チップ50や、PROM53及びROM55に供給される。

30

#### 【0054】

図4(a)に示す通り、演出制御基板23には、2つのDC/DCコンバータDC3, DC4が配置されており、各自に供給される直流電圧5Vに基づいて、1.5Vと1.05Vを生成している。ここで、直流電圧1.05Vは、複合チップ50のチップコア用の電源電圧であり、直流電圧1.5Vは、DRAM54とのI/O(入出力)用の電源電圧である。したがって、直流電圧1.5Vは、電源電圧として、DRAM54にも供給される。

40

#### 【0055】

図3に示す通り、演出インタフェイス基板22は、主制御部21から制御コマンドCMDとストローブ信号STBとを受けて、演出制御基板23に転送している。より詳細には、図4(a)に示す通りであり、制御コマンドCMDとストローブ信号STBは、入力バッファ40を経由して、演出制御基板23の複合チップ50(CPU回路51)に転送される。ここで、ストローブ信号STBは、受信割込み信号IRQ\_CMDであり、演出制御CPU63は、受信割込み信号IRQ\_CMDを受けて起動される割込み処理プログラム(割込みハンドラ)に基づいて、制御コマンドCMDを取得している。

#### 【0056】

図4(a)に示す通り、演出インタフェイス基板22の入力バッファ44は、枠中継基板35, 36からチャンスボタン11や音量スイッチVLSWのスイッチ信号を受け、各ス

50

イッチ信号を演出制御基板 23 の C P U 回路 51 に伝送している。具体的には、音量スイッチ V L S W の接点位置 (0 ~ 7) を示すエンコーダ出力の 3 b i t 長と、チャンスボタン 11 の O N / O F F 状態を示す 1 b i t 長を C P U 回路 51 に伝送している。

#### 【 0 0 5 7 】

また、演出インタフェイス基板 22 には、ランプ駆動基板 30 やモータランプ駆動基板 31 が接続されると共に、枠中継基板 35, 36 を経由して、ランプ駆動基板 37 にも接続されている。図示の通り、ランプ駆動基板 30 に対応して、出力バッファ 42 が配置され、モータランプ駆動基板 31 に対応して、入力バッファ 43a と出力バッファ 43b が配置されている。なお、図 4 (a) では、便宜上、入力バッファ 43a と出力バッファ 43b を総称して、入出力バッファ 43 と記載している。入力バッファ 43a は、可動演出体たる役物の現在位置 (演出モータ M1 ~ Mn の回転位置) を把握する原点センサの出力 S N0 ~ S Nn を受けて、演出制御基板 23 の C P U 回路 51 に伝送している。

10

#### 【 0 0 5 8 】

ランプ駆動基板 30、モータランプ駆動基板 31、及び、ランプ駆動基板 37 には、同種のドライバ I C が搭載されており、演出インタフェイス基板 22 は、演出制御基板 23 から受けるシリアル信号を、各ドライバ I C に転送している。シリアル信号は、具体的には、ランプ (モータ) 駆動信号 S D A T A とクロック信号 C K であり、駆動信号 S D A T A がクロック同期方式で各ドライバ I C に伝送され、多数の L E D ランプや電飾ランプによるランプ演出や、演出モータ M1 ~ Mn による役物演出が実行される。

20

#### 【 0 0 5 9 】

本実施例の場合、ランプ演出は、三系統のランプ群 C H 0 ~ C H 2 によって実行されており、ランプ駆動基板 37 は、枠中継基板 35, 36 を経由して、C H 0 のランプ駆動信号 S D A T A 0 を、クロック信号 C K 0 に同期して受けている。なお、シリアル信号として伝送される一連のランプ駆動信号 S D A T A 0 は、動作制御信号 E N A B L E 0 がアクティブルーレベルに変化したタイミングで、ドライバ I C からランプ群 C H 0 に出力されることで一斉に点灯状態が更新される。

#### 【 0 0 6 0 】

以上の点は、ランプ駆動基板 30 についても同様であり、ランプ駆動基板 30 のドライバ I C は、ランプ群 C H 1 のランプ駆動信号 S D A T A 1 を、クロック信号 C K 1 に同期して受け、動作制御信号 E N A B L E 1 がアクティブルーレベルに変化したタイミングで、ランプ群 C H 1 の点灯状態を一斉に更新している。

30

#### 【 0 0 6 1 】

一方、モータランプ駆動基板 31 に搭載されたドライバ I C は、クロック同期式で伝送されるランプ駆動信号を受けてランプ群 C H 2 を駆動すると共に、クロック同期式で伝送されるモータ駆動信号を受けて、複数のステッピングモータで構成された演出モータ群 M1 ~ Mn を駆動している。なお、ランプ駆動信号とモータ駆動信号は、一連のシリアル信号 S D A T A 2 であって、クロック信号 C K 1 に同期してシリアル伝送され、これを受けたドライバ I C は、動作制御信号 E N A B L E 2 がアクティブルーレベルに変化するタイミングで、ランプ群 C H 2 やモータ群 M1 ~ Mn の駆動状態を更新する。

40

#### 【 0 0 6 2 】

続いて、音声回路 S N D について説明する。図 4 (a) に示す通り、演出インタフェイス基板 22 には、演出制御基板 23 の C P U 回路 51 (演出制御 C P U 63) から受ける指示に基づいて音声信号を再生する音声プロセッサ (音声合成回路) 27 と、再生される音声信号の元データである圧縮音声データなどを記憶する音声メモリ 28 と、音声プロセッサ 27 から出力される音声信号を受けるデジタルアンプ 29 と、が搭載されている。

#### 【 0 0 6 3 】

音声プロセッサ 27 は、内部回路の異常動作時に、内部回路の設定値を自動的にデフォルト値 (初期値) にリセットする W D T 回路と、音声制御レジスタ S R G とを内蔵して構成されている。そして、音声プロセッサ 27 は、演出制御 C P U 63 から音声制御レジスタ S R G に受ける動作パラメータ (音声コマンドによる設定値) に基づいて、音声メモリ 2

50

8をアクセスして、必要な音声信号を再生して出力している。

【0064】

図4(a)に示す通り、音声プロセッサ27と、音声メモリ28とは、26bit長の音声アドレスバスと、16bit長の音声データバスで接続されている。そのため、音声メモリ28には、1Gbit(=2<sup>26</sup>\*16)のデータが記憶可能となる。

【0065】

音声制御レジスタSRGは、レジスタバンク1～レジスタバンク6に区分され、各々、00H～FFHのレジスタ番号で特定される。したがって、所定の設定動作は、レジスタバンクを特定した上で、演出制御CPU63が、所定のレジスタ番号(1バイト長)の音声制御レジスタSRGに、1バイト長の動作パラメータを書込むことで実現される。

10

【0066】

本実施例の場合、音声制御レジスタSRGのレジスタ番号(00H～FFH)は、演出制御CPU63のアドレス空間CS3に対応しており、例えば、レジスタ番号XXHの音声制御レジスタSRGに、動作パラメータYYHを設定する場合には、演出制御CPU63は、アドレス空間CS3のゼロ番地にXXHを書込み、次に、1番地にYYHを書込むことになる。すなわち、演出制御CPU63は、そのデータバスにXXHとYYHを、この順番に書き出すことになる。なお、本明細書において、添え字Hや、0X/0xの接頭記号は、数値が16進数表示であることを示している。

【0067】

また、本明細書において、アドレス空間CS0～CS7とは、揮発性の有無を含むメモリ種別や、データバス幅(8/16/32ビット)を、各々、規定可能なCPU回路51にとって外部メモリを意味する(内蔵メモリを除く)。このアドレス空間CS0～CS7は、異なるチップセレクト信号CS0～CS7で選択され、READ/WRITEアクセス時に機能するREAD/WRITE制御信号がメモリ種別に対応して最適化できるよう設定可能に構成されている。なお、この設定動作は、バスステートコントローラ66に対して実行される。

20

【0068】

図4(e)は、演出制御CPU63による音声レジスタSRGへの設定動作を図示したものであり、2bit長のアドレスバスA1-A0と、1バイト長のデータバスD7-D0の内容が示されている。なお、本実施例では、チップセレクト信号CS3は、アドレス空間CS3をアクセスする場合に、自動的にアクティブになるよう、電源投入時に設定されるが、この点は図6や図12に関して後述する。

30

【0069】

何れにしても、本実施例の場合、音声メモリ28に記憶された圧縮音声データは、13bit長のフレーズ番号NUM(000H～1FFFH)で特定されるフレーズ(phrase)圧縮データであり、一連の背景音楽の一曲分(BGM)や、ひと纏まりの演出音(予告音)などが、最高8192種類(=2<sup>13</sup>)、各々、フレーズ番号NUMに対応して記憶されている。そして、このフレーズ番号NUMは、演出制御CPU63から音声プロセッサ27の音声制御レジスタSRGに伝送される音声コマンドの設定値(動作パラメータ)によって特定される。

【0070】

前記の通り、上記の構成を有する音声メモリ28は、リセット信号RT3で電源リセットされ、音声プロセッサ27は、リセット信号RT4で電源リセットされる。図4(c)に示す通り、リセット信号RT4は、電源投入後、所定のアサート期間ASRT(Lレベル区間)を経て、Hレベルに立ち上がるが、本実施例では、その後、音声プロセッサ27の内部回路が自動的に機能して、初期化シーケンス処理が実行されるよう構成されている。なお、この初期化シーケンス処理は、所定の手順で実行される内部動作であり、初期化シーケンス処理の動作中は、演出制御CPU63が音声レジスタSRGをアクセスすることはできない。

40

【0071】

そして、内部動作たる初期化シーケンス処理が完了すると、CPU回路51に対する割込

50

み信号IRQ\_SND がLレベルに変化し、CPU回路51（演出制御CPU63）は、割込み信号IRQ\_SND に基づき割込み処理プログラムを実行する。そして、所定の命令に基づいて割込み信号IRQ\_SND がHレベルに戻されるが、その詳細については、図14(c)を参照して更に後述する。

#### 【0072】

図4(a)に示す通り、演出制御部23のCPU回路51のデータバスとアドレスバスは、液晶インタフェイス基板24に搭載された時計回路(real time clock)38と演出データメモリ39にも及んでいる。時計回路38は、CPU回路51のアドレスバスの下位4bitと、データバスの下位4bitに接続されており、チップセレクト信号CS4で時計回路38が選択された状態では、CPU回路51が、(4bit長アドレス値を有する)内部レジスタを任意にアクセスできるよう構成されている。

10

#### 【0073】

また、演出データメモリ39は、高速アクセス可能なメモリ素子SRAM(Static Random Access Memory)であって、CPU回路51のアドレスバスの16bitと、データバスの下位16bitに接続されており、チップセレクト信号CS4でチップ選択された状態では、SRAM(演出データメモリ)39に記憶されている遊技実績情報その他が、CPU回路51から適宜にR/Wアクセスされるようになっている。なお、チップセレクト信号CS4で選択されるアドレス空間CS4において、0番地から15番地までは時計回路38に付番されているので、SRAM39では使用しない。

20

#### 【0074】

時計回路38と演出データメモリ39は、不図示の二次電池で駆動されており、この二次電池は、遊技動作中、電源基板20からの給電電圧によって適宜に充電される。そのため、電源遮断後も、時計回路38の計時動作が継続され、また、演出データメモリ39に記憶された遊技実績情報が、永続的に記憶保持されることになる(不揮発性を付与)。なお、時計回路(RTC)38は、CPU回路51に対して、割込み信号IRQ\_RTCを出力可能に構成されている(RTC割込み)。このRTC割込みには、日、曜日、時、分、秒が特定可能なアラーム割込みと、所定時間経過後に起動されるタイマ割込みが存在するが、本実施例では、毎日の営業終了時に、日々の遊技実績情報を更新するアラーム割込みを活用している。

30

#### 【0075】

図4(a)の右側に示す通り、演出制御基板23には、CPU回路51やVDP回路52を内蔵する複合チップ50と、CPU回路51の制御プログラムを記憶する制御メモリ(PROM)53と、大量のデータを高速にアクセス可能なDRAM(Dynamic Random Access Memory)54と、演出制御に必要な大量のCGデータを記憶するCGROM55と、が搭載されている。

30

#### 【0076】

図7に関して後述するように、制御メモリ(PROM)53は、本実施例では、チップセレクト信号CS0で選択されるアドレス空間CS0に位置付けされている。また、DDR(Double-Data-Rate 3)で構成されるDRAM(Dynamic Random Access Memory)54は、チップセレクト信号CS5で選択されるアドレス空間CS5に位置付けされている。

40

#### 【0077】

図5(a)は、演出制御部23を構成する複合チップ50について、関連する回路素子も含めて図示した回路ブロック図である。図示の通り、実施例の複合チップ50には、所定時間毎にディスプレイリストDLを発行するCPU回路51と、発行されたディスプレイリストDLに基づいて画像データを生成して表示装置DS1, DS2を駆動するVDP回路52とが内蔵されている。そして、CPU回路51とVDP回路52とは、互いの送受信データを中継するCPUIF回路56を通して接続されている。

#### 【0078】

なお、VDP回路52には、音声プロセッサ27と同等の機能を発揮する音声回路SND

50

が内蔵されているが、これから説明する最初の実施例では、音声回路 S N D を活用していない。但し、最後に説明する実施例のように、V D P 回路 5 2 に内蔵された音声回路 S N D を活用すれば、音声メモリ 2 8 や音声プロセッサ 2 7 の配置が不要となる。

#### 【 0 0 7 9 】

先ず、C P U 回路 5 1 は、発振器 O S C 1 の発振出力（例えば 1 0 0 / 3 M H z ）を H C L K I 端子に受けて、これを周波数倍（例えば 8 倍）して、2 6 6 . 7 M H z 程度の C P U 動作クロックとしている。ここで、発振器 O S C 1 は、スペクトラムス拡散波を出力するよう構成されることで、電波障害 / 電磁妨害を防止する E M I ( Electromagnetic Interference ) 対策を図っている。

#### 【 0 0 8 0 】

一方、V D P 回路 5 2 は、発振器 O S C 2 の発振出力（例えば 4 0 M H z ）を P L L R E F 端子に受け、P L L ( Phase Locked Loop ) 回路で、適宜に周波数倍した上で、V D P 回路 5 2 のシステムクロック、表示装置用の表示クロック（ドットクロックなど）、及び、外付け D R A M 5 4 の D D R クロックとして使用している。すなわち、発振器 O S C 2 の出力は、V D P 回路 5 2 全体のリファレンスクロックとして機能している。なお、P L L 回路の周波数倍比は、所定の設定端子への設定値で規定される。

10

#### 【 0 0 8 1 】

そこで、このリファレンスクロックの重要性を考慮して、本実施例では、発振器 O S C 2 を V D P 回路 5 2 と同じ電源電圧 3 . 3 V で動作させると共に、出力イネーブル端子 O E が H レベル（= 3 . 3 V ）であることを条件に、リファレンスクロックを発振出力するよう構成されている。そして、万一、電源電圧 3 . 3 V が所定レベル以下に低下した場合には、その後、正常な演出動作は望めないので、マスク不能の割込み（N M I ）が生じるよう構成されている。

20

#### 【 0 0 8 2 】

また、複合チップ 5 0 には、H B T S L 端子が設けられ、H B T S L 端子の論理レベルに基づいて、電源投入（C P U リセット）後に実行されるブートプログラム（初期設定プログラム）が、C G R O M 5 5 に記憶されているか（H B T S L = H ）、それ以外のメモリに記憶されているか（H B T S L = L ）を特定している。図示の通り、この実施例では、H B T S L = L レベルに設定されており、演出制御 C P U 6 3 のアドレス空間 C S 0 のゼロ番地が、C G R O M 以外に割り当てられ、具体的には、アドレス空間 C S 0 は、制御メモリ 5 3 に割り当てられている。

30

#### 【 0 0 8 3 】

一方、H B T S L 端子 = H レベルに設定されている場合（破線参照）は、演出制御 C P U 6 3 のアドレス空間 C S 0 のゼロ番地が、C G R O M 5 5 に割り当てられる。この場合は、C G R O M 5 5 のメモリ種別と、バス幅（6 4 / 3 2 / 1 6 b i t ）とが、2 b i t 長の H B T B W D 端子と、4 b i t 長の H B T R M S L 端子への入力値に基づいて各々特定されようになっている。なお、これらの点は、図 3 4 に基づいて更に後述する。

#### 【 0 0 8 4 】

続いて、C P U 回路 5 1 と V D P 回路 5 2 について、互いの送受信データを中継する C P U I F 回路 5 6 について説明する。図 5 ( a ) に示す通り、C P U I F 回路 5 6 には、制御プログラムや必要な制御データを不揮発的に記憶する制御メモリ（P R O M ）5 3 と、2 M バイト程度の記憶容量を有するワークメモリ（R A M ）5 7 とが接続され、各々、C P U 回路 5 1 からアクセス可能に構成されている。先に説明した通り、制御メモリ（P R O M ）5 3 は、チップセレクト信号 C S 0 で選択されるアドレス空間 C S 0 に位置付けられ、ワークメモリ（R A M ）5 7 は、チップセレクト信号 C S 6 で選択されるアドレス空間 C S 6 に位置付けられている。

40

#### 【 0 0 8 5 】

このワークメモリ（R A M ）5 7 には、表示装置 D S 1 , D S 2 の各一フレームを特定する一連の指示コマンドが記載されたディスプレイリスト D L を、一次的に記憶する D L バッファ B U F が確保されている。本実施例の場合、一連の指示コマンドには、C G R O M

50

55 から画像素材（テクスチャ）を読み出してデコード（展開）するためのTXLOADコマンドなどのテクスチャロード系コマンドと、デコード（展開）先のVRAM領域（インデックス空間）を予め特定するなどの機能を有するSETINDEXコマンドなどのテクスチャ設定系コマンドと、デコード（展開）後の画像素材を仮想描画空間の所定位置に配置するためのSPRITEコマンドなどのプリミティブ描画系コマンドと、描画系コマンドによって仮想描画空間に描画された画像のうち、実際に表示装置に描画する描画領域を特定するためのSETDAVRコマンドやSETDAVFコマンドなどの環境設定コマンドと、インデックス空間を管理するインデックステーブルIDXTBLに関するインデックステーブル制御系コマンド（WRIDXTBL）が含まれる。

#### 【0086】

10

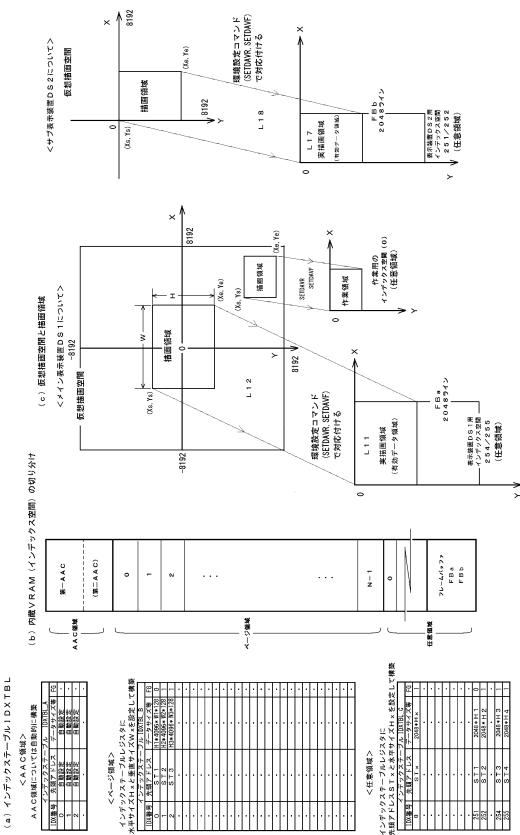

なお、図9(c)には、仮想描画空間（水平X方向±8192：垂直Y方向±8192）と、仮想描画空間の中で任意に設定可能な描画領域と、表示装置DS1, DS2に出力する画像データを一次保存するフレームバッファFBa, FBbにおける実描画領域との関係が図示されている。

#### 【0087】

次に、CPU回路51は、汎用のワンチップマイコンと同等の性能を有する回路であり、制御メモリ53の制御プログラムに基づき画像演出を統括的に制御する演出制御CPU63と、プログラムが暴走状態になるとCPUを強制リセットするウォッチドッグタイマ(WDT)と、16kバイト程度の記憶容量を有してCPUの作業領域として使用される内蔵RAM59と、CPU63を経由しないでデータ転送を実現するDMAC(Direct Memory Access Controller)60と、複数の入力ポートSi及び出力ポートSoを有するシリアル入出力ポート(SIO)61と、複数の入力ポートPi及び出力ポートPoを有するパラレル入出力ポート(PIO)62と、前記各部の動作を制御するべく設定値が設定される動作制御レジスタREGなどを有して構成されている。但し、外付けのWDT回路58を設けた本実施例では、CPU回路51に内蔵されたウォッチドッグタイマ(WDT)を活用していない。

20

#### 【0088】

なお、本明細書では、便宜上、入出力ポートとの表現を使用するが、演出制御部23において、入出力ポートには、独立して動作する入力ポートと出力ポートとが含まれている。この点は、以下に説明する入出力回路64pや入出力回路64sについても同様である。

30

#### 【0089】

パラレル入出力ポート62は、入出力回路64pを通して外部機器（演出インターフェイス基板22）に接続されており、演出制御CPU63は、入力回路64pを経由して、音量スイッチVLSWのエンコーダ出力3bitと、チャンスボタン11のスイッチ信号と、制御コマンドCMDと、割込み信号STBと、を受信するようになっている。エンコーダ出力3bitと、スイッチ信号1bitは、入出力回路64pを経由して、パラレル入出力ポート(PIO)62に供給されている。

#### 【0090】

同様に、受信した制御コマンドCMDは、入出力回路64pを経由して、パラレル入出力ポート(PIO)62に供給されている。また、ストローブ信号STBは、入出力回路64pを経由して、演出制御CPU63の割込み端子に供給されることで、受信割込み処理を起動させている。したがって、受信割込み処理に基づいて、制御コマンドCMDを把握した演出制御CPU63は、演出抽選などを経て、この制御コマンドCMDに対応する音声演出、ランプ演出、モータ演出、及び画像演出を統一的に制御することになる。

40

#### 【0091】

特に限定されないが、本実施例では、ランプ演出とモータ演出のために、VDP回路52のSMC部(Serial Management Controller)78を使用している。SMC部78は、LEDコントローラとMotorコントローラと、を内蔵した複合コントローラであり、クロック同期方式でシリアル信号を出力できるよう構成されている。また、Motorコントローラは、所定の制御レジスタ70への設定値に基づき、任意のタイミングで

50

ラッチパルスを出力可能に構成され、また、クロック同期方式でシリアル信号を入力可能に構成されている。

【0092】

そこで、本実施例では、クロック信号に同期してモータ駆動信号やLED駆動信号を、SMC部78から出力させる一方、適宜なタイミングで、ラッチパルスを、動作制御信号ENABLEとして出力するようにしている。また、演出モータ群M1～Mnからの原点センサ信号SN0～SNnをクロック同期方式でシリアル入力するよう構成されている。

【0093】

図4(a)に関して説明した通り、クロック信号CK0～CK2、駆動信号SDATA0～SDATA2、及び、動作制御信号ENABLE0～ENABLE2は、出力バッファ41～43を経由して、所定の駆動基板30, 31, 37に伝送される。また、原点センサ信号SN0～SNnは、モータランプ駆動基板31から入出力バッファ43を経由して、SMC部78にシリアル入力される。

10

【0094】

但し、本実施例において、SMC部78を使用することは必須ではない。すなわち、CPU回路51には、汎用のシリアル入出力ポートSIO61が内蔵されているので、これらを使用して、ランプ演出とモータ演出を実行することもできる。

【0095】

具体的には、図5(a)の破線に示す通りであり、破線で示す構成では、シリアル入出力ポートSIO61に内部接続されている入出力回路64sを経由して、クロック信号CK0～CK2、駆動信号SDATA0～SDATA2が出力され、入出力回路64pを経由して動作制御信号ENABLE0～ENABLE2が出力される。なお、便宜上、入出力ポートや入出力回路と表現するが、実際に機能するのは、出力ポートや出力回路である。

20

【0096】

ここで、シリアル出力ポートSOは、16段のFIFOレジスタを内蔵して構成されている。そして、DMAC回路60は、演出制御CPU63から動作開始指示(図17(b)ST18参照)を受けて起動し、ランプ/モータ駆動テーブル(図17(b)参照)から、必要な駆動データを順番に読み出し、シリアル出力ポートSOのFIFOレジスタにDMA転送するよう構成されている。FIFOレジスタに蓄積された駆動データは、クロック同期方式でシリアル出力ポートSOからシリアル出力される。なお、DMAC回路には、複数(例えば7)のDMAチャネルが存在するが、優先度に劣る第3のDMAチャネルでランプ駆動データをDMA転送し、最優先度の第1のDMAチャネルでモータ駆動データをDMA転送するよう構成されている。

30

【0097】

CPU回路51に内蔵された動作制御レジスタREGは、レジス番号(アドレス値)が0×FF400000以降に付番された8bit、16bit、又は32bit長のレジスタであり、演出制御CPU63から適宜にWRITE/READアクセス可能に構成されている(図7参照)。そのためノイズなどの影響で、動作制御レジスタREGに、不合理な値に設定される可能性がある。

40

【0098】

但し、例えば、意図的に無限ループ処理を実行させて外付けのWDT回路58を起動させることで、複合チップ50を異常リセットすることができる。この場合、動作制御レジスタREGの値が、電源投入後と同じデフォルト値(初期値)に戻され、且つ、VDP回路52についても、VDPレジスタRGijの値が、デフォルト値(初期値)に戻されることで異常状態が解消される。

【0099】

図4(b)は、このリセット動作に関連する回路構成であって、本実施例に特徴的なリセット機構を説明する図面である。なお、本明細書において、RGijと表記するVDPレジスタは、CPU回路51に内蔵された動作制御レジスタREGではなく、VDP回路52の内部動作を制御する制御レジスタ群70(図7参照)の何れかを意味する。また、図

50

4 ( b ) に示すシステム制御回路 520 とは、VDP レジスタ RGij ( 図 7 の制御レジスタ群 70 の何れか ) への設定値に基づいて機能する VDP 回路 52 の内部制御回路を意味する ( 図 4 ( a ) 参照 ) 。なお、VDP レジスタ RGij は、演出制御 CPU63 のアドレスマップにおいて、チップセレクト信号 CS7 で選択されるアドレス空間 CS7 に位置付けられる。

#### 【 0100 】

以上を踏まえてリセット機構について説明すると、図 4 ( b ) に示す通り、複合チップ 50 は、論理反転されたシステムリセット信号 SYSバーを受ける 3 個の OR ゲート G2 ~ G4 を経由して、内部回路がリセット可能に構成されている。但し、本実施例では、破線で示すように、内蔵 WDT を有効化しないので、OR ゲート G2 の入端子と出力端子は、直結状態となる。

10

#### 【 0101 】

何れにしても、CPU 回路 51 と VDP 回路 52 の間に、パターンチェック回路 CHK が設けられ、パターンチェック回路 CHK は、パラレル入出力ポート ( PIO ) 62 から、所定のキーワード列 ( リセット用の暗号列 ) を受けることを条件に、リセット信号 RST を出力するよう構成されている。

#### 【 0102 】

そして、複合チップ 50 の内部回路は、( 1 ) CPU 回路 51 と、( 2 ) VDP 回路 52 の表示回路 74 と、( 3 ) VDP 回路 52 における表示回路以外とに三分されて、各々、OR ゲート G2 ~ G4 から第 1 リセット経路 ~ 第 3 リセット経路のリセット信号を受けるよう構成されている。

20

#### 【 0103 】

先ず、入出力端子が直結状態の OR ゲート G2 は、第 1 リセット経路に関連しており、システムリセット信号 SYSバーに基づき、CPU 回路 51 の全体をシステムリセットされるように構成されている。また、OR ゲート G3 は、第 2 リセット経路に関連しており、システムリセット信号 SYSバーと、パターンチェック回路 CHK からのリセット信号 RST とを受けて、OR 論理に基づき、VDP 回路 52 全体をリセット可能に構成されている。

#### 【 0104 】

この第 2 リセット経路は、電源投入時の電源リセット動作だけでなく、所定の異常を検出した演出制御 CPU63 が、VDP 回路 52 の全体を異常リセットして初期状態に戻す用途で使用される。具体的には、VDP 回路 52 の内部動作を示す所定のステイタスレジスタ RGij に基づき、重大な異常が発生していると判断される場合には、パターンチェック回路 CHK からリセット信号 RST を発生させることで、VDP 回路 52 の全体を異常リセットしている。なお、表示回路 74 は、OR ゲート G4 を経由して、第 2 リセット経路 第 3 リセット経路で異常リセットされる。

30

#### 【 0105 】

一方、VDP 回路 52 に内蔵された内部回路は、第 4 リセット経路で、必要時に個々的にリセットすることも可能に構成されている。個々的にリセット可能な内部回路には、図 5 ( a ) に示すインデックステーブル IDXTBL 、データ転送回路 72 、プリローダ 73 、表示回路 74 、描画回路 76 、SMC 回路 78 、及び、音声回路 SND や、図 10 に示す ICM 回路が含まれている。

40

#### 【 0106 】

個別的なリセット動作を実現する手法は、図 4 ( b ) の下部に記載の通りであり、例えば、表示回路 74 は、所定の VDP レジスタ RGij ( システムコマンドレジスタ ) に、第 1 リセット値を書き込むことで、第 4 リセット経路 4A 第 3 リセット経路を経てリセットされる。

#### 【 0107 】

また、VDP 回路 52 の各内部回路 ( 72 , 73 , 74 , 76 , SND , . . . ) は、( 1 ) 第 1 の VDP レジスタ RGij ( リセット RQ レジスタ ) に、対象回路を特定する設

50

定値を書き込んだ後、(2)所定のVDPレジスタRGij(システムコマンドレジスタ)に、第2リセット値を書き込むことで、個々的にリセットされる(第4リセット経路4B)。なお、この実施例では使用しないが、音声回路SNDは、第4リセット経路4Bによるリセットだけでなく、所定のVDPレジスタ(回路設定コマンドレジスタ)に、リセット値を書き込むことでもリセット可能である(第4リセット経路4C)。

#### 【0108】

本実施例は、上記の構成を有するので、電源投入時やプログラム暴走時に、VDP回路52全体が自動的に初期状態に戻るだけでなく、必要に応じて、各部を初期状態に戻して異常事態の回復を図ることができる。例えば、一定期間、内蔵VRAM71に対してREAD/ WRITEアクセスがない描画回路76のフリーズ時には、第4リセット経路4Bを経由して描画回路76が個別的に初期化される(図17(d)のST16a参照)。プリローダ73やデータ転送回路72についても、ほぼ同様であり、所定の異常時には、第4リセット経路4Bを経由してプリローダ73が初期化され(図24のST27参照)、第4リセット経路4Bを経由してデータ転送回路72が初期化される(図19や図24のST27参照)。

10

#### 【0109】

また、表示回路74については、1/60秒毎の表示タイミングに、表示データの生成が間に合わないアンダーラン(Underrun)異常が続くような場合に、第4リセット経路4A又は第4リセット経路4Bを経由して、表示回路74が個別的に初期化される(図17のST10c参照)。なお、これら個別的なリセット動作については、図17以降に記載したプログラム処理に関して更に後述する。

20

#### 【0110】

以上、本実施例に特徴的なリセット機構について説明したが、何れかのリセット経路1~4が機能して、複合チップ50の内部回路がリセットされると、その内部回路に対応するVDPレジスタRGijの設定値は、電源投入後と同じデフォルト値に戻る。

#### 【0111】

続いて、CPU回路51の内部構成に戻って、特徴的な回路構成の説明を続ける。図6は、CPU回路51の内部構成をやや詳細に示すブロック図である。CPU回路51は、先に説明した内蔵RAM59、DMAC回路60、SIO61、PIO62、WDT以外にも、多くの特徴的な回路を含んで構成されている。

30

#### 【0112】

先ず第1に、CPU回路51は、命令用のCPUフェッチバスと、データ用のCPUメモリアクセスバスとを別々に有してハーバード・アーキテクチャを実現している。そのため、CPUコア(演出制御CPU)63が命令をメモリから読むフェッチ動作と、メモリアクセス動作とが競合せず、フェッチ動作を連続させることで高速処理を実現している。

#### 【0113】

また、CPUコア63は、複数個(例えば15個)のレジスタバンクRB0~RB14を有して構成されており、その使用の有無を選択できるよう構成されている。そして、レジスタバンクRBiの使用を許可した動作状態では、割込み処理の開始時に、CPUの内蔵レジスタ(例えば19個)のレジスタ値(各32bit長)が、空き状態のレジスタバンクRBiに自動的に退避される。

40

#### 【0114】

また、割込み処理の終了時に所定の復帰命令を実行すると、例えば19個の退避データが、対応する内蔵レジスタに自動的に復帰される。したがって、通常の構成のように、割込み処理の開始時にPUSH命令を19回実行し、割込み処理の終了時にPOP命令を19回実行する手間が不要となり、高速処理が実現される。

#### 【0115】

また、実施例のCPU回路51は、命令キャッシュメモリ67と、オペランドキャッシュメモリ89と、キャッシュコントローラ69とを設けることで、ハーバードキャッシュ動作を実現しており、同一アドレスをアクセスする場合に、キャッシュ済みのデータを活用

50

することでプログラム処理の更なる高速化を図っている。なお、バスプリッジ 6 5 と、周辺バス(1) 用のコントローラ、周辺バス(2) 用のコントローラ、及び、周辺バス(3) 用のコントローラとが設けられることで、内部バスと、周辺バス(1)、周辺バス(2)、及び周辺バス(3) とを適宜に接続している。

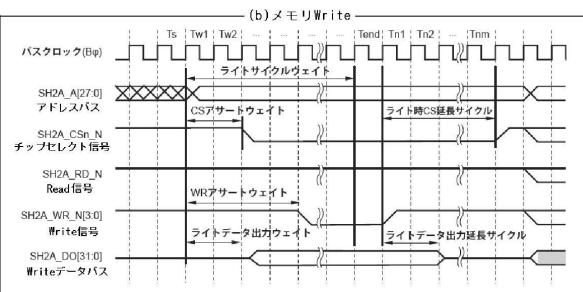

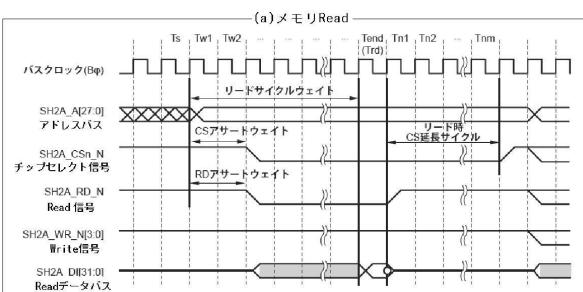

#### 【 0 1 1 6 】

次に、図 6 の回路構成において、バスステートコントローラ 6 6 は、動作制御レジスタ R E G への適宜な設定値に基づいて動作して、C P U 回路 5 1 に接続された各種メモリデバイスとのメモリREAD動作やメモリWRITE 動作を最適化する部分である。メモリREAD動作やメモリWRITE 動作は、例えば、図 3 5 に例示した動作タイミングで実行されるが、アドレスバス (28Bit) から出力されるアドレスデータと、READデータバス (32Bit) に読み出されるREADデータと、WRITE データバス (32Bit) に書き出されるWRITE データと、チップセレクト信号 C S 0 ~ C S 7 などの制御信号との動作タイミングが、動作制御レジスタ R E G への設定値に基づいて、各メモリデバイスの特性に対応して適宜に規定される。

10

#### 【 0 1 1 7 】

READデータバスとWRITE データバスが別々に設けられているので、上記したハーバード・アーキテクチャによる高速動作が実現される。なお、本明細書では、アドレスバス (28 Bit)、READデータバス (32Bit)、及び、WRITE データバス (32Bit) について、図 6 に示す内部バスや、周辺バス(1) ~ 周辺バス(3) などと区別する意味で、外部バスと総称することがある。

20

#### 【 0 1 1 8 】

図 7 は、チップセレクト信号 C S 0 ~ C S 7 によって選択されるアドレス空間 C S 0 ~ C S 7 を図示したものであり、バスステートコントローラ 6 6 を経由してアクセスされる演出制御 C P U 6 3 にとってのアドレスマップを図示したものである。先ず、各アドレス空間 C S 0 ~ C S 7 は、何れも、最大 6 4 M バイトに (= 0x4000000H = 67108864) に規定されている。

20

#### 【 0 1 1 9 】

先に説明した通り、アドレス空間 C S 0 ~ C S 7 とは、揮発性の有無を含むメモリ種別や、データバス幅 (8 / 16 / 32 ビット) を、各々、規定可能な C P U 回路 5 1 にとって外部メモリを意味する。そして、本実施例では、図 6 (b) や図 7 に示す通り、制御メモリ (P R O M) 5 3 がアドレス空間 C S 0、音声プロセッサ 2 7 の音声制御レジスタ S R G がアドレス空間 C S 3、時計回路 3 8 の内部レジスタや S R A M 3 9 がアドレス空間 C S 4、外付け D R A M (D D R) 5 4 がアドレス空間 C S 5、ワークメモリ 5 7 がアドレス空間 C S 6、V D P レジスタ R G i j がアドレス空間 C S 7 に位置付けられている。なお、アドレス空間 C S 1, C S 2 についての説明は省略する。

30

#### 【 0 1 2 0 】

ところで、図 7 から確認される通り、アドレス空間 C S 0 ~ C S 7 は、アドレス値 0x000 00000 ~ 0x1FFFFFFF (キャッシュ有効空間) だけでなく、アドレス値 0x20000000 ~ 0x3FFFFFFF (キャッシュ無効空間) にも確保されている。これは、アドレスビット A 2 9 = 1 のときには、C P U 回路 5 1 の内部動作に基づいて、キャッシュ無効とする一方、アドレスビット A 2 9 = 0 のときにキャッシュ有効とすることで、キャッシュ機能の活用を任意選択できるようにしたものである。

40

#### 【 0 1 2 1 】

そのため、本実施例では、全 3 2 b i t のアドレス情報 (ビット A 3 1 ~ A 0 ) のうち、ビット A 2 9 の値が 1 又は 0 の何れであっても、残り 3 1 b i t (ビット A 3 1 ~ A 3 0 とビット A 2 8 ~ A 0 ) の値が同じであれば、同一のメモリの同一番地を指示することになる。例えば、0x18000000番地をREADアクセスしても、0x38000000番地をREADアクセスしても、ワークメモリ 5 7 のゼロ番地から同一データが読み出されることになる。なお、0x18000000番地をREADアクセスした場合には、読み出したデータがキャッシュに保存されるが、図 6 (b) は、キャッシュ有効 / 無効のアクセス動作を図示している。

50

## 【0122】

もっとも、所定の動作制御レジスタ REGへの設定値に基づいて、命令キャッシュ及び/又はオペランドキャッシュについて、キャッシュ動作を無効化することもできる。但し、本実施例では、電源投入後、命令キャッシュ及びオペランドキャッシュについて、キャッシュ動作を有効化した上で、必要に応じて、キャッシュ無効空間をアクセスすることで、キャッシュ動作を無効化している。

## 【0123】

図7のメモリマップについて説明を続けると、0x40000000番地以降は、バスステートコントローラ66が機能しない内部メモリ空間であって、0xF0000000番地～0xFF3FFFFF番地は、キャッシュのアドレスアレイ空間に割り当てられている。また、0xFF400000番地～0xFFFF7FFFFF番地と、0xFFFFC0000番地～0xFFFFFFFFFF番地は、内蔵周辺モジュールに割り当てられ、具体的には、CPU回路の動作制御レジスタREGに割り当てられている。なお、内蔵RAM59のアドレス範囲は、0xFFFF80000～0xFFFFBFFFFである。

10

## 【0124】

CPU回路51の内部構成について説明を続けると、コンペアマッチタイマCMTと、マルチファンクションタイマユニットMTUは、CPU回路51に供給される外部信号をカウントしたり、或いは、内部クロックを遅倍又は分周した計数クロックをカウントして、カウント結果が所定値に達すると、割込み信号などを発生する回路である。特に限定されないが、本実施例では、マルチファンクションタイマユニットMTUを活用して、1mS割込み信号と、20μS割込み信号を発生させている。

20

## 【0125】

次に、割込みコントローラINTCは、VDP回路52やDMAC回路60やマルチファンクションタイマユニットMTUなどからの内部割込みと、IRQ\_CMD、IRQ SND、IRQ\_RCTなどの外部割込みを受けて、予め規定されている優先順位に基づいて、割込み処理（割込みハンドラ）を起動させる回路である。ここで、IRQ\_CMDは、制御コマンドCMDを受信すべきコマンド受信割込み信号、IRQ SNDは、音声プロセッサ27が初期化シーケンスを終えたことを示す終了割込み信号、IRQ\_RCTは、アラーム割込み信号である。

## 【0126】

そして、本実施例では、割込み優先度は、コマンド受信割込みIRQ\_CMDが最高レベルであり、以下、20μS割込み 1mS割込み VDP回路からの割込み（IRQ0, IRQ1, IRQ2, IRQ3） DMAC割込み IRQ SND IRQ RCTの順になっている（図14（d）参照）。なお、これらは何れも、マスク可能な割込みであり、マスク不能な割込みNMIは、先に説明した通り、発振器OSC2からリファレンスクロックが出力されていない場合に演出制御CPU63に出力される。

30

## 【0127】

そして、何れの割込み処理でも、CPUの複数の内蔵レジスタのレジスタ値（各32bit長）は、空き状態の何れかのレジスタバンクRBiに、自動的に退避される。そして、割込み処理の最後に所定の復帰命令を実行すると、退避データが、対応する内蔵レジスタに自動的に復帰される。

40

## 【0128】

続いて、DMAC回路60について説明する。実施例のDMAC回路60は、所定の動作制御レジスタREGへの設定値に基づいて、転送元（Source）から転送先（Destination）に対して、所定のDMAC転送モードで、所定のデータ転送単位毎に、所定回数、データ転送を繰り返す回路である。なお、同一の内部構成を有する複数チャネルのDMAC0～DMACnが用意されており、並列的に動作可能となっている。但し、優先度が決まっており（チャネル0 > … > チャネルn）、チャネル調停動作モードの並列動作時には、所定タイミングでのチャネル調停によって優先度の高いDMACiの動作が優先される。

## 【0129】

DMAC回路60の活用としては、例えば、シリアル出力ポートSOが機能する実施例（

50

図7(a)破線部参照)では、CPU回路51の動作制御レジスタREGには、ランプ/モータ駆動テーブルの先頭アドレス(転送元アドレスの先頭値)と、シリアル出力ポートSOの入力レジスタのアドレス(転送先アドレスの固定値)と、データ転送単位(8bit)と、転送回数と、が指定される。そして、所定の動作制御レジスタREGに動作開始指示を受けたDMAC回路60は、転送元アドレスを更新しつつ、所定の転送先アドレスに駆動データをDMA転送する。そして、全てのDMA転送が終われば、DMAC割込み(動作終了割込み)が生じるよう構成されている。

#### 【0130】

この点は、ディスプレイリストDLをDMAC回路60が発行する実施例(図20、図24(c))の場合もほぼ同様である。すなわち、演出制御CPU63は、CPU回路51の所定の動作制御レジスタREGに、転送元(DLバッファBUF)の先頭アドレスと、転送先(転送ポートTR\_PORT)のアドレスと、DMA転送モードと、データ転送単位と、転送回数、その他の条件を設定することになる。なお、これらの点は、図20に関して更に後述する。

10

#### 【0131】

ところで、一般に、DMA転送モードには、DMA転送の単位動作(R動作/W動作)の途中でバス制御権を開放するなど、DMA動作がメモリバスを占有しないサイクルスチール転送モードと、複数のR動作やW動作を連続させるなど、指定された転送回数が完了するまでバス制御権を解放しないバースト転送(パイプライン転送)モードと、他のデバイスから受けるDMA転送要求(デマンド)がアクティブの間はDMA動作を継続するデマンド転送モードなどが考えられる。しかし、本実施例のDMAC回路60は、DMA転送時のリードアクセス起動(R動作)とライトアクセス起動(W動作)の間に、少なくとも1サイクルのメモリ開放期間を設けたサイクルスチール転送モードで機能することで、演出制御CPU63の動作に支障が出ないようにしている。

20

#### 【0132】

図8は、サイクルスチール転送動作(a1)と、パイプライン転送(a2)とを説明する図面である。図8(a1)に示す通り、サイクルスチール転送モードで機能するDMAC回路60は、1データ転送のリードアクセス起動(R)とライトアクセス起動(W)の間に、少なくとも1サイクル空けて動作しており、この空いたサイクルでは、演出制御CPU63のバス使用が可能となる。図8(a1)と図8(a2)の対比関係から明らかのように、パイプライン転送では、一サイクル(一オペランド転送)が終わるまでは、バスがCPUに開放されないのでに対して、サイクルスチール転送モードでは、リードアクセス毎に、バスがCPUに開放されるので、CPUの動作が大きく遅れることがない。

30

#### 【0133】

そして、例えば、ディスプレイリストDLのVDP回路52への発行時に、DMAC回路60を使用する実施態様では、一サイクルのデータ転送単位(1オペランド)を、 $32 \times 2$ bitに設定し、ディスプレイリストDLが格納されている内蔵RAM59のソースアドレスを適宜に増加しつつ(1オペランド転送毎に+8)、固定アドレスで特定されるデータ転送回路72の転送ポートレジスタTR\_PORT(図10参照)に対して、DMA転送動作を実行している。

40

#### 【0134】

後述するように、実施例では、ディスプレイリストDLに、必要個数のNOP(no operation)コマンドを付加することで、全体のデータサイズを、固定値(例えば、 $4 \times 64 = 256$ バイト、又はその整数倍)に調整しており、 $32$ bit $\times$ 2回の一オペランド転送を32回(又はその整数倍)繰り返すことで、ディスプレイリストDLの発行を完了させている。なお、描画回路76がNOPコマンドを実行しても、事実上、何の変化も生じない。

#### 【0135】

また、DMA転送条件に関して動作モードを分類すると、一般に、單一オペランド転送(図8(b1)参照)と、連続オペランド転送(図8(b2)参照)と、ノンストップ転送

50

(図8(b3)参照)とが考えられる。

【0136】

ここで、單一オペラント転送とは、図8(b1)に示すように、DMA転送要求が与えられるたびに、1オペラントの転送を繰り返し、転送バイト数をカウントするバイトカウントがゼロになった時点で、DMA割込み要求が生じる動作モードを意味する。次に、連續オペラント転送とは、図8(b2)に示すように、1回のDMA要求で、バイトカウントがゼロになるまでDMA転送を繰り返す動作モードを意味する。

【0137】

これら、連續オペラント転送(b2)や單一オペラント転送(b1)では、1オペラント転送が終了するごとにチャネル調停が行われ、優先順位の高いチャネルのDMA要求がないことを条件に、現在のチャネルの転送が継続される(チャネル調停動作モード)。そこで、本実施例では、ディスプレイリストDLのVDP回路への発行や、ランプ駆動データやモータ駆動データのDMA転送は、單一オペラント転送方式を探っている。そして、並列動作時には、例えば、モータデータ>ディスプレイリストDL>ランプデータの優先度のチャネル調停となるよう、最適チャネルのDMA Ciを使用している。

10

【0138】

一方、ノンストップ転送とは、チャネル調停が実行されない動作モードであって、図8(b3)に記載の通り、1回のDMA要求で、バイトカウントがゼロになるまで連続的にDMA転送が繰り返される。本実施例では、電源投入時のメモリセクション初期化処理(図12のSP8)では、ノンストップ転送でプログラムやデータをDMA転送している。

20

【0139】

以上、CPU回路51について説明したので、次に、VDP回路52について説明する。VDP回路52には、画像演出を構成する静止画や動画の構成要素となる圧縮データを記憶するCGROM55と、4Gbit程度の記憶容量を有する外付けDRAM(Dynamic Random Access Memory)54と、メイン表示装置DS1と、サブ表示装置DS2とが接続されている。なお、DRAM54は、好適にはDDR3(Double-Data-Rate3SDRAM)で構成される。

【0140】

特に限定するものではないが、この実施例では、CGROM55は、62Gbit程度の記憶容量のNAND型フラッシュメモリで構成されたフラッシュSSD(solid state drive)で構成されており、シリアル伝送によって必要な圧縮データを取得するよう構成されている。そのため、パラレル伝送において不可避的に生じるスキュー(ビットデータ毎の伝送速度の差)の問題が解消され、極限的な高速伝送動作が可能となる。特に限定されないが、本実施例では、SerialATAに準拠したHSS(High Speed Serial)方式で、CGROM55を高速アクセスしている。

30

【0141】

なお、SerialATAに準拠したHSS方式を探るか否かに拘らず、NAND型のフラッシュメモリは、ハードディスクより機械的に安定であり、且つ高速アクセスが可能である一方で、シーケンシャルアクセスメモリであるため、DRAMやSRAM(Static Random Access Memory)に比較すると、ランダムアクセス性に問題がある。そこで、本実施例では、一群の圧縮データ(CGデータ)を、描画動作に先行してDRAM54に読み出しておくプリロード動作を実行することで、描画動作時におけるCGデータの円滑なランダムアクセスを実現している。ちなみに、アクセス速度は、内蔵VRAM>外付けDRAM>CGROMの順番に遅くなる。

40

【0142】

VDP回路52は、詳細には、VDP(Video Display Processor)の動作を規定する各種の動作パラメータが演出制御CPU63によって設定可能な制御レジスタ群70と、表示装置DS1, DS2に表示すべき画像データの生成時に使用される48Mバイト程度の内蔵VRAM(video RAM)71と、チップ内部の各部間のデータ送受信及びチップ外部とのデータ送受信を実行するデータ転送回路72と、内蔵VRAM71に関して、So

50

urceやDestination のアドレス情報を特定可能なインデックステーブルIDX TBLと、描画動作に先行して C G R O M 5 5 をREADアクセスするプリロード動作が実行可能なプリローダ 7 3 と、 C G R O M 5 5 から読み出した圧縮データをデコード（復号伸長 / 展開）するグラフィックスデコーダ（G D E C ）7 5 と、デコード（展開）後の静止画データや動画データを適宜に組み合わせて表示装置 D S 1 , D S 2 の各一フレーム分の画像データを生成する描画回路 7 6 と、描画回路 7 6 の動作の一部として、適宜な座標変換によって立体画像を生成するジオメトリエンジン 7 7 と、描画回路 7 6 が生成したフレームバッファ F B a , F B b の画像データを読み出して、適宜な画像処理を並列的に実行可能な 3 系統（A / B / C ）の表示回路 7 4 A ~ 7 4 C と、3 系統（A / B / C ）の表示回路 7 4 の出力を適宜に選択出力する出力選択部 7 9 と、出力選択部 7 9 が出力する画像データを L V D S 信号に変換する L V D S 部 8 0 と、シリアルデータ送受信可能な S M C 部 7 8 と、 C P U I F 回路 5 6 とのデータ送受信を中継する C P U I F 部 8 1 と、 C G R O M 5 5 からのデータ受信を中継する C G バス I F 部 8 2 と、外付け D R A M 5 4 とのデータ送受信を中継する D R A M I F 部 8 3 と、内蔵 V R A M 7 1 とのデータ送受信を中継する V R A M I F 部 8 4 と、を有して構成されている。なお、音声回路 S N D も内蔵されている。

#### 【 0 1 4 3 】

図 5 ( b ) には、 C P U I F 部 8 1 、 C G バス I F 部 8 2 、 D R A M I F 部 8 3 、及び、 V R A M I F 部 8 4 と、制御レジスタ群 7 0 、 C G R O M 5 5 、 D R A M 5 4 、及び内蔵 V R A M 7 1 との関係が図示されている。図示の通り、 C G R O M 5 5 から取得した C G データは、例えば、プリロードデータとして、データ転送回路 7 2 及び D R A M I F 部 8 3 を経由して、外付け D R A M 5 4 のプリロード領域に転送される。

#### 【 0 1 4 4 】

但し、上記したプリロード動作は、何ら必須動作ではなく、また、データ転送先も、外付け D R A M 5 4 に限定されず、内蔵 V R A M 7 1 であっても良い。したがって、例えば、プリロード動作を実行しない実施例では、 C G データは、データ転送回路 7 2 及び V R A M I F 部 8 4 を経由して、内蔵 V R A M 7 1 に転送される（図 5 ( b ) ）。

#### 【 0 1 4 5 】

ところで、本実施例では、内蔵 V R A M 7 1 には、 C G R O M 5 5 から読み出した圧縮データの展開領域、表示装置の W × H 個の表示ピクセルの各 A R G B 情報（ 3 2 b i t = 8 × 4 ）を特定する画像データを格納するフレームバッファ領域、及び、各表示ピクセルの深度情報を記憶する Z バッファ領域などが必要となる。なお、 A R G B 情報において、 A は、 8 b i t の プレーンデータ、 R G B は三原色の 8 b i t データを意味する。

#### 【 0 1 4 6 】

ここで、内蔵 V R A M 7 1 の上記した各領域は、演出制御 C P U 6 3 がディスプレイリスト D L に記載した各種の指示コマンド（前記したテクスチャや SPRITE など）に基づいて間接的にアクセスされるが、その READ / WRITE アクセスにおいて、一々、内蔵 V R A M 7 1 の Destination アドレスや、 Source アドレスを特定するのでは煩雑である。そこで、本実施例では、 C P U リセット後の初期処理において、描画動作で必要となる一次元または二次元の論理アドレス空間（以下、インデックス空間という）を確保して、各インデックス空間にインデックス番号を付与することで、インデックス番号に基づくアクセスを可能にしている。

#### 【 0 1 4 7 】

具体的には、 C P U リセット後、内蔵 V R A M 7 1 を 3 種類のメモリ領域に大別すると共に、各メモリ領域に、必要数のインデックス空間を確保している。そして、インデックス空間とインデックス番号とを紐付けて記憶するインデックステーブル IDX TBL （図 9 ( a ) 参照）を構築することで、その後のインデックス番号に基づく動作を実現している。

#### 【 0 1 4 8 】

このインデックス空間は、(1) 初期処理後に追加することや、逆に、(2) 開放することも必要となる。そこで、これら追加 / 開放の演出制御 C P U 6 3 の動作時に、追加 / 開放の処理が可能なタイミングか否か、また、追加 / 開放などの処理が実際に完了したか否か、

10

20

30

40

50

などを判定可能なフラグ領域 F G をインデックステーブルIDX\_TBLに設けている。なお、内蔵 V R A M 7 1 は、以下に説明する 2 つの A A C 領域(a1,a2) と、ページ領域(b) と、任意領域(c) の三種類のメモリ領域に大別され、この三種類のメモリ領域(a1,a2)(b)(c) に対応して、インデックステーブルIDX\_TBLが 3 区分されている(図 9 ( a ) )。図示の通り、この実施例では、A A C 領域(a) として、第一 A A C 領域(a1) と第二 A A C 領域(a2) が確保されているが、特に限定されるものではなく、何れか一方だけでも良い。なお、以下の説明では、第一と第二の A A C 領域(a1,a2) を総称する場合には、A A C 領域(a) と称する場合がある。

#### 【 0 1 4 9 】

本実施例の場合、内蔵 V R A M 7 1 は、(a) インデックス空間とそのインデックス番号が内部処理によって自動付与され、且つメモリキャッシュ機能を有する A A C 領域と、(b) 例えば 4 0 9 6 b i t × 1 2 8 ラインの二次元空間を単位空間として、その整数倍の範囲でインデックス空間が確保可能なページ領域と、(c) 先頭アドレス(空間先頭アドレス) S T x と水平サイズ H x が任意に設定できる任意領域と、に区分可能に構成されている(図 9 ( b ) 参照)。但し、V D P 回路 5 2 の内部動作を円滑化するため、任意領域(c) において任意設定されるインデックス空間の空間先頭アドレス S T x は、その下位 1 1 b i t が 0 であって、所定ビット(2 0 4 8 b i t = 2 5 6 バイト)単位とする必要がある。

10

#### 【 0 1 5 0 】

そして、C P U リセット後、各々に必要なアドレス空間の最大値と、領域先頭アドレス(下位 1 1 b i t = 0)を規定して、A A C 領域(a1) と、第二 A A C 領域(a2) と、ページ領域(b) とが確保され、その残りのメモリ領域が任意領域(c) となる。V D P 回路 5 2 の内部動作を円滑化するため、A A C 領域のアドレス空間の最大値は、2 0 4 8 b i t 単位で規定され、ページ領域のアドレス空間の最大値は、上記した 4 0 9 6 b i t × 1 2 8 ラインの単位空間の整数倍とされる。

20

#### 【 0 1 5 1 】

次に、このように確保された各領域(a1,a2)(b)(c) に必要個数のインデックス空間が設定される。なお、任意領域(c) を使用する場合、V D P 回路 5 2 の内部動作を円滑化するため、二次元データを扱うインデックス空間の水平サイズ H x は、2 5 6 b i t の倍数として、任意に設定可能である一方、その垂直サイズは固定値(例えば、2 0 4 8 ライン)となっている。

30

#### 【 0 1 5 2 】

何れにしても、第一と第二の A A C 領域(a1,a2) は、V D P 回路 5 2 によって、インデックス空間とインデックス番号が自動的に付与されるので、例えば、テクスチャ設定系コマンドのSETINDEXコマンドによって、デコード先を A A C 領域(a) に指定すれば、C G R O M 5 5 から C G データを読み出す TXLOAD(テクスチャロード)コマンドでは、C G R O M 5 5 のSourceアドレスと、展開(デコード)後の水平・垂直サイズなどを指定するだけで足りることになる。そこで、本実施例では、予告演出時などに一時的に出現するキャラクタなどの静止画(テクスチャ)や、エストリーム動画については、そのデコード先を A A C 領域(a) にしている。

40

#### 【 0 1 5 3 】

この A A C 領域(a) は、いずれも、メモリキャッシュ機能が付与されているので、例えば、C G R O M 5 5 の同一のテクスチャを複数回、A A C 領域(a) に読み出すような場合には、二度目以降は、A A C 領域(a) にキャッシュされているデコードデータが活用可能となり、余分なREADアクセスとデコード処理が抑制可能となる。もっとも、A A C 領域(a) を使い切った場合には、古いデータが自動的に破壊されるので、本実施例では、A A C 領域(a) を使用する場合、原則として第一 A A C 領域(a1) を使用することとし、繰り返し使用する特定のテクスチャだけを第二 A A C 領域(a2) に取得するようにしている。

#### 【 0 1 5 4 】

繰り返し使用するテクスチャとして、例えば、所定の予告演出時に繰り返し出現するキャラクタや、背景画面を静止画で構築する場合の背景画などを例示することができる。この

50

のような場合、テクスチャ設定系コマンドのSETINDEXコマンドによって、デコード先を第二A A C領域(a2)に設定し、TXLOADコマンドによって、キャラクタや背景画などのテクスチャを第二A A C領域(a2)にデコードした後は、第二A A C領域(a2)を使用しないことで、デコード結果を保護する。

#### 【0155】

そして、その後、SETINDEXコマンドによって、デコード先を第二A A C領域(a2)に指定した上で、取得済みのテクスチャを再取得する同一のTXLOADコマンドを実行させると、取得済みのテクスチャがキャッシュヒットするので、C G R O M 5 5へのREADアクセスと、デコード処理に要する時間を削除することができる。後述するように、このようなキャッシュヒット機能は、プリロード領域に先読みされたプリロードデータでも発揮されるが、プリロード領域でキャッシュヒットするプリロードデータは、デコード前の圧縮データであるのに対して、A A C領域でキャッシュヒットするのはデコード後の展開データである点に意義がある。

10

#### 【0156】

ところで、テクスチャ ( texture ) とは、一般に、物の表面の質感・手触りなどを指す概念であるが、本明細書では、静止画を構成するスプライト画像データや、動画一フレームを構成する画像データや、三角形や四角形などの描画プリミティブ ( primitive ) に貼り付ける画像データだけでなく、デコード後の画像データも含む概念として使用している。そして、内蔵V R A M 7 1の内部で、画像データをコピーする（以下、便宜上、移動と称する）場合には、テクスチャ設定系コマンドのSETINDEXコマンドによって、移動元の画像データをテクスチャとして設定した上で、SPRITEコマンドを実行することになる。

20

#### 【0157】

なお、SPRITEコマンドの実行により、移動元のSource画像データが、形式上は、図9 ( c ) に示す仮想描画空間に描画されるが、表示装置に実際に描画される仮想描画空間内の描画領域と、フレームバッファとなるインデックス空間との対応関係を、予め環境設定コマンド ( SETDAVR , SETDAVF ) や、テクスチャ設定系コマンド ( SETINDEX ) によって設定しておけば、例えば、SPRITEコマンドによる仮想描画空間への描画により、所定のインデックス空間 ( フレームバッファ ) には、移動元のSource画像データが描画されることになる（図9 ( c ) 参照）。

30

#### 【0158】

何れにしても、本実施例では、内蔵V R A M 7 1が、A A C領域(a1,a2)とページ領域(b)と任意領域(c)に大別され、各々に、適当数のインデックス空間を確保することができ、各インデックス空間は、各領域(a)(b)(c)ごとに独立のインデックス番号によって特定される。インデックス番号は、例えば、1バイト長であり、（内部回路によって自動付与されるA A C領域(a)を除いた）ページ領域(b)と任意領域(c)については、0～255の範囲で演出制御C P U 6 3が、インデックス番号を自由に付与することができる。

#### 【0159】

そこで、本実施例では、図9 ( a ) に示す通り、表示装置D S 1用として、任意領域(c)に、一対のフレームバッファF B aを確保して、ダブルバッファ構造の双方に、インデックス番号255, 254を付与している。すなわち、メイン表示装置D S 1用のフレームバッファF B aとして、トグル的に切り換えて使用されるインデックス空間255と、インデックス空間254を確保している。特に限定されないが、このインデックス空間255, 254は、表示装置D S 1の横方向ピクセル数に対応して、水平サイズ1280をしている。なお、各ピクセルは、A R G B情報32bitで特定されるので、水平サイズ1280は、 $32 \times 1280 = 40960$ bit ( 256bitの倍数 ) を意味する。

40

#### 【0160】

また、表示装置D S 2用として、任意領域(c)に、別の一対のフレームバッファF B bを確保して、ダブルバッファ構造の双方にインデックス番号252, 251を付与している。すなわち、サブ表示装置D S 2用のフレームバッファF B bとして、インデックス空間252と、インデックス空間251を確保している。このインデックス空間252, 25

50

1は、表示装置D S 2の横方向ピクセル数に対応して、水平サイズ480としている。この場合も、各ピクセルは、A R G B情報32bitで特定されるので、水平サイズ480は、 $32 \times 480 = 15360$ bit(256bitの倍数)を意味する。

#### 【0161】

なお、フレームバッファF B a, F B bを任意領域(c)に確保するのは、任意領域(c)には、32バイト(=256bit=8ピクセル分)の倍数として、任意の水平サイズに設定することができ、上記のように、表示装置D S 1, D S 2の水平ピクセル数に一致させれば、確保領域に無駄が生じないからである。一方、ページ領域(b)には、128ピクセル $\times$ 128ラインの単位空間の整数倍の水平/垂直サイズしか設定できない。

#### 【0162】

但し、任意領域(c)に確保される二次元のインデックス空間は、その垂直サイズが固定値(例えば、2048ライン)となっている。そのため、フレームバッファF B aにおいて、水平サイズ1280 $\times$ 垂直サイズ1024の領域だけが、メイン表示装置D S 1にとって有効データ領域となる。この点は、サブ表示装置D S 2についても同様であり、フレームバッファF B bにおいて、水平サイズ480 $\times$ 垂直サイズ800の領域だけが、サブ表示装置D S 2にとって有効データ領域となる(図9(c), 図17(e)参照)。

10

#### 【0163】

上記の点は更に後述するが、何れにしても、フレームバッファF B a, F B bは、描画回路76にとっての描画領域として、各ダブルバッファ(255/254, 252/251)が交互に使用され、また、表示回路74A, 74Bにとっての表示領域として、各ダブルバッファ(255/254, 252/251)が交互に使用される。なお、本実施例では、表示ピクセルの深度情報を記憶するZバッファを使用しないので欠番(253)が生じるが、Zバッファを使用する場合には、任意領域(c)におけるインデックス番号253, 250のインデックス空間253, 250が、表示装置D S 1と表示装置D S 2のためのZバッファとなる。

20

#### 【0164】

また、本実施例では、フレームバッファF B a, F B bが確保された任意領域(c)に、追加のインデックス空間(メモリ領域)を確保する場合には、0から始まるインデック番号を付与するようにしている。何ら限定されないが、本実施例では、キャラクタやその他の静止画で構成された演出画像を、必要に応じて、適宜な回転姿勢で表示画面の一部に出現させる予告演出用の作業領域として、任意領域(c)に、インデックス空間(0)を確保している。

30

#### 【0165】

但し、作業領域の使用は必須ではなく、また、任意領域(c)に代えて、ページ領域(b)に作業領域としてのインデックス空間を確保しても良い。ページ領域(b)を使用すれば、水平サイズ128(=4096bit) $\times$ 垂直サイズ128の正方形状の単位空間の倍数寸法のインデックス空間を確保できるので、小型の演出画像を扱うには好適である。

#### 【0166】

ところで、本実施例では、背景画も含め動画で構成されており、画像演出は、ほぼ動画のみで実現されている。特に、変動演出時には、多数(通常10個以上)の動画が同時に描画されている。これらの動画は、何れも、一連の動画フレームとして、圧縮状態でC G R O M 55に格納されているが、Iフレームのみで構成されたIストリーム動画と、IフレームとPフレームとで構成されたI Pストリーム動画とに区分される。ここで、Iフレーム(Intra coded frame)とは、他画面とは独立して、入力画像をそのまま圧縮するフレームを意味する。一方、Pフレーム(Predictive coded frame)とは、前方向予測符号化を行うフレームを意味し、時間的に過去に位置するIフレームまたはPフレームが必要となる。

40

#### 【0167】

そこで、本実施例では、I Pストリーム動画については、旧データの破壊が懸念されるA A C領域(a)ではなく、ページ領域(b)に展開している。すなわち、水平サイズ128 $\times$

50

垂直サイズ 128 の倍数寸法のインデックス空間を確保可能なページ領域(b)に、多数のインデックス空間 (IDX<sub>0</sub> ~ IDX<sub>N</sub>) を確保して、一連の動画フレームは、各動画 MV<sub>i</sub> に対応する、常に同一のインデックス空間 IDX<sub>i</sub> を使用してデコードするようにしている。すなわち、動画 MV<sub>1</sub> はインデックス空間 IDX<sub>1</sub> に展開され、動画 MV<sub>2</sub> はインデックス空間 IDX<sub>2</sub> に展開され、以下同様に、動画 MV<sub>i</sub> はインデックス空間 IDX<sub>i</sub> に展開されるよう構成されている。

#### 【0168】

動画 MV<sub>i</sub> について、更に具体的に説明すると、SETINDEXコマンドによって、「IPストリーム動画 MV<sub>i</sub> のデコード先は、ページ領域(b)におけるインデックス番号 i のインデックス空間 (i) である」と予め指定した上で、IPストリーム動画 MV<sub>i</sub> の動画一フレームを取得するTXLOADコマンドを実行させている。 10

#### 【0169】

すると、TXLOADコマンドが特定する CGROM55 上の動画一フレーム (一連の動画フレームの何れか) が、先ず、AAC領域(a) に取得され、その後、自動的に起動する GDEC (グラフィックスデコーダ) 75 によって、ページ領域(b) のインデックス空間 (i) に、取得した動画一フレームがデコードされて展開されることになる。

#### 【0170】

一方、本実施例では、IPストリーム動画については、静止画と同一扱いとしており、SETINDEXコマンドによって、「IPストリーム動画 MV<sub>j</sub> のデコード先は、第一AAC領域(a1) である」と指定して、TXLOADコマンドを実行させる。その結果、動画フレームは第一AAC領域(a1)に取得され、その後、自動的に起動する GDEC 75 が、第一ACC領域(a1)にデコードデータを展開している。先に説明した通り、AAC領域(a) のインデックス空間は、自動的に生成されるので、インデックス番号を指定する必要はない。なお、インデックス空間に必要となる展開ボリューム、つまり、デコードされたテクスチャ (動画フレーム) の水平サイズと垂直サイズは、展開先が AAC領域(a) か、ページ領域(b) かに拘らず、TXLOADコマンドによって特定される。 20

#### 【0171】

ところで、IPストリーム動画 MV<sub>i</sub> やIPストリーム動画 MV<sub>j</sub> は、一般に N 枚の動画フレーム (IフレームやPフレーム) で構成されている。そのため、TXLOADコマンドでは、例えば、k 枚目 (1 ~ k ~ N) の動画フレームが記憶されている CGROM55 のSourceアドレスと、展開後の水平・垂直サイズなどを指定することになる。何ら限定されないが、静止画を殆ど使用しない実施例では、内蔵VRAM71 のアドレス空間 48M バイトの大部分 (30M バイト程度) をページ領域(b) に割り当てている。そして、静止画を殆ど使用しない実施例では、AAC領域として、第一AAC領域(a1)だけを確保し、第二AAC領域(a2)を確保せず、また、前記したAAC領域のキャッシュヒット機能も活用しない。 30

#### 【0172】

なお、圧縮動画データのデコード処理を高速化するため、専用の GDEC (グラフィックスデコーダ) 回路を設けることも考えられる。そして、専用の GDEC 回路を VDP 回路 52 に内蔵されれば、N 枚の圧縮動画フレームで構成された圧縮動画データのデコード処理において、動画圧縮データの先頭アドレスを GDEC 回路に指示すれば足りるので、N 枚の圧縮動画フレームについて、1 枚ごとに先頭アドレスを指定する必要がなくなる。 40

#### 【0173】

しかし、このような専用の GDEC 回路を、圧縮アルゴリズム毎に複数個内蔵せらるるでは、VDP 回路 52 の内部構成が更に複雑化する。そこで、本実施例では、ソフトウェア GDEC とし、IPストリーム動画、IPストリーム動画、静止画、その他 値などのデータについて、各圧縮アルゴリズムに対応するソフトウェア処理によってデコード処理を実現している。なお、ハードウェア処理とソフトウェア処理の処理時間差は、あまり問題にならず、処理時間が問題になるのは、もっぱら、CGROM55 からのアクセス (READ) タイムである。 50

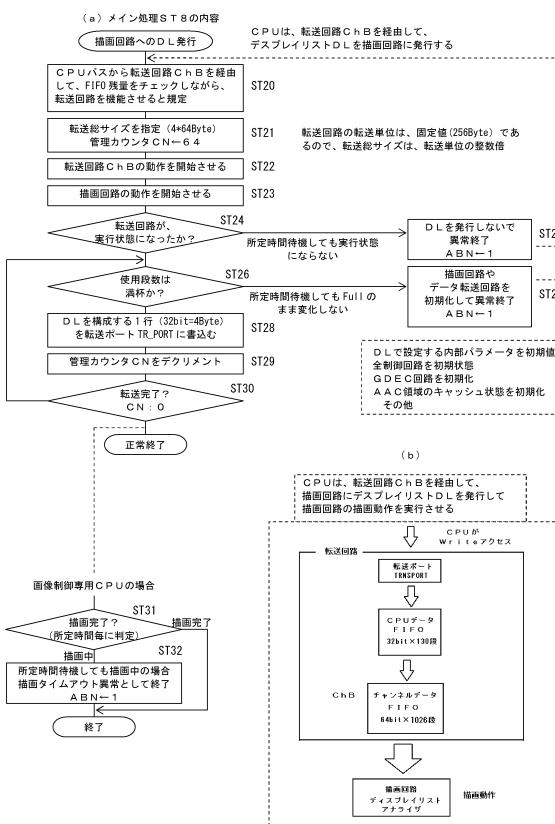

## 【0174】

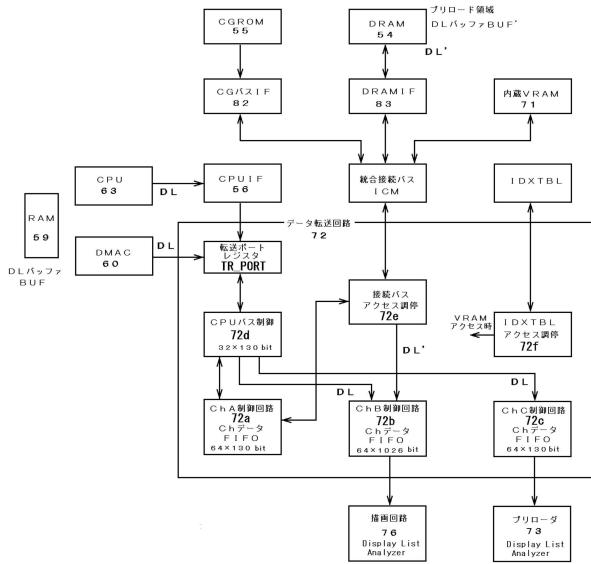

続いて、図5(a)に戻って説明を続けると、データ転送回路72は、VDP回路内部のリソース(記憶媒体)と外部記憶媒体を、転送元ポート又は転送先ポートとして、これらの間でDMA(Direct Memory Access)的にデータ転送動作を実行する回路である。図10は、このデータ転送回路72の内部構成を、関連する回路構成と共に記載したプロック図である。

## 【0175】

図10に示す通り、データ転送回路72は、ルータ機能を有する統合接続バスICMを経由して、CGROM55、DRAM54、及び、内蔵VRAM71とデータを送受信するよう構成されている。なお、CGROM55とDRAM54は、CGバスIF部82や、DMAIF部83を経由してアクセスされる。

10

## 【0176】

一方、CPU回路51は、データ転送回路72に内蔵された転送ポートレジスタTR\_PORTを経由して、描画回路76やプリローダ73にディスプレイリストDLを発行している。なお、CPU回路51とデータ転送回路72は、双方向に接続されているが、ディスプレイリストDLの発行時には、転送ポートレジスタTR\_PORTは、ディスプレイリストDLを構成する一単位のデータを受け入れるデータ書き込みポートとして機能する。なお、転送ポートレジスタTR\_PORTの書き込み単位(一単位データ長)は、CPUバス制御部72dの FIFO構造に対応して32bitとなる。

20

## 【0177】

図示の通り、演出制御CPU63は、CPUIF部81を経由して、転送ポートレジスタTR\_PORTをWRITEアクセスできる一方、DMAC回路60を活用する場合には、DMAC回路60が、転送ポートレジスタTR\_PORTを直接的にWRITEアクセスすることになる。そして、転送ポートレジスタTR\_PORTに書込まれた一連の指示コマンド(つまり、ディスプレイリストDLを構成する指示コマンド列)は、32bit単位で、FIFO構造(32bit×130段)のFIFOバッファを内蔵したCPUバス制御部72dに、自動蓄積されるよう構成されている。

## 【0178】

また、このデータ転送回路72は、3チャンネルChA~ChCの伝送経路で、データの送受信動作を実行しており、FIFO構造(64bit×N段)のFIFOバッファを有するChA制御回路72a(N=130段)と、ChB制御回路72b(N=1026段)と、ChC制御回路72c(N=130段)と、を有している。

30

## 【0179】

そして、CPUバス制御部72dに蓄積された指示コマンド列(ディスプレイリストDL)は、演出制御CPU63によるデータ転送レジスタRGij(各種制御レジスタ70の一種)への設定値に基づき、描画回路76か、又はプリローダ73に転送される。矢印で示す通り、ディスプレイリストDLは、CPUバス制御部72dから、ChB制御回路72bのFIFOバッファを経由して描画回路76に転送され、ChC制御回路72cのFIFOバッファを経由してプリローダ73に転送されるよう構成されている。

40

## 【0180】

なお、本実施例では、ChB制御回路72bと、ChC制御回路72bは、ディスプレイリストDLの転送動作に特化されており、CPUバス制御部72dのFIFOバッファに蓄積されたデータは、ChB制御回路72bか、ChC制御回路72cのFIFOバッファを経由して、各々、ディスプレイリストDLの一部として、描画回路76かプリローダ73のディスプレイリストアナライザ(Display List Analyzer)に転送される。

## 【0181】

そして、描画回路76は、転送されたディスプレイリストDLに基づいた描画動作を開始する。一方、プリローダ73は、転送されたディスプレイリストDLに基づき、必要なプリロード動作を実行する。プリロード動作によってCGROM55のCGデータが、DRAM54に確保されたプリロード領域に先読みされ、TXLOADコマンドなどに関して、テ

50

クスチャのSourceアドレスを変更したディスプレイリストDL（以下、書換えリストDL'）というが、DRAM54に確保されたDLバッファ領域BUF'に保存される。

#### 【0182】

一方、CGROM55、DRAM54、及び、内蔵VRAM71などの記憶媒体の間のデータ転送には、ChA制御回路72aと、接続バスアクセス調停回路72eとが機能する。また、インデックステーブルIDX\_TBLのアドレス情報が必要になる内蔵VRAM71のアクセス時には、IDX\_TBLアクセス調停回路72fが機能する。具体的に確認すると、ChA制御回路72aは、例えば、(a) CGROM55の圧縮データを内蔵VRAM71に転送する場合や、(b) CGROM55の圧縮データをプリロード(先読み)して外付けDRAM54に転送する場合や、(c) プリロード領域の先読みデータを、内蔵VRAM71に転送する場合に機能する。

10

#### 【0183】

ここで、ChA制御回路72aは、ChB制御回路72bやChC制御回路72cと並行して動作可能に構成されており、上記した(a)～(c)の動作は、ディスプレイリストDLの発行動作(図17のST8,図22のPT11)や、書換えリストDL'の転送動作(図22のPT10)と並行して実行可能となる。また、ChB制御回路72bとChC制御回路72cも、同時実行可能であり、例えば、ChB制御回路72bが機能する図22のステップPT10の処理と、ChC制御回路72cが機能するステップPT11の処理は並行して実行可能である。但し、転送ポートレジスタTR\_PORTは単一であるので、何れか一方(72b/72c)が転送ポートレジスタTR\_PORTを使用しているタイミングでは、他方(72c/72b)は、転送ポートレジスタTR\_PORTをアクセスすることはできない。

20

#### 【0184】

なお、ChA制御回路72aの動作時に、接続バスアクセス調停回路72eは、統合接続バスICMを経由する各記憶素子(CGROM55、DRAM54)とのデータ伝送を調停(Arbitration)している。一方、IDX\_TBLアクセス調停回路72fは、インデックステーブルIDX\_TBLに基づいてChA制御回路72aを制御することで、内蔵VRAM71とのデータ交信を調停している。なお、プリローダ73が機能する実施例の場合、DRAM54のDLバッファ領域BUF'に保存された書換えリストDL'は、接続バスアクセス調停回路72eと、ChB制御回路72bを経由して描画回路76に転送されることになる(図23(b)参照)。

30

#### 【0185】

上記の通り、本実施例のデータ転送回路72は、各種の記憶リソース(Resource)から任意に選択されたデータ転送元と、各種の記憶リソース(Resource)から任意に選択されたデータ転送先との間で、高速のデータ転送を実現している。図10から確認される通り、データ転送回路72が機能する記憶リソースには、内蔵VRAM71だけでなく、CPUIF部56、CGバスIF部82、DRAMIF部83を経由する外部デバイスも含まれる。

30

#### 【0186】

そして、CGROM55から1回に取得すべきデータ量(メモリシーケンシャルREAD)のように、ChA制御回路72aが機能する外部デバイスとのデータ転送量は、ChB制御回路72bやChC制御回路72cが機能するディスプレイリストDLの場合と比較して膨大であり、互いに、データ転送量が大きく相違する。

40

#### 【0187】

ここで、これら各種のデータ転送について、単位データ量や総転送データ量を、細かく設定可能に構成することも考えらえるが、これでは、VDP内部の制御動作が煩雑化し、円滑な転送動作が阻害される。そこで、本実施例では、データ転送の最低データ量Dminを一意に規定すると共に、総転送データ量を、最低データ量D Tminの整数倍となるよう制限することで、高速で円滑なデータ転送動作を実現している。特に限定されないが、実施例のデータ転送回路72では、最低データ量Dmin(単位データ量)を、256バ

50

イトとし、総転送データ量を、この整数倍に制限することにしている。

【0188】

したがって、32bit毎にCPUバス制御部72dの FIFO バッファに蓄積されたディスプレイリスト DL の指示コマンド列は、その総量が最低データ量 Dmin に達したタイミングで、ChB 制御回路 72b や ChC 制御回路 72b に転送され、各々の FIFO バッファに蓄積されることになる。

【0189】

ディスプレイリスト DL は、一連の指示コマンドで構成されているが、本実施例では、転送ポートレジスタ TR\_PORT の書き込み単位 (32bit) に対応して、ディスプレイリスト DL は、コマンド長が、32bit の整数 N 倍 ( $N > 0$ ) の指示コマンドのみで構成されている。したがって、データ転送回路 72 を経由して、ディスプレイリスト DL の指示コマンドを受ける描画回路 76 やプリローダ 73 は、素早く円滑にコマンド解析処理 (DL analyze) を開始することができる。なお、32bit の整数 N 倍のコマンド長は、その全てが有意ビットとは限らず、無意ビット (Don't care bit) も含んで、32bit の整数 N 倍という意味である。

10

【0190】

次に、プリローダ 73 について説明する。先に概略説明した通り、プリローダ 73 は、データ転送回路 72 (ChC 制御回路 72b) から転送されたディスプレイリスト DL を解釈して、TXLOAD コマンドが参照している CGROM55 上の CG データを、予め、DRAM54 のプリロード領域に転送する回路である。また、プリローダ 73 は、この TXLOAD コマンドに関し、CG データの参照先を、転送後のアドレスに書換えた書換えリスト DL' を、DRAM54 の DL バッファ BUF' に記憶する。なお、DL バッファ BUF' や、プリロード領域は、CPUリセット後の初期処理時 (図 17 の ST3) に、予め確保されている。

20

【0191】

そして、書換えリスト DL' は、描画回路 76 の描画動作の開始時に、データ転送回路 72 の接続バスアクセス調停回路 72e や、ChB 制御回路 72b を経由して、描画回路 76 のディスプレイリストアナライザ (DL Analyzer) に転送される。そして、描画回路 76 は、書換えリスト DL' に基づいて、描画動作を実行する。したがって、TXLOAD コマンドなどに基づき、本来は、CGROM55 から取得すべき CG データが、プリロード領域に先読みされているプリロードデータとして、DRAM54 のプリロード領域から取得される。この場合、プリロードデータは、上書き消去されない限り、繰り返し使用可能であり、プリロード領域にキャッシュヒットしたプリロードデータは、繰り返し再利用される。

30

【0192】

本実施例では、十分な記憶容量を有する外付け DRAM54 にプリロード領域を設定しているので、上記のキャッシュヒット機能が有効に機能する。また、外付け DRAM54 の記憶容量が大きいので、例えば、複数フレーム分の CG データを一気にプリロードする多重プリロードも可能である。すなわち、プリローダ 73 の動作期間に關し、CG データの先読み動作を含んだ一連のプリロード動作の動作期間を、VDP 回路 52 の間欠動作時の動作周期 の整数倍の範囲内で、適宜に設定することで多重プリロードが実現される。

40

【0193】

但し、以下の説明では、便宜上、多重プリロードのない実施例について説明するので、実施例のプリローダ 73 は、一動作周期 ( ) の間に、一フレーム分のプリロード動作を完了することにする。なお、図 17 に關し後述するように、本実施例では、VDP 回路 52 の間欠動作時の動作周期 は、表示装置 DS1 の垂直同期信号の 2 倍周期である 1 / 30 秒である。

【0194】

次に、描画回路 76 は、データ転送回路 72 を経由して転送されたディスプレイリスト DL や書換えリスト DL' の指示コマンド列を順番に解析して、グラフィックスデコーダ 75 やジオメトリエンジン 77 などと協働して、VRAM71 に形成されたフレームバッファ

50

に、各表示装置 D S 1 , D S 2 の一フレーム分の画像を描画する回路である。

【 0 1 9 5 】

上記の通り、プリローダ 7 3 を機能させる実施例では、書換えリスト D L ' の C G データの参照先は、 C G R O M 5 5 ではなく、 D R A M 5 4 に設定されたプリロード領域である。そのため、描画回路 7 6 による描画の実行中に生じる C G データへのシーケンシャルアクセスを迅速に実行することができ、動きの激しい高解像度の動画についても問題なく描画することができる。すなわち、本実施例によれば、 C G R O M 5 5 として、安価な S A T A モジュールを活用しつつ、複雑高度な画像演出を実行することができる。

【 0 1 9 6 】

ところで、プリローダ 7 3 を機能させるか否かに拘らず、ディスプレイリスト D L や書換えリスト D L ' の転送時に、仮にデータ化けが発生しても、描画回路 7 6 は、これを検出することはできない。また、ノイズなどの影響で、描画回路 7 6 がフリーズして、内蔵 V R A M 7 1 の READ / WRITE アクセスが異常停止することも有り得る。そこで、本実施例では、描画回路 7 6 が不合理な指示コマンド (analyze 不能のビット並び) を検出した場合や、一定期間、内蔵 V R A M 7 1 に対して READ / WRITE アクセスがない場合には、描画異常割込みを発生させるよう構成されている (描画異常割込みが許可状態)。なお、この点は、図 1 7 ( d ) に関して後述する。

【 0 1 9 7 】

次に、図 9 に関して説明した通り、 V R A M 7 1 の任意領域 (c) に確保されたフレームバッファ F B は、描画領域と読み出領域に区分されたダブルバッファであり、 2 つの領域を、交互に用途を切り替えて使用する。また、本実施例では、 2 つの表示装置 D S 1 , D S 2 が接続されているので、図 9 に示す通り、 2 区画のフレームバッファ F B a / F B b が確保されている。したがって、描画回路 7 6 は、表示装置 D S 1 用のフレームバッファ F B a の描画領域 (書き込み領域) に、一フレーム分の画像データを描画すると共に、表示装置 D S 2 用のフレームバッファ F B a の描画領域 (書き込み領域) に、一フレーム分の画像データを描画することになる。なお、描画領域に、画像データが書き込まれているとき、表示回路 7 4 は、他方の読み出領域 (表示領域) の画像データを読み出して、各表示装置 D S 1 , D S 2 に出力する。

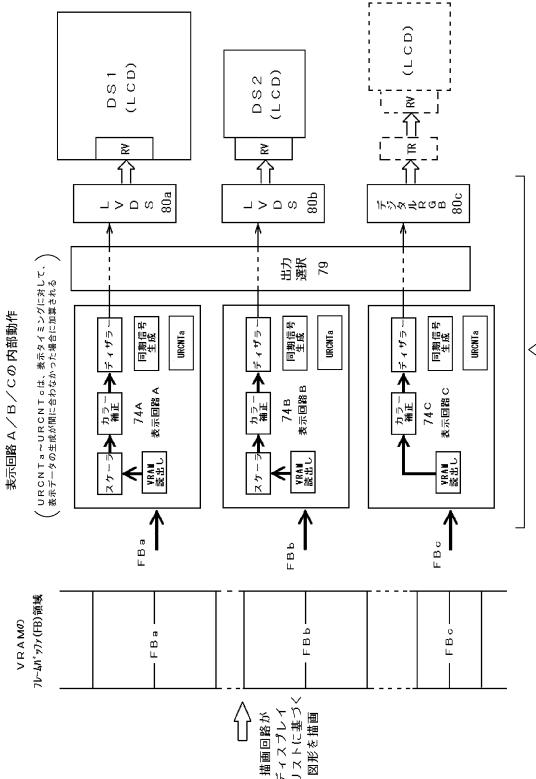

【 0 1 9 8 】

表示回路 7 4 は、フレームバッファ F B a , F B b の画像データを読み出して、最終的な画像処理を施した上で出力する回路である (図 1 1 ) 参照)。最終的な画像処理には、例えば、画像を拡大 / 縮小するスケーラのスケーリング処理、微妙なカラー補正処理、画像全体の量子化誤差が最小化するディザリング処理が含まれている。そして、これらの画像処理を経たデジタル R G B 信号 (合計 2 4 b i t ) が、水平同期信号や垂直同期信号と共に出力される。図 1 1 に示す通り、本実施例では、上記の動作を並列的に実行する 3 系統の表示回路 A / B / C が設けられており、各表示回路 7 4 A ~ 7 4 C は、各々に対応するフレームバッファ F B a / F B b / F B c の画像データを読み出して、上記の最終画像処理を実行する。但し、本実施例では、表示装置は 2 個であるので、フレームバッファ F B c は確保されておらず、表示回路 7 4 C が機能することもない。

【 0 1 9 9 】

この動作に関連して、この実施例の出力選択部 7 9 は、表示回路 7 4 A の出力信号を、 L V D S 部 8 0 a に伝送し、表示回路 7 4 B の出力信号を、 L V D S 部 8 0 b に伝送している (図 1 1 )。そして、 L V D S 部 8 0 a は、画像データ (合計 2 4 b i t のデジタル R G B 信号) を L V D S 信号に変換して、クロック信号を伝送する一対を加えて、全五対の差動信号としてメイン表示装置 D S 1 に出力している。なお、メイン表示装置 D S 1 には、 L V D S 信号の変換受信部 R V が内蔵されており、 L V D S 信号から R G B 信号を復元して、表示回路 7 4 A の出力に対応する画像を表示している。

【 0 2 0 0 】

この点は、 L V D S 部 8 0 b も同様であり、各 8 b i t のデジタル R G B 信号の合計 2 4 b i t について、クロック信号を伝送する一対を加えて、全五対の差動信号として変換受

10

20

30

40

50

信部 R V に出力し、サブ表示装置 D S 2 が変換受信部 R V から受ける合計 2 4 b i t の R G B 信号による画像表示を実現している。そのため、サブ表示装置 D S 2 と、メイン表示装置 D S 1 は、2 8 \* 2 8 \* 2 8 の解像度を有することになる。

#### 【 0 2 0 1 】

なお、必ずしも L V D S 信号とする必要は無く、例えば伝送距離が短い場合には、デジタル R G B 信号を、デジタル R G B 部 8 0 c を経由して、そのまま表示装置に伝送するか、或いは、伝送距離が長い場合には、デジタル R G B 信号を、変換送信部 T R ' において、V - B y - o n e (登録商標) 信号に変換して変換受信部 R V ' に伝送した後、変換受信部 R V ' においてデジタル R G B 信号に戻すのも好適である。なお、図 1 1 の破線は、この動作態様を示しているが、出力選択部 7 9 の動作を適宜に設定することで、表示回路 7 4 A ~ 7 4 C の何れの出力信号であっても上記の動作が可能となる。

10

#### 【 0 2 0 2 】

ところで、本実施例の場合、各表示回路 7 4 A ~ 7 4 B には、表示タイミングに対して、表示データの生成が間に合わなかった Underrun 異常をカウントするアンダーランカウンタ U R C N T a ~ U R C N T c が設けられている（図 1 1 参照）。そして、このアンダーランカウンタ U R C N T a ~ U R C N T c のカウンタ値は、アンダーラン異常が発生すると VBLANK 毎に自動的に加算されるよう構成されている。

#### 【 0 2 0 3 】

次に、S M C 部 7 8 (Serial Management Controller) は、L E D コントローラと M o t o r コントローラとを内蔵した複合コントローラである。そして、外部基板に搭載した L E D / M o t o r ドライバ（シフトレジスタを内蔵するドライバ I C ）に対して、クロック信号に同期して L E D 駆動信号やモータ駆動信号を出力する一方、適宜なタイミングで、ラッチパルスを出力可能に構成されている。

20

#### 【 0 2 0 4 】

上記した V D P 回路 5 2 の内部回路及びその動作に関し、内部回路が実行すべき動作内容は、演出制御 C P U 6 3 が、制御レジスタ群 7 0 に設定する動作パラメータ（設定値）で規定され、V D P 回路 5 2 の実行状態は、制御レジスタ群 7 0 の動作ステータス値を R E A D することで特定できるようになっている。制御レジスタ群 7 0 は、演出制御 C P U 6 3 のメモリマップ上、1 M バイト程度のアドレス空間（0 ~ F F F F F H ）にマッピングされた多数の V D P レジスタ R G i j を意味し、演出制御 C P U 6 3 は、C P U I F 部 8 1 を経由して動作パラメータの W R I T E （設定）動作と、動作ステータス値の R E A D 動作を実行するようになっている（図 5 ( b ) 参照）。

30

#### 【 0 2 0 5 】

制御レジスタ群 7 0 (V D P レジスタ R G i j ) には、割り込み動作などシステム動作に関する初期設定値が書き込まれる「システム制御レジスタ」と、内蔵 V R A M に A A C 領域(a) やページ領域(b) を確定する共に、インデックステーブル ID X T B L を構築又は変更などに関する「インデックステーブルレジスタ」と、演出制御 C P U 6 3 と V D P 回路 5 2 の内部回路との間のデータ転送回路 7 2 によるデータ転送処理に関する設定値などが書き込まれる「データ転送レジスタ」と、グラフィックスデコーダ 7 5 の実行状況を特定する「 G D E C レジスタ」と、指示コマンドや描画回路 7 6 に関する設定値が書き込まれる「描画レジスタ」と、プリローダ 7 3 の動作に関する設定値が書き込まれる「プリローダレジスタ」と、表示回路 7 4 の動作に関する設定値が書き込まれる「表示レジスタ」と、L E D コントローラ (S M C 部 7 8 ) に関する設定値が書き込まれる「 L E D 制御レジスタ」と、M o t o r コントローラ (S M C 部 7 8 ) に関する設定値が書き込まれる「モータ制御レジスタ」と、音声回路 S N D に関する設定値が書き込まれる「音声制御レジスタ S R G 」と、が含まれている。但し、本実施例では、音声回路 S N D を活用していない。

40

#### 【 0 2 0 6 】

何れにしても、以下の説明では、制御レジスタ群 7 0 に含まれる一又は複数のレジスタ R G i j を、上記した個別名称で呼ぶ場合と、V D P レジスタ R G i j と総称することがあるが、何れにしても、演出制御 C P U 6 3 は、所定の V D P レジスタ R G i j に、適宜な

50

設定値を書込むことで、VDP回路52の内部動作を制御している。具体的には、演出制御CPU63は、適宜な時間間隔で更新するディスプレイリストDLと、所定のVDPレジスタRGijへの設定値に基づいて、所定の画像演出を実現している。なお、この実施例では、ランプ演出やモータ演出も含め、演出制御CPU63が担当するので、VDPレジスタRGijには、LED制御レジスタやモータ制御レジスタも含まれる。

#### 【0207】

続いて、上記したCPU回路51とVDP回路52とを内蔵した複合チップ50によって実現される、画像演出、音声演出、モータ演出、及び、ランプ演出の統一的な演出制御動作について説明する。

#### 【0208】

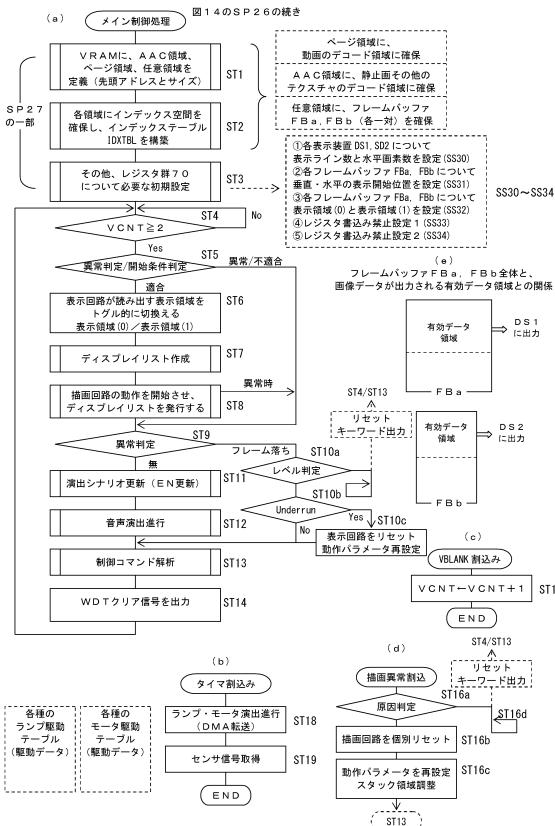

本実施例の場合、複合チップ50の動作は、電源投入や異常リセットによるパワーオンリセット動作(図12(a)参照)によって開始され、初期設定プログラム(ブートプログラム)Pininitによる初期設定処理(SP1~SP9)を経て、演出制御プログラムMain及び割込み処理プログラム(ベクタハンドラ)Voptによるメイン制御処理(SP10)に移行するよう構成されている。メイン制御処理については、図14(a)に、その導入部の処理内容が記載されており、本体部の処理内容が図17(a)に記載されている。なお、図14のステップSP27の処理は、図17(a)のステップST1~ST3の処理を含んでいる。

#### 【0209】

以上を踏まえて、パワーオンリセット動作について図12(a)に基づいて説明する。電源投入時など、システムリセット信号SYSが所定の期間(アサート期間)Lレベルを維持すると、全ての動作制御レジスタREGや、全てのVDPレジスタRGijは、所定のデフォルト値に自動設定される。そして、その後、システムリセット信号SYSがHレベル(ネガートレベル)に変化すると、本実施例では、最初に、アドレス空間CS0の先頭番地からの32bitデータが、演出制御CPU63のプログラムカウンタPCに設定され、これに続く32bitデータが、スタックポインタSPに設定されるよう構成されている。なお、図7や図13(c)では、プログラムカウンタPCやスタックポインタSPの初期値を記憶するメモリの先頭領域をベクタテーブルVECTと称している。

#### 【0210】

図12(b)に示す通り、このベクタテーブルVECTには、優先度と割込み要因などを特定するベクタ番号と、アドレス情報とが対応して記憶されている。ベクタ番号は、その番号が小さいほど優先度が高いが、例えば、ベクタ番号11は、マスク不能割込み(NMI)であって、アドレス情報として、NMI割込み時に実行される割込み処理プログラムの先頭アドレスが記憶されている。また、ベクタ番号64は、VDPからの内部割込み(VDP\_IRQ0)であって、アドレス情報として、VDP\_IRQ0割込み時に実行される割込み処理プログラムの先頭アドレスが記憶されている。

#### 【0211】

割込み優先度は、図14(d)に示す通りであるので、ベクタ番号64より小さいベクタ番号の欄には、制御コマンド受信割込みIRQ\_CMDと、20μSタイマ割込みと、1mSタイマ割込みについて、割込み処理プログラムの先頭アドレスが各々記憶されることになる。一方、ベクタ番号64より大きいベクタ番号の欄には、VDP\_IRQ1より優先度が低い割込み処理プログラム(IRQ\_SND, IRQ\_RTCなど)の先頭アドレスが各々記憶されている。

#### 【0212】

また、ベクタテーブルVECTにおいて、ベクタ番号0とベクタ番号1は、パワーオンリセット時にCPUのプログラムカウンタと、スタックポインタに自動設定されるべき、設定値が規定されている。図12(b)に示す通り、この実施例では、パワーオンリセット時(リセットアサート期間)の内部動作として、4バイトデータ「\*\*\*\*\*」が、プログラムカウンタPCに設定され、4バイトデータ「++++」がスタックポインタSPに設定される。なお、「\*\*\*\*\*」は、アドレス空間CS0に不揮発的に記憶されている初期

10

20

30

40

50

設定プログラム `P init` (図 12 の SP1 ~ SP9) の先頭アドレス値であり、「++」は、内蔵 RAM59 に確保された、LIFO (Last-In First-Out) 方式で機能するスタック領域の先端又は終端のアドレス値である。

#### 【0213】

なお、本実施例では、レジスタバンク `RBi` を有効活用するので、割込み処理時に、スタック領域が消費されることなく、それほどのメモリ容量は必要とされない。すなわち、本実施例では、スタック領域は、専ら、関数処理や、サブルーチン処理において活用される。

#### 【0214】

以上の動作の結果、その後、演出制御 `CPU63` は、アドレス値「\*\*\*\*」以降に記載された初期設定プログラム `P init` を実行することになる。但し、アドレス空間 `CS0` のメモリ READ 動作は、バスステートコントローラ 66 (図 6) の動作を規定する動作制御レジスタ `REG` のデフォルト値 (初期値) に基づいて実行される。この動作制御レジスタ `REG` の初期値は、リセットアサート期間 (システムリセット信号 `SYS` が L レベルを維持する図 4 (d) に示す期間) に自動的に設定される値であり、アドレス空間 `CS0` を、如何なるメモリデバイスで構成しても、問題なく READ アクセスできるよう、最遅 READ アクセス動作 (デフォルトアクセス動作) に設定されている。

10

#### 【0215】

そこで、このデフォルトアクセス動作を、最適なアクセス動作に変更するべく、最初に、アドレス空間 `CS0` に対するバスステートコントローラ 66 (図 6) の動作を規定する所定の動作制御レジスタ `REG` に最適値を設定する (SP1)。すなわち、初期設定プログラム `P init` (SP1 ~ SP9)、演出制御プログラム `MainB` (SP10)、定数データなどを格納した `PROM53` をアクセスする場合のメモリ READ 動作を、メモリデバイスに合わせて最適化するべく、バス幅やページアクセスの有無を設定すると共に、チップセレク信号 `CS0` や、READ 制御信号や、WRITE 制御信号その他の動作タイミングを最適設定する (図 35 参照)。

20

#### 【0216】

以上の設定の結果、ステップ SP2 以降の処理は、アドレス空間 `CS0` に記憶されているプログラムを、最適にメモリ READ して実行されることになる。そこで、次に、演出制御 `CPU63` が、`VDP` レジスタ `RGij` をアクセスする場合の READ / WRITE アクセス動作を最適化するべく、`VDP` レジスタ `RGij` に対するバスステートコントローラ 66 (図 6) の動作を規定する所定の動作制御レジスタ `REG` に最適値を設定する (SP2)。

30

#### 【0217】

先に説明した通り、本実施例では、`VDP` レジスタ `RGij` は、演出制御 `CPU63` のアドレス空間 `CS7` に位置付けられているので、チップセレク信号 `CS7` や、その他の制御信号の動作タイミングを最適設定するべく所定の動作制御レジスタ `REG` に所定値を書き込むことになる。

#### 【0218】

続いて、特定の `VDP` レジスタ `RGij` のレジスタ値を読み出して、その値が所定値 (デバイスコード) か否かを判定する (SP3)。これは、`VDP` 回路 52 のシステムクロックが安定化したことの確認判定である。すなわち、`VDP` 回路 52 は、PLLREF 端子に供給される発振器 `OSC2` の発振出力に基づいて動作するが、この `VDP` 回路 52 が、`CPU` 回路 51 からの指令 (つまり、`VDP` レジスタ `RGij` への設定など) を正常に受け付け可能か否かの判定である。

40

#### 【0219】

そして、デバイスコードの読み出し処理 (SP3) によって、システムクロックが安定化したことが確認できれば、その後は、`VDP` 回路 52 の正常動作を期待できるので、所定の `VDP` レジスタ `RGij` に対する設定処理を実行する (SP4 ~ SP6)。具体的には、先ず、演出制御 `CPU63` から `VDP` レジスタ `RGij` をアクセスする場合のエンディアン設定 (ビッグ / リトル) や、データバス幅を設定する (SP4)。

#### 【0220】

50

なお、本実施例では、設定値の最上位ビット(Most significant Bit)を、VDPレジスタRGijの最上位ビットに格納するピックエンディアンに設定し、データ32バス幅を32bitに設定するが、これらの設定値が、仮に、デフォルト値と同じであれば、これらの設定処理を省略することもできる(以下の処理も同様)。

#### 【0221】

次に、VDP回路からCPU回路への内部割込み(VDP\_IRQ0, VDP\_IRQ1, VDP\_IRQ2, VDP\_IRQ3)について、割込み有意レベル(H/L)を設定し、PLLREF端子(図5(a)参照)へのクロック信号(リファレンスクロック)に基づいてDDR(DRAM54)を機能させる旨を設定する(SP4)。なお、PLLREF端子に、発振器OSC2のリファレンスクロックが供給されることは図5(a)に関して説明した通りである。

10

#### 【0222】

続いて、図7に示すメモリマップを実現するべく、アドレス空間CS1~CS6を定義する(SP5)。先に説明した通り、アドレス空間CS3は、音声プロセッサ27の内部レジスタに付与され、アドレス空間CS4は、RTC38の内部レジスタやSRAM39のアドレス空間に付与され、アドレス空間CS5は、外付けDRAM(DDR)54に付与され、アドレス空間CS6は、内蔵CPUのワークメモリ57に付与される。

#### 【0223】

なお、VDPレジスタRGijが、アドレス空間CS7に割り当てられることは固定的に規定されているので、アドレス空間CS7の定義処理は不要である。また、アドレス空間CS0は、CPU回路51のメモリマップ0x00000000番地以降であることは予め固定的に規定されており、この規定を前提として、アドレス空間CS0が、CGROM55に確保されているか、その他のメモリデバイスに付与されるかは、HBTSL端子のH/Lレベルで規定される。

20

#### 【0224】

先に説明した通り、本実施例では、HBTSL端子=Lとなっており、CGROM55以外にアドレス空間CS0が定義されていることが示されている。そして、CGROM55以外である制御メモリ53の具体的なバス幅や、最適なアクセス動作については、ステップSP1において設定済みであるので、アドレス空間CS0についても、ステップSP5の処理は不要である。

30

#### 【0225】

続いて、ステップSP5の処理で定義されたアドレス空間CS1~CS6について、各アドレス空間CSiをアクセスする場合のバス幅やページアクセスの有無について、所定の動作制御レジスタREGに所定値を書込む(SP6)。また、チップセレク信号CSiその他を最適設定するべく、所定の動作制御レジスタREGに所定値を書込む(SP6)。これらの処理は、ステップSP1やSP2の処理と同様の内容であり、バスステートコントローラ66(図6)の動作を規定する動作制御レジスタへの書き込み処理によって、チップセレク信号CSi、READ制御信号、WRITE制御信号、その他の動作タイミングが最適に設定される。

#### 【0226】

続いて、WDT回路58にクリア信号を出力することで、異常リセットを回避する(SP7)。これは、電源投入後、WDT回路58が自動的に動作を開始することを考慮したものであり、この後も、繰り返し同様の処理が実行される。なお、ステップSP9の処理は、サブルーチンSP7として制御メモリ53に格納されているが、ステップSP9の終了時までは、制御メモリ53のサブルーチンSP7が呼び出され、ステップSP9の終了後は、外付けDRAM54に転送された別のサブルーチンSP7'が呼び出されて実行される。

40

#### 【0227】

続いて、アドレス空間CS0に格納されているプログラムやデータのうち、図12(b)や図13(c)に示すベクタハンドラVopt(割込み処理プログラム)、エラー復帰処理プログラムPiram、演出制御プログラムMainB、初期値有り変数D、及び、定

50

数データCを、外付けDRAM54や、内蔵RAM59に転送する(S P 8)。なお、初期値有り変数Dとは、所定の変数領域に記憶されている初期値データを意味する。このメモリセクションの初期化処理(S P 8)は、演出制御処理の高速化を図るため、プログラムやデータを転送する処理であり、アクセス速度に劣るROMへのアクセスを回避するための処理である。

#### 【0228】

そして、次に、レジスタバンクRBiを使用する旨の設定をする(S P 9)。そのため、その後は、割込み処理時に、レジスタバンクRB0～RB14が機能することになり、割込み処理が迅速化されると共に、スタック領域の消費が緩和される。

#### 【0229】

以上の処理は、アドレス空間CS0である制御メモリ53に格納されている「初期設定プログラムPininit」の実行によって実現される(図13(c)参照)。そして、この初期設定プログラムPininitの実行が終われば、続いて、演出制御プログラムMainによるメイン制御処理を実行する(S P 10)。ここで、メイン制御処理の実行とは、ステップS P 8の転送処理によって、制御メモリ53から外付けDRAM54に転送された「演出制御プログラムMain」の実行を意味する(図12(b)参照)。

10

#### 【0230】

メイン制御処理(演出制御プログラムMain)の具体的な内容については、図14(a)や、図17(a)に基づいて説明するが、それに先行して、メモリセクションの初期化処理(S P 8)について説明する。図13(a)に示す通り、メモリセクションの初期化処理(S P 8)では、最初に複数チャネルのDMACを動作停止状態に初期設定する。なお、この処理は、念のための形式的な処理に過ぎない。

20

#### 【0231】

以上の処理が終われば、所定チャネルのDMACiを起動させて、制御メモリ53の記憶されているベクタハンドラVopt(割込み処理プログラム)を、内蔵RAM59に、ノンストップ転送方式(図8(b3)参照)でDMA転送する。本実施例では、割込み処理プログラムVoptを内蔵RAM59に転送するので、外付けDRAM54の異常時においても、適切な異常対応処理が可能となる。

#### 【0232】

その後の処理も同じであり、所定チャネルのDMACiを使用して、ノンストップ転送方式で実行され、エラー復帰処理プログラムPiramを内蔵RAM59にDMA転送する(S P 62)。本実施例では、エラー復帰処理プログラムPiramを内蔵RAM59に転送するので、エラー復帰処理において、周辺回路を確実にリセット状態にすることができる。例えば、エラー復帰処理プログラムPiramを、内蔵RAM59以外の例えば外付けDRAM54に転送すると、エラー復帰処理時に、外付けDRAM54をリセット処理できないことになる。

30

#### 【0233】

次に、演出制御プログラムMainを、外付けDRAM54にDMA転送し(S P 63)、定数データCを、外付けDRAM54にDMA転送する(S P 64)。定数データには、演出抽選に使用する抽選データや、図17(b)に示す各種の駆動データテーブルにおける、ランプ駆動データやモータ駆動データが含まれる。また、初期値の有る変数Dを、外付けDRAM54にDMA転送するが(S P 65)、これら何れも、所定チャネルのDMACiを使用したノンストップ転送方式で実行される。

40

#### 【0234】

最後に、外付けDRAMの変数領域Bの先頭にクリアデータを書込む(S P 66)。この先頭アドレスを、仮にADbとすると、その後のDMA転送処理では、転送元アドレスをADbとし、転送先アドレスをADb+1と初期設定した後、各アドレス値ADb, ADb+1をインクリメント処理しつつ、このクリアデータを拡散させることで、変数領域Bのクリア処理を実行することになる(S P 67)。

#### 【0235】

50

以上説明したステップSP61～SP66、及びステップSP67の処理は、何れも、類似の動作であり図13(b)に示す通りである。すなわち、先ず、所定チャネルのDMA Ciに関し、DMA転送条件として、(1)サイクルスチール転送モード、(2)ノンストップ転送方式を探り、(3)SourceとDestinationのアドレス値をincrement更新すると、設定する(SP68)。

#### 【0236】

次に、転送元Sourceアドレスと、転送先Destinationアドレスの初期値を設定し(SP69)、転送サイズを設定し、割込み禁止などに設定した上で(SP70)、DMA転送の動作を開始させる(SP71)。なお、ステップSP68～SP71の設定は、何れも所定の動作制御レジスタREGへの設定動作によって実現される。

10

#### 【0237】

このメモリセクションの初期化処理では、DMA転送終了の割込みを禁止設定しているので(SP70)、DMA転送の動作を開始させた後は、所定の動作制御レジスタREGのステータスフラグを、繰り返しREADアクセスして、DMA転送の終了を待つ(SP72)。但し、動作終了までの処理時間を考慮して、WDT回路58に対して、クリア信号を繰り返し出力する(SP73)。そして、DMA転送の終了時には、所定の動作制御レジスタREGへの設定動作に基づいてDMACiを停止設定する。

#### 【0238】

続いて、メイン制御処理の動作内容について図14～図17に基づいて説明する。先に説明した通り、メイン制御処理については、図14(a)に、その導入部(SP20～SP27)の処理内容が記載されており、本体部(ST4～ST14)の処理内容が図17(a)に記載されている。なお、図14のステップSP27の処理は、図17(a)のステップST1～ST3の処理を含んでいる。

20

#### 【0239】

図14(a)に示す通り、メイン制御処理(導入部)では、最初に、CGROM55について、そのバス幅やROMデバイスの種別を特定する(SP20)。具体的には、図15(a)に示す通りであり、CGROM55とのインターフェイスを司るCGバスの動作状態を特定する所定のVDPレジスタRGij(例えばCGバスStatusレジスタ)をREADアクセスして(SP80)、CGバスについて動作設定が可能か否かを判定する(SP81)。

30

#### 【0240】

ここで、CGバスStatusレジスタの値が1であれば、CGバスの内部回路がリセット動作中であることを意味し、VDPレジスタRGijへの設定値を受け付けることができないことを意味する。そこで、CGバスStatusレジスタの値が1から0に変化していることを確認した上で(SP81)、CGROMを構成するメモリデバイスに対応して規定可能なデバイス区間(SPA0～SPA\_n)毎に(1)各デバイス区間SPAiの有効/無効、(2)ROMデバイスの種別、(3)データバス幅などの動作パラメータを、所定のVDPレジスタRGijに設定する(SP82)。

#### 【0241】

図14(a)に示す通り、この実施例では、CGROM55を複数領域(デバイス区間)に区分できるようになっており、例えば、デバイス区間(SPA0～SPA\_n)毎に、メモリデバイスや、データバス幅を選択可能に構成されている。メモリデバイスとしては、例えば、(1)本実施例で採用するSATAモジュール(AHSI/F)、(2)パラレルI/F(Interface)形式を採るメモリ素子、(3)シーケンシャルI/F形式を採るメモリ素子などに大別されるが、大別されたメモリデバイスごとに、メモリデバイスを具体的に選択可能であり、且つ、データバス幅などを任意に規定できるようになっている。

40

#### 【0242】

次に、デバイス区間(SPA0～SPA\_n)毎に選択されたメモリデバイスとのメモリREAD動作を最適化するべく、所定の動作パラメータを、所定のVDPレジスタRGijに設定する(SP83)。動作パラメータには、チップセレクト信号と、その他の制御信号(

50

READ制御信号など)との動作タイミングを規定する設定値が含まれている。また、シーケンシャルI/F形式を採るメモリ素子が選択された場合には、図15(b)も示す動作を実現するべく、アドレスラッチの出力タイミングや、読み出しクロック数なども特定される。

#### 【0243】

したがって、種類の異なるメモリデバイスを組合せてCGROM55を構成することもできる。但し、本実施例では、SATAモジュールだけを使用してCGROM55を構成し、デバイス区間(SPA0)だけを有効化し、他のデバイス区間(SPA1~SPAn)を無効化している。

#### 【0244】

何れにしても、ステップSP82~SP83の設定処理が終われば、その設定処理の実効化を図るべく、所定のVDPレジスタRGijに所定値を書き込む(SP84)。これは、CGバスの内部回路がステップSP82~SP83の設定処理に対応して動作できるまでに所定の時間を要することを考慮したものであり、内部回路の動作中は、前記したCGバスStatusレジスタ(SP80参照)の値が0となる。

10

#### 【0245】

したがって、その後は、CGバスStatusレジスタを繰り返しREADアクセスして(SP85)、Statusレジスタの値が1から0に戻ることを確認して処理を終える(SP86)。なお、所定回数の判定に拘らず、Statusレジスタの値が1から0に戻らない場合に、ステップSP66の処理を終えても良い。但し、その場合CGROMが正常にアクセスできない状態で遊技処理が始まるので、その後、何れかのタイミングでWDT回路58が起動して複合チップ50が異常リセット状態になる。そして、この場合は、再度、パワーオンリセット動作が実行されることになる。

20

#### 【0246】

一方、図14のステップSP20の処理が、正常に実行された後は、割込みコントローラINTCや、DMA C回路60や、マルチファンクションタイマユニットMTUなど、CPU回路51の内蔵回路をソフトウェア処理によって個々的に初期化する(SP21)。

#### 【0247】

次に、マルチファンクションタイマユニットMTUについて、所定のタイマ計測動作を開始させた後(SP22)、内部割込み及び内部割込みについて、所定の動作制御レジスタREGに許可設定値を書き込んで割込み許可状態に設定する(SP23)。

30

#### 【0248】

その結果、その後は、図14(d)に示す各種の割込みが生じ得ることになる。通常、このタイミングでは、音声プロセッサ27は、その初期化シーケンスを終えているので、図4(c)に示す通り、終了割込み信号IRQ\_SNDはLレベルに降下している筈である。そのため、図14(c)に示す割込み処理が起動され、演出制御CPU63は、エラーフラグERRを1に初期設定すると共に、アドレス空間CS3をREADアクセスして(SP30)、音声プロセッサ27の所定の音声レジスタSRGの値を取得して、初期化シーケンスが正常に終了しているか否かを判定する(SP31)。

#### 【0249】

そして、万一、初期化シーケンスが正常に終了していない場合には、演出制御CPU63は、音声プロセッサ27の所定の音声レジスタSRGにリセットコマンドを書き込むと共に(SP32)、1に初期設定されているエラーフラグERRを2にセットする(SP33)。このエラーフラグERRは、音声プロセッサ初期化処理(SP26)を実行するか否かを規定しており、エラーフラグERR=1がステップSP26の実行条件となっている。

40

#### 【0250】

一方、音声プロセッサ27は、リセットコマンドを受けたことに対応して、終了割込み信号IRQ\_SND=Hレベルの状態で、再度、初期化シーケンスを開始し、初期化シーケンスが終われば、終了割込み信号IRQ\_SNDはLレベルに降下させる。この結果、図14(c)の処理が再実行されることになる。

50

**【0251】**

以上、初期化シーケンスが正常に終了していない例外的な場合について説明したが、通常は、ステップSP31に続いて、ステップSP32の処理が実行され、演出制御CPU63は、所定の音声レジスタSRGに、所定値を書込むことで終了割込み信号IRQ\_SNDを、LレベルからHレベルに復帰させる(SP34)。

**【0252】**

そして、最後に、所定の音声レジスタSRGに所定値を書込むことで、全ての音声レジスタSRGへのREAD / WRITEアクセスを許可する(SP35)。この処理の結果、その後の音声プロセッサ初期化処理(SP26)では、必要な設定処理を実行できることになる。

**【0253】**

以上、ステップSP23の割込み許可設定に対応するMaskable Interruptの一例について説明したが、発振器OSC2の発振停止に基づくマスク不能割込み(Non Maskable Interrupt)は、任意のタイミングで起動可能である。先に説明した通り、内蔵CPU(演出制御CPU63)以外の回路の動作クロックは、発振器OSC2の出力クロックをPLL(Phase Locked Loop)で周波数倍して生成されており、発振器OSC2の発振が停止されれば、その後のVDP回路52の正常動作は不可能である。

**【0254】**

一方、演出制御CPU63の動作クロックは、発振器OSC1の出力クロックをPLLで倍して生成されており、プログラム処理は継続可能である。しかも、割込み処理プログラムは、内蔵RAM59に格納されている。そこで、演出制御CPU63は、異常事態の発生を音声やランプによって異常報知すると共に(SP28)、WDT回路58にクリア信号を出力し続ける(SP29)。異常報知は、例えば「異常事態が発生しました。至急、係員に連絡して下さい」との音声報知となる。なお、WDT回路58にクリア信号を出力し続けるのは、異常リセット動作を回避するためである。すなわち、発振器OSC1が動作を停止する重大な異常時には、仮に、異常リセット処理を繰り返しても、機器の正常復帰が望めないと考えられるからである。

**【0255】**

以上、図14(b)と、図14(c)について説明したので、図14(a)に戻って説明を続ける。ステップSP24では、外付けDRAMのプログラム領域を保護するため、必要領域を書込み禁止に設定する。次に、電源遮断時に電池で駆動されている時計回路38について、電源遮断時の正常動作を確認すると共に、念のためアラーム割込みについて再設定する(SP25)。

**【0256】**

そして、エラーフラグERR=1であることを条件に、音声プロセッサ27の内蔵レジスタ(音声レジスタSRG)に、必要な設定値を書込んで初期化処理を実行する(SP26)。なお、エラーフラグERR=0の場合は、所定時間、エラーフラグERR=1となるまで待機するが、限界時間を超える場合には、WDT回路58を起動させるべく無限ループ処理に移行する。

**【0257】**

次に、VDPレジスタRGijに、必要な設定値を書込むことで、VDP回路52の初期化処理を実行する(SP27)。なお、ステップSP27の処理には、図17のST1～ST3の処理が含まれている。

**【0258】**

以上、音声プロセッサから終了割込み信号IRQ\_SNDを受ける実施例について説明したが、図14(c)の割込み処理を省略するのも好適である。図16は、変形実施例を示しており、終了割込み信号IRQ\_SNDに代えて、マルチファンクションタイマユニットMTUが生成する1msタイマ割込信号を活用している。

**【0259】**

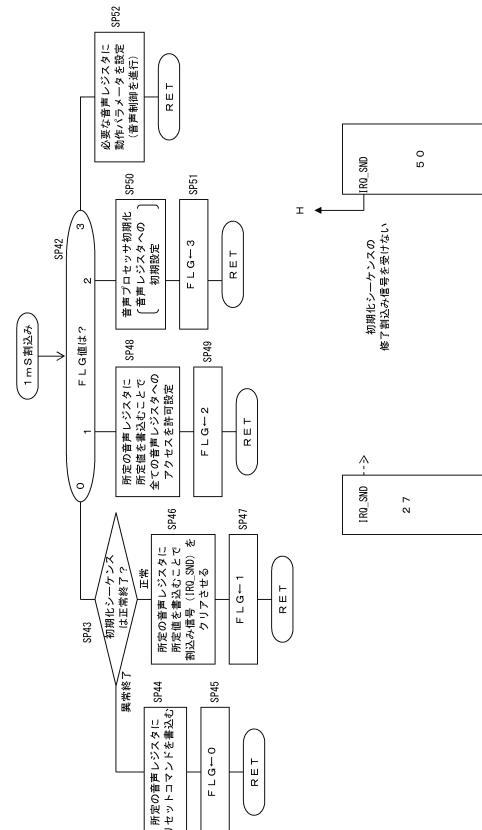

図16は、1msタイマ割込処理の一部を図示したものであり、初期状態がゼロである動作管理フラグFLGの値(0/1/2/3)に基づいて、4段階の動作を実現している。

10

20

30

40

50

なお、音声プロセッサ 27 の IRQ\_SND 出力端子は、開放状態とし、CPU 回路 51 の IRQ\_SND 入力端子は、H レベルに固定されている。

#### 【 0 2 6 0 】

1 ms タイマ割込み処理において、先ず、ステップ SP42 の処理で、動作管理フラグ FLG = 0 と判定される場合には、音声プロセッサ 27 の初期化シーケンスが正常終了していることを確認する (SP43)。そして、正常終了している場合には、所定の音声レジスタ SRG に所定値を書込むことで割込み信号 (IRQ\_SND) をクリアさせ (SP46)、動作管理フラグ FLG を 1 にする (SP47)。なお、ステップ SP43 と SP46 の処理は、図 14 (c) のステップ SP31 と SP34 の処理と同じである。

#### 【 0 2 6 1 】

一方、初期化シーケンスが正常終了していない場合には、所定の音声レジスタ SRG にリセットコマンドを書込むことで、音声プロセッサ 27 に初期化シーケンスを起動させ (SP44)、動作管理フラグ FLG をゼロに戻す (SP45)。なお、ステップ SP44 の処理は、図 14 (c) のステップ SP32 の処理に対応している。

#### 【 0 2 6 2 】

通常は、ステップ SP47 の処理を経て動作管理フラグ FLG = 1 となるので、次の 1 ms タイマ割込みでは、所定の音声レジスタに所定値を書込むことで全ての音声レジスタへのアクセスを許可し (SP48)、動作管理フラグ FLG = 2 に設定する (SP49)。ステップ SP48 の処理は、図 14 (c) のステップ SP35 の処理に対応している。

#### 【 0 2 6 3 】

次に、動作管理フラグ FLG = 2 の 1 ms タイマ割込みでは、図 14 (a) のステップ SP26 の場合と同様に、音声プロセッサ 27 の内蔵レジスタ (音声レジスタ SRG) に、必要な設定値を書込んで初期化処理を実行し (SP50)、動作管理フラグ FLG = 3 に設定する。

#### 【 0 2 6 4 】

動作管理フラグ FLG = 3 は、通常の音声制御状態を意味し、必要な音声レジスタ SRG に、必要な動作パラメータを設定することで、音声制御を進行させる (SP52)。

#### 【 0 2 6 5 】

以上、音声プロセッサ 27 の初期化シーケンスの正常終了を、割込み信号 (IRQ\_SND) に起因する割込み処理で確認する方法 (図 14 (c) の SP31) と、1 ms タイマ割込み処理で確認する方法 (図 16 の SP43) について説明したが、これらの方に、何ら限定されるものではない。例えば、図 14 のステップ SP26 の処理の一部として、音声プロセッサ 27 の初期化シーケンスが正常に終了したか否かを判定するのも好適である。

#### 【 0 2 6 6 】

以上、メイン制御処理の導入部 (図 14 の SP20 ~ SP27) について説明したので、以下、図 17 に基づいて、メイン制御処理の本体部の動作を説明する。図 17 に示す通り、演出制御 CPU63 の動作は、メイン制御処理 (a) と、1 ms 毎に起動するタイマ割込み処理 (b) と、制御コマンド CMD を受けて起動する受信割込み処理 (不図示) と、表示装置 DS1 の V ブランク (垂直帰線期間) の開始タイミングに生じる VBLANK 信号を受けて起動する VBLANK 割込み処理 (c) と、動作フリーズ時や不合理な指示コマンド検出時に生じる描画異常割込み処理 (d) と、を含んで構成されている。なお、20 μs 割込み処理については説明を省略する。

#### 【 0 2 6 7 】

受信割込み処理では、主制御部 21 から受けた制御コマンド CMD を、メイン制御処理 (ST13) において参照できるよう、所定の受信バッファに記憶して処理を終える。また、VBLANK 割込み処理 (図 17 (b)) では、VBLANK 割込み毎に、割込みカウンタ VCNT をインクリメントし (ST15)、メイン制御処理の開始タイミングでは、割込みカウンタ VCNT の値に基づいて、1 / 30 秒の動作開始タイミングを把握した上で、割込みカウンタ VCNT をゼロクリアしている (ST4)。

#### 【 0 2 6 8 】

10

20

30

40

50

一方、タイマ割込み処理には、図17(b)に示す通り、ランプ演出やモータ演出の進行処理(ST18)と、原点センサ信号S N 0 ~ S N n信号や、チャンスボタン信号などを取得するセンサ信号取得処理(ST19)とが含まれている。ランプ演出やモータ演出は、全ての演出動作を一元管理する演出シナリオに基づいて制御されており、演出カウンタE Nが管理する演出開始時に達すれば、演出シナリオ更新処理(ST11)において、モータ駆動テーブルやランプ駆動テーブルが特定されるようになっている。

#### 【0269】

そして、その後は、特定されたモータ駆動テーブルに基づいてモータ演出が進行し、特定されたモータ駆動テーブルに基づいてランプ演出が進行することになる。先に説明した通り、ステップST18の動作時に、DMA C回路(第1と第2のDMAチャンネル)60が機能する実施例もある。なお、モータ演出は、1mS毎に進行するが、ランプ演出は、1mSより長い適宜なタイミングで進行する。

10

#### 【0270】

一方、図17(d)に示す通り、描画異常割込み処理では、描画回路76の動作状態を示すステイタスレジスタRGijをREADアクセスして、割込み原因を特定する。具体的には、(1)異常な指示コマンドの検出(ビット化け)による描画異常割込みか、(2)描画回路76の動作異常(フリーズ)による描画異常割込みかを特定する(ST16a)。そして、異常な指示コマンドの検出に基づく描画異常割込みである場合には、所定のシステム制御レジスタRGijに、所定値を書き込むことで、描画回路76を初期化する(ST16b)。この動作は、図4(b)に示すリセット経路4Bの個別リセット動作に他ならない。

20

#### 【0271】

次に、個別リセット動作の正常終了を、所定のステイタスレジスタRGijで確認した後、描画回路76の動作を規定する一群の動作パラメータを所定の描画レジスタRGijに再設定して処理を終える(ST16c)。そして、戻り先アドレスを記憶するスタック領域を調整した後(割込み処理後の戻り先アドレスを消去する開放処理)、ステップST13の処理に移行させる(ST16c)。

#### 【0272】

一方、描画回路76の動作異常に基づく描画異常割込みの場合には、無限ループ処理に移行させることで(ST16d)、WDT回路58を起動させ、複合チップ50全体をリセットする。なお、CPU回路51をリセットしたくない場合には、所定のキーワード列をパターンチェック回路CHKに出力して、リセット信号\_RSTによってVDP回路52だけをリセットしても良い(図4(b)参照)。この場合には、VDP回路52のリセット動作の正常終了を確認した後、ステップST4やST13の処理に移行させる。なお、可能な限り制御コマンドCMDの読み落しを回避するためには、他の場合も含め、ステップST4より、ステップST13に移行される方が良い。

30

#### 【0273】

複合チップ50全体をリセットすると、それまでの演出が消滅して、演出制御が完全に初期状態(電源投入状態)に戻るが、VDP回路52だけをリセットする場合には、VDP回路52のリセット動作が完了するまで、所定の待機時間は生じるもの、一連の演出制御を継続させることができる。なお、演出制御CPU63は、画像演出、ランプ演出、及び、音声演出を統一的に制御しているので、各演出に不自然なズレが生じることもない。

40

#### 【0274】

続いて、プリローダを機能しない実施例について、メイン制御処理(a)について説明する。図17(a)に示す通り、メイン制御処理は、CPUリセット後に実行される導入初期処理(ST1~ST3)と、その後、1/30秒毎に繰り返し実行される定常処理(ST4~ST14)とに区分される。なお、初期処理(ST1~ST3)は、メイン制御処理の導入部の一部であり、定常処理がメイン制御処理の本体部を意味する。

#### 【0275】

そして、定常処理は、割込みカウンタVCNTが、VCNT 2となったタイミングで開

50

始されるので( S T 4 )、定常処理の動作周期 は、1 / 3 0 秒となる。この動作周期 は、演出制御 C P U 6 3 の制御に基づいて間欠動作する V D P 回路 5 2 について、その実質的な動作周期 に他ならない。なお、判定条件を、 V C N T = 2 とするのは、定常処理( S T 4 ~ S T 1 4 )が異常に長引いて、 V C N T = 2 のタイミングを見逃す可能性を考慮したものであるが、 V C N T = 3 となる事態が発生しないよう設計されている。

#### 【 0 2 7 6 】

以上を踏まえてメイン制御処理( 図 1 7 ( a ) )の説明を続けると、本実施例では、初期処理において、記憶容量 4 8 M バイトの内蔵 V R A M 7 1 を、適切な記憶容量を有する A C C 領域(a) と、ページ領域(b) と、任意領域(c) と、に適宜に切り分ける( S T 1 )。具体的には、 A C C 領域(a1,a2) と、ページ領域(b) について、各々の領域先頭アドレスと必要な総データサイズを、所定のインデックステーブルレジスタ R G i j に設定する( S T 1 )。すると、確保された A C C 領域(a1,a2) と、ページ領域(b) には含まれない残余領域が任意領域(c) となる。

10

#### 【 0 2 7 7 】

ここで、第一と第二の A C C 領域(a1,a2) と、ページ領域(b) の領域先頭アドレスは、各々の下位 1 1 b i t が 0 でなくてはならないが、2 0 4 8 b i t 単位で任意に選択可能である( 1 番地 = 1 バイトとして、2 5 6 番地ごとの選択 )。また、総データサイズも、単位サイズの整数倍の範囲で任意に選択される。特に限定されないが、 A C C 領域(a) の単位サイズは、2 0 4 8 b i t 、ページ領域(b) の単位サイズは、5 1 2 k b i t である。

20

#### 【 0 2 7 8 】

このように本実施例では、 A C C 領域(a1,a2) と、ページ領域(b) の領域設定に一定の条件を設けるが、それは、メモリ容量が限られている内蔵 V R A M 7 1 について、可能な限り無駄領域を排除する一方で、 V D P 回路 5 2 の内部動作の円滑化を図るためである。すなわち、内蔵 V R A M 7 1 の記憶容量を無闇に増加させると、製造コストの高騰やチップ面積の大型化が懸念される一方、無駄領域を完全に排除するような自由な領域設定を認めると、内部処理が煩雑化して、 V R A M アクセスの処理時間を短縮化できないためである。なお、以下に説明するインデックス空間の確保に、一定の制約を設けるのも同じ理由による。

#### 【 0 2 7 9 】

以上を踏まえて説明を続けると、ステップ S T 1 の処理に続いて、ページ領域(b) と、任意領域(c) について、必要なインデックス空間 I D X i を確保する( S T 2 )。具体的には、所定のインデックステーブルレジスタ R G i j に、必要な情報を設定することで、各領域(b)(c) のインデックス空間 I D X i を確保する。

30

#### 【 0 2 8 0 】

例えば、ページ領域(b) にインデックス空間 I D X i を設ける場合には、任意のインデックス番号 i に対応して、任意の水平サイズ H x と、任意の垂直サイズ W x の倍数情報( 単位空間に対する縦横の倍数情報 )が、所定のインデックステーブルレジスタ R G i j に設定される( S T 2 )。

#### 【 0 2 8 1 】

先に説明した通り、ページ領域(b) のインデックス空間 I D X i は、水平サイズ 1 2 8 × 垂直サイズ 1 2 8 ラインを単位空間としており、また、1 ピクセルは 3 2 b i t の情報で特定されるので、水平サイズ H x と垂直サイズ W x の設定に基づいて、データサイズ( b i t 長 ) = 3 2 × 1 2 8 × H x × 1 2 8 × W x のインデックス空間 I D X i が確保されることになる。なお、ページ領域(b) のインデックス空間 I D X i の先頭アドレス( 空間先頭アドレス )は、内部的に自動付与される。

40

#### 【 0 2 8 2 】

また、任意領域(c) にインデックス空間 I D X i を設ける場合には、任意のインデックス番号 i に対応して、任意の先頭アドレス( 空間先頭アドレス ) S T x と、任意の水平サイズ H x の倍数情報が、所定のインデックステーブルレジスタ R G i j に設定される( S T 2 )。ここで、任意とは、所定条件を前提とするもので、水平サイズ H x は 2 5 6 b i t

50