(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4104342号

(P4104342)

(45) 発行日 平成20年6月18日(2008.6.18)

(24) 登録日 平成20年4月4日(2008.4.4)

(51) Int.Cl.

H01L 21/8246 (2006.01)

H01L 27/105 (2006.01)

F 1

H01L 27/10 444B

請求項の数 4 (全 14 頁)

(21) 出願番号 特願2002-42139 (P2002-42139)

(22) 出願日 平成14年2月19日 (2002.2.19)

(65) 公開番号 特開2002-314044 (P2002-314044A)

(43) 公開日 平成14年10月25日 (2002.10.25)

審査請求日 平成16年9月15日 (2004.9.15)

(31) 優先権主張番号 09/797005

(32) 優先日 平成13年2月28日 (2001.2.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 シャン サン

アメリカ合衆国、コロラド州 80919

, コロラド・スプリングス、バックアイ・

ドライブ 505番

(72) 発明者 ジョージ ヒッカート

アメリカ合衆国、コロラド州 80922

, コロラド・スプリングス、ウィーヴァー

・ドライブ 5239番

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

上部電極層、下部電極層、及び、該上部電極層と該下部電極層に挟まれた強誘電体層を含む強誘電体キャバシタにキャップ層を形成する半導体装置の製造方法であって、

上部電極層上に導電性金属酸化物材料を含むアモルファス層を形成する工程と、

アモルファス層を結晶化したペロブスカイト構造又は層状ペロブスカイト構造の材料層に転化させるため非酸化性雰囲気でアモルファス層を加熱する第1のアニール処理工程と、

結晶化した材料層をキャップ層へ転化させるため、非還元性雰囲気中で結晶化した材料層を300乃至500で加熱する第2のアニール処理工程と、

を有する製造方法。

## 【請求項 2】

結晶化した層及び上部電極層をエッティングすることにより上部電極層をパターニングする工程を更に有する請求項1記載の製造方法。

## 【請求項 3】

第1のアニール処理工程は、アモルファス層を500乃至700で加熱する、請求項1又は2記載の製造方法。

## 【請求項 4】

上部電極層、下部電極層、及び、該上部電極層と該下部電極層に挟まれた強誘電体層を含む強誘電体キャバシタにキャップ層を形成する半導体装置の製造方法であって、

10

20

ストロンチウム、ルテニウム及び酸素を含むアモルファス層を上部電極層の上に形成する工程と、

アモルファス層を結晶化した層に転化させるため、窒素を含む非酸化性雰囲気でアモルファス層を加熱する第1のアニール処理工程と、

結晶化した層及び上部電極層をエッティングすることにより上部電極層をパターニングする工程と、

結晶化した材料層をキャップ層へ転化させるため、酸素を含む酸化性雰囲気中で結晶化した材料層を300乃至500で加熱する第2のアニール処理工程とを有し、

上部電極層は酸化イリジウムを含み、

強誘電体層はPZTを含み、

下部電極層は白金を含む、製造方法。

10

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、強誘電体メモリ集積回路の処理に係り、特に、強誘電体メモリ集積回路中の強誘電体キャパシタの上部電極の上に保護層を形成する処理に関する。

##### 【0002】

##### 【従来の技術】

強誘電体ランダムアクセスメモリ(FRAM)は、電源が切斷されてもデータが消えない不揮発性メモリ技術であるため、携帯電話機、携帯情報端末(PDA)、及び、デジタルカメラのようなハンドヘルド型電子装置用の好適なメモリ技術としての潜在的な能力を備えていることが従来から認識されている。これに対し、殆どのデスクトップ型コンピュータ及びノートブック型コンピュータで使用されるDRAMメモリに保持されたデータは、コンピュータの電源が切斷されると消える。これらのコンピュータは、電源が切斷されている期間にデータを保持するため、扱いにくく壊れ易いハードディスク装置のような付加的なコンポーネントを必要とする。このため、FRAMは、付加的な不揮発性データ記憶コンポーネントを不要にさせることによって、ハンドヘルド型装置の小型化と耐久性に寄与する。

20

##### 【0003】

FRAMは、電気的消去可能プログラマブル読み出し専用メモリ(EEPROM)及びフラッシュEEPROMのような他の不揮発性メモリ技術よりも優れている点がある。EEPROM及びフラッシュEEPROMの場合、読み出し時間はナノ秒からマイクロ秒の短い時間であるが、書き込み時間はミリ秒のオーダーに達する。読み出し時間と書き込み時間が数桁のオーダーで異なることは、フラッシュEEPROMのブロック消去特性と組み合わされ、EEPROM装置及びフラッシュEEPROM装置の設計及び使用法を複雑にする。一方、FRAMは、読み出し及び書き込みの両方の動作を1マイクロ秒以下の時間で行うことができる。

30

##### 【0004】

FRAMには卓越した耐久特性がある。FRAMメモリセルの耐用寿命は、1兆(10<sup>12</sup>)回以上の読み出し/書き込みサイクル数に達する。このように、読み出し/書き込みサイクル疲労に対して強い耐性があるので、FRAMは、毎秒1億乃至10億回の演算を実行する携帯型コンピュータのような装置に好適である。

40

##### 【0005】

FRAMメモリセルはキャパシタにより形成され、キャパシタの電極に印加される電圧及び/又は電流を操作することによりデータがアクセスされる。FRAMメモリセル中のキャパシタは、電極を隔離するため強誘電体化合物を使用する。一般的にFRAMで使用される強誘電体化合物は、一般的にPZTと称されるチタン酸ジルコン酸鉛Pb(Zr<sub>x</sub>Ti<sub>1-x</sub>)O<sub>3</sub>、及び、一般的にSBTと称されるタンタル酸ストロンチウムビスマスSrBiTiOのようなペロブスカイト構造を有する酸化物を含む。これらの強誘電体材料は、他の半導体装置と集積化されて、アドレッシング、選択及び制御論理用の回路を形成

50

する。残念ながら、多数の強誘電体材料のデータ保持力及び疲労耐性のような所望の電気特性は、典型的な半導体プロセス条件下で劣化する。したがって、半導体装置の製造者は、F R A M メモリセルを標準的な半導体製品と一体化する集積化プロセス及びパッケージングプロセスにおいて、強誘電体材料の高品質電気特性を維持する点で頻繁に困難に直面する。

#### 【 0 0 0 6 】

##### 【発明が解決しようとする課題】

プロセス中にF R A M が劣化する主要な理由の一つは、強誘電体材料内の酸素原子が水素のようなガスと反応することであると考えられる。水素の曝露は、フォトレジストを取り去るためのプラズマアッティングのようなクリーニング操作中に生じる。また、金属成膜プロセスは、屢々、形成された金属構造体を処理するため有機金属化合物、及び／又は、水素を使用することによって、水素を取り込む。さらに、半導体製造プロセスにおいて、化学的機械研磨（C M P）を用いて余分な材料を取り除くことは、一般的に行われている。C M Pは、タンゲステンのような余分な材料を効率的に取り除くことができるが、化学反応及び機械的振動は、水素を強誘電体層へ運び、P Z Tに損傷を加えると考えられる。したがって、最終的に形成されたF R A M の品質は、望ましい品質よりも著しく低く、かつ、ばらつきがある。

#### 【 0 0 0 7 】

本発明は、性能が改良され、プロセスの許容範囲が拡大されるように強誘電体コンポーネントが他の半導体装置と集積化された集積回路、及び、その集積回路の製造方法の提供を目的とする。

#### 【 0 0 0 8 】

さらに、本発明は、強誘電体キャパシタの上部電極にストロンチウム酸化ルテニウム（S R O）キャップ層を形成する方法の提供を目的とする。

#### 【 0 0 0 9 】

##### 【課題を解決するための手段】

本発明は、強誘電体材料の下側層を水素及びその他の還元ガスから保護するため、強誘電体キャパシタの上部電極に導電性ペロブスカイト構造又は層状ペロブスカイト構造材料からなる保護キャップを形成する。

#### 【 0 0 1 0 】

本発明は、導電性のペロブスカイト又は層状ペロブスカイト構造よりなる物質でできた保護キャップ層を強誘電体キャパシタの上部電極上に形成し、H<sub>2</sub>や他の還元性ガスによる劣化からキャップ層の下の強誘電体層を保護する方法を提供する。

#### 【 0 0 1 1 】

本発明によれば、ストロンチウム酸化ルテニウム（S R O）を含む保護キャップ層がキャパシタの上部電極上に成膜された強誘電体キャパシタを有する集積半導体装置が得られる。S R O キャップ層は、半導体製造プロセス中にキャパシタの強誘電体層を化学的機械劣化から保護する。特に、キャップ層は、水素が上部電極を通り、強誘電体層へ移動し、P Z Tのような強誘電体材料を劣化させることを妨げるものと考えられる。

#### 【 0 0 1 2 】

本発明の強誘電体キャパシタの上部電極にS R O キャップ層を形成する方法によれば、S R O キャップ層は、上部電極に成膜され後、2回のアニール処理が施される。第一に、最初にアモルファス相で堆積したキャップ層は、S R O を結晶化するため、非酸化性雰囲気中、500乃至700の温度でアニール処理される。第二に、結晶化したS R O キャップ層が、酸化性雰囲気中、300乃至500の温度で再度アニール処理される。堆積され結晶化され、酸素アニール処理されたS R O キャップ層は、後続の装置製造工程において、下側の強誘電体層に優れた水素劣化耐性を付与する。

#### 【 0 0 1 3 】

本発明によって得られる強誘電体キャパシタ構造体は、その後、アニーリング、クリーニング、多層メタル処理、配線形成、及び、組立の間に高温及び化学薬品に晒されるにもか

10

20

30

40

50

かわらず、劣化が抑制される。さらに、キャパシタ構造体の形成後に続くプロセスの悪影響が低減され、多種多様なプロセスをキャパシタ構造体の形成後に実行することが可能であり、これにより、強誘電体装置の性能を低下させることなく、集積化のレベルが非常に高い新しい装置を実現することができるようになる。

#### 【0014】

##### 【発明の実施の形態】

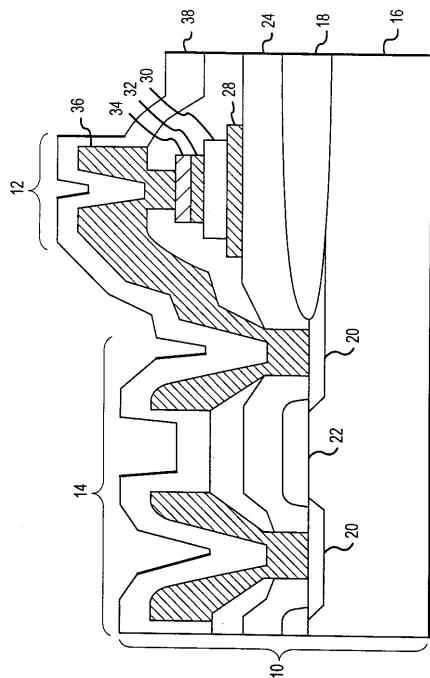

図1には、本発明の集積半導体装置に組み込まれた集積強誘電体メモリセル10が示されている。集積強誘電体メモリセル10は、強誘電体キャパシタ12と、電界効果トランジスタ(FET)14とを含む。この特定の実施例の場合に、強誘電体メモリセル10は、1個のトランジスタと1個のキャパシタとからなる1T-1Cメモリセルとして構成されている。メモリセル10は、シリコンエピタキシャル層16からなる単結晶シリコン基板のような基板を含む。厚い電界酸化物層18は、アクティブ領域を画成、隔離する。拡散領域20は、トランジスタ14のドレイン領域及びソース領域のようなアクティブ装置コンポーネントを形成する。ゲート電極22は、(図1の紙面に直交する方向へ延びるため図示されない)ワード線に接続されるか、若しくは、ワード線の一部を形成する。平坦化層24は、厚い層の上に塗布された酸化物のような絶縁材料により構成され、絶縁材料は、装置構造体の上に重なる平坦なワーキング表面を得るために、化学的研磨、機械研磨、化学的機械研磨などを用いて平坦化される。

#### 【0015】

好ましい一実施例において、密着層(図示せず)は、強誘電体キャパシタ12の集積半導体装置の台への密着を強化するため、強誘電体キャパシタ12と平坦化層24の間に設けられる。密着層は、(非常に薄いため図示されないが)好ましくは、50乃至200の厚さの酸化チタンによって形成されるが、密着性を示すものであれば、より厚い層でも薄い層でも構わない。

#### 【0016】

キャパシタ12は、下部電極層28と、強誘電体層30と、上部電極層32と、上部電極層32の上にあるSROキャップ層34により構成される。下部電極層28は、好ましくは、白金から形成され、500乃至2000の厚さを有し、より好ましくは、1000の厚さを有するが、集積半導体装置内で良好な電極特性を示すものであれば、厚さはより厚くても薄くても構わない。下部電極層28はプレート線に接続され、このプレート線は複数のメモリセルへ接続される。プレート線も図1の紙面に対し直交するので図示されない。

#### 【0017】

強誘電体層30は、好ましくは、チタン酸ジルコン酸鉛Pb(Zr<sub>x</sub>Ti<sub>1-x</sub>)O<sub>3</sub>、すなわち、PZT、或いは、タンタル酸ストロンチウムビスマスSrBiTiO、すなわち、SBTのようなペロブスカイト構造を有する酸化物を含む。強誘電体層30の厚さは、好ましくは、1000乃至2000、より好適には、約1800であるが、集積半導体装置内で優れた強誘電体特性を示すならば、より厚くても薄くても構わない。

#### 【0018】

上部電極層32は、好ましくは、白金のような導電性サブストレートから形成され、より好ましくは、酸化イリジウムから形成される。上部電極層32の厚さは、好ましくは、500乃至2000、より好適には、約1500であるが、集積半導体装置内で優れた電極特性(たとえば、導電性、適当なエレクトロマイグレーション・ストレスマイグレーション耐性、耐熱性、パターン形成可能性)を示すならば、より厚くても薄くても構わない。

#### 【0019】

好ましい一実施例において、SROキャップ層34は、上部電極層32の上に設けられる。SROキャップ層34は、好ましくは、ストロンチウムヒルテニウムの酸化物を含み、より好適には、y=(2-x)であり、かつ、xが0.9乃至1.1の値をとる場合に、Sr<sub>(x)</sub>Ru<sub>(y)</sub>O<sub>3</sub>を含む。SROキャップ層34の厚さは、好ましくは、200

10

20

30

40

50

乃至 1500、より好適には、約 500 であるが、下側の強誘電体層 30 内の強誘電体材料を化学的機械劣化から保護するならば、より厚い層でもより薄い層でも構わない。他の実施例では、キャップ層 34 は、SRO のような導電性ペロブスカイト構造に限定されず、YBaCuO<sub>3</sub> のような導電性層状ペロブスカイト構造材料でも構わない。

#### 【0020】

上部電極層 32 は、メタライゼーション層 36 を介してトランジスタ 14 のソース領域に接続される。メタライゼーション層 36 は、トランジスタ 14 のドレインとも接触し、ビット線コンタクトを形成する。好ましい一実施例では、続いて、パッシベーション層 38 が集積回路の表面全体に設けられる。

#### 【0021】

次に、本発明の製造方法について説明する。本発明の方法は、ストロンチウム及びルテニウムを含むアモルファス酸化物の層を、強誘電体キャパシタの上部電極の上に形成する工程と、アモルファス層を結晶化層へ転化させるため、酸化の生じない雰囲気中、アモルファス層を 500 乃至 700 の温度で加熱する工程と、結晶化層を本発明の SRO キャップ層へ転化させるため、還元の生じない雰囲気中、結晶化層を 300 乃至 500 の温度で加熱する工程と、を有する。

#### 【0022】

本発明の方法の好ましい一実施例によれば、強誘電体キャパシタの上部電極の上に形成されたアモルファス酸化物の層は、Sr<sub>(x)</sub>Ru<sub>(y)</sub>O<sub>3</sub> を含み、y = (2 - x) であり、かつ、x が 0.9 乃至 1.1 の値をとる。SRO 層は、ゾル・ゲル法、スパッタリング法、及び、化学気相成長法 (CVD) のような層状構造集積半導体装置に膜を形成する多数の技術によって形成することができる。アモルファス SRO 層は、SRO 層の結晶化を促進するため、窒素 (N<sub>2</sub>) 雰囲気中、又は、希ガス雰囲気中、約 650 の温度で加熱される。この酸化を生じないアニール処理は、代替的な実施例では、500 乃至 700 の温度範囲で実施される。

#### 【0023】

次に、結晶化した SRO 層は、本発明による酸素アニール処理された SRO キャップ層を形成するため、還元が生じない雰囲気又は酸化が生じる雰囲気中、約 5 時間に亘って約 400 で加熱される。この第 2 の加熱工程で使用される雰囲気は、窒素又は希ガスのような非還元性ガス中であり、より好ましくは、酸素 (O<sub>2</sub>) のような酸化性ガス中である。雰囲気は、非還元性であるため、水素 (H<sub>2</sub>) のような還元性ガスは存在するべきではない。本発明による方法の他の好ましい一局面では、結晶化した SRO 層及び上部電極層は、結晶化した SRO 層を最終的な SRO キャップ層へ転化するため第 2 の加熱工程が実行される前に、強誘電体キャパシタの上側層を形成するためエッティングされる。

#### 【0024】

本発明の SRO キャップ層を形成する方法は、従来の集積回路装置を形成する方法に組み込むことができる。強誘電体キャパシタの下部電極は、集積半導体装置のサブストレート層に形成される。好ましい一実施例において、下部電極は、下側のサブストレート層及び下部電極層と接触する密着層を構成する積層構造体を用いて形成され、密着層の上に設けられる。下側の層は、好ましくは、サブストレート層にチタン (Ti) 金属を成膜させ、酸素雰囲気中において金属層を 300 乃至 700 で加熱することにより形成された酸化チタンより成る。下部電極層は、好ましくは、導電性金属又は金属酸化物より成り、より好ましくは、白金から成る。下部電極層は、DC スパッタリングのような任意の標準的な成膜技術を用いて密着層上に形成してもよい。

#### 【0025】

下部電極層の形成に続いて、強誘電体層が下部電極層の上に形成される。強誘電体層は、好ましくは、チタン酸ジルコニア酸鉛、すなわち、PZT、或いは、タンタル酸ストロンチウムビスマス、すなわち、SBT のようなペロブスカイト結晶構造を有する酸化物より成る。本発明の好ましい一局面において、強誘電体材料は PZT である。PZT は、好ましくは、ランタンとカルシウムとストロンチウムからなる群より選択された金属がドープさ

10

20

30

40

50

れる。好ましくは、R F スパッタリング法、又は、ゾル・ゲル法が、強誘電体材料を下部電極に成膜させるため使用される。強誘電体層が形成された後、強誘電体材料を結晶化させるため、非還元性雰囲気中で、強誘電体層は加熱される。たとえば、強誘電体材料は、瞬間熱アニール（R T A）プロセスによって結晶化させられる。

## 【0026】

次に、上部電極層が強誘電体層の上に形成される。上部電極層は、好ましくは、金属又は導電性酸化物より成り、より好適には、白金酸化物又はイリジウム酸化物より成り、さらに好適には、酸化イリジウムより成る。上部電極は、D C スパッタリング法のような周知の層堆積技術を用いて、強誘電体層上に形成される。

## 【0027】

上部電極が強誘電体層の上に堆積した後、好ましくは、強誘電体層中のP Z Tの粒子成長を完了させるのに十分な間隔と温度とを有するアニーリング工程が行われる。典型的に、このアニール処理は、アルゴン、ネオン、ヘリウム、又は、キセノンのような不活性ガスを含む雰囲気とバランスした、好ましくは、酸素の分圧が1%乃至5%である雰囲気において約650で行われる。

## 【0028】

上部電極層が形成され、アニール処理された後、S R O キャップ層が、図2に示され、また、上述の説明のように上部電極層の上に形成される。

## 【0029】

S R O 層の形成後、多様な集積半導体製造プロセスが本発明の集積半導体装置を製造するため利用される。これらのプロセスには、化学的エッティング及びクリーニング、層間絶縁膜形成法（I L D）、C M P、並びに、アニール処理（rejuvenating anneal）が含まれる。

## 【0030】

本発明の方法及び構造体の具体的な利点は、プロセス設計者及び装置設計者に、プロセスの多様性及び制御にこれまで不可能であった広い許容範囲を与えることである。従来、強誘電体の成膜後の処理は、強誘電体材料を劣化させないようなプロセスに限定されていた。しかし、本発明によれば、水素照射を含む新しいプロセスを使用することが可能になり、プロセスの許容範囲が拡大し、プロセスをより簡単に制御することができる。

## 【0031】

キャパシタスタッフの強誘電体層を機械的及び化学的劣化から保護する上述のキャップ層の製造方法は、好ましくは、白金を含む下部電極と、好ましくは、酸化イリジウムを含む上部電極とを使用する。少なくとも一部の他の金属、他の金属酸化物、或いは、非金属性導電性物質は、強誘電体キャパシタスタッフの動作可能な下部電極及び上部電極を生成し得るものと期待される。

## 【0032】

ここで説明したプロセスは、好ましくは、キャパシタの積層を構成する種々の材料の層を成膜するためスパッタ成膜法を使用する。このプロセスは、化学気相成長（C V D）、スピノン技術と称される溶液化学的堆積などの、種々の層に適した公知の他の堆積法と組み合わせてもよい。

## 【0033】

## [例1]

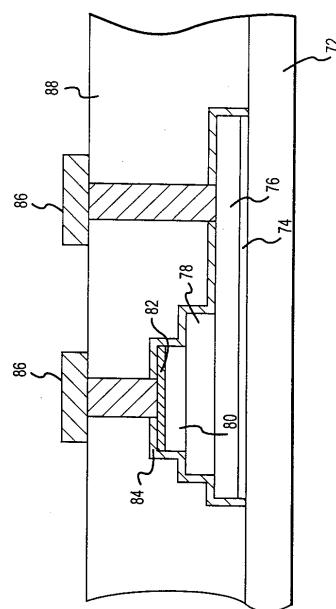

図2には、本例で使用される強誘電体キャパシタの概略が示されている。強誘電体キャパシタ70は、二酸化珪素（SiO<sub>2</sub>）サブストレート層72と、酸化チタン密着層74と、白金下部電極76と、P Z T 強誘電体層78と、酸化イリジウム上部電極80と、S R O キャップ層82と、アルミナ層84と、アルミナ金属配線用コンタクト86と、を含む。

## 【0034】

本例の場合に、酸化チタン密着層74の厚さは200であり、下部電極76の厚さは1500であり、P Z T 強誘電体層78の厚さは1800であり、酸化イリジウム上部

10

20

30

40

50

電極 8 0 の厚さは 1 5 0 0 であり、 S R O キャップ層 8 2 の厚さは 5 0 0 である。強誘電体キャパシタのエッティング後、アルミナ層 8 4 は、 S R O キャップ層の上方及びキャパシタスタックの側方に形成される。次に、二酸化珪素の中間層 8 8 がアルミナ層 8 4 の上に形成され、アルミナ層 8 4 とアルミニウム合金配線用コンタクト 8 6 が定位置にエッティングされる。

【 0 0 3 5 】

S R O キャップ層 8 2 を窒素雰囲気中、又は、酸素雰囲気中でアニール処理した後、 S R O キャップ層 8 2 の構造を X 線回折 ( X R D ) 測定した。 S R O キャップ層 8 2 の結晶構造を、アニール温度の関数として比較した結果を以下の表 1 に掲載する。

【 0 0 3 6 】

【表 1】

| アニール条件                                |   | S r R u O <sub>3</sub><br>(1 2 1) 構造 | S r R u O <sub>3</sub><br>(0 4 0) 構造 |

|---------------------------------------|---|--------------------------------------|--------------------------------------|

| アニール無し                                | C | 無                                    | 無                                    |

|                                       | B | 無                                    | 無                                    |

| N <sub>2</sub> 雰囲気中、1時間、500℃<br>のアニール | C | 無                                    | 無                                    |

|                                       | B | 無                                    | 無                                    |

| N <sub>2</sub> 雰囲気中、1時間、650℃<br>のアニール | C | 4 5 0                                | 無                                    |

|                                       | B | 4 6 0                                | 無                                    |

| O <sub>2</sub> 雰囲気中、1時間、650℃<br>のアニール | C | 6 2 0                                | 2 4 0                                |

|                                       | B | 6 0 0                                | 2 1 3                                |

表 1 に示された結果は、 S R O キャップ層の結晶化が、非還元性雰囲気中、 5 0 0 以下のアニール温度では生じないことを示す。これに対し、 6 5 0 のアニール温度で、アモルファス S R O を結晶化したペロブスカイト構造に転化するため、 ( 1 2 1 ) S r R u O<sub>3</sub> 及び / 又は ( 0 4 0 ) S r R u O<sub>3</sub> 結晶相が S R O キャップ層 8 2 に存在する。

【 0 0 3 7 】

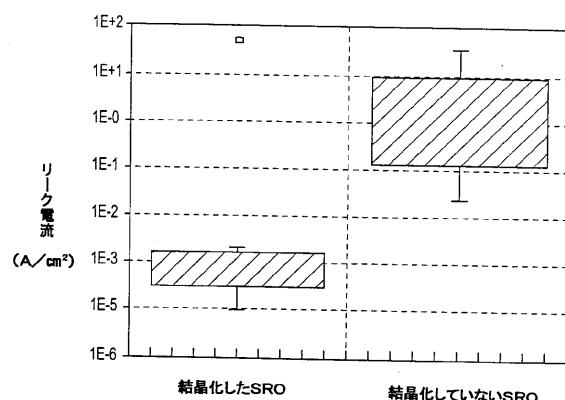

図 3 には、結晶 S R O キャップ層と非結晶 S R O キャップ層に対するリーク電流の比較が示されている。図 3 から、リーク電流は、 S R O キャップ層 8 2 中の S r R u O<sub>3</sub> が結晶化していないとき、 S R O キャップ層 8 2 が結晶化しているときよりも非常に大きくなることがわかる。リーク電流が大きくなると、強誘電体キャパシタの性能が劣化する。

【 0 0 3 8 】

[ 例 2 ]

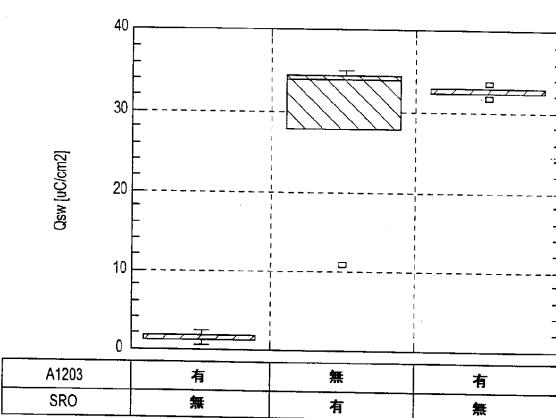

本例では、極性スイッチング電荷 ( Q<sub>s w</sub> ) が、 S R O キャップ層 8 2 及びアルミナ層 8 4 を含む強誘電体キャパシタと、 S R O キャップ層 8 2 及びアルミナ層 8 4 を含まない強誘電体キャパシタとに関して比較される。キャパシタは、図 2 に示されるように本質的に同じ構造を有するが、 S R O キャップ層 9 2 及びアルミナ層 8 4 が存在しないものが特に示されている。

【 0 0 3 9 】

図 4 では、エッティングと、アルミニウム合金配線用コンタクト 8 6 の形成後に、 3 種類の強誘電体キャパシタの Q<sub>s w</sub> を測定した。アルミニウム合金コンタクト 8 6 を処理する前の 3 種類のキャパシタの極性スイッチング電荷 Q<sub>s w</sub> の測定値は、全て約 3 3 μ C / cm<sup>2</sup> であった。第 1 のキャパシタは、図 2 に示されたような構造を有するが、 S R O キャップ層 8 2 を含まないキャパシタである。第 2 のキャパシタは、 S R O キャップ層 8 2 を含み、アルミナ層 8 4 を含まないキャパシタである。第 3 のキャパシタは、 S R O キャップ層 8 2 とアルミナ層 8 4 の両方が存在するキャパシタである。図 4 に示されるように、強誘電体層 7 8 内の P Z T は、アルミニウム合金コンタクト 8 6 の処理中に著しく劣化し、得られた Q<sub>s w</sub> は 0 μ C / cm<sup>2</sup> 付近であった。これに対し、 S R O キャップ層 8 2 を含む第 2 及び第 3 のキャパシタの場合、強誘電体層 7 8 内の P Z T の劣化は非常に少なかった

10

20

30

40

50

。

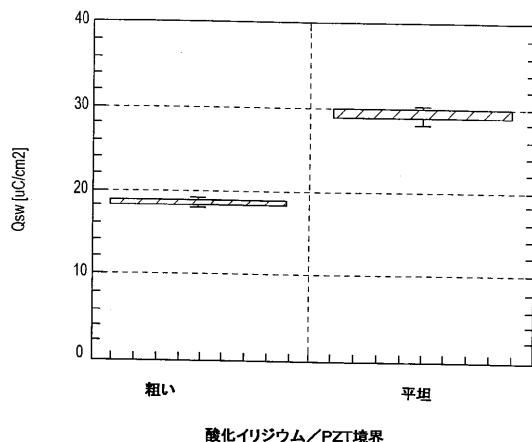

#### 【0040】

図5には、酸化イリジウム上部電極80とPZT強誘電体層78の境界で界面粗さが異なる図2に示されるような2種類の強誘電体キャパシタに関する $Q_{sw}$ が示されている。図5からわかるように、酸化イリジウム上部電極80とPZT強誘電体層78の間の境界が粗くなるにつれて、キャパシタの $Q_{sw}$ 値が低下する。本発明は、アルミナ層84の代わりにPZT層に使用してもよい。

#### 【0041】

##### [例3]

本例では、強誘電体キャパシタ中の強誘電体層におけるPZTの水素劣化を抑制するSROキャップ層の能力が実証される。実験は、SROキャップ層を含む強誘電体キャパシタを温度上昇中の水素雰囲気に放置することから開始した。PZTの水素劣化は、キャパシタの極性スイッチング電荷( $Q_{sw}$ )の減少を測定することによって測定した。種々のプロセス条件下で形成したSROキャップ層を比較することによって、非還元性雰囲気中、300乃至500で加熱したとき、SROキャップ層が水素に対する最強のバリアを形成することがわかった。

#### 【0042】

本例で使用された強誘電体キャパシタは、下層から上層へ順番に、サブストレート層と、密着層と、下部電極と、強誘電体層と、上部電極層と、SROキャップ層とを含む。密着層は、厚さが500の酸化チタン( $TiO_x$ )の層であり、下部電極は、厚さが1500の白金の層であり、強誘電体層は、厚さが1800のPZTの層であり、上部電極は、厚さが1500の酸化イリジウム( $IrO_x$ )の層であり、SROキャップ層の厚さは500である。

#### 【0043】

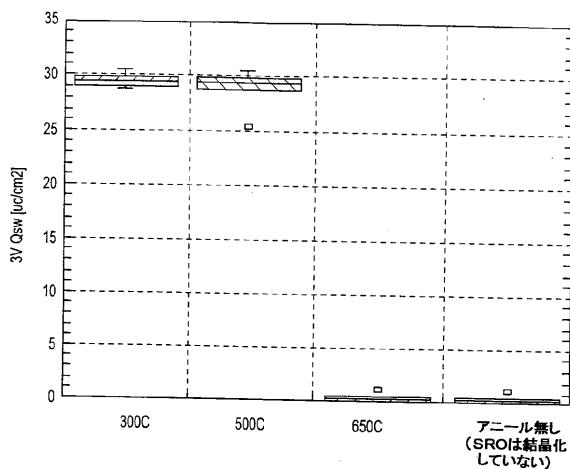

図6には、強誘電体キャパシタのサンプルを3%水素ガス( $H_2$ )を含有する雰囲気中、150で加熱した後の極性スイッチング電荷( $Q_{sw}$ )が示されている。この水素環境下に15分間置いた後、300乃至500の酸素中で加熱したSROキャップ層を有する強誘電体キャパシタは、 $30\mu C/cm^2$ の大きさの $Q_{sw}$ 値を維持した。これに対し、SROキャップ層が300乃至500の範囲ではなく、650で加熱された強誘電体キャパシタは、同じ水素環境下に置いた場合に、 $Q_{sw}$ 値は略0に達した。さらに、アニール処理していないSROキャップ層を有する強誘電体キャパシタ、すなわち、SROキャップ層が結晶化されず、アモルファスである強誘電体キャパシタは、同じ水素環境下に置いた場合に、略0の $Q_{sw}$ 値を示した。

#### 【0044】

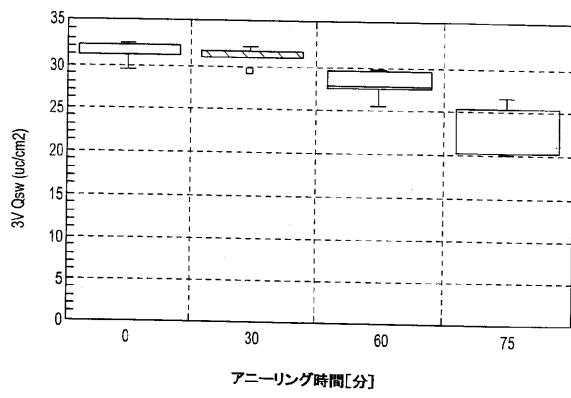

図7には、結晶化したSROを非還元性雰囲気中、300乃至500の温度で加熱して形成したSROキャップ層は、水素バリアとしての有効性が向上することが示されている。図7から、酸素中、300乃至500に加熱されたSROキャップ層を有する強誘電体キャパシタは、水素環境下に75分間置かれた場合でも、 $Q_{sw}$ 値を $20\mu C/cm^2$ の大きさに維持することがわかる。これに対し、SROキャップ層を650度で加熱した強誘電体キャパシタ、又は、SROキャップ層を全く加熱しなかった強誘電体キャパシタは、同じ水素環境下に15分間置いただけで、 $Q_{sw}$ 値が0になることがわかった。

#### 【0045】

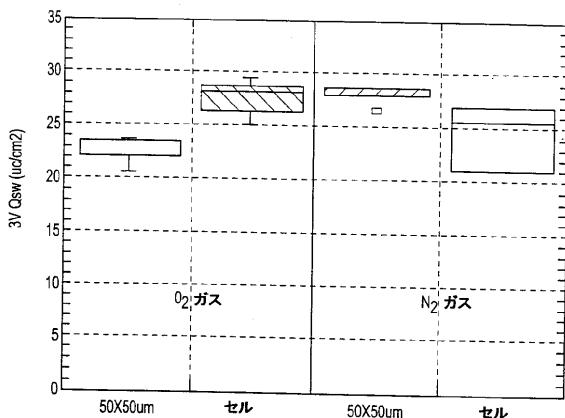

図8には、400で10時間に亘りアニール処理することによって形成したSROキャップ層を有する強誘電体キャパシタに対して測定した極性スイッチング電荷( $Q_{sw}$ )が示されている。この実験では、酸素( $O_2$ )雰囲気でアニール処理されたSROキャップ層と、水素( $N_2$ )雰囲気でアニール処理されたSROキャップ層との比較、並びに、 $50 \times 50\mu m$ の構造を有する強誘電体キャパシタと、セルキャパシタ構造を有する強誘電体キャパシタとの比較が行われた。SROキャップ層を400でアニール処理した後、強誘電体キャパシタにアルミニウム層1配線プロセスを施し、次に、配線プロセスによって生じたPZTの劣化を評価するため $Q_{sw}$ を測定した。

10

20

30

40

50

## 【0046】

$Q_{SW}$  の測定データから、400 でアニール処理した全ての SRO キャップ層は、下側にある強誘電体層内の PZT を、アルミニウム層 1 配線プロセス中に劣化から保護することがわかった。この結果は、SRO キャップ層が、酸素雰囲気中、又は、窒素雰囲気中の何れの雰囲気中でアニール処理された場合でも、下側の PZT を保護することを示している。したがって、本発明の SRO キャップ層形成方法における 300 乃至 500 のアニーリング工程は、酸素のような酸化性雰囲気、並びに、窒素や希ガス（たとえば、ヘリウム、アルゴン、クリプトン、及び、キセノン）のような不活性ガス雰囲気の両方の雰囲気を含む非還元性雰囲気において実行される。

## 【0047】

10

以上の通り、本発明は、特に、好ましい一実施例に関して例示的に説明されているが、本発明の精神並びに範囲を逸脱することなく、実施態様及び細部に関して種々の変更をなしえることが当業者によって認められるべきである。

## 【0048】

以上の説明に関して更に以下のような態様が考えられる。

## 【0049】

（付記 1） 上部電極層、下部電極層、及び、該上部電極層と該下部電極層に挟まれた強誘電体層を含む強誘電体キャパシタにキャップ層を形成する半導体装置の製造方法であつて、

上部電極層に導電性金属酸化物材料を含むアモルファス層を形成する工程と、

20

アモルファス層を結晶化したペロブスカイト構造又は層状ペロブスカイト構造の材料層に転化させるため非酸化性雰囲気でアモルファス層を加熱する、アモルファス層への第 1 のアニール処理工程と、

結晶化した材料層をキャップ層へ転化させるため、非還元性雰囲気中で結晶化した材料層を加熱する、結晶化した層への第 2 のアニール処理工程と、

を有する、製造方法。・・・（1）。

## 【0050】

（付記 2） 結晶化した層及び上部電極層をエッティングすることにより上部電極層をバターニングする工程を更に有する付記 1 記載の製造方法。・・・（2）。

## 【0051】

30

（付記 3） 上部電極層は酸化イリジウムを含む、付記 1 又は 2 記載の製造方法。

## 【0052】

（付記 4） アモルファス層は、ストロンチウム、ルテニウム及び酸素を含む、付記 1 乃至 3 のうちいずれか一項記載の製造方法。

## 【0053】

（付記 5） 第 1 のアニール処理工程は、アモルファス層を 500 乃至 700 で加熱する、付記 1 乃至 4 のうちいずれか一項記載の製造方法。・・・（3）。

## 【0054】

（付記 6） 第 2 のアニール処理工程は、結晶化した層を 300 乃至 500 で加熱する、付記 1 乃至 5 のうちいずれか一項記載の製造方法。・・・（4）。

40

## 【0055】

（付記 7） 第 2 のアニール処理工程における非還元性雰囲気は酸素を含む、付記 1 乃至 6 のうちいずれか一項記載の製造方法。

## 【0056】

（付記 8） 強誘電体層は PZT を含む、付記 1 乃至 7 のうちいずれか一項記載の製造方法。

## 【0057】

（付記 9） 上部電極層は、第 1 のアニール処理工程の後、かつ、第 2 のアニール処理工程の前にバターニングされる、付記 2 記載の製造方法。

## 【0058】

50

(付記 10) 上部電極層、下部電極層、及び、該上部電極層と該下部電極層に挟まれた強誘電体層を含む強誘電体キャパシタにキャップ層を形成する半導体装置の製造方法であつて、

ストロンチウム、ルテニウム及び酸素を含むアモルファス層を上部電極層の上に形成する工程と、

アモルファス層を結晶化した層に転化させるため、窒素を含む非酸化性雰囲気でアモルファス層を加熱する、アモルファス層への第1のアニール処理工程と、結晶化した層及び上部電極層をエッティングすることにより上部電極層をパターニングする工程と、

結晶化した材料層をキャップ層へ転化させるため、酸素を含む酸化性雰囲気中で結晶化した材料層を加熱する、結晶化した層への第2のアニール処理工程と、を有し、

上部電極層は酸化イリジウムを含み、

強誘電体層は P Z T を含み、

下部電極層は白金を含む、

製造方法。 . . . (5)。

#### 【0059】

(付記 11) 半導体基板と、

半導体基板に形成された半導体装置と、

強誘電体層及び該強誘電体層の上に形成された上部電極を含み、半導体基板の上に形成された強誘電体キャパシタと、

上部電極の上に形成された導電性ペロブスカイト構造又は層状ペロブスカイト構造材料を含むキャップ層と、

を有し、前記キャップ層は、ストロンチウム、ルテニウム及び酸素を含む集積半導体装置。 . . . (6)

#### 【0060】

(付記 12) 上部電極は、強誘電体層と接触する酸化イリジウム層を更に含む、付記 1 1 記載の集積半導体装置。 . . . (7)。

#### 【0061】

(付記 13) 強誘電体キャパシタの上に形成された絶縁層を更に有し、

絶縁層は、弱導電性の P Z T 及び酸化アルミニウムからなる群より選択された絶縁性金属酸化物を含む、

付記 1 1 又は 1 2 記載の集積半導体装置。 . . . (8)。

#### 【0063】

(付記 15) 強誘電体層は P Z T を含む、付記 1 1 乃至 1 4 のうちいずれか一項記載の集積半導体装置。

#### 【0064】

(付記 16) 下部電極は白金を含む、付記 1 1 乃至 1 5 のうちいずれか一項記載の集積半導体装置。

#### 【0065】

(付記 17) 集積半導体装置の素子を形成する強誘電体キャパシタであつて、

$0.9 \text{ 乃至 } 1.1$  の値をとる  $x$  と、 $y = (2 - x)$  を満たす値をとる  $y$  と、 $S r_{(x)} R u_{(y)} O_3$  とで表わされる金属酸化物を含むキャップ層と、

キャップ層の下側にあり、酸化イリジウムを含む上部電極層と、

白金を含む下部電極層と、

上部電極層と下部電極層の間に挟まれ、P Z T を含む強誘電体層と、

を有する強誘電体キャパシタ。 . . . (10)。

#### 【0066】

##### 【発明の効果】

本発明によれば、下部電極と、P Z T と、上部電極とを有する強誘電体キャパシタにおいて、上部電極を  $I r O_x$  と S R O の積層構造とすることにより、水素劣化耐性の強いキャパシタが得られる。

## 【0067】

また、本発明によれば、酸化物導電性物質を上部電極として有する強誘電体キャパシタにおいて、上部電極形成後に、低温アニールを行うことにより、水素劣化を抑制することができる。

## 【0068】

さらに、本発明によれば、 $SRO / IrO_x$ 構造を用いることによりプロセス劣化を抑制することができ、極性スイッチング電荷を高くし、飽和特性を低くすることができる。また、キャパシタのサイズ依存性も小さくすることが可能である。

## 【図面の簡単な説明】

【図1】本発明に従って製造された半導体回路上の強誘電体キャパシタの断面図である。 10

【図2】本発明の強誘電体キャパシタの断面図である。

【図3】結晶化した $SrRuO_3$ を含むストロンチウム酸化ルテニウム( $SRO$ )キャップ層と結晶化していない $SrRuO_3$ を含む $SRO$ キャップ層のリーク電流を比較するグラフである。

【図4】3種類の強誘電体キャパシタに対する極性スイッチング電荷( $Q_{sw}$ )を比較するグラフである。

【図5】強誘電体キャパシタの上部電極と強誘電体層の境界面の表面粗さに対して極性スイッチング電荷( $Q_{sw}$ )を比較するグラフである。

【図6】 $SRO$ キャップ層のアニール温度の関数として極性スイッチング電荷( $Q_{sw}$ )を比較するグラフである。 20

【図7】強誘電体キャパシタが水素雰囲気中に置かれた時間の関数として極性スイッチング電荷( $Q_{sw}$ )を比較するグラフである。

【図8】多数の $SRO$ キャップ層形成技術に対する極性スイッチング電荷( $Q_{sw}$ )のグラフである。

## 【符号の説明】

|     |                              |    |

|-----|------------------------------|----|

| 1 0 | 集積強誘電体メモリセル                  |    |

| 1 2 | 強誘電体キャパシタ                    |    |

| 1 4 | 電界効果トランジスタ                   |    |

| 1 6 | シリコンエピタキシャル層                 |    |

| 1 8 | 電界酸化物層                       | 30 |

| 2 0 | 拡散領域                         |    |

| 2 2 | ゲート電極                        |    |

| 2 4 | 平坦化層                         |    |

| 2 8 | 下部電極層                        |    |

| 3 0 | 強誘電体層                        |    |

| 3 2 | 上部電極層                        |    |

| 3 4 | ストロンチウム酸化ルテニウム( $SRO$ )キャップ層 |    |

| 3 6 | メタライゼーション層                   |    |

| 3 8 | パッシベーション層                    |    |

| 7 0 | 強誘電体キャパシタ                    | 40 |

| 7 2 | 二酸化珪素サブストレート層                |    |

| 7 4 | 酸化チタン密着層                     |    |

| 7 6 | 白金下部電極                       |    |

| 7 8 | PZT強誘電体層                     |    |

| 8 0 | 酸化イリジウム上部電極                  |    |

| 8 2 | $SRO$ キャップ層                  |    |

| 8 4 | アルミナ層                        |    |

| 8 6 | アルミナ金属配線用コンタクト               |    |

| 8 8 | 中間層                          |    |

【図1】

本発明に従って製造された半導体回路上の強誘電体キャパシタの断面図

【図2】

本発明の強誘電体キャパシタの断面図

【図3】

結晶化SrRuO<sub>3</sub>を含むSROキャップ層と非結晶化SrRuO<sub>3</sub>を含むSROキャップ層のリーク電流を比較するグラフ

【図4】

3種類の強誘電体キャパシタに対するQ<sub>sw</sub>を比較するグラフ

【図5】

強誘電体キャバシタの上部電極と強誘電体層の界面面の界面粗さに対して

$Q_{sw}$ を比較するグラフ

【図6】

SROキャップ層のアニール温度の関数として $Q_{sw}$ を比較するグラフ

【図7】

強誘電体キャバシタが水素雰囲気中に置かれた時間の関数として $Q_{sw}$ を比較するグラフ

【図8】

多数のSROキャップ層形成技術に対する $Q_{sw}$ のグラフ

---

フロントページの続き

(72)発明者 松浦 克好

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 齊藤 丈靖

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 小澤 聰一郎

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 佐藤 尚之

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 藤木 充司

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 三原 智

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 ジェフリー スコット クロス

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 堀井 義正

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 粟野 正明

(56)参考文献 特開平10-012830(JP,A)

特開2001-036026(JP,A)

特開2000-307081(JP,A)

特開2001-015696(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8246

H01L 27/105