(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-508548

(P2006-508548A)

(43) 公表日 平成18年3月9日(2006.3.9)

(51) Int.C1.

F 1

テーマコード(参考)

HO1L 29/78 (2006.01)

HO1L 29/78

301G

5F11O

HO1L 29/786 (2006.01)

HO1L 29/78

617J

5F14O

HO1L 21/336 (2006.01)

HO1L 29/78

616A

審査請求 未請求 予備審査請求 未請求 (全 15 頁)

(21) 出願番号 特願2004-570755 (P2004-570755)

(86) (22) 出願日 平成15年11月6日 (2003.11.6)

(85) 翻訳文提出日 平成17年7月27日 (2005.7.27)

(86) 國際出願番号 PCT/US2003/035355

(87) 國際公開番号 WO2004/051728

(87) 國際公開日 平成16年6月17日 (2004.6.17)

(31) 優先権主張番号 10255849.3

(32) 優先日 平成14年11月29日 (2002.11.29)

(33) 優先権主張国 ドイツ(DE)

(31) 優先権主張番号 10/442,745

(32) 優先日 平成15年5月21日 (2003.5.21)

(33) 優先権主張国 米国(US)

(71) 出願人 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノゼ、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68(番地なし)

(74) 代理人 100099324

弁理士 鈴木 正剛

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】ドープされたh i g h - k サイドウォールスペーサを有す電界効果トランジスタのドレイン/ソース拡張構造

## (57) 【要約】

h i g h - k スペーサエレメントから、下にある半導体領域へドーパント拡散することにより形成される拡張領域と併せて、電界効果トランジスタのゲート電極のh i g h - k 誘電体スペーサエレメントは、拡張領域に電荷担体密度の増加を提供する。このようにして、電荷担体密度を、略拡張領域のドーパントの固溶度に限定することが克服され、これにより、トランジスタのパフォーマンスを過度に落とすことなく、極めて浅い拡張領域が可能になる。

**【特許請求の範囲】****【請求項 1】**

電界効果トランジスタを形成する方法であって、

アクティブ領域 203 に形成されてこのアクティブ領域 203 からゲート絶縁層 206 により離間されているゲート電極 205 を備えた基板 201 に、ドープされた hig h - k 誘電体層 220 を形成するステップと、

前記 hig h - k 誘電体層 220 から前記活性領域 203 へドーパントを拡散して拡張領域 208 を形成するように、前記基板を熱処理するステップと、

前記ゲート電極 205 のサイドウォールで、サイドウォールスペーサ 210 を形成するために、前記 hig h - k 誘電体層 220 をパターニングするステップと、

前記電界効果トランジスタのソース及びドレイン領域 211 を形成するために、注入マスクとして前記サイドウォールスペーサ 210 を用いて、イオン注入プロセス 212 を実施するステップと、を有する方法。

**【請求項 2】**

前記ドープされた hig h - k 誘電体層 220 の形成ステップでは、少なくとも 1 つのドーパント材料の存在下で前記 hig h - k 誘電体層 220 のデポジットがなされる、請求項 1 記載の方法。

**【請求項 3】**

前記ドープされた hig h - k 誘電体層 220 の形成ステップには、前記 hig h - k 誘電体層 220 をデポジットするステップと、少なくとも 1 つのイオン注入及び犠牲層からの拡散により、前記 hig h - k 誘電体層 220 にドーパントを導入するステップとが含まれる、請求項 1 記載の方法。

**【請求項 4】**

前記ドープされた hig h - k 誘電体層 220 のドーパント濃度は、ほぼ、前記 hig h - k 誘電体層内でのドーパントの固溶度の範囲内、あるいはそれ以上である、請求項 1 記載の方法。

**【請求項 5】**

前記 hig h - k 誘電体層 206 のパターニングが、前記基板に熱処理を施す前に実施される、請求項 1 記載の方法。

**【請求項 6】**

前記基板 201 は、前記イオン注入プロセス 212 により導入されるドーパントの活性化と、格子の損傷の回復とが同時になされるように、前記イオン注入プロセス 212 後に、熱処理される、請求項 1 記載の方法。

**【請求項 7】**

前記 hig h - k 誘電体層 220 の形成前に、誘電体バリア層を形成するステップを更に有する、請求項 1 記載の方法。

**【請求項 8】**

前記基板 201 を熱処理ステップが、約 800 - 1200 の範囲の温度で実施される、請求項 1 記載の方法。

**【請求項 9】**

前記熱処理の持続時間が、約 10 秒から 30 分の範囲である、請求項 8 記載の方法。

**【請求項 10】**

前記 hig h - k 誘電体層 220 が、タンタル、ジルコニウム、ハフニウム、ランタン、イットリウム、及びストロンチウムのうちの少なくとも 1 つの酸化物及びシリケートの 1 つを有している、請求項 1 記載の方法。

**【請求項 11】**

電界効果トランジスタを形成する方法であって、

基板 201 に形成される活性領域 203 にソース及びドレイン領域 211 を形成するようにイオン注入プロセスを実施するステップを有し、前記基板は、前記活性領域 203 に形成されるとともにゲート絶縁層 206 により前記活性領域 203 から離間されたゲート

電極 205 を含み、前記ゲート電極は、そのサイドウォールに形成されているサイドウォールスペーサを有しており、

前記サイドウォールスペーサを取り除くステップと、

前記基板に、ドープされた hig h - k 誘電体層 220 を形成するステップと、

前記ドープされた hig h - k 層 229 から前記活性領域へドーパントを導入するよう前に前記基板をアニーリングするステップ、かつ、

前記ゲート電極 205 のサイドウォールに hig h - k サイドウォールスペーサを形成するように前記 hig h - k 誘電体層 220 をパターニングするステップ、を有する方法。

#### 【請求項 12】

前記基板 201 をアニーリングするステップは、前記イオン注入プロセス中に導入されるドーパントが活性化され、かつ、前記イオン注入プロセスがもたらす格子の損傷が少なくとも部分的に回復するように実施される、請求項 11 記載の方法。

#### 【請求項 13】

前記ドープされた hig h - k 誘電体層 220 の形成ステップは、少なくとも 1 つのドーパント材料の存在下で前記 hig h - k 誘電体層 220 をデポジットすることを含む、請求項 11 記載の方法。

#### 【請求項 14】

前記ドープされた hig h - k 誘電体層 220 の形成ステップは、前記 hig h - k 誘電体層 220 をデポジットするステップと、犠牲層からのイオン注入及び拡散の少なくとも一方によって前記 hig h - k 誘電体層にドーパントを導入するステップと、を有する、請求項 11 記載の方法。

#### 【請求項 15】

前記ドープされた hig h - k 誘電体層のドーパント濃度が、ほぼ、前記 hig h - k 誘電体層 220 内の固溶度の範囲内、あるいはそれ以上である、請求項 11 記載の方法。

#### 【請求項 16】

前記 hig h - k 導電体層 220 をパターニングするステップは、基板をアニーリングする前に行われる、請求項 11 記載の方法。

#### 【請求項 17】

電界効果トランジスタであって、

ドーパント濃度を有す活性半導体領域 203 に形成されてこの活性半導体領域 203 からゲート絶縁層 204 により離間されているゲート電極 205 と、

前記ゲート電極 205 のサイドウォールに形成されて前記活性半導体領域の一部の上にある、ドープされた hig h - k 誘電体スペーサエレメント 210 を有し、

前記 hig h - k 誘電体スペーサエレメント 210 と前記活性半導体領域との間の界面の一部におけるドーパント濃度が、前記活性半導体領域 203 の前記ドーパント濃度以上である、電界効果トランジスタ。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

概して本発明は、集積回路の製造に関し、また更に具体的には、MOSトランジスタ構造などの、高ドープされたシャロージャンクションを要求する、高度な電界効果トランジスタの製造に関する。

#### 【背景技術】

#### 【0002】

集積回路の製造プロセスは、個々の回路素子の加工寸法を縮小するという継続的な努力がもたらす様々な方法で改良が続けられている。また近い将来は、シリコン基板は入手が容易であるとともに、過去数十年にわたり開発されている十分に確立されたプロセス技術により、集積回路の大半は現在のところ、シリコンデバイスをベースとしている、あるいは近い将来はシリコンデバイスをベースとするであろう。改良された記録密度と向上した

10

20

30

40

50

パフォーマンスを有する集積回路を開発するうえでの主要な問題は、最新のCPUやメモリデバイスを生産するのに必要とされうる、非常に多くのトランジスタ素子を提供するために、MOSトランジスタエレメントなどのトランジスタエレメントを縮小することである。

寸法が縮小した電界効果トランジスタを製造する1つの重要な態様は、トランジスタのソース及びドレイン領域を離す導電性チャネルの形成を制御する、ゲート電極の長さの縮小である。トランジスタエレメントのソース及びドレイン領域は、基板あるいはウエル領域などの、周囲の結晶活性領域のドーパントと比較された、逆の導電型のドーパントを含む導電性の半導体領域である。

#### 【0003】

更に小型で速いトランジスタエレメントを得るためにには、ゲート長の縮小が必要であるが、しかしながら、縮小されたゲート長に対する、適切なトランジスタパフォーマンスを維持するためには、複数の問題点が更に含まれる。この点における1つの課題は、シャロージャンクション領域、つまり、ソース及びドレイン領域、を設けることであり、チャネルからドレイン及びソース領域のそれぞれの接触領域へ電荷担体を伝導して、抵抗率が最小となるように高導電率を示すことが求められる。

一般に、高導電率を持つシャロージャンクションの必要条件は、横方向に、また深さで変化するプロファイルを持つ、高ドープ濃度を達成するよう、イオン注入シーケンスを実施することによって満たされる。しかしながら、結晶基板領域に高用量のドーパントを導入することにより、結晶構造に大きな損傷が発生し、従って、ドーパントを活性化させるために、すなわち、ドーパントを結晶サイトに置くために、また、大きな結晶損傷を回復させるために、一回以上のアニールサイクルが要求される。しかしながら、アニールサイクルがドーパントを電気的に活性化し得ることから、ドーパント濃度は制限される。更に、結晶損傷の回復や、ドーパントの活性化に加えて、望ましくないドーパントの拡散がアニーリング中に発生し、これにより“不明瞭な(blurred)”ドーパントプロファイルがもたらされうる。図1a - 図1dを参照すると、従来の電界効果トランジスタを形成する、典型的な従来のプロセスフローが、関連の問題点を更に詳しく説明するために説明されている。

#### 【0004】

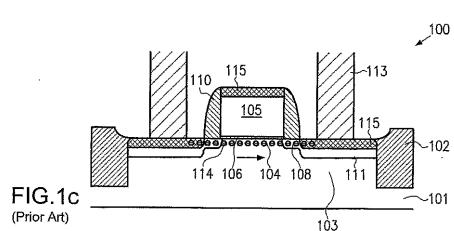

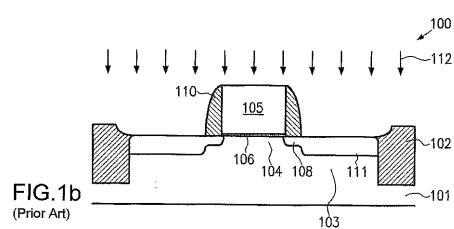

図1aに、中間の製造段階における、トランジスタ構造100の概略図を示す。トランジスタ構造100は、一般にシリコン基板、あるいはシリコン層を含む基板である、基板101を有しており、活性領域103がシャロートレンチアイソレーション(STI: Shallow Trench Isolation)により取り囲まれている。ゲート電極105は活性領域103上に形成されており、またそこから、ゲート絶縁層106により離間されている。先に述べている、図1aのゲート長は、ゲート電極105の横方向の寸法である。ゲート絶縁層106の下にある活性領域103の部分は、“先端(tip)”領域としても称されうる、ソース及びドレイン拡張領域108間に設けられる、チャネル領域104を表す。

#### 【0005】

図1aに示されているように、トランジスタ構造100を形成する一般的なプロセスフローは、以下のプロセステップを有しうる。高度なフォトリソグラフィ、エッティング、及び蒸着法で、シャロートレンチアイソレーションを形成した後、注入シーケンスが実施され、活性領域103内に所要のドーパントプロファイル(図示せず)が生成される。その後、ゲート絶縁層106が、ゲート電極105のゲート長と一致する所要の厚みを伴って、最新の酸化、及び/あるいは蒸着法により形成される。次に、ゲート電極105が、最新のフォトリソグラフィ及びエッティング技術により、プロシリコン層からパターニングされる。

次に、参考番号107により示されているイオン注入が実施され、活性領域103に所要の導電型のドーパントが導入され、これにより、拡張領域108が形成される。既述の通り、ゲート電極105のゲート長を縮小するには、拡張領域108を、109として示されている、約30 - 200 nmの範囲のゲート長に対して、約10 - 100 nmの範囲

10

20

30

40

50

の厚みで、浅くドープされた領域として提供することが要求される。従って、使用されるドーパントの型に応じて、相対的に低エネルギーで、また、拡張領域 108 内で所要の高ドープ濃度を提供するために高用量で、イオン注入 107 が実施される。

#### 【0006】

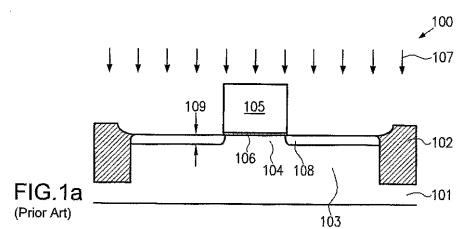

図 1 b に、製造段階が進んだ状態における、トランジスタ構造 100 を概略的に示す。一般に、二酸化シリコン、あるいは窒化シリコンで形成されている、サイドウォールスペーサ 110 は、ゲート電極 105 のサイドウォールに形成されている。サイドウォールスペーサ 110 は、自己整合された蒸着や異方性エッティング技術により形成され、後続のイオン注入シーケンス 112 に対して注入マスクとして働き、ソース及びドレイン領域 111 が形成される。

10

#### 【0007】

既に述べているように、高ドーパント濃度が、ソース及びドレイン領域 111 において、また同様に拡張領域 108 において要求され、その結果、深刻な結晶の損傷が注入シーケンス 107、112 の間に発生する。従って、通常は高速熱アニールなどの熱処理が一方では要求され、ドーパント原子が活性化され、また、ソース及びドレイン領域 111 と拡張領域 108 における、損傷を受けている構造が実質的に再結晶化される。しかしながら、高ドーパント濃度では、高速熱アニールサイクルによる電気的な活性化は、シリコン結晶のドーパントの固溶度により制限される。更に、ドーパントは活性領域 103 において、望ましくない結晶領域に直ちに拡散し、これにより、トランジスタのパフォーマンスが著しく落ちる。他方、ソース及びドレイン領域 111 と拡張領域 108 内に、結晶構造を効率的に再建するには、十分に長時間にわたって相対的に高い温度が要求されるが、このことは、ドーパント拡散を過度に増やしうる。結果として、トランジスタ構造 100 の活性化や回復に関しては、トレードオフがなされる。特に、デバイス寸法が 100 nm やそれ未満のゲート長にまで縮小されるので、活性化したドーパントが十分でないために低減された導電率、及び / あるいは、拡散による不明瞭なドーパントプロファイルにより、低下したトランジスタパフォーマンスの問題点が更に強調される。

20

#### 【0008】

図 1 c に、製造プロセスの完了後のトランジスタ構造 100 を概略的に示す。金属シリサイド領域 115 がゲート電極 105 の上部に形成され、また、コバルトシリサイド、あるいはいずれのほかの適切な耐火金属のシリサイドを有しうる、ドレイン及びソース領域 111 が形成される。接触線 113 がドレイン及びソース領域 111 と接して形成され、更なる回路素子（図示せず）や他の接続線（図示せず）へ電気接続が提供される。一般に接触線 113 は、タングステンや他の適切なバリアや接着剤を有している。

30

#### 【0009】

一般に金属シリサイド領域 115 の形成は、適切な高融点金属をデポジットあるいは蒸着することと、たとえ重くドープされた場合であっても、シリコンよりも著しく低いシート抵抗を持つ金属シリサイド領域 115 を得るために、後続の適切に設計されたアニールサイクルとを含む。接続線 113 は、誘電体層（便宜上、図示せず）をデポジットし、また、実質的に金属で充填されたバイアスを形成するために、誘電体層をパターニングすることにより形成され、通常、薄いバリアや接着層がバルク金属に充填する前に形成される。

40

#### 【0010】

トランジスタ構造 100 のオペレーション中、N チャネルトランジスタの場合は、114 により示されているように、実質的に電子を有したチャネル領域 104 に薄いチャネルが形成されるように電圧が接触線 113 に印加され、また、対応の制御電圧がゲート電極 105 に印加される。既述の通り、中でもトランジスタのパフォーマンスは、チャネル 104 から拡張領域 108 までの、また領域 108 のシート抵抗からの遷移抵抗 (transition resistance) に大きく依存している。その理由は、この領域には実質的に金属シリサイドが形成されないからである。拡張領域 108 とドレイン及びソース領域 111 を形成することが困難であることから、すなわち、十分に回復されていない格子の損傷と、活性ド

50

ーパント濃度の制限のために、デバイスのパフォーマンス、特に、極度に縮小されたトランジスタエレメント100に対するパフォーマンスは低下し、これにより、集積回路の回路素子を縮小することにより、通常は得られる利点が部分的に相殺されることになる。

#### 【0011】

上述の問題に鑑みて、上述の問題点を回避する、あるいは少なくとも実質的に低減する、電界効果トランジスタ構造を形成する、改良された技術が必要とされる。

#### 【発明の開示】

##### 【発明の詳細な説明】

#### 【0012】

概して本発明は、ゲート電極のサイドウォールに形成される、高誘電率を示す誘電体材料を有すサイドウォールスペーサが、コンピュータシミュレーションにより示されているように、下層の導電領域における電荷担体の蓄積を促進しうることを見いだしたことに基づくものである。この効果は、サイドウォールスペーサの誘電体材料から、下にある拡張領域へドーパントを外方拡散することにより得られる高ドープ濃度と組み合わせられ、これにより、注入ステップを回避し、従って、トランジスタエレメントの全体の導電率を大幅に高めることが出来る。

#### 【0013】

本発明の一実施形態によれば、活性領域に形成され、そこからゲート絶縁層により離されているゲート電極を含む基板に、ドープされた $h_{igh-k}$ 誘電体層を形成することを含む電界効果トランジスタを形成する方法が提供される。基板を用いて熱処理が実施され、 $h_{igh-k}$ 誘電体層から活性領域へドーパントを拡散し、拡張領域が形成される。ゲート電極のサイドウォールにサイドウォールスペーサを形成するために、 $h_{igh-k}$ 誘電体層がパターニングされ、また、注入マスクとしてサイドウォールスペーサを用いて、注入プロセスが実施され、ソース及びドレイン領域が形成される。

#### 【0014】

本発明の更なる実施形態によれば、活性領域に形成され、そこからゲート絶縁層により離されているゲート電極を含む基板に設けられている活性領域に、ソース及びドレイン領域を形成するために、注入プロセスを実施することを含み、ゲート電極は、そのサイドウォールに形成され、注入マスクとして働く、サイドウォールスペーサを有するものである電界効果トランジスタを形成する方法が提供される。次に、サイドウォールスペーサが取り除かれ、ドープされた $h_{igh-k}$ 誘電体層が形成される。次に基板は、 $h_{igh-k}$ 誘電体層から下にある領域へドーパントを拡散するために熱処理され、これにより、注入プロセスにより導入された原子が、少なくとも部分的に活性化される。更に、ゲート電極に $h_{igh-k}$ サイドウォールスペーサを形成するために、 $h_{igh-k}$ 誘電体層がパターニングされる。

#### 【0015】

本発明の更に別の実施形態によれば、誘電体領域の下に、導電性の浅くドープされた半導体領域を形成する方法は、半導体領域を有す基板に、誘電体層を形成することを含み、誘電体層は、タンタル、及び／あるいはジルコニウム、及び／あるいはハフニウム、及び／あるいはランタン、及び／あるいはイットリウム、及び／あるいはストロンチウムの酸化物を有する。ドーパントが誘電体層に導入され、基板がアニールされてドーパントが半導体領域に拡散される。次に、誘電体層がパターニングされ、ドープされた半導体領域に誘電体領域が形成され、外部電場の存在下で、誘電体領域下の電荷担体の蓄積が増加される。

#### 【0016】

本発明の更にまた別の実施形態によれば、電界効果トランジスタは、活性半導体領域の上に形成され、そこからゲート絶縁層により離されている、ゲート電極を有している。ドープされた $h_{igh-k}$ 誘電体スペーサエレメントは、ゲート電極のサイドウォールに、また、半導体領域の一部に形成される。スペーサエレメントと半導体領域との間の界面(interface)の少なくとも一部におけるドーパント濃度は、スペーサエレメントにおいて

10

20

30

40

50

は等しく、また、半導体領域においては、それよりも高い。

#### 【0017】

本発明は、様々な改良を行い、また、他の形態で実施することができるが、ここに説明されている特定の実施例は、例示として示したものであり、以下にその詳細を記載する。しかし当然のことながら、ここに示した特定の実施例は、本発明を開示されている特定の形態に限定するものではなく、むしろ本発明は添付の請求項によって規定されている発明の範疇に属する全ての改良、等価物、及び変形例をカバーするものである。

#### 【発明を実施するための最良の形態】

#### 【0018】

本発明の実施例を以下に記載する。簡素化のため、現実の実施品におけるすべての特徴を本明細書に記載することはしていない。当然のことながら、そのような現実の実施品の開発においては、開発者における特定の目標を達成するため、システム的制限やビジネス的制限との摺り合せなど、多くの特定の実施の決定がなされる。それらは各実施形態によって様々に変化するものである。更に、そのような開発努力は複雑で時間を消費するものであるのは当然のことであるが、それでもなお、この開示の恩恵を有する当業者にとっては通常作業の範疇に入るものである。

#### 【0019】

本発明を添付の図面を参照しながら説明する。半導体デバイスの様々な構造と注入領域が非常に正確で鋭い形状とプロファイルを有し各図面に描かれているが、当業者であれば実際にこれらの領域や構造が図面に示されているほど正確なものではないと認識できるであろう。加えて、図面に描かれている様々な特徴と注入領域の相対的な大きさは、製造されているデバイスの特徴や領域のサイズと比較すると誇張や縮小されている。しかしながら、添付の図面は本発明の実施例を説明・解説する目的で添付されているものである。本明細書で使用される用語や言い回しは関連技術において当業者たちによって理解される単語や言い回しと一貫した意味を持つものと理解、解釈される。本明細書において用語あるいは言い回しを一貫して使用していても、これらの用語や言い回しのいかなる特定の定義、すなわち、当業者により理解される通常の意味及び慣習的な意味からは異なる定義を意味するものではない。用語や言い回しを、特定の意味を有する範囲において用いる場合、つまり当業者により理解されているのとは異なる意味で用いる場合、本明細書においては、直接かつ明確にそのような言葉や言い回しの特定の定義を行う。

#### 【0020】

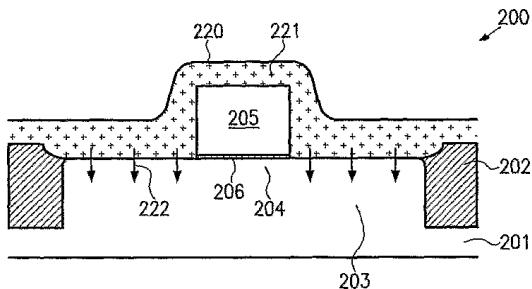

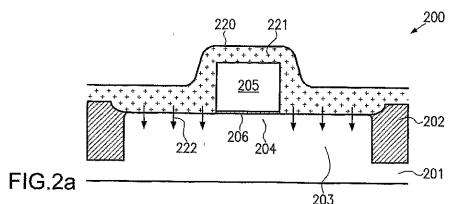

図2a - 図2fを参照すると、本発明の実施形態が説明されている。高度なドーパント濃度を持つ半導体領域が最小の結晶損傷しか持たずに得られ、また、外部電場の存在下で、誘電率の向上により電荷担体の蓄積が増加されるように、誘電体層が高ドープされた半導体領域に設けられる。この点において、“high-k”誘電体層あるいは材料は、通常用いられている誘電体材料である二酸化シリコンや窒化シリコンの誘電率を超える誘電率を示す、いずれの材料をも特定することを意味する。これら通常用いられている誘電材料における誘電率は、誘電体層を形成するプロセス技術に応じて、約3.5から7.5までの範囲である。従って、以下の明細書では、添付の請求の範囲と同様に、“high-k”という用語は、あるいは特に規定がない場合、約8又はそれ以上の比誘電率に関する。更に、本発明は電界効果トランジスタの形成に対して、特に、従来のデバイスよりも高い導電率を示す、改良された拡張領域に対して、有利に使用されうる。しかしながら、本発明の原理はまた、相対的に浅くドープされた半導体領域において、高導電率が要求される、別の回路素子の形成にも応用できる。

#### 【0021】

図2aに、基板201を備えたトランジスタ構造200を概略的に示す。基板201はシリコン基板、シリコン-オン-インシュレータ(SOI:Silicon-on-Insulator)基板、あるいは、活性半導体領域203を有することができるのであれば、いずれのほかの適切な基板でありうる。活性領域203は絶縁構造202に取り囲まれており、該絶縁構造202は、本例では、シャロートレンチアイソレーション(STI:Shallow Trench Iso

10

20

30

40

50

lation) 構造の形で提供されている。ポリシリコンなどや、あるいは、いずれの他のゲート電極材料を有しているゲート電極 205 は、活性領域 203 上に形成され、また、そこからゲート絶縁層 206 により離間されている。ゲート長と称される、ゲート電極 205 の横方向の寸法は、活性領域 203 のチャネル領域 204 を実質的に形成している。いくつかの実施形態では、ゲート長は、約 30 - 200 nm の範囲である。更に、誘電体層 220 が、後続のプロセスステップでサイドウォールスペーサエレメントを形成するように設計されている厚みを備えて、トランジスタ構造 200 上に形成される。誘電体層 220 は、タンタル、ジルコニウム、ハフニウムなどのシリケートあるいは酸化物などの、high h-k 材料を有しており、それらは一般に、約 10 - 20 の、あるいはそれ以上の比誘電率を有している。その他の適切な high h-k 材料には、ランタン、イットリウム、ストロンチウムなどで形成されている酸化物が含まれ、それらは、20 を超える比誘電率を有している。誘電体層 220 は更に、N 型ドーパントとして、ヒ素、及び / あるいはリン原子、あるいは P 型ドーパントとして、ボロン、及び / あるいはインジウムなどの、所望の導電型のドーパント 221 を有している。誘電体層 220 のドーパント 221 の濃度は、特定の一実施形態では、誘電体層 220 の材料内のドーパント 221 の固溶度の範囲内であるか、あるいはそれぞれの固溶度としては一層高いものとなっている。しかしながら、別の実施形態では、ドーパント 221 の濃度は、半導体構造 200 の更なるプロセスに要求される適切な値に調整される。

10

## 【0022】

図 2a に示されているように、トランジスタ構造 200 の製造に対する、一般的なプロセスフローは以下のプロセスを有しうる。図 1a を参照して既に説明されているように、活性領域 203、絶縁構造 202、ゲート絶縁層 206、及びゲート電極 205 の形成は、実質的に同じステップを有しうる。従来のプロセスフローとは異なり、high h-k 誘電体材料を有している誘電体層 220 は、化学蒸着 (CVD) プロセス、あるいは物理蒸着 (PVD) プロセスなどの適切な蒸着法により、蒸着 (あるいはデポジット) がなされる。誘電体層 220 を蒸着する間、所要の濃度でドーパント 221 が誘電体層 220 へ導入されるように、蒸着雰囲気が制御されうる。例えば、ドーパントを含むいずれの先駆ガスが蒸着雰囲気に加えられ、例えば、それぞれの先駆ガスの流量が、最終的に所要のドーパント濃度を得るように制御される。

20

## 【0023】

別の実施形態では、既知の蒸着レシピに従って、誘電体層 220 の蒸着が行われ、その後、ドーパント 221 がいずれの適切な技術により、誘電体層 220 に導入されうる。例えば、誘電体層にドーパント 221 を導入するために、注入シーケンスが実施されうる。別の実施形態では、付加的な拡散層 (図示せず) が、誘電体層 220 上に形成されるとともに、ドーパント 221 がその後、トランジスタ構造 200 をアニールすることにより、誘電体層 220 に導入されうる。選択される方法に関わらず、ドーパント導入後の誘電体層 220 のドーパント濃度は、約  $10^{19} - 10^{21}$  atoms/cm<sup>3</sup> でありうる。

30

## 【0024】

その後、誘電体層 220 に用いられる材料、ドーパント 221 の型、ドーパント 221 の所要の浸入度、などに応じて、例えば、約 800 から 1200 の範囲で、約 10 秒から 30 分間、アニーリングするなどの、熱処理を実施することによって、活性領域 203 にドーパント 221 の一部が導入されうる。

40

## 【0025】

参照番号 222 により示されているように、活性領域 203 にドーパント 221 を外方拡散することにより、誘電体層 220 のドーパント濃度により制御されうるプロセスにより、また、活性領域 203 の結晶構造に実質的に損傷を与えることなく、主に、アニールサイクルのプロセスパラメータにより、活性領域 203 に所要のドーパント濃度を確立できる。

## 【0026】

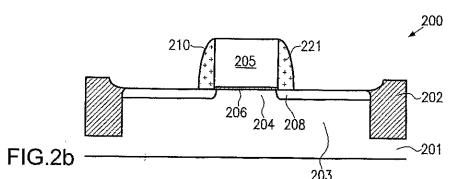

図 2b に、ドーパント 221 を活性領域 203 に導入し、これにより拡張領域 208 が

50

形成される、熱処理完了後のトランジスタ構造 200 を概略的に示す。いくつかの実施形態では、ドーパント濃度は約  $10^{19} - 5 \times 10^{20}$  atom cm<sup>-3</sup> でありうる。サイドウォールスペーサ 210 が、従来の異方性エッチングプロセスにより形成されている、ゲート電極 205 のサイドウォールに形成される。

#### 【0027】

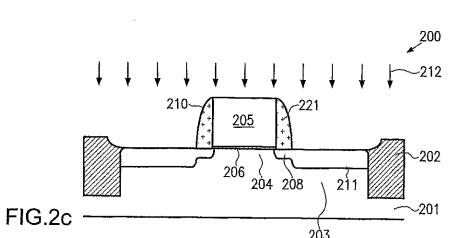

図 2c に、更に進んだ製造状態におけるトランジスタ構造 200 を示す。ソース及びドレイン領域 211 は、参照番号 212 により示されているように、注入プロセス 212 により、活性領域 203 に形成される。既に述べているように、注入プロセス 212 を実施することにより、拡張領域 208 内、あるいは下に部分的にソース及びドレイン領域 211 が形成されるように、所要の導電型のドーパントが、活性領域 203 の特定の深さへ導入され、特定のトランジスタパフォーマンスに応じて、ドーパントプロファイルが得られる。ドレイン及びソース領域 211 をドープするための一般的なエネルギーは、ヒ素、リン、ボロン、インジウムなどのドーパント型に応じて、約  $10^{15} - 10^{16}$  イオン / cm<sup>2</sup> の範囲の投与量で、約 30 - 90 keV の範囲である。

#### 【0028】

イオン注入 212 後に、注入 212 により導入されたドーパントを活性化させるために、また、イオン衝撃 (ion bombardment) がもたらす格子の損傷を回復させるために、熱処理が実施される。例えば、アニールプロセスが、約 900 - 1200 の範囲の温度で、約 10 - 300 秒間、実施される。このアニールサイクル中に、更なるドーパントが拡張領域 208 にも導入され、及び / あるいは、拡張領域 208 のドーパントがまた、活性化されうる、すなわち、格子サイトに転送される。レーザーアニーリングなどの、非平衡アニールプロセスが実施されない限りは、達成可能なドーパントの活性化が活性領域 203 の結晶領域におけるドーパントの固溶度によって決定されるように、一般的なアニールサイクルが熱平衡条件の下で実施される。

誘電体層 220 から、及び / あるいはスペーサエレメント 210 からドーパント 221 を導入することにより、拡張領域 208 に相対的に高ドープ濃度を提供することにより、スペーサ 210 により覆われている少なくとも拡張領域 208 が、最小限の結晶損傷を示し、従って、ドーピングの程度が固溶度により制限されていても、従来のデバイスと比較すると導電性の著しい向上を示す。以下に詳しく説明しているように、従来のデバイスと同様、回復されていない結晶損傷による電荷担体の散乱が著しく低減するからである。

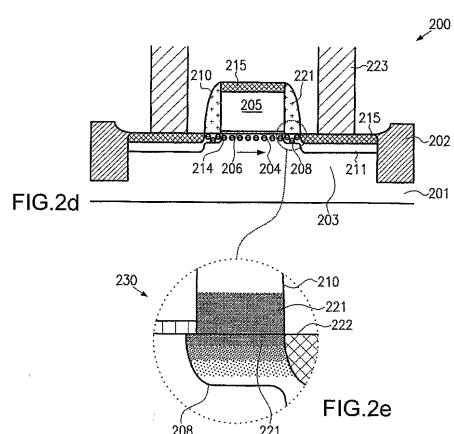

#### 【0029】

図 2d に、完成したトランジスタ構造 200 を概略的に示す。金属シリサイド領域 215 は、ゲート電極 205 及び、ドレインとソース領域 211 の上部に形成される。更に、接触線が設けられ、他の回路素子（図示せず）、及び / あるいは導電線（図示せず）へ、ソース及びドレイン領域 211 が電気的に接続される。

#### 【0030】

図 2d に示されているトランジスタ構造 200 を形成するプロセスステップは、図 1c に関して既に説明されているステップと同様であるため、対応する説明は省略する。

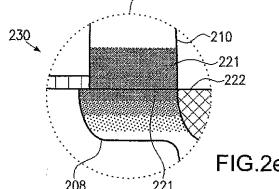

#### 【0031】

動作時においては、ゲート電極 205 に加えられる制御電圧、及び接触線 213 を介してソース及びドレイン領域 211 へ加えられる対応のオペレーション電圧が、214 として示されているように、ソース及びドレイン間のチャネル領域 204 に電流フローを確立する。便宜上、N 型の電界効果トランジスタが示されている一方で、実質的に同一の基準が P 型トランジスタにも適用される。既に説明しているように、拡張領域 208 の部位 230 における欠陥率が低減されたことで、電荷担体の散乱が小さくなつて導電性の向上をもたらす。更に、サイドウォールスペーサ 210 の高誘電率により、下にある拡張領域 208 への静電結合が増加し、これにより、部位 230 の電荷担体の蓄積が増加される。増加した静電接合と、固溶度の範囲内でありうる拡張領域 208 の高ドーパント濃度により、電荷担体濃度は、通常は  $3 \times 10^{20}$  / cm<sup>3</sup> の範囲である、固溶度により決定される大きさのオーダーを十分に超える。従って、従来のデバイスに相当する拡張領域 208 における

10

20

20

30

40

50

るドーパント濃度に対しても、電荷担体密度の増加が本発明により達成され、付加的には欠陥値の低減が導電率を高めることにもなりうる。これにより、トランジスタのパフォーマンスを落とすことなく、極めて浅いシャロー拡張領域 208 を可能にする。

#### 【0032】

図 2 e に部位 230 を拡大したものを概略的に示す。図 2 e に示すように、スペーサエレメント 210 と拡張領域 208 との間の界面（インターフェース）222 付近のドーパント 221 の濃度は、拡散メカニズムにより、実質的には拡張領域 208 における対応するドーパント濃度以上となっている。拡張領域 208 へドーパント 221 を外方拡散するために実施されるアニールサイクルが、スペーサエレメント 210（あるいは誘電体層 220（図 2 a））を“空乏状態(deplete)”とするに十分長く、また、インターフェース 222 において略平衡状態が得られるに十分でかつ拡張領域 208 内にドーパントを蓄積するまでに十分に長い時間にわたって実施される場合に、インターフェース 222 の両側面に実質的に等しい濃度が得られる。特に、スペーサエレメント 210 における初期のドーパント濃度が、スペーサ材料や、下層の活性領域 203 の固溶度の限界を越えるように選択される場合、固溶度のオーダーに近い高ドープ濃度や、活性層 203 が、ドーパント 221 を拡張領域 208 へ拡散することにより得られうる。更に従来のプロセスフローでは通常、拡張領域のドーパント濃度が、所望のアニールサイクル中に低減される。これは、例えば、ドーパントを活性化させ、また、望ましくないドーパントの外方拡散によるドレイン及びソース領域の形成後に、結晶の損傷を回復させるためになされる。しかしながら、上述の本発明の実施形態によれば、これらのアニールサイクル中のドーパント濃度は、実質的に維持されうる、あるいは、インターフェース 222 におけるドーパント濃度が高いことで、濃度が高くすらなり得る。その理由は、ドーパント 221 がドープされたスペーサエレメント 210 は、下層の拡張領域 208 よりもその濃度が高い限りは、ドーパント 210 を継続的に提供することになるからである。

#### 【0033】

上述の例示の実施形態では、活性領域 203 へのドーパント 221 の外方拡散は実質的に、誘電体層 220（図 2 a）から下の基板領域へ発生する。他の実施形態では、アニールサイクルを実施せずに、誘電体層 220 をまずパターニングし、また、スペーサエレメント 210 の形成後に、活性領域 203 へドーパント 221 を導入することが好ましいと考えられ、例えば、ソース及びドレイン領域 211 を形成における注入プロセス 212（図 2 c）後に要求される、アニールサイクル中である。

#### 【0034】

本発明の別の実施形態では、ソース及びドレイン領域 211 は、二酸化シリコン、及び／あるいは窒化シリコンなどの、従来の low-k 材料を有しうる、対応のサイドウォールスペーサエレメント（図示せず）を形成することにより、拡張領域 208 を形成する前に、かつ、ドレイン及びソース領域 211 を形成するために、イオン注入プロセス後にサイドウォールスペーサを取り除く前に形成されうる。その後、プロセスシーケンスが、図 2 a に関して説明されているように継続され、誘電体層 220 から、及び／あるいは、スペーサエレメント 210 からのドーパント 221 の導入が、ドレイン及びソース領域 211 におけるドーパントを活性化するために用いられる、別々の、あるいは共通のアニールサイクルで実施されうる（図 2 c の注入シーケンス 212 はもはや要求されない）。

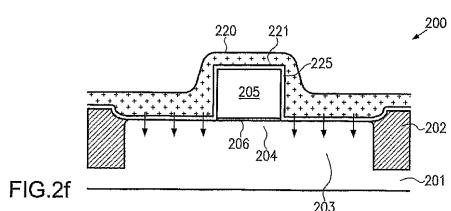

#### 【0035】

図 2 f に、本発明の更なる実施形態による、早期の製造段階におけるトランジスタ構造 200 を示す。トランジスタ 200 は、図 2 a の構造と全く同様であり、かつ、付加的には、誘電体層 220 の下に形成されたバリア層 225 を備えている。バリア層 225 は、活性領域 203 へのドーパント 221 の拡散を過度に遅らせることなく、下にある活性層 203 に、及び／あるいは隣接するゲート電極 205 に、層 220 の誘電体材料が必要以上に拡散されないための優れた特徴を示す、low-k 誘電体材料を有しうる。例えば、誘電体層 220 に含まれる、いくつかの high-k コンポーネントは、高温においては十分に安定しておらず、かつ、すぐに拡散しうる。その結果、バリア層 225 は、これら

10

20

30

40

50

のコンポーネントが、隣接する領域へ拡散するのを十分に防ぎうる。誘電体層 220 やバリア層 225 により形成される積層の全体の誘電率を過度に落とすことなく、十分なバリア特性を提供するように、バリア層 225 の厚みが選択されるという利点を有す。いくつかの実施形態では、3 - 10 nm の厚みを有す、二酸化シリコン、及び / あるいは窒化シリコン層は、隣接する領域に high-k 材料が拡散するのを十分に防ぎうる。更に、別の実施形態では、バリア層 225 は、層 225 の形成中にドープされうる、あるいは誘電体層 220 から活性領域 203 へドーパント 221 を導入するために、アニールサイクルが実施されるまで、非ドープのままにされうる。

#### 【0036】

本発明による利益を享受し得る当業者であれば、本発明に関して等価の範囲内で種々の変形及び実施が可能であることは明らかであることから、上述の個々の実施形態は、例示的なものに過ぎない。例えば、上述した方法における各ステップは、その実行順序を変えることもできる。更に上述した構成あるいは設計の詳細は、なんら本発明を限定することを意図するものではなく、請求の範囲の記載にのみ限定されるものである。従って、上述した特定の実施形態は、変形及び修正が可能であることは明らかであり、このようなバリエーションは、本発明の趣旨及び範囲内のものである。従って、本発明の保護は、請求の範囲によってのみ限定されるものである。

#### 【図面の簡単な説明】

#### 【0037】

【図 1 a】典型的な従来のプロセスフローの様々な製造段階におけるトランジスタ構造の概略的断面図。

【図 1 b】典型的な従来のプロセスフローの様々な製造段階におけるトランジスタ構造の概略的断面図。

【図 1 c】典型的な従来のプロセスフローの様々な製造段階におけるトランジスタ構造の概略的断面図。

【図 2 a】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

【図 2 b】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

【図 2 c】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

【図 2 d】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

【図 2 e】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

【図 2 f】本発明の実施形態による様々な製造段階におけるトランジスタ構造の形をした半導体構造の概略的断面図。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                   | Int'l Application No<br>PCT/US 03/35355                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H01L21/336 H01L29/78 H01L21/225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                   |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                   |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Citation of document, with indication, where appropriate, of the relevant passages                                | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 6 200 869 B1 (LIN MING-REN ET AL)<br>13 March 2001 (2001-03-13)<br>column 4, line 26 - line 48; figures 1-5    | 1-17                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 2001/038123 A1 (YU BIN)<br>8 November 2001 (2001-11-08)<br>paragraph '0036! - paragraph '0041!;<br>figures 2-6 | 1-17                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 5 926 715 A (FAN DER-TSYR ET AL)<br>20 July 1999 (1999-07-20)<br>the whole document                            | 1-17                                                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                   | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                   |                                                                                |

| Date of the actual completion of the international search<br><br><b>22 March 2004</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                   | Date of mailing of the International search report<br><br><b>30/03/2004</b>    |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   | Authorized officer<br><br><b>Nesso, S</b>                                      |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US 03/35355

| Patent document cited in search report | Publication date | Patent family member(s) |                          | Publication date         |

|----------------------------------------|------------------|-------------------------|--------------------------|--------------------------|

| US 6200869                             | B1<br>13-03-2001 | US<br>US                | 6297115 B1<br>6566212 B1 | 02-10-2001<br>20-05-2003 |

| US 2001038123                          | A1<br>08-11-2001 | NONE                    |                          |                          |

| US 5926715                             | A<br>20-07-1999  | NONE                    |                          |                          |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 トーマス フォイデル

ドイツ、01445 ラーデボイル、ツィーレシュトラッセ 13 アー

(72)発明者 マンフレッド ホルストマン

ドイツ、01099 ドレスデン、バオツネル シュトラッセ 18

(72)発明者 カルシュテン ビークツォレク

ドイツ、01109 ドレスデン、アム シュルフェルト 24

(72)発明者 シュテファン クリューゲル

ドイツ、01468 ボクスドルフ、アン デール オテリッツ 4

F ターム(参考) 5F110 AA30 CC02 DD05 DD13 EE05 EE09 EE14 EE31 GG02 GG12

GG28 HJ01 HJ04 HJ13 HJ16 HJ23 HK05 HM15 NN62

5F140 AA13 AC36 BA01 BF04 BF11 BF18 BG08 BG09 BG11 BG12

BG14 BG50 BG51 BG52 BG53 BG54 BH14 BH49 BJ01 BJ08

BK02 BK03 BK13 BK16 BK21 CB04