(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4686122号

(P4686122)

(45) 発行日 平成23年5月18日(2011.5.18)

(24) 登録日 平成23年2月18日(2011.2.18)

|              |                 |

|--------------|-----------------|

| (51) Int.Cl. | F 1             |

| G09F 9/30    | (2006.01)       |

| G09F 9/00    | (2006.01)       |

| H01L 29/786  | (2006.01)       |

| H01L 21/336  | (2006.01)       |

| H05B 33/10   | (2006.01)       |

| GO9F 9/30    | GO9F 9/30 338   |

| G09F 9/00    | G09F 9/00 338   |

| H01L 29/786  | H01L 29/78 612Z |

| H01L 21/336  | H01L 29/78 627G |

| H05B 33/10   | HO5B 33/10      |

請求項の数 5 (全 12 頁) 最終頁に続く

(21) 出願番号 特願2003-400612 (P2003-400612)

(22) 出願日 平成15年11月28日 (2003.11.28)

(65) 公開番号 特開2005-164741 (P2005-164741A)

(43) 公開日 平成17年6月23日 (2005.6.23)

審査請求日 平成18年11月17日 (2006.11.17)

(73) 特許権者 302020207

東芝モバイルディスプレイ株式会社

埼玉県深谷市幡羅町一丁目9番地2

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

マトリクス状に配列するとともにそれぞれが表示素子及び多結晶シリコン薄膜トランジスタを備えた複数の画素を具備し、

前記複数の画素は表示色が異なる第1乃至第3画素を複数組含み、それら第1乃至第3画素の前記表示素子はストライプ状に配列し、

前記複数の画素のうち、前記表示素子が前記ストライプ状の配列の同一列を構成している複数の前記画素は、前記多結晶シリコン薄膜トランジスタが前記列と平行な第1直線上で配列したものからなる第1画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1直線から離間した第2直線上で配列したものからなる第2画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1及び第2直線から離間した第3直線上で配列したものからなる第3画素群とを構成し、前記第1乃至第3画素群のそれにおける前記多結晶シリコン薄膜トランジスタの移動度のばらつきは、各列における前記多結晶シリコン薄膜トランジスタの移動度のばらつきと比較してより小さいことを特徴とするアクティブマトリクス型表示装置。

## 【請求項 2】

前記複数の画素のそれにおいて、前記表示素子はそれに流れる電流の大きさに応じて光学特性が変化する素子であり、前記多結晶シリコン薄膜トランジスタは第1電源端子と第2電源端子との間で前記表示素子と直列に接続された駆動トランジスタであることを特徴とする請求項1に記載のアクティブマトリクス型表示装置。

**【請求項 3】**

前記複数の画素のそれぞれは、映像信号線と前記駆動トランジスタのゲートとの間に接続されるとともにそれらの間の導通／非導通を走査信号線から供給される走査信号に基いて制御する画素スイッチと、前記駆動トランジスタのゲートと前記第1電源端子との間に接続されたキャパシタとをさらに備えたことを特徴とする請求項2に記載のアクティブマトリクス型表示装置。

**【請求項 4】**

各列において、前記第1画素群を構成した前記画素と前記第2画素群を構成した前記画素と前記第3画素群を構成した前記画素とは前記列に平行な方向にこの順番で繰り返し配列したことを特徴とする請求項1乃至請求項3の何れか1項に記載のアクティブマトリクス型表示装置。 10

**【請求項 5】**

マトリクス状に配列するとともにそれが表示素子及び多結晶シリコン薄膜トランジスタを備えた複数の画素を具備し、前記複数の画素は表示色が異なる第1乃至第3画素を複数組含み、それら第1乃至第3画素の前記表示素子はストライプ状に配列し、前記複数の画素のうち、前記表示素子が前記ストライプ状の配列の同一列を構成している複数の前記画素は、前記多結晶シリコン薄膜トランジスタが前記列と平行な第1直線上で配列したものからなる第1画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1直線から離間した第2直線上で配列したものからなる第2画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1及び第2直線から離間した第3直線上で配列したものからなる第3画素群とを構成したアクティブマトリクス型表示装置の製造方法であって、 20

非晶質シリコン層にレーザ光を線状ビームとして照射するとともに前記線状ビームの照射位置を前記列と交差する走査方向へ前記画素の前記走査方向の長さよりも狭いピッチで段階的にずらすことにより前記多結晶シリコン薄膜トランジスタの多結晶シリコン層を形成する工程を含み、

前記線状ビームが照射される領域の長手方向と前記列とを互いに平行とすることにより、前記第1乃至第3画素群のそれにおける前記多結晶シリコン薄膜トランジスタの移動度のばらつきを、各列における前記多結晶シリコン薄膜トランジスタの移動度のばらつきと比較してより小さくすることを特徴とするアクティブマトリクス型表示装置の製造方法。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、アクティブマトリクス型表示装置及びその製造方法に関する。

**【背景技術】****【0002】**

発光ダイオード表示装置や液晶表示装置などの表示装置は、薄型である等の有利な特徴から、事務機器やコンピュータなどで利用されている。また、近年では、液晶表示装置と比較して以下の点で優れた有機EL(Electro-Luminescence)表示装置の開発が盛んに行われている。 40

**【0003】**

1) 有機EL表示装置は、高輝度であり且つ自己発光型であるため、明るく鮮明な表示、広い視野角、バックライトレスによる低消費電力化・軽量化・薄型化を実現可能である。

2) 有機EL表示装置は、直流定電圧駆動のためノイズに強い。

3) 液晶表示装置の応答速度は msec オーダーであるのに対し、有機EL表示装置の応答速度は μsec オーダーと速いため、滑らかな動画表示が可能である。

4) 有機EL表示装置は、表示素子を固体のみで構成可能であるため、使用温度範囲がより広くなる可能性がある。 50

## 【0004】

ところで、上記の表示装置のなかでも、各画素に多結晶シリコン薄膜トランジスタを使用したアクティブマトリクス型表示装置は、特に優れた表示特性を実現可能である。

## 【0005】

しかしながら、そのようなアクティブマトリクス型表示装置では、各画素間で多結晶シリコン薄膜トランジスタの特性がばらつくことに起因して表示ムラが視認され易い。これは、表示素子が有機EL素子のように流れる電流の大きさに応じて光学特性が変化する素子であり且つ先の多結晶シリコン薄膜トランジスタが表示素子に直列に接続された駆動トランジスタである場合に特に顕著である。

## 【0006】

10

なお、本発明に関連した技術を記載した文献として、以下の特許文献1がある。この文献には、表示部の周辺に配置される駆動回路を正規回路と冗長回路とで構成するとともに、或る正規回路に含まれる多結晶シリコン薄膜トランジスタを形成するためのレーザアニールと、それと対を成す冗長回路に含まれる多結晶シリコン薄膜トランジスタを形成するためのレーザアニールとを別々のレーザショットで行うことが記載されている。また、この文献には、レーザアニールに際し、線状ビームを画素の配列に対して斜め方向に走査させることが記載されている。しかしながら、この文献には、多結晶シリコン薄膜トランジスタの画素に対する相対位置を画素間で異ならしめることは記載されていない。

【特許文献1】特開平11-344723号公報

## 【発明の開示】

20

## 【発明が解決しようとする課題】

## 【0007】

本発明は、上記問題点に鑑みてなされたものであり、表示ムラが視認され難いアクティブマトリクス型表示装置及びその製造方法を提供することを目的とする。

## 【課題を解決するための手段】

## 【0008】

30

上記課題を解決するために、本発明は、マトリクス状に配列するとともにそれが表示素子及び多結晶シリコン薄膜トランジスタを備えた複数の画素を具備し、前記複数の画素は表示色が異なる第1乃至第3画素を複数組含み、それら第1乃至第3画素の前記表示素子はストライプ状に配列し、前記複数の画素のうち、前記表示素子が前記ストライプ状の配列の同一列を構成している複数の前記画素は、前記多結晶シリコン薄膜トランジスタが前記列と平行な第1直線上で配列したものからなる第1画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1直線から離間した第2直線上で配列したものからなる第2画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1及び第2直線から離間した第3直線上で配列したものからなる第3画素群とを構成し、前記第1乃至第3画素群のそれぞれにおける前記多結晶シリコン薄膜トランジスタの移動度のばらつきは、各列における前記多結晶シリコン薄膜トランジスタの移動度のばらつきと比較してより小さいことを特徴とするアクティブマトリクス型表示装置を提供する。

## 【0009】

40

また、本発明は、マトリクス状に配列するとともにそれが表示素子及び多結晶シリコン薄膜トランジスタを備えた複数の画素を具備し、前記複数の画素は表示色が異なる第1乃至第3画素を複数組含み、それら第1乃至第3画素の前記表示素子はストライプ状に配列し、前記複数の画素のうち、前記表示素子が前記ストライプ状の配列の同一列を構成している複数の前記画素は、前記多結晶シリコン薄膜トランジスタが前記列と平行な第1直線上で配列したものからなる第1画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1直線から離間した第2直線上で配列したものからなる第2画素群と、前記多結晶シリコン薄膜トランジスタが前記列と平行であり且つ前記第1及び第2直線から離間した第3直線上で配列したものからなる第3画素群とを構成したアクティブマトリクス型表示装置の製造方法であって、非晶質シリコン層にレーザ光を線状ビー

50

ムとして照射するとともに前記線状ビームの照射位置を前記列と交差する走査方向へ前記画素の前記走査方向の長さよりも狭いピッチで段階的にずらすことにより前記多結晶シリコン薄膜トランジスタの多結晶シリコン層を形成する工程を含み、前記線状ビームが照射される領域の長手方向と前記列とを互いに平行とすることにより、前記第1乃至第3画素群のそれにおける前記多結晶シリコン薄膜トランジスタの移動度のばらつきを、各列における前記多結晶シリコン薄膜トランジスタの移動度のばらつきと比較してより小さくすることを特徴とするアクティブマトリクス型表示装置の製造方法を提供する。

#### 【0010】

なお、ここで、用語「線状ビーム」は、一般に使用されるように、平面に対して法線方向から放射したときに先の平面内の直線状或いは帯状の領域全体を同時に照射し得る光ビームを意味する。 10

#### 【0011】

複数の画素のそれぞれにおいて、表示素子はそれに流れる電流の大きさに応じて光学特性が変化する素子であってもよい。また、多結晶シリコン薄膜トランジスタは第1電源端子と第2電源端子との間で表示素子と直列に接続された駆動トランジスタであってもよい。この場合、複数の画素のそれぞれは、映像信号線と駆動トランジスタのゲートとの間に接続されるとともにそれらの間の導通／非導通を走査信号線から供給される走査信号に基づいて制御する画素スイッチと、駆動トランジスタのゲートと第1電源端子との間に接続されたキャパシタとをさらに備えていてもよい。 20

#### 【0013】

マトリクス状に配列した複数の画素が形成する各列において、第1画素群を構成した画素と第2画素群を構成した画素とはその列に平行な方向に交互に配列していてもよい。 20

#### 【発明の効果】

#### 【0014】

本発明によると、表示ムラが視認され難いアクティブマトリクス型表示装置及びその製造方法が提供される。 20

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様または類似の機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。 30

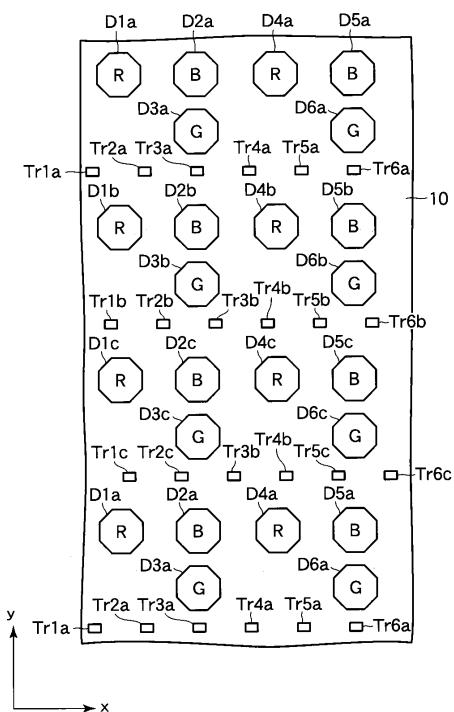

#### 【0016】

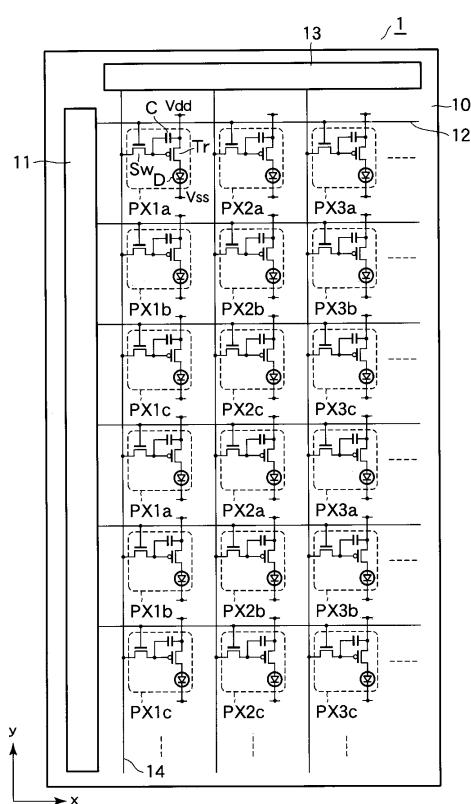

図1は、本発明の一態様に係るアクティブマトリクス型表示装置を概略的に示す平面図である。図1には、本態様に係るアクティブマトリクス型表示装置の一例として、有機EL表示装置1を描いている。 30

#### 【0017】

この有機EL表示装置1は、ガラス基板のような絶縁基板10を備えている。基板10の一主面上には、画素PXがマトリクス状に配置されている。基板10上には、さらに、走査信号線ドライバ11に接続された走査信号線12と、映像信号線ドライバ13に接続された映像信号線14とが互いに交差するように配置されている。 40

#### 【0018】

画素PXは、駆動制御素子である駆動トランジスタTrと、キャパシタCと、画素スイッチSwと、表示素子である有機EL素子Dとで構成されている。これらのうち、駆動トランジスタTrとキャパシタCと画素スイッチSwとは駆動回路を構成している。なお、ここでは、一例として、駆動用トランジスタTrはpチャネル多結晶シリコン薄膜トランジスタ(poly-Si TFT)であり、画素スイッチSwはnチャネルpoly-Si TFTであることをとする。また、ここでは、画素PX(3×M-2)a, PX(3×M-2)b, PX(3×M-2)cの発光色が赤色であり、画素PX(3×M-1)a, PX(3×M-1)b, PX(3×M-1)cの発光色が青色であり、画素PX(3×M)a, PX(3×M)b, PX(3×M)cの発光色が緑色であるとする。 50

## 【0019】

駆動トランジスタTrと有機EL素子Dとは、高電位の第1電源端子Vddと低電位の第2電源端子Vssとの間に直列に接続されている。画素スイッチSwは、映像信号線14と駆動トランジスタTrのゲートとの間に接続されており、その制御端子であるゲートは走査信号線12に接続されている。また、キャパシタCは、第1電源端子Vddと駆動トランジスタTrのゲートとの間に接続されている。

## 【0020】

本態様において、画素PXが形成する各列において、画素PXNaで構成された画素群と、画素PXNbで構成された画素群と、画素PXNcで構成された画素群とは、当該列に対する駆動トランジスタTrのx方向に関する相対位置が互いに異なっている。なお、x方向は、画素PXが形成する各列と交差する方向であって、後述する走査方向と等しい。また、y方向は、画素PXが形成する各列に平行な方向であって、後述する線状ビームが照射される領域の長手方向と等しい。

10

## 【0021】

次に、この有機EL表示装置1の製造方法について説明する。

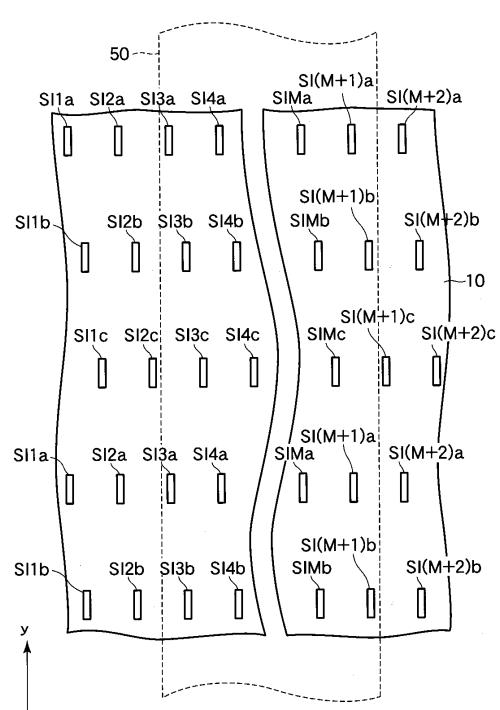

図2は、図1に示す表示装置の製造に利用可能な方法の一例を示す平面図である。図2において、参照符号SIは、基板10上に形成されたシリコン層のうち、駆動トランジスタTrのチャネル領域及びソース・ドレイン領域が形成される半導体層として使用される部分（以下、トランジスタ形成部という）を示している。また、参照符号50は、レーザアニールの際にシリコン層に照射するレーザ光である線状ビームを示している。

20

## 【0022】

なお、トランジスタ形成部SIに付した添え字は、図1に示す画素PXに付した添え字と対応している。また、図2において、線状ビーム50よりも右側に位置したシリコン層は非晶質シリコン層であり、線状ビーム50よりも左側に位置したシリコン層は結晶質シリコン層である。

## 【0023】

本態様では、レーザアニールに際し、図2に示すように、線状ビーム50の長手方向をy方向と平行とするとともに、基板10上で線状ビーム50をx方向に所定のピッチPで走査させる。すなわち、線状ビーム50を基板10に対してx方向にピッチPで相対移動させる。典型的には、線状ビーム50の位置はアニール装置内で固定し、ステージ上の基板10を線状ビーム50に対して連続的に移動させ、所定のタイミングで線状ビーム50をパルス照射する。

30

## 【0024】

なお、線状ビーム50を走査するピッチPは、画素PXのx方向の長さ、すなわち画素ピッチ、よりも狭くする。例えば、ピッチPは、画素ピッチの1/3程度とする。また、線状ビーム50のx方向の長さは、線状ビーム50を走査するピッチPよりも長くする。

## 【0025】

このような方法でレーザアニールを行うと、表示ムラが視認され難くなる。これについては、図3に示す構造と対比しながら説明する。

## 【0026】

40

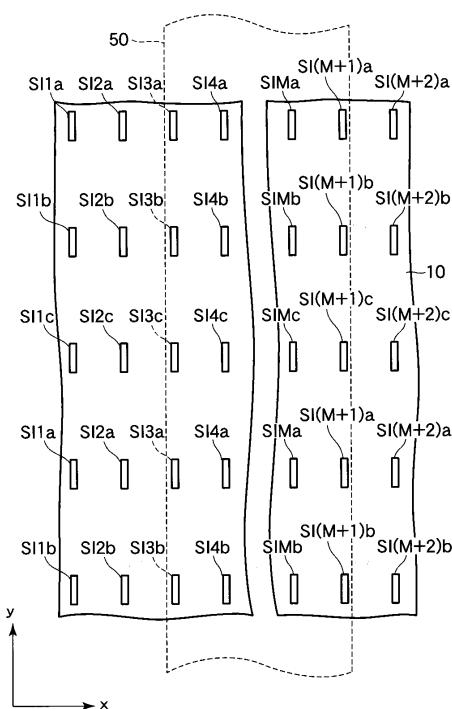

図3は、比較例に係るレーザアニール法を示す平面図である。

図3に示す構造では、トランジスタ形成部SINA, SINB, SINCは、y方向に一列に並んでいる。そのため、図3に示す方法では、1回のレーザショットで、y方向に並んだトランジスタ形成部SINA, SINB, SINCの全てが同時に線状ビーム50を照射されることとなる。

## 【0027】

ところで、本発明者の調査により、同一のレーザショットでシリコン層のレーザアニールを行ったトランジスタ間では、別々のレーザショットでシリコン層のレーザアニールを行ったトランジスタ間と比較して、移動度のばらつきが極めて小さいことが判明している。そのため、図3の方法により製造した有機EL表示装置1では、y方向に並んだ画素P

50

X間に於ける駆動トランジスタTrの移動度のばらつきは、x方向に並んだ画素PX間に於ける駆動トランジスタTrの移動度のばらつきに比べて小さくなる。

#### 【0028】

駆動トランジスタTrの移動度が設計値よりも小さいと、有機EL素子Dの輝度は、画素PXに供給する映像信号の大きさから期待される値よりも低くなる。他方、駆動トランジスタTrの移動度が設計値よりも大きいと、有機EL素子Dの輝度は、画素PXに供給する映像信号の大きさから期待される値よりも高くなる。

#### 【0029】

そのため、図3の方法によると、x方向に並んだ画素PX間では輝度がばらつき、y方向に並んだ画素PX間では輝度のばらつきは殆んど生じない。それゆえ、図3の方法により製造した有機EL表示装置1では、各画素PXの輝度のばらつきがy方向に隣接した画素PXによって補償されることなく、したがって、y方向に延在した筋状の表示ムラ、具体的には輝度ムラ、が視認され易い。

#### 【0030】

これに対し、図2の方法によると、x方向に並んだ画素PX間では輝度がばらつくのに加え、y方向に並んだ画素PXのうち画素PXNaからなる画素群と画素PXNbからなる画素群と画素PXNcからなる画素群との間で輝度がばらつく。このようなばらつきはランダムに生じるので、各画素PXの輝度のばらつきは、x方向及びy方向に隣接した画素PXにより補償される。したがって、本態様によると、表示ムラが視認され難くなる。

#### 【0031】

なお、図2の方法を採用した場合、得られる有機EL表示装置1には、画素PXNaからなる画素群、画素PXNbからなる画素群、及び画素PXNcからなる画素群のそれぞれにおける駆動トランジスタTrの移動度のばらつきが、それら画素PXNa乃至PXNcを含む列における駆動トランジスタTrの移動度のばらつきと比較してより小さいという特徴がある。

#### 【0032】

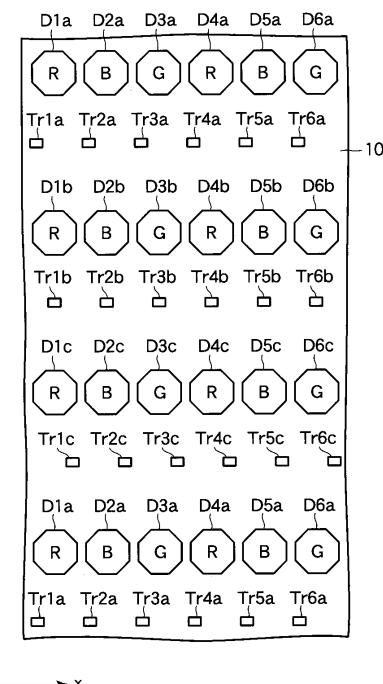

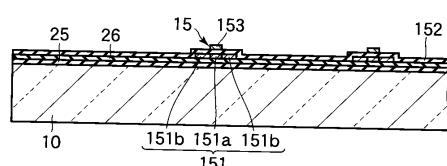

本態様において、有機EL素子Dには様々な配置が可能である。これについては、図4及び図5を参照しながら説明する。

#### 【0033】

図4は、図1の有機EL表示装置に採用可能な有機EL素子の配置の一例を概略的に示す平面図である。また、図5は、参考例に係る有機EL表示装置に採用可能な有機EL素子の配置の一例を概略的に示す平面図である。なお、図4及び図5において、有機EL素子D及び駆動トランジスタTrに付した添え字は、図1に示す画素PXに付した添え字と対応している。

#### 【0034】

図4及び図5に示す構造では、例えば、有機EL素子D(3×m-2)a、D(3×m-2)b、D(3×m-2)cの発光色は赤色であり、有機EL素子D(3×m-1)a、D(3×m-1)b、D(3×m-1)cの発光色は青色であり、有機EL素子D(3×m)a、D(3×m)b、D(3×m)cの発光色は緑色である。

#### 【0035】

図4に示す構造では、発光色が赤、青、緑色の有機EL素子Dは、x方向にこの順に繰り返し配列している。すなわち、それら有機EL素子Dはストライプ状に配列している。他方、図5に示す構造では、発光色が赤、青、緑色の有機EL素子Dは、L字型に配列している。このように、有機EL素子Dには様々な配置が可能である。

#### 【0036】

本態様では、上記の通り、画素PXがy方向に形成する各列を3つの画素群、すなわち、画素PXNaからなる画素群、画素PXNbからなる画素群、及び画素PXNcからなる画素群、で構成したが、各列を構成する画素群の数は3つ以上であれば特に制限はない。

#### 【0037】

10

20

30

40

50

また、本態様では、それら画素群間で駆動トランジスタ  $T_r$  の  $x$  方向に関する位置を異ならしめたが、それら画素群間で、画素  $P_X$  に含まれる他のトランジスタの  $x$  方向に関する位置を異ならしめてもよい。例えば、それら画素群間で、画素スイッチ  $S_w$  として使用するトランジスタの  $x$  方向に関する位置を異ならしめてもよい。或いは、画素  $P_X$  に他の回路構成を採用した場合には、それら画素群間で、画素  $P_X$  に含まれるさらに他のトランジスタの  $x$  方向に関する位置を異ならしめてもよい。但し、上述した効果は、第1電源端子  $V_{dd}$  と第2電源端子  $V_{ss}$ との間で有機EL素子  $D$  と直列に接続されたトランジスタの  $x$  方向に関する位置を先の画素群間で異ならしめた場合に最も顕著である。

#### 【0038】

さらに、本態様では、アクティブマトリクス表示装置として有機EL表示装置1を例示したが、上述した効果は他のアクティブマトリクス表示装置でも得ることができる。先の技術は、特に、表示素子としてそれに流れる電流の大きさに応じて光学特性が変化するものを使用したアクティブマトリクス表示装置に極めて有効である。10

#### 【実施例】

#### 【0039】

以下、本発明の実施例について説明する。

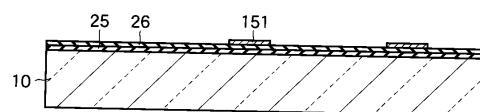

##### (実施例)

図6乃至図11は、図1に示す表示装置の製造に利用可能な方法の一例を示す断面図である。20

#### 【0040】

本例では、図1に示す有機EL表示装置1を、図6乃至図11を参照しながら以下に説明する方法により製造した。なお、この有機EL表示装置1には、トランジスタ形成部SIに図2の配置を採用するとともに、有機EL素子D及び駆動トランジスタ  $T_r$  に図4の配置を採用した。20

#### 【0041】

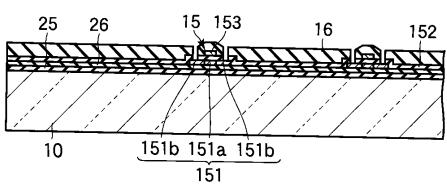

まず、ガラス基板10上に、アンダーコート層として、例えば、 $SiN_x$ 層25と $SiO_2$ 層26とを形成した後、その上に、例えば厚さ50nmの非晶質シリコン層を形成した。次いで、非晶質シリコン層を例えばXeClエキシマレーザを用いてレーザアニールすることにより、多結晶シリコン層とした。さらに、この多結晶シリコン層を図2に示すトランジスタ形成部SIに対応した部分が残留するようにパターニングすることにより、図6に示す形状の多結晶シリコン層151を形成した。30

#### 【0042】

なお、ここでは、 $x$ 方向に並んだ3つの画素  $P_X$  でトリプレットを構成し、このトリプレットの  $x$  方向の長さは  $198\mu m$  とした。すなわち、画素  $P_X$  の  $x$  方向の長さは  $66\mu m$  とした。また、レーザアニールに際しては、1回のレーザショットで線状ビーム50が照射される領域の走査方向( $x$ 方向)の長さは  $440\mu m$  とし、線状ビーム50は  $22\mu m$  のピッチで走査した。すなわち、1箇所当たりのレーザショット数を20回とした。さらに、トランジスタ形成部SINbはトランジスタ形成部SINAに対して  $x$  方向に  $22\mu m$  だけずらして配置し、トランジスタ形成部SINCはトランジスタ形成部SINAに対して  $x$  方向に  $44\mu m$  だけずらして配置した。40

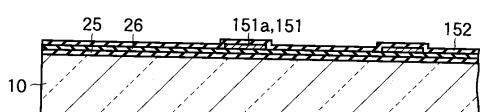

#### 【0043】

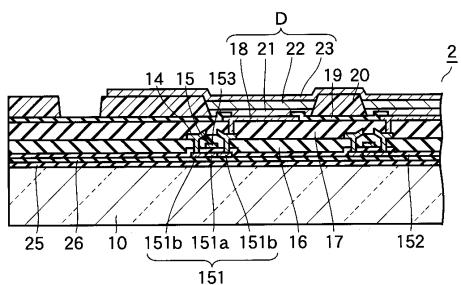

次に、図7に示すように、基板10の多結晶シリコン層151を形成した面に、ゲート絶縁膜152を形成した。続いて、イオンドーピング法により、多結晶シリコン層151内に $n^+$ 領域151aを形成した。

#### 【0044】

次いで、図8に示すように、ゲート絶縁膜152上にゲート電極153を形成した。さらに、このゲート電極153をマスクとして用いたイオンドーピング法により、多結晶シリコン層151内に $p^+$ 領域151bを形成した。このようにして、駆動トランジスタ  $T_r$  として $p$ チャネル $poly-Si TFT$ 15を作製した。なお、これと同時に、画素スイッチ  $S_w$  として用いられるトランジスタや走査信号線ドライバ11及び映像信号線ドラ50

イバ13内のトランジスタも作製した。また、ゲート電極153を形成する際、映像信号線14なども同時に形成した。

#### 【0045】

その後、図9に示すように、基板10のpチャネルpolycrystallineを形成した面に、厚さ700nmの層間絶縁膜16を形成した。次いで、層間絶縁膜16及びゲート絶縁膜152に貫通孔を形成した。

#### 【0046】

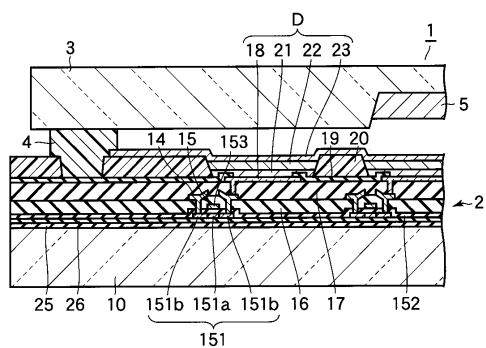

次に、図10に示すように、映像信号線14及びパッシベーション膜17を順次形成した。パッシベーション膜17に貫通孔を形成した後、陽極としてITO(Indium Tin Oxide)からなる透明電極18を形成した。次いで、透明電極18の中央部に対応した位置に開口を有する親水性層19を形成し、親水性層19上に隔壁20を形成した。その後、PEDOT(ポリエチレンジオキシチオフェン)を含有したバッファ層21及びルミネッセンス性有機化合物を含有した発光層22を順次形成した。さらに、発光層22上に陰極23を形成した。以上のようにして、アレイ基板2を完成した。

#### 【0047】

その後、図11に示すように、封止基板3であるガラス基板の一方の正面の周縁部に紫外線硬化型樹脂を塗布してシール層4を形成した。また、封止基板3のアレイ基板2との対向面に設けられた凹部に、シート状の乾燥剤5を貼り付けた。次いで、封止基板3とアレイ基板2とを、封止基板3のシール層4を設けた面とアレイ基板2の陰極23を設けた面とが対向するように乾燥室素ガスのような不活性ガス中で貼り合せた。さらに、紫外線照射によりシール層を硬化させることにより、図11に示す有機EL表示装置1を完成了。なお、ここでは、封止基板3を用いてアレイ基板2を封止したが、樹脂フィルムを貼り付けることによりアレイ基板2を封止してもよい。

#### 【0048】

以上のことにより得られた有機EL表示装置1を外部駆動回路及び電源と接続した。さらに、これをベゼルで支持するとともに、アレイ基板2の外側表面上に反射防止膜として円偏光板を設けた。この状態で表示特性を調べたところ、表示ムラが視認されることはなかった。

#### 【0049】

なお、この例では、有機EL表示装置1をアレイ基板2側から表示光を取り出す下面発光型としたが、封止基板3側から表示光を取り出す上面発光型としてもよい。この場合も、表示ムラが視認されるのを防止することができる。

#### 【0050】

##### (比較例)

トランジスタ形成部SINA乃至SINCのx方向に関する位置を互いに等しくしたこと以外は上記実施例で説明したのと同様の方法により有機EL表示装置1を作製した。すなわち、本例では、トランジスタ形成部SIに図3の配置を採用した。

この有機EL表示装置1の表示特性を調べたところ、y方向に延在した筋状の輝度ムラが視認された。

#### 【図面の簡単な説明】

#### 【0051】

【図1】本発明の一態様に係るアクティブマトリクス型表示装置を概略的に示す平面図。

【図2】図1に示す表示装置の製造に利用可能な方法の一例を示す平面図。

【図3】比較例に係るレーザアニール法を示す平面図。

【図4】図1の表示装置に採用可能な表示素子の配置の一例を概略的に示す平面図。

【図5】参考例に係る表示装置に採用可能な表示素子の配置の一例を概略的に示す平面図。

【図6】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

【図7】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

【図8】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

10

20

30

40

50

【図9】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

【図10】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

【図11】図1に示す表示装置の製造に利用可能な方法の一例を示す断面図。

【符号の説明】

【0052】

1 ... 表示装置、2 ... アレイ基板、3 ... 封止基板、4 ... シール層、5 ... 乾燥剤、10 ... 絶縁基板、11 ... 走査信号線ドライバ、12 ... 走査信号線、13 ... 映像信号線ドライバ、14 ... 映像信号線、15 ... poly-Si TFT、16 ... 層間絶縁膜、17 ... パッシベーション膜、18 ... 陽極、19 ... 親水性層、20 ... 隔壁、21 ... バッファ層、22 ... 発光層、23 ... 陰極、25 ... アンダーコート層、26 ... アンダーコート層、50 ... 線状ビーム、151a ... n<sup>+</sup>領域、153 ... ゲート電極、151b ... p<sup>+</sup>領域、PX ... 画素、Tr ... 駆動トランジスタ、C ... キャパシタ、Sw ... 画素スイッチ、D ... 表示素子、Vdd ... 第1電源端子、Vss ... 第2電源端子、SI ... トランジスタ形成部。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

| (51)Int.Cl.              | F I             |

|--------------------------|-----------------|

| H 0 5 B 33/12 (2006.01)  | H 0 5 B 33/12 B |

| H 0 1 L 51/50 (2006.01)  | H 0 5 B 33/14 A |

| G 0 2 F 1/1345 (2006.01) | G 0 2 F 1/1345  |

| G 0 2 F 1/1368 (2006.01) | G 0 2 F 1/1368  |

(72)発明者 後藤 康正

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

審査官 松岡 智也

(56)参考文献 特開平10-319386 (JP, A)

特開平07-302907 (JP, A)

特開平06-289431 (JP, A)

特開平10-319437 (JP, A)

特開平09-063950 (JP, A)

特開平09-321310 (JP, A)

特開2002-366057 (JP, A)

特開平09-260681 (JP, A)

特開平10-240168 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 F 9 / 0 0、9 / 3 0

G 0 2 F 1 / 1 3 4 3 - 1 / 1 3 4 5、

1 / 1 3 5 - 1 / 1 3 6 8、

H 0 1 L 2 1 / 3 3、2 9 / 7 8 6、5 1 / 5 0、

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8