(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2007-0119747

(43) 공개일자 2007년12월20일

(51) Int. Cl.

G06K 19/077 (2006.01) H05K 7/06 (2006.01)

(21) 출원번호 10-2007-7026127

(22) 출원일자 2007년11월09일

심사청구일자 없음

번역문제출일자 2007년11월09일

(86) 국제출원번호 PCT/US2006/013225

국제출원일자 2006년04월10일

(87) 국제공개번호 WO 2006/110616

국제공개일자 2006년10월19일

(30) 우선권주장

11/209,345 2005년08월22일 미국(US)

60/670,076 2005년04월11일 미국(US)

(71) 출원인

아베소, 임크.

미합중국 미네소타 55421, 프리들리, 슈트 411,

이스트 리버 로드 5155

(72) 발명자

웬나쓰, 토마스, 제이.

미국, 55316 미네소타, 챔플린, 오스보우 플레이

스 5117

퀸들렌, 스테펜, 에프.

미국, 27511 노스 캐롤리나, 캐리, 위스퍼우드 드

라이브 220

(뒷면에 계속)

(74) 대리인

장훈

전체 청구항 수 : 총 31 항

**(54) 인쇄된 소자들을 가진 적층 구조****(57) 요 약**

본 발명은 전자 구성요소들을 기준 처리들에 의해 쉽게 열 적층될 수 있는 전자 코어 구조로 통합한다. 이 구조는 디스플레이, 배터리 또는 다른 전원, 접적 회로들, 스위치들, 자기 스트라이프 애팔레이터, 안테나, 스마트 칩들 또는 다른 입력 디바이스들과 같은 다수의 원하는 전자 구성요소들을 포함할 수 있다. 이 구조는 층들을 브리징하고, 전자 구성요소 치수들의 변동을 보상하기 위해 적층된 버퍼층들을 포함한다. 이 구조는 또한 코어층 구조의 일부로서 배터리 패키징을 통합하고, 원하는 특성들을 부여하기 위해 전자 코어층들의 일부로서 인쇄된 전자 회로를 사용할 수 있다. 다양한 구성요소들이 이 구조에 통합될 수 있다.

**대표도**

(72) 발명자

심, 데이비드, 지.

미국, 55345 미네소타, 미네톤카, 애쉬크로프트 로

드 5363

맥도갈, 제임스, 피.

미국, 89012 네바다, 헨더슨, 체스트너트 럭지 써

클 202

---

## 특허청구의 범위

### 청구항 1

디스플레이 및 상기 디스플레이를 구동하는 연관된 전자장치들을 적층된 유닛으로 제공하기 위한 얇고 적층된 코어 구조에 있어서,

적층 가능한 재료의 베이스층 및 최상부층;

적어도 하나의 디스플레이 구성요소를 구동하기 위한 접적 회로 구성요소에 대한 접속 지점들을 갖고, 전원에 대한 접속을 위한 전기 트레이스들을 갖는 디스플레이 셀;

하나 이상의 표면들 상에 인쇄된 전기 트레이스들을 갖는 적어도 하나의 미리 형성된 구성요소 접속층으로서, 상기 디스플레이 셀에 동작 가능하게 전기적으로 접속되고 상기 베이스층과 상기 최상부층 사이에 고정되는 상기 적어도 하나의 미리 형성된 구성요소 접속층; 및

상기 베이스층과 상기 최상부층 사이에 구성된 버퍼층으로서, 상기 베이스층과 상기 최상부층 사이의 구성요소들 간의 두께차들을 보상하고 상기 적층된 코어 구조에 대한 원하는 전체 두께를 달성하도록 허용하는 형성 가능한 재료로 이루어지는, 상기 버퍼층을 포함하는, 얇고 적층된 코어 구조.

### 청구항 2

제 1 항에 있어서,

상기 적어도 하나의 디스플레이 구성요소는 상기 접적 회로 구성요소에 동작 가능하게 전기적으로 접속되는 복수의 픽셀들을 인쇄함으로써 형성되는, 얇고 적층된 코어 구조.

### 청구항 3

제 2 항에 있어서,

상기 복수의 픽셀들은 디스플레이 수신 접속 지점들에 짹(matingly)으로 접속되는, 얇고 적층된 코어 구조.

### 청구항 4

제 1 항에 있어서,

상기 베이스층은 인접한 하부 커버 표면에 대한 적층에 적당한, 얇고 적층된 코어 구조.

### 청구항 5

제 1 항에 있어서,

상기 최상부층은 인접한 상부 커버 표면에 대한 적층에 적당한, 얇고 적층된 코어 구조.

### 청구항 6

제 1 항에 있어서,

침 접촉 플레이트가 상기 코어 구조에 적어도 부분적으로 탑재되고, 상기 적층된 구조의 내부의 전기 트레이스들은 상기 침 플레이트로부터 측면으로 배치되는 상기 접적 회로 구성요소에 상기 침 플레이트를 동작 가능하게 전기적으로 접속하는, 얇고 적층된 코어 구조.

### 청구항 7

제 6 항에 있어서,

상기 침 접촉 플레이트는 스마트 카드용 접촉 플레이트이며, 상기 접적 회로 구성요소는 스마트 카드 기능들을 수행하도록 구성되는, 얇고 적층된 코어 구조.

### 청구항 8

제 1 항에 있어서,

상기 구성요소 접속층은 구성요소들을 수신하고 상기 베이스층과 상기 최상부층 사이의 구성요소들 간의 두께차들을 보상하도록 조력하기 위하여 간극들(apertures)로 미리 형성되는, 얇고 적층된 코어 구조.

### 청구항 9

제 1 항에 있어서,

상기 구성요소 접속층은 구성요소들을 수신하고 상기 베이스층과 상기 최상부층 사이의 구성요소들 간의 두께차들을 보상하도록 조력하기 위하여 간극들로 미리 형성되고, 상기 베퍼층은 상기 간극과 연관된 공동들(cavities)을 채우도록 형성 가능한, 얇고 적층된 코어 구조.

### 청구항 10

제 1 항에 있어서,

상기 구성요소 접속층은 상부 및 하부 표면들 상에 인쇄된 전기 트레이스들을 갖는, 얇고 적층된 코어 구조.

### 청구항 11

디스플레이를 구비한 얇고 적층된 코어 구조를 제조하는 방법에 있어서,

적층에 적당한 베이스층을 제공하는 단계;

전자크롬 잉크의 대응하는 층으로 적어도 하나의 퍽셀을 인쇄함으로써 형성된 적어도 하나의 디스플레이 구성요소를 구동하는 부착된 접적 회로 구성요소, 및 상기 적어도 하나의 퍽셀 및 상기 접적 회로 구성요소를 전기적으로 동작 가능하게 접속하는 트레이스들을 디스플레이 셀에 제공하는 단계;

상기 접적 회로 구성요소에 대한 전기적으로 동작 가능한 접속을 위한 전원 구성요소를 제공하는 단계;

상기 디스플레이 셀에 인접하게 개재되고, 상기 접적 회로 구성요소, 상기 전원 구성요소 및 상기 디스플레이 셀 중 하나 이상에 동작 가능하게 접속되는 인쇄된 전기 구성요소들을 가진 적어도 하나의 표면들을 갖는 적어도 하나의 커버층을 제공하는 단계; 및

상기 선행하는 소자들 사이에 적어도 하나의 베퍼층을 개재함으로써 상기 베이스층, 상기 디스플레이 셀, 상기 전원 구성요소 및 상기 커버층을 적층된 유닛으로 조합하는 단계로서, 상기 베퍼층은 상기 베이스층과 상기 커버층 사이의 상기 구성요소들의 두께의 치수 변동들을 보상하고, 상기 적층된 유닛에 대한 원하는 총 수직 치수를 달성하기에 충분한 그 자신의 수직 치수의 두께의 범위를 제공하도록 형성 가능하고 차동적으로 적용되는, 상기 조합 단계를 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 12

제 11 항에 있어서,

상기 적어도 하나의 퍽셀을 인쇄하는 단계는 상기 접적 회로 구성요소에 동작 가능하게 전기적으로 접속된 복수의 퍽셀들을 인쇄하는 단계를 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 13

제 12 항에 있어서,

상기 적어도 하나의 퍽셀을 인쇄하는 단계는 상기 접적 회로 구성요소에 동작 가능하게 전기적으로 접속된 복수의 퍽셀들을 인쇄하는 단계를 포함하고, 그에 의해 상기 복수의 퍽셀들은 디스플레이 수신 접속 지점들에 찍으로 접속되는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 14

제 11 항에 있어서,

상기 코어 구조에 적어도 부분적으로 탑재된 칩 접촉 플레이트를 제공하는 단계를 더 포함하며, 상기 적층된 구조의 내부의 전기 트레이스들은 상기 칩 플레이트로부터 측면으로 배치된 위치에 있는 상기 접적 회로 구성요소

에 상기 칩 플레이트를 동작 가능하게 전기적으로 접속하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 15

제 14 항에 있어서,

상기 칩 접촉 플레이트는 스마트 카드용 접촉 플레이트이며, 스마트 카드 기능들을 수행하기 위하여 상기 접착 회로 구성요소를 구성하는 단계를 더 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 16

제 1 항에 있어서,

상기 커버층을 제공하는 단계는 구성요소들을 수신하고 상기 베이스층과 상기 커버층 사이의 구성요소들 간의 두께차들을 보상하도록 조력하기 위하여 간극들로 미리 형성된 층을 제공하는 단계를 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 17

제 16 항에 있어서,

상기 커버층을 제공하는 단계는 구성요소들을 수신하고 상기 베이스층과 상기 커버층 사이의 구성요소들 간의 두께차들을 보상하도록 조력하기 위하여 간극들로 미리 형성된 층을 제공하는 단계를 포함하고, 상기 베이스층은 상기 간극과 연관된 공동들을 채우도록 형성 가능한, 얇고 적층된 코어 구조 제조 방법.

### 청구항 18

제 17 항에 있어서,

상기 간극들로 미리 형성된 층은 상부 및 하부 표면들 상에 인쇄된 전기 트레이스들을 갖는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 19

디스플레이를 구비한 얇고 적층된 코어 구조를 제조하는 방법에 있어서,

적층에 적당한 베이스층을 제공하는 단계;

전자크롬 잉크의 대응하는 층으로 복수의 광센들을 인쇄함으로써 상기 디스플레이를 구동하는 부착된 접착 회로 구성요소, 및 상기 광센들과 상기 접착 회로 구성요소를 전기적으로 동작 가능하게 접속하는 트레이스들을 디스플레이 셀에 제공하는 단계;

상기 접착 회로에 전력을 전달하도록 전기적으로 동작 가능하게 접속된 전원 구성요소를 제공하는 단계;

상기 접착 회로 구성요소, 상기 전원 구성요소 및 상기 디스플레이 셀 중 하나 이상에 동작 가능하게 전기적으로 접속되는 전기 구성요소들을 상기 커버층의 하나 이상의 외부 또는 내부 표면들 상에 인쇄함으로써 상기 디스플레이 셀에 인접하게 개재된 적어도 하나의 커버층을 제공하는 단계; 및

상기 선행하는 소자들 사이에 적어도 하나의 베이스층을 개재함으로써 상기 베이스층, 상기 디스플레이 셀, 상기 전원 구성요소 및 상기 커버층을 적층된 유닛으로 조합하는 단계로서, 상기 베이스층은 상기 디스플레이 셀, 및 상기 베이스층과 상기 커버층의 외부 표면 사이에 개재된 다른 구성요소들의 두께의 차수 변동들을 보상하고 상기 적층된 유닛에 대한 원하는 총 수직 차수를 달성하기에 충분한 그 자신의 수직 차수의 두께의 범위를 제공하도록 형성 가능하고 적층되는, 상기 조합 단계를 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 20

제 19 항에 있어서,

상기 적어도 하나의 베이스층은 인쇄 기술에 의해 이용되는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 21

제 19 항에 있어서,

상기 베피충은 공동들을 채우고, 상기 베피충의 두께가 상기 치수 변동들을 보상함에 따라, 상기 구조의 균일한 두께로의 수평화를 허용하기 위해 적층시 흐름 가능하게 되는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 22

제 19 항에 있어서,

다중 베피충들이 인쇄되고 흐르는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 23

제 19 항에 있어서,

원하는 치수화를 달성하기 위하여 상기 베피충 재료의 적용 후에 닌 롤러들(nip rollers)이 사용되는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 24

제 19 항에 있어서,

상기 둘 이상의 외부 또는 내부 표면들 상의 전기 구성요소들의 인쇄는 안테나들, 저항기들 및 커패시터들을 포함하는 상기 원하는 구성요소들을 형성하기 위하여 다른 인쇄된 충들과 결합될 수 있는 도전성 트레이스들 또는 저항성 또는 유전성 재료들의 인쇄를 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 25

제 19 항에 있어서,

애노드들, 캐소드들, 전류 콜렉터들 및 전해질 부피를 포함하는 충들을 이용하는 인쇄 기술들을 사용함으로써 배터리 구성요소를 형성하는 단계를 더 포함하는, 얇고 적층된 코어 구조 제조 방법.

### 청구항 26

정보 처리를 위한 하나 이상의 전자 구성요소들을 적층된 유닛에 제공하기 위한 얇고 적층된 코어 구조에 있어서,

적층 가능한 재료의 베이스충 및 최상부충;

접속 지점들을 가지고 전원 구성요소에 대한 접속을 위한 전기 트레이스들을 갖는 적어도 하나의 전자 구성요소;

하나 이상의 표면들 상에 인쇄된 전기 트레이스들을 가진 적어도 하나의 미리 형성된 구성요소 접속충으로서, 상기 적어도 하나의 전자 구성요소에 동작 가능하게 전기적으로 접속되고 상기 베이스충과 상기 최상부충 사이에 고정되는 상기 적어도 하나의 미리 형성된 구성요소 접속충; 및

상기 베이스충과 상기 최상부충 사이에 구성된 베피충으로서, 상기 베이스충과 상기 최상부충 사이의 구성요소들 간의 두께차들을 보상하고 상기 적층된 코어 구조에 대한 원하는 전체 두께를 달성하도록 허용하는 형성 가능한 재료로 이루어지는, 상기 베피충을 포함하는, 얇고 적층된 코어 구조.

### 청구항 27

제 26 항에 있어서,

상기 적어도 하나의 전자 구성요소는 집적 회로 구성요소인, 얇고 적층된 코어 구조.

### 청구항 28

제 26 항에 있어서,

상기 적어도 하나의 전자 구성요소는 자기 스트라이프 에뮬레이터인, 얇고 적층된 코어 구조.

## 청구항 29

제 26 항에 있어서,

상기 적어도 하나의 전자 구성요소는 생체측정 센서인, 핵고 적층된 코어 구조.

## 청구항 30

제 26 항에 있어서,

칩 접촉 플레이트가 상기 코어 구조에 적어도 부분적으로 탑재되고, 상기 적층된 구조의 내부의 전기 트레이스들은 상기 칩 플레이트로부터 측면으로 배치되는 접적 회로 구성요소에 상기 칩 플레이트를 동작 가능하게 전기적으로 접속하는, 핵고 적층된 코어 구조.

## 청구항 31

제 30 항에 있어서,

상기 칩 접촉 플레이트는 스마트 카드용 접촉 플레이트이고, 상기 접적 회로 구성요소는 스마트 카드 기능들을 수행하도록 구성되는, 핵고 적층된 코어 구조.

## 명세서

### 기술 분야

<1> 관련 출원에 대한 상호 참조

<2> 본 출원은 2005년 4월 11일에 출원된 미국 가 출원 제60/670,076호의 이권을 주장한다.

<3> 본 발명은 내장된 전자 기능을 가진 적층 구조, 예를 들면 디스플레이 및 디스플레이를 구동하기 위한 연관된 전자장치에 관한 것이다. 디스플레이 및/또는 상기 구조의 다른 기능적 소자들은 인쇄 처리들에 의해 형성된다.

### 배경 기술

<4> 플라스틱 적층된 카드 산업은 신용 카드들, 식별 카드들, 로열티 카드들 및 정보를 포함하는 다른 정액 토큰들(flat tokens)을 생성하기 위해 열 적층(hot lamination)의 처리에 의존해왔다. 이러한 처리는 불투명도, 그래픽스 및 보호층들과 같은 다양한 기능들을 갖는 다양한 플라스틱 시트들을 완성된 스택으로 적층하는 것으로 이루어진다. 층들은 불투명하거나 투명할 수 있고, 자기 스트라이프들과 같은 기능적 소자들을 포함할 수 있다. 원하는 층들이 조립되었으면, 조립은 연속 구조를 형성하기 위해 다양한 층들을 함께 용해하도록 가열 및 압력을 받는다. 대부분의 지갑들 및 돈주머니들이 보여주는 바와 같이, 다양한 요구들을 충족하기 위하여 수억 만개의 카드들이 생산되었다. 많은 상황들에서, 카드는 별도의 요금 없이 제공되며, 따라서 제공자들은 비용을 의식하고 있다.

<5> 통상적인 조립은 중심층, 통상적으로 미리 인쇄되는 전후 그래픽층, 광택을 제공하고 인쇄된 그래픽들을 보호하는 자기스트립 및 투명 보호층들로 이루어진다. 흔히, 홀로그램들과 같은 보안 특징들이 이 구조에 포함된다. 스마트 카드들은 리세스(recess)를 압연(mill)하고 접적된 칩 플레이트 및 접적 회로를 탑재하여 적층 후에 마이크로프로세서 및 칩 플레이트를 카드에 부가함으로써 생산된다. IC는, IC가 무접촉 모드로 RF를 통해 통신하도록 허용하기를 원한다면, 안테나에 부착될 수 있다. 기존의 열 적층 카드들에 대한 바람직한 재료들은 폴리비닐염화물(PVC), 폴리프로필렌, 폴리카보네이트, 폴리에스테르, 및 대략 110°C 내지 190°C의 범위의 용해 온도를 가진 다른 적당한 플라스틱으로 이루어진 층들을 포함한다.

<6> 카드들 등을 생산하는데 사용되는 열 적층 처리는 전체적으로 대량의 인스톨된 카드 생산력을 나타낸다. 접착 결합에 의존하는 냉 적층과 같은 다른 처리들이 개발되었지만 제한적으로 구현되었다. 임의의 새로운 카드 구조들은 기존의 열 적층 처리들과 호환 가능하다면 더욱 유용하다.

<7> 완성된 적층된 카드의 원하는 속성들은 높은 광택, 일그러지지 않은 그래픽들 및 균일하고 평坦한 표면들을 포함한다. 그 외에도, 금융 거래 및 식별 카드들에 대해, 그 구조는 ISO 표준들을 충족해야 한다. 카드들에 대한 ISO 표준들은 온도 및 습도 저항, 유연성, 적층 세기, 평坦 및 물리적 치수들과 같은 성능 요건들을 규정한다. 식별 카드에 대한 응용 범위는 카드의 물리적 특성들을 결정할 것이다. 카드들의 물리적 특성들(ID-1, ID-2 및

ID-3)은 ISO/IEC 7810:2003 식별 카드들-물리적 특성들에 기술되어 있다. 자기 스트라이프들, 접적 회로들, 또는 광 메모리를 가진 카드들에 대한 테스트들은 ISO/IEC 10373-1 식별 카드들-테스트 방법들에 기술되어 있다. 접적 회로 카드들의 접촉들에 대한 요건들은 ISO/IEC 7816-1 식별 카드들- 접촉들을 가진 접적 회로 카드들에 의해 커버된다. 양각된 문자들에 대한 명세는 ISO/IEC 7811-1:2002 식별 카드들-기록 기술-파트 1: 양각에서 제 공된다. ISO 7813은 금융 거래 카드들에 의해 충족되어야 하는 요건들을 기재한다. 반면, ISO/IEC 7501은 여권 들 및 비자들과 같은 기계 판독 가능한 여행 서류들을 커버한다. 또 다른 형태의 식별 카드는 얇은 연성 카드 (TFC: thin flexible card)이며, 이것은 ISO/IEC 15457에 의해 커버된다. 부가의 관련 표준들은 부록 A에서 식 별된다. 모든 이들 표준들은 본 명세서에 참조로서 포함된다.

- <8> 접적 회로들(IC들), 안테나들, 배터리들, 디스플레이들, 스위치들 및 다른 회로와 같은 열 적층에 앞서 전자 구 성요소들을 통합하면 열 적층 처리가 실행될 때 상당한 어려움이 있다. 주요 어려움은 상이한 구성요소들의 다 양한 높이들 및 이용된 재료들의 다양한 열 전달 특성들로부터 유발된다. 이들이 적당히 처리되지 않으면, 적층 될 층들에서의 적소의 전자 구성요소들로 열 적층 처리를 수행하는 것은 표면 결함들, 수용할 수 없는 휘어짐 (warping) 또는 내부 구성요소들에 대한 손상을 유발할 것이다.

- <9> RFID 안테나들 및 그 칩들은 열 적층된 카드들에 미리 통합되었다. 구리 배선, 에칭된 금속 또는 인쇄된 은인, 안테나는 통상적으로 작은 IC에 접속되고, 작은 IC는 상감(inlay)으로서 제공되고 개별 층으로서 구조에 끼워진다. 열 적층 처리는 IC가 작은 크기로 제한될 수 있고 안테나가 얇게 유지될 수 있기 때문에 주로 RFID에 대한 수용 가능한 결과들을 산출한다. 그러나, 더욱 복잡한 구조들은 구성요소들의 수 및 크기와 비주얼 및 ISO 품질 표준들을 충족해야 할 요구로 인해, 수용할 수 있는 결과들을 산출하는 것을 더욱 어렵게 한다.

- <10> 전자 구성요소들을 카드들에 통합하기 위한 다른 접근방식들은 압연과 같은 기계적 수단을 통해 공동들 (cavities)의 형성을 수반한다. 이러한 한 접근방식에서, 카드 코어는 전자 구성요소들을 수신하는 공동을 생성하도록 압연된다. 구성요소들의 배치 후에, 구조를 수평화하도록 압연된 영역에 용기에 든 액체가 첨가될 수 있다. 이 접근방식은 비교적 느리고, 간단한 적층 방식에 비해 비용 효율적이며 대량의 제조 처리를 유발하지 않는다.

- <11> 더욱 정교해진 전자장치들을 카드 구조들에 통합하려는 욕구를 처리하기 위한 다양한 접근방식들이 제안되어 왔다. 독일 참고문헌들, Patentschrift DE19923138 C1 및 Offenlegungsschrift DE 10219306 A1은, 느슨한 막들 (loose films)을 활용하여 전자 구성요소들을 포함하기 위한 분리된 구조가 만들어지며, 느슨한 막들은 그 후에 층들을 용해하기 위해 열 적층되는, 접근방식을 교시하고 있다. 이 접근방식은 미가공 재료들의 고유한 변동성 으로 인해 대량으로 구현하기 어렵고, 적층을 넘어서 원하는 결과들을 달성하기 위해 제조 처리에서 부가적인 단계들을 요구한다. 전자 구성요소들을 탑재하고 후속적으로 개별 층들을 부가하는 분리된 구조의 사용은 전자 구성요소들을 비용 효과적으로 통합하기 위한 재생산 가능한 수단을 적절히 제공하지 않는다.

- <12> 종래 기술은 구성요소들의 두께와 정확히 매칭할 수 없는 특정 두께들을 가진 막들의 사용을 요구한다. 이러한 문제를 회피하기 위하여, 제조업자는 이용 가능한 막들을 매칭하기 위한 매우 특정한 구성요소의 두께들을 요구 한다. 구성요소들 및 막들 모두의 제조 변동은 흔히, 잘못 매칭된 높이들로 인해 저급한 결과들을 유발할 것이다. 최종적으로, 이러한 접근방식은 개별 구성요소 및 막 모두의 변동을 보상하도록 시도하지만, 다수의 구성요소들이 적층된 구조에 사용될 때 도입되는 증가된 변동을 처리하지는 않는다. 제조 처리 자체가 고려해야 할 배 치 및 다이 절단들의 허용오차에 대한 요구를 도입한다.

- <13> 특정한 ISO 표준들 중 하나의 핵심 양태는 전체 카드에 대한 특정한 두께를 요구한다. ISO 표준들은 카드에 대해  $0.030 \pm 0.002$  인치의 전체 두께를 지정한다. 카드들이 통상적으로 각각 0.005인치인 2개의 그래픽스 층들과, 통상적으로 0.002인치인 투명한 보호층을 요구하기 때문에, 이것은 기능적 전자 구성요소들과 전자 코 어층들을 통합하기에 이용 가능한 총 0.016 내지 0.020인치를 남겨둔다.

- <14> 이러한 요건은 배터리가 카드에 통합되어야 하는 경우에 특별한 도전들이 있다. 현재 미리 패키징된 배터리 구 성들은 통상적으로 0.012 내지 0.016인치의 두께이고, 이것은 배터리에 쉽게 삽입되기 위해 남아있는 충분한 두께를 남겨두지 않고, 구성요소들을 숨기기에 적당한 불투명도를 제공한다. 부가적으로, 현재 배터리 패키징 기 술들은 적층 처리 동안 고려해야 할 매우 가변적인 패키지 치수들을 유발한다.

- <15> 유연성을 지정하는 ISO 표준들은 또한, 전자 구성요소들을 카드에 통합하는데 관련된 특별한 도전들이 있다. 회로 접적도는 연성 제품을 생산할 때 중요한 고려사항이다. 적층 처리는 다양한 구성요소들에 대한 압력을 최 소화하는 구조를 생산해야 한다. IC들, 안테나들, 스위치들, 배터리들, 자기 스트라이프 애뮬레이터들 및 디스

플레이들과 같은 다양한 전자 구성요소들이 카드에 포함될 수 있다. 각각의 구성요소는 상이한 두께, 크기 및 유연성을 가질 수 있지만, 카드에 패키징되어야 하고, 전자 회로들의 전기적 세기를 유지하면서 원하는 전체 카드 유연성을 유발해야 한다.

<16> 특정 카드들의 전자 패키지의 일부로서 디스플레이를 통합하는 것이 매우 바람직하다. 종래의 디스플레이 기술들은 ISO 순응 카드로의 통합에는 적당하지 않다. 종래 기술의 디스플레이들에는 다양한 제한들이 내재되어 있다. 성공적으로 디스플레이를 집적화하기 위해, 양호한 디스플레이의 연성이고, 배터리 요건들을 최소화하기 위해 저전력을 사용하고, 요구된 전자 구성요소들의 수를 최소화하기 위해 3V 미만에서 동작하고, 현재 처리들을 사용하여 열 적층될 수 있다.

<17> 디스플레이를 포함할 수 있는 연관된 전자 구성요소들을 가진 전자 코어 구조로서, 열 적층될 수 있고, 금융 거래 및/또는 식별 카드들에 대한 ISO 표준을 충족하는 상기 전자 코어 구조에 대한 요구가 있다. 특히, 맞춤화된 최종 그래픽 층들을 적용하여 고객들에게 전달하기 위한 카드들을 생산하는 당사자는 고객의 요구들을 충족시키기 위한 기능들을 제공하는 전자 코어 구조를 요구한다.

### 발명의 상세한 설명

<18> 본 발명은 다양한 전자 구성요소들을 포함하는 적층된 유닛을 제공하기 위한 얇은 적층 구조를 포함한다. 본 발명은, 다양한 금융 카드 및 다른 응용들의 특정한 전자 기능을 제공하고, 요구된 구조 세기를 가지고, 표준들 및/또는 사용자 요건들에 의해 지정된 바와 같이, 치수 요건들, 유연성, 및 특정한 응용의 다른 물리적 요건과 일관되게 남아 있으면서 완성층들을 적용하도록 허용하는 전자 코어 구조를 효율적으로 생성하는데 사용될 수 있다. 그 외에도, 적층된 구조의 모든 소자들 및 구성요소들이 일반적으로 종래의 인쇄 라인에 인쇄될 수 있거나 인쇄 라인에 쉽게 부가될 수 있기 때문에, 그 구조는 효율적으로, 신속하고 여유있게 생산될 수 있다.

<19> 이 구조는 인접한 하부 커버 표면들에 적층하는데 적당한 연성 베이스 시트 및 인접한 상부 커버 표면에 적층하는데 적당한 연성 최상부 시트를 포함한다. 삽입된 전자 구성요소들은 연성 베이스 시트 및 최상부 시트의 사이에 적층된다. 다양한 성분들은, 스위치들, 자기 스트라이프 에뮬레이터, 안테나, 디스플레이들, 스마트 카드 칩들 또는 다른 입력 또는 데이터 처리 디바이스들과 같이 2개의 시트들 사이에 포함될 수 있다.

<20> 하나의 비제한적인 실시예에서, 전자 코어 구조는, 디스플레이를 구동하는 접적 회로에 대한 접속 지점들을 갖고 이러한 접속 지점들로부터 전원으로 이끄는 전기 트레이스들을 갖는 디스플레이 셀을 구비한다. 디스플레이는 디스플레이 수신 접속 지점들에 짹으로(matingly) 접속되거나 접적 회로 구동기에 동작 가능하게 접속된 복수의 핀들을 인쇄함으로써 형성될 수 있다. 또한, 2개 이상의 표면들을 갖고 하나 이상의 표면들 상에 인쇄된 전기 트레이스들을 갖는 적어도 하나의 미리 형성된 구성요소 접속 시트는 디스플레이 셀에 동작 가능하게 접속되고 베이스 시트와 최상부 시트 사이에 고정된다. 베퍼층은 베이스 시트와 최상부 시트 사이에 배치되고, 디스플레이 셀의 구성요소들 내에서 구성요소들 간의 두께차들 및 높이 변동들을 보상하고 적층 구조에 대한 원하는 전체 두께가 재생 가능한 방식으로 달성되도록 허용하는 형성 가능한 재료로 이루어진다.

<21> 본 발명은 또한, 연성 베이스 시트를 제공하고, 전자크롬 잉크의 대응하는 층 및 전극으로 복수의 핀들을 인쇄함으로써 형성되는 디스플레이를 구동하는 부착된 접적 회로, 및 접적 회로 및 핀들을 전기적으로 동작 가능하게 접속하는 트레이스들을 디스플레이 셀에 제공함으로써 디스플레이 또는 다른 전자 구성요소들을 가진 얇고 적층된 구조를 제조하는 방법을 더 포함한다. 상기 방법은 또한, 접적 회로에 전기적으로 동작 가능하게 접속된 전원을 제공하는 단계와, 디스플레이 셀에 인접하게 개재되고 접적 회로, 전원 및 디스플레이 중 하나 이상에 동작 가능하게 접속된 인쇄된 전기 구성요소들을 가진 하나 이상의 외부 또는 내부 표면들을 갖는 적어도 하나의 커버층을 제공하는 단계를 포함한다. 베이스 시트, 전자 구성요소들, 전원 및 커버층은 앞선 소자들 사이에 적어도 하나의 베퍼층을 제공하는 단계를 포함한다. 베퍼층은 전자 구성요소들의 치수들의 치수 변동들을 보상하고, 적층된 유닛에 대한 원하는 총 수직 치수를 달성하기에 적당한 그 자신의 수직 치수들의 범위를 제공하도록 형성된다.

<22> 또 다른 실시예에서, 본 발명은 연성 베이스 시트를 제공하고, 전자크롬 잉크의 대응하는 층 및 전극으로 복수의 핀들을 인쇄함으로써 디스플레이를 구동하는 부착된 접적 회로, 및 접적 회로 및 핀들을 전기적으로 동작 가능하게 접속하는 트레이스들을 디스플레이 셀에 제공함으로써 전자 구성요소들을 가진 얇고 적층된 구조를 제조하는 방법을 포함한다. 이 방법은 또한, 접적 회로에 전기적으로 동작 가능하게 접속된 전원을 제공하는 단계와, 접적 회로, 전원 및 디스플레이 중 하나 이상에 동작 가능하게 접속된 전기 구성요소들을 하나 이상의 외부 또는 내부 표면들 상에 인쇄함으로써 디스플레이 셀에 인접하게 개재된 적어도 하나의 커버층을 제공하는 단

계를 포함한다. 베이스 시트, 디스플레이 셀, 전원 및 커버층은 앞선 소자들 사이에 적어도 하나의 버퍼층을 개재함으로써 적층된 유닛으로 조합된다. 버퍼층은 디스플레이 셀, 전원 및 다른 전자 구성요소들의 두께의 치수변동들을 보상하고, 적층된 유닛에 대한 원하는 총 수직 치수를 달성하기에 적당한 그 자신의 수직 치수들에서의 두께의 범위를 제공하도록 형성 및 적층된다.

<23> 카드에 또한 사용될 수 있는 본 발명의 또 다른 실시예에서, 적층된 구조에 의해 제공된 상호접속 회로는 구조에 존재하는 IC들의 수를 최소화하도록 구현된다. 예를 들면, 기존의 스마트 카드들은 카드 구조 외부의 판독기구조와 통신을 요구하며, 접촉 칩 플레이트를 통해 또는 무접촉 안테나를 통해 달성된다. 종래의 스마트 카드 IC는 칩 플레이트 상에 위치되며 판독기와의 통신 프로토콜을 제공하기 위한 소프트웨어를 포함하고, 암호 및 저장된 값 계산들과 같은 기능들을 수행한다. 디스플레이들 또는 자기 스트라이프 에뮬레이터들과 같은 많은 전자 구성요소들은 그 기능들을 제어하기 위한 IC를 요구한다. 본 발명은 모든 필요한 제어, 통신 및 데이터 조작기능들을 수행하기 위한 하나의 IC 상에 모든 구성요소들의 조합을 허용한다. IC, 안테나 또는 에뮬레이터 없이 표준화된 접촉들을 제공하는 칩 플레이트를 탑재하고 적층된 구조의 상호 접속 회로를 그 구조의 어디에서나 IC에 상호접속하는 것을 제공함으로써 통신이 달성된다.

<24> 버퍼층은 액체 인쇄 기술에 의해 이용되며, 치수 변동들을 보상하기 위하여 버퍼층 흐름에 따라 보이드들(voids)을 채우고 구조를 균일한 원하는 두께로 수평화하기 위해 적층 동안 유동적이다. 버퍼층이 이용되고 적당한 두께가 설정된 후에, 버퍼 재료들은 처리 및 최종 적층 동안 다양한 구성요소들을 적소에 유지하도록 경화된다. 하나 이상의 버퍼층들이 사용될 수 있다. 닌 롤러들(nip rollers)은 원하는 치수화를 달성하기 위한 임의의 인쇄 단계 및/또는 버퍼층 재료의 적용 후에 사용될 수 있다. 둘 이상의 외부 또는 내부 표면들 상의 전자 구성요소들의 인쇄는 도전성 트레이스들 또는 저항성 또는 유전성 재료들을 인쇄하는 단계를 포함할 수 있고, 이들은 안테나들, 커패시터들, 디스플레이들 또는 저항기들을 포함하는 원하는 구성요소들을 형성하기 위해 다른 인쇄된 층들과 결합될 수 있다. 배터리는 또한 애노드들, 캐소드들, 전류 콜렉터들 및 전해질을 포함하는 배터리 재료의 층들을 이용하기 위해 인쇄 기술들을 사용함으로써 형성될 수 있다. 배터리층은 특히 열 적층 처리동안 코어층들로서 이용되는 플라스틱들과 호환 가능해야 한다.

<25> 전자 코어 구조 재료들은 인쇄 기술들이 배터리를 형성하기 위해 이용될 때, 배터리 패키징을 형성할 수 있다. 버퍼층은 또한 최종 적층에 앞서 배터리의 전해질을 포함하도록 밀봉의 전부 및 일부를 형성할 수 있다. 버퍼층은 소비자들 또는 다른 사람들에게 분배되는 최종 카드 제품으로의 최종 적층에 앞서 전자 코어 구조들의 처리를 허용하기 위해 충분한 세기로 경화될 수 있다.

## 실시예

<45> 도입

<46> 본 발명은 전자 구성요소들을, 기준 처리들에 의해 쉽게 열 적층될 수 있는 전자 코어 구조로 통합함으로써 종래 기술의 다양한 결점들에 대한 해결책을 제공한다. 이 구조는 디스플레이, 배터리 또는 다른 전원, 접속 회로들, 스위치들, 자기 스트라이프 에뮬레이터, 안테나, 스마트 칩들 또는 다른 입력 디바이스들과 같은 다수의 원하는 전자 구성요소들을 포함하기 위한 수단을 포함한다. 이 구조는 층들을 브리징하기 위해 적층된 버퍼층들의 사용을 포함하고 전자 구성요소 치수들의 변동을 보상한다. 이 구조는 또한 코어층 구조의 일부로서 배터리 패키징을 통합하고, 원하는 특성들을 부여하기 위해 전자 코어층들의 일부로서 인쇄된 전자 회로를 사용할 수 있다.

<47> 상술된 바와 같이, 다양한 구성요소들이 구조에 통합될 수 있다. 하나의 비제한적인 실시예에서, 디스플레이는 적층된 구조에 포함된다. 그러나, 당업자는 다양한 적층된 구조 응용들이 디스플레이의 포함 없이 본 발명에 의해 제공됨을 알 것이다.

<48> 전자 코어 구조의 하위-조립으로서 사용될 수 있는 디스플레이 셀은 전자 구성요소들을 삽입하고, 관련 ISO 표준들에 따르기 위해 다른 층들과 종래의 열 적층 처리를 통해 처리될 수 있다. 디스플레이 셀은 스마트 카드, 라벨 또는 다른 얇은 정보-디스플레이 구조의 초점을 형성하고 다양한 구성요소들을 포함할 수 있다. 통상적인 구성요소들은 IC들, 디스플레이들, 배터리들, 스위치들, 안테나들 및 접속 회로의 조합들을 포함한다.

<49> 특정한 전자 코어에 요구된 IC들은 최종 응용에 의존한다. 몇몇 경우들에 있어서는, 둘 이상의 칩들이 요구된 기능들을 수행하기 위해 필요할 수 있다. 먼저, 일반적으로 외부 입력들에 기초하여 데이터를 발생 및/또는 전송할 것이다. 예를 들면, 하나의 카드에서, 마이크로프로세서는 카드 상의 스위치로부터 입력 후에 미리 프로그래밍된 알고리즘에 기초하여 거래 승인 번호(Transaction Authorization Number)를 발생시킨다. 데이터는 데이터

터 스트림을 디스플레이된 이미지로 변환하는 디스플레이 구동 칩에 후속적으로 전송된다. 대안적으로, 무선 주파수 수신기 회로는 특정한 팬독기 디바이스 또는 방송 무선파들로부터 신호를 취하고, 이 신호를 디스플레이 구동기에 대한 데이터 스트림으로 변환할 수 있다. 다른 경우들에 있어서, 단일 칩은 원하는 값을 생성하기 위하여 디스플레이를 구동할 뿐만 아니라 필요한 데이터를 발생시키는데 모두 사용될 수 있다. 디스플레이가 그 구조에 존재하지 않는다면, IC는 접촉 패드, RF 안테나 또는 자기 스트라이프 에뮬레이터를 통해 팬독기와 통신하기 위해 사용될 수 있다. 전자 코어 구조는 카드 외부의 기기와 동적 통신이 요구되는 IC들을 포함한다.

<50> 구성요소들 및 막들의 제조 허용오차들로 인해 고유한 치수 변동을 갖는 임의의 하나의 구성요소 및 가변 높이들을 갖는 구조에서의 상이한 구성요소들로부터 하나의 도전이 발생한다. 특히, IC 구성요소들은 완전히 균일하지 않을 것이다. IC 높이의 변동은 기판에 대한 부착으로 인해 다이 높이차들 및 변동의 2개의 주요한 소스들로부터 유발될 것이다. 다이 높이의 변동은 실리콘 웨이퍼들의 그라인딩 및 폴리싱 동안 허용오차들의 결과이다. 다이 부착으로 인한 높이 변동들은 이용된 방법의 함수이다. 배선 결합 기술들이 이용되면, 루프 높이 및 접착 방법은 변동을 도입할 것이다. 플립 칩 부착 방법들은 이용된 결합 기술뿐만 아니라 다이 범핑 변동(die bumping variation)의 결과로서의 변동을 발생시킨다. 두 경우들에 있어서, 캡슐제의 사용은 상당한 부가의 변동을 제공할 것이다. 부착된 구성요소들에 대한 통상적인 다이 높이들은 캡슐제 없이 대략 .007 내지 .012인치들이다.

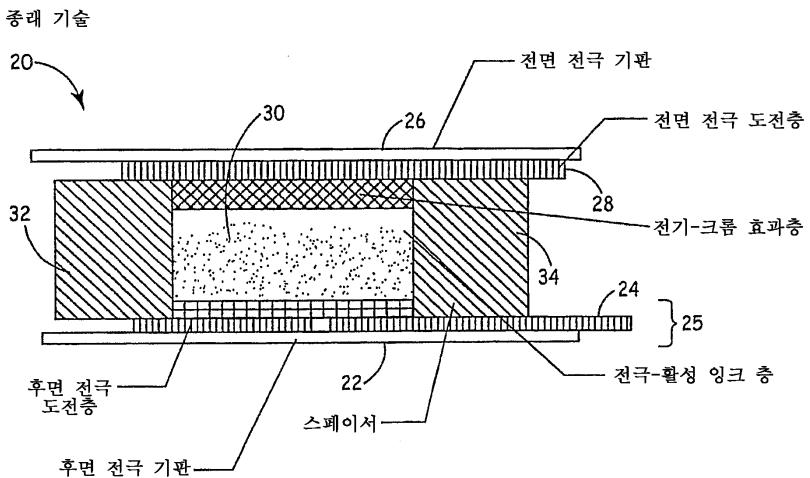

<51> 전자크롬 잉크들을 포함하는 본 발명에 사용 가능한 하나의 디스플레이는, 본 발명의 범위가 다른 디스플레이 기술들도 또한 포함하지만, 미국 특허들 제6,639,709호 및 제6,744,549호와 미국 공개 번호 제2002/0171081 A1 호에 이미 개시되어 있다. 디스플레이들은 높이들의 몇몇 변동을 도입하는 종래의 인쇄 처리를 통해 생산될 수 있다. 그러나, 양호한 디스플레이들은 이 응용에 대한 다른 디스플레이 기술들보다 상당한 이점들을 보인다. 이 점들은 유연성, 낮은 전력 요건들 및 열 적층 처리를 견디는 강력한 구성을 포함한다. 양호한 디스플레이들의 통상적인 높이는 대략 0.006 인치(.150mm)이다. 디스플레이 높이는 후면 막들(backplane films), 인듐 주석 산화물(ITO) 전면 막들(frontplane films) 및 접착 개스킷들(gaskets)과 같은 디스플레이의 개별 구성요소들의 높이의 변동뿐만 아니라 인쇄 높이의 변동에 의해 약간 변할 수 있다.

<52> 주지된 바와 같이, 디스플레이는 전자크롬인 특별한 잉크들로 인쇄함으로써 형성될 수 있다. IC와, IC 및 디스플레이와 연관된 특정한 소규모 패드들 및 트레이스들을 제외하고, 본 명세서에서 만들어지고 조립된 바와 같이 설명된 다양한 층들 상의 다른 구조들이 또한 인쇄 방법들에 의해 형성되고, 인쇄 기술들에 의해 이용된 적층 접착제들 또는 다른 재료들에 의해 층들이 결합된다. 적당한 인쇄 방법들은 스크린 인쇄, 플렉소그래픽(flexographic) 및 그라비어 인쇄(gravure printing)를 포함한다. 이들 방법들의 사용은 그러한 기능적 구조들을 만들기 위해 통상적으로 사용되는 특별한 박막 형성 기기 및 청결한 공간 환경 없이 구조들의 대량의 효율적인 생산을 허용한다. 즉, 최종 카드들로 쉽게 처리될 수 있는 다수의 코어 구조들의 비용 저렴한 대규모의 생산을 허용한다.

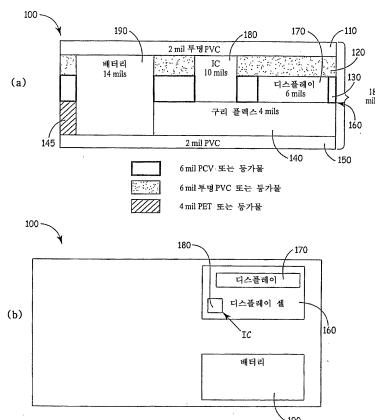

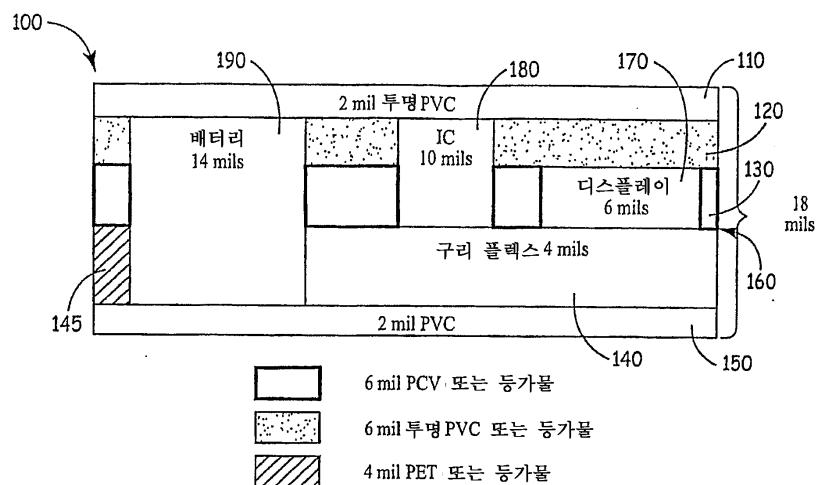

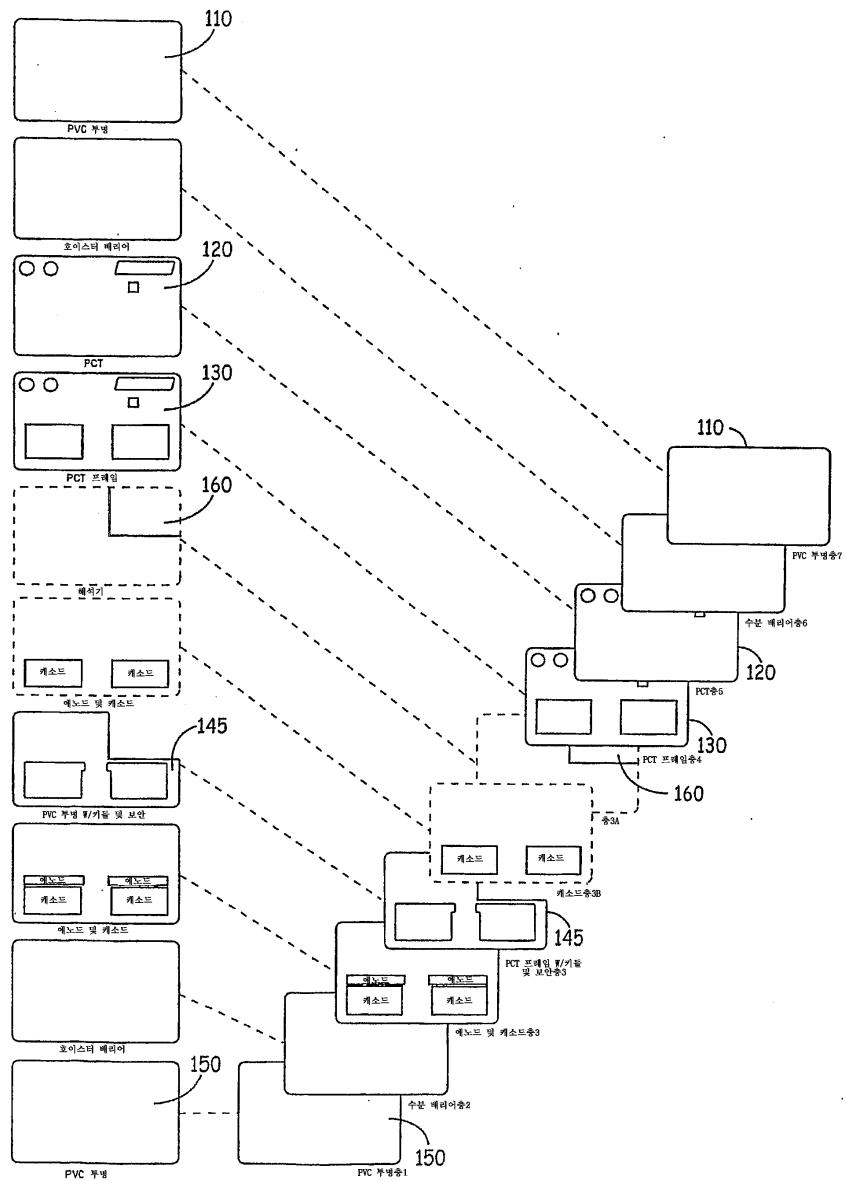

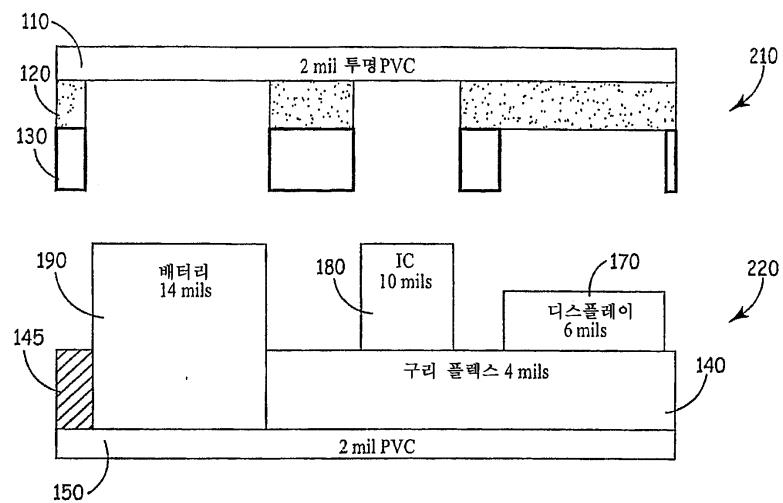

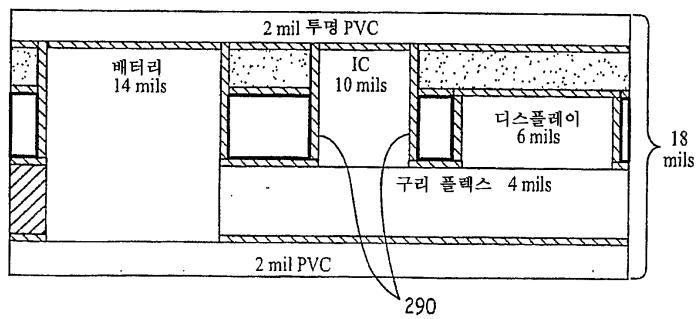

### 외부층들

<54> 도 2a에 최상으로 도시된 바와 같이, 본 명세서에 도시된 구조(100)의 외부층들은 연성 베이스 시트(150) 및 연성 최상부 시트(110)이다. 이들 층들은 통상적으로 PVC, 폴리프로필렌 또는 다른 적당한 열가소성 물질들로 이루어진다. 각각은 약 1.5mils 내지 3mils의 두께를 가지고, 바람직한 두께는 약 2mils이다. 도 2a에 도시된 바와 같이, 외부층들(110 및 150)은 플렉스 회로 기판층(flex circuit substrate layer)(140) 상에 탑재되고 디스플레이(170) 및 IC(180)를 포함하는 디스플레이 셀, 배터리(190) 및 제 1 커버층(120) 및 제 2 커버층(130)과 같은 내부층들과 같은 다양한 전자 구성요소들을 사이에 끼운다.

<55> 이 응용이 금융 거래 카드 또는 ISO 표준들을 충족시키는 다른 카드들일 때, 이들 시트들은 소비자들 또는 다른 사람들에게 제공된 카드의 최종 외부층들이 아니다. 오히려, 이들은 그래픽스층에 의해 커버되고, 도 5에 도시된 바와 같이 투명한 PVC층들을 포함할 수 있다. 외부층들과 그래픽들을 조합하는 것은 외부층 상에 그래픽들을 미리 인쇄함으로써 달성될 수 있으며, 이는 본원 발명의 범위내에 있다. 그 경우, 외부층은 .006 내지 .008인치들이다. 수분 배리어는 분리막이 될 수 있지만 내부층들(110 및 150) 상에 균일한 코팅으로서 첨가되는 것이 바람직하다. 응용이 라벨이면 그래픽층들은 내부 구성요소들을 숨기기 위하여 그래픽 잉크들 또는 다른 수단을 사용함으로써 생성될 수 있다.

<56> 수분 배리어들은 전원이 인쇄되고 전자 코어가 배터리 패키징으로서 기능할 때 분리층들로서 도입된다. 배리어 코팅은 배터리 화학을 보존하도록 의도되고 배터리 전해질로부터 환경으로의 수분 누출을 방지한다. 수분 배리어 없이, 배터리는 시간에 걸쳐 수분을 손실하게 되어 배터리 성능의 저하를 유발할 것이다. 수용할 수 있는 배

리어 코팅들은 본 기술 분야에 널리 알려져 있고, 알루미늄 금속화, 박편들 및 막들에 적용된 다른 특별한 코팅들을 포함한다. "수분(moisture)" 배리어에 대한 참조가 이루어졌지만, 이것은 누출하는 경우에 배터리의 기능을 손상시키는 배터리 반응에 임의의 일시적으로 유용한 배리어를 포함한다. 미리 패키징된 배터리들은 배터리 패키징에 통합된 배리어 코팅을 가지며 따라서 배리어 코팅들의 추가를 요구하지 않는다.

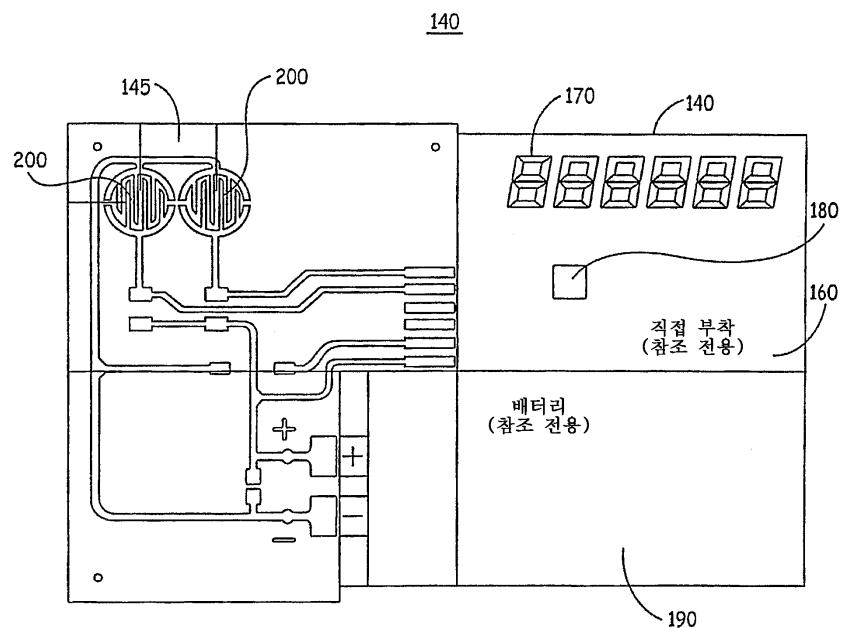

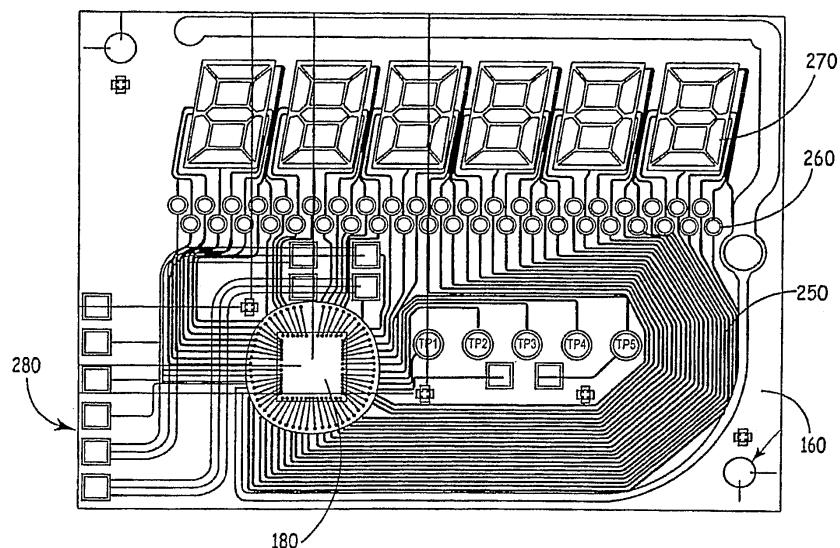

#### <57> 디스플레이 셀

<58> 본 구조의 한 양태는 준비된 기판(140) 상에 디스플레이(170) 및 구동 IC(180)를 포함하는 디스플레이 셀(160)의 사용이다. 디스플레이 셀(160)은 도 3에 도시된 바와 같이 플렉스 회로층(140) 상에 놓인다. 도 12에 도시된 바와 같이, 통상적인 디스플레이 셀(160)은 본 기술 분야에 널리 알려진 기술들을 통해 플렉스 회로층(140) 상에서 생성된 에칭된 구리 연성 회로를 포함한다. 구리 플렉스는 매우 조밀하게 이격된 부착 패드들을 가진 IC(180)에 대한 부착에 필요한 트레이스 해상도를 제공한다. 통상적인 IC들 상의 부착 패드들은 크기가 가변적이며, 패드들 사이에 .002 인치 이격된 .002 인치 패드들로부터 패드들 사이에 .005인치 이격된 최대 .005인치 패드들까지 이격된다. 반도체 산업의 동향은 크기 및 패드들 사이의 거리 모두를 계속 축소시키는 것이다. 에칭된 구리 연성 회로들은 본 기술 분야에 널리 알려져 있고, 요구된 라인 간격을 생성할 수 있다. 그 외에도, 에칭된 금속 스퍼터링된 막들이 또한 요구된 디스플레이 회로 및 다이 부착 기판으로서 기능할 수 있다. 적당한 백플레인 재료들에 대한 요건들은 최소 2mil 라인들 및 간격의 트레이스 해상도, 부착 처리 동안 IC에 대한 적당한 접착 및 mil당 제곱당 100옴보다 작은 저항이다.

<59> 따라서, 디스플레이 셀(160)은 요즘 인쇄 이외의 처리들에 의해 생성되고 기술된 인쇄 및 적층 처리에 대한 입력들로서 요구되게 될 2개 타입들의 구성요소들(막 또는 시트 재료들 이외)을 통합한다. 제 1 타입의 구성요소는 IC들이며, 현재 특별한 청결한 공간 생산 설비들을 요구한다. 제 2 타입의 구성요소는 에칭된 구리 연성 기판이다. 본 발명의 디스플레이 셀(160)에 대한 구리 기판은 도 1에 도시된 후면, 본 기술 분야에 널리 알려져 있고 당업자에 의해 구리 플렉스로서 흔히 참조되는 도전성 박편 코팅된 기판을 먼저 에칭함으로써 생산된다. 후면은 디스플레이용 전극들, IC(180)에 대한 부착 면적 및 구동 IC에 대한 굑셀 트레이스들에 대한 상호접속들로서 역할하는 굑셀 트레이스들(250)을 포함한다. 구동 IC들에 대한 입력 리드들은 전자 코어 기판에서 나머지 회로 소자들에 대한 후속 부착을 위해 디스플레이 셀(160)의 하지(280)에 이르게 한다.

<60> 본 명세서에 사용된 바와 같이, 디스플레이 셀(160)에 대한 "광셀"은 디스플레이 소자들(260 및 270)과 같이 임의의 기하학 형상의 임의의 디스플레이 소자를 의미하고, 이것은 개별적으로 전기적으로 제어 가능하다. 따라서, 광셀 디스플레이 소자는 원형, 사각형, 긴 다각형, 또는 다른 광셀들로 이미지 글자를 형성하는데 유용한 임의의 다른 형상 또는 아이콘 또는 문자를 단독으로 포함하는 임의의 형상의 형태일 수 있다. 광셀의 전기 제어는 IC 상에 전용 I/O를 제공함으로써 또는 패시브 매트릭스와 같은 로우 및 컬럼 어드레싱 또는 회로 설계 멀티플렉싱을 제공함으로써 달성을 수 있다.

<61> 디스플레이 셀(160)의 디스플레이부(170)는 전자크롬 잉크를 인쇄하고, 접착 개스킷을 인쇄하고, 디스플레이 구조를 완성하기 위해 패터닝된 후면 상에 투명 도전층을 적층함으로써 광셀 트레이스들(250) 위에 조립된다. 디스플레이 구동 IC(180)는 그 후 본 기술 분야에 널리 알려진 플립 칩 또는 배선 결합 기술들과 같은 다양한 기술들을 사용하여 부착된다. 디스플레이 셀(160)은 통상적으로, 에칭된 구리 패턴의 다수의 응답들(replications)을 포함하는 시트 또는 룰 상에 인접한 직사각형들에서 생성된다. 그 후, 각각의 디스플레이 셀은 IC를 수신한 후에, 인쇄 및 적층 처리에 대한 입력들이 되는 개별 부품들로 단일화된다.

<62> 다양한 종래의 인쇄 처리들은 스크린 처리, 스텐실(stencil) 처리, 플렉소그래픽 처리, 그라비어 처리 또는 임의의 처리 조합을 포함하여 디스플레이(170)를 생성하기 위해 사용될 수 있다. 양호한 인쇄 처리는 평상형(flatbed) 방법들 또는 회전식(rotary) 방법들에 의해 스크린 인쇄된다. 사용된 잉크들은 미국 특허 번호 제 6,879,424호에 기술된 전자크롬 잉크들이다. 디스플레이 셀의 구조에 관련된 다른 세부사항들은 2005년 1월 4일에 출원되고, 발명의 명칭이 "Universal Display Module"이며, 본 명세서에 참조로서 포함된 미국 특허 출원 일련 번호 제11/029,201호에서 볼 수 있다.

<63> 전형적으로 인쇄된 범용 디스플레이 모듈은 도 1에 도시되어 있고, 일반적으로 참조 번호(20)로 식별된다. 범용 디스플레이 모듈(20)은, 적어도 하나의 전극을 포함할 수 있는 후면 회로(24)로 패터닝된 백플레인 기판(22)과 전기적으로 도전성이고 투명한 최상부 플레이인 기판(26)과, 적어도 하나의 전극을 포함할 수 있는 최상부 플레이인 도전층(28)과, 디스플레이(30) 및 한 쌍의 스페이서들(32 및 34)로 이루어진 후면(25)을 포함한다. 대안적으로, 전극들은 최상부 플레이인 또는 백플레이인 상에 나란한 관계로 이격부에 형성될 수 있다. 범용 디스플레이 모듈(20)은 또한, 백플레이인(24)에 대한 최상부 플레이인(26)을 밀봉하기 위한 접착 개스킷(도시되지 않음)을

포함한다. 최상부 플레인(26) 및 백플레인(24)은 또한 예를 들면 도전성 에폭시(도시되지 않음)로 함께 단락된다.

#### <64> 전원들

IC 칩(180) 및 다른 전자 구성요소들은 처리 또는 다른 기능들을 수행하기 위하여 전력을 요구한다. 다양한 전원들은 전자 소자들에게 무선으로 전력을 공급하기 위한 외부 소스들로부터 방사된 에너지를 흡수하는데 사용되는 부착된 RF 안테나를 가진 정류기와 같은 전기 코어 구조에 제공될 수 있다. 또 다른 전원은 주위 광에 의해 도달되는 코어 구조층 상에 배치될 수 있는 하나 이상의 광전 셀들이다. 다른 가능한 전원은 코어 구조에 삽입된 배터리(190)이다. 모든 경우들에 있어서, 전원은 통상적으로, IC가 탑재되는 층 상의 전력 입력 트레이스들에서 IC 칩(180)에 접속된다.

<66> 스마트 카드들에 사용하기 위한 적당한 배터리들은 얇은 형태 인자를 요구한다. 이러한 배터리들은 일반적으로 본 기술 분야에 알려져 있고 리튬 기술 또는 탄소 아연 화학에 통상적으로 기초한다. 적당한 미리 패키징된 리튬 배터리의 예는 부품 번호 FP252903M002로서, 플로리다 레이크랜드의 솔리코어 인코포레이티드(Solicore Inc.)로부터 이용 가능하다. 탄소 아연 화학에 기초한 적당한 미리 패키징된 배터리는 부품 번호 1-1-ZC 하의 오하이오, 클리브랜드의 얇은 배터리 기술로부터 이용 가능하다. 다른 얇은 배터리 기술들은 또한 고체 상태의 구성들 또는 다른 전기화학 시스템들에 기초하여 알려져 있다. 본 발명에 대한 전원은 1차 또는 2차 셀들로 이루어질 수 있다. 슈퍼 커페시터들과 같은 저장 디바이스들은 판독기를 통해 충전 수단과 조합하여 활용될 수 있다. 종래의 IC들 및 다른 구성요소들을 위한 적당한 전원들에 대한 통상적인 요건들은 .016의 최대 두께를 부과한 코어 구조를 갖는 적어도 1.5볼트들의 전위, 적어도 5밀리-암페어-시간의 용량이다.

<67> 미리 패키징된 유닛들로 생산된 배터리들은 본 발명의 전자 코어에 통합될 수 있다. 배터리들의 전체 두께는 .012 내지 .016인치의 범위로 생산된다. 미리 패키징된 배터리(190)는 연성 베이스 시트(150)와 연성 최상부 시트(110) 사이의 구조(100)에 삽입 및 내장될 수 있다. 대안적으로, 배터리(190)의 화학 구성요소들은 배터리층들을 포함하는 재료들을 침착함으로써 적층된 구조(100)와, 종래의 스크린 인쇄, 플렉소그래픽 인쇄 또는 그라비어 인쇄를 포함한 다양한 알려진 인쇄 기술들에 의한 특징들 상에 배치될 수 있다.

<68> 배터리들로부터 유도된 에너지는 셀내의 화학 반응의 결과이다. 배터리의 용량 및 이용 가능한 전력은 반응에 이용 가능한 배터리 재료의 양의 강력한 기능이다. 대부분은, 이것은 재료들의 부피로서 생각될 수 있다. 카드 구조들에서 이용 가능한 면적은 크게 고정되기 때문에, 배터리 재료 부피를 최대화하기 위한 욕구는 두께를 최대화하기 위한 욕구에 대응한다.

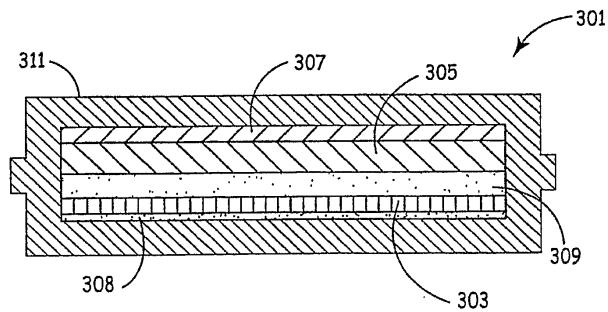

<69> 배터리들은 배터리 재료들을 포함하고 전해질의 적당한 레벨(증발에 민감할 수 있음)을 유지하기 위한 패키징을 요구한다. 구조(100)에 삽입된 얇은 형태 인자 배터리들의 경우에, 패키징은 재료를 넣는 미리 패키징된 막들의 형태이다. 패키징막들은 통상적으로, .003 내지 .005 인치의 두께들이며, 필요한 패키징의 결과로서 총 배터리 두께의 .006 내지 .010으로 변환된다. 배터리(190)가 구조(100)에 인쇄되는 경우에, 본 발명은 종래의 배터리 패키징 재료들보다는 배터리를 넣기 위해 전자 코어를 포함하는 층들 또는 막들을 활용한다.

<70> 도 14에 도시된 바와 같이, 배터리 인쇄의 하나의 알려진 방법에서, 미리 패키징된 얇은 연성 인쇄된 배터리(301)의 구성요소들은 인쇄된 애노드(303), 인쇄된 캐소드(305), 캐소드 전류 콜렉터(307), 애노드 전류 콜렉터(308), 분리기(309) 및 분리기 내의 수성 전해질을 포함하며, 모두 연성의 얇은 배터리 패키지 하우징(311) 내에 포함된다. 탄소 아연 셀의 캐소드 조립은 캐소드 전류 콜렉터(307) 및 전해질 망간 이산화물, 활성 재료(305)를 포함하며, 이들은 캐소드 전류 콜렉터 잉크가 최소로 접착되거나 균열이 없는 연성 시트 상에 인쇄된다. 전류 콜렉터(307)는 스텐실, 스크린 또는 다른 적당한 인쇄 장치를 사용하여 연성 시트 상에 침착된다. 캐소드 전류 콜렉터 잉크는 방전 동안 캐소드의 감소시에 발생되는 전자들을 전달하기에 충분한 재료들로부터 공식화된 잉크가 될 수 있다. 전해질 망간 이산화물 캐소드를 사용하는 탄소 아연 셀에서, 캐소드 전류 콜렉터는 탄소 잉크가 바람직하다. 인쇄된 콜렉터는 그 후 적당한 건조 및 용매 증발을 보증하기 위해 적당히 경화된다. 도 14에 도시된 바와 같이, 이 얇은 배터리 인쇄의 알려진 방법들은 패키징 또는 하우징(311)되는 배터리 두께의 실질적인 비율을 유발한다.

<71> 본 발명에서, 코어 구조의 다른 양태들에 사용된 인쇄 라인은 코어 구조의 건설 동안 배터리 재료들을 배치시키는데에도 또한 사용될 수 있다. 도 14에 도시된 미리 패키징된 배터리의 패키징막들을 대신하기 위하여 전자 코어 구조의 일부가 되는 막들을 사용함으로써, 배터리의 용량을 증가시키거나 또는 배터리의 전체 정규 두께를 감소시키기 위하여 부가의 부피가 이용 가능하다. 본 발명의 일 실시예는 막층 조립 동안 배터리 재료들을 전자

코어 구조로 건설함으로써 부가의 패키징막들을 제거하는 것이다.

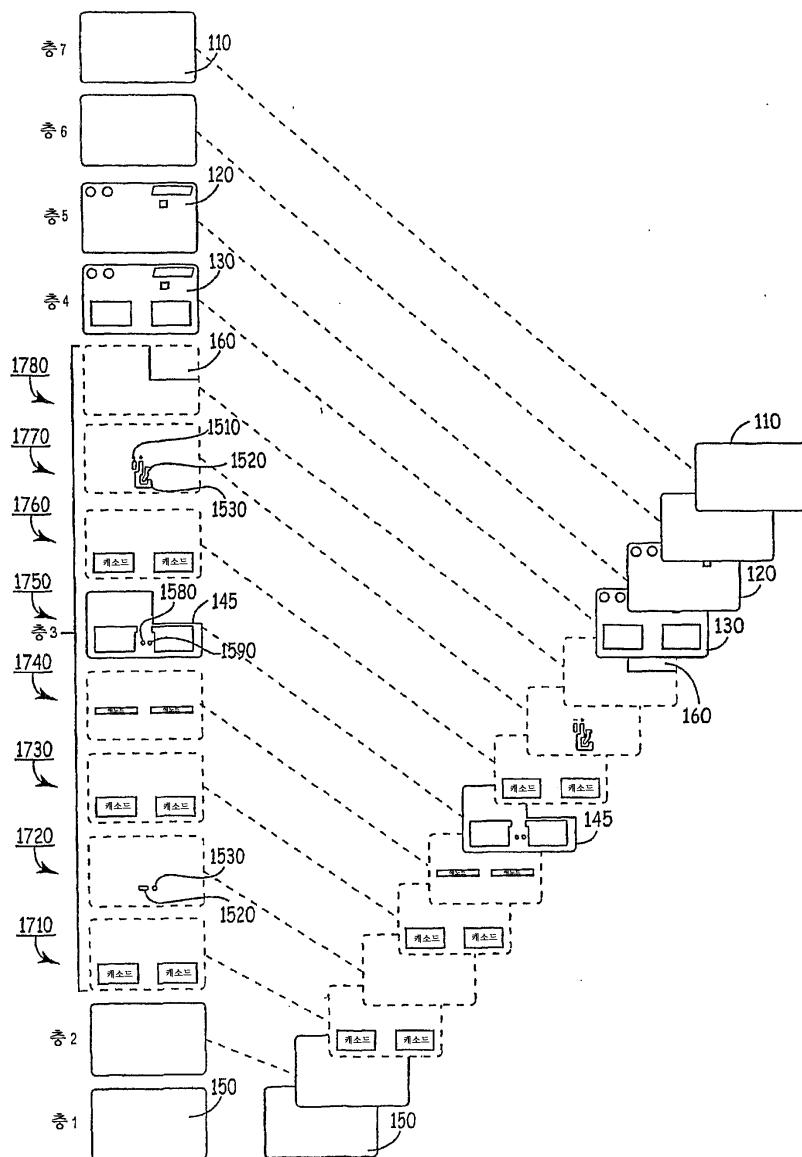

<72> 본 발명에 따라, 배터리들은 여러 단계들에서 코어 구조의 구성 동안 인쇄 및 삽입될 수 있다. 도 17은 도 13에 도시된 일 실시예에 따라 삽입된 배터리들의 구성 단계들(1710 내지 1780)을 도시한다. 일 실시예의 방법은 스크린 인쇄 처리들을 활용한다. 제 1 단계는 애노드 및 캐소드에 대한 전류 콜렉터들의 생성을 포함한다. 탄소 아연 화학의 경우에, 캐소드 전류 콜렉터는 도전성 탄소로 이루어진다. 전류 콜렉터는 층(110 또는 150) 상에 인쇄된다. 단계(1710)에서, 전류 콜렉터는 베이스층(150) 상에 인쇄되는 것으로 도시된다. 애노드 전류 콜렉터는 적당한 도전성 코팅에 의해 또는 도전성 박편의 사용에 의해 형성된다. 애노드와 캐소드 사이 및 셀들 사이의 상호접속 회로는 뉴욕 펠함의 스프레이얼렛 코포레이션(Spraylat Corp)으로부터 스프레이얼렛 XCM-015와 같은 도전성 은 잉크를 사용하여 형성되며, 이것은 단계들(1720 및 1770)에서 인쇄된다. 캐소드 재료는 그 후에 단계(1730)에서 코어층(145)의 높이를 매칭하도록 인쇄된다. 애노드는 단계(1740)에서 코어층(145)의 높이까지 재료를 배치함으로써 형성된다. 단계(1750)에서, 코어층(145)은 부 버퍼층을 사용하여 베이스 시트(150)에 적층되며, 이것은 본 명세서에 더욱 상세히 기술된다.

<73> 디스플레이 셀(160)과 같은 전자 구성요소들은 단계(1780)에서 코어에 배치되고, 전자 구성요소들과 배터리 사이의 전기적 상호접속들이 형성된다. 원한다면, 부가의 캐소드 재료가 배터리 용량을 부가하기 위해 조립의 단계(1760)에서 인쇄될 수 있다. 부가의 캐소드 재료는 코어층(130)의 두께를 초과해서는 안된다. 원하는 캐소드 높이가 인쇄되었으면, 코어층(130)은 부 버퍼층을 사용하여 코어층(145)에 적층된다. 이 처리는 다양한 코어층들에 의해 형성된 웰(well)에 포함된 인쇄된 배터리를 효과적으로 생성한다. 배터리는 원한다면 분리 시트의 부가 및 형성된 웰로의 배터리 전해질의 부가에 의해 완성된다. 전해질은 인쇄 또는 비인쇄 방법들을 통해 주입될 수 있다. 대안적으로, 젤이 되게 하는 적당한 점착제와 물이 주입될 수 있다. 나란한 구성에서, 분리기 시트는 셀을 습식시키고 전해질을 적소에 유지한다. 공동 면(co-facial) 구성에서, 분리기는 전해질을 적소에 유지하고 캐소드로부터 애노드를 분리하기 위한 두 가지의 기능을 한다. 배치된 배터리 재료들은 그 후 셀을 밀봉하기 위해 코어층(120)의 적층을 통해 밀봉된다.

<74> 당업자는 다양한 셀 기하학들이 배터리의 애노드와 캐소드를 형성하기 위해 사용될 수 있음을 알 것이다. 또한 셀들이 생성되어 전원의 전압을 증가시키기 위해 직렬로 접속될 수 있음을 알 것이다. 셀 기하학들은 나란한 기하학(층의 한 표면 상에)으로 애노드 및 캐소드를 생성하거나 또는 분리층들의 대향면들 상에 애노드 및 캐소드를 인쇄하고 셀을 완성하기 위해 대향면들 사이에 분리 시트를 사용하여 공동 면 기하학을 생성함으로써 가변할 수 있다.

<75> 리튬 셀들의 경우, 애노드는 원하는 형태로 베이스 시트(150) 상에 리튬 금속을 스퍼터링함으로써 형성된다. 스크린 인쇄 처리와 같은 적당한 처리를 사용하여 인쇄된 도전성 은을 사용하는 이전 예와 동일한 방식으로 내부 접속들이 형성된다. 캐소드는 코어층들(130, 140 및 145)로 이루어진 전해질 웰을 형성하기 위한 유사한 적층 방식을 사용하여 코어층(150) 상에 인쇄된다.

<76> 아연 셀에서, 애노드는 아연이 소비되는 경우에도 방전 동안 도전성을 유지한다. 하우징 외부에 음의 단자를 형성하는 애노드 텁은 개별 애노드 콜렉터와 전기 접촉되기 보다는 아연 잉크와 직접 접속된다. 스크린 인쇄의 경우, 잉크의 인쇄 능력에 대한 최적의 메시 개구(optimum mesh opening)가 결정된다. 이러한 결정에서 고려할 인자들은 아연의 입자 크기, 잉크 점착력 및 전단기 하의 다른 흐름 특성들 및 충분한 용량을 달성하는데 필요한 잉크의 요구된 두께를 포함한다. 아연 금속의 다른 적당한 소스들은 아연 박편 또는 아연 메시를 포함하며, 이것은 배터리 애노드로서 작용한다. 아연 박편과 같은 재료는 핑엔 플레이스 라인의 일부로서 구조에 배치되어 배터리 구성 동안 침착될 수 있다.

<77> 공동 면 전극 조립들 동안, 분리기(309)는, 이온들의 흐름을 예전히 가능하게 하면서 전극들을 전기적으로 분리하기 위해 포함된다. 본 명세서에 사용된 바와 같이, "공동 면" 전극들은 주 애노드 표면과 주 캐소드 표면 사이의 면과 면 사이에 긴 면적을 공유하며, 이들은 코어층들의 대향 면 표면들 상에 있다(공동 면 전극들은 나란한 전극들과 구별되며, 주 애노드 조립(가능하다면, 애노드 플러스 콜렉터) 표면 및 주 캐소드 조립(가능하다면 캐소드 플러스 콜렉터) 표면이 동일한 면에 근사적으로 놓여 있고 기판 재료의 단일 조각 상에 직접 또는 간접적으로 인쇄됨). 애노드와 캐소드층들 사이의 분리기(309)는 페이퍼 분리기, 젤이 된 분리기 또는 인쇄된 분리기가 될 수 있다. 공동 면 배열을 갖는 전극 조립을 사용하는 탄소 아연 실시예에서, 코팅된 크래프트 페이퍼 분리기(coated kraft paper separator)는 분리기로서 활용될 수 있다. 본 발명에 따른 탄소 아연 셀 실시예에 대해, 전해질은 분리기를 포화하는 아연 염화물의 수용액인 것이 바람직하다.

<78> 인쇄된 배터리로부터 IC 칩(180)에 이르는 입력 트레이스들까지의 접촉들은 또한 인쇄 처리에서 형성될 수

있다. 일 실시예에서(도시되지 않음), 전극에 대한 전류 콜렉터는 밀봉 영역으로 측면으로 연장되는 반면, 제 2 금속 외부 단자는 밀봉 영역으로 연장되며 밀봉 영역 내의 전류 콜렉터에 접촉한다. 이 실시예에서, 전류 흐름에 대한 전기 도전성은 내부 전류 콜렉터와 외부 단자 사이의 물리적 접촉에 의해 제공된다. 또 다른 실시예에서(도시되지 않음), 전류 콜렉터 및 외부 단자는 물리적으로 접촉되지 않는다. 오히려, 전기 도전성은 밀봉 영역 내에 적어도 부분적으로 위치되고 2개의 구조들을 브리징하는 전기적으로 도전성인 접착제 또는 애폭시에 의해 제공된다. 애노드 및 캐소드의 전기적 접촉들은 배터리의 측면 밀봉의 외부로 연장하는 접촉을 제공함으로써, 전해질로부터 물리적으로 분리된다. 당업자는 다른 접촉 배열들이 구현될 수 있음을 알 것이다.

<79> 애노드 및 캐소드 외부 단자들 또는 접촉들은 연성 비도전성 중합체 기판 상에 은 기반 도전성 중합체 잉크로 인쇄되는 것이 바람직하다. 캐소드 콜렉터는 콜렉터 및 외부 접촉이 적어도 셀 패키지 또는 컨테이너의 밀봉 영역에서 오버랩하도록 외부 캐소드 접촉 상에 인쇄된다. 동일한 방식으로, 애노드 잉크는 애노드 및 외부 접촉이 적어도 셀 패키지 또는 컨테이너의 밀봉 영역에서 오버랩하도록 외부 애노드 접촉 상에 인쇄된다.

<80> 캐소드 전류 콜렉터 형상은 캐소드 잉크와 충분한 접촉을 허용하기 위해 선택되며, 또한 밀봉 영역에서 캐소드 텁의 일부를 오버랩하는 영역을 형성하는 것이 바람직하다. 전류 콜렉터 잉크는 건조되고, 그 후 캐소드 잉크는 전류 콜렉트 상에 인쇄되고 건조된다. 분리기(309)는 그 후 공동 면 배열로 캐소드들의 경우에 애노드(303)와 캐소드(305) 사이에 배치된다.

<81> 다양한 수단에 의해 배터리 구조로 전해질이 도입된다. 일 실시예에서, 방법은 코어 구성에 의해 형성된 웰에 미리 결정된 부피의 액체 전해질을 시여하는 시여 시스템(dispensing system)을 포함한다. 웰은 베이스층(150) 및 중간층들(145, 130 및 120)의 다이-컷 개구들(die-cut openings)에 의해 형성된다. 웰의 총 높이는 층들(145, 130 및 120)에 대한 막 두께에 종속하여 대략 10 내지 14mils이다. 층들(150/145, 145/130, 130/120) 사이의 벼파층들은 배터리 밀봉을 제공하며, 층들 사이의 전해질의 누설을 방지한다. 열 적층 동안, 배터리층들 및 벼파층들은 높은 세기를 갖는 밀봉을 배터리에 제공하기 위해 용해된다. 필요하다면, 캐소드와 애노드의 개선된 습식을 제공하는 분리기 시트가 사용될 수 있다. 대안적으로, 전해질은 스크린 또는 스텐실 인쇄와 같은 인쇄 방법들을 사용하여 애노드 및 캐소드 위에 인쇄되도록 허용하기 위하여 충분히 젤이 될 수 있다(예를 들면, 화학에 실질적으로 영향을 미치지 않는 적당한 접착제의 사용에 의해).

#### 스위치들 및 다른 입력 구성요소들

<83> 전자 코어 구조에 통합될 수 있는 다른 전기적 구성요소들은 IC 칩들에 대한 입력 신호들을 제공 또는 수신하거나 회로들을 완성하기 위하여 도 4에 도시된 스위치 접촉들(200), 또는 센서들과 같은 다른 디바이스들을 포함한다.

<84> 많은 응용들에서, 스위치는 전자장치들을 활성화하고 구성요소들에 전력을 턴온하기 위해 필요할 수 있다. 종래의 멤브레인 스위치 기술이 본 발명에서 활용될 수 있다. 돔형, 평면 또는 양각 스위치들과 같은 여러 개의 다양한 스위치들이 이용 가능하다. 돔형 스위치들의 경우, 통상적으로, 금속 돔은 활성화시 누르는 회로 위에 배치된다. 돔들은 돔들을 손상시키거나 영구적으로 밀어 넣지 않고 열 적층될 수 있다.

<85> 대안적으로, 스위치에 대한 전기 접촉 패드들은 카드에서 미리 결정된 위치 및 깊이로 층(145) 또는 또 다른 적당한 층 상에 인쇄된다. 일단 열 적층이 완료되었으면, 돔이 배치되도록 공동이 압연될 수 있고, 카드는 스위치 돔을 삽입하기 위해 다시 밀봉된다. 따라서, 압연이 비인쇄 처리일지라도, 전자 코어 구조는 인쇄 라인에 통합되거나 인쇄되는 대부분의 구성요소들로 우선 제작될 수 있다. 응용에 필요하다면, 코어는 압연된 공동 또는 돔 용 다이 컷을 후속하여 가질 수 있고, 초기의 인쇄 처리의 효율성들로부터 이점을 가진다. 평면 스위치들의 경우, 스위치는 회로의 2개의 절반들을 분리하는 스페이서를 파열시키지 않고 적층되어야 한다. 양호한 돔들은 .018인치들의 높이를 가진 직경 6밀리미터이다. 촉감을 위해 돌출한 돔을 포함하지 않는 평면 스위치는 도 3에 도시된 층들 외에도, 각각 플렉스 회로층, 스페이서층 및 단락층(shorting layer)과 같이, 다양한 층들을 사용하여 생산된다.

<86> 부가 또는 대안적인 전자 구성요소들은 본 발명의 층(145)에 포함될 수 있다. 예시된 실시예가 전자 구성요소로서 디스플레이를 사용하지만, 자기 스트라이프 애플레이터들, RF 안테나, 또는 생체측정 센서들과 같은 다른 디바이스가 본 발명의 범위를 벗어나지 않고 통합될 수 있다.

#### 인쇄된 층들 및 상호접촉들

<88> 디스플레이 셀(160) 및 다양한 봉쇄층들(containment layers)의 표면들은 전기 소자들에 대한 필요한 접속 회로를 전달하기 위해 사용될 수 있다. 구조(100)가 복수의 층들을 포함할 수 있기 때문에, 각 층, 전후는 인쇄 가

능하거나, 저항성, 유전성 또는 다른 구성요소들을 포함한 회로에 사용될 수 있다. 쓰루홀 인쇄와 같은 기술들은 층의 한 면에서 다른 면으로 도전성 회로를 유발하기 위해 활용될 수 있다. 이 방법은 알려져 있으며, 비아(via)를 통해 도전성 재료를 제공함으로써 전기적으로 접속되는 막층을 통해 비아를 제공함으로써 달성된다. 회로는 인쇄된 은, 또는 본 기술 분야에 알려진 다른 도전성, 저항성 또는 유전성 재료들과 같은 도전성 트레이스들의 형태가 될 수 있다. 따라서, 미리 조립된 몇 개의 항목들을 제외하고, 적층 구조의 모든 소자들 및 구성요소들은 인쇄 라인에 인쇄되거나 또는 인쇄 라인에 쉽게 부가될 수 있다. 예를 들면, IC(180)가 인쇄 이외의 처리들에 의해 현재 생산되더라도, 디스플레이 셀(160)의 일부로서의 IC(180)의 인스톨들은 전자 코어 구조의 다른 층들을 형성하기 위해 이용된 인쇄 라인에서 동시에 수행될 수 있고, 따라서 IC는 전자 코어 구조에 적당히 접적된다.

- <89> 인쇄 처리들의 사용은 고속 및 저비용으로 대량의 시트들 및/또는 롤들에서 많은 개별 구조들에 대한 회로 부분들을 가진 층들을 생산하는 것을 가능하게 한다. 하나 또는 두개의 표면들 상에 인쇄된 전기 트레이스들을 갖는 이들 미리 형성된 구성요소층들은 단일화될 수 있고, 하기에 기술된 바와 같이, 디스플레이 셀(160) 및 층들 사이에 적당한 전기 접속을 제공하는 비아들 및 위치적으로 짹으로 인쇄된 구조들로, 베이스 시트와 최상부 시트 사이의 적층 처리들로 조립될 수 있다.

- <90> 인쇄된 층들, 디스플레이 팩셀들, 도전성 트레이스들, 저항기들, 스위치들, 배터리들, 커패시터들 및 도전성 접착제와 같은 광범위한 소자들을 건설하거나 인쇄하기 위해 알려진 처리들이 사용될 수 있다. 이들 소자들 및 구성요소들은 도 2a 및 도 3을 참조로 사용하여, 원하는 구조들 및 접속들을 만들기 위한 필요에 따라, 플렉스 회로층(140), 제 1 커버층(120) 및 제 2 커버층(130)을 포함한 상술된 층들 중 어느 하나의 최상부 또는 하부에 인쇄될 수 있다. 이들 인쇄 가능한 소자들은, 또한 부가의 층들을 구현하는 것이 더욱 복잡한 구조들 및 접속들을 용이하도록 더욱 인쇄 가능한 표면들을 제공할 때, 도 3에 도시되지 않은 부가의 층들 상에 인쇄될 수 있다.

- <91> 예를 들면, 도 3 및 도 4를 참조하여, 단락 패드들이 제 1 커버층(120) 상의 최상부에 인쇄될 수 있고, 그에 의해 스위치(200)용 멤브레인을 형성한다. 또한 다른 예로서, 제 2 커버층(130)의 하부 상의 적당한 위치들에 분로들(shunts)이 또한 인쇄될 수 있으며, 제 2 커버층(130)은 플렉스 회로층(140) 상에 원하는 회로들로 점프하기 위해 조립시 플렉스 회로층(140)에 인접할 것이다. 다양한 다른 구성요소들은 디스플레이(170), 저항기들, 커패시터들 및 안테나들에 대한 전극들과 같이 플렉스 회로층(140)에 동작 가능하게 접속된 구성요소들 및 이와의 접속을 형성하기 위해 제 2 커버층(130)의 하부 상에 인쇄될 수 있다. 부가적으로, 더욱 복잡한 접속들은 후속 트레이스들이 동일한 위치 상에 인쇄되도록 허용하는 원하는 층들의 부분들 상에 크로스오버 절연을 인쇄함으로써 형성될 수 있다.

- <92> 또 다른 예에서, 도전성 접착제가 제 2 커버층(130)의 하부 상에 비도전성 접착제와 함께 패턴 인쇄될 수 있어서, 도전성 접착제는 플렉스 회로층(140) 및 층(130) 상에 원하는 회로를 접속하기 위해 패턴 인쇄된다. 원하는 층 상에 커패시터들 또는 저항기들을 인쇄하는 것을 포함한 다양한 다른 인쇄된 구성들이 또한 달성될 수 있다. 이들 인쇄된 소자들은 대안적으로 원하는 층 상에 탑재된 표면이 될 수 있다.

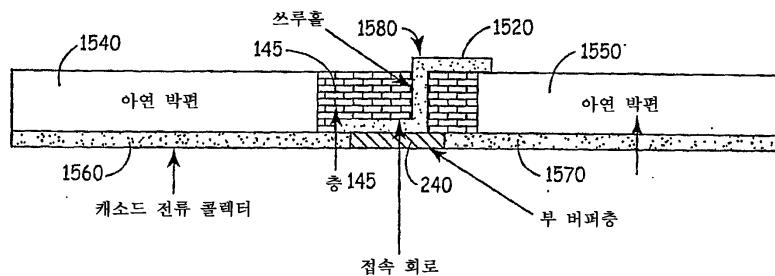

- <93> 도 16a를 참조하여, 기존의 스마트 카드 접촉 카드들은 카드(1600)와 스마트 카드 판독기(도시되지 않음) 사이의 접촉 지점들을 형성하기 위해 칩 플레이트(1610)를 활용한다. 마이크로프로세서(1620)는 배선 결합, 플립 칩 또는 칩 플레이트 하의 다른 종래의 다이 부착 방법들을 통해 플레이트(1610)에 통상적으로 부착되고, 카드 상에 포함된 데이터, 처리기 및 프로그래밍을 하우징하기 위해 전기적 및 물리적으로 부착된다. 몇몇 실시예들에서, 칩 플레이트(1610) 및 마이크로프로세서(1620)를 고정하기 위해 아교(glue)(1630) 또는 다른 접착제 및 지지(1640)가 또한 제공된다. 접촉 스마트 카드들은 스마트 카드 칩을 카드들의 다른 구성요소들과 현재 접속하지 않는다. 그러나 디스플레이 또는 생체측정 센서와 같은 카드의 다른 전자 구성요소들에 이 마이크로프로세서를 접속하는 것이 바람직할 수 있다. 이들의 경우들에 있어서, 코어층(145) 상의 인쇄된 회로는 스마트 카드 칩 플레이트와, 하기에 더욱 상세히 기술되는 바와 같이 IC(180)과 같은 다른 구성요소들 사이의 도전 경로를 제공하기 위해 사용될 수 있다.

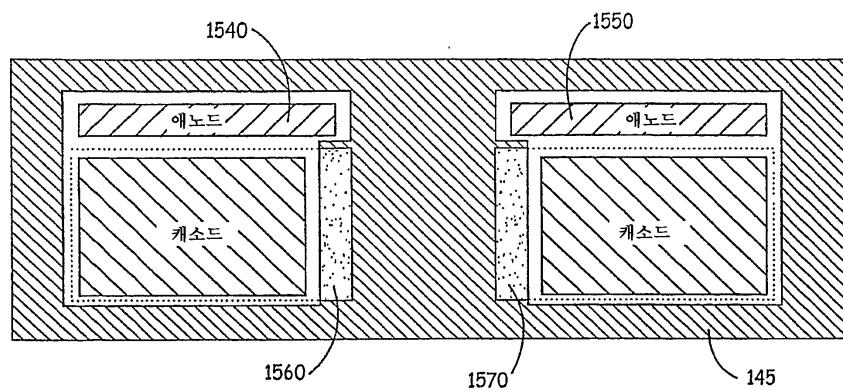

#### 배터리 상호접속

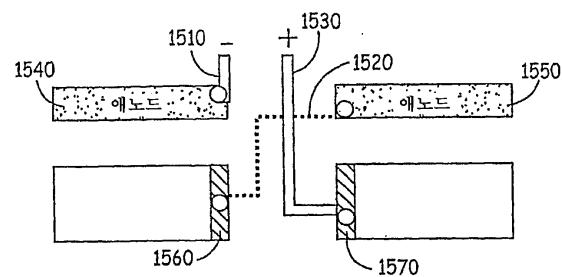

- <95> 이미 주지된 바와 같이, 2개 이상의 셀들이 생성되고 전원의 전압을 증가시키기 위해 직렬로 접속된다. 셀 기하학들은 도 15a를 참조하여 가변할 수 있으며, 일 실시예에서, 2개의 배터리들이 나란한 기하학으로 인쇄되고 상호접속된다. 제 1 배터리의 애노드(1540) 및 캐소드 전류 콜렉터(1560)가 위치되고, 제 2 배터리의 애노드(1550) 및 캐소드 전류 콜렉터(1570)가 나란히 인쇄된다. 이를 배터리들을 직렬로 접속하기 위하여, 도전성 브리지(1510)는 음의 단자를 형성하기 위해 제 1 배터리의 애노드(1540)에 전기적으로 접속되고, 도전성 브리지

(1530)는 양의 단자를 형성하기 위해 제 2 배터리의 캐소드 전류 콜렉터(1570)로부터 제공되며, 도전성 브리지(1520)는 제 2 배터리의 애노드(1550)에 제 1 배터리의 캐소드 전류 콜렉터(1560)를 접속한다.

<96> 도 15a 및 도 15b를 참조하여, 음의 단자를 형성하는 도전성 브리지(1510)가 애노드(1540)로부터 코어층(145)의 최상부로 이끌어지는 것을 볼 수 있다. 양의 단자를 형성하는 도전성 브리지(1530)는 또한 코어층(145)(도 15b에 도시되지 않음)의 최상부로 연결된다. 코어층(145)을 통해 2개의 셀들 사이의 상호접속을 달성하기 위하여, 코어층(145)의 쓰루홀(1580)이 제공된다. 도전성 브리지(1520)는 도 15b에 도시된 바와 같이, 쓰루홀(1580)을 통과시켜, 코어층(145) 아래에 있는 제 1 배터리의 캐소드 전류 콜렉터(1560)를 코어층(145) 위에 있는 제 2 배터리의 애노드(1550)에 접속한다. 유사하게, 도전성 브리지(1530)는 코어층(145)의 최상부의 양의 단자를 형성하기 위해 코어층(145) 아래에 있는 제 2 배터리의 캐소드 전류 콜렉터(1570)를 코어층(145)의 상부 표면에 쓰루홀(1580)을 통과시킴으로써 제공된다.

<97> 도전성 브리지들(1510, 1520 및 1530)은 스프레일렛 XCM-015와 같은 도전성은 잉크를 사용하여 형성된다. 도 17을 참조하여, 단계들(1720 및 1770)은 코어 구조 건설의 일부로서 이들 도전성 브리지들의 인쇄를 도시한다. 쓰루홀(1580 및 1590)은 또한, 도전성 잉크가 코어층(145)을 통해 전기 접속들을 생성하도록 허용하는 도 17의 코어층(145)에 도시된다.

<98> 도전성 브리지들(1510, 1520 및 1530)이 코어층(145)을 통해 배터리들을 상호접속하는 것과 관련하여 기술된다. 그러나, 당업자는 적충된 구조의 다양한 층들의 양단 및 이들을 통한 도전성 재료들을 유발하는 이들 원리들이 본 발명의 다른 전기적 구성요소들 및 다른 층들에 적용될 수 있음을 알 것이다.

#### 스마트 카드 처리

<100> 디스플레이를 구동하는 마이크로프로세서와 같은 마이크로프로세서를 이미 포함한 전자 구성요소들에 대한 접속의 경우에, 접촉 스마트 카드 칩은 구성으로부터 제거될 수 있다. 다시, 도 16a를 참조하여, 본 발명의 이 실시 예에서, 칩 플레이트(1610)는 칩 플레이트의 후면에 부착된 종래의 스마트 카드 마이크로프로세서(1620) 없이 판독기에 대한 표준 접촉 인터페이스를 제공하기 위하여 사용된다. 디스플레이 또는 다른 구성요소들을 제어하는데 사용된 마이크로프로세서는 외부 판독기들과 통신하기 위하여 스마트 카드 칩 상에 일반적으로 하우징된 소프트웨어뿐만 아니라 소자 제어를 위한 소프트웨어를 호스팅하는 이중 목적의 역할을 한다.

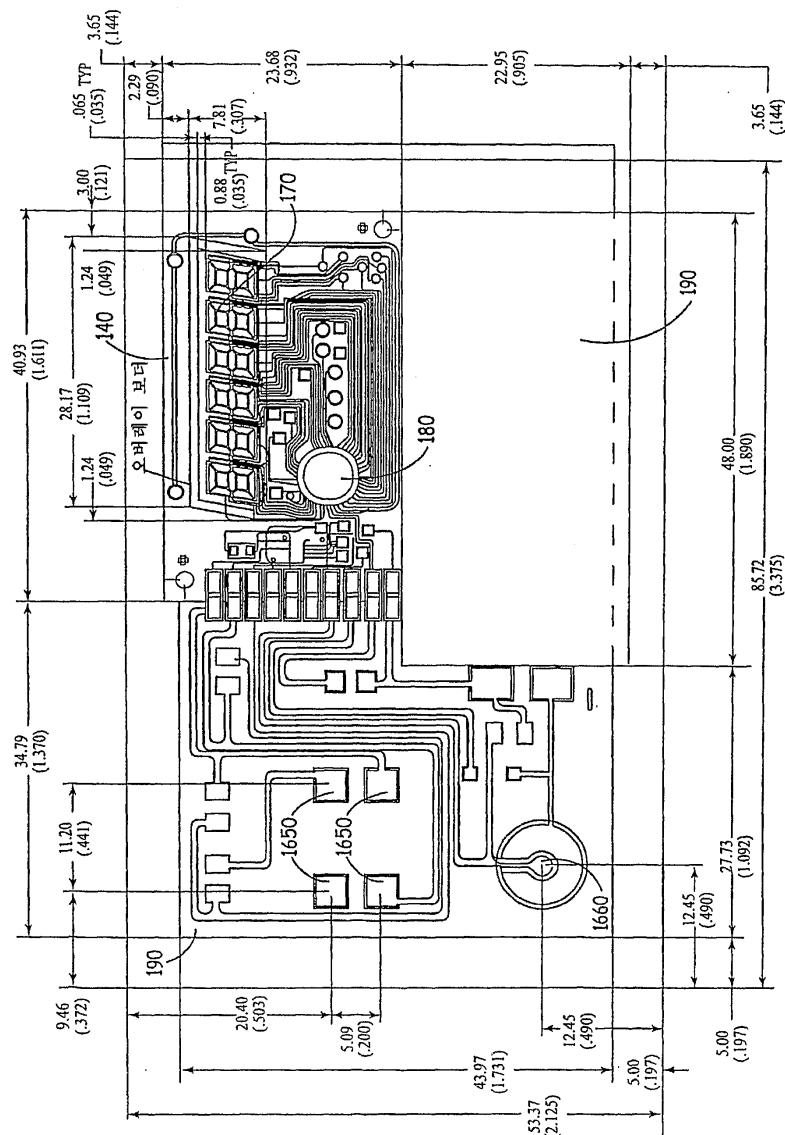

<101> 도 16b를 참조하여, IC(180)는 기존의 "스마트 카드들"에서 집적 회로들에 의해 현재 수행된 처리를 대체하기 위해 사용될 수 있다. 기존 스마트 카드들의 물리적 구조는 ISO 표준들(7810, 7816/1 및 7816/2)에 의해 지정된다. 일반적으로, 그 구조는 카드 상에 삽입되는 인쇄된 회로 및 집적 회로 칩(180)의 2개의 소자들로 이루어진다. 도 16b를 참조한다. 칩 플레이트(1610)는 IC(180)의 처리 기능들 또는 스위치(1660)로부터의 신호들이 칩 플레이트가 표준 판독기에 있을 때 플레이트(1610)로 도달하도록 허용하는 접촉들(1650)과 전기적으로 접속된다.

<102> 도 16b에 도시된 인쇄된 회로는, 전력 및 데이터에 대한 5개의 접속 지점들을 제공하는 ISO 표준 7816/3에 따른다. 칩 플레이트 회로는 카드 상에 제공된 리세스에 밀폐되어 고정되고, 회로 칩 상에서 베닝(burn)되고, 도전재료로 채워지고, 돌출한 접촉들로 밀봉된다. 인쇄된 회로는 기계 압력 및 정전기로부터 회로 칩을 보호한다. 칩과의 통신은 "칩 플레이트(chip plate)"를 통해 달성되며, 인쇄된 회로를 오버레이하는 접촉들을 포함한다.

<103> 칩 플레이트는 카드 수신기 디바이스(CAD) 또는 카드 판독기와 집적 회로 칩 사이에 접촉 패드들로서 역할한다. 집적 회로 칩은 논리를 제공하고 카드와 판독기 사이의 통신 차량으로서 기능한다. 칩은 또한, 적당한 암호 프로그램들뿐만 아니라 필요한 보안 프로그램들을 포함한다.

<104> 본 발명에 따르면, IC(180)는 디스플레이(170)를 구동한다. 그러나, 기존 "스마트 카드들(smart cards)"의 집적 회로 칩의 처리 기능들과 IC(180)의 디스플레이 처리 기능들을 조합하는 것이 바람직할 수 있다. 2개의 칩들이 단일 카드에 공동으로 존재할 수 있지만, 스마트 칩이 디스플레이 구동기 IC(180)와 같은 또 다른 칩과 통신하도록 요구되는 경우에는, 트레이스들의 세트를 통해 데이터 라인들이 접속된다. 기술된 바와 같이, 현재의 칩 플레이트들은 칩과 함께 사용하기 위한 6개 또는 8개의 접속들을 가지며, 이들은 전력 및 다른 통신 라인들을 포함한다.

<105> 2개의 분리된 IC들의 결점들을 회피하기 위하여, 디스플레이 구동기 IC(180)는 기존의 스마트 칩들과 동일한 기능 및 메모리를 포함하도록 설계될 수 있다. 스마트 카드 칩들 상의 현재 모든 프로그래밍은 IC(180)에 포함될 수 있고, 그에 의해 제 2 마이크로프로세서를 제거한다. 이를 달성하기 위하여, 스마트 카드 접촉들의 요건들에 따르는 칩 플레이트는 연성 최상부 시트(110)에서의 개구부에 탑재되지만, 연관된 IC가 존재하지

않는다. IC(180) 이 외의 다른 처리기가 요구되지 않는다. 표준 스마트 카드 프로토콜들에 대한 신호들이 IC(180)에 및 그로부터 흐르도록 허용하기 위하여 칩 플레이트로부터 IC(180) 및 배터리(190)까지 총(145), 제 2 커버층(130) 및/또는 플렉스 회로층(140)의 표면들 상에 적당한 접속들이 인쇄될 수 있다.

<106> 자기 스트라이프 에뮬레이터

기술된 바와 같이, 다양한 전기 구성요소들이 본 발명의 코어 구조에 포함될 수 있다. 한 적당한 구성요소들은 미국 특허 제4,701,601호에 기술된 디바이스와 같은 자기 스트라이프 에뮬레이터일 수 있다. 자기 스트라이프 에뮬레이터를 구비한 카드는 자기 스트라이프를 판독 및 인터페이싱하는 센서를 구비한 거래 단말들과 함께 사용될 수 있다. 카드는 자기 스트라이프 상에 통상적으로 인코딩된 정보에 대응하는 가변 자계를 발생시키기 위한 변환기(transducer)를 포함할 수 있다. 본 발명의 경우에, IC(180)는 메모리에 저장된 거래 데이터를 추출하고, 변환기에 출력 신호들을 공급한다. 변환기는 거래 단말의 센서에 의해 판독되는 거래 정보에 대응하는 가변 자계를 발생시킨다. 이것은 카드 응용들을 위한 자기 스트라이프 에뮬레이터를 포함하는 코어 구조를 생성한다.

<108> 생체측정 센서들

<109> 본 발명에 통합될 수 있는 또 다른 전기 구성요소가 다양한 생체측정 센서들 중 어느 하나이다. 일 실시예에서, 생체측정 센서는 지문 이미지 캡처를 지원하도록 설계된 마이크로-압력 센서이다. 이러한 하나의 적당한 센서의 예는 마이크로프로세서 기반 디바이스들에 삽입될 수 있는 캘리포니아 밀피타스의 피델리카 마이크로시스템즈 인코포레이티드(Fidelica Microsystems, Inc)로부터 피델리카 이미지 센서 모델 3002이다. 응용 가능한 호스트 구성요소들과 통합될 때, 센서는 사용자들이 다양한 전자 인증 보안 기능들을 수행할 수 있게 허용할 수 있다. 다시, 본 발명의 코어 구조는 카드 응용들에 요구되거나 바람직한 이러한 특징을 포함할 수 있다.

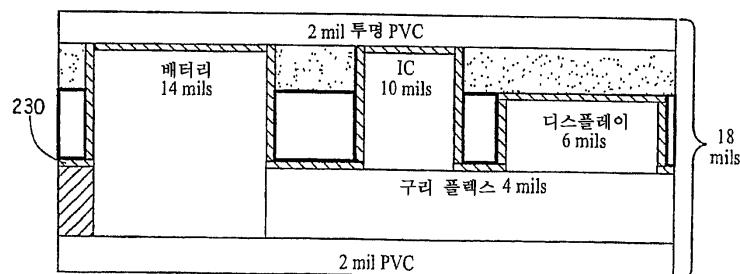

<110> 버퍼층들

<111> 상이한 구성요소들 및 막들의 가변 치수 성질로 인해, 및 결과로서 생긴 카드들에 대한 평탄의 ISO 요건들 및 개별 구성요소들의 상이한 예들 중에서 발생하는 변동들로 인해, 구조(100)의 조립은 버퍼층들을 포함한다. 이들 형성 가능한 층들은 다양한 구성요소들 중에서 균등화를 제공하고, 베이스 시트(150)의 외부로부터 최상부 시트(110)의 외부까지 측정될 때(도 2a 참조) 특정한 치수 "H"가 전자 코어 구조에서 달성될 수 있도록 허용한다.

<112> 접착제와 같은 흐름 가능한 버퍼 재료는 구조(100)에서 2개 이상의 층들 사이에 이용된다. 하기에 기술되는 바와 같이, 버퍼층들은 각각의 구성요소 및 막들의 임의의 생산 분량 내에서 발생하는 변동을 조정한다. 예를 들면, IC(180)의 높이는 불균일할 수 있거나 원하는 정규 치수를 벗어날 수 있지만 변동은 버퍼층들을 보상한다. 원하는 높이 치수 H는 다중층들에서 버퍼링함으로써 달성된다; 구조(100)의 층들의 각각이 하기와 같이 함께 적층될 때, 흐름 가능한 접착제층들은 초과 치수를 흡수하고, 다양한 구성요소들 및 층들의 각각에 대한 미달 치수를 채운다. 버퍼 응용 후에 사용된 넓 롤러들은 원하는 치수들을 확립하도록 돋는다. 각각의 다이 컷 층의 웹에서의 공동들은 초과 치수 소자들로부터 흐름 가능한 접착제를 흡수한다. 공동들은 일반적으로 IC, 배터리 및 디스플레이 셀과 같은 다양한 소자들을 수평화하도록 설계된다. 공동들이 소자들의 가변 치수들을 정확히 맞추도록 형성될 수 없기 때문에, 이들은 다양한 소자들 주위에 작은 공동들을 유발하는 약간 초과 크기이다. 흐름 가능한 버퍼 재료는 공동들을 채우고 균일한 구조를 제공한다.

<113> 열 적층 동안, 코어 구조의 막 층들을 구성하는데 사용된 수지들이 또한 흐른다. 다양한 소자들 주위에 형성된 공동들은 열 적층 처리 동안 흐르는 수지에 의해 채워진다. 수지가 미리 형성된 공동들로부터 보이드들을 채우기 때문에, 흐름 처리 동안 순실된 부피로 인한 카드 표면의 갈라짐들, 금힘들 또는 함몰들과 같은 수용할 수 없는 표면 결함들을 유발할 수 있다. 따라서, 흐름 가능한 버퍼 재료의 사용은 코어 형성 동안 발생하는 공동들을 미리 채우고, 그에 의해 이러한 결함들을 유발하는 부피 부족들을 제거한다.

<114> 주 버퍼층 및 부 버퍼층의 2개의 버퍼층들이 하기에 기술된다. 이들 버퍼층들은 1.0 내지 3.0mil 및 0.25 내지 1.0mils의 각각의 두께를 가질 수 있다. 양호한 두께들은 주 버퍼층들에 대해 2.5mils이고 부 버퍼층에 대해 .5 내지 1.0mils이다.

<115> 먼저, 주 버퍼층이 기술된다. 도 6과 관련하여, 구조(100)의 조립 동안, 연성 최상부 시트(110)가 제 1 커버층(120)에 적층되고, 제 1 커버층(120)은 제 2 커버층(130)에 적층되고, 그에 의해 최상부 조립층(210)을 형성한다. 베이스 조립층(220)은 도 6에 도시된 베이스 시트(150), 디스플레이 셀(160)과 디스플레이(170) 및 IC(180), 및 배터리(190)와 같이 복수의 소자들 및 층들을 함께 적층하여 형성된다. 이들 소자들은 최상부 조립 층(210) 및 베이스 조립층(220)의 원하는 두께를 달성하기 위해 넓 롤러들을 사용하여, 종래의 적층 기술들로

적층된다.

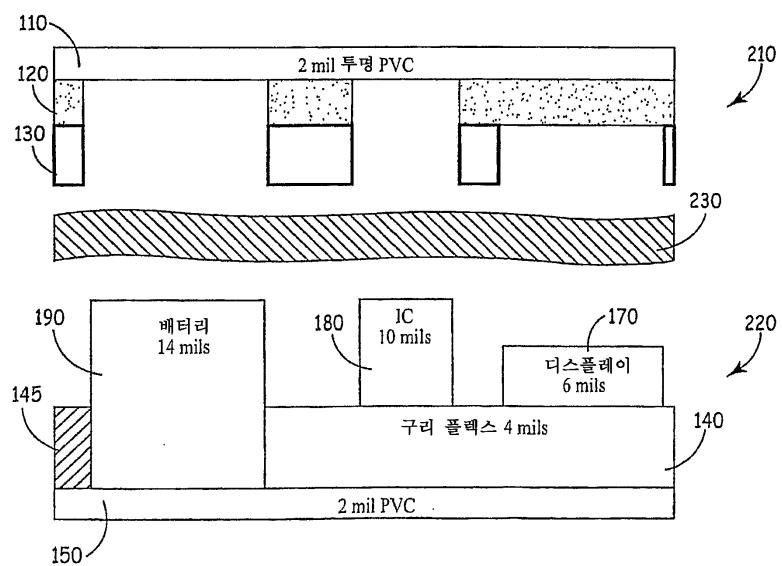

&lt;116&gt;

기술된 바와 같이, 원하지 않는 치수 변동들은 이를 층들에서 적층된 소자들에서 발생한다. 도 7을 참조하여, 주 베퍼층(230)은 변동들을 실질적으로 평준화하고 수용 가능한 치수를 달성하기 위해 최상부 조립층(210)과 베이스 조립층(220) 사이에 위치될 것이다. 주 베퍼층(230)은 도 8에 도시된 바와 같이, 최상부 조립층(210) 위에 흐르는 적층 접착제로 형성될 수 있다. 주 베퍼층(230)은 스크린, 스텐실, 패드 또는 플렉소그래픽 인쇄를 포함한 다양한 방법들에 의해 최상부 조립층(210)에 적용될 수 있다. 이들 인쇄 처리들은 최상부 조립층(210)의 윤곽들을 미러링(mirroring)하는 윤곽들을 갖는 플레이트로 달성될 수 있다. 플레이트는 최상부 조립층(210)의 리세스들에 접착제의 충분한 커버리지(coverage)를 공급하기 위하여 최상부 조립층(210)상의 대응하는 위치와 매칭된다. 따라서, 간단히 하기 위해 도 7이 균일한 두께의 베퍼층(230)을 도시하고 있지만, 상기 방법에 의해 이용된 이 층은, 흐름 가능한 재료의 공급원들이 공동들로 이주해야 하는 위치들에 더 많은 재료를 전달하기 위해 선택된 재료 두께 및 부피의 패턴을 가질 것이다. 주 베퍼층은 코어 형성 동안 형성된 보이드들 및 치수 불일치(disparity)들이 보상되고 채워지는 것을 보장하기 위해 충분한 베퍼 재료를 제공한다.

&lt;117&gt;

도 9를 참조하여, 최상부 조립층(210) 및 베이스 조립층(220)이 병합되고, 패터닝된 주 베퍼층(230)은 다양한 구성요소들의 초과 치수들을 흡수하고 미달 치수들을 채우고, 그에 의해 넓 롤러들에 의해 결정된 원하는 높이 치수를 달성하기 위하여 높이 분산들을 형성한다. 임의의 초과 베퍼 재료는 커버 시트들의 에지들에서 스며 나오도록 허용되며, 원하는 형상을 형성하기 위해 후속적으로 트리밍(trim)된다.

&lt;118&gt;

베퍼층들의 사용은 또한, 전자 코어 구조를 유발하는 원하는 기계적 세기를 제공할 수 있다. 다양한 소자들 및 공동들을 조립하기 위해 실질적 고체 구성을 제공함으로써, 결과로서 생긴 코어 구조는 매우 바람직한 딱딱함(stiffness) 및 기계적 세기를 나타낸다. 더욱이, 다양한 층들을 함께 고정하기 위한 베퍼층들의 사용이 상호 접속된 전자 회로들의 전기적 세기를 증가시킨다. 적당한 베퍼층 재료는 인쇄 처리들에 의해 그 응용을 허용하기 위해 원하는 접착성 또는 다른 물리적 특성들을 가져야 하며, 코어 구조층들을 함께 유지하는데 노력하도록 흐름 가능하고 경화 가능하여야 한다. 그러나, 베퍼 재료는 영구 접착제이어야 할 필요는 없다. 베퍼층 재료는 또한, 베퍼 재료가 용해된 상태에서 막층들 및 전기 구성요소들의 수지들과 호환 가능하도록 열 적층 처리 동안 PVC 또는 다른 층들 및 임의의 부가의 인쇄된 재료들과 혼합된다. 다양한 재료군들은 아크릴산염들, 우레탄들, 플라스티콜들, 폴리에스테르들, 또는 인쇄 및 경화 다음의 세기에 적당한 접착성의 다른 유사한 재료들과 같은 베퍼 재료로서 적당하다.

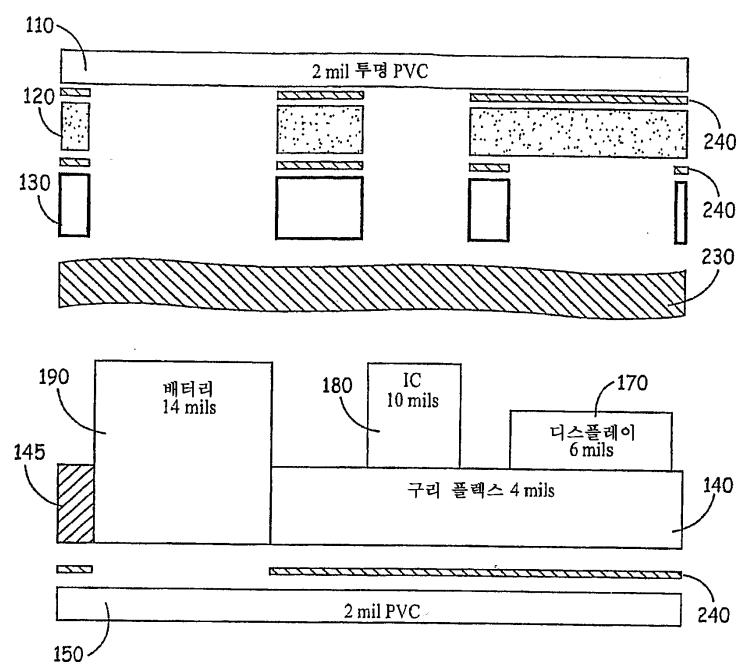

&lt;119&gt;

플렉스 회로층(140)에 접착된 주 베퍼층(230) 외에도, 복수의 부 베퍼층들(240)이 또한 도 10 및 도 11에 도시된 바와 같이, 다른 층들 사이에서 흐르고 접착될 수 있다. 이것은 원하는 높이 치수가 구조(100)에서의 다중층들에서 베퍼링을 보상함으로써 달성되도록 허용한다. 부 베퍼층들(240)은 또한 제조 동안 다양한 층들을 함께 접착하는 기능을 한다. 최종적으로 부 베퍼층들 및 중간 넓 롤러들은 주어진 구조가 기판의 최상부 또는 하부로부터 알려진 거리에서 재현 가능하게 배치되도록 허용한다. 이것은, 특정한 응용에 있어서, 종단 사용자가 코어 구조에서 삽입된 임의의 소자들에 접속하기 위하여 압연 또는 다른 처리들을 사용하는 것이 바람직한 경우에 중요할 수 있다.

&lt;120&gt;

다양한 구성요소들 및 층들의 높이 치수를 균등화하는 것 외에도, 주 베퍼층(230) 및 부 베퍼층들(240)은 다른 치수 문제들을 보정할 수 있다. 예를 들면, 적층될 층이 IC(180)에 맞추도록 다이 컷되면, 구조가 IC를 쉽게 수신하도록 허용하기 위하여 "초과 컷(over-cutting)"될 수 있다. 하나의 전자 코어 구조가 다른 구조에 발생하는 "초과 컷"의 변동은 IC 크기의 변동과는 별개이다. IC들의 형상이 수용 가능한 치수들로 형성될 수 있지만, 구조(100) 상의 배치는 가변될 수 있어서, 보상이 필요한 위치 변동들을 유발한다. 따라서, 칩이 구조 및 그 주위에 이용된 다이 컷 층에 탑재된 후, 공동이 그 주위에 형성될 수 있다. 이 경우에, 베퍼층들은 도 11에 도시된 바와 같이 IC의 높이 변동들에서만 채워지는 것이 아니라, IC(180) 주위의 공동 볼륨들(290)에도 또한 채워진다.

&lt;121&gt;

예 1 - 이산 구성요소 배치 및 다중 적층 회로들

&lt;122&gt;

상기 개시내용과 일관되게, 본 발명은, 코어 전자 구조를 형성하기 위해 함께 적층되는 도 6에 도시된 베이스층(220) 및 커버층(210)의 2개의 복합층들과의 구성에서 기술될 것이다.

&lt;123&gt;

전자 코어는 부분 레이아웃을 위한 적당한 구성에서 베이스 시트(150) 상에 필요한 구성요소들을 배치함으로써 구성된다. 베이스 시트는 열 적층 처리를 통해 외부층들에 적층되는 PVC 또는 다른 막이 될 수 있다. 베이스 시트의 두께는 .001 내지 .005인치들의 범위가 바람직할 것이며, .002 인치의 두께가 바람직하다. 다양한 구성요

소들은 압력 감도 접착제의 얇은 층으로 적소에 유지된다.

<124> 베이스 시트(150) 상에 배치된 구성요소들은 맴브레인 스위치 돔들, 배터리 및 디스플레이 셀을 포함한다. 초기 구성요소 배치는 수평화를 요구하는 다양한 높이들뿐만 아니라 경감 영역들(relief areas)의 이격을 결정한다. 디스플레이 셀 및 배터리 텁들의 기판 두께를 매칭하는 다이 컷층(145)을 미리 적층하는 것이 바람직하지만, 요구되는 것은 아니다. 기판의 표면은 돔들이 배치되는 스위치 기반 회로를 포함할 수 있다.

<125> 적층의 양호한 방법은 UV 방사, EB 방사 또는 열을 통해 경화하는 영구적인 적층 접착제들을 사용하는 것이다. 베이스층 적층은 높이를 설정하고 이 층의 잠재적 높이 변동을 감소시키는 넓 지점을 통해 강행될 수 있다.

<126> 코어는 동일한 평면 및 상면에 디스플레이 셀 접촉들, 배터리 텁들 및 스위치 접촉들로 이루어진다. 돔들은 스위치들 위에 배치될 수 있고, 본 기술 분야에 널리 알려진 접착 기술들을 사용하여 접착될 수 있다. 이것은 커버층(210)에 후속적으로 적층되는 베이스층(220)을 완성한다.

<127> 커버층(210)은 하부 상에 인쇄된 모든 필요한 접촉 회로들을 가지며, 이것은 베이스층(220) 상에 있는 스위치, 배터리 및 디스플레이 셀 전기 접촉들을 접촉할 것이다. 커버층은 디스플레이 높이, 칩 세트, 배터리 및 스위치 돔들의 윤곽들을 매칭하도록 설계된다. 커버층은 베이스층 또는 "구성요소층"의 지형(topography)을 매칭하기 위한 다이 컷들로 막들을 적층함으로써 3차원 형태로 결성될 수 있다. 커버층은 베이스층 상에 배치된 상이한 높이의 소자들의 수에 기초하여 하위층들의 최소수를 갖는다. 커버층은 코어에 삽입된 디스플레이가 시청되도록 허용하는 투명한 막들로 구성될 수 있다.

<128> 최종 조립 단계는 영구 적층 접착제를 사용하여 베이스층(220)과 커버층(210)을 적층하는 것이다. 흐름 가능한 접착제의 .001 내지 .002인치의 베퍼링층(230)은 커버층을 베이스층에 결합하도록 사용되고, 전체 구조는 접착제를 용해하기 전에 .018인치에서 설정된 고체 넓 지점을 통과한다. 접착제는 스크린 인쇄, 패드 인쇄, 시여 또는 스프레이를 통해 이용된다. 3차원 구조는 완전히 커버되어야 하며, 전기 접촉 영역들에는 접착제가 없어야 한다.

<129> 최종 적층 접착제는 영구적이고, 투명한 커버층을 통해 경화되는 UV 또는 EB와 같은 방사 경화된 접착제들의 군으로부터 선택될 수 있다. 대안적으로, 영구적인 열 용해가 이용될 수 있으며, 이것은 넓 지점을 통해 냉각된다. 열 용해는 완성된 카드를 생산하는 열 적층 단계 동안 환류(reflow)의 부가적 이점을 가진다. 모든 베퍼링들은, 다양한 층들이 영구적으로 용해되는 것을 방지함으로써 열 적층 처리를 방해하지 않는 접착제로 구성되어야 하며, 결과로서 생긴 카드는 ISO 명세들을 통과해야 한다. 응용에 적당한 하나의 이러한 접착제는 라드큐어 UV-170-SP(Radcure UV-170-SP)이다.

<130> 베이스 시트(150) 및 최상부 막(110)의 재료들은 PVC 또는 열 적층에 적당한 다른 플라스틱들로 구성된다. 대안적으로, 폴리비닐알코올(PVA)과 같은 열 밀봉 또는 다른 상용 열 밀봉 코팅들은 열 적층 동안 완성 표면들의 적당한 결합을 보장하기 위하여 최외부 표면들 상에 코팅될 수 있다.

#### 예 2 - 평면 회로 및 전기 접속들

<132> 또 다른 예에서, 베이스층(220)의 구성은 디스플레이 셀 및 배터리 구성요소들의 접촉 지점들과 매칭하고 스위치들에 대한 베이스를 포함하는 구조의 최상부 상에 전체 접속 회로를 인쇄함으로써 수정된다. 접속 회로와 구성요소들 사이의 전기 접속은 각각의 접속에 대한 접속 경로를 제공하기 위해 시여 바늘을 통해 제공된다. 나머지 구조는 예 1과 동일하게 남아 있다.

<133> 예 1 및 예 2는 전자 코어 내의 인쇄 회로의 내부 유연성을 기술한다. 전자 코어는 최종 조립에 앞서 회로 소자들을 인쇄하기 위해 5 내지 7개의 개별 표면들을 통상적으로 가질 것이다. 본 발명의 이 실시예는 코어 내의 회로를 적층하고, 필요한 회로들을 맞추도록 모든 이용 가능한 표면들을 사용하기 위한 능력을 제공한다. 이것은 정교한 회로들이 스마트 카드에 이용 가능한 영역 내에 포함되어야 할 때 유용하다. 이것은 종래의 단일 표면보다 5 내지 7배의 성능을 효과적으로 제공한다.

<134> 코어층들 사이의 전기 접속들은 층들을 통한 도전성 비아들의 도입을 통해 획득될 수 있다. 이 실행은 회로들이 접속될 레지스터에서의 각각 원하는 층을 통해 홀들을 드릴하거나 펀칭하고 쓰루-홀 회로 경로들을 제공하기 위하여 도전성 애폴시 또는 다른 재료로 홀들을 채움으로써 달성된다.

#### 예 3 - 삽입된 탄소/아연 배터리

<136> 기술된 바와 같이, 스마트 카드에 사용하기에 적당한 배터리들은 총 두께가 통상적으로 .012 내지

.016인치이다. 총 두께 중 .006 내지 .010인치는 배터리를 밀봉하기 위한 패키징막들로 구성된다. 이 예는 코어의 복잡성 및 전체 두께를 절감하는 배터리 패키징의 일부로서의 코어층들의 사용을 예시한다.

<137> 이 구성은 예 1에 도시된 베이스층(220)/커버층(210)에 기초한다. 베이스층 상에서, 배터리 애노드들 및 전류 콜렉터들은 제 2 막 PVC층(150)의 최상부에 침착된다. 개별적으로, 동일한 층 상에서, 캐소드들 및 전류 콜렉터들 또한 인쇄된다. 배터리층들의 총 두께는 디스플레이 높이와 매칭하는 .006인치이다. 2개의 분리된 셀들은 시스템으로부터 요구된 3V를 달성하도록 요구된다. 부착 회로는 다른 소자들에 직렬로 배터리들을 접속한다.

<138> 커버층(210)은 적층시 경감을 제공하기 위하여 배터리 전극들 위에 배출 영역(evacuated area)을 갖도록 구성된다. 최종 적층에 앞서, 배터리 구성을 완료하기 위해 웰에 배터리 전해질이 부가된다. 적층시, 전해질은 이를 활성화하기 위해 셀들을 습식시킨다.

#### 예 4 - 삽입된 리튬 배터리

<140> 리튬 배터리 화학의 사용은 셀당 2.8V의 이점을 가지며, 이것은 코어의 구성을 단순화한다. 그러나, 리튬 화학은 물과 리튬의 반응성으로 인해 건조 공간 환경에서 셀의 조립을 요구한다.

<141> 따라서, 이것은 코어 구조로의 통합에 앞서 배터리 구성요소의 미리 형성(pre-forming)을 요구한다. 이것은, .010인치의 두께인 코어 막에 애노드를 미리 형성하기 위하여 스파터링된 리튬 금속을 갖는 구리 박편 전류 콜렉터를 적층함으로써 달성된다. 코어 막은 배터리의 형상으로 다이 컷하며 웰을 형성한다. 그 후에 웰은 전해질 및 캐소드 재료로 채워지고, 캐소드 전류 콜렉터를 형성하는 구리 박편으로 밀봉된다. 결과로서 생긴 구조는 .010인치이며 .014인치의 총 두께를 가진 분리된 셀보다 더 많은 용량을 가진다.

<142> 상술된 배터리층은 한 표면 상에 애노드 접속과 대향쪽 상에 캐소드 접속을 가진다. 하부 전극에 대한 전기 접속은 회로를 하부 전극에 이끌어 생성된다. 최상부 전극에 대한 전기 접속은 막을 통해 비아를 제공하고 쓰루홀 기술들을 사용하여 백플레인에 접속함으로써 생성된다.

<143> 다른 예들로서, 커버층 및 베이스층들은 예 1에 기술된 접착제의 .001 내지 .002인치의 벼퍼층들을 사용하여 적층된다.

#### 예 5 - PVC층들

<145> 코어 구성은 다양한 막들을 사용하여 구성될 수 있다. 적당한 적층 접착제를 선택함으로써, 성공적인 열 적층은 모든 층들이 적층 처리 동안 막의 용해점에 도달하는 것을 요구하지 않는다. 대안적으로, 층들은 선택된 막의 용해점에 도달하고 적층 처리 동안 용해되는 막들로 구성될 수 있다. 폴리비닐염화물 및 폴리프로필렌과 같은 적당한 막들은 본 기술 분야에 널리 알려져 있다. 적층 처리는 층들이 흐르도록 하고 용해될 적당한 표면들을 제공하기 위하여, 적층 접착제들이 와플(waffle) 또는 다른 적당한 패턴으로 패턴 인쇄되는 것을 제외하고 일정하게 유지된다. 적층 처리는 다양한 층들을 수평하게 하기 위해 여전히 사용되지만, 접착제의 주 목적은 적층에 앞서 다양한 층들을 함께 유지하기 위한 것이다. 인쇄된 배터리의 경우에, 벼퍼층은 최종 적층에 앞서 배터리 전해질을 포함하기 위한 개스킷의 형성을 보증하기 위하여 배터리 주위의 연속층으로서 인쇄된다. 이러한 인쇄는 카드의 다른 영역들에서 패턴이 사용되는 경우에도 수행된다.

#### 결론

<147> 상기 예들은 본 발명의 인쇄 및 적층된 구조의 범위 및 유연성을 도시한다. 특히, 본 발명은, 다양한 금융 카드 및 다른 응용들의 지정된 전자 기능을 제공하고, 요구된 구성 접적도를 가지며, 완성층들이 표준들 및/또는 사용자 요건들에 의해 지정된 대로, 치수 요건들, 유연성 및 특정 응용의 다른 물리적 요건들과 일관되게 유지하면서 적용되도록 허용하는 전자 코어 구조를 효과적으로 생산하기 위해 사용될 수 있다. 당업자는 다른 구성요소들 및 구성들이 실시될 수 있고 본 발명의 범위 내에 있음을 알 것이다.

#### 부록 A

#### 스마트 카드 명세들

<150> ISO 7810 - 규정 조항에 규정된 식별 카드들에 대한 특성들 및 국제 교환을 위한 이러한 카드들의 사용을 기술한 일련의 표준들 중 하나. 이 국제 표준은 카드 재료들, 구성, 특성들 및 카드들의 4개의 크기들에 대한 치수들을 포함하는 식별 카드들의 물리적 특성들을 지정한다. 0.008mm(0.003인치)를 초과하지 않는 에지 버링(edge burring)에 대한 표준들을 포함한 은행 카드들에 대한 정규 치수, 표면 왜곡들 및 시그너처 패널들.

- <151> ISO/IEC 7811-1 식별 카드들- 기록 기술 -파트 1: 양각 ISO/IEC 7811의 이 부분은 규정 조항에 규정된 식별 카드들에 대한 파라미터들 및 국제 교환을 위한 이러한 카드들의 사용을 기술한 일련의 표준들 중 하나이다. ISO/IEC 7811의 이 부분은 식별 카드들 상의 양각된 문자들에 대한 요건들을 지정한다. 양각된 문자들은 명세표 발행기들(imprinters)의 사용에 의해 또는 비주얼 또는 기계 판독에 의해 데이터의 전달을 위해 의도된다. 인간 및 기계 양태들과 상태를 최소 요건들 모두를 고려한다.

- <152> ISO/IEC 7811-3 식별 카드들 - 기록 기술 - 파트 3: ID-1 카드들 상의 양각된 문자들의 위치

- <153> ISO 7812 & 7814 - 자기 스트라이프 재료의 위치 및 표면 프로파일

- <154> ISO 7813 식별 카드들 - 금융 거래 카드들은 금융 거래 카드들의 치수들이 0.76 + 또는 - 0.08mm(0.030 + 또는 -.0003인치) 두께, 85.47mm(3.375인치) 넓이 및 54.03mm(2.127인치) 높이이어야 함을 지정한다.

- <155> ISO 7816-1 식별 카드들- 접촉들을 가진 접적 회로(들) 카드들 - 파트 1: 물리적 특성들은 접촉들을 가진 접적 회로(들) 카드들의 물리적 특성들을 지정한다. 이것은 ID-1 카드 타입의 식별 카드들에 적용하며, 식별에 대한 미국 국제 표준에 지정된 바와 같이, 양각 및/또는 자기 스트라이프를 포함할 수 있다.

- <156> ISO/IEC 7816-2 정보 기술 - 식별 카드들 - 접촉들을 가진 접적 회로(들) 카드들 - 파트 2: 접촉들의 치수들 및 위치. ID-1 카드 타입의 접적 회로(들) 카드들 상의 접촉들의 각각에 대한 치수들, 위치들 및 할당을 지정한다. ISO/IEC 7816-1과 결합하여 사용하기 위한 것임.

- <157> ISO/IEC 7816-3 정보 기술 - 식별 카드들 - 접촉들을 가진 접적 회로(들) 카드들 - 파트 3: 전자 신호들 및 전송 프로토콜들은 접적 회로(들) 카드와 단말과 같은 인터페이스 디바이스 사이의 정보 교환, 신호 구조들 및 전력을 지정한다. 이것은 또한, 신호율들, 전압 레벨들, 전류값들, 패리티 규정, 동작 절차, 전송 메커니즘들 및 카드와의 통신을 커버한다.

- <158> ISO 14443-1 - 식별 카드들 - 표준을 전개한 접근(RF) 접적 회로 카드들 - 파트 1: 물리적 특성들은 접근 카드들(PICCs)의 물리적 특성들을 지정한다. 이것은 결합 디바이스의 근처에서 동작하는 카드 타입 ID-1의 식별 카드들에 적용한다. 이 표준은 ISO/IEC 14443의 나중 부분들과 결합하여 사용되어야 한다. 전자 초안을 획득하기 위해서는: 글로벌 엔지니어링 도큐먼트, 인코포레이티드,<http://www.global.ihs.com>.

- <159> ISO 14443-2 식별 카드들 - 표준을 전개한 접근 접적 회로 카드들 - 파트 2: 무선 주파수 인터페이스 및 파라미터들은 접근 카드와 접근 결합 디바이스 사이의 무접촉 인터페이스의 2개의 타입의 전기적 특성들을 기술한다. 그 외에도, 전력 및 양방향 통신 모두를 포함한다. 접근 결합 디바이스들(PCDs)과 접근 카드들(PICCs) 사이의 양방향 통신 및 전력을 제공하기 위해 필드들의 특성들을 지정한다. ISO/IEC 14443의 이러한 파트는 ISO/IEC 14443의 다른 파트들과 결합하여 사용되어야 한다. ISO/IEC 14443의 이러한 파트는 결합 필드들을 발생시키는 수단도 전자기 방사 및 인간 노출 조정과의 순응 수단도 지정하지도 않으며, 이것은 국가에 따라 가변될 수 있다.

- <160> ISO 14443-3 - 식별 카드들 - 표준을 전개한 접근 접적 회로 카드들 - 파트 3: 전자 신호들 및 전송 프로토콜들

- <161> ISO 14443-3 - 식별 카드들 - 표준을 전개한 접근 접적 회로 카드들 - 파트 4: 보안 특징들은 (a) 접근 결합 디바이스(PCD)의 필드를 입력하는 접근 카드들(PICCs)에 대한 폴링; (b) PCDs와 PICCs 사이의 통신의 초기 단계 동안에 사용된 바이트 포맷, 프레임 및 타이밍; (c) 요청 명령 컨텐트에 대한 초기 요청 및 응답; (d) 여러 PICCs(충돌방지) 중에서 하나의 PICC를 지정하고 이와 통신하는 방법; (e) PCD와 PICC 사이의 통신들을 초기화 하기 위해 요구되는 다른 파라미터들; 및 (f) 응용 기준에 기초하여 여러 PICCs 중에서 하나의 PICC의 선택을 용이하게 하고 속도를 증가시키기 위한 선택적 수단.

- <162> ISO/IEC 10373 식별 카드들 - 테스트 방법들

- <163> ISO/IEC 7816-4 정보 기술 - 식별 카드들 - 접촉들을 가진 접적 회로(들) 카드들 - 파트 4: 교환을 위한 내부 산업 명령들은 무접촉 환경의 특별한 요구들을 특징짓는 반이중 블록 전송 프로토콜을 지정하고, 프로토콜의 활성 및 비활성 시퀀스를 규정한다. ISO/IEC 14443의 이 파트는 ISO/IEC 14443의 다른 파트들과 결합하여 사용되도록 의도되며, 타입 A 및 타입 B의 접근 카드들에 적용 가능하다.

- <164> ISO/IEC 7816-5 식별 카드들 - 접촉들을 가진 접적 회로(들) 카드들 - 파트 5: 응용 식별자들에 대한 넘버링 시스템 및 등록 절차

- <165> ISO/IEC 7816-6 식별 카드들 - 접촉들을 가진 접적 회로(들) 카드들 - 파트 6: 내부 산업 데이터 요소들

- <166> ISO 8583:1987 은행 카드 발원 메시지들 - 교환 메시지 명세들 - 금융 거래들에 대한 컨텐트

- <167> ISO 8583:1993 금융 거래 카드 발원 메시지들 - 교환 메시지 명세들

- <168> ISO/IEC 8825-1 정보 기술 - ASN.1 인코딩 규칙들: 기본 엔코딩 규칙들(BER)의 명세, 카논 인코딩 규칙들(CER) 및 구분된 인코딩 규칙들(DER)

- <169> ISO/IEC 8859 정보 처리 - 8 비트 단일-바이트 코딩된 그래픽 문자 세트들

- <170> ISO 9362 뱅킹 - 뱅킹 전기통신 메시지들 - 은행 식별자 코드들

- <171> ISO 9564-1 뱅킹 - PIN 관리 및 보안 - 파트 1: ATM 및 POS 시스템들에서 온라인 PIN 핸들링에 대한 기본 원리들 및 요건들

- <172> ISO 9564-3 뱅킹 - PIN 관리 및 보안 - 파트 3: ATM 및 POS 시스템들에서 오프라인 PIN 핸들링에 대한 요건들

- <173> ISO/IEC 9796-2:2002 정보 기술 - 보안 기술들 - 메시지 복구를 제공하는 디지털 시그너처 방식들 - 파트 2: 정수 인수분해 기반 메커니즘들

- <174> ISO/IEC 9791-1 정보 기술 - 보안 기술들 - 메시지 인증 코드들 - 파트 1: 블록 암호를 사용한 메커니즘들

- <175> ISO/IEC 10116 정보 기술 - 보안 기술들 - n 비트 블록 암호에 대한 폐라션(peration)의 모드들

- <176> ISO/IEC 10118-3 정보 기술 - 보안 기술들 - 해시 함수들- 파트 3: 전용 해시 함수들

- <177> ISO 11568-2:1994 뱅킹 - 키 관리(소매) - 파트 2: 대칭 암호들에 대한 키 관리 기술들

- <178> ISO 13491-1 뱅킹 - 보안 암호 디바이스들(소매) - 파트 1: 개념들, 요건들 및 평가 방법들

- <179> ISO 13616 뱅킹 및 관련 금융 서비스들 - 국제 은행 계좌 번호(IBAN)

- <180> ISO 16609 뱅킹 - 대칭 기술들을 사용한 메시지 인증에 대한 요건들

- <181> ISO 639-1 언어들의 이름들의 표현을 위한 코드들 - 파트 1: 알파-2 코드

- <182> 주지: 이 표준은 ISO에 의해 계속 개선된다. ISO 639-1:1988에 대한 부가들/변경들: 언어들의 이름들의 표현에 대한 코드들은 <http://lcweb.loc.gov/standards/iso639-2/codechanges.html>에서 이용 가능하다.

- <183> ISO 3166 국가들의 이름들의 표현들을 위한 코드들 및 통화들 및 편드들의 표현을 위한 하위분할 ISO 4217 코드들

- <184> FIPS 180-2 보안 해시 표준

### 도면의 간단한 설명

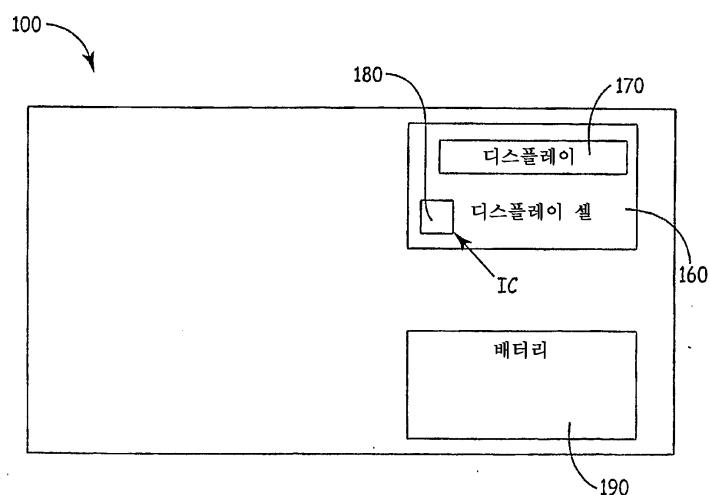

- <26> 도 1은 디스플레이 셀 구성요소들의 개략적인 단면 측면도.

- <27> 도 2a는 디스플레이 셀 및 배터리를 통합하는 본 발명의 구조의 개략적인 단면 측면도.

- <28> 도 2b는 디스플레이 셀을 통합하는 본 발명의 구조의 개략적인 상면도.

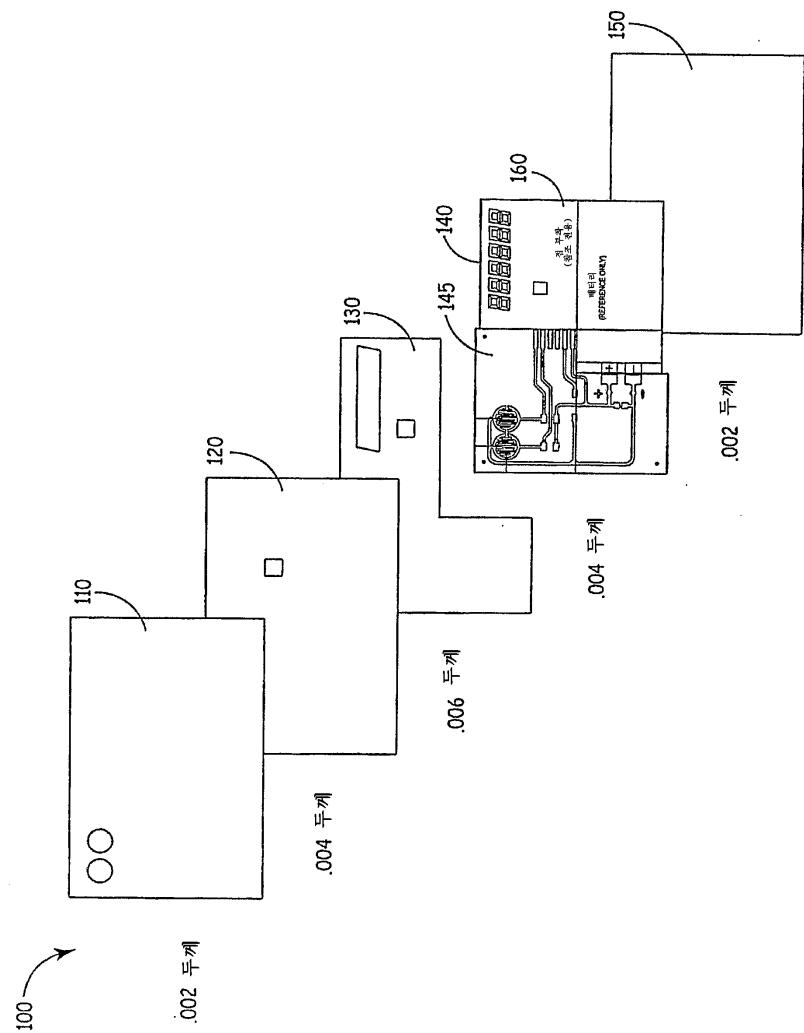

- <29> 도 3은 디스플레이 셀을 통합하는 본 발명의 한 구조의 개략적인 전개도.

- <30> 도 4는 상호 접속 회로 베어링층들(140 및 145)과 미리 패키징된 배터리를 통합하는 본 발명의 한 구조의 개략적인 상면도.

- <31> 도 5는 디스플레이 셀 및 인쇄된 배터리를 통합하는 본 발명의 또 다른 구조의 개략적인 전개도.

- <32> 도 6은 도 2a와 같이 본 발명의 부분 조립된 구조의 개략적인 단면 측면도.

- <33> 도 7은 최상부 조립층과 베이스 조립층 사이에 도시된 주 베퍼층을 가진 도 2a와 같이 본 발명의 부분 조립된 구조의 개략적인 단면 전개된 측면도.

- <34> 도 8은 최상부 조립층에 적용된 도시된 주 베퍼층을 가진 도 2a와 같이 본 발명의 부분 조립된 구조의 개략적인 단면 전개된 측면도.

- <35> 도 9는 주 벼페총을 통합하는 도 2a와 같이 본 발명의 조립된 구조의 개략적인 단면 전개된 측면도.

- <36> 도 10은 구조의 층들 사이에 도시된 주 벼페총 및 부 벼페총들을 가진 도 2a와 같이 본 발명의 부분 조립된 구조의 개략적인 단면 전개된 측면도.

- <37> 도 11은 주 벼페총 및 부 벼페총들을 통합하는 도 2a와 같이 본 발명의 조립된 구조의 개략적인 단면 측면도.

- <38> 도 12는 도 2b와 같이 디스플레이 셀(160)의 개략적인 상면도.

- <39> 도 13은 본 발명의 전기화학 셀들의 개략도.

- <40> 도 14는 전기화학 셀의 단면도.

- <41> 도 15a 및 도 15b는 본 발명의 2개의 전기적으로 상호접속된 전기화학 셀들의 개략도들.

- <42> 도 16a는 스마트 카드에 대한 종래의 칩 플레이트 구조의 개략도.

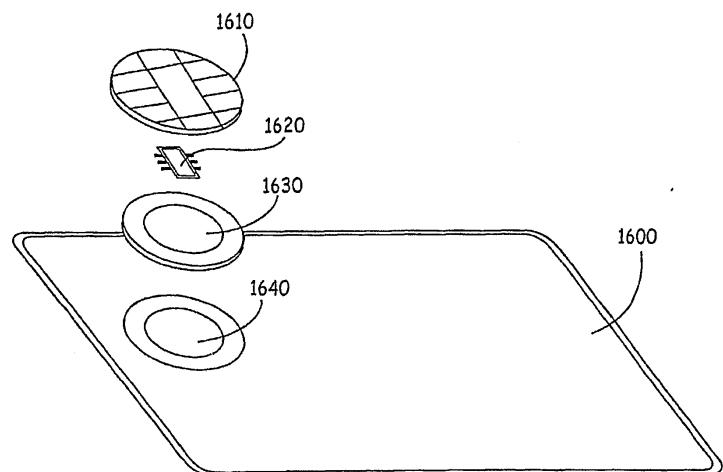

- <43> 도 16b는 디스플레이 및 IC 구성요소들의 합동을 스마트 카드에 제공하기 위하여 본 발명의 한 실시예에서 전자 코어에 사용된 회로의 화보 평면도.

- <44> 도 17은 하나 이상의 배터리를 통합하고 배터리 상호접속을 제공하는 본 발명의 실시예의 또 다른 구조의 개략적인 전개도.

## 도면

### 도면1

## 도면2a

## 도면2b

도면3

도면4

## 도면5

## 도면6

## 도면7

도면8

도면9

도면10

도면11

도면12

도면13

## 도면14

종래기술

## 도면15a

## 도면15b

도면16a

도면16b

## 도면17