(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5902548号

(P5902548)

(45) 発行日 平成28年4月13日(2016.4.13)

(24) 登録日 平成28年3月18日(2016.3.18)

|                          |                      |

|--------------------------|----------------------|

| (51) Int.Cl.             | F 1                  |

| HO 1 L 21/336 (2006.01)  | HO 1 L 29/78 6 1 8 A |

| HO 1 L 29/786 (2006.01)  | HO 1 L 29/78 6 2 7 F |

| HO 1 L 21/8242 (2006.01) | HO 1 L 29/78 6 2 7 Z |

| HO 1 L 27/108 (2006.01)  | HO 1 L 29/78 6 1 8 Z |

| HO 1 L 21/8247 (2006.01) | HO 1 L 29/78 6 2 6 C |

請求項の数 2 (全 44 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2012-105587 (P2012-105587)  | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成24年5月7日(2012.5.7)           | (72) 発明者  | 野田 耕生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2012-253331 (P2012-253331A) | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成24年12月20日(2012.12.20)       | (72) 発明者  | 本田 達也<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日        | 平成27年4月24日(2015.4.24)         | (72) 発明者  | 関根 祐輔<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2011-106054 (P2011-106054)  |           |                                                |

| (32) 優先日     | 平成23年5月11日(2011.5.11)         |           |                                                |

| (33) 優先権主張国  | 日本国(JP)                       |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に第1の絶縁膜を形成し、前記第1の絶縁膜上に第2の絶縁膜を形成し、前記第1の絶縁膜上および前記第2の絶縁膜上に100以上600以下の基板温度で酸化物半導体膜を成膜し、前記酸化物半導体膜を成膜した後、250以上650以下の温度で加熱処理を行い前記酸化物半導体膜上に第3の絶縁膜を成膜し、前記第3の絶縁膜上にゲート電極を形成し、前記第1の絶縁膜は、上面の高さが前記第2の絶縁膜の上面の高さと概略一致する領域を有し、前記第1の絶縁膜は、前記酸化物半導体膜に酸素を供給することができる機能を有し、前記第2の絶縁膜は、酸素の拡散を抑制することができる機能を有し、前記第2の絶縁膜は、前記ゲート電極と重ならない領域を有することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、前記酸化物半導体膜は、In、SnおよびZnを含むことを特徴とする半導体装置の作製方法。

10

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、酸化物半導体を用いたトランジスタなどの半導体素子を含む半導体装置およびその作製方法に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光表示装置、および電子機器は全て半導体装置である。

**【背景技術】****【0003】**

液晶表示装置に代表されるように、ガラス基板などに形成されるトランジスタの多くは非晶質シリコン、多結晶シリコンなどによって構成されている。非晶質シリコンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応することができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガラス基板の大面積化には適していないという欠点を有している。

**【0004】**

シリコンを用いたトランジスタのほかに、近年は酸化物半導体を用いてトランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、In-Ga-Zn-O系酸化物を用いてトランジスタを作製し、表示装置の画素のスイッチング素子などに用いる技術が特許文献1および特許文献2で開示されている。

**【0005】**

酸化物半導体膜を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較すると高い電界効果移動度を有するため表示装置の性能を著しく向上させることができると期待されている。

**【0006】**

一方で、トランジスタに高い電界効果移動度を要求する半導体装置に関しては、多結晶シリコンや単結晶シリコンを用いたトランジスタが用いられることが多い。酸化物半導体を用いたトランジスタを表示装置以外の半導体装置に用いる場合、多結晶シリコンや単結晶シリコンを用いたトランジスタ並に高い電界効果移動度を要求されることがある。

**【0007】**

高い電界効果移動度を有するIn-Sn-Zn-O系酸化物を用いたトランジスタが開示されている（非特許文献1参照。）。

**【先行技術文献】****【特許文献】****【0008】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【非特許文献】****【0009】**

【非特許文献1】Eri Fukumoto, Toshiaki Arai, Naruhiko Morosawa, Kazuhiko Tokunaga, Yasuhiko Terai, Takashige Fujimori and Tatsuya Sasaoka, 「High Mobility Oxide Semiconductor TFT for Circuit Integration of AM-OLED」、IDW'10 p631-p634

**【発明の概要】****【発明が解決しようとする課題】****【0010】**

トランジスタに高い電界効果移動度を要求する半導体装置にも酸化物半導体を用いたトランジスタに高い電界効果移動度を要求する半導体装置にも酸化物半導体を用いたトランジ

10

20

30

40

50

ンジスタを適用できる可能性がある。

【0011】

しかしながら、酸化物半導体を用いたトランジスタは、熱バイアス試験（BT試験）や光バイアス試験などにより電気的特性の変動が生じることがあり、信頼性が十分とは言い難い。

【0012】

そこで、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供することを課題の一とする。

【0013】

また、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有するトランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供することを課題の一とする。 10

【課題を解決するための手段】

【0014】

本発明の一態様であるトランジスタに用いる酸化物半導体は、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む。

【0015】

また、トランジスタの作製工程において、近接の絶縁膜または／およびイオン注入により酸化物半導体へ酸素が供給され、キャリア発生源となる酸素欠損を低減する。

【0016】

また、トランジスタの作製工程において、酸化物半導体を高純度化し、キャリア発生源となる水素濃度を極めて低くする。 20

【0017】

本発明の一態様であるトランジスタの作製方法を以下に示す。

【0018】

まず、基板表面に吸着する水素などの不純物を低減する処理を行い、次に下地絶縁膜を成膜し、次に酸化物半導体膜を成膜し、次に第1の加熱処理を行う。好ましくは、下地絶縁膜は、加熱処理により酸素を放出する絶縁膜である。なお、基板表面が十分に清浄である場合、基板表面に吸着する不純物を低減する処理を行わなくても構わない。 30

【0019】

基板表面に吸着する不純物を低減する処理として、例えばプラズマ処理、加熱処理または薬液処理を行う。好ましくはプラズマ処理を行う。プラズマ処理は、具体的には希ガス（ヘリウム、ネオン、アルゴン、クリプトン、キセノンなど）、酸素または窒素を含む雰囲気においてプラズマを生成し、基板に対してバイアス電圧を印加することで基板表面の処理を行えばよい。基板表面の不純物を低減することにより、基板と下地絶縁膜との界面準位密度を低減できる。該界面準位は、トランジスタのしきい値電圧の変動の原因となりうる。そのため、前述した界面準位密度を低減することで、基板面内におけるトランジスタのしきい値電圧のばらつきや、信頼性の低下を防止することができる。

【0020】

基板表面に吸着する不純物を低減する処理を行った後、大気暴露せずに下地絶縁膜を成膜すると好ましい。こうすることで、大気暴露により基板表面に不純物が再吸着することを防止できる。 40

【0021】

下地絶縁膜として、加熱処理により酸素を放出する絶縁膜を設けることにより、酸化物半導体膜中に生じる酸素欠損を、後に行う加熱処理によって補償することができる。酸化物半導体膜中の酸素欠損はキャリア発生源となるため、得られるトランジスタのしきい値電圧を変動させる要因となりうる。

【0022】

また、加熱処理により酸素を放出する下地絶縁膜を設けることにより、下地絶縁膜と酸化物半導体膜との界面準位密度を低減することができる。該界面準位は、得られるトランジ 50

スタの動作に関連して生じる電荷をトラップする事があるため、トランジスタの信頼性を低下させる原因となりうる。

#### 【0023】

なお、下地絶縁膜は平坦性を有することが好ましい。具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、さらに好ましくは0.1nm以下とする。下地絶縁膜に対し、化学機械研磨(CMP:Chemical Mechanical Polishing)処理などの平坦化処理を行ってもよい。下地絶縁膜が平坦性を有することで、下地絶縁膜と酸化物半導体膜との界面状態が良好となるため、得られるトランジスタの電界効果移動度が向上し、かつしきい値電圧の変動も低減できる。

#### 【0024】

酸化物半導体膜は、In-Al-Sn-Zn-O系材料、In-Sn-Zn-O系材料、In-Al-Zn-O系材料、Zn-Sn-O系材料などを用いる。特に、In-Sn-Zn-O系材料を用いると、高い電界効果移動度および高い信頼性を有するトランジスタが得られるため好ましい。

#### 【0025】

なお、酸化物半導体膜は基板加熱しつつ成膜すると、得られるトランジスタの電界効果移動度が向上するため好ましい。酸化物半導体膜の成膜時における基板加熱温度は、100以上600以下、好ましくは150以上550以下、さらに好ましくは200以上500以下とする。酸化物半導体膜はスパッタリング法を用いて成膜すると好ましい。

10

#### 【0026】

なお、酸化物半導体膜は、2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上のバンドギャップを有する。酸化物半導体膜が上記の範囲のバンドギャップを有することにより、オフ電流の極めて小さいトランジスタを得ることができる。

#### 【0027】

酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

#### 【0028】

好ましくは、酸化物半導体膜は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

20

#### 【0029】

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜は、非晶質相に結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

30

#### 【0030】

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

40

#### 【0031】

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形

50

成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、C A A C - O S 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【 0 0 3 2 】

C A A C - O S 膜に含まれる結晶部の c 軸は、C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、C A A C - O S 膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、C A A C - O S 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

10

#### 【 0 0 3 3 】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

#### 【 0 0 3 4 】

酸化物半導体膜の成膜後、第1の加熱処理を行うと好ましい。第1の加熱処理は、減圧雰囲気（10Pa以下）、不活性雰囲気（窒素、希ガスなどの不活性ガスからなる雰囲気）または酸化性雰囲気（酸素、オゾン、亜酸化窒素などの酸化性ガスを10ppm以上含む雰囲気）において、250以上650以下、好ましくは300以上600以下の温度で行う。

20

#### 【 0 0 3 5 】

第1の加熱処理により、酸化物半導体膜中の水素などの不純物濃度を低減することができる。または下地絶縁膜と酸化物半導体膜との界面状態を良好にすることができる。酸化物半導体膜を成膜してから第1の加熱処理を行うため、下地絶縁膜から放出される酸素が外方拡散していくことを防止できる。なお、不活性雰囲気または減圧雰囲気で加熱処理を行った後、温度を下げずに雰囲気を変え、酸化性雰囲気での加熱処理を行っても構わない。このような方法で加熱処理を行うことで、不活性雰囲気または減圧雰囲気にて酸化物半導体膜から不純物を低減し、その後、酸化性雰囲気にて不純物の除去時に生じた酸素欠損を低減することができる。

#### 【 0 0 3 6 】

なお、加熱処理、成膜には、不純物の少ないガスを用いる。特に水分の含有の少ないガスを用いると好ましい。具体的には、露点が-70以下のガスを用いればよい。

30

#### 【 0 0 3 7 】

第1の加熱処理を行った後、酸化物半導体膜を加工して島状にする。酸化物半導体膜の加工はフォトマスクを用いてレジストマスクを形成し、ドライエッティング法またはウェットエッティング法によってレジストマスクの形成部以外をエッティングすればよい。このような加工工程をフォトリソグラフィ工程と呼ぶ。

#### 【 0 0 3 8 】

次に、導電膜を成膜し、フォトリソグラフィ工程などによって加工して酸化物半導体膜と少なくとも一部が接するソース電極およびドレイン電極を形成する。

#### 【 0 0 3 9 】

40

次に、ゲート絶縁膜および導電膜を順に成膜し、該導電膜をフォトリソグラフィ工程などによって加工して酸化物半導体膜と重疊するゲート電極を形成する。ゲート絶縁膜として、加熱処理により酸素を放出する絶縁膜を用いると好ましい。

#### 【 0 0 4 0 】

次に、第2の加熱処理を行う。第2の加熱処理は第1の加熱処理と同様の条件で行えばよい。第2の加熱処理を行うことで、下地絶縁膜およびゲート絶縁膜から酸素が放出され、酸化物半導体膜中の酸素欠損を低減できる。また、下地絶縁膜と酸化物半導体膜との界面準位密度、酸化物半導体膜とゲート絶縁膜との界面準位密度を低減することができるため、得られるトランジスタの電界効果移動度を高め、しきい値電圧のばらつきを低減させ、かつ信頼性を向上させることができる。

50

**【0041】**

以上 の方法で、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ信頼性の高い酸化物半導体を用いたトランジスタを作製することができる。

**【0042】**

なお、トランジスタを覆って層間絶縁膜を設けると好ましい。層間絶縁膜を設けることにより、下地絶縁膜およびゲート絶縁膜から放出される酸素がトランジスタから外方拡散していくことを防止できる。層間絶縁膜を設ける場合、層間絶縁膜を成膜した後に第2の加熱処理を行ってもよい。

**【0043】**

トランジスタは、好ましくはトップゲート構造とする。即ち、酸化物半導体膜よりもゲート電極を後から形成する構造とすると好ましい。トップゲート構造を採用することで、ゲート電極をマスクに自己整合的にチャネル領域、ソース領域およびドレイン領域を有する酸化物半導体膜を形成することができる。ゲート電極とソース領域およびドレイン領域との重なりがほとんど生じないため、寄生容量を小さくするとともにトランジスタを微細化することができる。また、ゲート電極をマスクに用いることで、チャネル領域、ソース領域およびドレイン領域を形成するためにフォトマスクを必要とせず、工程を簡略化できる。なお、ボトムゲート構造を除外するものではない。

10

**【0044】**

このようにして得られたトランジスタは、高い電界効果移動度を有し（例えば、電界効果移動度が $31 \text{ cm}^2 / \text{V s}$ 以上）、しきい値電圧のばらつきが小さく、高い信頼性を有し（例えば、マイナスB T試験によるしきい値電圧の変動幅が1V以下）、かつオフ電流を極めて小さくできるため（例えば、チャネル長が $3 \mu\text{m}$ 、かつ基板温度が $85^\circ\text{C}$ のときのチャネル幅が $1 \mu\text{m}$ 当たりのオフ電流が $10 \text{ zA}$ 以下）、これまで実現が困難であった高性能の半導体装置を作製することが可能となる。

20

**【発明の効果】****【0045】**

本発明の一態様によって、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供することができる。

**【0046】**

また、このようにして得られたトランジスタを用いて、これまで実現が困難であった高性能の半導体装置を提供することができる。

30

**【図面の簡単な説明】****【0047】**

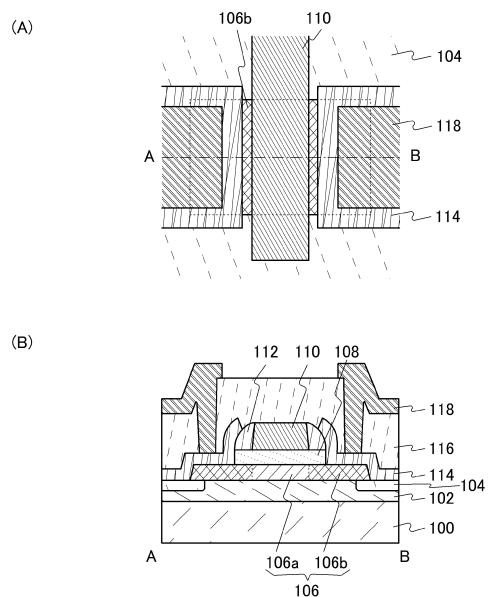

【図1】本発明の一態様に係るトランジスタの上面図および断面図。

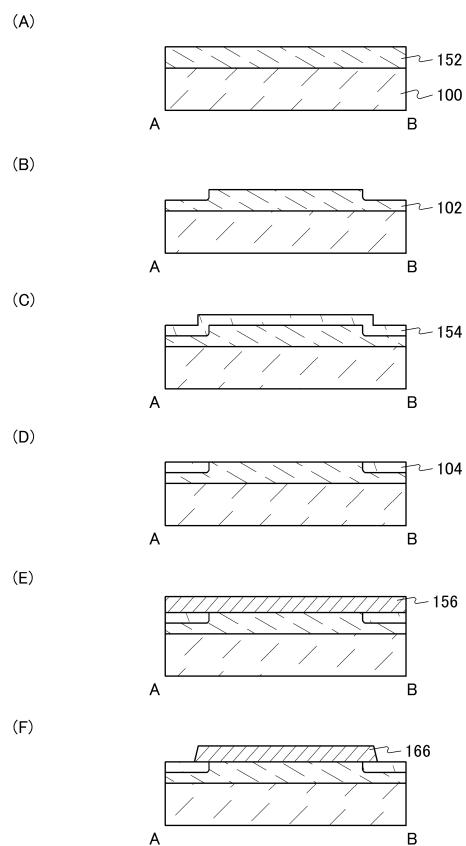

【図2】図1に示すトランジスタの作製方法を説明する図。

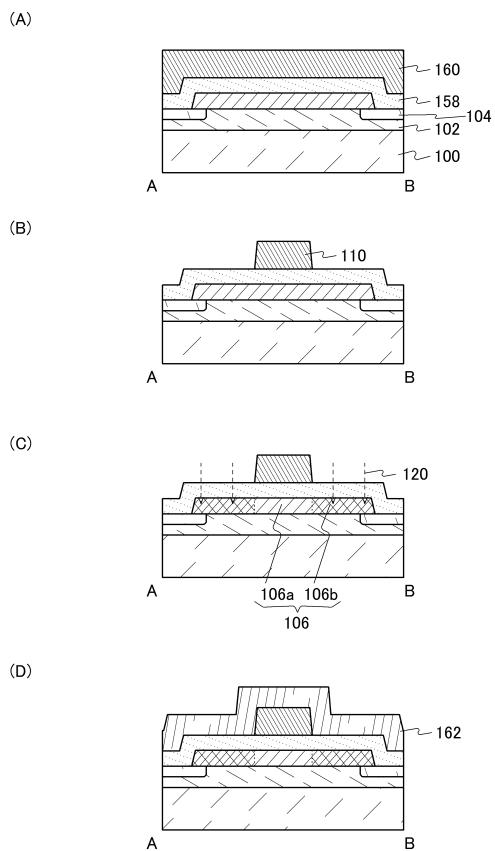

【図3】図1に示すトランジスタの作製方法を説明する図。

【図4】図1に示すトランジスタの作製方法を説明する図。

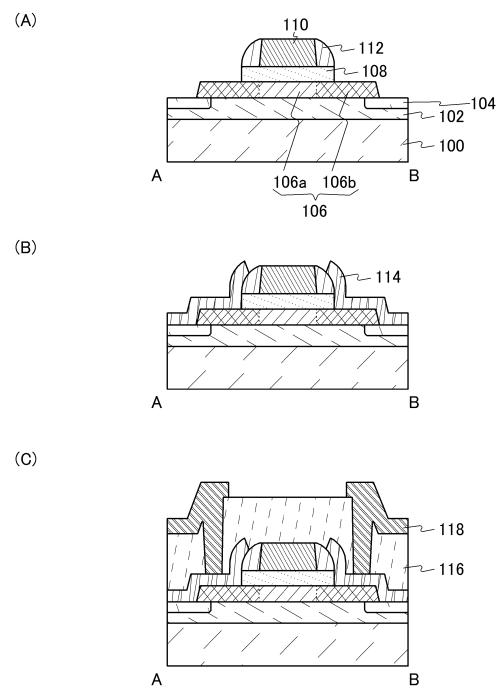

【図5】本発明の一態様に係るトランジスタの上面図および断面図。

【図6】図5に示すトランジスタの作製方法を説明する図。

【図7】図5に示すトランジスタの作製方法を説明する図。

40

【図8】本発明の一態様に係る半導体装置の作製方法を示す断面図、回路図および電気的特性を示す図。

【図9】本発明の一態様に係る半導体装置の作製方法を示す断面図、回路図および電気的特性を示す図。

【図10】本発明の一態様に係るトランジスタを用いたCPUの具体例を示すブロック図およびその一部の回路図。

【図11】本発明の一態様に係る電子機器の一例を示す斜視図。

【図12】トランジスタの構造を示す上面図および断面図。

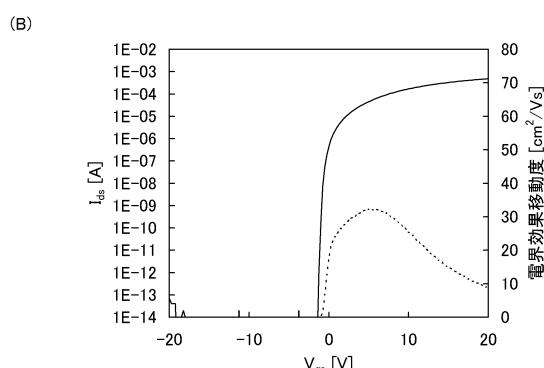

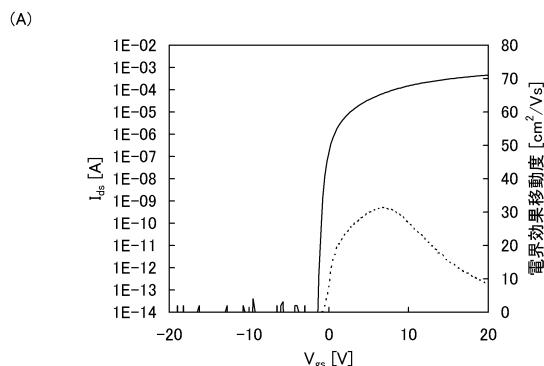

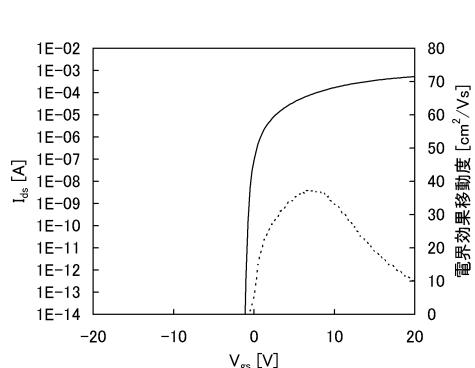

【図13】試料1および試料2であるトランジスタの $V_{g_s}$ - $I_{d_s}$ 特性および電界効果移動度を示す図。

50

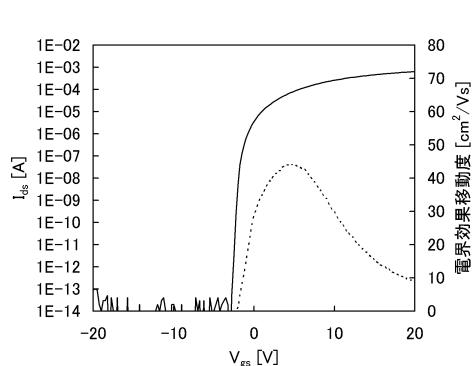

【図14】試料3および試料4であるトランジスタのV<sub>g s</sub>-I<sub>d s</sub>特性および電界効果移動度を示す図。

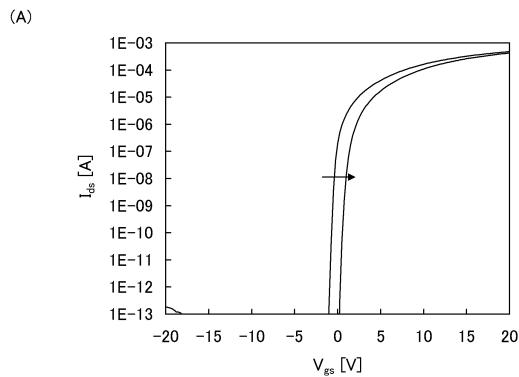

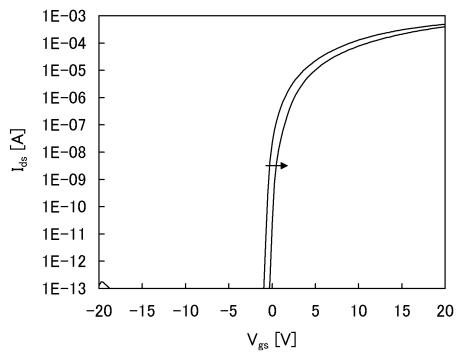

【図15】試料1であるトランジスタのBT試験前後のV<sub>g s</sub>-I<sub>d s</sub>特性を示す図。

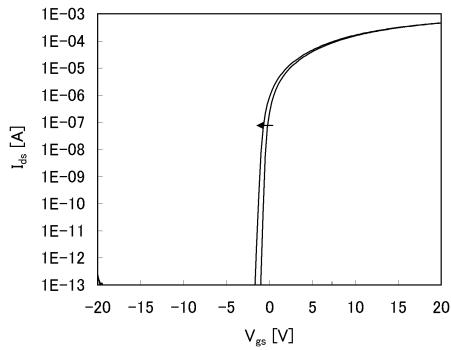

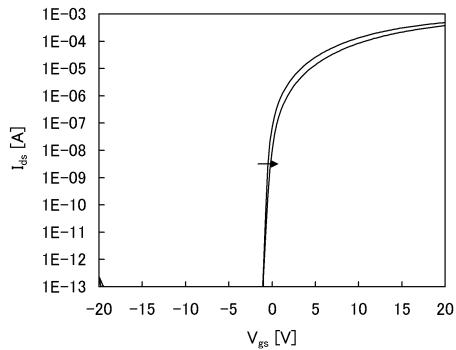

【図16】試料4であるトランジスタのBT試験前後のV<sub>g s</sub>-I<sub>d s</sub>特性を示す図。

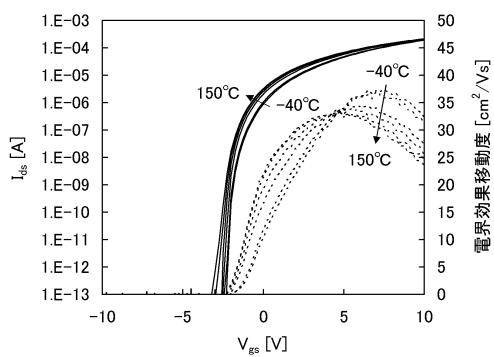

【図17】試料4であるトランジスタの測定温度によるV<sub>g s</sub>-I<sub>d s</sub>特性および電界効果移動度の変動を示す図。

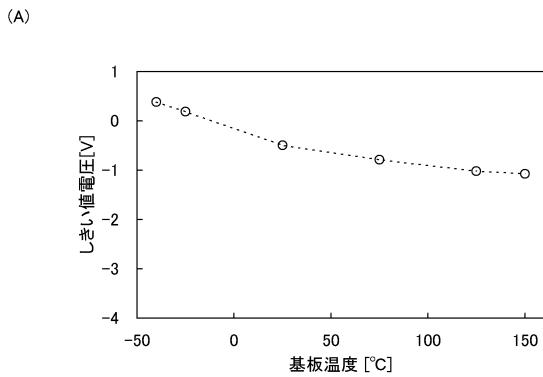

【図18】試料4であるトランジスタのしきい値電圧および電界効果移動度と基板温度の関係を示す図。

【図19】In-Sn-Zn-O膜のXRDスペクトルを示す図。

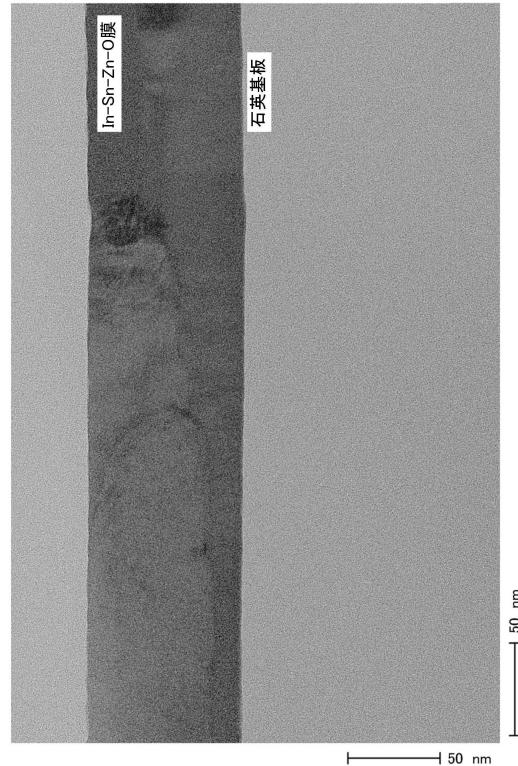

【図20】In-Sn-Zn-O膜のTEM断面像。

10

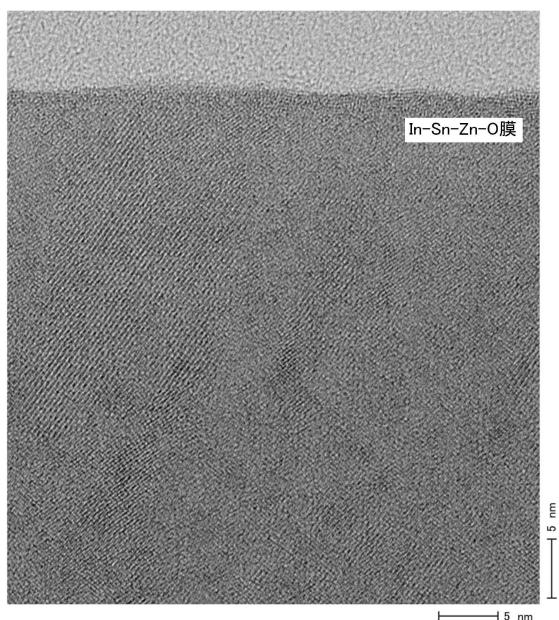

【図21】In-Sn-Zn-O膜のTEM断面像。

【図22】In-Sn-Zn-O膜を用いたトランジスタのオフ電流を示す図。

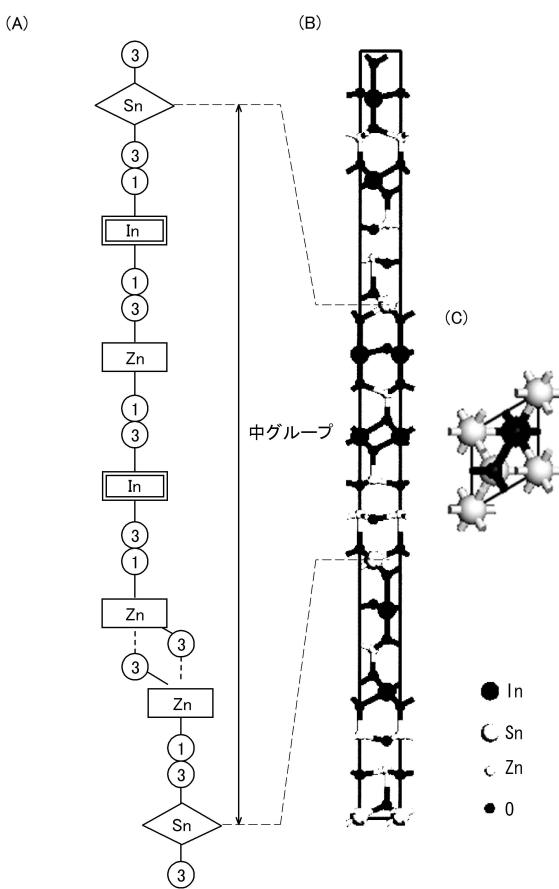

【図23】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図24】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

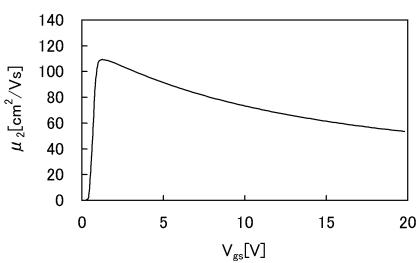

【図25】計算によって得られた電界効果移動度のV<sub>g s</sub>依存性を説明する図。

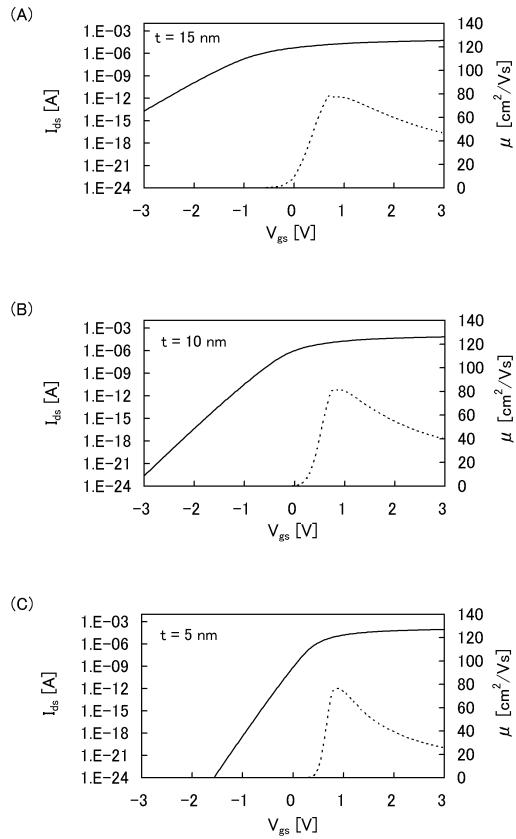

【図26】計算によって得られたI<sub>d s</sub>および電界効果移動度のV<sub>g s</sub>依存性を説明する図。

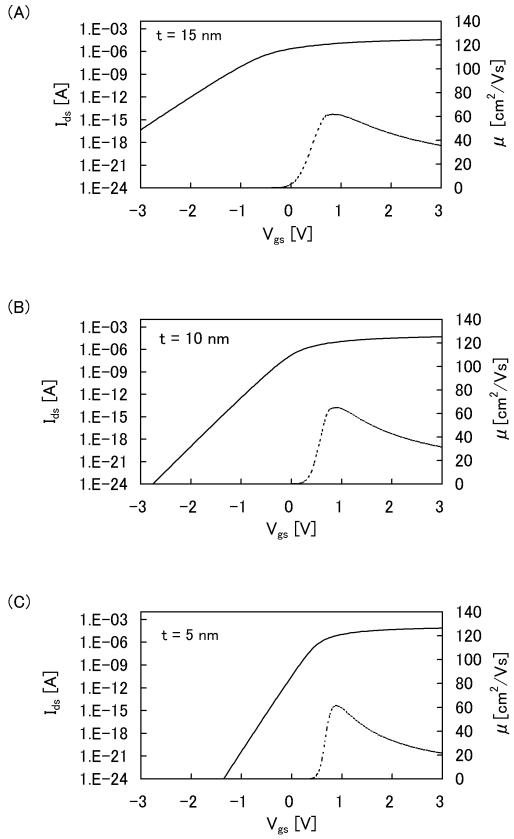

【図27】計算によって得られたI<sub>d s</sub>および電界効果移動度のV<sub>g s</sub>依存性を説明する図。

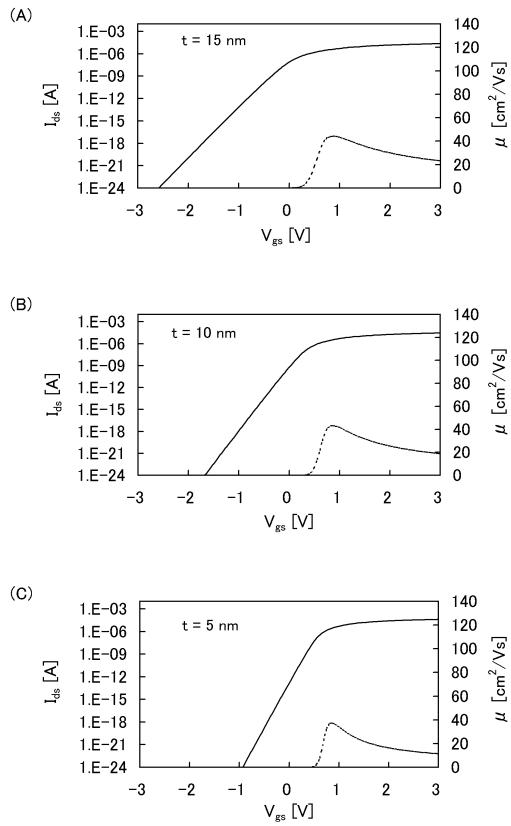

【図28】計算によって得られたI<sub>d s</sub>および電界効果移動度のV<sub>g s</sub>依存性を説明する図。 20

#### 【発明を実施するための形態】

##### 【0048】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

##### 【0049】

30

以下、本明細書で用いる用語について簡単に説明する。

##### 【0050】

トランジスタのソースとドレインについては、一方をドレインと呼ぶとき他方をソースとする。即ち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えてよい。

##### 【0051】

電圧は、基準の電位（例えば接地電位（GND））との電位差のことを示す場合が多い。よって、電圧と電位を言い換えてもよい。

##### 【0052】

「接続する」と表現されても、実際の回路においては物理的な接続部分がなく、配線が延在している場合もある。 40

##### 【0053】

第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、発明を特定するための固有の名称を示すものではない。

##### 【0054】

##### (実施の形態1)

本実施の形態では、本発明の一態様であるトランジスタの一例について、図1乃至図4などを用いて説明する。

##### 【0055】

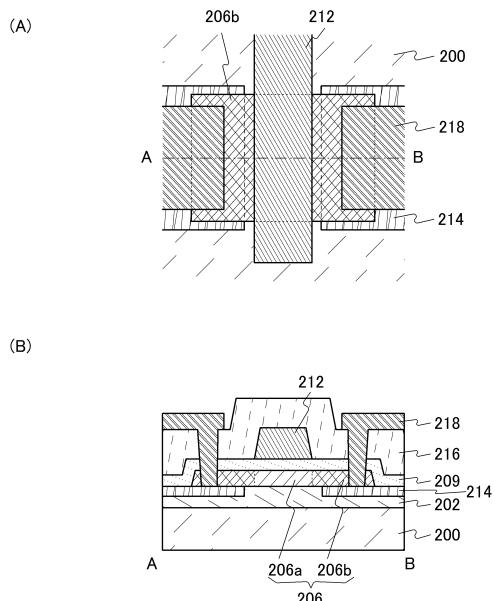

図1は、トップゲート・トップコンタクト構造のトランジスタの上面図および断面図であ 50

る。図1(A)にトランジスタの上面図を示す。また、図1(B)に図1(A)の一点鎖線A-Bに対応する断面A-Bを示す。

#### 【0056】

図1(B)に示すトランジスタは、基板100上に設けられた下地絶縁膜102と、下地絶縁膜102の周辺に設けられた保護絶縁膜104と、下地絶縁膜102および保護絶縁膜104上に設けられた高抵抗領域106aおよび低抵抗領域106bを有する酸化物半導体膜106と、酸化物半導体膜106上に設けられたゲート絶縁膜108と、ゲート絶縁膜108を介して酸化物半導体膜106と重畠して設けられたゲート電極110と、ゲート電極110の側面と接して設けられた側壁絶縁膜112と、少なくとも酸化物半導体膜106と接して設けられた一対の電極114と、少なくとも酸化物半導体膜106、ゲート電極110および一対の電極114を覆って設けられた層間絶縁膜116と、層間絶縁膜116に設けられた開口部を介して少なくとも一対の電極114の一方と接続して設けられた配線118と、を有する。

#### 【0057】

なお、図示しないが、層間絶縁膜116および配線118を覆って設けられた保護膜を有していても構わない。該保護膜を設けることで、層間絶縁膜116の表面伝導に起因して生じる微小リーキ電流を低減することができ、トランジスタのオフ電流を低減することができる。保護膜としては、アクリル樹脂、ポリイミド樹脂、エポキシ樹脂およびシリコーン樹脂などから選択して用いればよい。

#### 【0058】

オフ電流とは、広義にトランジスタがオフ状態のときに流れるドレイン電流をいう。トランジスタのオフ状態とは、nチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より低い状態をいう。または、pチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より高い状態をいう。ドレイン電流とは、トランジスタのソース-ドレイン間の電流をいう。また、ゲート電圧とは、ソース電位を基準としたときのゲート電位との電位差をいう。

#### 【0059】

オフ電流は、ノーマリーオフ型のトランジスタにおいて、ゲート電圧が0Vのときに流れるドレイン電流を指すことがある。ノーマリーオフ型のトランジスタとは、nチャネル型のトランジスタにおいて、しきい値電圧が0Vより大きいものをいう。または、pチャネル型のトランジスタにおいて、しきい値電圧が0Vより小さいものをいう。

#### 【0060】

酸化物半導体膜106は、厚さを1nm以上40nm以下とする。好ましくは、厚さを3nm以上20nm以下とする。特に、チャネル長が30nm以下のトランジスタにおいては、酸化物半導体膜106の厚さを5nm程度することで、短チャネル効果を抑制でき、安定な電気的特性を得ることができる。

#### 【0061】

酸化物半導体膜106として、例えば、In-Al-Sn-Zn-O系材料、In-Sn-Zn-O系材料、In-Al-Zn-O系材料、Zn-Sn-O系材料などを用いればよい。ここで、例えば、In-Sn-Zn-O系の材料は、インジウム、スズ、亜鉛を有する酸化物、という意味であり、その組成比は特に問わない。上記材料を酸化物半導体膜106に用いることで、高い電界効果移動度のトランジスタを得ることができる。

#### 【0062】

酸化物半導体膜106は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を選択する。バンドギャップが前述の範囲にある酸化物半導体膜106を用いることで、トランジスタのオフ電流を小さくすることができる。

#### 【0063】

なお、酸化物半導体膜106は、水素、アルカリ金属およびアルカリ土類金属などが低減され、極めて不純物濃度の低い酸化物半導体膜106であると好ましい。酸化物半導体膜

10

20

30

40

50

106が前述の不純物を有すると、不純物の形成する準位によりバンドギャップ内の再結合が起こり、トランジスタはオフ電流が増大してしまう。

#### 【0064】

酸化物半導体膜106中の水素濃度は、二次イオン質量分析(SIMS: Secondary Ion Mass Spectrometry)において、 $5 \times 10^{-9} \text{ cm}^{-3}$ 未満、好ましくは $5 \times 10^{-8} \text{ cm}^{-3}$ 以下、より好ましくは $1 \times 10^{-8} \text{ cm}^{-3}$ 以下、さらに好ましくは $5 \times 10^{-7} \text{ cm}^{-3}$ 以下とする。

#### 【0065】

また、酸化物半導体膜106中のアルカリ金属濃度は、SIMSにおいて、ナトリウム濃度が $5 \times 10^{-6} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{-6} \text{ cm}^{-3}$ 以下、さらに好ましくは $1 \times 10^{-5} \text{ cm}^{-3}$ 以下とする。同様に、リチウム濃度は、 $5 \times 10^{-5} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{-5} \text{ cm}^{-3}$ 以下とする。同様に、カリウム濃度は、 $5 \times 10^{-5} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{-5} \text{ cm}^{-3}$ 以下とする。

#### 【0066】

以上に示した酸化物半導体膜106を用いたトランジスタは、電界効果移動度が高く、オフ電流は小さい。具体的には、トランジスタの電界効果移動度を $31 \text{ cm}^2 / \text{Vs}$ 以上、または $40 \text{ cm}^2 / \text{Vs}$ 以上、 $60 \text{ cm}^2 / \text{Vs}$ 以上、 $80 \text{ cm}^2 / \text{Vs}$ 以上または $100 \text{ cm}^2 / \text{Vs}$ 以上とすることができる、例えばチャネル長が $3 \mu\text{m}$ 、チャネル幅が $1 \mu\text{m}$ のときのオフ電流を $1 \times 10^{-18} \text{ A}$ 以下、 $1 \times 10^{-21} \text{ A}$ 以下または $1 \times 10^{-24} \text{ A}$ 以下とすることができます。

#### 【0067】

酸化物半導体膜106は非単結晶であると好ましい。トランジスタの動作、外部からの光や熱の影響で、酸化物半導体膜106に酸素欠損が生じた場合に、酸化物半導体膜106が完全な単結晶であると、酸素欠損を補償するための格子間酸素が存在しないため酸化物半導体膜106中に該酸素欠損に起因するキャリアが生成されてしまう。そのため、トランジスタのしきい値電圧がマイナス方向に変動してしまうことがある。

#### 【0068】

酸化物半導体膜106は、結晶性を有すると好ましい。例えば、多結晶膜またはCAC-OS膜を用いる。

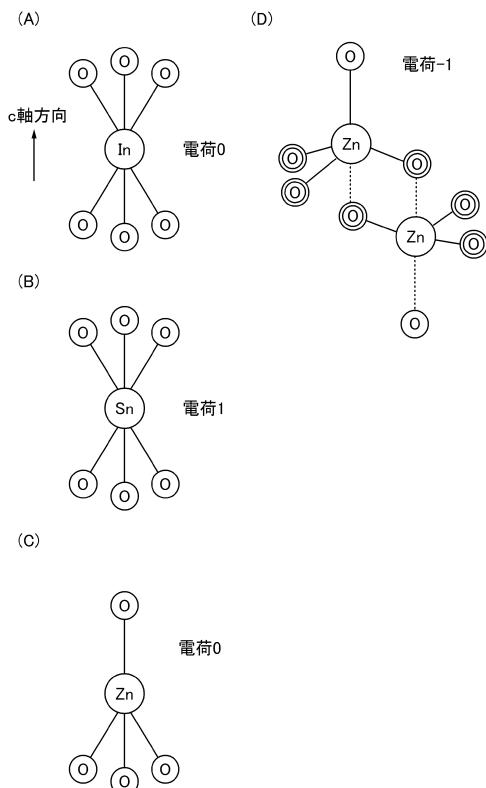

#### 【0069】

CAC-OS膜に含まれる結晶構造の一例について図23および図24を用いて詳細に説明する。なお、特に断りがない限り、図23および図24は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図23において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

#### 【0070】

図23(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。このような金属原子が1個に対して、近接の酸素原子のみ示した構造を、ここでは小グループと呼ぶ。図23(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図23(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図23(A)に示す小グループは電荷が0である。

#### 【0071】

図23(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、による構造を示す。図23(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図23(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図23(C)に示す小グループは電荷が0である。

#### 【0072】

図23(B)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図23(B)の上半分には3個の4配位のOがあり、下半分には3個の4配位

10

20

30

40

50

の〇がある。図23(B)に示す小グループは電荷が+1となる。

#### 【0073】

図23(D)に、2個のZnを含む小グループを示す。図23(D)の上半分には1個の4配位の〇があり、下半分には1個の4配位の〇がある。図23(D)に示す小グループは電荷が-1となる。図23(E)に、1個の5配位のInと、Inに近接の3個の3配位の〇と、Inに近接の2個の4配位の〇と、を有する構造を示す。3配位の〇は、いずれもab面に存在する。図23(E)の上半分及び下半分にはそれぞれ1個ずつ4配位の〇がある。図23(E)に示す小グループは電荷が0である。

#### 【0074】

ここでは、小グループのいくつかの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。10

#### 【0075】

ここで、これらの小グループ同士が結合する規則について説明する。図23(A)に示す6配位のInの上半分の3個の〇は、下方向にそれぞれ3個の近接Inを有し、下半分の3個の〇は、上方向にそれぞれ3個の近接Inを有する。図23(C)に示す4配位のZnの上半分の1個の〇は、下方向に1個の近接Znを有し、下半分の3個の〇は、それぞれ上方向に3個の近接Znを有する。この様に、金属原子の上方向の4配位の〇の数と、その〇の下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位の〇の数と、その〇の上方向にある近接金属原子の数は等しい。〇は4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。したがって、金属原子の上方向にある4配位の〇の数と、別の金属原子の下方向にある4配位の〇の数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位の〇を介して結合する場合、4配位の〇が3個であるため、5配位の金属原子(In)または4配位の金属原子(Zn)のいずれかと結合することになる。20

#### 【0076】

これらの配位数を有する金属原子は、c軸方向において、4配位の〇を介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

#### 【0077】

図24(A)に、In-Sn-Zn-O系の層構造を構成する中グループのモデル図の例を示す。図24(B)に、3つの中グループで構成される大グループを示す。なお、図24(C)は、図24(B)の層構造をc軸方向から観察した場合の原子配列を示す。30

#### 【0078】

図24(A)においては、簡単のため、3配位の〇は省略し、4配位の〇は個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位の〇があることを丸枠の3として示している。同様に、図24(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位の〇があり、丸枠の1として示している。また、同様に、図24(A)において、下半分には1個の4配位の〇があり、上半分には3個の4配位の〇があるZnと、上半分には1個の4配位の〇があり、下半分には3個の4配位の〇があるZnとを示している。40

#### 【0079】

図24(A)において、In-Sn-Zn-O系の層構造を構成する中グループは、上から順に4配位の〇が3個ずつ上半分および下半分にあるSnが、4配位の〇が1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位の〇があるZnと結合し、そのZnの下半分の1個の4配位の〇を介して4配位の〇が3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位の〇があるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位の〇を介して4配位の〇が3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。なお、大グループを構成する中グループは50

、全て同じ構成の中グループとは限らない。

#### 【0080】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。したがって、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図23(D)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

10

#### 【0081】

具体的には、図24(B)に示した大グループが繰り返されることで、In-Sn-Zn-O系の結晶(In<sub>2</sub>SnZn<sub>3</sub>O<sub>8</sub>)を得ることができる。なお、得られるIn-Sn-Zn-O系の層構造は、In<sub>2</sub>SnZn<sub>2</sub>O<sub>7</sub>(ZnO)<sub>m</sub>(mは0または自然数。)とする組成式で表すことができる。

#### 【0082】

また、このほかにも、In-Al-Sn-Zn-O系材料、In-Al-Zn-O系材料、Sn-Zn-O系材料などを用いた場合も同様である。

#### 【0083】

CAAC-OS膜は、下地となる膜が平坦であると形成されやすい。具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、さらに好ましくは0.1nm以下となるように下地となる膜を設ける。なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、式(1)にて定義される。

20

#### 【0084】

#### 【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x,y) - Z_0| dx dy \quad (1)$$

#### 【0085】

30

なお、式(1)において、S<sub>0</sub>は、測定面(座標(x<sub>1</sub>, y<sub>1</sub>)(x<sub>1</sub>, y<sub>2</sub>)(x<sub>2</sub>, y<sub>1</sub>)(x<sub>2</sub>, y<sub>2</sub>)で表される4点によって囲まれる長方形の領域)の面積を指し、Z<sub>0</sub>は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM: Atomic Force Microscope)にて評価可能である。

#### 【0086】

図1(B)に示すトランジスタは、ゲート電極110をマスクに用いて、自己整合的に酸化物半導体膜106の低抵抗領域106b(それぞれトランジスタのソース領域およびドレイン領域として機能する。)および高抵抗領域106a(トランジスタのチャネル領域として機能する。)を形成することができる。そのため、微細なトランジスタを得ることができる。また、低抵抗領域106bおよび高抵抗領域106aを形成するためのフォトリソグラフィ工程を省略することができるため、フォトリソグラフィ工程に関連するコストが削減し、歩留まりが向上する。また、低抵抗領域106bとゲート電極110とがほとんど重ならないため、低抵抗領域106bおよびゲート電極110が形成する寄生容量が生じず、トランジスタの高速動作が可能となる。

40

#### 【0087】

図1(B)に示すトランジスタは、側壁絶縁膜112を有するため、トランジスタがオン状態のときには、低抵抗領域106bを介して、一対の電極114から高抵抗領域106aに電流が流れることになる。低抵抗領域106bを介することで、電界集中が緩和され、チャネル長の小さい微細なトランジスタにおいてもホットキャリア劣化などの劣化を抑制でき、信頼性を高めることができる。

50

## 【0088】

なお、図1に示すトランジスタは、酸化物半導体膜106における側壁絶縁膜112と重畠する領域を低抵抗領域106bに含めているが、これに限定されない。例えば、酸化物半導体膜106における側壁絶縁膜112と重畠する領域を高抵抗領域106aに含めても構わない。このような構造とすることでも、前述のホットキャリア劣化などの劣化を低減することができる。

## 【0089】

下地絶縁膜102は、加熱処理により酸素を放出する絶縁膜を用いると好ましい。

## 【0090】

また、下地絶縁膜102は、酸化物半導体膜106が結晶成長しやすいように、十分な平坦性を有することが好ましい。10

## 【0091】

下地絶縁膜102は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化セシウム、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。

## 【0092】

酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS: Hydrogen Forward scattering Spectrometry)を用いて測定した場合のものである。また、構成元素の組成は、その合計が100原子%を超えない値をとる。20

## 【0093】

「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy: 昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、特に $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上であることをいう。30

## 【0094】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

## 【0095】

TDS分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そしてこの積分値と標準試料との比較により、気体の全放出量を計算することができる。

## 【0096】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量( $N_{O_2}$ )は、式(2)で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかに $CH_3OH$ があるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。40

## 【0097】

## 【数2】

$$N_{O_2} = \frac{N_{H_2}}{S_{H_2}} \times S_{O_2} \times \alpha \quad (2)$$

## 【0098】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$  は、標準試料を TDS 分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$  とする。 $S_{O_2}$  は、絶縁膜を TDS 分析したときのイオン強度の積分値である。 $\alpha$  は、TDS 分析におけるイオン強度に影響する係数である。式(2)の詳細については、特開平6-275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置 EMD-WA1000S/W を用い、標準試料として  $1 \times 10^{-6}$  atoms/cm<sup>3</sup> の水素原子を含むシリコンウェハを用いて測定した。

10

## 【0099】

また、TDS 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の  $\alpha$  は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

## 【0100】

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

20

## 【0101】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ ))) であってもよい。酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ ))) とは、シリコン原子数の 2 倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

## 【0102】

下地絶縁膜 102 から酸化物半導体膜 106 に酸素が供給されることで、酸化物半導体膜 106 と下地絶縁膜 102 との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜 106 と下地絶縁膜 102 との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少ないトランジスタを得ることができる。

30

## 【0103】

さらに、酸化物半導体膜 106 の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そこで、下地絶縁膜 102 から酸化物半導体膜 106 に酸素が十分に供給され、好ましくは酸化物半導体膜 106 に酸素が過剰に含まれていることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜 106 の酸素欠損を低減することができる。

40

## 【0104】

保護絶縁膜 104 は、250 以上 450 以下、好ましくは 150 以上 800 以下の温度範囲において、例えば 1 時間の加熱処理を行っても酸素を透過しない性質を有すると好ましい。

## 【0105】

以上のような性質により、保護絶縁膜 104 を下地絶縁膜 102 の周辺に設ける構造とすると、下地絶縁膜 102 から加熱処理によって放出された酸素が、トランジスタの外方へ拡散していくことを抑制できる。このように、下地絶縁膜 102 に酸素が保持されるため、トランジスタの電界効果移動度の低下を防止し、しきい値電圧のばらつきを低減させ、かつ信頼性を向上させることができる。

50

## 【0106】

ただし、保護絶縁膜104を設けない構造を探ることもできる。

## 【0107】

保護絶縁膜104は、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニア、酸化イットリウム、酸化ランタン、酸化セシウム、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。

## 【0108】

また、基板100として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。10

## 【0109】

ゲート電極110は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層または積層で用いればよい。または、少なくともInおよびZnを含む酸化物または酸窒化物を用いても構わない。例えば、In-Ga-Zn-O-N系材料などを用いればよい。

## 【0110】

ゲート絶縁膜108は、下地絶縁膜102と同様の方法および同様の材料によって形成すればよい。20

## 【0111】

一对の電極114は、ゲート電極110と同様の方法および同様の材料によって形成すればよい。

## 【0112】

層間絶縁膜116は、下地絶縁膜102と同様の方法および同様の材料によって形成すればよい。また、層間絶縁膜116として、樹脂材料（ポリイミド樹脂、アクリル樹脂など）を積層して設けてもよい。樹脂材料は、厚く成膜することが比較的容易であり、また、感光性樹脂を用いれば加工も容易であるため、層間絶縁膜116に適した材料である。

## 【0113】

配線118は、ゲート電極110と同様の方法および同様の材料によって形成すればよい。30

## 【0114】

以下にトランジスタの電界効果移動度について図25乃至図28を用いて説明する。

## 【0115】

酸化物半導体に限らず、トランジスタの電界効果移動度は、様々な理由によって本来の得られるはずの電界効果移動度よりも低く測定される。電界効果移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面における欠陥がある。ここでは、Levinsonモデルを用い、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出す。

## 【0116】

本来のトランジスタの電界効果移動度を $\mu_0$ とし、半導体中に何らかのポテンシャル障壁（粒界等）が存在すると仮定したときに測定される電界効果移動度 $\mu$ は数式(3)で表される。

## 【0117】

## 【数3】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right) \quad (3)$$

## 【0118】

ここで、Eはポテンシャル障壁の高さであり、kはボルツマン定数、Tは絶対温度である50

。なお、Levinsonモデルでは、ポテンシャル障壁の高さEが欠陥に由来すると仮定し、式(4)で表される。

【0119】

【数4】

$$E = \frac{e^2 N^2}{8\epsilon n} = \frac{e^3 N^2 t}{8\epsilon C_{ox} V_{gs}} \quad (4)$$

【0120】

ここで、eは電気素量、Nはチャネル内の単位面積あたりの平均欠陥密度、 $\epsilon$ は半導体の誘電率、nはチャネルの単位面積あたりのキャリア密度、 $C_{ox}$ は単位面積当たりのゲート絶縁膜容量、 $V_{gs}$ はゲート電圧、tはチャネルの厚さである。なお、厚さが30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

10

【0121】

線形領域におけるドレイン電流 $I_{ds}$ は、式(5)で表される。

【0122】

【数5】

$$\frac{I_{ds}}{V_{gs}} = \frac{W\mu V_{ds} C_{ox}}{L} \exp\left(-\frac{E}{kT}\right) \quad (5)$$

【0123】

20

ここで、Lはチャネル長、Wはチャネル幅であり、ここでは、LおよびWは10μmとする。また、 $V_{ds}$ はドレイン電圧である。

【0124】

式(5)の両辺の対数を取ると、式(6)で表される。

【0125】

【数6】

$$\ln\left(\frac{I_{ds}}{V_{gs}}\right) = \ln\left(\frac{W\mu V_{ds} C_{ox}}{L}\right) - \frac{E}{kT} = \ln\left(\frac{W\mu V_{ds} C_{ox}}{L}\right) - \frac{e^3 N^2 t}{8kT\epsilon C_{ox} V_{gs}} \quad (6)$$

30

【0126】

式(6)の右辺は $V_{gs}$ の関数であるため、縦軸を $\ln(I_{ds}/V_{gs})$ 、横軸を $1/V_{gs}$ とする直線の傾きから欠陥密度Nが求められる。即ち、トランジスタの $V_{gs}$ - $I_{ds}$ 特性から半導体中の欠陥密度Nが得られる。

【0127】

半導体中の欠陥密度Nは半導体の成膜時の基板温度に依存する。半導体として、In、SnおよびZnの比率が、In : Sn : Zn = 1 : 1 : 1 [原子数比] のIn-Sn-Zn-Oターゲットを用いて成膜した酸化物半導体を用いた場合、酸化物半導体中の欠陥密度Nは $1 \times 10^{12} / \text{cm}^2$ 程度となる。

【0128】

40

上述した酸化物半導体中の欠陥密度Nをもとに、式(3)および式(4)を用いて計算すると、本来のトランジスタの電界効果移動度 $\mu_0$ は $120 \text{ cm}^2/\text{Vs}$ となる。したがって、酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥がない、理想的なトランジスタの電界効果移動度 $\mu_0$ は $120 \text{ cm}^2/\text{Vs}$ とわかる。ところが、欠陥の多い酸化物半導体では、トランジスタの電界効果移動度 $\mu$ は $30 \text{ cm}^2/\text{Vs}$ 程度である。

【0129】

また、半導体内部に欠陥がなくても、チャネルとゲート絶縁膜との界面散乱によってトランジスタの輸送特性は影響を受ける。ゲート絶縁膜界面からxだけ離れた場所における電界効果移動度 $\mu_1$ は、式(7)で表される。

50

## 【0130】

## 【数7】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp(-\frac{x}{l}) \quad (7)$$

## 【0131】

ここで、Dはゲート電極による電界強度、Bは定数、lは界面散乱の影響が生じる深さである。Bおよびlは、トランジスタの電気的特性の実測より求めることができ、上記酸化物半導体を用いたトランジスタの電気的特性の実測からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $l = 10 \text{ nm}$ が得られる。Dが増加すると、即ち $V_{gs}$ が高くなると、式(7)の第2項が増加するため、電界効果移動度 $\mu_1$ は低下することがわかる。

10

## 【0132】

酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥のない、理想的なトランジスタの電界効果移動度 $\mu_2$ を計算した結果を図25に示す。なお、計算にはシノプシス社製Sentaurus Deviceを使用し、酸化物半導体のバンドギャップを2.8eV、電子親和力を4.7eV、比誘電率を15、厚さを15nmとした。さらに、ゲートの仕事関数を5.5eV、ソースおよびドレインの仕事関数を4.6eVとした。また、ゲート絶縁膜の厚さは100nm、比誘電率を4.1とした。また、チャネル長およびチャネル幅はともに10μm、 $V_{ds}$ は0.1Vとした。

## 【0133】

図25で示されるように、 $V_{gs}$ が1V近傍で電界効果移動度 $\mu_2$ は $100 \text{ cm}^2/\text{Vs}$ 以上のピークを有するが、 $V_{gs}$ がさらに高くなると、界面散乱の影響が大きくなり、電界効果移動度 $\mu_2$ が低下することがわかる。

20

## 【0134】

このような理想的なトランジスタを微細化した場合について、計算した結果を図26乃至図28に示す。なお、計算には図1(B)に示した構造のトランジスタを仮定している。ここで、低抵抗領域106bの抵抗率を $2 \times 10^{-3} \text{ cm}$ 、ゲート電極110の幅を33nm、側壁絶縁膜112の幅を5nm、チャネル幅を40nmとする。なお、チャネル領域を便宜上高抵抗領域106aという名称で記載しているが、ここではチャネル領域を真性半導体と仮定している。

30

## 【0135】

計算にはシノプシス社製Sentaurus Deviceを使用した。図26は、図1(B)に示される構造のトランジスタの $I_{ds}$ (実線)および電界効果移動度 $\mu$ (点線)の $V_{gs}$ 依存性である。なお、 $I_{ds}$ は $V_{ds}$ を1Vとし、電界効果移動度 $\mu$ は $V_{ds}$ を0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図26(A)に、10nmとした場合を図26(B)に、5nmとした場合を図26(C)にそれぞれ示す。

## 【0136】

図26より、ゲート絶縁膜が薄くなるほど、オフ状態(ここでは $V_{gs}$ が-3Vから0Vの範囲を指す。)でのドレイン電流 $I_{ds}$ が低下する。一方、電界効果移動度 $\mu$ のピーク値やオン状態(ここでは $V_{gs}$ が0Vから3Vの範囲を指す。)でのドレイン電流 $I_{ds}$ には目立った変化がない。図26より、 $V_{gs}$ が1V近傍で $I_{ds}$ は半導体装置であるメモリなどに必要とされる10μAを超えることがわかる。

40

## 【0137】

同様に、図1(B)で示されるトランジスタとは側壁絶縁膜112と重畠する酸化物半導体膜106の領域が高抵抗領域106aに含まれる点で構造の異なるトランジスタについても計算を行っている。換言すると、該トランジスタは側壁絶縁膜112の幅だけオフセット領域を有するトランジスタである。なお、オフセット領域の幅をオフセット長( $L_{off}$ )ともいう。

## 【0138】

20

30

40

50

側壁絶縁膜 112 と重畳する酸化物半導体膜 106 の領域が高抵抗領域 106a に含まれる場合のトランジスタにおいて、Looff を 5 nm とし、ドレイン電流  $I_{ds}$  (実線) および電界効果移動度  $\mu$  (点線) の  $V_{gs}$  依存性を図 27 に示す。なお、 $I_{ds}$  は、 $V_{ds}$  を 1 V とし、電界効果移動度  $\mu$  は  $V_{ds}$  を 0.1 V として計算している。ここで、ゲート絶縁膜の厚さが 15 nm とした場合を図 27 (A) に、10 nm とした場合を図 27 (B) に、5 nm とした場合を図 27 (C) にそれぞれ示す。

#### 【0139】

また、図 28 は、図 1 (B) に示される構造から、側壁絶縁膜 112 と重畳する酸化物半導体膜 106 の領域を高抵抗領域 106a としているトランジスタで、Looff を 15 nm としたもののドレイン電流  $I_{ds}$  (実線) および電界効果移動度  $\mu$  (点線) の  $V_{gs}$  依存性である。なお、 $I_{ds}$  は、 $V_{ds}$  を 1 V とし、電界効果移動度  $\mu$  は  $V_{ds}$  を 0.1 V として計算している。ここで、ゲート絶縁膜の厚さが 15 nm とした場合を図 28 (A) に、10 nm とした場合を図 28 (B) に、5 nm とした場合を図 28 (C) にそれぞれ示す。

#### 【0140】

図 27 および図 28 に示した計算結果より、図 26 と同様に、いずれもゲート絶縁膜が薄くなるほどオフ状態 (ここでは  $V_{gs}$  が -3 V から 0 V の範囲を指す。) でのドレイン電流  $I_{ds}$  が低下する。一方、電界効果移動度  $\mu$  のピーク値やオン状態 (ここでは  $V_{gs}$  が 0 V から 3 V の範囲を指す。) でのドレイン電流  $I_{ds}$  には目立った変化がないとわかる。

10

20

#### 【0141】

なお、電界効果移動度  $\mu$  のピークは、図 26 では  $80 \text{ cm}^2 / \text{Vs}$  程度であるが、図 27 では  $60 \text{ cm}^2 / \text{Vs}$  程度、図 28 では  $40 \text{ cm}^2 / \text{Vs}$  程度、Looff が増加するほど低下することがわかる。また、オフ状態での  $I_{ds}$  も同様の傾向となることがわかる。一方、オン状態の  $I_{ds}$  はオフセット長 Looff の増加に伴って減少するが、オフ状態の  $I_{ds}$  の低下に比べると緩やかである。また、いずれの計算結果からも  $V_{gs}$  が 1 V 近傍で、 $I_{ds}$  はメモリなどに必要とされる  $10 \mu\text{A}$  を超えることがわかる。

#### 【0142】

図 1 (B) に示すトランジスタの作製方法の一例を以下に示す。

#### 【0143】

30

ここで、全ての膜において、トランジスタの特性に悪影響を与える水素などの不純物が含まれないよう成膜することが好ましい。

#### 【0144】

例えば、基板 100 の表面に付着している不純物が膜に取り込まれてしまうことがある。それを防止するためには、下地絶縁膜 102 の成膜前に基板 100 表面の不純物を低減する処理を行うことが好ましい。不純物を低減する処理として、プラズマ処理、加熱処理または薬液処理が挙げられる。

#### 【0145】

なお、成膜を行う装置内 (成膜室など) に起因する不純物も問題となるため、あらかじめ除去しておくと好ましい。具体的には、成膜室などをベーキングして不純物を放出させておけばよい。

40

#### 【0146】

また、成膜室は、あらかじめ 5 分程度のダミー成膜をダミー基板 100 枚程度に対し行っておくと好ましい。なお、ダミー成膜を 1 枚行うごとに成膜室の排気を行うとより好ましい。ダミー成膜とは、ダミー基板に対してスパッタリング法などによる成膜を行うことと、ダミー基板および成膜室内壁に膜を堆積させ、成膜室内の不純物および成膜室内壁の吸着物を膜中に閉じこめることをいう。ダミー基板は、放出ガスの少ない材料が好ましく、例えば基板 100 と同様の材料を用いてよい。ダミー成膜を行うことで、後に成膜される膜中の不純物濃度を低減することができる。

#### 【0147】

50

なお、成膜室などにおけるベーキングおよびダミー成膜は、トランジスタの作製工程時の温度よりも高い温度で行うとよい。あらかじめ高い温度とすることで、それよりも低い温度における不純物の放出量を低減することができる。

#### 【0148】

また成膜に用いるガスの純度も膜中の不純物濃度に影響するため、なるべく純度の高いものを用いる。特に水分の含有の少ないガスを用いると好ましい。具体的には、露点が -70 以下ガスを用いればよい。さらに好ましくは、例えば、純度が 9 N であるアルゴンガス（露点 -121 、水 0.1 p p b 、水素 0.5 p p b ）および純度が 8 N の酸素ガス（露点 -112 、水 1 p p b 、水素 1 p p b ）を用いる。

#### 【0149】

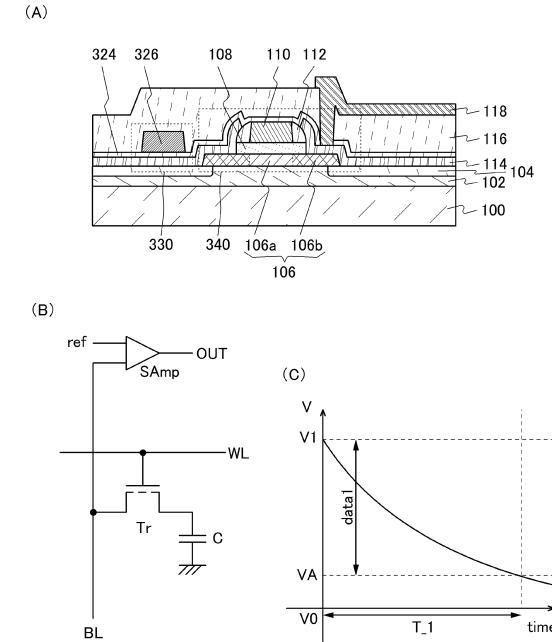

まず、基板 100 に対して表面の不純物を低減する処理を行う。不純物を低減する処理後、大気暴露せずに、スパッタリング法、蒸着法、プラズマ化学気相成長法（PCVD 法）、パルスレーザー堆積法（PLD 法）、原子層堆積法（ALD 法）または分子線エピタキシー法（MBE 法）などを用いて下地絶縁膜 152 を成膜する（図 2 (A) 参照。）。

10

#### 【0150】

下地絶縁膜 152 は、好ましくはスパッタリング法により、基板加熱温度を室温以上 200 以下、好ましくは 50 以上 150 以下とし、酸素ガス雰囲気で成膜する。なお、酸素ガスに希ガスを加えて用いてもよく、その場合は酸素ガスの割合は 30 体積 % 以上、好ましくは 50 体積 % 以上、さらに好ましくは 80 体積 % 以上とする。下地絶縁膜 152 の厚さは、100 nm 以上 1000 nm 以下、好ましくは 200 nm 以上 700 nm 以下とする。成膜時の基板加熱温度が低いほど、成膜雰囲気中の酸素ガス割合が高いほど、厚さが厚いほど、下地絶縁膜 152 を加熱処理した際に放出される酸素の量は多くなる。スパッタリング法は、PCVD 法と比べて膜中の水素濃度を低減することができる。なお、下地絶縁膜 152 を 1000 nm を超える厚さで成膜しても構わないが、生産性を低下させない程度の厚さとする。

20

#### 【0151】

次に、フォトリソグラフィ工程などによって下地絶縁膜 152 を加工し、下地絶縁膜 102 を形成する（図 2 (B) 参照。）。

#### 【0152】

次に、スパッタリング法、蒸着法、PCVD 法、PLD 法、ALD 法または MBE 法などを用いて保護絶縁膜 154 を成膜する（図 2 (C) 参照。）。

30

#### 【0153】

次に、CMP 处理によって、下地絶縁膜 102 と表面の高さが揃った保護絶縁膜 104 を形成する（図 2 (D) 参照。）。なお、下地絶縁膜 102 と保護絶縁膜 104 とは、概略表面の高さが一致していればよい。このとき、前述の CMP 处理が下地絶縁膜 102 の平坦化処理を兼ねてもよい。なお、CMP 处理による平坦化処理に加えて、プラズマ処理による平坦化処理を行ってもよい。

#### 【0154】

次に、スパッタリング法、蒸着法、PCVD 法、PLD 法、ALD 法または MBE 法などを用いて酸化物半導体膜 156 を成膜する（図 2 (E) 参照。）。

40

#### 【0155】

酸化物半導体膜 156 は、好ましくはスパッタリング法により、基板加熱温度を 100 以上 600 以下、好ましくは 150 以上 550 以下、さらに好ましくは 200 以上 500 以下とし、酸素ガス雰囲気で成膜する。酸化物半導体膜 156 の厚さは、1 nm 以上 40 nm 以下、好ましくは 3 nm 以上 20 nm 以下とする。成膜時の基板加熱温度が高いほど、得られる酸化物半導体膜 156 の不純物濃度は低くなる。また、酸化物半導体膜 156 中の原子配列が整い、高密度化され、多結晶膜または CAAc - OS 膜が形成されやすくなる。さらに、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が含まれないため、多結晶膜または CAAc - OS 膜が形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気としてもよく、その場合は酸素ガスの割合は 30 体積 % 以上

50

、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。なお、酸化物半導体膜156は薄いほど、トランジスタの短チャネル効果が低減される。ただし、薄くしすぎると界面散乱の影響が強くなり、電界効果移動度の低下が起こることがある。

#### 【0156】

酸化物半導体膜156としてIn-Sn-Zn-O系材料をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Sn:Zn=2:1:3、In:Sn:Zn=1:2:2、In:Sn:Zn=1:1:1またはIn:Sn:Zn=20:45:35で示されるIn-Sn-Zn-Oターゲットを用いる。前述の原子数比近傍であるIn-Sn-Zn-Oターゲットを用いて酸化物半導体膜156を成膜することで、多結晶膜またはCAC-OS膜が形成されやすくなる。

10

#### 【0157】

次に、第1の加熱処理を行う。第1の加熱処理は、減圧雰囲気、不活性雰囲気または酸化性雰囲気で行う。第1の加熱処理により、酸化物半導体膜156中の不純物濃度を低減することができる。

#### 【0158】

第1の加熱処理は、減圧雰囲気または不活性雰囲気で加熱処理を行った後、温度を保持しつつ酸化性雰囲気に切り替えてさらに加熱処理を行うと好ましい。これは、減圧雰囲気または不活性雰囲気にて加熱処理を行うと、酸化物半導体膜156中の不純物濃度を効果的に低減することができるが、同時に酸素欠損も生じてしまうためあり、このとき生じた酸素欠損を、酸化性雰囲気での加熱処理により低減することができる。

20

#### 【0159】

酸化物半導体膜156は、成膜時の基板加熱に加え、第1の加熱処理を行うことで、膜中の不純物準位密度を極めて小さくすることが可能となる。その結果、トランジスタの電界効果移動度を後述する理想的な電界効果移動度近くまで高めることができる。

#### 【0160】

なお、酸化物半導体膜156に酸素イオンを注入し、加熱処理により酸化物半導体膜156に含まれる水素などの不純物を放出させ、該加熱処理と同時に、またはその後の加熱処理（第1の加熱処理など）により酸化物半導体膜156を結晶化させてもよい。

#### 【0161】

また、本発明において、第1の加熱処理の代わりにレーザビームを照射して選択的に酸化物半導体膜156を結晶化してもよい。または、第1の加熱処理を行いながらレーザビームを照射して選択的に酸化物半導体膜156を結晶化してもよい。レーザビームの照射は、不活性雰囲気、酸化性雰囲気または減圧雰囲気で行う。レーザビームの照射を行う場合、連続発振型のレーザビーム（CWレーザビーム）またはパルス発振型のレーザビーム（パルスレーザビーム）を用いることができる。例えば、Arレーザ、Krレーザまたはエキシマレーザなどの気体レーザ、または単結晶もしくは多結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>もしくはGdVO<sub>4</sub>にドーパントとしてNd、Yb、Cr、Ti、Ho、Er、TmおよびTaの一種以上が添加されているものを媒質としたレーザ、もしくはガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザなどの固体レーザ、または銅蒸気もしくは金蒸気の一種以上から発振される蒸気レーザを用いることができる。このようなレーザビームの基本波、または基本波の第2高調波乃至第5高調波のいずれかのレーザビームを照射することで、酸化物半導体膜156を結晶化することができる。なお、照射するレーザビームは、酸化物半導体膜156のバンドギャップよりもエネルギーの大きいものを用いると好ましい。例えば、KrF、ArF、XeCl、またはXeFのエキシマレーザ発振器から射出されるレーザビームを用いてもよい。なお、レーザビームの形状が線状であっても構わない。

30

40

#### 【0162】

なお、異なる条件下において、複数回のレーザビーム照射を行っても構わない。例えば、1回目のレーザビーム照射を希ガス雰囲気または減圧雰囲気で行い、2回目のレーザビーム照射を酸化性雰囲気で行うと、酸化物半導体膜156の酸素欠損を低減しつつ高い結晶

50

性が得られるため好ましい。

【0163】

次に、酸化物半導体膜156をフォトリソグラフィ工程などによって加工して酸化物半導体膜166を形成する(図2(F)参照。)。

【0164】

次に、ゲート絶縁膜158、導電膜160をこの順番で成膜する(図3(A)参照。)。成膜方法は、いずれもスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いればよい。

【0165】

ゲート絶縁膜158は、好ましくは下地絶縁膜152と同様の方法で成膜する。

10

【0166】

次に、フォトリソグラフィ工程などによって導電膜160を加工し、ゲート電極110を形成する(図3(B)参照。)。

【0167】

次に、ゲート電極110をマスクに用い、ゲート絶縁膜158を介して酸化物半導体膜156の抵抗値を低減する機能を有する不純物120を添加し、高抵抗領域106aおよび低抵抗領域106bを有する酸化物半導体膜106を形成する(図3(C)参照。)。なお、不純物120は、リン、窒素またはホウ素などを用いればよい。不純物120の添加後に250以上650以下の温度で加熱処理を行う。なお、不純物120は、イオン注入法を用いて添加すると、イオンドーピング法を用いて添加した場合と比べ、酸化物半導体膜106中への水素の混入が少なくなるため好ましい。ただし、イオンドーピング法を除外するものではない。

20

【0168】

なお、ゲート絶縁膜158を介して不純物120を添加することにより、酸化物半導体膜106に不純物120の添加する際に生じるダメージを低減することができる。

【0169】

次に、絶縁膜162をスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて成膜する(図3(D)参照。)。絶縁膜162は、下地絶縁膜152と同様の方法で成膜してもよい。

【0170】

30

次に、絶縁膜162をエッチングすることにより側壁絶縁膜112を形成する。該エッチングは、異方性の高いエッチングを用いる。側壁絶縁膜112は、絶縁膜162に異方性の高いエッチング工程を行うことで自己整合的に形成することができる。例えば、ドライエッチング法を用いると好ましい。ドライエッチング法に用いるエッチングガスとしては、例えば、トリフルオロメタン、オクタフルオロシクロブタン、テトラフルオロメタンなどのフッ素を含むガスが挙げられる。エッチングガスには、希ガスまたは水素を添加してもよい。ドライエッチング法は、基板に高周波電圧を印加する、反応性イオンエッチング法(RIE法)を用いると好ましい。

【0171】

側壁絶縁膜112を形成した後、ゲート絶縁膜158を加工し、ゲート絶縁膜108を形成することができる(図4(A)参照。)なお、側壁絶縁膜112の形成と同じ工程でゲート絶縁膜108を形成しても構わない。

40

【0172】

なお、ゲート電極110の形成直後の工程に代えて、側壁絶縁膜112の形成後にゲート電極110および側壁絶縁膜112をマスクに用い、(ゲート絶縁膜108の形成前の場合は、ゲート絶縁膜158を介して)酸化物半導体膜166へ不純物120を添加しても構わない。こうすることで、側壁絶縁膜112と重畠する酸化物半導体膜106の領域を高抵抗領域106aに含めることができる。

【0173】

次に、導電膜をスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE

50

E法などを用いて成膜し、フォトリソグラフィ工程などによって該導電膜を加工し、一対の電極114を形成する(図4(B)参照。)。

#### 【0174】

次に、層間絶縁膜116をスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて成膜し、一対の電極114を露出する開口部を設ける。なお、層間絶縁膜116に樹脂材料を積層して設ける場合、さらにスピンドルコート法、スリットコート法などを用いて樹脂材料を形成すればよい。樹脂材料に感光性材料を用いて形成してもよい。

#### 【0175】

次に、導電膜をスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて成膜し、フォトリソグラフィ工程などによって該導電膜を加工して、一対の電極114のそれぞれと接する配線118を形成する(図4(C)参照。)。なお、層間絶縁膜116として、少なくとも一部に20nm以上、好ましくは50nm以上、さらに好ましくは100nm以上の厚さを有する酸化アルミニウム膜を用いると好ましい。酸化アルミニウム膜を用いることによって、トランジスタの外部から水素または水などのトランジスタの電気的特性に悪影響を及ぼす不純物の侵入を抑制できる。また、下地絶縁膜102から放出された酸素がトランジスタから外方拡散することを抑制できる。これらの効果は、酸化アルミニウム膜の膜質にもよるが、ある程度の厚さが必要とされる。ただし、あまりに酸化アルミニウム膜を厚くしすぎると生産性が低下してしまうため、適切な厚さを選択するとよい。なお、酸化アルミニウム膜に代えて、窒化シリコンまたは窒化酸化シリコンを用いても構わない。

#### 【0176】

ここで、第2の加熱処理を行う。第2の加熱処理は、層間絶縁膜116の形成後、配線118の形成後、またはその両方に行えばよい。第2の加熱処理は、減圧雰囲気、不活性雰囲気または酸化性雰囲気において、150以上550以下、好ましくは250以上400以下の温度で行う。第2の加熱処理を行うことで、下地絶縁膜102およびゲート絶縁膜108から酸素が放出され、酸化物半導体膜106中の酸素欠損を低減することができる。また、下地絶縁膜102と酸化物半導体膜106との界面準位密度、および酸化物半導体膜106とゲート絶縁膜108との界面準位密度を低減することができるため、トランジスタのしきい値電圧のばらつきを低減させ、かつ信頼性を向上させることができる。なお、第2の加熱処理を、不純物120の添加後の加熱処理に代えても構わない。

#### 【0177】

また、層間絶縁膜116に樹脂材料を用いる場合、樹脂材料に対する加熱処理と第2の加熱処理を共通化しても構わない。

#### 【0178】

以上の工程によって、図1(B)に示すトランジスタを作製することができる。

#### 【0179】

本実施の形態により、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、高い信頼性を有し、オフ電流の極めて小さい酸化物半導体を用いたトランジスタを得ることができる。

#### 【0180】

そのため、本実施の形態で示した酸化物半導体膜を用いたトランジスタは、オフ電流が低いという特性を有し、かつ高い電界効果移動度を有するため、トランジスタに高い電界効果移動度が要求されるロジック回路にも適用することができる。

#### 【0181】

本実施の形態は、他の実施の形態と組み合わせて用いても構わない。

#### 【0182】

##### (実施の形態2)

本実施の形態では、実施の形態1とは異なる構造のトランジスタについて図5乃至図7などを用いて説明する。

10

20

30

40

50

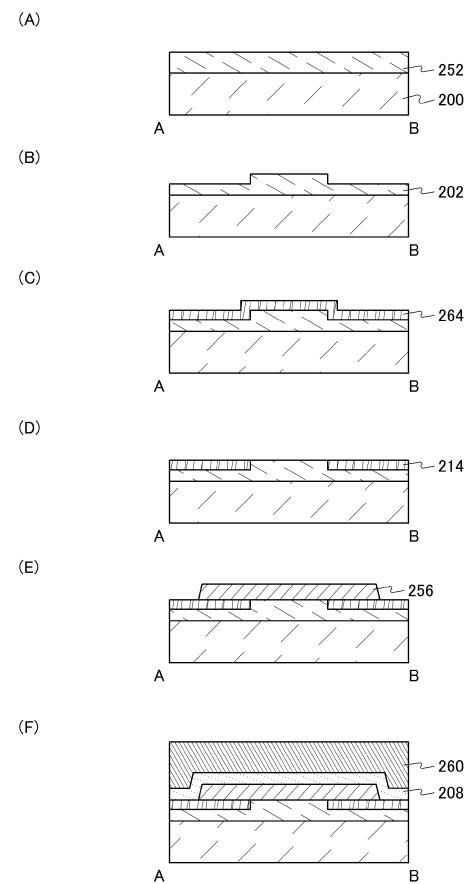

**【0183】**

図5は、トップゲート・ボトムコンタクト構造のトランジスタの上面図および断面図である。図5(A)にトランジスタの上面図を示す。また、図5(B)に図5(A)の一点鎖線A-Bに対応する断面A-Bを示す。

**【0184】**

図5(B)に示すトランジスタは、基板200と、基板200上に設けられた下地絶縁膜202と、下地絶縁膜202の溝部に設けられた一対の電極214と、下地絶縁膜202および一対の電極214上に設けられた高抵抗領域206aおよび低抵抗領域206bを有する酸化物半導体膜206と、酸化物半導体膜206上に設けられたゲート絶縁膜208と、ゲート絶縁膜208を介して酸化物半導体膜206と重畠して設けられたゲート電極210と、ゲート絶縁膜208およびゲート電極210を覆って設けられた層間絶縁膜216と、層間絶縁膜216、ゲート絶縁膜208および酸化物半導体膜206に設けられた開口部を介して一対の電極214と接続する配線218と、を有する。なお、図示しないが、層間絶縁膜216および配線218を覆って設けられた保護膜を有していても構わない。該保護膜を設けることで、層間絶縁膜216の表面伝導に起因して生じる微小リーケ電流を低減することができる。

10

**【0185】**

なお、基板200、下地絶縁膜202、酸化物半導体膜206、ゲート絶縁膜208、ゲート電極210、一対の電極214、層間絶縁膜216および配線218は、それぞれ基板100、下地絶縁膜102、酸化物半導体膜106、ゲート絶縁膜108、ゲート電極110、一対の電極114、層間絶縁膜116および配線118と同様の材料および同様の方法で形成すればよい。

20

**【0186】**

図5(B)に示すトランジスタは、一対の電極214が酸化物半導体膜206の下部で接している点で図1(B)に示すトランジスタと異なる。このような構造とすることで、一対の電極214を形成する際に、酸化物半導体膜206の一部がプラズマや薬液などに曝されてしまうことがない。したがって、酸化物半導体膜206を薄く形成する場合(例えば、5nm以下の厚さで形成する場合)などに好ましい構造である。

**【0187】**

図5(B)に示すトランジスタの作製方法の一例を以下に示す。

30

**【0188】**

まず、基板200に下地絶縁膜252を成膜する(図6(A)参照。)。

**【0189】**

次に、下地絶縁膜252を加工して下地絶縁膜202を形成する(図6(B)参照。)。

**【0190】**

次に、導電膜264を成膜する(図6(C)参照。)。

**【0191】**

次に、CMP処理を行い、下地絶縁膜202と表面の高さが揃った一対の電極214を形成する(図6(D)参照。)。

**【0192】**

次に、酸化物半導体膜256を形成する(図6(E)参照。)。

40

**【0193】**

次に、第1の加熱処理を行う。第1の加熱処理の詳細は実施の形態1の説明を参照する。

**【0194】**

次に、ゲート絶縁膜208、導電膜260をこの順番で成膜する(図6(F)参照。)。

**【0195】**

次に、導電膜260を加工してゲート電極210を形成する(図7(A)参照。)。

**【0196】**

次に、ゲート電極210をマスクに用い、ゲート絶縁膜208を介して酸化物半導体膜256の抵抗値を低減する機能を有する不純物220を添加し、高抵抗領域206aおよび

50

低抵抗領域 206b を有する酸化物半導体膜 206 を形成する(図 7(B) 参照。)。不純物 220 に関しては、実施の形態 1 における不純物 120 の材料、添加方法およびその後の加熱処理の説明を参照する。

#### 【0197】

次に、層間絶縁膜 216 を成膜し、一対の電極 214 を露出する開口部を設ける。次に、導電膜を成膜し、該導電膜を加工して、一対の電極 214 のそれぞれと接する配線 218 を形成する(図 7(C) 参照。)。

#### 【0198】

ここで、第 2 の加熱処理を行う。第 2 の加熱処理の詳細は実施の形態 1 の説明を参照する。

10

#### 【0199】

以上の工程によって、図 5(B) に示すトランジスタを作製することができる。

#### 【0200】

本実施の形態により、高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、高い信頼性を有し、オフ電流の極めて小さい酸化物半導体を用いたトランジスタを得ることができる。

#### 【0201】

本実施の形態は、他の実施の形態と組み合わせて用いても構わない。

#### 【0202】

(実施の形態 3)

20

本実施の形態では、実施の形態 1 または実施の形態 2 に示したトランジスタを用いて、半導体装置であるメモリを作製する例について説明する。

#### 【0203】

揮発性メモリの代表的な例としては、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶する D R A M (Dynamic Random Access Memory)、フリップフロップなどの回路を用いて記憶内容を保持する S R A M (Static Random Access Memory) がある。

#### 【0204】

メモリに含まれるトランジスタの一部に実施の形態 1 または実施の形態 2 で示したトランジスタを適用することができる。

30

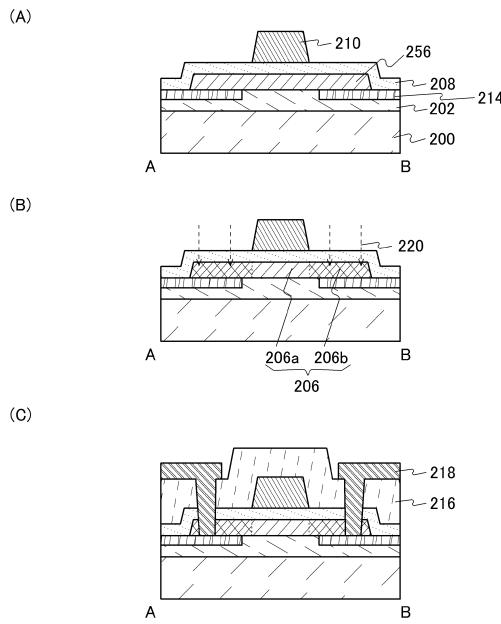

#### 【0205】

例えば、実施の形態 1 で示したトランジスタを適用した半導体装置である D R A M の例について図 8 を用いて説明する。

#### 【0206】

図 8(A) に D R A M の断面図を示す。トランジスタ 340 は、基板 100 と、基板 100 上に設けられた下地絶縁膜 102 と、下地絶縁膜 102 の周辺に設けられた保護絶縁膜 104 と、下地絶縁膜 102 および保護絶縁膜 104 上に設けられた高抵抗領域 106a および低抵抗領域 106b を有する酸化物半導体膜 106 と、酸化物半導体膜 106 上に設けられたゲート絶縁膜 108 と、ゲート絶縁膜 108 を介して高抵抗領域 106a と重畳して設けられたゲート電極 110 と、ゲート電極 110 の側面と接する側壁絶縁膜 112 と、少なくとも低抵抗領域 106b および側壁絶縁膜 112 と接する一対の電極 114 と、を有する。なお、高抵抗領域 106a は、ゲート電極 110 にトランジスタ 340 のしきい値電圧以上の電圧が印加されたときチャネルを形成する。

40

#### 【0207】

また、トランジスタ 340 は、トランジスタ 340 を覆って設けられた層間絶縁膜 324 と、層間絶縁膜 324 上に設けられた電極 326 と、を有している。一対の電極 114 のうち一方と、層間絶縁膜 324 と、電極 326 とによって、キャパシタ 330 を構成する。なお、図では平行平板型のキャパシタを示すが、容量を大きくするためにスタック型またはトレーナー型のキャパシタを使用してもよい。

#### 【0208】

50

さらに、トランジスタ340は、層間絶縁膜324と、電極326とを覆って設けられた層間絶縁膜116と、層間絶縁膜116および層間絶縁膜324に設けられた開口部を介して一対の電極114のうち他方と接続する配線118と、を有する。なお、図示しないが、層間絶縁膜116および配線118を覆って設けられた保護膜を有していても構わない。該保護膜を設けることで、層間絶縁膜116の表面伝導に起因して生じる微小リーク電流を低減することができ、トランジスタのオフ電流を低減することができる。

#### 【0209】

図8(B)は、図8(A)に示すDRAMの回路図である。DRAMは、ピット線BLと、ワード線WLと、センスアンプSAMPと、トランジスタTrと、キャパシタCと、を有する。なお、トランジスタTrは、トランジスタ340に相当し、キャパシタCは、キャパシタ330に相当する。

10

#### 【0210】

キャパシタCに保持された電位の時間変化は、トランジスタTrのオフ電流によって図8(C)に示すように徐々に低減していくことが知られている。当初V0からV1まで充電された電位は、時間が経過するとdata1を読み出す限界点であるVAまで低減する。この期間を保持期間T\_1とする。即ち、2値DRAMの場合、保持期間T\_1の間にリフレッシュ動作を行う必要がある。

#### 【0211】

ここで、トランジスタTrにトランジスタ340を適用することにより、トランジスタTrのオフ電流を極めて小さくすることができるため、保持期間T\_1を長くすることができる。即ち、リフレッシュ動作の間隔を長くとることが可能となるため、DRAMの消費電力を低減することができる。また、トランジスタTrの電界効果移動度が高いため、DRAMを高速動作させることができる。

20

#### 【0212】

例えば、高純度化され、オフ電流が $1 \times 10^{-18} A$ 以下、 $1 \times 10^{-21} A$ 以下、好ましくは $1 \times 10^{-24} A$ 以下となった酸化物半導体膜を用いたトランジスタでDRAMを構成すると、リフレッシュ動作の間隔を数十秒～数十年間とすることができる。

#### 【0213】

以上のように、本発明の一態様に係るトランジスタをDRAMに適用することによって、信頼性が高く、消費電力の小さく、かつ高速動作が可能なDRAMを得ることができる。

30

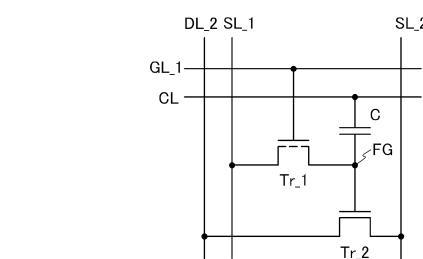

#### 【0214】

次に、実施の形態1で示したトランジスタを適用した半導体装置である不揮発性メモリの例について図9を用いて説明する。

#### 【0215】

図9(A)に、不揮発性メモリの断面図を示す。トランジスタ350は、基板100と、基板100上に設けられた下地絶縁膜382と、下地絶縁膜382上に設けられた第1の抵抗領域384a、第2の抵抗領域384b、および第3の抵抗領域384cを有する半導体膜384と、半導体膜384上に設けられたゲート絶縁膜386と、ゲート絶縁膜386を介して第1の抵抗領域384aと重畳して設けられたゲート電極392と、ゲート電極392の側面と接する側壁絶縁膜394と、を有する。半導体膜384において、第1の抵抗領域384a、第2の抵抗領域384b、第3の抵抗領域384cの順で抵抗が低くなる。なお、第1の抵抗領域384aは、ゲート電極392にトランジスタ350のしきい値電圧以上の電圧が印加されたときチャネルを形成する。図示しないが、第3の抵抗領域384cと接する一対の電極を設けてよい。

40

#### 【0216】

トランジスタ350として、酸化物半導体膜以外の半導体膜、例えば、多結晶シリコン膜、単結晶シリコン膜、多結晶ゲルマニウム膜、単結晶ゲルマニウム膜などの第14族元素を含む半導体膜を有するトランジスタを用いてもよいし、実施の形態1または実施の形態2で示した酸化物半導体膜を用いたトランジスタを用いてもよい。

#### 【0217】

10

20

30

40

50

また、トランジスタ350に接して層間絶縁膜396が設けられている。なお、層間絶縁膜396は、トランジスタ340の形成面でもあるため、層間絶縁膜396の表面は可能な限り平坦とする。具体的には、層間絶縁膜396の表面は、Raが1nm以下、好ましくは0.3nm以下、さらに好ましくは0.1nm以下であると好ましい。

#### 【0218】

層間絶縁膜396は、単層または積層構造で設ければよく、酸化物半導体膜106と接する層を加熱処理により酸素を放出する絶縁膜とすると好ましい。

#### 【0219】

層間絶縁膜396上にトランジスタ340が設けられている。トランジスタ340が有する一対の電極114のうち一方は、トランジスタ350が有するゲート電極392と接続されている。また、トランジスタ340が有する一対の電極114のうち一方と、層間絶縁膜324と、電極326とによってキャパシタ330が構成されている。なお、図では平行平板型のキャパシタを示すが、容量を大きくするためにスタック型またはトレンチ型のキャパシタを使用してもよい。

10

#### 【0220】

図9(B)は、図9(A)に示す不揮発性メモリの回路図である。不揮発性メモリは、トランジスタTr\_1と、トランジスタTr\_1のゲートと接続するゲート線GL\_1と、トランジスタTr\_1のソースと接続するソース線SL\_1と、トランジスタTr\_2と、トランジスタTr\_2のソースと接続するソース線SL\_2と、トランジスタTr\_2のドレインと接続するドレイン線DL\_2と、キャパシタCと、キャパシタCの一端と接続する容量線CLと、キャパシタCの他端、トランジスタTr\_1のドレインおよびトランジスタTr\_2のゲートと接続するフローティングゲートFGと、を有する。なお、トランジスタTr\_1は、トランジスタ340に相当し、トランジスタTr\_2は、トランジスタ350に相当し、キャパシタCは、キャパシタ330に相当する。

20

#### 【0221】

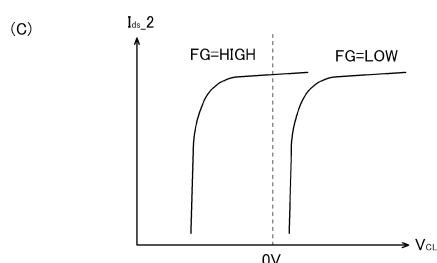

なお、本実施の形態に示す不揮発性メモリは、フローティングゲートFGの電位に応じて、トランジスタTr\_2の見かけ上のしきい値電圧が変動することを利用したものである。例えば、図9(C)は容量線CLの電位V<sub>CL</sub>と、トランジスタTr\_2を流れるドレイン電流I<sub>ds\_2</sub>との関係を説明する図である。

30

#### 【0222】

ここで、フローティングゲートFGは、トランジスタTr\_1を介して、電位を調整することができる。例えば、ソース線SL\_1の電位をVDDとする。このとき、ゲート線GL\_1の電位をトランジスタTr\_1のしきい値電圧V<sub>th</sub>にVDDを加えた電位以上とすることで、フローティングゲートFGの電位をHIGHにすることができる。また、ゲート線GL\_1の電位をトランジスタTr\_1のしきい値電圧V<sub>th</sub>以下とすることで、フローティングゲートFGの電位をLOWにすることができる。

#### 【0223】

そのため、FG = LOWで示したV<sub>CL</sub> - I<sub>ds\_2</sub>カーブと、FG = HIGHで示したV<sub>CL</sub> - I<sub>ds\_2</sub>カーブのいずれかを得ることができる。即ち、FG = LOWでは、V<sub>CL</sub> = 0Vにてドレイン電流I<sub>ds\_2</sub>が小さいため、データ0となる。また、FG = HIGHでは、V<sub>CL</sub> = 0Vにてドレイン電流I<sub>ds\_2</sub>が大きいため、データ1となる。このようにして、データを記憶することができる。

40

#### 【0224】

ここで、トランジスタTr\_1にトランジスタ340を適用することにより、トランジスタTr\_1のオフ電流を極めて小さくすることができるため、図9(B)に示すフローティングゲートFGに蓄積された電荷がトランジスタTr\_1を通して意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保持することができる。また、トランジスタTr\_1の電界効果移動度が高いため、不揮発性メモリを高速動作させることができる。

#### 【0225】

50

以上のように、本発明の一態様に係るトランジスタを不揮発性メモリに適用することによって、長期間の信頼性が高く、消費電力の小さく、かつ高速動作が可能な不揮発性メモリを得ることができる。

#### 【0226】

本実施の形態は、他の実施の形態と組み合わせて用いても構わない。

#### 【0227】

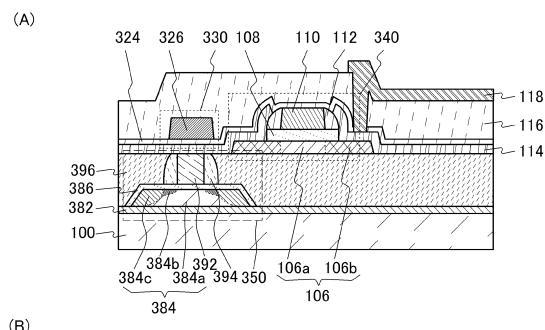

##### (実施の形態4)

実施の形態1または実施の形態2で示したトランジスタ、および実施の形態3で示した半導体装置を少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

10

#### 【0228】

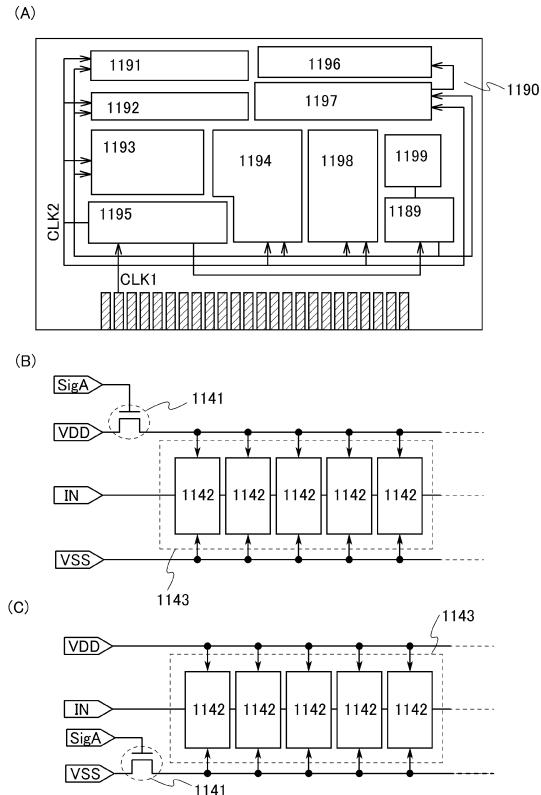

図10(A)は、CPUの具体的な構成を示すブロック図である。図10(A)に示すCPUは、基板1190上に、演算回路(ALU: Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてよい。もちろん、図10(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

20

#### 【0229】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

#### 【0230】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行う。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行う。

30

#### 【0231】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

40

#### 【0232】

図10(A)に示すCPUでは、レジスタ1196に、実施の形態3の半導体装置が設けられている。

#### 【0233】

図10(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。即ち、レジスタ1196が有する半導体装置において、位相反転素子によるデータの保持を行うか、キャパシタによるデータの保持を行うか、を選択する。位相反転素子によるデータの保持を行う場合、レジスタ1196内の半導体装置への電源電圧の供給が行われる。キャパシタによ

50

るデータの保持を行う場合、キャパシタへのデータの書き換えが行われ、レジスタ 1196 内の半導体装置への電源電圧の供給を停止することができる。

#### 【0234】

電源停止に関しては、図 10 (B) または図 10 (C) に示すように、半導体装置群と、電源電位 VDD または電源電位 VSS の与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図 10 (B) および図 10 (C) の回路の説明を行う。

#### 【0235】

図 10 (B) および図 10 (C) では、半導体装置への電源電位の供給を制御するスイッチング素子に、酸化物半導体を活性層に用いたトランジスタを含む記憶回路の構成の一例を示す。

10

#### 【0236】

図 10 (B) に示す記憶装置は、スイッチング素子 1141 と、半導体装置 1142 を複数有する半導体装置群 1143 とを有している。具体的に、各半導体装置 1142 には、実施の形態 3 に示す半導体装置を用いることができる。半導体装置群 1143 が有する各半導体装置 1142 には、スイッチング素子 1141 を介して、ハイレベルの電源電位 VDD が供給されている。さらに、半導体装置群 1143 が有する各半導体装置 1142 には、信号 IN の電位と、ローレベルの電源電位 VSS の電位が与えられている。

#### 【0237】

図 10 (B) では、スイッチング素子 1141 として、実施の形態 1 または実施の形態 2 で示したトランジスタを用いることができる。該トランジスタは、そのゲートに与えられる信号 Sig A によりスイッチングが制御される。

20

#### 【0238】

なお、図 10 (B) では、スイッチング素子 1141 がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子 1141 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

#### 【0239】

また、図 10 (C) には、半導体装置群 1143 が有する各半導体装置 1142 に、スイッチング素子 1141 を介して、ローレベルの電源電位 VSS が供給されている、記憶装置の一例を示す。スイッチング素子 1141 により、半導体装置群 1143 が有する各半導体装置 1142 への、ローレベルの電源電位 VSS の供給を制御することができる。

30

#### 【0240】

半導体装置群と、電源電位 VDD または電源電位 VSS の与えられているノード間に、スイッチング素子を設け、一時的に CPU の動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPU の動作を停止することができ、それにより消費電力を低減することができる。

40

#### 【0241】

また、実施の形態 1 または実施の形態 2 で示したトランジスタ、および実施の形態 3 で示した半導体装置を用いることで、低消費電力で高速動作が可能な CPU を得ることができる。

#### 【0242】

ここでは、CPU を例に挙げて説明したが、DSP (Digital Signal Processor)、カスタム LSI、FPGA (Field Programmable Gate Array) などの LSI にも応用可能である。

#### 【0243】

本実施の形態は、他の実施の形態と組み合わせて用いても構わない。

50

**【0244】**

(実施の形態5)

本実施の形態では、実施の形態3または実施の形態4を適用した電子機器の例について説明する。

**【0245】**

図11(A)は携帯型情報端末である。携帯型情報端末は、筐体500と、ボタン501と、マイクロフォン502と、表示部503と、スピーカ504と、カメラ505と、を具備し、携帯型電話機としての機能を有する。図示しないが、携帯型情報端末のメモリまたはCPUとして実施の形態3で示した半導体装置または実施の形態4に示したCPUを用いることができる。

10

**【0246】**

図11(B)は、デジタルスチルカメラである。デジタルスチルカメラは、筐体520と、ボタン521と、マイクロフォン522と、表示部523と、を具備する。図示しないが、デジタルスチルカメラのメモリとして、実施の形態3に示した半導体装置を用いることができる。

**【0247】**

本発明の一態様に係るトランジスタ、または半導体装置を用いることで、信頼性が高く、高性能の電子機器を得ることができる。

**【0248】**

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

20

**【実施例1】****【0249】**

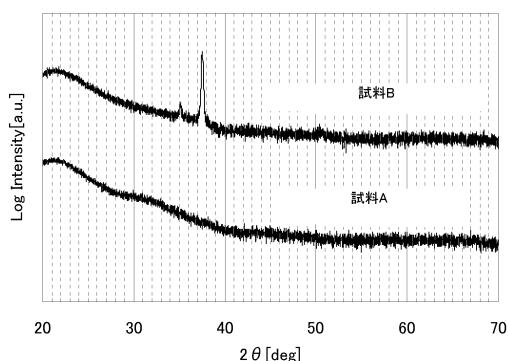

本実施例では、In-Sn-Zn-O膜の結晶状態について説明する。

**【0250】**

まずは、In-Sn-Zn-O膜のX線回折(XRD:X-Ray Diffraction)分析を行った。XRD分析には、Bruker AXS社製X線回折装置D8 ADVANCEを用い、Out-of-Plane法で測定した。

**【0251】**

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

30

**【0252】**

まず、脱水素化処理済みの石英基板を準備した。

**【0253】**

次に、石英基板上にIn-Sn-Zn-O膜を100nmの厚さで成膜した。

**【0254】**

In-Sn-Zn-O膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、In:Sn:Zn=1:1:1[原子数比]のIn-Sn-Zn-Oターゲットを用いた。なお、成膜時の基板加熱温度は室温または200とした。このようにして作製した試料を試料Aとした。

**【0255】**

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を下げずに酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

40

**【0256】**

図19に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2が35deg近傍および37deg~38degに結晶由来のピークが観測された。

**【0257】**

次に、試料Bの透過型電子顕微鏡(TEM:Transmission Electron Microscope)断面像を図20および図21に示す。

50

**【0258】**

図20および図21は、それぞれ50万倍および400万倍のTEM断面像である。なお、TEMは、日立H-9000NARを用い、加速電圧を300kVとした。

**【0259】**

図20および図21に示すように、試料BにおけるIn-Sn-Zn-O膜は様々な結晶方位を有する多結晶であることがわかる。

**【実施例2】****【0260】**

本実施例では、In-Sn-Zn-O膜を酸化物半導体膜に用いたトランジスタの電気的特性について説明する。

10

**【0261】**

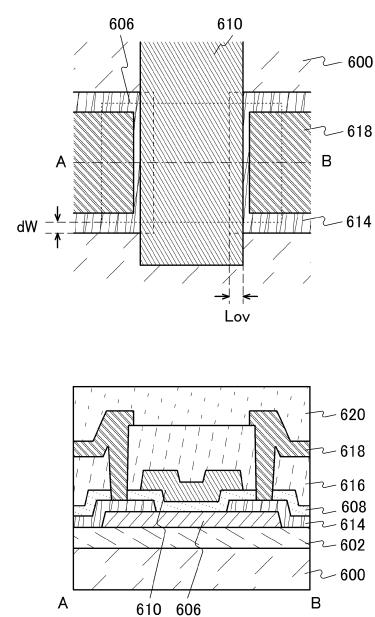

図12は、本実施例で作製したトランジスタの構造を示す上面図および断面図である。図12(A)はトランジスタの上面図である。また、図12(B)は図12(A)の一点鎖線A-Bに対応する断面図である。

**【0262】**

図12(B)に示すトランジスタは、基板600と、基板600上に設けられた下地絶縁膜602と、下地絶縁膜602上に設けられた酸化物半導体膜606と、酸化物半導体膜606と接する一対の電極614と、酸化物半導体膜606および一対の電極614上に設けられたゲート絶縁膜608と、ゲート絶縁膜608を介して酸化物半導体膜606と重畠して設けられたゲート電極610と、ゲート絶縁膜608およびゲート電極610を覆って設けられた層間絶縁膜616と、ゲート絶縁膜608と層間絶縁膜616に設けられた開口部を介して一対の電極614と接続する配線618と、層間絶縁膜616および配線618を覆って設けられた保護膜620と、を有する。

20

**【0263】**

基板600としてはガラス基板を、下地絶縁膜602としては酸化シリコン膜を、酸化物半導体膜606としてはIn-Sn-Zn-O膜を、一対の電極614としてはタンゲステン膜を、ゲート絶縁膜608としては酸化シリコン膜を、ゲート電極610としては窒化タンタル膜とタンゲステン膜との積層構造を、層間絶縁膜616としては酸化窒化シリコン膜とポリイミド膜との積層構造を、配線618としてはチタン膜、アルミニウム膜、チタン膜がこの順で形成された積層構造を、保護膜620としてはポリイミド膜を、それぞれ用いた。

30

**【0264】**

なお、図12(A)に示す構造のトランジスタにおいて、ゲート電極610と一対の電極614との重畠する幅をL<sub>0V</sub>と呼ぶ。同様に、酸化物半導体膜606に対する一対の電極614のはみ出しをd<sub>W</sub>と呼ぶ。

**【0265】**

図12(B)に示す構造のトランジスタの作製方法を以下に説明する。

**【0266】**

まず、基板600の表面に対し、アルゴン雰囲気でプラズマ処理を行った。プラズマ処理は、スパッタリング装置を用い、基板600側にバイアス電力を200W(RF)印加して3分間行った。

40

**【0267】**

続けて、真空状態を保ったまま、下地絶縁膜602である酸化シリコン膜を300nmの厚さで成膜した。

**【0268】**

酸化シリコン膜は、スパッタリング装置を用い、酸素雰囲気で電力を1500W(RF)として成膜した。ターゲットは、石英ターゲットを用いた。なお、成膜時の基板加熱温度は100とした。

**【0269】**

次に、下地絶縁膜602の表面をCMP処理し、Ra=0.2nm程度まで平坦化した。

50

**【0270】**

次に、酸化物半導体膜である In - Sn - Zn - O 膜を 15 nm の厚さで成膜した。

**【0271】**

In - Sn - Zn - O 膜は、スパッタリング装置を用い、アルゴン : 酸素 = 2 : 3 [ 体積比 ] の混合雰囲気で電力を 100W (DC) として成膜した。ターゲットは、In : Sn : Zn = 1 : 1 : 1 [ 原子数比 ] の In - Sn - Zn - O ターゲットを用いた。なお、成膜時の基板加熱温度は 200 とした。

**【0272】**

次に、加熱処理を、250 、 450 または 650 の温度で行った。加熱処理は、はじめに窒素雰囲気で 1 時間の加熱処理を行い、温度を保持したままさらに酸素雰囲気で 1 時間の加熱処理を行った。

10

**【0273】**

次に、フォトリソグラフィ工程によって酸化物半導体膜を加工して、酸化物半導体膜 606 を形成した。

**【0274】**

次に、タンゲステン膜を 50 nm の厚さで成膜した。

**【0275】**

タンゲステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を 1000W (DC) として成膜した。なお、成膜時の基板加熱温度は 200 とした。

**【0276】**

次に、フォトリソグラフィ工程によってタンゲステン膜を加工して、一対の電極 614 を形成した。

20

**【0277】**

次に、ゲート絶縁膜 608 である酸化シリコン膜を 100 nm の厚さで成膜した。なお、酸化シリコン膜の比誘電率は 3.8 とした。

**【0278】**

ゲート絶縁膜 608 である酸化シリコン膜は、下地絶縁膜 602 と同様の方法で成膜した。

。

**【0279】**

次に、窒化タンタル膜およびタンゲステン膜を、この順番でそれぞれ 15 nm および 135 nm の厚さで成膜した。

30

**【0280】**

窒化タンタル膜は、スパッタリング装置を用い、アルゴン : 窒素 = 5 : 1 の混合雰囲気で電力を 1000W (DC) として成膜した。なお、成膜時に基板加熱は行っていない。

**【0281】**

タンゲステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を 4000W (DC) として成膜した。なお、成膜時の基板加熱温度は 200 とした。

**【0282】**

次に、フォトリソグラフィ工程によって窒化タンタル膜およびタンゲステン膜を加工して、ゲート電極 610 を形成した。

40

**【0283】**

次に、層間絶縁膜 616 となる酸化窒化シリコン膜を 300 nm の厚さで成膜した。

**【0284】**

層間絶縁膜 616 となる酸化窒化シリコン膜は、PCVD 装置を用い、モノシラン : 亜酸化窒素 = 1 : 200 の混合雰囲気で電力を 35W (RF) として成膜した。なお、成膜時の基板加熱温度は 325 とした。

**【0285】**

次に、フォトリソグラフィ工程によって層間絶縁膜 616 となる酸化窒化シリコン膜を加工した。

**【0286】**

50

次に、層間絶縁膜 616 となる感光性ポリイミドを 1500 nm の厚さで成膜した。

**【0287】**

次に、層間絶縁膜 616 となる酸化窒化シリコン膜のフォトリソグラフィ工程で用いたフォトマスクを用いて層間絶縁膜 616 となる感光性ポリイミドを露光し、その後現像し、感光性ポリイミド膜を硬化させるために加熱処理を行い、酸化窒化シリコン膜と合わせて層間絶縁膜 616 を形成した。加熱処理は、窒素雰囲気において、300 °C の温度で行った。

**【0288】**

次に、チタン膜、アルミニウム膜およびチタン膜を、この順番でそれぞれ 50 nm、100 nm および 5 nm の厚さで成膜した。

10

**【0289】**

チタン膜は、二層ともにスパッタリング装置を用い、アルゴン雰囲気で電力を 1000 W (DC) として成膜した。なお、成膜時に基板加熱は行っていない。

**【0290】**

アルミニウム膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を 1000 W (DC) として成膜した。なお、成膜時に基板加熱は行っていない。

**【0291】**

次に、フォトリソグラフィ工程によってチタン膜、アルミニウム膜およびチタン膜を加工して、配線 618 を形成した。

**【0292】**

次に、保護膜 620 である感光性ポリイミド膜を 1500 nm の厚さで成膜した。

20

**【0293】**

次に、配線 618 のフォトリソグラフィ工程で用いたフォトマスクを用いて感光性ポリイミドを露光し、その後現像して、保護膜 620 に配線 618 を露出する開口部を形成した。

**【0294】**

次に、感光性ポリイミド膜を硬化させるために加熱処理を行った。加熱処理は、層間絶縁膜 616 で用いた感光性ポリイミド膜に対する加熱処理と同様の方法で行った。

**【0295】**

以上の工程で、図 12 (B) に示す構造のトランジスタを作製した。

30

**【0296】**

次に、図 12 (B) に示す構造のトランジスタの電気的特性を評価した。

**【0297】**

本実施例に示す構造のトランジスタにおける  $V_{g_s}$  -  $I_{d_s}$  特性を測定し、結果を図 13 および図 14 に示す。測定に用いたトランジスタは、チャネル長 L が 3 μm、チャネル幅 W が 10 μm、 $L_o V$  が片側 3 μm (合計 6 μm)、dW が片側 3 μm (合計 6 μm) である。なお、 $V_{d_s}$  は 10 V とした。

**【0298】**

図 13 および図 14 に、トランジスタの  $I_{d_s}$  (実線) および電界効果移動度 (点線) と  $V_{g_s}$  依存性を示す。

40

**【0299】**

ここで、各試料は酸化物半導体膜 606 成膜後に行う加熱処理条件が異なる。試料 1 は加熱処理なしである。なお、試料 2 乃至試料 4 は、それぞれ 250 °C、450 °C、650 °C の温度で加熱処理を行っている。

**【0300】**

ここで、図 13 (A) は試料 1、図 13 (B) は試料 2、図 14 (A) は試料 3、図 14 (B) は試料 4 とそれぞれ対応する。

**【0301】**

試料 1 乃至試料 4 では、全ての試料でトランジスタのスイッチング特性が得られていることがわかる。また、試料 1 と、試料 2 乃至試料 4 と、を比較すると、酸化物半導体膜の成

50

膜後に加熱処理を行うことでトランジスタの電界効果移動度が高くなることがわかる。発明者等は、これが加熱処理により酸化物半導体膜中の不純物濃度を低減されたためである、と考えた。したがって、酸化物半導体膜の成膜後に行う加熱処理によって酸化物半導体膜中の不純物濃度を低減し、その結果、トランジスタの電界効果移動度を理想的な電界効果移動度に近づけることができたとわかる。

### 【0302】

このように、酸化物半導体膜の成膜後に加熱処理を行うことで、酸化物半導体膜中の不純物濃度が低減され、その結果トランジスタの電界効果移動度を高めることができたとわかる。

### 【実施例3】

10

### 【0303】

本実施例では、実施例2で作製した試料1および試料4のトランジスタに対してBT試験を行った。

### 【0304】

本実施例におけるBT試験について説明する。BT試験を行うトランジスタは実施例2で示したトランジスタと同様の構造とした。

### 【0305】

まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行った。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁膜608に印加される電界強度が2MV/cmとなるように $V_{gs}$ に20Vを印加し、そのまま1時間保持した。次に、 $V_{gs}$ を0Vとした。次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 測定を行った。これをプラスBT試験と呼ぶ。

20

### 【0306】

同様に、まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行った。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁膜608に印加される電界強度が-2MV/cmとなるように $V_{gs}$ に-20Vを印加し、そのまま1時間保持した。次に、 $V_{gs}$ を0Vとした。次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 測定を行った。これをマイナスBT試験と呼ぶ。

30

### 【0307】

試料1のプラスBT試験の結果を図15(A)に、マイナスBT試験の結果を図15(B)に示す。また、試料4のプラスBT試験の結果を図16(A)に、マイナスBT試験の結果を図16(B)に示す。なお、図には、BT試験前後の $V_{gs}$ - $I_{ds}$ 特性の変動をわかりやすくするために矢印を付している。

### 【0308】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび-0.42Vであった。また、試料4のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。

### 【0309】

40

試料1および試料4は、BT試験前後におけるしきい値電圧の変動が小さく、信頼性の高いトランジスタであることがわかる。

### 【実施例4】

### 【0310】

本実施例では、実施例2で作製した試料4のトランジスタにおいて、基板温度と電気的特性の関係について評価した。

### 【0311】

測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、LoVが片側3μm(合計6μm)、dWが0μmである。なお、 $V_{ds}$ は10Vとした。なお、基板温度は-40、-25、25、75、125および150で行った。

50

**【0312】**

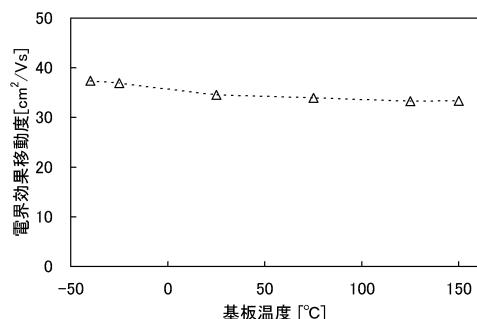

図17に、 $I_{ds}$ （実線）および電界効果移動度（点線）の $V_{gs}$ 依存性を示す。また、図18（A）に基板温度としきい値電圧の関係を、図18（B）に基板温度と電界効果移動度の関係を示す。

**【0313】**

図18（A）より、基板温度が高いほどしきい値電圧は低くなることがわかる。なお、その範囲は0.38V（-40）～-1.08V（150）であった。

**【0314】**

また、図18（B）より、基板温度が高いほど電界効果移動度が低くなることがわかる。なお、その範囲は $37.4 \text{ cm}^2/\text{Vs}$ （-40）～ $33.4 \text{ cm}^2/\text{Vs}$ （150）であった。10

**【0315】**

試料4は、上述の温度範囲において電気的特性の変動が小さいことがわかる。

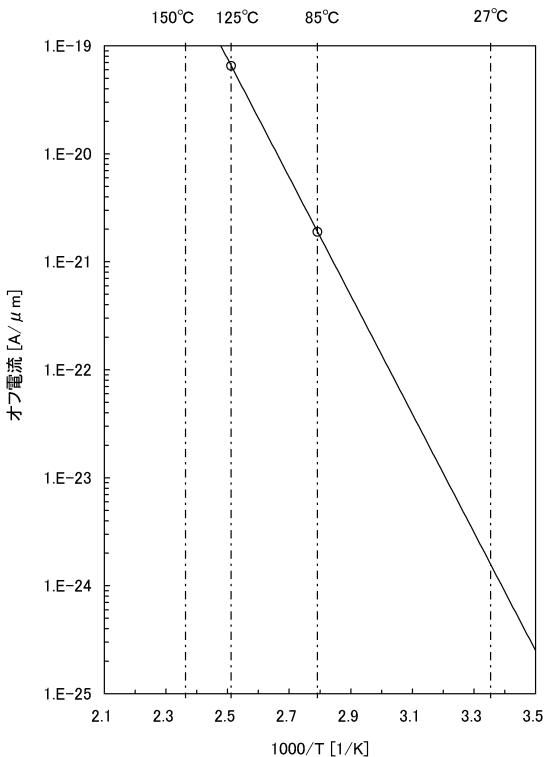

**【実施例5】****【0316】**

本実施例では、In-Sn-Zn-O膜を用いたトランジスタのチャネル幅が1μm当たりのオフ電流を評価した。

**【0317】**

測定に用いたトランジスタの構造は、実施例2の図12に示すトランジスタにおいて、Lが3μm、Wが10cm、LoVが-2μm、dWが0μmである。なお、LoVが-2μmということは、ゲート電極610と一対の電極614の重なりがなく、その幅が片側で2μmずつ（合計4μm）となる構造（いわゆるオフセット領域（Looff）を有する構造）である。20

**【0318】**

なお、本実施例において、酸化物半導体膜606およびゲート絶縁膜608は実施例2とは異なる方法で設けられる。

**【0319】**

以下に、本実施例における酸化物半導体膜606の形成方法について説明する。

**【0320】**

まず、酸化物半導体膜であるIn-Sn-Zn-O膜を15nmの厚さで成膜する。30

**【0321】**

In-Sn-Zn-O膜は、スパッタリング装置を用い、アルゴン：酸素=2:3[体積比]の混合雰囲気で電力を100W(DC)として成膜する。ターゲットは、In:Sn:Zn=1:1:1[原子数比]のIn-Sn-Zn-Oターゲットを用いる。なお、成膜時の基板加熱および成膜後の加熱処理は行っていない。

**【0322】**

次に、フォトリソグラフィ工程によって酸化物半導体膜を加工して、酸化物半導体膜606を形成する。

**【0323】**

同様にゲート絶縁膜608の成膜方法について以下に説明する。40

**【0324】**

まず、ゲート絶縁膜608として酸化窒化シリコン膜を300nmの厚さで成膜する。

**【0325】**

酸化窒化シリコン膜は、PCVD装置を用い、モノシラン：亜酸化窒素=1:200の混合雰囲気で電力を150W(RF)として成膜する。なお、成膜時の基板加熱温度は400とする。

**【0326】**

なお、本実施例において、基板600、下地絶縁膜602、一対の電極614、ゲート電極610、層間絶縁膜616、配線618および保護膜620は、実施例2と同様の方法および同様の材料で設けられる。50

## 【0327】

図22に、トランジスタのオフ電流と測定時に基板温度（絶対温度）の逆数との関係を示す。ここでは、簡単のため測定時に基板温度の逆数に1000を掛けた数値（1000/T）を横軸としている。

## 【0328】

以下にトランジスタのオフ電流の測定方法を簡単に説明する。なお測定対象となるトランジスタを第1のトランジスタと呼ぶ。

## 【0329】

第1のトランジスタのドレインはフローティングゲートFGと接続され、フローティングゲートFGは第2のトランジスタのゲートと接続される。

10

## 【0330】

まず、第1のトランジスタをオフ状態とし、次に、フローティングゲートFGに電荷を与える。なお、第2のトランジスタには一定のドレン電圧が印加されている。

## 【0331】

このとき、フローティングゲートFGの電荷が第1のトランジスタを通じて徐々にリークする。フローティングゲートFGの電荷が抜けると、第2のトランジスタのソース電位が変化する。このソース電位の時間に対する変化量から第1のトランジスタからリークする電荷量が見積もられ、オフ電流を測定することができる。

## 【0332】

図22より、本実施例で示したトランジスタは、チャネル幅が1μm当たりのオフ電流（単位：A/μm）が、測定時の基板温度が85°のとき $2 \times 10^{-21}$ A/μm(22A/μm)であった。

20

## 【0333】

本実施例に示したように、In-Sn-Zn-O膜を用いたトランジスタのオフ電流は極めて小さいことがわかる。

## 【符号の説明】

## 【0334】

|       |         |    |

|-------|---------|----|

| 100   | 基板      |    |

| 102   | 下地絶縁膜   |    |

| 104   | 保護絶縁膜   | 30 |

| 106   | 酸化物半導体膜 |    |

| 106 a | 高抵抗領域   |    |

| 106 b | 低抵抗領域   |    |

| 108   | ゲート絶縁膜  |    |

| 110   | ゲート電極   |    |

| 112   | 側壁絶縁膜   |    |

| 114   | 一対の電極   |    |

| 116   | 層間絶縁膜   |    |

| 118   | 配線      |    |

| 120   | 不純物     | 40 |

| 152   | 下地絶縁膜   |    |

| 154   | 保護絶縁膜   |    |

| 156   | 酸化物半導体膜 |    |

| 158   | ゲート絶縁膜  |    |

| 160   | 導電膜     |    |

| 162   | 絶縁膜     |    |

| 166   | 酸化物半導体膜 |    |

| 200   | 基板      |    |

| 202   | 下地絶縁膜   |    |

| 206   | 酸化物半導体膜 | 50 |

|         |                |    |

|---------|----------------|----|

| 2 0 6 a | 高抵抗領域          |    |

| 2 0 6 b | 低抵抗領域          |    |

| 2 0 8   | ゲート絶縁膜         |    |

| 2 1 0   | ゲート電極          |    |

| 2 1 4   | 一対の電極          |    |

| 2 1 6   | 層間絶縁膜          |    |

| 2 1 8   | 配線             |    |

| 2 2 0   | 不純物            |    |

| 2 5 2   | 下地絶縁膜          |    |

| 2 5 6   | 酸化物半導体膜        | 10 |

| 2 6 0   | 導電膜            |    |

| 2 6 4   | 導電膜            |    |

| 3 2 4   | 層間絶縁膜          |    |

| 3 2 6   | 電極             |    |

| 3 3 0   | キャパシタ          |    |

| 3 4 0   | トランジスタ         |    |

| 3 5 0   | トランジスタ         |    |

| 3 8 2   | 下地絶縁膜          |    |

| 3 8 4   | 半導体膜           |    |

| 3 8 4 a | 抵抗領域           | 20 |

| 3 8 4 b | 抵抗領域           |    |

| 3 8 4 c | 抵抗領域           |    |

| 3 8 6   | ゲート絶縁膜         |    |

| 3 9 2   | ゲート電極          |    |

| 3 9 4   | 側壁絶縁膜          |    |

| 3 9 6   | 層間絶縁膜          |    |

| 5 0 0   | 筐体             |    |

| 5 0 1   | ボタン            |    |

| 5 0 2   | マイクロフォン        |    |

| 5 0 3   | 表示部            | 30 |

| 5 0 4   | スピーカ           |    |

| 5 0 5   | カメラ            |    |

| 5 2 0   | 筐体             |    |

| 5 2 1   | ボタン            |    |

| 5 2 2   | マイクロフォン        |    |

| 5 2 3   | 表示部            |    |

| 6 0 0   | 基板             |    |

| 6 0 2   | 下地絶縁膜          |    |

| 6 0 6   | 酸化物半導体膜        |    |

| 6 0 8   | ゲート絶縁膜         | 40 |

| 6 1 0   | ゲート電極          |    |

| 6 1 4   | 一対の電極          |    |

| 6 1 6   | 層間絶縁膜          |    |

| 6 1 8   | 配線             |    |

| 6 2 0   | 保護膜            |    |

| 1 1 4 1 | スイッチング素子       |    |

| 1 1 4 2 | 半導体装置          |    |

| 1 1 4 3 | 半導体装置群         |    |

| 1 1 8 9 | R O M インターフェース |    |

| 1 1 9 0 | 基板             | 50 |

|         |                |

|---------|----------------|

| 1 1 9 1 | A L U          |

| 1 1 9 2 | A L U コントローラ   |

| 1 1 9 3 | インストラクションデコーダ  |

| 1 1 9 4 | インターフェースコントローラ |

| 1 1 9 5 | タイミングコントローラ    |

| 1 1 9 6 | レジスタ           |

| 1 1 9 7 | レジスタコントローラ     |

| 1 1 9 8 | バスインターフェース     |

| 1 1 9 9 | R O M          |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

(B)

【図16】

(B)

【図17】

【図18】

(B)

【図19】

【図22】

【図23】

【図25】

【図26】

【図27】

【図28】

【図20】

【図21】

【図24】

---

フロントページの続き

| (51)Int.Cl.              | F I                  |

|--------------------------|----------------------|

| H 01 L 27/115 (2006.01)  | H 01 L 29/78 6 2 7 B |

| H 01 L 29/788 (2006.01)  | H 01 L 29/78 6 1 8 B |

| H 01 L 29/792 (2006.01)  | H 01 L 27/10 3 2 1   |

| H 01 L 21/28 (2006.01)   | H 01 L 27/10 6 1 5   |

| H 01 L 29/417 (2006.01)  | H 01 L 27/10 4 3 4   |

| H 01 L 27/10 (2006.01)   | H 01 L 27/10 6 7 1 C |

| H 01 L 27/08 (2006.01)   | H 01 L 27/10 6 7 1 Z |

| H 01 L 21/8234 (2006.01) | H 01 L 29/78 3 7 1   |

| H 01 L 27/088 (2006.01)  | H 01 L 21/28 3 0 1 B |

| H 01 L 51/50 (2006.01)   | H 01 L 29/50 M       |

| H 01 L 27/06 (2006.01)   | H 01 L 27/10 4 8 1   |

|                          | H 01 L 27/10 6 2 1 Z |

|                          | H 01 L 27/10 6 2 5 Z |

|                          | H 01 L 27/10 4 6 1   |

|                          | H 01 L 27/08 3 3 1 E |

|                          | H 01 L 27/08 1 0 2 B |

|                          | H 01 L 27/08 1 0 2 E |

|                          | H 05 B 33/14 A       |

|                          | H 01 L 27/06 1 0 2 A |

(72)発明者 戸松 浩之

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 岩本 勉

(56)参考文献 特開2008-042088(JP, A)

特開2011-091381(JP, A)

特開2008-311342(JP, A)

特開2011-009393(JP, A)

米国特許出願公開第2008/0038882(US, A1)

米国特許出願公開第2011/0068336(US, A1)

國際公開第2009/034953(WO, A1)

特開2008-277665(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336、29/786