## (12) 发明专利

(10) 授权公告号 CN 106664067 B

(45) 授权公告日 2021.06.25

(21) 申请号 201580045640.7

詹姆斯·E·巴特林

(22) 申请日 2015.09.25

(74) 专利代理机构 北京律盟知识产权代理有限公司 11287

(65) 同一申请的已公布的文献号

申请公布号 CN 106664067 A

代理人 沈锦华

(43) 申请公布日 2017.05.10

(51) Int.CI.

H03F 3/45 (2006.01)

(30) 优先权数据

62/055,052 2014.09.25 US

(56) 对比文件

US 8717070 B1, 2014.05.06

14/863,779 2015.09.24 US

US 6462621 B1, 2002.10.08

(85) PCT国际申请进入国家阶段日

US 6515464 B1, 2003.02.04

2017.02.24

US 5559471 A, 1996.09.24

(86) PCT国际申请的申请数据

US 7196577 B2, 2007.03.27

PCT/US2015/052138 2015.09.25

US 8299850 B1, 2012.10.30

(87) PCT国际申请的公布数据

US 2011241916 A1, 2011.10.06

W02016/049412 EN 2016.03.31

CN 103248330 A, 2013.08.14

(73) 专利权人 密克罗奇普技术公司

CN 101860335 A, 2010.10.13

地址 美国亚利桑那州

CN 103001596 A, 2013.03.27

(72) 发明人 布赖恩·克里斯

审查员 伍春燕

权利要求书2页 说明书6页 附图2页

## (54) 发明名称

可选择可编程的增益或运算放大器

## (57) 摘要

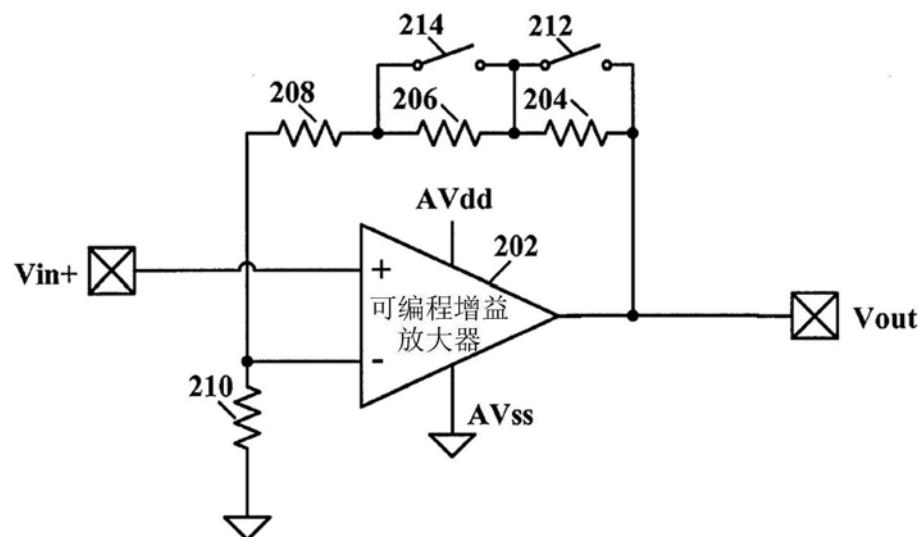

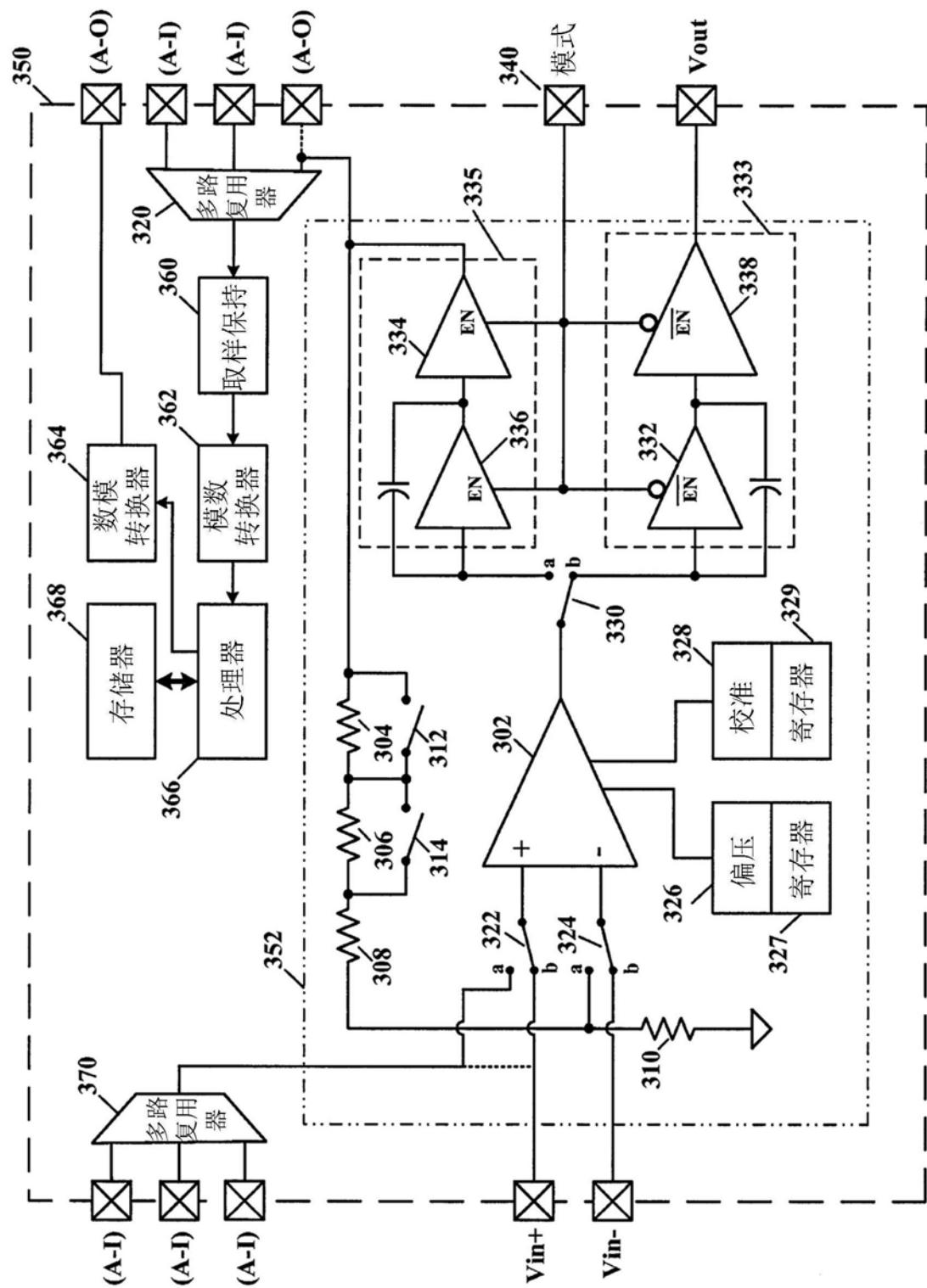

一种可被配置为可编程增益放大器或运算放大器的集成电路放大器(352)包括两个输出块，一个输出块经优化以用于可编程增益放大器操作，且另一输出块经优化以用于运算放大器应用。共用单一输入级(302)、输入偏移校准电路(328)及偏压产生电路(326)与任一放大器配置一起使用。因此，消除所述输入级、偏移校准电路及偏压产生电路的重复，同时仍可选择地提供可编程增益放大器或运算放大器配置。

1. 一种可配置放大器，其包括：

差分输入级，其具有非反相输入、反相输入和输出；

第一输出块，其包括至少一个被配置为由具有第一逻辑状态的模式控制信号启用的输出驱动器；

可配置反馈网络，其与所述第一输出块的输出耦合；

第二输出块，其包括至少一个被配置为由具有第二逻辑状态的模式控制信号启用的输出驱动器；

多个开关，其耦合到所述差分输入级的所述非反相输入、所述反相输入和所述输出、所述可配置反馈网络、所述第一输出块及所述第二输出块；

可编程偏压电路，其耦合到所述差分输入级；

可编程校准电路，其耦合到所述差分输入级；

其中至少根据所述模式控制信号的逻辑状态，所述可配置放大器被配置为：

在第一模式时，控制所述多个开关以将所述差分输入级的所述输出与所述第一输出块的输入耦合以及通过所述可配置反馈网络以将所述第一输出块的所述输出与所述差分输入级的所述反相输入耦合，以形成可编程增益放大器，并根据预设的增益放大器设置控制所述偏压电路和所述校准电路，以及关闭所述第二输出块，且

在第二模式时，分别地控制所述多个开关中的至少某些开关以将所述差分输入级的所述输出与所述第二输出块的输入耦合，将所述可配置反馈网络从所述差分输入级解耦，以及将所述差分输入级的所述非反相输入和所述反相输入与包括所述可配置放大器的集成电路的外部连接耦合，以作为运算放大器工作，并根据预设的运算放大器设置控制所述偏压电路和所述校准电路，以及关闭所述第一输出块。

2. 根据权利要求1所述的可配置放大器，其中所述第一输出块包括第一中间级及第一输出级，每一者被配置为由所述模式控制信号启用或关闭，且所述第二输出块包括第二中间级及第二输出级，每一者被配置为由所述模式控制信号启用或关闭。

3. 根据权利要求1所述的可配置放大器，其中所述偏压电路在处于所述第一模式时具有用于所述可编程增益放大器配置的第一组偏压参数，且在处于所述第二模式时具有用于所述运算放大器配置的第二组偏压参数。

4. 根据权利要求3所述的可配置放大器，其中所述第一组偏压参数及所述第二组偏压参数存储在偏压存储器中。

5. 根据权利要求4所述的可配置放大器，其中所述校准电路在处于所述第一模式时具有用于所述可编程增益放大器配置的第一组校准参数，且在处于所述第二模式时具有用于所述运算放大器配置的第二组校准参数。

6. 根据权利要求5所述的可配置放大器，其中所述第一组校准参数及所述第二组校准参数存储在校准存储器中。

7. 根据权利要求6所述的可配置放大器，其中所述第一组校准参数及所述第二组校准参数各自具有输入偏移校准参数。

8. 根据权利要求1所述的可配置放大器，其中所述第一输出块的输出耦合到所述集成电路的第三外部连接。

9. 根据权利要求1所述的可配置放大器，其中所述第二输出块的输出耦合到所述集成

电路的第四外部连接。

10. 根据权利要求1所述的可配置放大器，其进一步包括模式选择输入，所述模式选择输入接收用于在所述第一模式与所述第二模式之间选择的所述模式控制信号。

11. 根据权利要求1所述的可配置放大器，其进一步包括所述第一及所述第二输出块的补偿网络。

12. 一种微控制器集成电路，其包括：

数字处理器及存储器；

模数转换器，其具有耦合到所述数字处理器的数字输出；以及

根据前述权利要求中任一项所述的可配置放大器。

13. 根据权利要求12所述的微控制器集成电路，其进一步包括耦合在所述第一输出块与所述模数转换器之间的多路复用器。

14. 根据权利要求12所述的微控制器集成电路，其进一步包括用于存储所述第一及第二模式的所述多个开关的断开及闭合设置的配置寄存器。

## 可选择可编程的增益或运算放大器

[0001] 相关专利申请案

[0002] 本申请案主张2014年9月25日申请的共同拥有的美国临时专利申请案第62/055,052号的优先权；所述美国临时专利申请案出于所有目的以引用方式并入本文中。

### 技术领域

[0003] 本发明涉及集成电路放大器，且特定来说，涉及包括差分输入、偏压电路、偏移校准电路及可选择为可编程增益放大器(PGA)或运算放大器(Op-Amp)的配置的集成电路放大器。

### 背景技术

[0004] 在小型几何结构过程中，模拟电路的成本因为模拟有源元件与过程不成比例而变得更贵。客户在使用模拟组件时想要最大灵活性。在许多情况中，无法在同一集成电路装置中提供可编程增益放大器(PGA)及运算放大器(Op-Amp)两者的功能，因为制造此种装置成本过大。微控制器提供芯片上系统且可将许多系统组件集成在单个集成电路(例如处理器、存储器)及外围装置(例如接口、模数及数模转换器、振荡器、比较器、定时器等)内。特定来说，微控制器获益于将模拟放大器集成为外围装置。然而，此类模拟放大器如数字元件般与过程不成比例。

### 发明内容

[0005] 因此，需要一种可配置为可编程增益放大器(PGA)或运算放大器(Op-Amp)且具有最小额外成本及半导体裸片基板面的集成电路放大器。

[0006] 根据实施例，一种可配置放大器可包括：差分输入级；第一输出块；第二输出块；多个开关，其耦合到所述差分输入级、所述第一输出块及所述第二输出块；其中在所述多个开关中的某些开关可能以第一模式布置时，所述差分输入级与所述第一输出块可耦合在一起作为可编程增益放大器，且在所述多个开关中的所述某些开关可以第二模式布置时，所述差分输入级与所述第二输出块可耦合在一起作为运算放大器。

[0007] 根据进一步实施例，所述第一输出块可包括第一中间级及第一输出级，且所述第二输出块可包括第二中间级及第二输出级。根据进一步实施例，偏压电路可耦合到所述差分输入级。根据进一步实施例，所述偏压电路可在处于所述第一模式时具有用于所述可编程增益放大器配置的第一组偏压参数且在处于所述第二模式时具有用于所述运算放大器配置的第二组偏压参数。根据进一步实施例，所述第一及第二偏压参数可存储在偏压存储器中。根据进一步实施例，校准电路可耦合到所述差分输入级。

[0008] 根据进一步实施例，所述校准电路可在处于所述第一模式时具有用于所述可编程增益放大器配置的第一组校准参数且在处于所述第二模式时具有用于所述运算放大器配置的第二组校准参数。根据进一步实施例，所述第一及所述第二校准参数可经存储在校准存储器中。根据进一步实施例，所述第一及第二校准参数各自可具有输入偏移校准参数。根

据进一步实施例,所述差分输入级的第一及第二输入可耦合到集成电路的第一及第二外部连接。根据进一步实施例,所述第一输出块的输出可耦合到所述集成电路的第三外部连接。根据进一步实施例,所述第二输出块的输出可耦合到所述集成电路的第四外部连接。

[0009] 根据进一步实施例,可提供用于在所述第一模式与所述第二模式之间选择的模式选择输入。根据进一步实施例,可提供用于所述第一及第二输出块的补偿网络。

[0010] 根据另一实施例,一种微控制器集成电路可包括:数字处理器及存储器;模数转换器(ADC),其具有耦合到所述数字处理器的数字输出;可配置模拟放大器可包括:差分输入级;第一输出块;第二输出块;多个开关,其耦合到所述差分输入级、所述第一输出块及所述第二输出块;其中在所述多个开关中的某些开关可能以第一模式布置时,所述差分输入级与所述第一输出块可耦合在一起作为可编程增益放大器,且在所述多个开关中的所述某些开关可能以第二模式布置时,所述差分输入级与所述第二输出块可耦合在一起作为运算放大器;且所述处理器控制所述第一及第二模式。

[0011] 根据进一步实施例,多路复用器可耦合在所述第一输出块与所述ADC之间。根据进一步实施例,可提供用于存储所述第一及第二模式的所述多个开关的断开及闭合设置的配置寄存器。根据进一步实施例,集成电路封装可在其上具有多个外部连接。

[0012] 根据进一步实施例,所述差分输入级的第一及第二输入可耦合到所述多个外部连接中的第一及第二连接。根据进一步实施例,所述第一输出块的输出可耦合到所述多个外部连接中的第三连接。根据进一步实施例,所述第二输出块的输出可耦合到所述多个外部连接中的第四连接。根据进一步实施例,可提供用于在所述第一模式与所述第二模式之间选择的模式选择输入。根据进一步实施例,所述多个外部连接中的第五连接可耦合到所述模式选择输入。

[0013] 根据又一实施例,一种用于将放大器配置为可编程增益放大器或运算放大器的方法可包括下列步骤:提供差分输入级;提供第一输出块,其具有可切换地耦合到所述差分输入级的输出的输入;提供第二输出块,其具有可切换地耦合到所述差分输入级的所述输出的输入;且提供多个开关,其耦合到所述差分输入级以及所述第一及第二输出块;在所述多个开关可能以第一模式布置时,将所述差分输入级与所述第一输出块耦合在一起作为可编程增益放大器;及在所述多个开关可能以第二模式布置时,将所述差分输入级与所述第二输出块耦合在一起作为运算放大器。

[0014] 根据所述方法的进一步实施例,其可包括针对所述第一及第二模式将所述差分输入级的偏压参数存储在偏压存储器中的步骤。根据所述方法的进一步实施例,其可包括针对所述第一及第二模式将所述差分输入级的输入偏移校准参数存储在偏移存储器中的步骤。

## 附图说明

[0015] 可通过结合附图参考下文描述获得对本发明的更全面理解,在附图中:

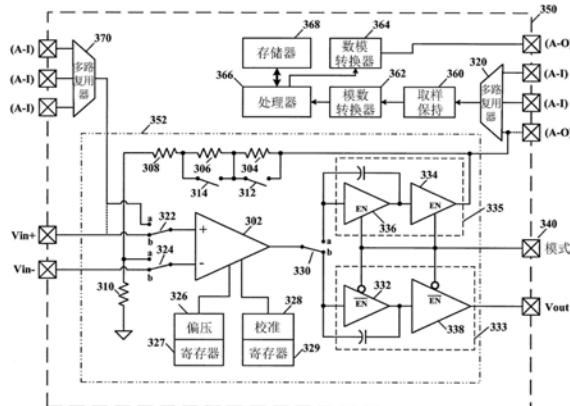

[0016] 图1说明根据本发明的教示的运算放大器(Op-Amp)的示意图;

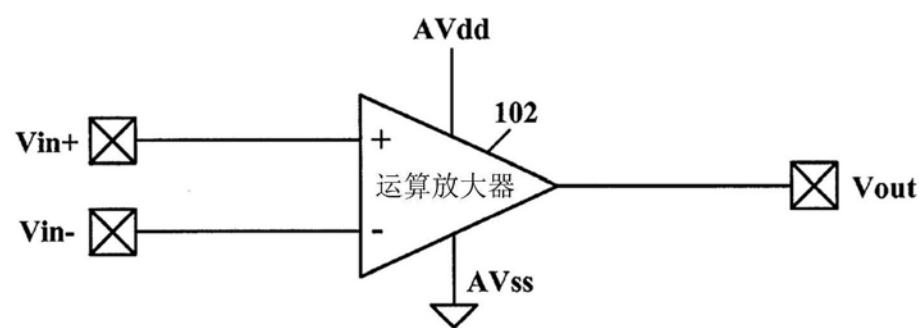

[0017] 图2说明根据本发明的教示的可编程增益放大器(PGA)的示意图;及

[0018] 图3说明根据本发明的具体实例实施例的包括可配置为可编程增益放大器(PGA)或运算放大器(Op-Amp)的放大器的微控制器的示意图及框图。

[0019] 虽然本发明容许各种修改及替代形式,但其具体实例实施例已在附图中加以展示且在本文中详细描述。然而,应理解,本文中具体实例实施例的描述并非意图将本发明限于本文中揭示的特定形式。

## 具体实施方式

[0020] 根据本发明的各种实施例,集成电路放大器具有两个中间级及两个输出级,一个中间级及输出级经优化以用于可编程增益放大器(PGA)操作,且另一中间级及输出级经优化以用于运算放大器(Op-Amp)应用。共用单一输入级、输入偏移校准电路及偏压产生电路可与PGA或Op-Amp配置一起使用。因此,消除输入级、偏移校准电路及偏压产生电路的重复。

[0021] 根据本发明的各种实施例,另一放大器输入级、输入偏移校准电路及偏压产生电路的成本可通过不必将其重复用于放大器配置中的每一者(例如,PGA或Op-Amp配置)而节省。这些电路相当于PGA或Op-Amp的总成本的约百分之八十,因此根据本发明的各种实施例可节省混合信号集成电路的显著量制造成本及显著量装置制造。

[0022] 现在参考附图,示意地说明实例实施例的细节。附图中的相同元件将由相同数字表示,且相似元件将由具有不同小写字母后缀的相同数字表示。

[0023] 参考图1,图中描绘根据本发明的教示的运算放大器(Op-Amp)的示意图。模拟放大器是许多微控制器中所要的外围装置。图1展示可用于微控制器集成电路中的常规运算放大器(Op-Amp)102。Op-Amp 102在微控制器集成电路中具有灵活用途(通常约10MHz的带宽)。Op-Amp 102可集成为外围装置且然后将仅需要3个外部集成电路封装连接(接脚)。Op-Amp 102通常使用大输出驱动结构以用于耦合到外部低阻抗负载。Op-Amp 102可包括差分输入Vin+及Vin-及单端输出Vout。

[0024] 与微控制器集成的Op-Amp 102的典型应用可例如但不限于控制功能,例如马达控制。在马达控制应用中,具有两个输入节点及一个输出节点的三节点Op-Amp 102提供最大设计灵活性。通常,马达应用具有例如但不限于10MHz增益带宽(GBW)的有限带宽需求,且输出驱动器具有高电流容量以处置来自微控制器集成电路外部的较高电流汲取负载。

[0025] 参考图2,图中描绘根据本发明的教示的可编程增益放大器(PGA)的示意图。PGA202提供具有在模拟信号应用中容易且具成本效益的实施方案的设计灵活性。图2展示可用于微控制器集成电路中的常规PGA。PGA 202包括可具有约100MHz的增益带宽(GBW)的单一输入增益块。在微控制器应用中,来自PGA的输出信号可在内部使用,且因此,此装置将需要仅一个外部集成电路封装连接(接脚)。通常,在微控制器应用中,PGA具备用于驱动低功率内部模拟电路(例如多路复用器、取样保持、模数转换器(ADC)等)的小输出驱动器。

[0026] PGA 202包括经配置为具有由反馈回路电阻器204、206、208及210提供的可选择增益的非反相单一输入放大器的差分输入放大器,其中电阻器204、206及208的不同组合可用于选择不同固定增益。所展示的是分别接通及断开反馈回路的电阻器204及206以提供多达四个不同固定增益的两个增益选择开关212及214。

[0027] PGA 202使用可参考共用电源或接地的模拟信号的一个输入。通常,PGA 202的输出经内部耦合到另一模拟电路(例如,模数转换器)或耦合到具有到模数转换器(ADC)的输出的模拟多路复用器的输入,或耦合到ADC与PGA 202输出之间的取样保持电路。因此,对PGA 202输出的利用可无需外部集成电路封装连接。因此,仅一个外部封装连接(接脚)可能

是必要的,借此最小化微控制器集成电路封装接脚计数。

[0028] 与微控制器集成的PGA 202的典型应用可例如但不限于模拟数据获取、开关模式电源(SMPS)电压及电流反馈测量。在SMPS应用中,仅需要外部1接脚PGA 202。在耦合到微控制器集成电路中的模拟多路复用器的输出时,无需连接到其的外部连接。同样地,PGA 202可与模数转换器(例如,取样保持电路)组合使用。来自PGA 202的输出信号通常无需在微控制器封装外部使用,且常相对于接地来测量由PGA 202放大的信号,因此仅一个用于操作PGA 202的外部输入(接脚)是必要的,其最小化微控制器集成电路封装接脚计数。然而,在微控制器集成电路装置中具有两种类型的放大器(PGA及Op-Amp)通常过于昂贵。如上文提及,模拟电路与过程不成比例且小过程昂贵。另外,高输出驱动及大带宽容量需要大量半导体裸片面积及高电力消耗。

[0029] 参考图3,图中描绘根据本发明的具体实例实施例的包括可配置为可编程增益放大器(PGA)或运算放大器(Op-Amp)的放大器的微控制器的示意图及框图。混合信号(模拟及数字)微控制器350可包括可配置为可编程增益放大器(PGA)或运算放大器(Op-Amp)的模拟放大器352、与程序及数据存储器368耦合的数字处理器366、数模转换器(DAC)364、具有耦合到数字处理器366的输出的模数转换器(ADC)362、耦合到ADC 362的输入的取样保持电路360、及多路复用器320及370。根据本发明的教示,本文中考虑更多或更少数目的多路复用器、DAC及ADC。通常,处理器366将具有对前述电路功能的控制。可提供微控制器集成电路上的多个外部连接以用于电源及接地(未展示)以及模拟及数字输入及输出。这些外部连接还可耦合到开关电路(未展示),所述开关电路可经编程以进一步将相应外部连接耦合到内部电路功能(例如,ADC、DAC、多路复用器及串行通信)的输入或输出。

[0030] 可配置模拟放大器352可包括差分输入级302以及相关联的配置逻辑及开关电路,例如:开关304、306、308、322、324及330;电阻器304、306、308及310;偏压电路326、偏压寄存器327、校准电路328、校准寄存器329。此外,提供彼此独立的第一输出块335及第二输出块333。根据一个实施例,每一输出块335及333可分别包括与第一输出级334耦合的第一中间级336及与第二输出级338耦合的第二中间级332。然而,其它实施例可包括输出块335及333中的每一者或一者中的单一组合的输出级或更多级。

[0031] 在图1及图2中展示的Op-Amp 102及PGA 202电路中,输入电路、偏压电路及校准电路在操作上不受输出放大器电路影响。输入电路、偏压电路及校准电路主要是差分输入电路及可为差分输入电路提供偏压及偏移校准的附加电路。针对具有自动输入偏移校准的差分输入放大器的更详细描述,参见James B.Nolan及Kumen Blake共同拥有的标题为“混合信号集成电路装置中的模拟电路的自我自动校准(Self Auto-Calibration of Analog Circuits in a Mixed Signal Integrated Circuit Device)”的美国专利第7,973,684 B2号;且所述专利出于所有目的以引用方式并入本文中。

[0032] 因此,期望最小化微控制器集成电路中的放大器电路“额外负担”的额外重复例项。因而仅需要一个差分输入级302。差分输入级302可使其参数及特性(例如偏压及偏移校准)由一个偏压电路326及一个校准(例如,输入偏移校准)电路328提供。其中每一放大器配置(Op-Amp或PGA)特有的偏压及校准参数可分别存储在偏压寄存器(例如,存储器)327及校准寄存器329中。

[0033] 在图3中,根据一个实施例,展示具有两组中间级336及332以及两组输出级334及

338的放大器352,一组(336、334)经优化以用于PGA类操作,另一组(332、338)经优化以用于0p-Amp类操作。然而,如上文陈述,可按不同方式配置两个输出块335及333。PGA组(336、334)可为高速(例如,100MHz GBW),但不具有显著输出驱动能力,0p-Amp组(332、338)为低速(例如,10MHz GBW),但具有良好外部负载驱动能力。每一中间组及输出组可具有其自身的补偿网络以确保其稳定操作。配置寄存器(未展示)可经实施以向0p-Amp及PGA配置(例如但不限于模式、增益、偏移校准等)提供独立配置参数。

[0034] “模式”控制信号340可用于选择所要的0p-Amp或PGA配置且实现放大器352的适当分段。在一个实施例中,模式控制信号340输入可在外部,且在另一实施例中,其可在内部受控制而无需外部控制连接。在进一步实施例中,前述模式控制信号340的两个连接可供设计者/用户用于选择使用内部控制输入还是外部控制输入。

[0035] 在替代例中,装置配置寄存器(未展示)可用于选择哪个放大器配置以及PGA或0p-Amp模式布置等所需要的其它微控制器配置参数(例如输入-输出类型、多路复用器/ADC/DAC及内部开关(例如,开关312、314、322、324及330))。可通过可出于多个其它目的由微控制器使用的串行端口(未展示)存取装置配置寄存器(未展示)。本文揭示的各种实施例提供最大应用灵活性且需要最小额外成本及集成电路裸片基板面。开关312、314、322、324及330可以是场效晶体管。

[0036] 根据一些实施例,放大器352的一个、两个或三个节点可在其任一操作模式中以外部方式耦合。举例来说,可提供装置配置寄存器(未展示,但与上文描述的装置配置寄存器相同或相似),其允许选择放大器352中的哪些节点将与微控制器350IC封装中的哪些外部连接(接脚)耦合。还可取决于操作模式固定对外部接脚的指派,例如在放大器352的0p-Amp操作模式中可在外部指派三个(3)接脚,且在PGA操作模式中仅指派一个或两个接脚。

[0037] 在开关322、324及330位于“b”位置中(如在图3中展示)且模式选择信号340低、借此启用第二输出块333时,放大器352被配置为0p-Amp。因而差分输入级302的正(+)输入被耦合到Vin+外部连接,差分输入级302的负(-)输入被耦合到Vin-外部连接,差分输入级302的输出被耦合到第二输出块333的输入,且第二输出块333的输出被耦合到Vout外部连接。因此,标准0p-Amp配置被提供于微控制器350中,其中到微控制器350的所有必要连接提供为两个外部输入(Vin+、Vin-)及一个外部输出(Vout)。第二输出块333通常具有较高输出能力,因为第二输出级338比PGA配置中所用的较小容量第一输出级334具有更大电流处置容量且能够驱动更多外部负载。

[0038] 在开关322、324及330位于“a”位置中且模式选择信号340高、借此启用第一输出块335时,放大器352被配置为可编程增益放大器(PGA)。在一个实施例中,仅差分输入级302的正(+)输入被耦合到多路复用器370的输出,或在另一实施例中被耦合到Vin+外部连接(展示为虚线)。多路复用器370可具有耦合到多个外部连接的多个模拟输入。接着,这些多个模拟输入(A到I)中的任一者的选择可被提供到差分输入级302的正(+)输入。差分输入级302的负(-)输入耦合到增益设置反馈网络电阻器310及308,其中其它两个增益设置反馈电阻器306及304分别使用开关314及312接通或断开增益设置反馈网络。

[0039] 在一个实施例中,第一输出块335的输出耦合到增益设置反馈网络电阻器304且耦合到多路复用器320的输入。在另一实施例中,第一输出块335的输出耦合到电阻器304,且任选地可在耦合到或未耦合到多路复用器320的输入的情况下耦合到模拟输出外部连接

(A-0) (在图3中展示为虚线)。在耦合到多路复用器320的输入时,第一输出块335的驱动能力无需与通常用于驱动外部负载的第二输出块333 (Op-Amp) 的输出驱动能力一样大。通过外部连接 (A-I) 的多个模拟输入可提供到多路复用器320及370。可由处理器366控制多路复用器320及370。模拟信号输出 (例如,DAC 364、来自第二输出块333的输出 (Vout)、来自第一输出块335的输出) 可耦合到外部连接 (A-0)。用于数字输入 (D-I) 及输出 (D-O) 以及可配置模拟输入-输出 (A-I/O) 及数字输入-输出 (D-I/O) 的外部连接未在本文中展示但已予以考虑。操作所选择的可配置模拟放大器352模式所不需要的外部连接可通过可由处理器366控制的相应输入-输出配置多路复用器 (未展示) 用于其它信号/功能目的。

图1

图2

图3