(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5418073号

(P5418073)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

(51) Int.Cl.

H03M 1/74 (2006.01)

H04N 5/378 (2011.01)

F 1

H03M 1/74

H04N 5/335 780

請求項の数 6 (全 16 頁)

(21) 出願番号 特願2009-198869 (P2009-198869)

(22) 出願日 平成21年8月28日 (2009.8.28)

(65) 公開番号 特開2011-50007 (P2011-50007A)

(43) 公開日 平成23年3月10日 (2011.3.10)

審査請求日 平成24年8月21日 (2012.8.21)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100080160

弁理士 松尾 憲一郎

(72) 発明者 松本 静徳

神奈川県横浜市保土ヶ谷区神戸町134

ソニーエルエスアイデザイン株式会社内

(72) 発明者 宮崎 親雄

神奈川県横浜市保土ヶ谷区神戸町134

ソニーエルエスアイデザイン株式会社内

審査官 船越 亮

最終頁に続く

(54) 【発明の名称】 DA変換器及び固体撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基準電流を発生する基準電流発生回路と、

前記基準電流に応じた電流を供給する複数の電流源と、

供給される電流に応じた電圧を出力する電圧出力回路と、

前記電流源毎に設けられ、前記電流源の接続先を前記電圧出力回路とするか所定負荷とするかを切り替える複数の切替回路と、

入力されるデジタル信号に基づいて、前記複数の切替回路を制御して、前記複数の電流源のうち前記電圧出力回路へ接続する電流源を選択し、前記デジタル信号に応じた電圧を前記電圧出力回路から出力させる制御部と、を備え、

前記複数の電流源は、前記基準電流に応じた電流値の第1電流源と、前記第1電流源の電流値に比例する電流値の複数の第2電流源とを含み、

前記第1電流源は、前記第2電流源の電流値を第1電流値と第2電流値とで切り替える切替回路を有し、

前記制御部からの制御信号に基づき、前記基準電流発生回路の動作を停止させることなく、前記複数の電流源のうち少なくとも1つの電流源の動作を停止させるスイッチを設けてあり、

前記第1電流源は、前記第1電流源の動作停止に伴う前記基準電流への影響を抑制するために設けられる第1電流伝達回路を介して前記基準電流発生回路に接続されており、

前記第2電流源は、前記第2電流源の動作停止に伴う前記第1電流源への影響を抑制す

10

20

るために設けられる第2電流伝達回路を介して前記第1電流源に接続されており、

前記スイッチは、前記第1電流源の動作を停止するスイッチと、各前記第2電流源に対応して複数設けられ、前記制御部からの制御信号に基づき各前記第2電流源の動作を個別に停止するスイッチであるDA変換器。

【請求項2】

前記電圧出力回路に正電流又は負電流を供給して、オフセットレベルを補正するオフセット調整用電流源と、

前記制御部からの制御信号に基づき、前記オフセット調整用電流源の動作を停止させるスイッチを設けた請求項1に記載のDA変換器。

【請求項3】

10

入射光量を電気信号に変換するマトリクス状に配置された複数の画素と、

前記複数の画素を行毎に選択制御する行走査回路と、

入力されるデジタル信号に応じた参照電圧を生成するDA変換器と、

前記画素から得られるアナログ信号と前記DA変換器で生成された参照電圧とを比較し、デジタル信号に変換する複数のAD変換器と、を備え、

前記DA変換器は、

基準電流を発生する基準電流発生回路と、

前記基準電流に応じた電流を供給する複数の電流源と、

供給される電流に応じた電圧を出力する電圧出力回路と、

前記電流源毎に設けられ、前記電流源の接続先を前記電圧出力回路とするか所定負荷とするかを切り替える複数の切替回路と、

20

入力されるデジタル信号に基づいて、前記複数の切替回路を制御して、前記複数の電流源のうち前記電圧出力回路へ接続する電流源を選択し、前記デジタル信号に応じた電圧を前記電圧出力回路から出力させる制御部と、を備え、

前記複数の電流源は、前記基準電流に応じた電流値の第1電流源と、前記第1電流源の電流値に比例する電流値の複数の第2電流源とを含み、

前記第1電流源は、前記第2電流源の電流値を第1電流値と第2電流値とで切り替える切替回路を有し、

前記制御部からの制御信号に基づき、前記基準電流発生回路の動作を停止させることなく、前記複数の電流源のうち少なくとも1つの電流源の動作を停止させるスイッチを設けており、

30

前記第1電流源は、前記第1電流源の動作停止に伴う前記基準電流への影響を抑制するために設けられる第1電流伝達回路を介して前記基準電流発生回路に接続されており、

前記第2電流源は、前記第2電流源の動作停止に伴う前記第1電流源への影響を抑制するために設けられる第2電流伝達回路を介して前記第1電流源に接続されており、

前記スイッチは、前記第1電流源の動作を停止するスイッチと、各前記第2電流源に対応して複数設けられ、前記制御部からの制御信号に基づき各前記第2電流源の動作を個別に停止するスイッチである固体撮像装置。

【請求項4】

40

前記制御部は、前記行走査回路による各行毎の動作において前記画素が選択されない水平プランキング期間に、前記スイッチを制御して電流源の動作を停止する請求項3に記載の固体撮像装置。

【請求項5】

前記制御部は、前記行走査回路による各フレーム毎の動作において前記デジタル信号の出力が行われない垂直プランキング期間に、前記スイッチを制御して電流源の動作を停止する請求項3又は4に記載の固体撮像装置。

【請求項6】

前記電圧出力回路に正電流又は負電流を供給して、オフセットレベルを補正するオフセット調整用電流源と、

前記制御部からの制御信号に基づき、前記オフセット調整用電流源の動作を停止させる

50

スイッチを設けた請求項 3 ~ 5 のいずれか 1 項に記載の固体撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、D A 変換器及び固体撮像装置に関する。詳細には、電流制御型 D A 変換器及びそれを備えた固体撮像装置に関する。

【0002】

従来より、電流制御型 D A (デジタル - アナログ) 変換器が知られている。この電流制御型 D A 変換器は、電流加算型 D A 変換器とも呼ばれる(例えば、特許文献 1 参照)。

【0003】

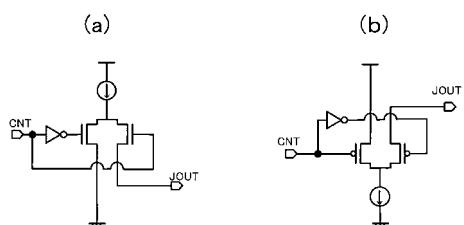

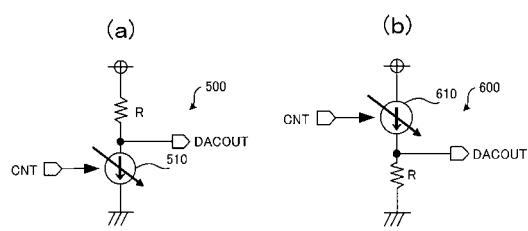

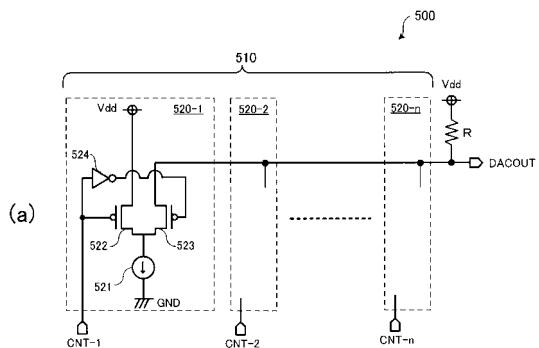

図 11 に電流制御型 D A 変換器の簡易回路図を示す。図 11 (a) は電源基準型の D A 変換器 500 であり、図 11 (b) はグランド基準型の D A 変換器 600 である。これらの D A 変換器 500, 600 は、いずれも、内部に可変電流源 510, 610 を有している。そして、制御信号 CNT に基づいて内部の可変電流源 510, 610 を制御し、出力部に配置した抵抗 R に流れる電流を変更する。これにより、抵抗 R に印加される電圧を変化させて、出力端子 D A C O U T に所望の電圧レベルを発生させるようにしている。

【0004】

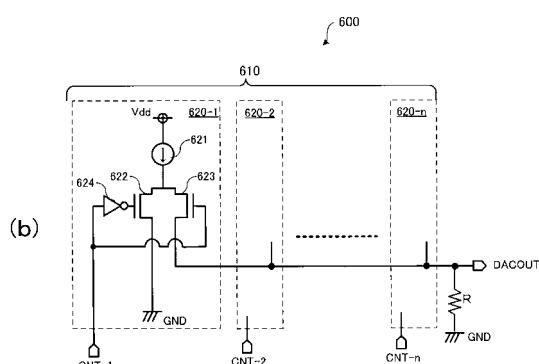

可変電流源 510 は、図 12 (a) に示すように、複数の電流源部 520 - 1 ~ 520 - n を有している。可変電流源 510 では、外部から入力される制御信号 CNT - 1 ~ CNT - n により電流源部 520 - 1 ~ 520 - n を制御することで、抵抗 R に流れる電流を制御している。また、可変電流源 610 は、図 12 (b) に示すように、複数の電流源部 620 - 1 ~ 620 - n を有している。可変電流源 610 では、外部から入力される制御信号 CNT - 1 ~ CNT - n により電流源部 620 - 1 ~ 620 - n を制御することで、抵抗 R に流れる電流を制御している。

【0005】

以下、図 12 (a) の構成を例にとり、その具体的な構成及び動作について説明する。なお、以下においては、電流源部 520 - 1 ~ 520 - n のうち任意の電流源を電流源部 520 と呼ぶ。また、制御信号 CNT - 1 ~ CNT - n のうち任意の電流源を制御信号 CNT という。

【0006】

電流源部 520 は、定電流源 521 と、一対の PMOS トランジスタ 522, 523 とインバータ回路 524 とから構成される。PMOS トランジスタ 522, 523 はソースが定電流源 521 に接続される。また、PMOS トランジスタ 522 はドレインが電源 Vdd に接続され、PMOS トランジスタ 523 はドレインが出力端子 D A C O U T に接続される。そして、制御信号 CNT に対して背反制御を行うために、PMOS トランジスタ 522, 523 のゲート間にインバータ回路 524 を設けている。

【0007】

このように電流源部 520 が構成されているため、制御信号 CNT の状態によりオン状態とする PMOS トランジスタが切り替わる。すなわち、制御信号 CNT が L レベルのときには、PMOS トランジスタ 522 がオン状態となり、PMOS トランジスタ 523 がオフ状態となる。このとき、定電流源 521 と出力端子 D A C O U T との間は接続されず、出力端子 D A C O U T の電圧に影響を及ぼさない。一方、制御信号 CNT が H レベルのときには、PMOS トランジスタ 522 がオフ状態となり、PMOS トランジスタ 523 がオン状態となる。このとき、定電流源 521 と出力端子 D A C O U T との間は接続され、定電流源 521 の電流値に応じた電流が抵抗 R に流れ、出力端子 D A C O U T の電圧レベルが下がる。

【0008】

可変電流源 510 は、以上のように構成されているため、制御信号 CNT - 1 ~ CNT - n により、電流源部 520 - 1 ~ 520 - n を制御することで、抵抗 R へ流す電流を制御することができる。すなわち、制御信号 CNT - 1 ~ CNT - n のうち H レベルにする

10

20

30

40

50

制御信号 CNT の数を増加させることにより、出力端子 D A C O U T の電圧レベルが下がり、H レベルにする制御信号 CNT の数を低減させることにより、出力端子 D A C O U T の電圧レベルが上がる。

【 0 0 0 9 】

このような D A 変換器 500, 600 は、例えば、固体撮像装置などに用いることができる。固体撮像装置では、例えば、D A 変換器から階段状に変化させた参照電圧を出力させ、画素アレイ部の各画素から読み出したアナログ信号と比較する。そして、その比較時間に応じて画素アレイ部の各画素から読み出したアナログ信号の電圧値を検出してデジタル値として出力する（例えば、特許文献 2 参照）。

【先行技術文献】

10

【特許文献】

【 0 0 1 0 】

【特許文献 1】特開平 11-261420 号公報

【特許文献 2】特開 2005-323331 号公報

【発明の概要】

【発明が解決しようとする課題】

【 0 0 1 1 】

上記電流制御型 D A 変換器 500, 600 においては、制御信号 CNT を変化させて出力端子 D A C O U T に流れる電流を変化させる。

【 0 0 1 2 】

20

このとき、電流源部 520, 620 から見ると、電流の流れ先が基準電位（電源 Vdd, グランド GND）であるのか、抵抗 R であるのかが変わるのである。従って、電流源部 520, 620 が一定の電流を流し続いていることには変わりがない。

【 0 0 1 3 】

このような電流制御型 D A 変換器を、例えば上述のような固体撮像装置に用いた場合、D A 変換が必要ない期間が存在するにもかかわらず、一定の電流を流し続けることになる。そのため、必要な電力を消費してしまうことになる。

【 0 0 1 4 】

そこで、本発明は、かかる課題を解決するために、D A 変換を必要としない期間において、消費電力を低減することができる D A 変換器を提供することを目的とする。

30

【課題を解決するための手段】

【 0 0 1 5 】

上記目的を達成するために、請求項 1 に係る発明は、基準電流を発生する基準電流発生回路と、前記基準電流に応じた電流を供給する複数の電流源と、供給される電流に応じた電圧を出力する電圧出力回路と、前記電流源毎に設けられ、前記電流源の接続先を前記電圧出力回路とするか所定負荷とするかを切り替える複数の切替回路と、入力されるデジタル信号に基づいて、前記複数の切替回路を制御して、前記複数の電流源のうち前記電圧出力回路へ接続する電流源を選択し、前記デジタル信号に応じた電圧を前記電圧出力回路から出力させる制御部と、を備え、前記複数の電流源は、前記基準電流に応じた電流値の第 1 電流源と、前記第 1 電流源の電流値に比例する電流値の複数の第 2 電流源とを含み、前記第 1 電流源は、前記第 2 電流源の電流値を第 1 電流値と第 2 電流値とで切り替える切替回路を有し、前記制御部からの制御信号に基づき、前記基準電流発生回路の動作を停止させることなく、前記複数の電流源のうち少なくとも 1 つの電流源の動作を停止させるスイッチを設けてあり、前記第 1 電流源は、前記第 1 電流源の動作停止に伴う前記基準電流への影響を抑制するために設けられる第 1 電流伝達回路を介して前記基準電流発生回路に接続されており、前記第 2 電流源は、前記第 2 電流源の動作停止に伴う前記第 1 電流源への影響を抑制するために設けられる第 2 電流伝達回路を介して前記第 1 電流源に接続されており、前記スイッチは、前記第 1 電流源の動作を停止するスイッチと、各前記第 2 電流源に対応して複数設けられ、前記制御部からの制御信号に基づき各前記第 2 電流源の動作を個別に停止するスイッチである D A 変換器とした。

40

50

## 【0019】

また、請求項2に係る発明は、請求項1に記載のDA変換器において、前記電圧出力回路に正電流又は負電流を供給して、オフセットレベルを補正するオフセット調整用電流源と、前記制御部からの制御信号に基づき、前記オフセット調整用電流源の動作を停止させるスイッチを設けるものとした。

## 【0020】

また、請求項3に係る発明は、入射光量を電気信号に変換するマトリクス状に配置された複数の画素と、前記複数の画素を行毎に選択制御する行走査回路と、入力されるデジタル信号に応じた参照電圧を生成するDA変換器と、前記画素から得られるアナログ信号と前記DA変換器で生成された参照電圧とを比較し、デジタル信号に変換する複数のAD変換器と、を備え、前記DA変換器は、基準電流を発生する基準電流発生回路と、前記基準電流に応じた電流を供給する複数の電流源と、供給される電流に応じた電圧を出力する電圧出力回路と、前記電流源毎に設けられ、前記電流源の接続先を前記電圧出力回路とするか所定負荷とするかを切り替える複数の切替回路と、入力されるデジタル信号に基づいて、前記複数の切替回路を制御して、前記複数の電流源のうち前記電圧出力回路へ接続する電流源を選択し、前記デジタル信号に応じた電圧を前記電圧出力回路から出力させる制御部と、を備え、前記複数の電流源は、前記基準電流に応じた電流値の第1電流源と、前記第1電流源の電流値に比例する電流値の複数の第2電流源とを含み、前記第1電流源は、前記第2電流源の電流値を第1電流値と第2電流値とで切り替える切替回路を有し、前記制御部からの制御信号に基づき、前記基準電流発生回路の動作を停止させることなく、前記複数の電流源のうち少なくとも1つの電流源の動作を停止させるスイッチを設けてあり、前記第1電流源は、前記第1電流源の動作停止に伴う前記基準電流への影響を抑制するために設けられる第1電流伝達回路を介して前記基準電流発生回路に接続されており、前記第2電流源は、前記第2電流源の動作停止に伴う前記第1電流源への影響を抑制するために設けられる第2電流伝達回路を介して前記第1電流源に接続されており、前記スイッチは、前記第1電流源の動作を停止するスイッチと、各前記第2電流源に対応して複数設けられ、前記制御部からの制御信号に基づき各前記第2電流源の動作を個別に停止するスイッチである固体撮像装置とした。

## 【0021】

また、請求項4に係る発明は、請求項3に記載の固体撮像装置において、前記制御部は、前記行走査回路による各行毎の動作において前記画素が選択されない水平プランキング期間に、前記スイッチを制御して電流源の動作を停止するものである。

## 【0022】

また、請求項5に係る発明は、請求項3又は4に記載の固体撮像装置において、前記制御部は、前記行走査回路による各フレーム毎の動作において前記デジタル信号の出力が行われない垂直プランキング期間に、前記スイッチを制御して電流源の動作を停止するものである。

## 【0026】

また、請求項6に係る発明は、請求項3～5のいずれか1項に記載の固体撮像装置において、前記電圧出力回路に正電流又は負電流を供給して、オフセットレベルを補正するオフセット調整用電流源と、前記制御部からの制御信号に基づき、前記オフセット調整用電流源の動作を停止させるスイッチを設けたものである。

## 【発明の効果】

## 【0027】

本発明によれば、DA変換を必要としない期間において、消費電力を低減することができるDA変換器及びそれを備えた固体撮像装置を提供することを目的とする。

## 【図面の簡単な説明】

## 【0028】

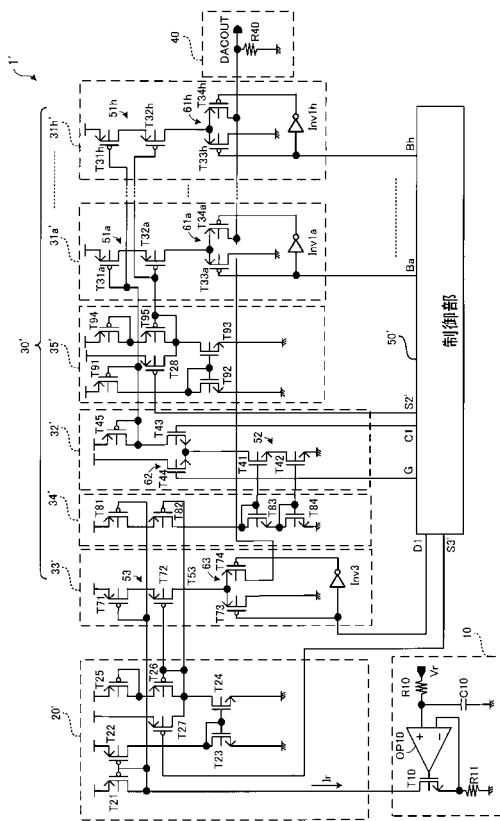

【図1】本発明の一実施形態に係るDA変換器の構成を示す図である。

【図2】電流源を停止するスイッチの他の例を示す図である。

10

20

30

40

50

【図3】電流源を停止するスイッチの他の例を示す図である。

【図4】電流源の他の例を示す図である。

【図5】本発明の一実施形態に係るDA変換器の他の構成を示す図である。

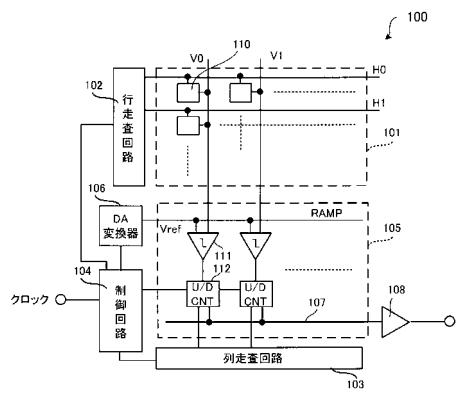

【図6】本発明の一実施形態に係る固体撮像装置の構成を示す図である。

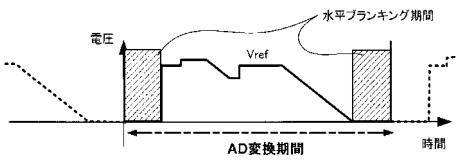

【図7】AD変換処理期間の説明図である。

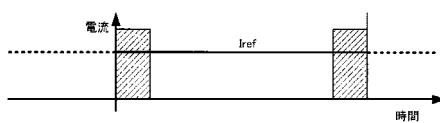

【図8】電流源の動作を停止する期間の説明図である。

【図9】電流源の動作を停止する期間の説明図である。

【図10】AD変換処理期間の説明図である。

【図11】従来の電流制御型DA変換器の簡易回路図である。

【図12】電流制御型DA変換器の構成図である。

10

【発明を実施するための形態】

【0029】

本実施形態に係るDA変換器及び固体撮像装置のDA変換器は、基準電流に応じた電流を供給する複数の電流源と、これらの電流源から供給される電流に応じた電圧を出力する電圧出力回路とを有している。

【0030】

さらに、DA変換器は、上記電流源毎に設けられ、電流源の接続先を電圧出力回路とするか所定負荷とするかを切り替える複数の切替回路と、入力されるデジタル信号に基づいて、これらの切替回路を制御する制御部を有する。

【0031】

そして、この制御部は、複数の電流源のうち電圧出力回路へ接続する電流源を選択し、デジタル信号に応じた電圧を電圧出力回路から出力させる。

20

【0032】

しかも、制御部からの制御信号に基づき、複数の電流源のうち少なくとも1つの電流源の動作を停止させるスイッチを設けている。

【0033】

そのため、DA変換を必要としない期間において、複数の電流源のうち少なくとも1つの電流源の動作を停止させることができるので、消費電力を低減することができる。特に、DA変換を必要としない期間において、複数の電流源の全てを停止させるようにすれば、消費電力の低減率を高めることができる。

30

【0034】

また、本実施形態のDA変換器は、上記基準電流を発生する基準電流発生回路を有しており、基準電流発生回路において基準電流の発生を停止することなく、電流源の動作を制御する。これにより、DA変換を必要としない期間が短い場合であっても、電流源の動作を停止させることができる。すなわち、基準電流発生回路として、基準電圧に応じた基準電流を発生させるフィードバックループを有する基準電流発生回路を用いた場合、基準電流発生回路の動作を停止すると、その後、動作を再開させるまでに時間がかかる。しかし、基準電流発生回路において基準電流の発生を停止することなく、電流源の動作を制御することにより、電流源の動作を迅速に再開させることができる。

40

【0035】

以下、図面を参照して、本発明の実施形態を説明する。なお、説明は以下の順序で行う。

1. 第1実施形態 (DA変換器)

2. 第2実施形態 (DA変換器を有する固体撮像装置)

【0036】

[1. 第1実施形態]

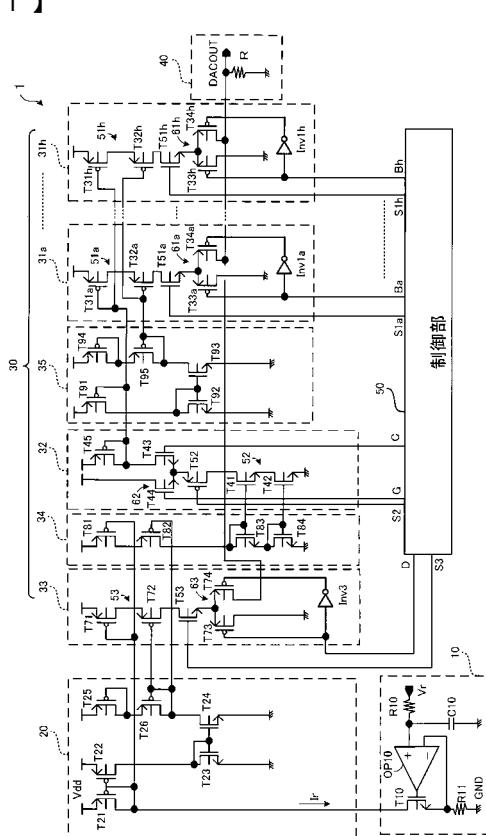

まず、第1実施形態のDA変換器について図1を参照して具体的に説明する。

【0037】

(DA変換器の全体構成)

図1に示すように、第1実施形態のDA変換器1は、基準電流発生回路10と、電流伝

50

達回路部 20 と、電流源部 30 と、電圧出力回路 40、制御部 50 とを有している。

【0038】

基準電流発生回路 10 は、入力される基準電圧  $V_r$  に応じた基準電流  $I_r$  を発生する。基準電流発生回路 10 で発生した基準電流  $I_r$  に応じた電流が、電流伝達回路部 20 を介して電流源部 30 に伝達される。電流源部 30 は複数の電流源を有しており、制御部 50 によって電圧出力回路 40 へ接続する電流源が選択される。電圧出力回路 40 は、抵抗  $R$  により構成され、接続された電流源に応じた電流が抵抗  $R$  に流れる。そして、電圧出力回路 40 は、抵抗  $R$  に生じる電圧を出力端子  $DACOUT$  から出力する。

【0039】

制御部 50 には、 $n$  ビットのデジタル信号が入力される。ここでは、制御部 50 には、4 ビットのデジタル信号が入力されるものとして説明する。制御部 50 は、入力されるデジタル信号に応じた電圧が出力端子  $DACOUT$  から出力されるように、電圧出力回路 40 へ接続する電流源を選択する。

【0040】

電流源部 30 には、同一回路構成である 8 個の第 1 電流源部 31a ~ 31h と、ゲイン切替用の第 2 電流源部 32 と、オフセット調整用の第 3 電流源部 33 とを有しており、それぞれ制御部 50 により制御される。また、電流源部 30 には、電流伝達回路部 20 と第 2 電流源部 32 との間に第 2 電流伝達回路部 34 が設けられ、第 2 電流源部 32 と第 1 電流源部 31a ~ 31h との間に第 3 電流伝達回路部 35 が設けられる。なお、以下において第 1 電流源部 31a ~ 31h のいずれか又は全部をいうときには、第 1 電流源部 31 とする。

【0041】

本実施形態の DA 変換器 1 では、第 1 電流源部 31a ~ 31h 及び第 3 電流源部 33 はそれぞれ電流源 51a ~ 51h, 53 を有している。そして、各電流源 51a ~ 51h, 53 に対応させて、電流源 51a ~ 51h, 53 の接続先を電圧出力回路 40 とするか所定負荷とするかを切り替える切替回路 61a ~ 61h, 63 を有している。電流源 51a ~ 51h は、PMOS トランジスタ T31a ~ T31h と PMOS トランジスタ T32a ~ T32h とがカスコード接続されて構成される。電流源 53 は、PMOS トランジスタ T71, T72 がカスコード接続されて構成される。また、切替回路 61a ~ 61h は、ドレインがグランド GND に接続された PMOS トランジスタ T33a ~ T33h と、ドレインが電圧出力回路 40 に接続された PMOS トランジスタ T34a ~ T34h とを有している。また、切替回路 63 は、ドレインがグランド GND に接続された PMOS トランジスタ T73 と、ドレインが電圧出力回路 40 に接続された PMOS トランジスタ T74 とを有している。なお、以下において、電流源 51a ~ 51h のいずれか又は全部をいうことには、電流源 51 という場合がある。また、切替回路 61a ~ 61h のいずれか又は全部をいうことには、切替回路 61 という場合がある。

【0042】

また、第 2 電流源部 32 は、電流源 52 と、第 1 電流源部 31a ~ 31h の電流源 51a ~ 51h の電流値を 2 段階（第 1 電流値と第 2 電流値）に切り替える切替回路 62 とを有している。電流源 52 は、NMOS トランジスタ T41, T42 がカスコード接続されて構成される。また、切替回路 62 は、ドレインが電源  $Vdd$  に接続された NMOS トランジスタ T44 と、ドレインが PMOS トランジスタ T45 を介して電源に接続された NMOS トランジスタ T43 とを有している。切替回路 62 においては、NMOS トランジスタ T44 をオフ状態としたときに電流源 51 の電流値が第 1 電流値となり、NMOS トランジスタ T44 をオン状態としたときに電流源 51 の電流値が第 2 電流値となる。

【0043】

なお、電流源 52 は第 2 電流伝達回路部 34 により、また、電流源 53 は電流伝達回路部 20 により、それぞれ基準電流  $I_r$  に比例した電流値の電流源となる。また、電流源 51a ~ 51h は、第 3 電流伝達回路部 35 及び切替回路 62 に状態の応じた電流値の電流源であり、この電流値も基準電流  $I_r$  に比例する。

10

20

30

40

50

## 【0044】

第2電流源部32は、制御部50からの制御に基づいて、切替回路62により、第1電流源部31における電流源の電流値を2段階（第1電流値と第2電流値）に切り替える。制御部50は、入力されるデジタル信号の値が7以内のとき、第2電流源部32により第1電流値に切り替える。また、制御部50は、入力されるデジタル信号の値が8以上のとき、第2電流源部32により第2電流値に切り替える。なお、制御部50からゲイン制御線GにLレベルの信号を出力すると、第1電流値に切り替わり、制御部50からゲイン制御線GにHレベルの信号を出力すると、第2電流値に切り替わる。

## 【0045】

制御部50は、第1電流源部31の電流値を第1電流値にしたとき、入力されるデジタル信号の値に応じて、切替回路61a～61hを制御する。これにより、第1電流源部31a～31hが制御され、デジタル信号の値として0～7までに対応する電圧が出力端子D A C O U Tから出力される。また、制御部50は、第1電流源部31の電流値を第2電流値にしたときも同様に、入力されるデジタル信号の値に応じて、切替回路61a～61hを制御する。これにより、第1電流源部31a～31hが制御され、デジタル信号の値として8～15までに対応する電圧を出力端子D A C O U Tから出力される。なお、第1電流源部31a～31hにそれぞれ接続された制御線B a～B hを制御部50から制御することで、出力端子D A C O U Tから出力される電圧が変わる。すなわち、制御線B a～B hのうち制御部50からHレベルの制御信号が出力された制御線に接続された第1電流源部31の電流値を合計した電流値の電流が電圧出力回路40の抵抗Rに流れる。

10

20

## 【0046】

第3電流源部33は、第1電流源部31a～31hに対する制御により出力端子D A C O U Tに発生させた出力電圧のオフセットレベルを補正する。制御部50は、第3電流源部33を制御して、電圧出力回路40に正電流又は負電流を供給して、出力電圧のオフセットレベルを補正する。

## 【0047】

## (電流源の停止制御)

本実施形態のD A変換器1において、切替回路61a～61h, 63によって電流源51a～51h, 53の接続先を電圧出力回路40としない場合でも、所定負荷(P M O SトランジスタT33a～T33h, T73)に接続されて電力の消費が発生する。また、第2電流源部32でも、同様に電力の消費が発生する。

30

## 【0048】

しかしながら、D A変換が必要ない期間が存在するような装置にこのD A変換器1を組み込む場合に、D A変換が必要ない期間も第1電流源部31、第2電流源部32及び第3電流源部33において一定の電流を流し続けると、必要な電力を消費してしまう。

## 【0049】

そこで、本実施形態のD A変換器1では、第1電流源部31a～31h、第2電流源部32、第3電流源部33のそれぞれの動作を停止させて、消費電力を低減することができるよう構成されている。

## 【0050】

第1電流源部31a～31hには停止制御線S1a～S1hが接続されている。制御部50から第1電流源部31a～31hのうち停止させる第1電流源部31を選択し、選択した第1電流源部31に接続された停止制御線S1にLレベルの信号を出力する。これにより、選択された第1電流源部31の動作が停止する。

40

## 【0051】

各第1電流源部31には、電流源51a～51hの動作を停止するために、停止制御線S1a～S1hにそのゲートが接続されたトランジスタT51a～T51hを有している。なお、以下において、トランジスタT51a～T51hのいずれか又は全部をいうことには、トランジスタT51という場合がある。

## 【0052】

50

各トランジスタT51は、それぞれ電流源51と、切替回路61との間に設けられる。そして、このトランジスタT51は、停止制御線S1により制御部50から制御され、電流源51から切替回路61への電流の供給と遮断を切り替える。すなわち、トランジスタT51は、電流源51の動作停止を行うスイッチとして機能する。このように、制御部50は、停止制御線S1a～S1hに出力する制御信号を制御することで、電流源51a～51hの動作を一括又は個別に停止することができる。

#### 【0053】

また、同様に、第2電流源部32には停止制御線S2が接続されており、制御部50から停止制御線S2にHレベルの信号を出力することにより、第2電流源部32の動作が停止する。

10

#### 【0054】

第2電流源部32には、電流源52の動作を停止するために、停止制御線S2にそのゲートが接続されたトランジスタT52を有している。このトランジスタT52は、電流源52と切替回路62との間に設けられる。そして、このトランジスタT52は、停止制御線S2により制御部50から制御され、切替回路62から電流源52への電流の供給と遮断を切り替える。すなわち、トランジスタT52は、電流源52の動作停止を行うスイッチとして機能する。制御部50は、停止制御線S2に出力する制御信号を制御することで、電流源52の動作を停止することができる。電流源52の動作が停止すると、電流源51a～51hの動作も停止する。このように、制御部50は、停止制御線S2を制御することにより、第1電流源部31a～31h及び第2電流源部32の動作を一括して停止することができる。

20

#### 【0055】

また、同様に、第3電流源部33には停止制御線S3が接続されており、制御部50から停止制御線S3にLレベルの信号を出力することにより、第3電流源部33の動作が停止する。

#### 【0056】

第3電流源部33には、電流源53の動作を停止するために、停止制御線S3にそのゲートが接続されたトランジスタT53を有している。このトランジスタT53は、電流源53と切替回路63との間に設けられる。そして、このトランジスタT53は、停止制御線S3により制御部50から制御され、電流源53から切替回路63への電流の供給と遮断を切り替える。すなわち、トランジスタT53は、電流源53の動作停止を行うスイッチとして機能する。このように、制御部50は、停止制御線S3に出力する制御信号を制御することで、電流源53の動作を停止することができる。

30

#### 【0057】

一方、基準電流発生回路10は、制御部50により、第1電流源部31、第2電流源部32、第3電流源部33の動作が停止した場合であっても、継続して基準電流Irを発生する。このようにすることで、電流源部31, 32, 33の動作停止期間が短い場合であっても、電流源部31, 32, 33の動作を迅速に再開させることができる。

#### 【0058】

基準電流発生回路10は、オペアンプOP10の出力端子と反転入力端子(-)とをNMOSトランジスタT10のゲート-ソースを介して接続することでフィードバックループを構成している。オペアンプOP10の非反転入力端子(+)には、基準電圧Vrが入力されており、オペアンプOP10は、抵抗R11に生じる電圧が基準電圧Vrとなるように、出力端子DACOUTから出力する電圧を制御する。これにより、基準電流発生回路10により、基準電圧Vrに応じた基準電流Ir( $Vr / R11$ )が発生する。なお、抵抗R10とコンデンサC10は、オペアンプOP10の非反転入力端子(+)へ入力される基準電圧Vrのノイズを低減させるためのフィルタである。

40

#### 【0059】

この基準電流発生回路10では、このようにフィードバックループを構成している。従って、例えば、基準電流発生回路10に入力する電圧を0Vにして基準電流発生回路10

50

からの基準電流  $I_r$  の発生を停止した後、基準電流発生回路 10 に入力する電圧を基準電圧  $V_r$  にすると、フィードバック制御により所望の基準電流  $I_r$  を発生させるまでに時間がかかる。

#### 【0060】

そこで、本実施形態に係るDA変換器1では、上述したように、電流源部31, 32, 33の動作を停止するときでも、基準電流発生回路10を継続して動作させている。

#### 【0061】

(その他の回路構成)

電流伝達回路部20は、第3電流源部33の動作停止に伴う基準電流  $I_r$  への影響を抑制するために設けられる。

10

#### 【0062】

この電流伝達回路部20は、カレントミラー接続された一対のPMOSトランジスタT21, T22と、同じくカレントミラー接続された一対のNMOSトランジスタT23, T24を有している。また、電流伝達回路部20は、カスコード接続されたPMOSトランジスタT25, T26を有している。PMOSトランジスタT22のドレインはNMOSトランジスタT23のドレインに接続されており、NMOSトランジスタT24のドレインは、PMOSトランジスタT26のドレインに接続されている。そして、電流伝達回路部20が有する複数のカレントミラー回路を経由して、PMOSトランジスタT26が第3電流源部33のPMOSトランジスタT72にカレントミラー接続される。また、PMOSトランジスタT21はPMOSトランジスタT71とカレントミラー接続される。これにより、カスコード接続されたPMOSトランジスタT71, T72が基準電流  $I_r$  に応じた電流値の電流源53として機能する。

20

#### 【0063】

また、第2電流伝達回路部34は、第2電流源部32の動作停止に伴う基準電流  $I_r$  への影響を抑制するために設けられる。

#### 【0064】

この第2電流伝達回路部34では、PMOSトランジスタT21とカレントミラー接続されたPMOSトランジスタT81と、PMOSトランジスタT26とカレントミラー接続されたPMOSトランジスタT82とがカスコード接続されて構成された電流源を備える。また、第2電流伝達回路部34は、カスコード接続されたNMOSトランジスタT83, T84を備える。このNMOSトランジスタT83, T84は、第2電流源部32においてカスコード接続されたNMOSトランジスタT41, T42とそれぞれカレントミラー接続される。これにより、カスコード接続されたNMOSトランジスタT41, T42が基準電流  $I_r$  に応じた電流値の電流源52として機能する。

30

#### 【0065】

また、第3電流伝達回路部35は、第1電流源部31の動作停止に伴う第2電流源部32へ影響を抑制するために設けられる。

#### 【0066】

この第3電流伝達回路部35は、PMOSトランジスタT44とカレントミラー接続されたPMOSトランジスタT91と、カスコード接続された一対のNMOSトランジスタT92, T93を有している。また、第3電流伝達回路部35は、カスコード接続されたPMOSトランジスタT94, T95を有している。PMOSトランジスタT91のドレインはNMOSトランジスタT92のドレインに接続されており、NMOSトランジスタT93のドレインは、PMOSトランジスタT95のドレインに接続されている。そして、第3電流伝達回路部35が有する複数のカレントミラー回路を経由して、PMOSトランジスタT95が第1電流源部31a～31hのPMOSトランジスタT32a～T32hにカレントミラー接続される。また、第2電流源部32のPMOSトランジスタT45は第1電流源部31a～31hのPMOSトランジスタT31a～T31hとカレントミラー接続される。これにより、カスコード接続されたPMOSトランジスタT31a～T31h, T32a～T32hが第1電流値又は第2電流値に応じた電流値の電流源51a

40

50

~ 51 h として機能する。

【0067】

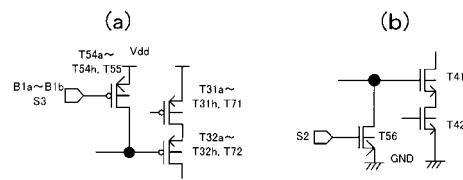

ところで、上述のDA変換器1では、電流源51, 53と切替回路61, 63との間にスイッチとしてNMOSトランジスタT51, T53を設けて、電流源部31, 33を停止するようにしたが、電流源部31, 33の停止は他の方法でも行うことができる。

【0068】

例えば、図2(a)に示すように、電流源51, 53を構成するPMOSトランジスタT32a~T32h, T72のゲートを電源Vddに接続するPMOSトランジスタT54a~T54h, T55を設けるようにしてもよい。この場合、PMOSトランジスタT54a~T54h, T55が電流源51, 53を停止するスイッチとして機能する。

10

【0069】

また、図3(a)に示すように、切替回路61, 63を構成する2つのPMOSトランジスタ(T33a~T33h, T73), (T34a~T34h, T74)の動作を同時に両方停止するために、NAND回路70a~70h, 71を設けるようにしてもよい。この場合、切替回路61, 63をそれぞれ構成する2つのPMOSトランジスタ(T33a~T33h, T73), (T34a~T34h, T74)が電流源51, 53を停止するスイッチとして機能する。

【0070】

また、上述のDA変換器1では、電流源52と切替回路62との間にスイッチとしてPMOSトランジスタT52を設けて、第2電流源部32を停止するようにしたが、第2電流源部32の停止は他の方法でも行うことができる。

20

【0071】

例えば、図2(b)に示すように、電流源52を構成するNMOSトランジスタT41のゲートをグランドGNDに接続するNMOSトランジスタT56を設けるようにしてもよい。この場合、このNMOSトランジスタT56が電流源52を停止するスイッチとして機能する。

【0072】

また、図3(b)に示すように、切替回路62を構成する2つのNMOSトランジスタT43, T44の動作を同時に両方停止するために、NOR回路72を設けるようにしてもよい。この場合、切替回路62を構成する2つのNMOSトランジスタT43, T44が電流源52を停止するスイッチとして機能する。

30

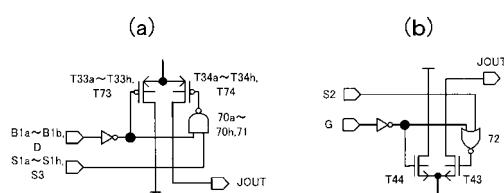

【0073】

上述のDA変換器1では、電流源部31, 33の電流源51, 53を図4(a)に示すグランド基準型の電流源として説明したが、図4(b)に示す電源基準型の電流源を用いてもよい。また、電流源部32の電流源52を図4(b)に示す電源基準型の電流源として説明したが、図4(a)に示すグランド基準型の電流源を用いてもよい。

【0074】

また、上述のDA変換器1では、各電流源部31, 32, 33に電流源51, 52, 53を停止するスイッチを設けることしたが、これに限られない。図5に示すDA変換器1'のように第2電流伝達回路部34'や第3電流伝達回路部35'の動作を停止させることにより、電流源部31', 32', 33'の電流源51, 52, 53を停止させてもよい。

40

【0075】

この場合、第2電流伝達回路部34'の電流源を構成するPMOSトランジスタT82のゲートを電源Vddに接続するPMOSトランジスタT27を設けるようにしてもよい。この場合、PMOSトランジスタT27は電流源51~53を一括して停止するスイッチとして機能する。

【0076】

この場合、第3電流伝達回路部35'の電流源を構成するPMOSトランジスタT95のゲートを電源Vddに接続するPMOSトランジスタT28を設けるようにしてもよい

50

。この場合、PMOSトランジスタT28は電流源51a～51hを一括して停止するスイッチとして機能する。

【0077】

なお、上述したDA変換器1において、電流源部31, 32, 33に対してそれぞれの動作を停止するスイッチを設けることとしたが、これに限られない。例えば、第1電流源部31を停止するスイッチを設けず、第2電流源部32の動作を停止させるスイッチのみで第1電流源部31と第2電流源部32とを同時に停止させるようにしてもよい。

【0078】

[2. 第2実施形態]

次に、第2実施形態の固体撮像装置について図6を参照して具体的に説明する。この固体撮像装置は、CMOSイメージセンサであり、第1実施形態のDA変換器を適用したものである。

10

【0079】

図6に示すように、固体撮像装置100は、撮像部としての画素アレイ部101、行走査回路102、列走査回路103、制御回路104、ADC群105、DA変換器106、水平出力線107、出力アンプ108を有する。DA変換器106は、第1実施形態のDA変換器と同様の構成である。

【0080】

画素アレイ部101には、入射光量を電気信号に変換する単位画素110がマトリクス状に2次元配列されている。単位画素110には、光電変換を行うフォトダイオードと、このフォトダイオードが生成した信号電荷を読み出す転送トランジスタと、この読み出された信号電荷を画素信号に変換するアンプトランジスタ等が設けられている。

20

【0081】

行走査回路102は、複数の単位画素110を行H0, H1, …毎に選択制御する。すなわち、各単位画素110の転送トランジスタは行走査回路102によって制御され、各単位画素110で生成された画素信号が各列毎に設けた列線Vx(列線V0, V1...)からADC群105に出力される。

【0082】

ADC群105は、画素アレイ部101の各列に対応して比較器111及びUDカウンタ112よりなるAD変換器が設けられている。そして、比較器111ではDA変換器106から出力される参照電圧Vrefと画素信号とを比較し、この比較結果をUDカウンタ112に出力する。UDカウンタ112は制御回路104及び列走査回路103の制御に基づいて比較器111からの出力をカウントし、そのカウント値をデジタル信号として水平出力線107を通して出力アンプ108に出力する。なお、DA変換器106は、制御回路104から入力されるデジタル信号に応じた電圧を参照電圧Vrefとして出力する。

30

【0083】

ここで、固体撮像装置100の動作を説明する。

【0084】

固体撮像装置100は、任意の行Hx(行H0, H1, ...)の単位画素110から列線Vxへの1回目の読み出しが安定した後、参照電圧Vrefを時間変化させた階段状の波形RAMPをDA変換器106から比較器111に入力していく。これにより、列線Vxの電圧と、RAMP波形の参照電圧Vrefとの比較を行う。

40

【0085】

動作シーケンスとしては、階段状の波形RAMPとなる参照電圧Vrefの入力開始と同時に、UDカウンタ112で1回目のカウントが開始される。このとき、UDカウンタ112はダウンカウントをする。波形RAMPの参照電圧Vrefが列線Vxの電圧と等しくなったとき、この比較器111の出力は反転し、同時にUDカウンタ112に付属したメモリに比較期間に応じたカウント値が保持される。

【0086】

50

この1回目の読み出し時は、単位画素110のリセット成分  $V_{reset}$  を読み出してあり、  $V_{reset}$  内には、単位画素110毎にばらつくノイズがオフセットとして含まれている。ここで、リセットレベルは全画素共通であり、また  $V_{reset}$  のばらつきは一般に小さいことが分かっているため、1回目の  $V_{reset}$  読み出し時には、波形RAMPの参照電圧  $V_{ref}$  を調整することにより比較期間を短くすることが可能となる。

#### 【0087】

次に、2回目の読み出しほは、  $V_{reset}$  に加え単位画素110毎の入射光量に応じた信号成分を読み出し、1回目の読み出しと同様の動作を行う。すなわち、任意の行  $H_x$  の単位画素110から列線  $V_x$  への2回目の読み出しが安定した後、DA変換器106により参照電圧  $V_{ref}$  を時間変化させた階段状の波形RAMPを入力し、列線  $V_x$  の電圧との比較を比較器111にて行う。階段状の波形RAMPとなる参照電圧  $V_{ref}$  の入力開始と同時に、UDカウンタで2回目のカウントが開始される

10

#### 【0088】

このとき、UDカウンタ112はアップカウントをする。ここで任意の比較器111において波形RAMPの参照電圧  $V_{ref}$  と列線  $V_x$  の電圧が等しくなったとき比較器111の出力は反転し、同時にUDカウンタ112に付属したメモリ内に比較期間に応じたカウントが保持される。

#### 【0089】

この一連の動作において、1回目のカウントと2回目のカウントとでは、メモリ内の同じ場所に保持され、2回目のカウント後の出力値がノイズ成分を除去した純粋な信号量を表すことになる。

20

#### 【0090】

以上のAD変換期間終了後、列走査回路103により、メモリに保持されたnビットのデジタル信号が水平出力線107を経て、外部出力され、その後、順次行毎に同様の動作が繰り返され、2次元画像が生成される。

#### 【0091】

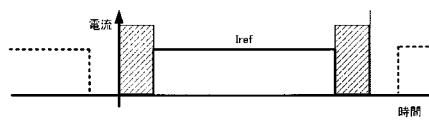

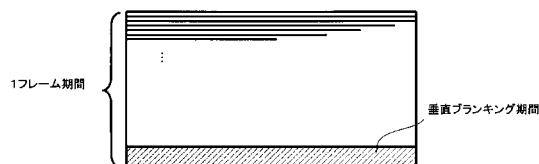

ここで、画素アレイ部101からは、1ライン単位で画素信号が出力される。そして、画素アレイ部101は、ライン単位で画素信号が出力する毎に、図7に示すように、画素信号が出力しない期間がある。この期間は、一般に水平プランキング期間と呼ばれる。

30

#### 【0092】

従って、この水平プランキング期間では、DA変換器106から参照電圧  $V_{ref}$  を出力する必要がない。しかし、上述のように切替回路61, 62, 63(図1参照)の接続先を切り替えるだけでは、図8に示すように、継続して電流源51, 52, 53が動作するため、電力を消費し続ける。

#### 【0093】

そこで、本実施形態に係る固体撮像装置100では、水平プランキング期間において、図9に示すように、DA変換器106内の電流源51, 52, 53の動作を停止させるようしている。具体的には、制御回路104は、DA変換器106を制御して、電流源51, 52, 53の動作を停止させる。なお、制御回路104は、DA変換器106の電流源52を停止させないようにすることもできる。このようにすることで、電流源51の動作停止解除時の動作開始を早めることができる。

40

#### 【0094】

また、画素アレイ部101からは、1フレーム単位の画素信号が出力された後、図10に示すように、画素信号が出力しない期間がある。この期間は、一般に垂直プランキング期間と呼ばれる。

#### 【0095】

従って、この垂直プランキング期間では、DA変換器106から参照電圧  $V_{ref}$  を出力する必要がない。

#### 【0096】

50

そこで、本実施形態に係る固体撮像装置 100 では、垂直プランキング期間において、DA 变換器 106 内の電流源 51, 52, 53 の動作を停止させるようにしている。具体的には、制御回路 104 は、DA 变換器 106 を制御して、電流源 51, 52, 53 の動作を停止させる。なお、制御回路 104 は、DA 变換器 106 の電流源 52 を停止させないようすることもできる。このようにすることで、電流源 51 の動作停止解除時の動作開始を早めることができる。

### 【0097】

以上のように、本実施形態に係る固体撮像装置 100 では、AD 变換が必要ない期間において、DA 变換器 106 内の電流源 51, 52, 53 の動作を停止するため、消費電力を低減することができる。

10

### 【符号の説明】

#### 【0098】

1, 1' DA 变換器

10 基準電流発生回路

20 電流伝達回路部

30 電流源部

40 電圧出力回路

50 制御部

51a ~ 51h, 52, 53 電流源

61a ~ 61h, 62, 63 切替回路

T51a ~ T51h, T53 NMOS トランジスタ (スイッチ)

T52 PMOS トランジスタ (スイッチ)

20

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開2005-286552(JP,A)

特開平06-177766(JP,A)

特開2003-051747(JP,A)

特開平11-122048(JP,A)

特開平02-288616(JP,A)

特開2007-059991(JP,A)

特開2005-109962(JP,A)

特開平05-206860(JP,A)

特開平10-256914(JP,A)

特開平02-311027(JP,A)

特開平06-164401(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88

H04N 5/378