(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6182309号

(P6182309)

(45) 発行日 平成29年8月16日(2017.8.16)

(24) 登録日 平成29年7月28日(2017.7.28)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 21/60 (2006.01)H01L 23/12 501B

H01L 21/92 602D

H01L 21/92 604B

H01L 21/60 311Q

請求項の数 5 (全 14 頁)

(21) 出願番号

特願2012-259682 (P2012-259682)

(22) 出願日

平成24年11月28日 (2012.11.28)

(65) 公開番号

特開2014-107427 (P2014-107427A)

(43) 公開日

平成26年6月9日 (2014.6.9)

審査請求日

平成27年10月28日 (2015.10.28)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 千野 明晃

長野県長野市小島田町80番地 新光電気

工業 株式会社 内

審査官 麻川 倫広

最終頁に続く

(54) 【発明の名称】配線基板、半導体装置及び配線基板の製造方法

(57) 【特許請求の範囲】

【請求項 1】

最外層の配線パターンと、

前記配線パターンの少なくとも一部を接続パッドとして露出する開口部を有するソルダ

レジスト層と、前記接続パッド上に形成されたはんだ層と、柱状に形成され、前記はんだ層によって全

体が被覆された金属ポストとを含むはんだバンプと、

を有し、前記金属ポストの前記接続パッド側の面と前記接続パッドとの間には前記はんだ層が介

在しており、前記はんだバンプは、凹部を有する本体部と、前記本体部の端部から外側に突出した鍔

部とを有する金属層を有し、前記金属ポストは、前記凹部を充填するポスト部と、前記ポスト部よりも大径に形成さ

れ、前記ポスト部上及び前記鍔部上に形成された大径部とを有し、前記ポスト部は、前記鍔部から前記接続パッドに向かって厚さ方向に延びるように形成

され、

前記ポスト部の一部は、前記開口部内に配置されており、

前記はんだ層は錫-銅合金で形成され、

前記金属ポストは銅で形成され、

前記金属層は、錫-銅合金で形成され、且つ前記はんだ層に比べて銅の含有率が高いこ

とを特徴とする配線基板。

【請求項 2】

前記接続パッド上に形成され、前記金属ポストと同じ材料からなる金属膜を有し、

前記はんだ層が前記金属膜上に形成されていることを特徴とする請求項1に記載の配線基板。

【請求項 3】

請求項1又は2に記載の配線基板と、

前記はんだバンプを介して前記接続パッドと電気的に接続され、前記配線基板に実装された半導体チップと、

を有することを特徴とする半導体装置。

10

【請求項 4】

最外層の配線パターンと、前記配線パターンの少なくとも一部を接続パッドとして露出する開口部を有するソルダレジスト層とを有する構造体を準備する工程と、

前記ソルダレジスト層の表面と前記接続パッドの表面とを被覆するシード層を形成する工程と、

前記開口部よりも大径に形成され、前記開口部を露出させる開口パターンを有するレジスト層を前記シード層上に形成する工程と、

前記開口パターンから露出された前記シード層上に第1はんだ層を形成する工程と、

前記第1はんだ層上に、凹部を有する本体部と、前記本体部の端部から外側に突出した鈸部とを有する金属層を形成する工程と、

20

前記第1はんだ層上に、前記凹部を充填するポスト部と、前記ポスト部よりも大径に形成され、前記ポスト部上及び前記鈸部上に形成された大径部とを有する金属ポストを形成する工程と、

前記金属ポスト上に第2はんだ層を形成する工程と、

前記レジスト層を除去する工程と、

前記第1はんだ層及び前記第2はんだ層をマスクにして、前記シード層をエッティングにより除去するとともに、前記金属層の周縁部の一部及び前記金属ポストの周縁部の一部を除去する工程と、

リフロー加熱によって前記第1はんだ層と前記第2はんだ層とを接合することにより、前記金属ポスト全体を被覆する1つの第3はんだ層を形成する工程と、

30

を有し、

前記第3はんだ層を形成する工程では、前記開口部内に一部が配置された前記金属ポスト及び前記金属層を被覆するように前記第3はんだ層が形成され、

前記第1はんだ層と前記金属ポストと前記第2はんだ層とは、前記レジスト層をマスクとし、前記シード層をめっき給電層に利用した電解めっき法により形成され、

前記第1はんだ層は錫-銅合金で形成され、

前記金属ポストは銅で形成され、

前記金属層は、錫-銅合金で形成され、且つ前記第1はんだ層に比べて銅の含有率が高いことを特徴とする配線基板の製造方法。

【請求項 5】

前記金属層を形成する工程では、前記第1はんだ層を形成した後の構造体を、前記第1はんだ層を形成する際に使用しためっき液に浸漬したまま、前記第1はんだ層を形成するときよりも電流密度を低くした状態で電解めっき法を施すことにより、前記金属層を前記第1はんだ層上に形成する工程を有することを特徴とする請求項4に記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板、半導体装置及び配線基板の製造方法に関するものである。

【背景技術】

40

50

## 【0002】

従来、半導体チップ等の他の電子部品と接続されるはんだバンプを有する配線基板が知られている（例えば、特許文献1，2参照）。このような配線基板の製造方法としては、以下のような方法が知られている。

## 【0003】

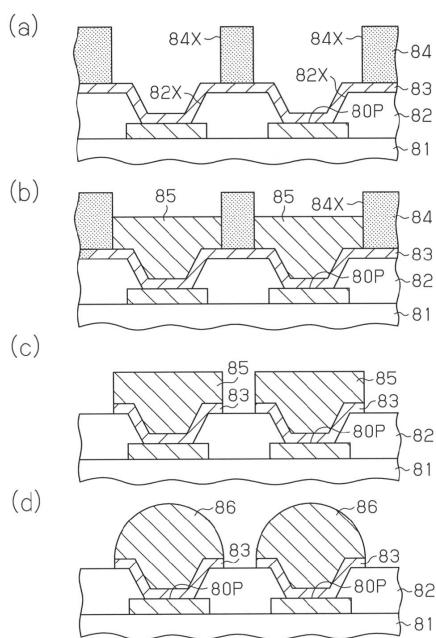

例えば図6(a)に示すように、まず、ビルドアップ配線（図示略）に接続された接続パッド80Pが層間絶縁層81の上に形成され、接続パッド80P上に開口部82Xを有するソルダレジスト層82が形成された構造体を準備する。続いて、開口部82Xの内側面を含むソルダレジスト層82の表面を被覆するようにシード層83を形成し、そのシード層83上に、上記開口部82Xよりも大径に形成された開口部84Xを有するレジスト層84を形成する。10

## 【0004】

次いで、図6(b)に示す工程では、レジスト層84をめっきマスクとし、シード層83をめっき給電層に利用するはんだめっき法（例えば、電解Sn-Cuめっき法）を施し、開口部84Xから露出するシード層83の上面にはんだめっき層85を形成する。続いて、図6(c)に示す工程では、図6(b)に示したレジスト層84及び不要なシード層83を除去する。その後、はんだめっき層85をリフロー加熱することにより、はんだめっき層85を溶融させて接続パッド80Pに接合させる。これにより、図6(d)に示すように、ソルダレジスト層82の上面から突出するはんだバンプ86が得られる。20

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】特開平10-326965号公報

【特許文献2】特開2004-200412号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

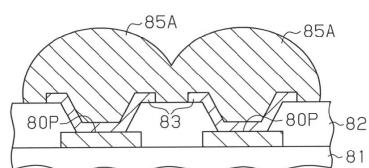

ところで、近年では、半導体チップの高性能化に伴って配線基板の接続パッドの狭ピッチ化が進められている。さらに、半導体チップとの接続の十分な信頼性を得るためにには、配線基板においてソルダレジスト層82の上面からのはんだバンプ86の高さを十分に（例えば、40μm以上）確保する必要がある。しかしながら、接続パッド80Pの狭ピッチ化が進むと、はんだバンプ86を高く形成することが困難になる。すなわち、はんだバンプ86の高さを十分に確保するために上記はんだめっき層85を高く形成した場合には、図7に示すように、隣接するはんだバンプ85A同士がリフロー後にショートしやすくなるという問題が発生する。このため、はんだバンプ86を高く形成することが難しく、高性能な半導体チップの実装に容易に対応できないという問題がある。30

## 【課題を解決するための手段】

## 【0007】

本発明の一観点によれば、最外層の配線パターンと、前記配線パターンの少なくとも一部を接続パッドとして露出する開口部を有するソルダレジスト層と、前記接続パッド上に形成されたはんだ層と、柱状に形成され、前記はんだ層によって全体が被覆された金属ポストとを含むはんだバンプと、を有し、前記金属ポストの前記接続パッド側の面と前記接続パッドとの間には前記はんだ層が介在しており、前記はんだバンプは、凹部を有する本体部と、前記本体部の端部から外側に突出した鍔部とを有する金属層を有し、前記金属ポストは、前記凹部を充填するポスト部と、前記ポスト部よりも大径に形成され、前記ポスト部上及び前記鍔部上に形成された大径部とを有し、前記ポスト部は、前記鍔部から前記接続パッドに向かって厚さ方向に延びるよう形成され、前記ポスト部の一部は、前記開口部内に配置されており、前記はんだ層は錫-銅合金で形成され、前記金属ポストは銅で形成され、前記金属層は、錫-銅合金で形成され、且つ前記はんだ層に比べて銅の含有率が高い。40

**【発明の効果】****【0008】**

本発明の一観点によれば、隣接するはんだバンプ同士のショートを抑制することができるという効果を奏する。

**【図面の簡単な説明】****【0009】**

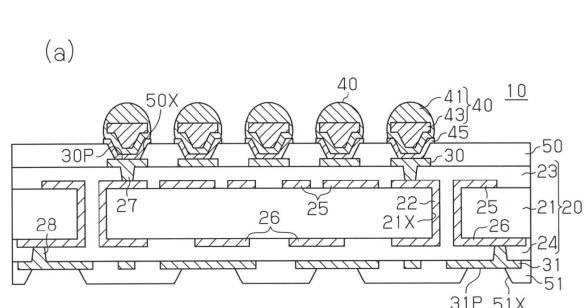

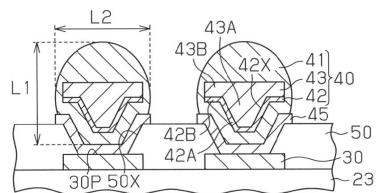

【図1】(a)は、一実施形態の配線基板を示す概略断面図、(b)は、(a)に示した配線基板の一部を拡大した拡大断面図。

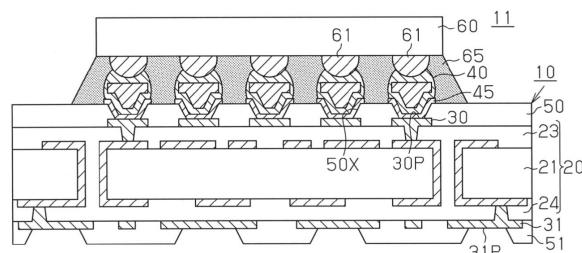

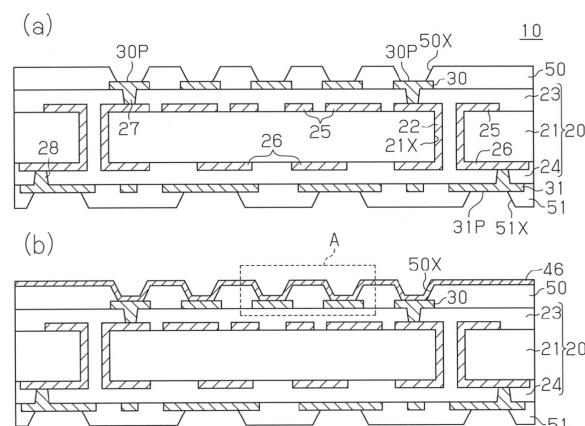

**【図2】一実施形態の半導体装置を示す概略断面図。****【図3】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。**

10

**【図4】(a)～(d)は、一実施形態の配線基板の製造方法を示す概略断面図。****【図5】(a)～(c)は、一実施形態の配線基板の製造方法を示す概略断面図。****【図6】(a)～(d)は、従来の配線基板の製造方法を示す概略断面図。****【図7】従来の配線基板の製造方法の問題点を示す説明図。****【発明を実施するための形態】****【0010】**

以下、一実施形態を添付図面を参照して説明する。

なお、添付図面は、特徴を分かりやすくするために便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを省略している。

20

**【0011】**

まず、配線基板10の構造について説明する。

図1(a)に示すように、配線基板10は、基板本体20と、最上層の配線パターン30と、最下層の配線パターン31と、はんだバンプ40と、ソルダレジスト層50, 51とを有している。

**【0012】**

基板本体20は、コア基板21と、コア基板21の貫通孔21Xに形成された貫通電極22と、コア基板21に積層された複数の絶縁層23, 24と、コア基板21の上面及び下面にそれぞれ形成された配線25, 26と、複数の絶縁層23, 24に形成されたビア27, 28とを有している。基板本体20に設けられた貫通電極22、配線25, 26及びビア27, 28は、配線パターン30と配線パターン31とを電気的に接続している。なお、コア基板21の材料としては、例えばガラスエポキシ樹脂などの絶縁性樹脂を用いることができる。また、貫通電極22、配線25, 26及びビア27, 28の材料としては、例えば銅(Cu)や銅合金を用いることができる。また、絶縁層23, 24の材料としては、例えばエポキシ系樹脂やポリイミド系樹脂などの絶縁性樹脂を用いることができる。

30

**【0013】**

配線パターン31は、基板本体20の下面側に設けられている。この配線パターン31は、当該配線基板10をマザーボード等の実装用基板に実装する際に使用されるはんだボールやリードピン等の外部接続端子を配設するための外部接続用パッド31Pを有している。この外部接続用パッド31Pは、図示は省略するが、例えば平面視でマトリクス状に配置されている。また、各外部接続用パッド31Pの平面形状は、例えば円形状に形成されている。

40

**【0014】**

ソルダレジスト層51は、配線パターン31の一部を覆うように絶縁層24の下面に設けられている。ソルダレジスト層51の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。このソルダレジスト層51には、配線パターン31の一部を上記外部接続用パッド31Pとして露出させるための複数の開口部51Xが形成されている。開口部51Xは、図1(a)において下側から上側(配線パターン31側)に向か

50

うに連れて径が小さくなるテーパ状に形成されている。具体的には、本例の開口部 51X は、上側の開口端の径が下側の開口端の径よりも小径となる円錐台形状に形成されている。なお、必要に応じて、上記開口部 51X から露出する配線パターン 31 上に OSP (Organic Solderability Preservative) 処理を施して OSP 膜を形成し、その OSP 膜に外部接続端子を接続するようにしてもよい。また、開口部 51X から露出する配線パターン 31 上に金属層を形成し、その金属層に上記外部接続端子を接続するようにしてもよい。金属層の例としては、金 (Au) 層、ニッケル (Ni) / Au 層 (配線パターン 31 の下面に Ni 層と Au 層をこの順番で積層した金属層) や、Ni / パラジウム (Pd) / Au 層 (配線パターン 31 上に Ni 層と Pd 層と Au 層をこの順番で積層した金属層) などを挙げることができる。また、上記開口部 51X から露出する配線パターン 31 (あるいは、配線パターン 31 上に OSP 膜や金属層が形成されている場合には、それら OSP 膜又は金属層) 自体を、外部接続端子としてもよい。なお、上記ソルダレジスト層 51 の厚さは、例えば 15 ~ 30 μm 程度とすることができます。

#### 【0015】

一方、配線パターン 30 は、基板本体 20 のチップ実装面側 (図 1 では、上面側) に設けられている。この配線パターン 30 は、当該配線基板 10 に実装される半導体チップ 60 (図 2 参照) のバンプ 61 が接続される接続パッド 30P を有する。接続パッド 30P は、図示は省略するが、半導体チップ 60 のバンプ 61 の配設形態に応じて、半導体チップ 60 が実装される実装領域に例えば平面視でマトリクス状に配列されている。各接続パッド 30P の平面形状は、例えば円形状に形成されている。接続パッド 30P の直径は、例えば 30 ~ 40 μm 程度とすることができます。

#### 【0016】

ソルダレジスト層 50 は、配線パターン 30 を覆うように基板本体 20 のチップ実装面側に設けられている。ソルダレジスト層 50 の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。このソルダレジスト層 50 には、配線パターン 30 の一部を上記接続パッド 30P として露出させるための複数の開口部 50X が形成されている。開口部 50X は、図 1 (a) において上側から下側 (配線パターン 30 側) に向かうに連れて径が小さくなるテーパ状に形成されている。具体的には、本例の開口部 50X は、下側の開口端の径が上側の開口端の径よりも小径となる円錐台形状に形成されている。これら開口部 50X から露出する配線パターン 30 上、つまり接続パッド 30P 上には、はんだバンプ 40 が形成されている。具体的には、接続パッド 30P 上には金属膜 45 が形成され、その金属膜 45 上にははんだバンプ 40 が形成されている。金属膜 45 は、開口部 50X から露出する配線パターン 30 の上面、開口部 50X の内側面、及び開口部 50X 周辺に位置するソルダレジスト層 50 の上面を被覆するように形成されている。すなわち、金属膜 45 は中空ハット状に形成されている。金属膜 45 の材料としては、例えば銅や銅合金を用いることができる。金属膜 45 の厚さは、例えば 0.5 ~ 1 μm 程度とすることができる。また、ソルダレジスト層 50 の厚さは、例えば 15 ~ 30 μm 程度とすることができる。

#### 【0017】

次に、はんだバンプ 40 の構造について説明する。

図 1 (b) に示すように、はんだバンプ 40 は、はんだ層 41 と、金属層 42 と、金属ポスト 43 とを有している。

#### 【0018】

はんだ層 41 は、金属層 42 及び金属ポスト 43 全体を被覆するように形成されている。はんだ層 41 は、金属ポスト 43 に引き寄せられるように形成され、厚さ方向に延びるように形成されている。具体的には、はんだ層 41 は、厚さ方向と断面視で直交する平面方向よりも厚さ方向に広がるように形成されている。すなわち、はんだ層 41 の断面形状は略楕円状、具体的には長軸が厚さ方向に延びる略楕円状に形成されている。例えば、はんだ層 41 の厚さ方向の長さ L1 は例えば 65 ~ 75 μm 程度とすることができます、はんだ層 41 の平面方向の長さ L2 は例えば 50 ~ 60 μm 程度とすることができます。はんだ層

10

20

30

40

50

41の材料としては、例えば錫(Sn)とCuの合金やSnと銀(Ag)とCuの合金を用いることができる。

【0019】

金属層42は、はんだ層41中に浮いた状態で保持されている。金属層42は、その側面全面及び下面全面がはんだ層41によって被覆されている。金属層42は、上記金属膜45との間にははんだ層41が介在された状態で、金属膜45の形状に沿って形成されている。すなわち、金属層42は中空ハット状に形成されている。具体的には、金属層42は、本体部42Aと、その本体部42Aの端部から外側に突出する鍔部42Bとを有する形状に形成され、その本体部42Aには凹部42Xが形成されている。凹部42Xは、鍔部42Bから接続パッド30Pに向かって下方に延びるように形成されている。具体的には、凹部42Xは、図1(b)において上側から下側(配線パターン30側)に向かうに連れて径が小さくなるテーパ状に形成されている。例えば、本例の凹部42Xは、下側の開口端の径が上側の開口端の径よりも小径となる円錐台形状に形成されている。金属層42の材料としては、はんだ層41と同様に、例えばSnとCuの合金やSnとAgとCuの合金を用いることができる。但し、金属層42は、上記はんだ層41よりもCuリッチな金属層である。すなわち、金属層42は、はんだ層41に比べてCuの濃度が濃い金属層である。例えば、Cuリッチな金属層42におけるCu濃度は80~95wt%程度とすることができる。なお、金属層42の厚さは、例えば1~3μm程度とすることができる。

【0020】

金属ポスト43は、金属層42上に形成されている。金属ポスト43は、はんだ層41中に浮いた状態で保持されている。金属ポスト43は、その側面全面及び上面全面がはんだ層41によって被覆されている。この金属ポスト43は、厚さ方向に柱状に延びるように形成されている。具体的には、金属ポスト43は、断面視略T字状に形成されている。詳述すると、金属ポスト43は、上記凹部42Xを充填するように形成されたポスト部43Aと、ポスト部43Aの上面及び鍔部42Bの上面を被覆するように形成され、ポスト部43Aよりも大径に形成された大径部43Bとを有している。

【0021】

ポスト部43Aは、大径部43Bの下面から下方に延びるように形成され、その一部が開口部50X内に入り込むように形成されている。すなわち、ポスト部43Aの一部は開口部50X内に配置されている。このポスト部43Aは、図1(b)において上側から下側に向かうに連れて径が小さくなるテーパ状に形成されている。具体的には、本例のポスト部43Aは、上面が下面よりも小径となる円錐台形状に形成されている。このようなポスト部43Aの高さは、例えば15~18μm程度とすることができる。ポスト部43Aの上面の直径は、例えば40~50μm程度とすることができる。

【0022】

大径部43Bは、ポスト部43Aの上面及び鍔部42Bの上面から上方に延びるように形成されている。本例の大径部43Bは、円柱状に形成されている。この大径部43Bの直径は、ポスト部43Aの上面の直径よりも大径に形成されている。例えば、大径部43Bの直径は45~55μm程度とすることができる。大径部43Bの厚さは、例えば3~5μm程度とすることができる。

【0023】

これらポスト部43A及び大径部43B(つまり、金属ポスト43)の材料としては、例えば銅、ニッケルや金などの金属又はこれらの金属を少なくとも一種以上含む合金を用いることができ、本実施形態では銅を用いている。

【0024】

このような構造を有するはんだバンプ40のピッチは、例えば90~105μm程度とすることができる。また、隣り合うはんだバンプ40の間隔は、例えば20~45μm程度とすることができる。

【0025】

10

20

30

40

50

次に、半導体装置 11 の構造について説明する。

図 2 に示すように、半導体装置 11 は、上記配線基板 10 と、その配線基板 10 に実装された半導体チップ 60 と、アンダーフィル樹脂 65 を有している。

【0026】

半導体チップ 60 は、その回路形成面（図 2 では、下面）に、複数のバンプ 61 が形成されている。半導体チップ 60 は、バンプ 61 及び上記はんだバンプ 40 を介して、配線基板 10 の接続パッド 30P と電気的に接続されている。すなわち、半導体チップ 60 は、配線基板 10 にフリップチップ接合されている。

【0027】

半導体チップ 60 としては、例えば C P U (Central Processing Unit) チップや G P U (Graphics Processing Unit) チップなどのロジックチップを用いることができる。この半導体チップ 60 の大きさは、例えば平面視で  $3\text{ mm} \times 3\text{ mm} \sim 12\text{ mm} \times 12\text{ mm}$  程度とすることができます。半導体チップ 60 の厚さは、例えば  $50 \sim 100\text{ }\mu\text{m}$  程度とすることができます。

10

【0028】

また、上記バンプ 61 としては、例えば金バンプやはんだバンプを用いることができる。はんだバンプの材料としては、例えば鉛 (Pb) を含む合金、Sn と Au の合金、Sn と Cu の合金、Sn と Ag の合金、Sn と Ag と Cu の合金等を用いることができる。

【0029】

アンダーフィル樹脂 65 は、配線基板 10 の上面と半導体チップ 60 の下面との隙間を充填するように形成されている。このアンダーフィル樹脂 65 は、バンプ 61 とはんだバンプ 40 (接続パッド 30P) との接続部分の接続強度を向上させると共に、配線パターン 30 の腐食やエレクトロマイグレーションの発生を抑制し、配線パターン 30 の信頼性の低下を防ぐための樹脂である。アンダーフィル樹脂 65 の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。

20

【0030】

次に、配線基板 10 及び半導体装置 11 の作用について説明する。

接続パッド 30P 上に、はんだ層 41 と、そのはんだ層 41 によって全体が被覆され、厚さ方向に延びるように柱状に形成された金属ポスト 43 を含むはんだバンプ 40 を形成するようにした。すなわち、はんだバンプ 40 では、金属ポスト 43 をはんだ層 41 中に浮いた状態で保持するようにした。これにより、はんだ層 41 が、そのはんだ層 41 の内部に形成された金属ポスト 43 に引き寄せられるように形成される。このため、はんだ層 41 が平面方向に広がることが抑制され、はんだ層 41 が平面方向よりも厚さ方向に延びるよう形成される。このように、はんだバンプ 40 では、はんだ層 41 よりも剛性の高い金属ポスト 43 が芯となり、その金属ポスト 43 によってはんだ層 41 (はんだバンプ 40) が高く形成されるようにその形状が保持される。

30

【0031】

次に、配線基板 10 の製造方法について説明する。

図 3 (a) に示すように、まず、はんだバンプ 40 が形成される前段階の配線基板 10 を準備する。この配線基板 10 は、公知の製造方法により製造することができるため、その概略について図 3 (a) を参照しながら簡単に説明する。

40

【0032】

まず、コア基板 21 の所要箇所に貫通孔 21X を形成し、その貫通孔 21X の内側面にめっきを施して貫通電極 22 を形成することで両面を導通させた後、例えばサブトラクティブ法により配線 25, 26 を形成する。次に、コア基板 21 の上面及び下面にそれぞれ絶縁層 23, 24 を樹脂フィルムの真空ラミネートにより形成し、加熱して硬化させる。なお、ペースト状又は液状の樹脂の塗布と加熱により絶縁層 23, 24 を形成してもよい。続いて、絶縁層 23, 24 にそれぞれ開口部を形成し、必要であればデスマニア処理した後、例えばセミアディティブ法によりビア 27, 28 及び配線パターン 30, 31 を形成する。次いで、配線パターン 30 の一部を接続パッド 30P として露出させるための開口

50

部 50X を有するソルダレジスト層 50 を形成するとともに、配線パターン 31 の一部を外部接続用パッド 31P として露出させるための開口部 51X を有するソルダレジスト層 51 を形成する。

【0033】

続いて、図 3 (b) に示す工程では、開口部 50X の内側面を含むソルダレジスト層 50 の表面 (上面) 全面及び開口部 50X から露出する配線パターン 30 の上面を被覆するようにシード層 46 を形成する。シード層 46 の材料としては、例えば銅や銅合金を用いることができる。このシード層 46 は、例えば無電解 Cu めっき法やスパッタリング法によって形成することができる。

【0034】

以下の工程では、図 3 (b) の配線基板 10 の A 部 (破線枠参照) を拡大した拡大断面図を参照しながら説明する。

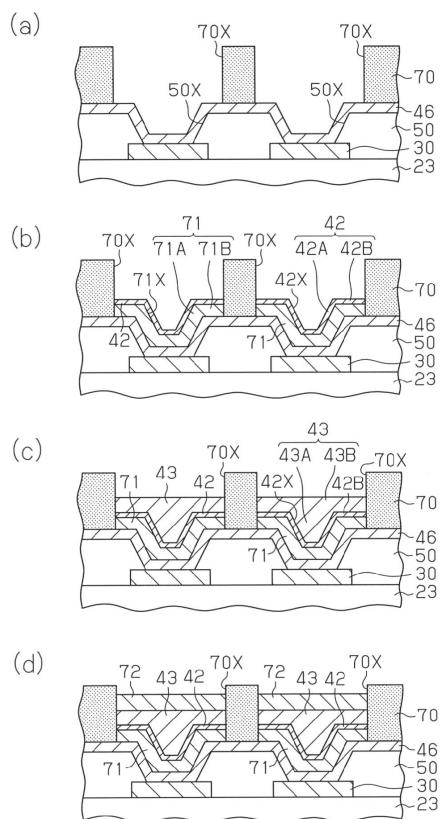

図 4 (a) に示す工程では、シード層 46 上に、所要の箇所に開口パターン 70X を有するレジスト層 70 を形成する。この開口パターン 70X は、はんだバンプ 40 (図 1 参照) の形成領域に対応する部分のシード層 46 を露出するように形成される。また、開口パターン 70X は、ソルダレジスト層 50 の開口部 50X よりも大径に形成されている。このため、ソルダレジスト層 50 の上面に形成されたシード層 46 の一部がレジスト層 70 の開口パターン 70X から露出される。レジスト層 70 の材料としては、耐めっき性がある材料を用いることができる。具体的には、レジスト層 70 の材料としては、感光性のドライフィルムレジスト又は液状のフォトレジスト (例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト) 等を用いることができる。例えば感光性のドライフィルムレジストを用いる場合には、シード層 46 の上面にドライフィルムを熱圧着によりラミネートし、そのドライフィルムをフォトリソグラフィ法によりパターンングして上記開口パターン 70X を有するレジスト層 70 を形成する。また、液状のフォトレジストを用いる場合にも、同様の工程を経て、レジスト層 70 を形成することができる。なお、上記開口パターン 70X の平面形状は円形状に形成されており、開口パターン 70X の直径は例えば 60 ~ 70 μm 程度とすることができます。

【0035】

次いで、図 4 (b) に示す工程では、上記レジスト層 70 をめっきマスクとして、シード層 46 の上面に、そのシード層 46 をめっき給電層に利用する電解めっき法を施す。具体的には、レジスト層 70 の開口パターン 70X から露出されたシード層 46 の上面に電解めっき法 (例えば、電解 Sn - Cu めっき法) を施すことにより、そのシード層 46 上にはんだめっき層 71 と Cu リッチな金属層 42 とを順に積層する。例えば、まず、電解 Sn - Cu めっき用のめっき液に図 4 (a) に示した構造体を浸漬し、電解の初期に電流密度を高く (例えば、1.5 A / dm<sup>2</sup> 程度) した状態で電解めっき法を施し、シード層 46 上に Sn を多く含んだはんだめっき層 71 を形成する。その後、はんだめっき層 71 が形成された構造体を上記めっき液に浸漬したまま電流密度を低く (例えば、0.5 A / dm<sup>2</sup> 程度) して電解めっき法を施し、上記はんだめっき層 71 上に Sn をほとんど含まない Cu リッチな金属層 42 を形成する。これにより、開口パターン 70X から露出されたシード層 46 の上面全面を被覆するように、シード層 46 の形状に沿ってはんだめっき層 71 が形成される。また、はんだめっき層 71 の上面全面を被覆するように、シード層 46 及びはんだめっき層 71 の形状に沿って金属層 42 が形成される。このため、はんだめっき層 71 及び金属層 42 は中空ハット状に形成される。すなわち、はんだめっき層 71 は、凹部 71X を有する本体部 71A と、本体部 71A の端部から外側に突出した鰐部 71B とを有する形状に形成されている。また、金属層 42 は、凹部 42X を有する本体部 42A と、本体部 42A の端部から外側に突出した鰐部 42B とを有する形状に形成されている。このように、本例の電解 Sn - Cu めっき法では、はんだめっき層 71 の本体部 71A に凹部 71X が形成され、金属層 42 の本体部 42A に凹部 42X が形成されるように、めっき時間等のめっき条件が設定されている。はんだめっき層 71 の厚さは例えば 10 ~ 15 μm 程度とす

10

20

30

40

50

ることができる。

【0036】

次に、図4(c)に示す工程では、上記レジスト層70をめっきマスクとして、金属層42の上面に、シード層46をめっき給電層に利用する電解めっき法を施す。具体的には、金属層42の上面に電解めっき法(例えば、電解Cuめっき法)を施すことにより、その金属層42上に金属ポスト43を形成する。これにより、金属層42の凹部42Xを充填する柱状のポスト部43Aと、そのポスト部43Aの上面及び金属層42の鍔部42Bの上面を被覆する柱状の大径部43Bとを有する金属ポスト43が形成される。このとき、Snを多く含んだSn-Cu合金からなる金属層ではなく、Snをほとんど含まないCuリッチな金属層42上に電解Cuめっき法が施されるため、金属層42上に金属ポスト43(Cuめっき層)を好適に形成することができる。

【0037】

続いて、図4(d)に示す工程では、上記レジスト層70をめっきマスクとして、金属ポスト43の上面に、シード層46をめっき給電層に利用する電解めっき法を施す。具体的には、金属ポスト43の上面に電解めっき法(例えば、電解Sn-Cuめっき法)を施すことにより、その金属ポスト43上にはんだめっき層72を形成する。これにより、金属ポスト43の上面全面を被覆するように、Sn-Cu合金からなるはんだめっき層72が形成される。このはんだめっき層72の厚さは、例えば3~5μm程度とすることができます。なお、はんだめっき層72の材料としては、Sn-Cu合金に限らず、Snやその他のはんだ材料であってもよい。

【0038】

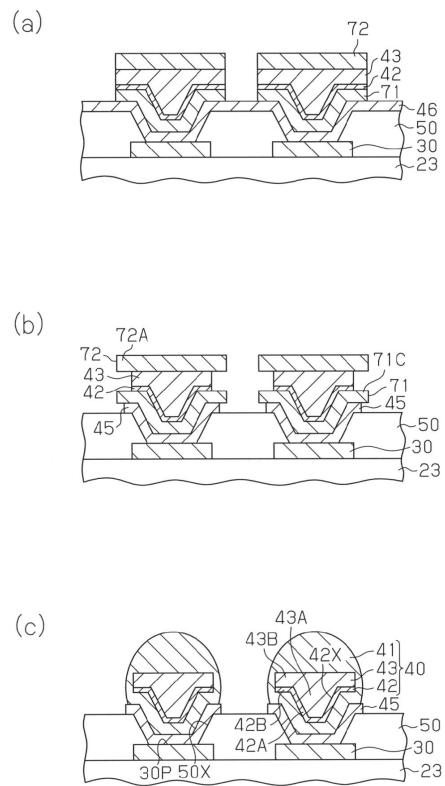

次いで、図5(a)に示す工程では、図4(d)に示したレジスト層70を例えばアルカリ性の剥離液により除去する。

次に、はんだめっき層71, 72をエッティングマスクとして、シード層46をエッティングし、不要なシード層46を除去する。これにより、図5(b)に示すように、シード層46が中空ハット状の複数の金属膜45にパターニングされる。本工程のエッティング処理は、例えばウェットエッティングにより行うことができる。このようなウェットエッティングにより金属膜45を形成すると、はんだめっき層71のマスク効果によるサイドエッティング及びアンダーカットにより、金属膜45の周縁部が内側に後退するように形成される。これにより、はんだめっき層71の周縁部が金属膜45の周縁部から外側に突出する突出部71Cとなる。さらに、本工程では、シード層46(金属膜45)と同様の材料からなる金属層42及び金属ポスト43の側面を露出した状態で、上記エッティング処理(ウェットエッティング)を行うようにした。このため、はんだめっき層72のマスク効果によるサイドエッティング及びアンダーカットにより、金属層42及び金属ポスト43の周縁部が内側に後退するように一部溶解除去される。これにより、はんだめっき層72の周縁部が金属層42及び金属ポスト43の周縁部から外側に突出する突出部72Aとなる。換言すると、本工程では、不要なシード層46を除去するとともに、金属層42及び金属ポスト43の周縁部の一部が溶解除去されるようにエッティング処理が行われる。

【0039】

そして、図5(b)に示した構造体を例えば230~260程度の温度でリフロー加熱する。これにより、はんだめっき層71, 72が接合される。具体的には、はんだめっき層71, 72が溶融して合金となり、図5(c)に示すように、一つのはんだ層41が金属膜45上に形成される。上記リフロー時には、金属層42及び金属ポスト43(つまり、Cu層)にはんだが引き寄せられるようにしてはんだ層41が形成される。詳述すると、本例では、金属層42の凹部42Xを充填するように金属ポスト43が形成されることで該金属ポスト43が厚さ方向に延在して形成されているため、その高く形成された金属ポスト43に引き寄せられてはんだ層41が形成される。このため、はんだが平面方向に広がることを抑制することができ、はんだ層41を高く形成することができる。また、リフロー時に、2つのはんだめっき層71, 72によって挟まれた金属層42及び金属ポスト43の周縁部がはんだめっき層71, 72の周縁部よりも内側に後退するように形成

10

20

30

40

50

されている。このため、溶融したはんだめっき層71, 72内に金属層42及び金属ポスト43が取り込まれやすくなる。このように金属層42及び金属ポスト43をはんだめっき層71, 72に取り込ませると、上記リフロー時に、金属ポスト43及び金属層42の側面にはんだが引き寄せられるため、はんだ層41が平面方向に広がるのが好適に抑制され、厚さ方向に延びるように形成される。このため、はんだめっき層71, 72の析出高さを高くした場合であっても、それらははんだめっき層71, 72をリフローしたときに、隣り合うはんだ層41がショートすることが好適に抑制される。さらに、はんだ層41が平面方向よりも厚さ方向に延びるように形成されるため、はんだ層41の高さを高く保つことができる。このように、本工程によって、はんだ層41とそのはんだ層41中に浮いた状態で保持された金属層42及び金属ポスト43とを含むはんだバンプ40が形成される。

10

#### 【0040】

以上の製造工程により、図1に示した配線基板10が製造される。

以上説明した本実施形態によれば、以下の効果を奏することができる。

(1)はんだバンプ40では、厚さ方向に延びる柱状の金属ポスト43をはんだ層41中に浮いた状態で保持するようにした。これにより、はんだ層41が、そのはんだ層41の内部に形成された金属ポスト43に引き寄せられるように形成される。このため、はんだ層41が平面方向に広がることが抑制され、はんだ層41が平面方向よりも厚さ方向に延びるように形成される。したがって、隣り合うはんだ層41がショートすることを好適に抑制することができ、はんだ層41の高さを高く保つことができる。この結果、接続パッド30Pの狭ピッチ化が進んだ場合であっても、はんだ層41を高く形成することができ、半導体チップ60との接続の十分な信頼性を得ることができる。

20

#### 【0041】

(2)ところで、はんだバンプを高く形成する方法としては、シード層上にCu層を形成し、そのCu層上にはんだめっき層を形成した後に、リフロー加熱することによりCu層上にはんだ層を形成する方法も考えられる。このような比較例の場合には、Cu層を高く形成した分だけはんだバンプ全体を高く形成することができる。しかし、この場合には、Cu層上のみにはんだめっき層が形成されることになるため、はんだ層自体は平面方向に広がるように形成され、はんだ層自体を厚さ方向に延びるように形成することは困難である。すなわち、はんだ層によって被覆されるのがCu層の一部であり、そのCu層の一部のみにはんだ層が引き寄せられるだけであるため、はんだ層を高く保持することが困難である。

30

#### 【0042】

これに対し、本実施形態のはんだバンプ40では、金属ポスト43及び金属層42を全体的にはんだ層41で被覆するようにしたため、金属ポスト43及び金属層42の全体を芯として利用することができる。これにより、金属ポスト43及び金属層42全体に引き寄せられるようにはんだ層41が形成され、接続パッド30P(金属膜45)と金属ポスト43との間にもはんだ層41が形成される。このため、上記Cu層と金属ポスト43及び金属層42との厚さが同じである場合には、比較例のはんだバンプよりも本実施形態のはんだバンプ40を高く形成することができる。

40

#### 【0043】

(3)ところで、金属ポスト43がはんだバンプ40内において自由に回転してしまうと、はんだバンプ40の外形も金属ポスト43の回転に合わせて変化するため、はんだバンプ40の高さを保てなくなる虞がある。これに対し、本実施形態では、金属ポスト43の一部(ポスト部43Aの下端部)が開口部50X内に配置されるように金属ポスト43を形成するようにした。これにより、はんだリフロー時の金属ポスト43の回転を好適に抑制することができる。また、金属ポスト43の一部を開口部50X内に配置したことにより、半導体チップ60の実装時に金属ポスト43が半導体チップ60のバンプ61に押圧される場合であっても、上記開口部50Xがガイドとして機能して金属ポスト43の回転及び移動を好適に抑制することができる。

50

## 【0044】

(4) シード層46(金属膜45)と金属ポスト43と同じ材料とし、不要なシード層46を除去する際に、金属ポスト43の周縁部の一部を溶解除去するようにした。これにより、リフロー時に、溶融したはんだめっき層71, 72内に金属層42及び金属ポスト43が取り込まれやすくなり、金属ポスト43及び金属層42の側面にはんだが引き寄せられるため、はんだ層41が平面方向に広がるのを好適に抑制することができる。

## 【0045】

## (他の実施形態)

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

・上記実施形態では、金属層42を、凹部42Xが形成された本体部42Aと鰫部42Bとを有する中空ハット状に形成するようにした。これに限らず、例えば凹部42Xの形成を省略し、金属層42を断面視略T字状に形成するようにしてもよい。

10

## 【0046】

・上記実施形態では、はんだめっき層71を、凹部71Xを有する本体部71Aと鰫部71Bとを有する中空ハット状に形成するようにした。これに限らず、例えば凹部71Xの形成を省略し、はんだめっき層71を断面視略T字状に形成するようにしてもよい。この場合には、はんだめっき層71上に金属層42を形成し、その金属層42上に柱状(例えば、円柱状)の金属ポスト43を形成する。

## 【0047】

・上記実施形態における金属層42を省略してもよい。例えば、金属ポスト43の材料がニッケルの場合には、金属層42(Cuリッチ層)を設けなくとも、はんだめっき層71上に電解Niめっき法を施すことにより、はんだめっき層71上に金属ポスト43(Ni層)を好適に形成することができる。このため、このような場合には金属層42を省略してもよい。

20

## 【0048】

・上記実施形態では、電解めっき法によりはんだめっき層71, 72及び金属ポスト43を形成するようにした。これに限らず、例えば印刷法などにより接続パッド30P上にはんだペーストを転写して、Sn-Cu合金等からなる第1はんだ層を形成するようにしてもよい。また、印刷法などにより、上記第1導電層上に金属ポスト43を形成するようにしてもよい。また、印刷法などにより金属ポスト上にはんだペーストを転写して、Sn-Cu合金等からなる第2はんだ層を形成するようにしてもよい。なお、第1はんだ層及び第2はんだ層の材料としては、Sn-Cuに限らず、Snやその他のはんだ材料であってもよい。

30

## 【0049】

・上記各実施形態の配線基板10において、最外層の配線パターン30, 31よりも内層の構造については特に限定されない。すなわち、配線基板10は、少なくとも、最外層の配線パターン30, 31が基板内部を通じて相互に電気的に接続された構造を有していれば十分であるため、最外層の配線パターン30, 31よりも内層の構造については特に限定されない。例えばコア基板21の構造及び材質は特に限定されない。また、コア基板21上に形成される下層配線(例えば、配線25, 26)とその下層配線を覆う絶縁層(例えば、絶縁層23, 24)の層数についても特に限定されない。あるいは、基板本体20を、コア基板21を有するコア付きビルドアップ基板に代えて、コア基板21を含まないコアレス基板としてもよい。

40

## 【符号の説明】

## 【0050】

10 配線基板

11 半導体装置

30 配線パターン

30P 接続パッド

40 はんだバンプ

50

- 4 1 はんだ層 (第3はんだ層)

4 2 金属層

4 2 A 本体部

4 2 B 鎔部

4 2 X 凹部

4 3 金属ポスト

4 3 A ポスト部

4 3 B 大径部

4 5 金属膜

4 6 シード層

5 0 ソルダレジスト層

5 0 X 開口部

6 0 半導体チップ

7 0 レジスト層

7 0 X 開口パターン

7 1 はんだめっき層 (第1はんだ層)

7 2 はんだめっき層 (第2はんだ層)

10

【図1】

(b)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開平04-269834(JP,A)

特開2006-295109(JP,A)

特開2012-064911(JP,A)

特開2005-294482(JP,A)

特開2005-222966(JP,A)

特開2012-231130(JP,A)

特開平10-326965(JP,A)

特開平09-266230(JP,A)

特開2006-066865(JP,A)

特開2000-294586(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/447-21/449

21/60-21/607

23/12-23/15

H05K 1/18