(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7256675号**

**(P7256675)**

(45)発行日 令和5年4月12日(2023.4.12)

(24)登録日 令和5年4月4日(2023.4.4)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 21/318 (2006.01) | H 01 L | 21/318 | C       |

| H 01 L | 21/316 (2006.01) | H 01 L | 21/316 | X       |

| H 01 L | 21/31 (2006.01)  | H 01 L | 21/318 | B       |

| H 01 L | 21/336 (2006.01) | H 01 L | 21/31  | C       |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78  | 3 0 1 G |

請求項の数 19 (全17頁) 最終頁に続く

(21)出願番号

特願2019-78428(P2019-78428)

(22)出願日

平成31年4月17日(2019.4.17)

(65)公開番号

特開2019-192907(P2019-192907)

A)

(43)公開日

令和1年10月31日(2019.10.31)

審査請求日

令和4年4月13日(2022.4.13)

(31)優先権主張番号

10-2018-0048568

(32)優先日

平成30年4月26日(2018.4.26)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者

390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.大韓民国京畿道水原市靈通区三星路12

9129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人

100107766

弁理士 伊東 忠重

(74)代理人

100070150

弁理士 伊東 忠彦

(74)代理人

100091214

最終頁に続く

(54)【発明の名称】 低誘電膜の形成方法及び半導体素子の形成方法

**(57)【特許請求の範囲】****【請求項1】**

基板上にシリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給して低誘電膜を形成することを含み、

前記低誘電膜を形成することは、複数のメインサイクルを含み、該複数のメインサイクルの各々が、シリコンソース供給段階、炭素ソース供給段階、酸素ソース供給段階、及び窒素ソース供給段階の各々を少なくとも1回含み、

前記メインサイクルの各々は、前記炭素ソース供給段階及び前記酸素ソース供給段階が交互に遂行されるサブサイクルを含み、

前記サブサイクル中及び前記サブサイクル間に前記シリコンソース及び前記窒素ソースは供給されない、低誘電膜の形成方法。

**【請求項2】**

前記サブサイクルの各々で、前記酸素ソース供給段階は、前記炭素ソース供給段階の後に遂行される請求項1に記載の低誘電膜の形成方法。

**【請求項3】**

前記サブサイクルで、前記炭素ソース供給段階と前記酸素ソース供給段階との間には他のソースが供給されない請求項1に記載の低誘電膜の形成方法。

**【請求項4】**

前記サブサイクルの各々で、前記炭素ソース供給段階は、3秒乃至100秒間遂行される請求項1に記載の低誘電膜の形成方法。

10

20

**【請求項 5】**

前記サブサイクルの各々で、前記酸素ソース供給段階は、3秒乃至15秒間遂行される請求項1に記載の低誘電膜の形成方法。

**【請求項 6】**

前記サブサイクルの各々で、前記酸素ソース供給段階の遂行時間は、前記炭素ソース供給段階の遂行時間より短い請求項1に記載の低誘電膜の形成方法。

**【請求項 7】**

前記サブサイクルは、5回以上30回以下に遂行される請求項1に記載の低誘電膜の形成方法。

**【請求項 8】**

前記メインサイクルの各々で、前記シリコンソース供給段階は、前記サブサイクルの前に遂行される請求項1に記載の低誘電膜の形成方法。

10

**【請求項 9】**

前記シリコンソース供給段階は、3秒乃至50秒間遂行される請求項8に記載の低誘電膜の形成方法。

**【請求項 10】**

前記メインサイクルの各々で、前記窒素ソース供給段階は、前記サブサイクルの後に遂行される請求項1に記載の低誘電膜の形成方法。

**【請求項 11】**

前記窒素ソース供給段階は、3秒乃至50秒間遂行される請求項10に記載の低誘電膜の形成方法。

20

**【請求項 12】**

前記メインサイクルの各々は、前記窒素ソース供給段階の後に、第2の炭素ソース供給段階をさらに含む請求項10に記載の低誘電膜の形成方法。

**【請求項 13】**

前記低誘電膜は、SiOCN膜である請求項1に記載の低誘電膜の形成方法。

**【請求項 14】**

前記SiOCN膜の炭素組成と酸素組成とは、

$$\text{炭素組成 (at\%)} = 0.4 * \text{酸素組成 (at\%)} + 21.6$$

という関係を有する請求項13に記載の低誘電膜の形成方法。

30

**【請求項 15】**

前記SiOCN膜の炭素組成と酸素組成との合計は、35at%乃至50at%である請求項13に記載の低誘電膜の形成方法。

**【請求項 16】**

前記シリコンソース供給段階、前記炭素ソース供給段階、前記酸素ソース供給段階、及び前記窒素ソース供給段階の間にページ段階をさらに含む請求項1に記載の低誘電膜の形成方法。

**【請求項 17】**

基板上にシリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給して低誘電膜を形成することを含み、

40

前記低誘電膜を形成することは、複数のメインサイクルを含み、該複数のメインサイクルの各々が順に遂行されるシリコンソース供給段階、複数のサブサイクルの遂行段階、及び窒素ソース供給段階を含み、

前記サブサイクルの各々が、炭素ソース供給段階及び酸素ソース供給段階を含み、前記サブサイクル中及び前記サブサイクル間に前記シリコンソース及び前記窒素ソースは供給されない、低誘電膜の形成方法。

**【請求項 18】**

基板上にゲートパターンを形成することと、

前記ゲートパターンを覆うゲートスペーサー層を形成することと、

前記ゲートスペーサー層をエッチングしてゲートスペーサーを形成することと、を含み、

50

前記ゲートスペーサー層を形成することは、複数のメインサイクルを含み、該複数のメインサイクルの各々が、シリコンソース供給段階、炭素ソース供給段階、酸素ソース供給段階、及び窒素ソース供給段階の各々を少なくとも1回含み、

前記メインサイクルの各々は、前記炭素ソース供給段階及び前記酸素ソース供給段階が交互に遂行されるサブサイクルを含み、

前記サブサイクル中及び前記サブサイクル間にシリコンソース及び窒素ソースは供給されない、半導体素子の形成方法。

#### 【請求項19】

前記ゲートスペーサーを形成した後、前記ゲートパターンの間に前記基板を露出するリセス領域を形成することをさらに含む請求項18に記載の半導体素子の形成方法。 10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は膜形成方法に係り、低誘電膜の形成方法及び半導体素子の形成方法に係る。

##### 【背景技術】

##### 【0002】

半導体素子は小型化、多機能化、及び／又は低い製造単価等の特性によって多くの電子産業で使用されている。半導体素子はデータを格納する記憶素子、データを演算処理する論理素子、及び多様な機能を同時に遂行できるハイブリッド(hybrid)素子等を含むことができる。 20

##### 【0003】

電子産業が高度に発展することに応じて、半導体素子の高集積化に対する要求が段々高くなっている。したがって、微細なパターンを定義する露光工程の工程マージン減少等の様々な問題点が発生されて半導体素子の具現が段々難しくなる。また、電子産業の発展によって半導体素子の高速化に対する要求も段々高くなる。このような半導体素子の高集積化及び／又は高速化に対する要求を充足させるために多様な研究が遂行されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【文献】米国特許出願公開第2016/0322218号明細書

30

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

本発明が達成しようとする一技術的課題は炭素組成と酸素組成とを全て高めることができる低誘電膜の形成方法を提供することにある。

##### 【0006】

本発明が達成しようとする他の技術的課題は耐エッチング性を改善し、半導体素子の電気的特性を改善することができる半導体素子の形成方法を提供することにある。

##### 【課題を解決するための手段】

##### 【0007】

本発明に係る低誘電膜形成方法は、基板上にシリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給して低誘電膜を形成することを含み、前記低誘電膜を形成することはシリコンソース供給段階、炭素ソース供給段階、酸素ソース供給段階、及び窒素ソース供給段階の各々を少なくとも1回含む複数のメインサイクル(main cycles)を含み、前記メインサイクルの各々は前記炭素ソース供給段階及び前記酸素ソース供給段階が交互に遂行されるサブサイクル(sub cycles)を含むことができる。

##### 【0008】

本発明に係る低誘電膜形成方法は、基板上にシリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給して低誘電膜を形成することを含み、前記低誘電膜を形成することは順に遂行されるシリコンソース供給段階、サブサイクルの遂行段階、及び窒素ソース

50

供給段階を 1 つのサイクルとする複数のメインサイクルを含み、前記サブサイクルは炭素ソース供給段階及び酸素ソース供給段階を 1 つのサブサイクルとして複数回遂行することができる。

#### 【 0 0 0 9 】

本発明に係る半導体素子の形成方法は、基板上にゲートパターンを形成することと、前記ゲートパターンを覆うゲートスペーサー層を形成することと、前記ゲートスペーサー層をエッチングしてゲートスペーサーを形成することと、を含み、前記ゲートスペーサー層を形成することはシリコンソース供給段階、炭素ソース供給段階、酸素ソース供給段階、及び窒素ソース供給段階の各々を少なくとも 1 回含む複数のメインサイクル (main cycles) を含み、前記メインサイクルの各々は前記炭素ソース供給段階及び前記酸素ソース供給段階が交互に遂行されるサブサイクル (sub cycles) を含むことができる。10

#### 【発明の効果】

#### 【 0 0 1 0 】

本発明の概念によれば、炭素組成と酸素組成とを全て高めることができる低誘電膜の形成方法が提供されることができる。したがって、低誘電膜の耐エッチング性を改善し、半導体素子の電気的特性を改善することができる。

#### 【図面の簡単な説明】

#### 【 0 0 1 1 】

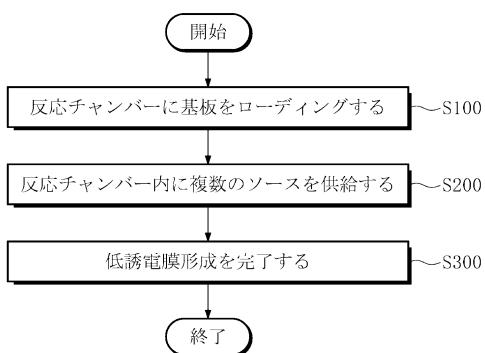

【図 1】本発明の実施形態に係る膜形成方法の工程フローチャートである。

20

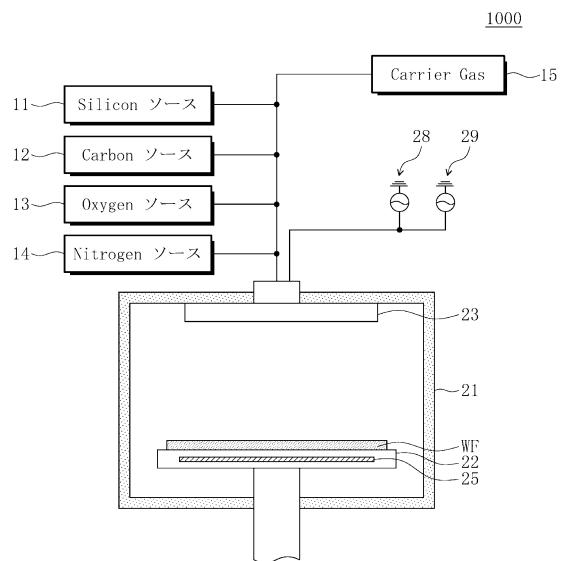

【図 2】本発明の実施形態に係る膜を形成するための蒸着装置の概念図である。

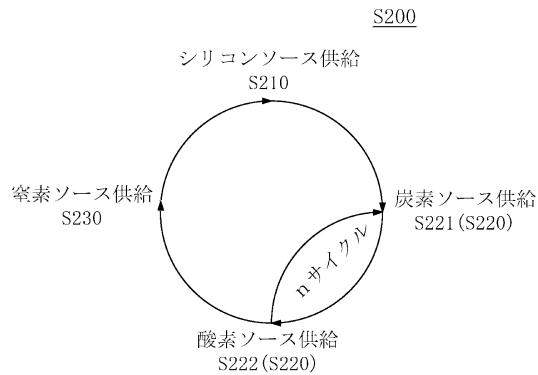

【図 3】本発明の実施形態に係るプロセスガスの供給シークエンスを示す概念図である。

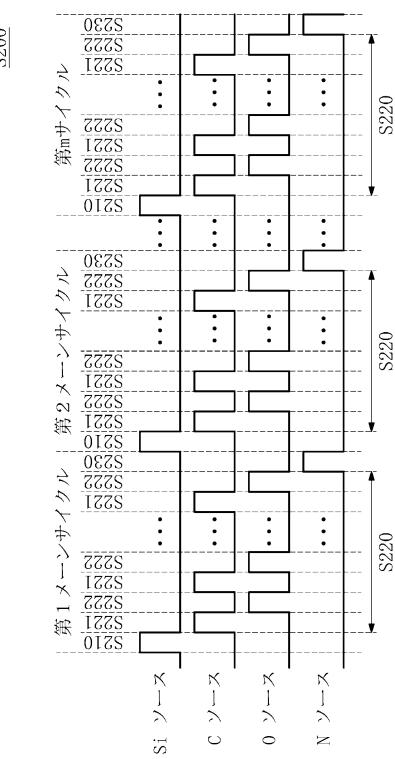

【図 4】本発明の実施形態に係るプロセスガスの供給サイクルを示すタイミングダイヤグラムである。

【図 5】図 4 のサイクルの中で 1 つのサイクルの遂行時間を示すタイミングダイヤグラムである。

【図 6】本発明の実施形態に係るプロセスガスの供給シークエンスを示す概念図である。

【図 7】本発明の実施形態に係るプロセスガスの供給サイクルを示すタイミングダイヤグラムである。

【図 8】図 6 のサイクルの中で 1 つのサイクルの遂行時間を示すタイミングダイヤグラムである。30

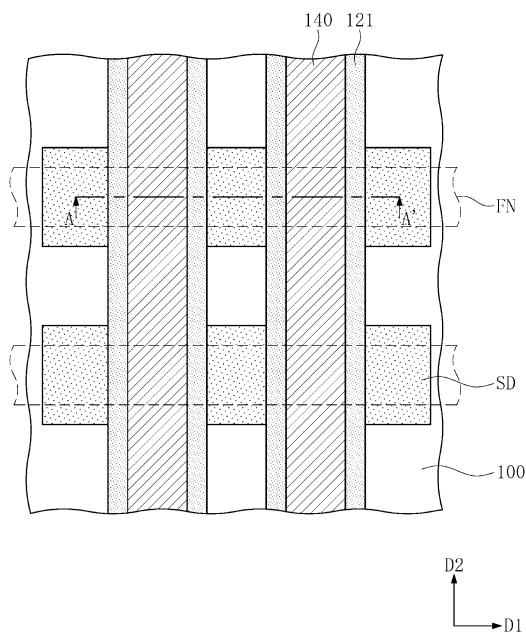

【図 9】本発明の実施形態に係る半導体素子の平面図である。

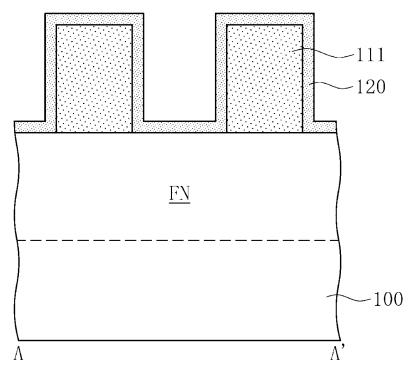

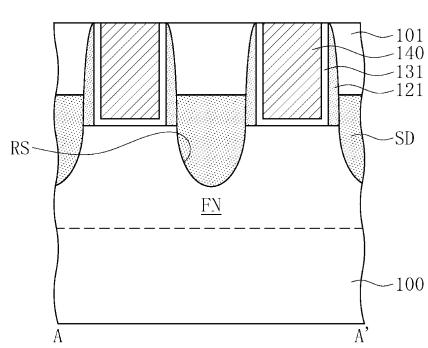

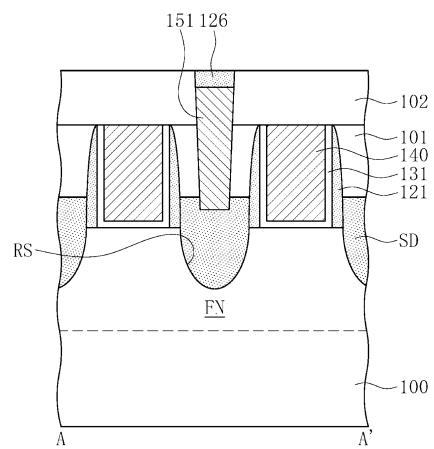

【図 10】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

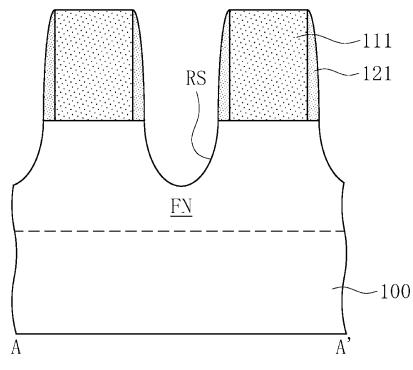

【図 11】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

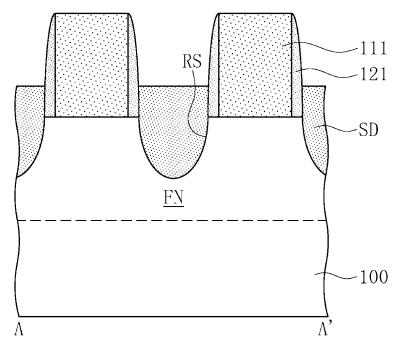

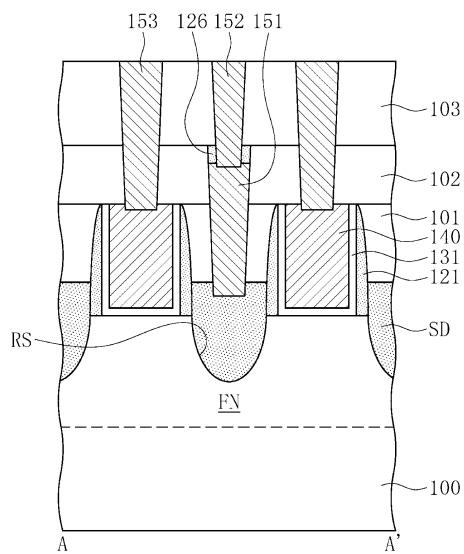

【図 12】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

【図 13】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

【図 14】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

【図 15】本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

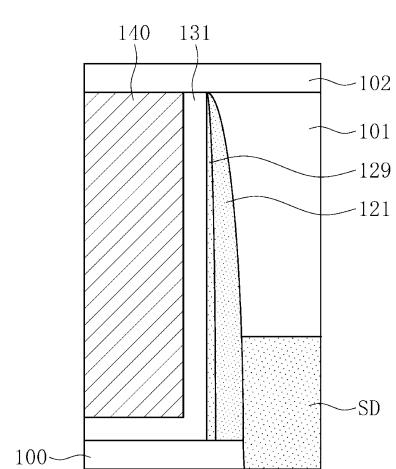

【図 16】本発明の実施形態に係るゲートスペーサーを説明するための図面であって、図 15 の一部領域の拡大図である。

#### 【発明を実施するための形態】

#### 【 0 0 1 2 】

以下、添付した図面を参照して本発明の実施形態を説明することによって本発明を詳細に説明する。

50

**【 0 0 1 3 】**

図 1 は本発明の実施形態に係る膜形成方法の工程フロー チャートである。図 2 は本発明の実施形態に係る膜を形成するための蒸着装置 1 0 0 0 の概念図である。

**【 0 0 1 4 】**

図 1 及び図 2 を参照すれば、蒸着装置 1 0 0 0 は反応チャンバー 2 1 を含む。一例として、蒸着装置 1 0 0 0 はプラズマ原子層成長 ( P l a s m a E n h a n c e d A L D 、 P E A L D ) 装置である。蒸着装置 1 0 0 0 は、反応チャンバー 2 1 の内部に提供され、基板 W F がローディングされるステージ 2 2 及び反応チャンバー 2 1 内に反応ガスを供給するシャワー ヘッド 2 3 を含む。ステージ 2 2 はその内部にヒーター 2 5 を含んで基板 W F を望む温度に維持する。シャワー ヘッド 2 3 又はシャワー ヘッド 2 3 に連結される上部電極には 1 3 . 5 6 M H z 又は 2 7 M H z の H R F パワー 2 8 ( 及び必要によって 5 M H z 以下 ( 4 0 0 k H z 乃至 5 0 0 k H z ) の L R F パワー 2 9 ) を印加し、ステージ 2 2 は接地することによって、シャワー ヘッド 2 3 とステージ 2 2 との間にプラズマが励起される。

10

**【 0 0 1 5 】**

シャワー ヘッド 2 3 を通じて反応チャンバー 2 1 内にプロセスガスが供給される。一例として、シャワー ヘッド 2 3 は複数の供給ラインを通じてシリコンソース 1 1 、炭素ソース 1 2 、酸素ソース 1 3 、及び窒素ソース 1 4 と連結される。シャワー ヘッド 2 3 にキャリヤーガス供給部 1 5 が連結される。シリコンソース 1 1 、炭素ソース 1 2 、酸素ソース 1 3 、及び窒素ソース 1 4 は互いに分離された個別供給ラインを通じてシャワー ヘッド 2 3 に供給され得る。これとは異なり、前記個別供給ラインの少なくとも一部は互いに重畠されてもよい。

20

**【 0 0 1 6 】**

キャリヤーガス供給部 1 5 から供給されるキャリヤーガスは他のソース及び / 又は前駆体を反応チャンバー 2 1 内に運搬する。前記キャリヤーガスは反応チャンバー 2 1 内部の未反応物質又は反応副産物をパージ ( p u r g e ) する役割を遂行する。前記キャリヤーガスはヘリウム ( H e ) 又はネオン ( N e ) のような不活性ガスであるか、或いは窒素 ( N 2 ) 又は二酸化炭素 ( C O 2 ) のように活性が極めて低い気体である。しかし、本発明がここに限定されることではない。キャリヤーガス供給部 1 5 の供給ラインはシリコンソース 1 1 、炭素ソース 1 2 、酸素ソース 1 3 、及び窒素ソース 1 4 の供給ラインと少なくとも一部が重畠される。これとは異なり、キャリヤーガス供給部 1 5 の供給ラインはシリコンソース 1 1 、炭素ソース 1 2 、酸素ソース 1 3 、及び窒素ソース 1 4 の供給ラインと分離されてもよい。

30

**【 0 0 1 7 】**

反応チャンバー 2 1 のステージ 2 2 上に基板がローディングされる ( S 1 0 0 ) 。基板 W F はウエハーである。反応チャンバー 2 1 内に複数のソースが供給されて前記基板上に低誘電膜が形成される ( S 2 0 0 ) 。前記低誘電膜が目的とする厚さに形成された後、前記低誘電膜の形成工程が完了され ( S 3 0 0 ) 、基板 W F を反応チャンバー 2 1 から搬出する。本明細書で、低誘電膜は誘電率が 8 より小さい膜を称することができる。低誘電膜は酸化シリコン、二酸化シリコンに比べて誘電率が小さい膜である。したがって、一部の実施形態において、低誘電膜は誘電率が約 7 より小さいか、約 6 より小さいか、約 5 . 0 より小さいか、約 4 . 5 より小さいか、約 4 . 2 より小さいか、約 4 . 0 より小さいか、約 3 . 9 ( 二酸化シリコンの誘電率 ) より小さいか、約 3 . 7 より小さいか、約 3 . 5 より小さいか、或いは約 2 . 0 より小さい。

40

**【 0 0 1 8 】**

## &lt;シリコンソース&gt;

シリコンソース 1 1 はモノフルオロシラン ( S i F H 3 ) 、ジフルオロシラン ( S i F 2 H 2 ) 、トリフルオロシラン ( S i F 3 H ) 、テトラフルオロシラン ( S i F 4 ) 、モノフルオロジシラン ( S i 2 F H 5 ) 、ジフルオロジシラン ( S i 2 F 2 H 4 ) 、トリフルオロジシラン ( S i 2 F 3 H 3 ) 、テトラフルオロジシラン ( S i 2 F 4 H 2 ) 、ペンタフルオ

50

ロジシラン ( $\text{Si}_2\text{F}_5\text{H}$ )、ヘキサフルオロジシラン ( $\text{Si}_2\text{F}_6$ )、モノクロロシラン ( $\text{SiClH}_3$ )、ジクロロシラン ( $\text{SiCl}_2\text{H}_2$ )、トリクロロシラン ( $\text{SiCl}_3\text{H}$ )、テトラクロロシラン ( $\text{SiCl}_4$ )、モノクロロジシラン ( $\text{Si}_2\text{ClH}_5$ )、ジクロロジシラン ( $\text{Si}_2\text{Cl}_2\text{H}_4$ )、トリクロロジシラン ( $\text{Si}_2\text{Cl}_3\text{H}_3$ )、テトラクロロジシラン ( $\text{Si}_2\text{Cl}_4\text{H}_2$ )、ペンタクロロジシラン ( $\text{Si}_2\text{Cl}_5\text{H}$ )、ヘキサクロロジシラン ( $\text{Si}_2\text{Cl}_6$ )、モノブロモシラン ( $\text{SiBrH}_3$ )、ジブロモシラン ( $\text{SiBr}_2\text{H}_2$ )、トリブロモシラン ( $\text{SiBr}_3\text{H}$ )、テトラブロモシラン ( $\text{SiBr}_4$ )、モノブロモジシラン ( $\text{Si}_2\text{BrH}_5$ )、ジブロモジシラン ( $\text{Si}_2\text{Br}_2\text{H}_4$ )、トリブロモジシラン ( $\text{Si}_2\text{Br}_3\text{H}_3$ )、テトラブロモジシラン ( $\text{Si}_2\text{Br}_4\text{H}_2$ )、ペンタブロモジシラン ( $\text{Si}_2\text{Br}_5\text{H}$ )、ヘキサブロモジシラン ( $\text{Si}_2\text{Br}_6$ )、モノヨードシラン ( $\text{SiIH}_3$ )、ジヨードシラン ( $\text{SiI}_2\text{H}_2$ )、トリヨードシラン ( $\text{SiI}_3\text{H}$ )、テトラヨードシラン ( $\text{SiI}_4$ )、モノヨードジシラン ( $\text{Si}_2\text{IH}_5$ )、ジヨードジシラン ( $\text{Si}_2\text{I}_2\text{H}_4$ )、トリヨードジシラン ( $\text{Si}_2\text{I}_3\text{H}_3$ )、テトラヨードジシラン ( $\text{Si}_2\text{I}_4\text{H}_2$ )、ペンタヨードジシラン ( $\text{Si}_2\text{I}_5\text{H}$ )、ヘキサヨードジシラン ( $\text{Si}_2\text{I}_6$ ) 等のようなハロゲンで置換されたシラン系シリコン前駆体である。

#### 【0019】

選択的に、前記シリコンソースはジエチルシラン ( $\text{Et}_2\text{SiH}_2$ )、テトラエチルオルトシリケート ( $\text{Si}(\text{OCH}_2\text{CH}_3)_4$ 、TEOS)、又はアルキルアミノシラン系化合物であるが、ここに限定されることではない。前記アルキルアミノシラン系化合物は、例えばジイソプロピルアミノシラン ( $\text{H}_3\text{Si}(\text{N}(i-\text{Pr})_2)$ )、ビス(ターシャリーブチルアミノ)シラン ( $(\text{C}_4\text{H}_9(\text{H})\text{N})_2\text{SiH}_2$ )、テトラキス(ジメチルアミノ)シラン ( $\text{Si}(\text{NMe}_2)_4$ )、テトラキス(エチルメチルアミノ)シラン ( $\text{Si}(\text{NEtMe})_4$ )、テトラキス(ジエチルアミノ)シラン ( $\text{Si}(\text{NEt}_2)_4$ )、トリス(ジメチルアミノ)シラン ( $\text{HSi}(\text{NMe}_2)_3$ )、トリス(エチルメチルアミノ)シラン ( $\text{HSi}(\text{NEtMe})_3$ )、トリス(ジエチルアミノ)シラン ( $\text{HSi}(\text{NEt}_2)_3$ )、トリス(ジメチルヒドラジノ)シラン ( $\text{HSi}(\text{NH})\text{NMe}_2)_3$ )、ビス(ジエチルアミノ)シラン ( $\text{H}_2\text{Si}(\text{NEt}_2)_2$ )、ビス(ジイソプロピルアミノ)シラン ( $\text{H}_2\text{Si}(\text{N}(i-\text{Pr})_2)_2$ )、トリス(イソプロピルアミノ)シラン ( $\text{HSi}(\text{N}(i-\text{Pr})_2)_3$ )、又は(ジイソプロピルアミノ)シラン ( $\text{H}_3\text{Si}(\text{N}(i-\text{Pr})_2)_2$ )を含むが、ここに限定されることではない。

#### 【0020】

ここで、Meはメチル基、Etはエチル基、i-Prはイソプロピル基を示す。

#### 【0021】

##### <炭素ソース>

炭素ソース12は炭素数1乃至10のアルカン(alkane)、炭素数2乃至10のアルケン(alkene)、炭素数1乃至15のアルキルアミン、炭素数4乃至15の含窒素(nitrogen-containing)ヘテロ環化合物、炭素数1乃至20のアルキルシラン、炭素数1乃至20のアルコキシシラン、及び炭素数1乃至20のアルキルシロキサンで構成される群から選択される1種以上である。

#### 【0022】

炭素数1乃至10のアルカンはメタン、エタン、プロパン、ブタン(すべての異性体)、ペンタン(すべての異性体)、ヘキサン(すべての異性体)、ヘプテン(すべての異性体)、オクタン(すべての異性体)、ノナン(すべての異性体)、デカン(すべての異性体)、又はこれらの混合物である。

#### 【0023】

炭素数2乃至10のアルケンはエチレン、プロピレン、ブテン(すべての異性体)、ペンテン(すべての異性体)、ヘキセン(すべての異性体)、ヘプテン(すべての異性体)、オクテン(すべての異性体)、ノネン(すべての異性体)、デカン(すべての異性体)、又はこれらの混合物である。炭素数1乃至15のアルキルアミンは、例えば $\text{NR}^1\text{R}^2\text{R}^3$ の化学式を有することができる。ここで、 $\text{R}^1$ 、 $\text{R}^2$ 、及び $\text{R}^3$ は各々独立的に水素、ハ

10

20

30

40

50

ロゲン元素、炭素数 1 乃至 10 のアルキル、炭素数 1 乃至 10 のアルケニル、炭素数 1 乃至 10 のアルキルアミノ、炭素数 6 乃至 12 のアリール、炭素数 7 乃至 12 のアリールアルキル、炭素数 7 乃至 12 のアルキルアリール、及び炭素数 3 ( 実施形態に応じては 5 乃至 12 ) のシクロアルキルで構成される群から選択することができる。この時、R<sup>1</sup>、R<sup>2</sup>、及び R<sup>3</sup> の中の少なくとも 1 つは炭素数 1 乃至 10 のアルキルである。一部の実施形態において、R<sup>1</sup>、R<sup>2</sup>、及び R<sup>3</sup> の中のいずれか 2 つは互いに連結されて環模様を形成することもできる。一部の実施形態において、2 つ以上のアルキルアミンが互いに連結されてアルキルジアミン、アルキルトリアミン等を形成することができ、これらもここに含まれることができる。

## 【0024】

10

## &lt; 酸素ソース、窒素ソース &gt;

酸素ソース 13 は、例えば O<sub>3</sub>、H<sub>2</sub>O、O<sub>2</sub>、NO<sub>2</sub>、NO、N<sub>2</sub>O、H<sub>2</sub>O、アルコール ( alcohol )、金属アルコキシド ( alkoxide )、プラズマ O<sub>2</sub>、リモートプラズマ O<sub>2</sub>、プラズマ N<sub>2</sub>O、プラズマ H<sub>2</sub>O、又はこれらの組み合わせである。窒素ソース 14 は、例えば N<sub>2</sub>、NH<sub>3</sub>、ヒドラジン N<sub>2</sub>H<sub>4</sub>、プラズマ N<sub>2</sub>、リモートプラズマ N<sub>2</sub>、又はこれらの組み合わせである。

## 【0025】

以下では上述したプロセスガスを反応チャンバー 21 内に供給して低誘電膜を形成するシーケンスが形成される。前記低誘電膜は SiOCN 膜である。

## 【0026】

20

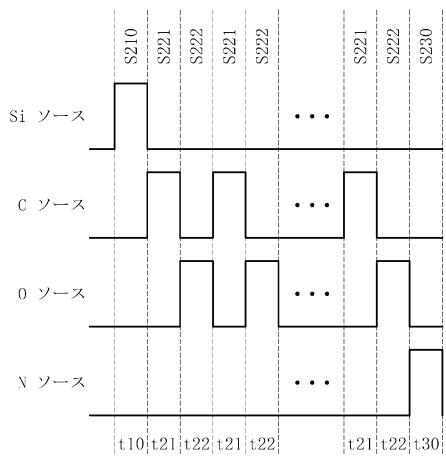

図 3 は本発明の実施形態に係るプロセスガスの供給シーケンスを示す概念図である。図 4 は本発明の実施形態に係るプロセスガスの供給サイクルを示すタイミングダイヤグラムである。図 5 は図 4 のサイクルの中で 1 つのサイクルの遂行時間を示すタイミングダイヤグラムである。

## 【0027】

図 3 乃至図 5 を参照すれば、図 2 の反応チャンバー内に複数のソースを供給して低誘電膜を形成する工程 ( S200 ) はシリコンソース供給段階 ( S210 )、炭素及び酸素ソースを供給するサブサイクル ( S220 )、及び窒素ソース供給段階 ( S230 ) を含む。一例として、低誘電膜を形成する工程 ( S200 ) はシリコンソース供給段階 ( S210 )、炭素ソース供給段階 ( S221 )、酸素ソース供給段階 ( S222 )、及び窒素ソース供給段階 ( S230 ) の各々を少なくとも 1 回以上含むメインサイクルを含む。前記メインサイクルは複数回遂行される。一例として、前記低誘電膜は図 4 に図示されたように m 回のメインサイクルによって形成されることができる。前記メインサイクルの回数は前記低誘電膜の目的とする厚さに応じて決定されることができる。一例として、前記メインサイクルの回数 m は約 5 乃至 20 である。

30

## 【0028】

各メインサイクルで、シリコンソース供給段階 ( S210 )、サブサイクル ( S220 )、及び窒素ソース供給段階 ( S230 ) が順に遂行される。以下、本明細書で各メインサイクルの開始地点はシリコンソース供給段階 ( S210 ) の開始始点として定義される。以下、1 つのメインサイクルを基準に説明される。

40

## 【0029】

先ず、シリコンソース供給段階 ( S210 ) が遂行される。シリコンソース供給段階 ( S210 ) は上述したシリコンソースの中で少なくとも 1 つを図 2 の反応チャンバー 21 内に供給することを含む。一例として、前記シリコンソースとしてヘキサクロロジシラン ( hexachlorodisilane、HCD ) が供給される場合、ヘキサクロロジシランの 2 つのシリコンを結合する化学結合が解離されて基板に結合されることができる。

## 【0030】

以後、炭素及び酸素ソースを供給するサブサイクル ( S220 ) が遂行される。サブサイクル ( S220 ) の各々は 1 回の炭素ソース供給段階 ( S221 ) と 1 回の酸素ソース供給段階 ( S222 ) とを含む。一例として、前記サブサイクルの回数 n は 5 乃至 30 で

50

ある。実施形態によれば、各メインサイクルを構成するサブサイクルの回数は互いに異なることができる。これとは異なり、各メインサイクルを構成するサブサイクルは同一な回数に遂行されてもよい。

#### 【0031】

炭素ソース供給段階（S221）が遂行される。炭素ソース供給段階（S221）は上述した炭素ソースの中で少なくとも1つを図2の反応チャンバー21内に供給することを含む。一例として、前記炭素ソースとしてC<sub>3</sub>H<sub>6</sub>のようにC<sub>x</sub>H<sub>y</sub>（x、yは常数）で表現されるソースが供給されることができる。前記炭素ソースはシリコンソース供給段階（S210）によって基板上に付着されたシリコンと化学結合される。その後、酸素ソース供給段階（S222）が遂行される。酸素ソース供給段階（S222）は上述した酸素ソースの中で少なくとも1つを図2の反応チャンバー21内に供給することを含む。一例として、前記酸素ソースとしてO<sub>2</sub>が供給される。

10

#### 【0032】

前記シリコンと結合した炭素ソースは相対的に長い炭素結合構造によって以後に供給される酸素が基板に吸着されることを妨害する立体障害（steric hindrance）をもたらすことができる。即ち、立体障害によって酸素が結合されることがあるサイトが減少され、これにしたがって酸素の供給時間を増やしても低誘電膜内の酸素濃度を増加させることには限界があり得る。また、立体障害の程度は炭素ソースの供給程度によって影響を受けるので、低誘電膜内の炭素濃度と酸素濃度とを同時に増加させることは容易でないことがある。低誘電膜内の炭素含量は湿式エッティング耐性に影響を及ぼし、湿式エッティング耐性が要求される水準より低い場合、ゲート電極のスペーサー等の目的として低誘電膜が使用されるのに制限があり得る。低誘電膜内の酸素含量は低誘電膜の誘電率に影響を及ぼし、誘電率が要求される水準より大きい場合、寄生キャパシタンスが増加して半導体素子の電気的特性が劣化されてしまい得る。

20

#### 【0033】

本発明の実施形態によれば、炭素及び酸素ソースの供給は複数のサブサイクル（S220）によって繰り返して遂行されることがある。サブサイクル（S220）によって低誘電膜内の炭素濃度と酸素濃度とが同時に増加されることがある。供給される酸素の一部は基板と既に結合された炭素と結合してCO又はCO<sub>2</sub>の形態に基板から脱離することができ、したがって立体障害が一時的に除去及び／又は緩和されることがある。したがって、酸素が基板とより容易に結合されることがある。また、シリコンと結合された長い炭素結合構造がさらに多い数の相対的に短い炭素結合構造に変更されることがある。したがって、低誘電膜内の炭素濃度と酸素濃度とが同時に増加されることがある。

30

#### 【0034】

1回のサブサイクルを構成する炭素ソース供給段階（S221）と酸素ソース供給段階（S222）との間にはシリコンソース及び窒素ソースのような他のソースが供給されないとし得る。また、複数のサブサイクルの間に他のソースが供給されないとし得る。一例として、酸素ソース供給段階（S222）の進行時間t<sub>22</sub>は約3秒乃至約15秒である。炭素ソース供給段階（S221）の進行時間t<sub>21</sub>は約3秒乃至約100秒である。シリコンソース供給段階（S210）の進行時間（t<sub>10</sub>）は約3秒乃至約50秒である。酸素ソース供給段階（S222）の進行時間t<sub>22</sub>は炭素ソース供給段階（S221）の各々の進行時間t<sub>21</sub>より短い。酸素ソース供給段階（S222）の進行時間t<sub>22</sub>はシリコンソース供給段階（S210）の進行時間（t<sub>10</sub>）より短い。

40

#### 【0035】

サブサイクル（S220）が完了された後、窒素ソース供給段階（S230）が遂行される。窒素ソース供給段階（S230）は上述した窒素ソースの中で少なくとも1つを図2の反応チャンバー21内に供給することを含む。一例として、前記窒素ソースとしてNH<sub>3</sub>が供給されることがある。窒素ソース供給段階（S230）の進行時間t<sub>30</sub>は約3秒乃至約50秒である。一例として、窒素ソース供給段階（S230）の進行時間t<sub>30</sub>は酸素ソース供給段階（S222）の進行時間t<sub>22</sub>より長い。窒素ソース供給段階（

50

S<sub>2</sub>C<sub>3</sub>O<sub>0</sub>)の進行時間t<sub>3</sub>は炭素ソース供給段階(S<sub>2</sub>C<sub>2</sub>1)の進行時間t<sub>2</sub>より短い。

#### 【0036】

図3乃至図5では図示しないが、各ソースの供給段階の間にページ(purge)過程が遂行される。ページガスは、例えばヘリウム(He)、ネオン(Ne)のような不活性ガス、窒素(N<sub>2</sub>)又は二酸化炭素(CO<sub>2</sub>)のように活性が極めて低い気体である。しかし、本発明がここに限定されることではない。

#### 【0037】

前記シリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給する段階は各々独立的にプラズマによって活性化される段階を含むことができる。即ち、反応チャンバー温度が比較的低い場合にはプラズマ形成のためのRFパワーを供給することによって低誘電膜の形成に必要であるエネルギーを供給することができる。一部の実施形態において、前記シリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給する段階の中でいずれか1つの段階又はいずれか2段階のみにプラズマ形成のためのRFパワーが供給されることができる。一部の実施形態において、前記シリコンソース、炭素ソース、酸素ソース、及び窒素ソースを供給する段階の全体に亘って各々プラズマ形成のためのRFパワーが供給されることができる。

10

#### 【0038】

上述した低誘電膜の形成工程は約400乃至約700の温度で、さらに比較的低温である約450乃至約630の温度でも遂行されることができる。実施形態によれば、低誘電膜の形成工程は使用される炭素ソースの種類に応じてはさらに低い温度である500以下の温度でも遂行されることができる。

20

#### 【0039】

前記低誘電膜はSiOCN膜である。前記SiOCN膜の炭素組成と酸素組成とは数学式(1)のような関係を有する。

#### 【0040】

$$\text{炭素組成 (at\%)} = 0.4 * (\text{酸素組成 at\%}) + 21.6 \quad (1)$$

前記SiOCN膜の炭素組成と酸素組成との合計は約35at%乃至約50at%である。一例として、前記SiOCN膜の組成はXPS(X-ray photoelectron spectroscopy)で分析することができる。本発明の実施形態に係って形成された低誘電膜は高い炭素組成によって高い湿式エッチング耐性を有しながらも、高い酸素組成によって低い誘電率を有することができる。一例として、本発明の実施形態に係って形成された低誘電膜は約5.0以下の低い誘電率を有することができる。

30

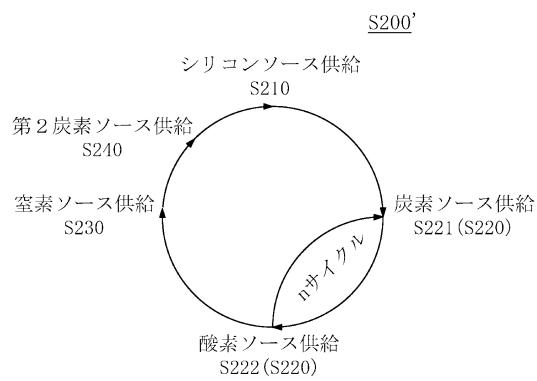

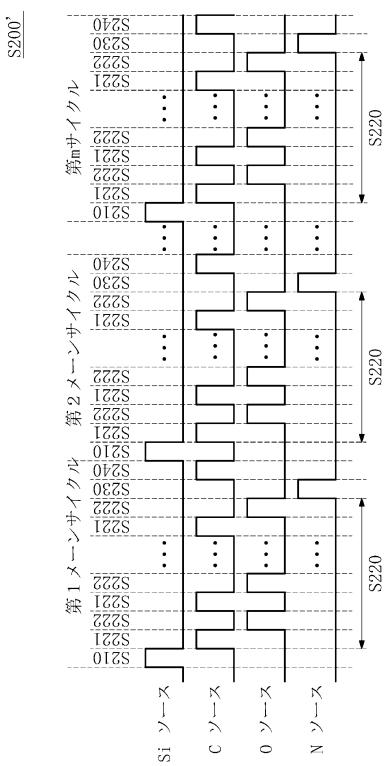

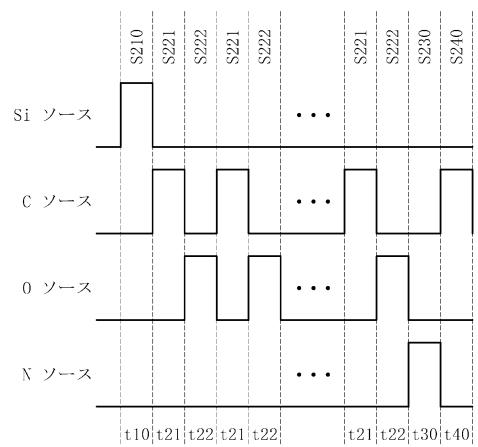

#### 【0041】

図6は本発明の実施形態に係るプロセスガスの供給シーケンスを示す概念図である。図7は本発明の実施形態に係るプロセスガスの供給サイクルを示すタイミングダイヤグラムである。図8は図7のサイクルの中で1つのサイクルの遂行時間を示すタイミングダイヤグラムである。説明を簡易化するために重複された構成に対する説明は省略される。

#### 【0042】

図6乃至図8を参照すれば、図2の反応チャンバー内に複数のソースを供給して低誘電膜を形成する工程(S<sub>2</sub>00')はシリコンソース供給段階(S<sub>2</sub>10)、炭素及び酸素ソースを供給するサブサイクル(S<sub>2</sub>20)、及び窒素ソース供給段階(S<sub>2</sub>30)を含む。一例として、低誘電膜を形成する工程(S<sub>2</sub>00)はシリコンソース供給段階(S<sub>2</sub>10)、炭素ソース供給段階(S<sub>2</sub>21)、酸素ソース供給段階(S<sub>2</sub>22)、及び窒素ソース供給段階(S<sub>2</sub>30)の各々を少なくとも1回以上含むメインサイクルを含む。前記メインサイクルは複数回遂行される。

40

#### 【0043】

本実施形態において、前記メインサイクルは窒素ソース供給段階(S<sub>2</sub>30)の後、第2炭素ソース供給段階(S<sub>2</sub>40)をさらに含む。第2炭素ソース供給段階(S<sub>2</sub>40)の進行時間t<sub>4</sub>はサブサイクル(S<sub>2</sub>20)内の炭素ソース供給段階(S<sub>2</sub>21)の進

50

行時間  $t_{21}$  と異なることができる。一例として、第 2 炭素ソース供給段階 (S 240) の進行時間  $t_{40}$  はサブサイクル (S 220) 内の炭素ソース供給段階 (S 221) の進行時間  $t_{21}$  より長い。一例として、第 2 炭素ソース供給段階 (S 240) の進行時間  $t_{40}$  は約 10 秒乃至約 15 秒である。

#### 【0044】

図 9 は本発明の実施形態に係る半導体素子の平面図である。図 10 乃至図 15 は本発明の実施形態に係る半導体素子の製造方法を説明するための図面であって、図 9 の A - A' 線に沿う断面図である。

#### 【0045】

図 9 及び図 10 を参照して、基板 100 の上部にピン構造体 FN が形成される。一例として、基板 100 はシリコン基板又はゲルマニウム基板であるか、或いは SOI (Silicon On Insulator) 基板である。ピン構造体 FN は第 1 方向 D1 に各々延長され、第 1 方向 D1 と交差する第 2 方向 D2 に互いに離隔される。ピン構造体 FN の形成は基板 100 の上部をパターニングしてトレンチを形成するエッチング工程を含む。その後、ピン構造体 FN の間のトレンチの下部に素子分離膜が形成される。一例として、前記素子分離膜はシリコン酸化膜を含む。

10

#### 【0046】

ピン構造体 FN 上に第 2 方向 D2 に延長されるゲートパターン 111 が形成される。ゲートパターン 111 はポリシリコンを含む。ゲートパターン 111 の形成はポリシリコン層上にマスクパターンを形成した後、これを利用するエッチング工程を遂行することを含む。前記マスクパターンはシリコン窒化膜又はシリコン酸窒化膜を含む。前記マスクパターンの一部はゲートパターン 111 上に残留する。

20

#### 【0047】

ゲートパターン 111 が形成された基板 100 上にゲートスペーサー層 120 が形成される。ゲートスペーサー層 120 は図 1 乃至図 8 を参照して説明された方法によって形成された低誘電膜に相応することができる。一例として、ゲートスペーサー層 120 は SiOCN 膜を含むことができる。ゲートスペーサー層 120 はゲートパターン 111 及びこれらの間に露出されたピン構造体 FN をコンフォーマルに覆う。

#### 【0048】

図 9 及び図 11 を参照して、ゲートパターン 111 の間にリセス領域 RS が形成される。ゲートスペーサー層 120 の一部は共にエッチングされて基板 100 を、より詳細にはリセス領域 RS を露出する。その結果、ゲートスペーサー 121 が形成される。リセス領域 RS の形成は湿式エッチング及び / 又は乾式エッチング工程を含む。一例として、リセス領域 RS の形成工程の間に、フッ酸 (HF) を含むエッチャントが使用されることができる。リセス領域 RS の形成の間にゲートパターン 111 (又は、これら上のマスクパターン) が露出される。

30

#### 【0049】

図 9 及び図 12 を参照して、リセス領域 RS の露出された表面に形成された自然酸化膜を除去する工程が遂行される。前記自然酸化膜の除去工程はクリーニング工程を含む。その後、リセス領域 RS 上にソース / ドレイン領域 SD が形成される。ソース / ドレイン領域 SD は露出されたリセス領域 RS の表面をシードとするエピタキシャル工程によって形成される。ソース / ドレイン領域 SD は基板 100 と同一な物質で形成される。これとは異なり、ソース / ドレイン領域 SD はピン構造体 FN に圧縮歪み又は引張歪みを提供する物質で形成されてもよい。一例として、基板 100 がシリコン基板である場合、ソース / ドレイン領域 SD は Si より格子定数が小さい SiC 層又は Si より格子定数が大きい SiGe 層を含むことができる。

40

#### 【0050】

図 9 及び図 13 を参照して、ゲートパターン 111 を除去した後、ゲート絶縁パターン 131 及びゲート電極 140 が形成される。ゲートパターン 111 を除去する前、ソース / ドレイン領域 SD を覆い、ゲートパターン 111 を露出する第 1 層間絶縁膜 101 が形

50

成される。一例として、第1層間絶縁膜101はシリコン酸化物を含むことができる。

**【0051】**

ゲートパターン111の除去工程、図11のリセス領域RSの形成工程、及び図12の自然酸化膜の除去工程の全てはエッチング工程を随伴する。本発明の実施形態に係るゲートスペーサー121は高い炭素濃度を有するので、これらのエッチング工程を遂行する時に高い耐エッチング性を有する。

**【0052】**

ゲート絶縁パターン131はシリコン酸化膜、シリコン酸窒化膜、及びシリコン酸化膜より誘電率が高い高誘電膜の中で少なくとも1つに形成されることがある。実施形態によれば、ゲート絶縁パターン131を形成する前に熱的酸化(Thermal Oxidation)及び/又は化学的酸化(Chemical Oxidation)による界面膜が形成されることがある。ゲート電極140はチタニウム、タンタル、タンクスティン、及びこれらの導電性窒化物のような金属物質で形成されることがある。

**【0053】**

図9及び図14を参照して、第1層間絶縁膜101を覆う第2層間絶縁膜102を形成することができる。第1及び第2層間絶縁膜101、102を貫通してソース/ドレイン領域SDに連結される下部コンタクト151が形成される。下部コンタクト151の形成は第1及び第2層間絶縁膜101、102を貫通するコンタクトホールを形成し、導電物質でコンタクトホールを満たすことを含む。コンタクトホールの上部に下部コンタクト151を覆うマスクパターン126を形成する。

**【0054】**

マスクパターン126は図1乃至図8を参照して説明された方法にて形成された低誘電膜である。一例として、マスクパターン126はSiOCN膜を含むことができる。

**【0055】**

図9及び図15を参照して、第2層間絶縁膜102を覆う第3層間絶縁膜103を形成することができる。第2及び第3層間絶縁膜102、103を貫通してゲート電極140の上部に連結されるゲートコンタクト153が形成される。また、第3層間絶縁膜103を貫通して下部コンタクト151に連結される上部コンタクト152が形成される。上部コンタクト152はゲートコンタクト153と共に形成される。上部コンタクト152のためのコンタクトホールとゲートコンタクト153のためのコンタクトホールとは同時に形成される。マスクパターン126は高いエッチング耐性を有するので、前記コンタクトホールの形成の間に下部コンタクト151を保護することができる。

**【0056】**

図16は本発明の実施形態に係るゲートスペーサーを説明するための図面であって、図15の一部領域の拡大図である。図16を参照して、本実施形態に係る半導体素子はゲート電極140とゲートスペーサー121との間にインナースペーサー129をさらに含むことができる。インナースペーサー129はゲートスペーサー121と異なる物質で形成されることがある。インナースペーサー129は実質的に炭素を含まない物質で形成されることがある。一例として、インナースペーサー129はSiN膜又はSiON膜を含むことができる。一例として、図10を参照して説明されたゲートスペーサー層120を形成する前にSiN膜又はSiON膜を形成する工程が遂行されることがある。

**【0057】**

本発明の実施形態に対する以上の説明は本発明の説明をための例示を提供する。したがって、本発明は以上の実施形態に限定されなく、本発明の技術的思想内で当該技術分野の通常の知識を有する者によって前記実施形態を組合して実施する等様々な修正及び変更が可能であることは明らかである。

**【符号の説明】**

**【0058】**

1000 蒸着装置

11 シリコンガス

10

20

30

40

50

1 2 炭素ソース

1 3 酸素ソース

1 4 窒素ソース

1 5 キャリヤーガス供給部

2 1 反応チャンバー

2 2 ステージ

2 3 シャワーヘッド

2 5 ヒーター

WF 基板

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図 3】

【図 4】

【図 5】

【図 6】

10

20

30

40

50

【 四 7 】

【図8】

【 9 】

【図10】

10

20

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図15】

【図16】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|         |                 |     |         |        |

|---------|-----------------|-----|---------|--------|

| C 2 3 C | 16/42 (2006.01) | F I | C 2 3 C | 16/42  |

| C 2 3 C | 16/455(2006.01) |     | C 2 3 C | 16/455 |

弁理士 大貴 進介

## (72)発明者 李 善英

大韓民国京畿道龍仁市器興区三星二路 95 女子寄宿舎ナルシス 415号

## (72)発明者 康 みん 材

大韓民国京畿道華城市東灘循環大路 20街 70

## (72)発明者 金 せ 娟

大韓民国京畿道華城市盤松洞 シボムデウンマウル ワールドメリダン バンド ウボラアパート 3

45棟 2301号

## (72)発明者 金 台原

大韓民国京畿道華城市ティーテクジョンゴル路 106棟 702号

## (72)発明者 卓 容 そく

大韓民国ソウル特別市恩平区津寛洞 ウンピョン ニュー - タウン サンリムマウル 828棟 604号

## (72)発明者 金 善政

大韓民国京畿道水原市靈通区二儀洞 光教イー - ピヨナンセサン 6115棟 1401号

## 審査官 長谷川 直也

(56)参考文献 特開2014-146670 (JP, A)

国際公開第2013/027549 (WO, A1)

特開2016-066688 (JP, A)

特開2014-183218 (JP, A)

特表2008-527723 (JP, A)

米国特許出願公開第2017/0186603 (US, A1)

米国特許出願公開第2017/0117140 (US, A1)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 21 / 318

H 01 L 21 / 316

H 01 L 21 / 31

H 01 L 21 / 336

C 2 3 C 16 / 42

C 2 3 C 16 / 455