**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.

*HO1L 27/115* (2006.01)

*HO1L 21/8247* (2006.01)

(45) 공고일자

2007년02월22일

(11) 등록번호

10-0685742

(24) 등록일자

2007년02월15일

(21) 출원번호

10-2005-0068303

(65) 공개번호

10-2007-0013733

(22) 출원일자

2005년07월27일

(43) 공개일자

2007년01월31일

심사청구일자

2005년07월27일

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

안재영

경기도 성남시 분당구 장안동 장안타운 건영아파트 104동401호

황기현

경기도 성남시 분당구 정자동 한솔마을 LG아파트 202동604호

노진태

경기 수원시 영통동 1051-4번지 102호

김홍석

경기 용인시 풍덕천동 1112 신정마을 806동 302호

이성해

경기 수원시 영통동 신나무실 신성아파트 521동 1706호

(74) 대리인

박영우

(56) 선행기술조사문헌

국내 공개특허공보 제2004-46340호

\* 심사관에 의하여 인용된 문헌

**심사관 : 박근오**

전체 청구항 수 : 총 9 항

(54) 불휘발성 메모리 장치 및 이의 제조 방법

**(57) 요약**

불휘발성 메모리 장치 및 이의 제조 방법에서, 기판 상에 실리콘 산화막을 형성한다. 실리콘 산화막의 상부에 라디칼 질화 공정을 수행하여 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하는 베리어막을 형성한다. 상기 베리어막 상에 실리콘 질화물을 포함하는 트랩핑막, 블로킹막 및 게이트 전극막을 형성한다. 게이트 전극막, 블록킹막, 트랩핑막 및 베리어막을 부분적으로 삭각한다. 본 발명에 따르면 베리어막의 상부와 하부 사이에 계면이 존재하지 않기 때문에 불휘발성 메모리 장치의 전기적 신뢰도가 증가한다.

**대표도**

도 1

**특허청구의 범위****청구항 1.**

채널 영역을 갖는 기판;

상기 기판의 상기 채널 영역 상에 형성되고, 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하고, 상기 기판 상에 형성되는 실리콘 산화막의 상부에 라디칼 질화 공정을 수행한 후 상기 실리콘 산화막을 부분적으로 식각하여 형성되는 베리어막 패턴;

상기 베리어막 패턴 상에 형성되고 실리콘 질화물을 포함하는 트랩핑막 패턴;

상기 트랩핑막 패턴 상에 형성되는 블록킹막 패턴; 및

상기 블록킹막 패턴 상에 형성되는 게이트 전극막 패턴을 포함하는 불휘발성 메모리 장치.

**청구항 2.**

삭제

**청구항 3.**

제 1 항에 있어서, 상기 라디칼 질화 공정은 암모니아 가스를 포함하는 반응 가스를 사용하는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 4.**

제 3 항에 있어서, 상기 반응 가스는 테트라클로로실란, 디클로로실란 또는 이들의 혼합물을 더 포함하는 것을 특징으로 하는 불휘발성 메모리 장치 형성 방법.

**청구항 5.**

기판 상에 실리콘 산화막을 형성하는 단계;

상기 실리콘 산화막의 상부에 라디칼 질화 공정을 수행하여 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하는 베리어막을 형성하는 단계;

상기 베리어막 상에 실리콘 질화물을 포함하는 트랩핑막을 형성하는 단계;

상기 트랩핑막 상에 블록킹막을 형성하는 단계;

상기 블록킹막 상에 게이트 전극막을 형성하는 단계; 및

상기 게이트 전극막, 상기 블록킹막, 상기 트랩핑막 및 상기 베리어막을 부분적으로 식각하는 단계를 포함하는 불휘발성 메모리 장치 형성 방법.

**청구항 6.**

삭제

**청구항 7.**

제 5 항에 있어서, 상기 산화막을 형성하는 단계는 라디칼 산화 공정을 수행하는 것을 특징으로 하는 불휘발성 메모리 장치 형성 방법.

**청구항 8.**

제 5 항에 있어서, 상기 라디칼 질화 공정은 암모니아를 포함하는 반응 가스를 사용하여 수행하는 것을 특징으로 하는 불휘발성 메모리 장치 형성 방법.

**청구항 9.**

제 8 항에 있어서, 상기 반응 가스는 테트라클로로실란, 디클로로실란 또는 이들의 혼합물을 더 포함하는 것을 특징으로 하는 불휘발성 메모리 장치 형성 방법.

**청구항 10.**

제 5 항에 있어서, 상기 트랩핑막을 형성하는 단계는 헥사클로로디실란, 트리실란 및 옥타클로트리실란으로 이루어진 그룹에서 선택된 적어도 하나의 물질을 포함하는 반응 가스를 사용하는 것을 특징으로 불휘발성 메모리 장치의 형성 방법.

**청구항 11.**

제 5 항에 있어서, 상기 트랩핑막을 형성하는 단계는 450°C 내지 650°C의 온도에서 수행하는 것을 특징으로 하는 불휘발성 메모리 장치 형성 방법.

명세서

**발명의 상세한 설명****발명의 목적****발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 불휘발성 메모리 장치 및 이의 제조 방법에 관한 것이다. 보다 상세하게는 전원이 제거되어도 데이터를 유지하는 불휘발성 메모리 장치 및 이의 제조 방법에 관한 것이다.

반도체 메모리 장치는 DRAM(dynamic random access memory) 및 SRAM(static random access memory)과 같이 데이터의 입·출력이 상대적으로 빠른 반면, 시간이 경과됨에 따라 데이터가 소실되는 휘발성(volatile) 메모리 장치와, ROM(read only memory)과 같이 데이터의 입·출력이 상대적으로 느리지만, 데이터를 영구 저장이 가능한 불휘발성(non-volatile) 메모리 장치로 구분될 수 있다. 상기 불휘발성 메모리 장치의 경우, 전기적으로 데이터의 입·출력이 가능한 EEPROM(electrically erasable programmable read only memory) 또는 플래시 EEPROM 메모리에 대한 수요가 늘고 있다. 상기 플래시 EEPROM 메모리 장치는 F-N 터널링(Fowler-Nordheim tunneling) 또는 채널 열전자 주입(channel

hot electron injection)을 이용하여 전기적으로 데이터의 프로그래밍(programming) 및 소거(erasing)를 수행한다. 상기 플래시 메모리 장치는 플로팅 게이트 타입의 불휘발성 메모리 장치와 SONOS(silicon-oxide-nitride-oxide-semiconductor) 타입의 불휘발성 메모리 장치로 크게 구분될 수 있다.

또한, SONOS 타입의 불휘발성 메모리 장치에서 리텐션(retention) 특성을 개선하기 위하여 터널 산화막 패턴 상에 순차적으로 형성된 제1 실리콘 질화막 패턴과 제2 실리콘 질화막 패턴을 포함하는 이중 막(bi-layer) 불휘발성 메모리 장치가 개발되었다.

그러나 이중 막 불휘발성 메모리 장치는 터널 산화막 패턴과 제1 실리콘 질화막 패턴 사이에 형성되는 계면에 의해서 전기적 신뢰도가 감소되는 문제점이 있었다. 또한, 제1 실리콘 질화막 패턴과 제2 실리콘 질화막 패턴의 두께 조절이 어렵다는 문제점이 있었다. 이와 더불어 제1 실리콘 질화막 패턴의 트랩 밀도를 상대적으로 감소시키고 제2 실리콘 질화막 패턴의 트랩 밀도를 상대적으로 증가시키는 것이 공정상 어렵다는 문제점이 있었다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 제1 목적은 전기적 신뢰도가 큰 불휘발성 메모리 장치를 제공하는 것이다.

본 발명의 제2 목적은 상기 불휘발성 메모리 장치의 제조 방법을 제공하는 것이다.

### 발명의 구성

상기 제1 목적을 달성하기 위한 본 발명의 일 실시예에 따르면 불휘발성 메모리 장치는 채널 영역을 갖는 기판, 상기 기판의 상기 채널 영역 상에 형성되는 베리어막 패턴, 상기 베리어막 패턴 상에 형성되고 실리콘 질화물을 포함하는 트랩핑막 패턴, 상기 트랩핑막 패턴 상에 형성되는 블록킹막 패턴 및 상기 블록킹막 패턴 상에 형성되는 게이트 전극막 패턴을 포함한다. 상기 베리어막 패턴은 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함한다. 또한 상기 베리어막 패턴은 상기 기판 상에 형성되는 실리콘 산화막의 상부에 라디칼 질화 공정을 수행한 후 상기 실리콘 산화막을 부분적으로 식각하여 형성된다.

상기 제2 목적을 달성하기 위한 본 발명의 일 실시예에 따르면, 기판 상에 실리콘 산화막을 형성한다. 상기 실리콘 산화막의 상부에 라디칼 질화 공정을 수행하여 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하는 베리어막을 형성한다. 상기 베리어막 상에 실리콘 질화물을 포함하는 트랩핑막을 형성한다. 상기 트랩핑막 상에 블록킹막을 형성한다. 상기 블록킹막 상에 게이트 전극막을 형성한다. 상기 게이트 전극막, 상기 블록킹막, 상기 트랩핑막 및 상기 베리어막을 부분적으로 식각한다.

본 발명에 따르면, 라디칼 질화 공정을 통해 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하는 베리어막 패턴이 형성된다. 따라서 상부와 하부 사이에는 계면이 존재하지 않을 수 있다는 장점이 있다. 또한, 상부의 두께를 효과적으로 조절할 수 있기 때문에 상부는 상대적으로 큰 두께 균일도를 가질 수 있다. 그리고 상부는 상대적으로 치밀한 구조를 갖는 동시에 상대적으로 작은 수의 실리콘-실리콘 결합을 갖기 때문에 상부는 상대적으로 낮은 트랩 밀도를 가질 수 있다.

또한, 헥사클로로디실란, 트리실란, 옥타클로트리실란 또는 이들의 혼합물을 포함하는 실리콘 소스 가스를 사용하여 베리어막 상에 실리콘 질화물을 포함하는 트랩핑막을 형성한다. 트랩핑막은 상대적으로 낮은 온도에서 형성될 수 있기 때문에 트랩핑막의 형성 속도가 상대적으로 느리다. 따라서 트랩핑막의 두께를 효과적으로 제어할 수 있다. 또한, 트랩핑막은 상대적으로 높은 트랩 밀도를 가질 수 있다. 그리고 베리어막과 기판 사이에 위치하는 계면 특성을 개선할 수 있다.

이하, 본 발명의 실시예들에 따른 불휘발성 메모리 장치 및 이의 제조 방법을 첨부된 도면들을 참조하여 상세하게 설명하겠지만, 본 발명이 하기의 실시예들에 의하여 제한되는 것은 아니다. 따라서 해당 분야에서 통상의 지식을 가진 당업자라면 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정하거나 변경할 수 있을 것이다.

첨부된 도면들에서 구성 요소들의 크기는 본 발명을 보다 용이하게 설명하기 위하여 실제보다 확대 또는 축소되었을 수 있다. 제1 구성 요소 "상에" 제2 구성 요소가 형성된다고 언급되는 경우 제2 구성 요소가 제1 구성 요소와 접하면서 제1 구성 요소의 위쪽에 형성됨을 의미할 수도 있지만 제1 구성 요소와 제2 구성 요소 사이에 제3 구성 요소가 개재될 수도 있다.

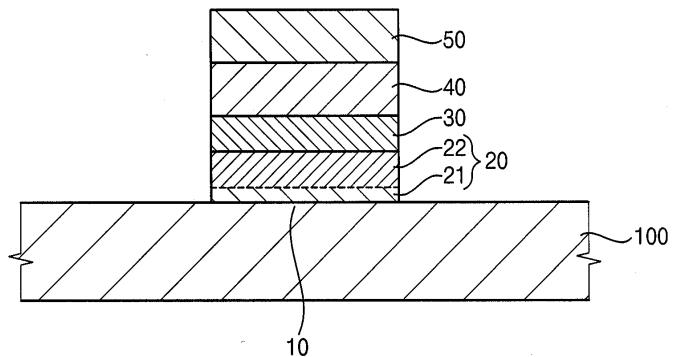

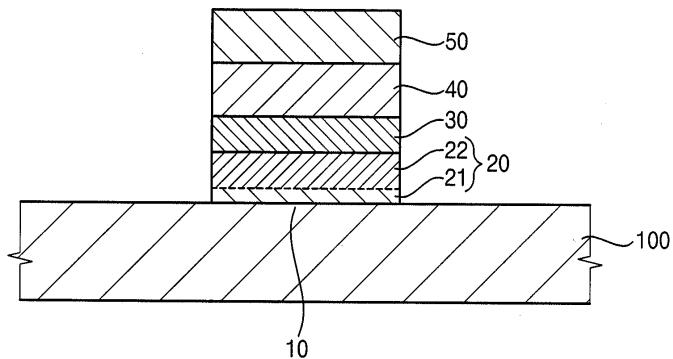

도 1은 본 발명의 일 실시예에 따른 불휘발성 메모리 장치를 나타내는 단면도이다.

도 1을 참조하면, 불휘발성 메모리 장치(1000)는 채널 영역(10)을 갖는 기판(100), 베리어막 패턴(20), 트랩핑막 패턴(30), 블록킹막 패턴(40) 및 게이트 전극막 패턴(50)을 포함한다.

구체적으로 기판(100)의 채널 영역(10) 상에 에너지 장벽의 역할을 하는 베리어막 패턴(20)이 위치한다. 베리어막 패턴(20)은 실리콘 산화물로 이루어진 하부(21)와 실리콘 질화물로 이루어진 상부(22)를 포함한다. 베리어막 패턴(20)은 기판(100) 상에 형성되는 실리콘 산화막의 상부에 암모니아( $\text{NH}_3$ )를 포함하는 반응 가스를 사용하는 라디칼 질화 공정을 수행한 후 상기 실리콘 산화막을 부분적으로 침식하여 형성한다. 따라서 하부(21)와 상부(22)의 사이에는 계면(interface)이 존재하지 않는다.

하부(21)의 두께가 약 15Å 미만인 경우 에너지 장벽으로서의 역할을 효과적으로 수행할 수 없다는 문제점이 있다. 반면에 하부(21)의 두께가 약 50Å을 초과하면 불휘발성 메모리 장치의 동작 전압이 상대적으로 증가한다는 문제점이 있다. 따라서 하부(21)의 두께는 약 15Å 내지 약 50Å일 수 있다.

상부(22)는 라디칼 질화 공정을 통해서 형성되기 때문에 상대적으로 치밀한 구조를 갖는 동시에 상대적으로 작은 수의 실리콘-실리콘 결합을 갖는다. 따라서 상부(22)는 상대적으로 낮은 트랩 밀도를 갖는다.

상부(22)의 두께가 약 10Å 미만인 경우 에너지 장벽으로서의 역할을 효과적으로 수행할 수 없다는 문제점이 있다. 반면에 상부(22)의 두께가 200Å을 초과하는 경우 상기 불휘발성 메모리 장치의 동작 전압이 상대적으로 높다는 문제점이 있다. 따라서 상부(22)의 두께는 약 10Å 내지 약 200Å일 수 있다.

베리어막 패턴(20) 상에 실리콘 질화물을 포함하는 트랩핑막 패턴(30)이 위치한다. 트랩핑막 패턴(30)은 헥사클로로디실란(HCS;  $\text{Si}_2\text{Cl}_6$ ), 트리실란( $\text{Si}_3\text{H}_8$ ), 옥타클로로트리실란( $\text{Si}_3\text{Cl}_8$ ) 또는 이들의 혼합물을 포함하는 실리콘 소스 가스와 암모니아와 같은 질소 소스 가스를 사용하는 화학 기상 증착 공정 또는 원자층 증착 (atomic layer deposition; ALD) 공정을 통하여 형성되기 때문에 실리콘-실리콘 결합을 상대적으로 많이 포함하고 있다. 따라서 트랩핑막 패턴(30)은 베리어막 패턴(20)의 상부(22)보다 실질적으로 큰 트랩 밀도를 갖는다.

트랩핑막 패턴(30)의 두께가 약 10Å 미만인 경우, 트랩 수가 상대적으로 적어 캐리어들을 효과적으로 트랩할 수 없다는 문제점이 있다. 반면에 트랩핑막 패턴(30)의 약 200Å을 초과하는 경우, 불휘발성 메모리 장치를 동작하는데 필요한 동작 전압이 상대적으로 증가한다는 문제점이 있다. 따라서 트랩핑막 패턴(30)의 두께는 약 10Å 내지 약 200Å일 수 있다.

트랩핑막 패턴(30) 상에 블록킹막 패턴(40) 및 게이트 전극막 패턴(50)이 순차적으로 위치한다. 블록킹막 패턴(40)은 고유전 물질을 포함할 수 있다. 게이트 전극막 패턴(50)은 도핑된 폴리실리콘과 같은 도전성 물질을 포함할 수 있다.

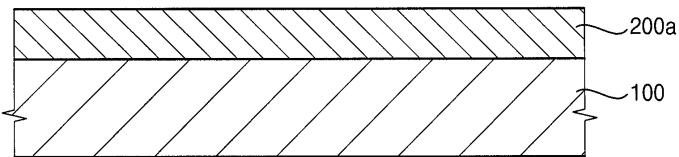

도 2 내지 6은 도 1에 도시된 불휘발성 메모리 장치의 제조 방법을 설명하기 위한 단면도들이다.

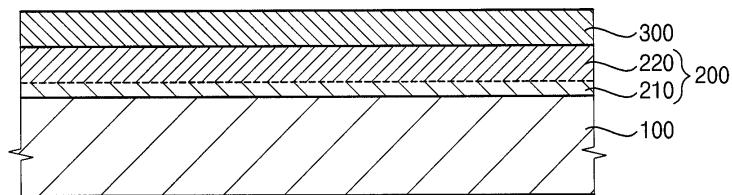

도 2를 참조하면, 기판(100) 상에 산화막(200a)을 형성한다. 산화막(200a)은 열 산화(thermal oxidation) 공정, 화학 기상 증착(chemical vapor deposition; CVD) 공정 또는 라디칼 산화(radical oxidation) 공정을 사용하여 형성할 수 있다.

산화막(200a)은 후속 공정에 의해서 실리콘 산화물로 이루어지는 하부층(210) 및 실리콘 질화물로 이루어지는 상부층(220)을 포함하는 베리어막(200)으로 형성된다. 베리어막(200)에 포함되는 하부층(210) 및 상부층(220)은 에너지 장벽들의 역할을 한다.

불휘발성 반도체 메모리 장치의 저장된 데이터를 보존하는 능력은 에너지 장벽들로서의 역할을 하는 하부층(210) 및 상부층(220)의 신뢰성에 주로 의존한다. 따라서 상부층(210) 및 하부층(220)은 프로그래밍 동작과 소거 동작을 반복하는 횟수에 제한적인 요소로 작용한다. 통상적인 불휘발성 반도체 메모리 장치는 적어도 약 100만회 이상의 프로그래밍 동작과 소거 동작을 반복할 수 있을 것이 요구된다.

따라서 후속하여 하부층(210) 및 상부층(220)을 포함하는 베리어막(200)으로 형성되는 산화막(200a)은 약 1Torr 이하의 낮은 압력, 약 800°C 이상의 온도, 그리고 산소( $\text{O}_2$ ), 수소( $\text{H}_2$ ) 및 질소( $\text{N}_2$ ) 가스 분위기 하에서 라디칼 산화 공정을 이용하여 형성하는 것이 바람직하다.

이는 상기 라디칼 산화 공정에 의하여 산화막(200a)을 형성할 경우, 산화막(200a)의 치밀성을 증가시킨 수 있다는 장점이 있기 때문이다. 또한 산화막(200a)의 두께를 적절하게 조절할 수 있다는 장점이 있기 때문이다.

산화막(200a)의 두께가 약 25Å 미만인 경우, 베리어막(200)의 두께가 상대적으로 얇아 베리어막(200)이 에너지 장벽으로서의 역할을 충분히 수행하지 못하는 문제점이 있다. 반면에 산화막(200a)의 두께가 250Å을 초과하는 경우, 베리어막(200)의 두께가 상대적으로 두꺼워져서 불휘발성 메모리 장치의 동작 전압이 증가하는 문제점이 있다. 따라서 산화막(200a)의 두께는 약 25Å 내지 약 250Å인 것이 바람직하다.

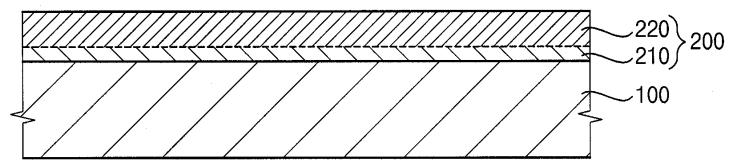

도 3을 참조하면, 산화막(200a)의 상부에 라디칼 질화 공정을 수행하여 실리콘 산화물로 이루어진 하부층(210) 및 실리콘 질화물로 이루어진 상부층(220)을 포함하는 베리어막(200)을 형성한다.

일본 특허 제2002-203917호에는 테트라클로로 실란(TCS;  $\text{SiCl}_4$ )을 사용하는 화학 기상 증착 공정에 의해서 터널 산화막 상에 제1 질화막을 형성하는 것을 특징으로 하는 불휘발성 메모리 장치의 형성 방법이 개시되어 있다. 그러나 상기 화학 기상 증착 공정에 의해서 상기 제1 질화막을 형성하는 경우 터널 산화막과 제1 질화막 사이에 계면이 발생하여 상기 계면에서 캐리어들이 트랩되거나 상기 계면에서 캐리어들의 에너지가 감소되는 문제점이 있었다.

또한 상기 화학 기상 증착 공정에 의해서 상기 제1 질화막을 형성하는 경우, 상기 제1 질화막의 두께를 효과적으로 조절할 수 없어 상기 제1 질화막의 두께 균일도(thickness uniformity)가 상대적으로 낮다는 문제점이 있었다.

그리고 상기 화학 기상 증착 공정에 의해서 상기 제1 질화막을 형성하는 경우, 상기 제1 질화막이 치밀한 구조를 가지지 못하기 때문에 상기 질화막의 트랩 밀도(trap density)가 상대적으로 크다는 문제점이 있었다.

따라서 본 발명에서는 산화막(200a)의 상부에 라디칼 질화 공정을 수행하여 실리콘 산화물로 이루어진 하부층(210) 및 실리콘 질화물로 이루어진 상부층(220)을 포함하는 베리어막(200)을 형성한다.

구체적으로 암모니아( $\text{NH}_3$ )를 포함하는 반응 가스를 사용하는 라디칼 질화 공정을 통하여 베리어막(200)을 형성할 수 있다. 상기 반응 가스는 질소( $\text{N}_2$ ) 가스를 포함할 수 있다. 또한, 상기 반응 가스는 테트라클로로실란, 디클로로실란(DCS;  $\text{SiH}_2\text{Cl}_2$ ) 또는 이들의 혼합물을 포함할 수 있다.

상기 라디칼 질화 공정에 의해서 베리어막(200)을 형성하는 경우, 하부층(210) 및 상부층(220)의 사이에 계면이 형성되지 않기 때문에 하부층(210) 및 상부층(220)의 사이에서 캐리어들이 트랩되지 않는다는 장점이 있다. 또한 하부층(210) 및 상부층(220)의 사이에서 캐리어들의 에너지가 감소되지 않는다는 장점이 있다.

또한 상기 라디칼 질화 공정에 의해서 베리어막(200)을 형성하는 경우, 상부층(220)의 두께를 효과적으로 조절할 수 있기 때문에 상부층(220)의 두께 균일도가 상대적으로 크다는 장점이 있다.

그리고 상부층(220)은 라디칼 질화 공정을 통해서 형성되기 때문에 상대적으로 치밀한 구조를 갖는 동시에 상대적으로 작은 수의 실리콘-실리콘 결합을 갖는다. 따라서 상부층(220)은 상대적으로 낮은 트랩 밀도를 갖는다는 장점이 있다.

상부층(220)의 두께가 약 10Å 미만인 경우 에너지 장벽으로서의 역할을 효과적으로 수행할 수 없다는 문제점이 있다. 반면에 상부층(220)의 두께가 200Å을 초과하는 경우 상기 불휘발성 메모리 장치의 동작 전압이 상대적으로 높다는 문제점이 있다. 따라서 상부층(220)의 두께는 약 10Å 내지 약 200Å일 수 있다.

하부층(210)의 두께가 약 15Å 미만인 경우 에너지 장벽으로서의 역할을 효과적으로 수행할 수 없다는 문제점이 있다. 반면에 하부층(210)의 두께가 약 50Å을 초과하면 상기 불휘발성 메모리 장치의 동작 전압이 상대적으로 증가한다는 문제점이 있다. 따라서 하부층(210)의 두께는 약 15Å 내지 약 50Å일 수 있다.

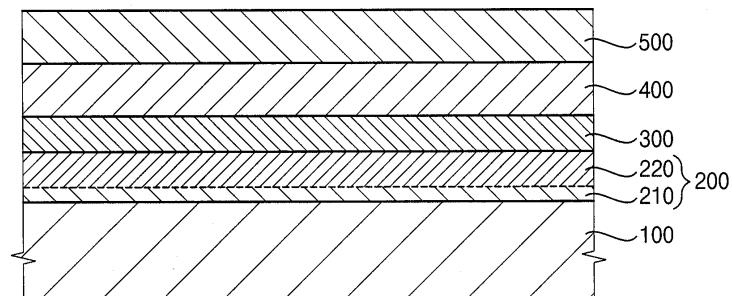

도 4를 참조하면, 베리어막(200) 상에 실리콘 질화물을 포함하는 트랩핑막(300)을 형성한다.

일본 특허 제2002-203917호에는 디클로로실란을 사용하는 화학 기상 증착 공정을 통해 상기 제1 질화막 상에 제2 질화막을 형성하는 것을 특징으로 하는 불휘발성 메모리 장치의 제조 방법이 개시되어 있다.

그러나 디클로로실란을 사용하여 상기 제2 질화막을 형성하는 경우, 상기 디클로로실란의 흡착 계수(sticking coefficient)가 상대적으로 크기 때문에 단차 도포성(step coverage)이 상대적으로 작다. 따라서 상기 제2 질화막의 두께 균일성이 감소한다는 문제점이 있다.

또한 디클로로실란을 사용하여 상기 제2 질화막을 형성하는 경우, 약 700°C 이상의 온도에서 상기 제2 질화막이 형성되기 때문에 상기 제2 질화막의 형성 속도가 상대적으로 높아 상기 제2 질화막의 두께를 효과적으로 제어할 수 없다는 문제점이 있다.

따라서 본 발명에서는 헥사클로로디실란(HCS;  $\text{Si}_2\text{Cl}_6$ ), 트리실란( $\text{Si}_3\text{H}_8$ ), 옥타클로트리실란( $\text{Si}_3\text{Cl}_8$ ) 또는 이들의 혼합물을 포함하는 실리콘 소스 가스와 암모니아( $\text{NH}_3$ )와 같은 질소 소스 가스를 사용하여 트랩핑막(300)을 형성한다. 트랩핑막(300)은 화학 기상 증착 공정 또는 원자층 증착 (atomic layer deposition; ALD) 공정에 의해서 형성될 수 있다.

상기 실리콘 소스 가스를 사용하여 트랩핑막(300)을 형성하는 경우, 상기 실리콘 소스 가스의 흡착 계수(sticking coefficient) 상대적으로 작기 때문에 단차 도포성이 상대적으로 크다. 따라서 트랩핑막(300)의 두께 균일성이 증가한다는 장점이 있다.

또한, 상기 실리콘 소스 가스를 사용하여 트랩핑막(300)을 형성하는 경우, 약 450°C 내지 약 650°C의 온도에서 트랩핑막(300)을 형성할 수 있기 때문에 트랩핑막(300)의 형성 속도가 상대적으로 낮아 트랩핑막(300)의 두께를 효과적으로 제어할 수 있다는 장점이 있다.

그리고 상기 실리콘 소스 가스는 디클로로실란 가스보다 실리콘-실리콘 결합을 많이 포함하고 있다. 일반적으로 실리콘-실리콘 결합의 수가 증가하는 경우 트랩 밀도도 증가하기 때문에 상기 실리콘 소스 가스를 사용하여 트랩핑막(300)을 형성하는 경우 트랩핑막(300)은 상대적으로 높은 트랩 밀도를 가질 수 있는 장점이 있다.

이와 더불어 헥사클로로디실란 또는 옥타클로로트리실란은 디클로로실란보다 염소를 많이 포함하고 있다. 일반적으로 염소는 베리어막(200)과 기판(100)의 사이에 위치하는 계면으로 유입되어 계면 특성을 개선시킨다. 따라서 헥사클로로디실란 또는 옥타클로로트리실란을 사용하여 트랩핑막(300)을 형성하는 경우 상기 계면 특성이 디클로로실란을 사용할 때 보다 개선되어 채널 영역 내에 채널을 효과적으로 형성할 수 있다는 장점이 있다.

트랩핑막(300)을 형성할 때의 온도가 약 450°C 미만인 경우, 염화 암모늄( $\text{NH}_4\text{Cl}$ )과 같은 부산물이 발생하기 때문에 바람직하지 않다. 반면에 트랩핑막(300)을 형성할 때의 온도가 약 650°C를 초과하는 경우 트랩핑막(300)의 형성 속도가 상대적으로 높아 트랩핑막(300)의 두께를 효과적으로 제어할 수 없다는 단점이 있다. 따라서 트랩핑막(300)을 형성할 때의 온도는 약 450°C 내지 약 650°C일 수 있다.

트랩핑막(300)의 두께가 약 10Å 미만인 경우, 트랩 수가 상대적으로 적어 캐리어들을 효과적으로 트랩할 수 없다는 문제점이 있다. 반면에 트랩핑막(300)의 두께가 약 200Å을 초과하는 경우, 불휘발성 메모리 장치를 동작하는데 필요한 동작 전압이 상대적으로 증가한다는 문제점이 있다. 따라서 트랩핑막(300)의 두께는 약 10Å 내지 약 200Å일 수 있다.

도 5를 참조하면, 트랩핑막(300) 상에 블록킹막(400) 및 게이트 전극막(500)을 순차적으로 형성한다. 블록킹막(400)은 고유전 물질을 포함할 수 있으며 게이트 전극막(500)은 도핑된 폴리실리콘과 같은 도전성 물질을 포함할 수 있다.

도 6을 참조하면, 게이트 전극막(500), 블록킹막(400), 트랩핑막(300), 베리어막(200)을 순차적으로 씌어하여 게이트 전극막 패턴(50), 블록킹막 패턴(40), 트랩핑막 패턴(30) 및 베리어막 패턴(20)을 형성한다. 베리어막 패턴(20)은 하부(21) 및 상부(22)를 포함한다. 따라서 기판(100), 베리어막 패턴(20), 트랩핑막 패턴(30), 블록킹막 패턴(40) 및 게이트 전극막 패턴(50)을 포함하는 불휘발성 메모리 장치(1000)가 형성된다. 베리어막 패턴(20)의 아래에 위치한 기판(100)의 일부는 채널 영역(10)으로 사용된다.

### 발명의 효과

본 발명에 따르면, 라디칼 질화 공정을 통해 실리콘 질화물로 이루어진 상부와 실리콘 산화물로 이루어진 하부를 포함하는 베리어막 패턴이 형성된다. 따라서 상부와 하부 사이에는 계면이 존재하지 않을 수 있다는 장점이 있다. 또한, 상부의 두께

를 효과적으로 조절할 수 있기 때문에 상부는 상대적으로 큰 두께 균일도를 가질 수 있다. 그리고 상부는 상대적으로 치밀한 구조를 갖는 동시에 상대적으로 작은 수의 실리콘-실리콘 결합을 갖기 때문에 상부는 상대적으로 낮은 트랩 밀도를 가질 수 있다.

또한, 헥사클로로디실란, 트리실란, 옥타클로트리실란 또는 이들의 혼합물을 포함하는 실리콘 소스 가스를 사용하여 베리어막 상에 실리콘 질화물을 포함하는 트랩핑막을 형성한다. 트랩핑막은 상대적으로 낮은 온도에서 형성될 수 있기 때문에 트랩핑막의 형성 속도가 상대적으로 느린다. 따라서 트랩핑막의 두께를 효과적으로 제어할 수 있다. 또한, 트랩핑막은 상대적으로 높은 트랩 밀도를 가질 수 있다. 그리고 베리어막과 기판 사이에 위치하는 계면 특성을 개선할 수 있다.

본 발명의 바람직한 실시예들을 참조하여 설명하였지만 해당 기술 분야의 숙련된 당업자라면 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 도면의 간단한 설명

도 1은 본 발명의 일 실시예에 따른 불휘발성 메모리 장치를 나타내는 단면도이다.

도 2 내지 6은 도 1에 도시된 불휘발성 메모리 장치의 형성 방법을 나타내는 단면도들이다.

<도면의 주요 부분에 대한 부호의 설명>

10: 채널 영역 21: 하부

22: 하부 30: 트랩핑막 패턴

40: 블록킹막 패턴 50: 게이트 전극막 패턴

100: 기판 200a: 산화막

200: 베리어막 210: 터널 산화막

220: 제1 질화막 300: 트랩핑막

400: 블록킹막 500: 게이트 전극막

### 도면

#### 도면1

1000

도면2

도면3

도면4

도면5

도면6

1000